# **UCLA**

### **UCLA Electronic Theses and Dissertations**

#### **Title**

Effects of Cooling on the Overall Power Consumption of Processors

### **Permalink**

https://escholarship.org/uc/item/0pn4n7hs

### **Author**

Park, Won Ho

### **Publication Date**

2012

Peer reviewed|Thesis/dissertation

### UNIVERSITY OF CALIFORNIA

## Los Angeles

Effects of Cooling on the Overall Power Consumption of Processors

A dissertation submitted in partial satisfaction of the requirements for the degree Doctor of Philosophy in Electrical Engineering

by

Won Ho Park

© Copyright by

Won Ho Park

2012

### ABSTRACT OF THE DISSERTATION

Effects of Cooling on the Overall Power Consumption of Processors

by

#### Won Ho Park

Doctor of Philosophy in Electrical Engineering

University of California, Los Angeles, 2012

Professor Chih-Kong Ken Yang, Chair

To address the power and thermal problems of high-performance computing systems, the possibility of using advance cooling systems is explored to realize overall system power improvement that includes the cost of cooling power. Realistic system-level modeling that includes the electronic and refrigeration systems will expedite the analysis of the optimal operating temperature points, the amount of total power reduction at reduced temperatures, and the dependence of the refrigerated performance on the power profile of the electronics. Highly-efficient miniature-scale refrigeration system for electronic cooling is developed to experimentally demonstrate the amount of total power saving for processors at various operating conditions. A processor that dissipates 175.4W of maximum power with 30% electronic leakage power operating at 97°C is cooled using our refrigeration system. Measurements show that with a minimum refrigeration COP of 2.7, the processor operates with junction temperature <40°C and offers a 25% total system power reduction over the non-refrigerated design. Not only the measurement results validate our system-level model,

but this experiment is the *first demonstration* of active cooling that lead to reduced total wall power. Furthermore, a model that captures different relations and parameters of multicore processor and the refrigeration system is constructed based on the measured results. This model is used to present an energy-efficient workload scheduling that optimizes power efficiency under the actively cooled environment that can potentially be applied to large scale multi-core, multi-processor computing environment. Finally the proposed methodology is combined with the G/G/m-models to reduce both total power and response time degradation while meeting target SLA requirements.

| ne dissertation of won Ho Park is app | proved.                             |

|---------------------------------------|-------------------------------------|

|                                       |                                     |

|                                       |                                     |

| -                                     | Youngho Ju                          |

|                                       |                                     |

| -                                     | Jason Woo                           |

|                                       |                                     |

| -                                     | Dejan Markovic                      |

|                                       |                                     |

| -                                     | Chih-Kong Ken Yang, Committee Chair |

|                                       |                                     |

University of California, Los Angeles

2012

# TABLE OF CONTENTS

| CHAPTER 1 Introduction                                                   | 1  |

|--------------------------------------------------------------------------|----|

| 1.1 Motivation                                                           | 2  |

| 1.2 Organization                                                         | 8  |

| CHAPTER 2 Background                                                     | 11 |

| 2.1 Electronic System with Vapor Compression Refrigeration               | 13 |

| 2.1.1 Sources of Electronic Power.                                       | 16 |

| 2.1.2 Cooling Power and Refrigeration Efficiency                         | 21 |

| 2.2 Electronic System with Embedded Thermoelectric Coolers               | 23 |

| 2.2.1 Electronic Profile of Modern Microprocessors                       | 24 |

| 2.2.2 Embedded Thermoelectric Coolers                                    | 28 |

| 2.2.3 Performance of eTEC                                                | 31 |

| 2.3 Common Power Saving Techniques in Multi-Core Multi-Processor Systems | 33 |

| 2.3.1 Basic Power Saving Techniques                                      | 34 |

| 2.3.2 G/G/m Model for Capacity Planning                                  | 35 |

| 2.4 Summary                                                              | 38 |

| CHAPTER 3 Analysis of Refrigeration Requirements for Electronic Cooling  | 41 |

| 3.1 Cooling a Microprocessor                                             | 42 |

| 3.2 Varying P <sub>leakage</sub> /P <sub>electric</sub> Ratios           | 44 |

| 3.3 Varying Cooling Parameters                                           | 52 |

| 3.4 Summary                                                              | 55 |

| CHAPTER 4 Analysis of eTEC-based Cooling                                 | 57 |

| 4.1 Cooling a Microprocessor Using eTECs                       | 58  |

|----------------------------------------------------------------|-----|

| 4.2 Results of Cooling a Microprocessor                        | 63  |

| 4.3 Summary                                                    | 66  |

| CHAPTER 5 Measured Results Using Refrigerated Cooling          | 67  |

| 5.1 Overall System Description                                 | 68  |

| 5.2 Performance of the Refrigeration System                    | 71  |

| 5.3 Experimental Results                                       | 74  |

| 5.4 Summary                                                    | 79  |

| CHAPTER 6 Effects of Cooling on Workload Management in HPCs    | 81  |

| 6.1 Multi-Core Processor Under the Actively Cooled Environment | 82  |

| 6.2 Workload Scheduling Methodology                            | 87  |

| 6.3 Assignment of Workload Based on Target SLA                 | 94  |

| 6.4 Summary                                                    | 98  |

| CHAPTER 7 Conclusion                                           | 100 |

| 7.1 Contributions                                              | 100 |

| 7.2 Future Work                                                | 103 |

| Rihliography                                                   | 106 |

# LIST OF FIGURES

| Figure 1-1: (a) Number of worldwide installed bases of data center. (b) Worldwide              |   |

|------------------------------------------------------------------------------------------------|---|

| spending on new servers and operation cost.                                                    | 2 |

| Figure 1-2: Energy breakdown of different data centers.                                        | 3 |

| Figure 1-3: Power breakdown of different types of servers.                                     | 5 |

| Figure 2-1: Three possible configurations of a computing server unit with (a) a typical        |   |

| configuration of a fan for the chassis, (b) dedicated fan-cooling for the processor, and (c) a |   |

| refrigerated-cooling for the processor.                                                        | 4 |

| Figure 2-2: (a) Model of conventional air cooler. (b) Model of the same electric system        |   |

| using a refrigeration system.                                                                  | 6 |

| Figure 2-3: Normalized performance and power as a function of temperature of a 65nm            |   |

| technology device.                                                                             | 8 |

| Figure 2-4: The performance of different refrigeration systems. 2                              | 1 |

| Figure 2-5: Schematic of a thermoelectric cooler.                                              | 4 |

| Figure 2-6: Electronic parameters of three different types of processors with (a) power        |   |

| density of core and last-level cache block at 70°C and 100°C and (b) leakage power ratio o     | f |

| core and last-level cache block at 70°C and 100°C.                                             | 6 |

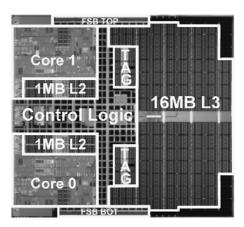

| Figure 2-7: Floorplan of the Xeon processor. (Adapted from [43])                               | 7 |

| Figure 2-8: Electronic parameters of major function components in the core block of the        |   |

| Xeon processor with (a) power density at 70°C and 100°C and (b) leakage power ratio at         |   |

| 70°C and 100°C                                                                                 | 8 |

| Figure 2-9: View of a microelectronic system with embedded TEC locally cooling a                                           |

|----------------------------------------------------------------------------------------------------------------------------|

| functional block. 29                                                                                                       |

| Figure 2-10: The performance curves of an embedded thermoelectric cooler with height and                                   |

| area of 100um and 6.25mm <sup>2</sup> , respectively. (Adapted from[24])                                                   |

| Figure 2-11: A Generic G/G/m model for multi-server systems                                                                |

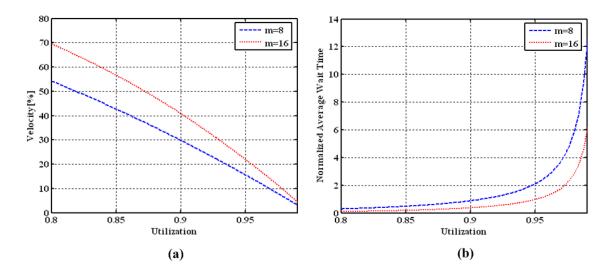

| Figure 2-12: (a) Execution velocity and (b) normalized average wait time at different                                      |

| utilization for m=8 and m=16 processors. 38                                                                                |

| Figure 2-13: Overall simulator framework                                                                                   |

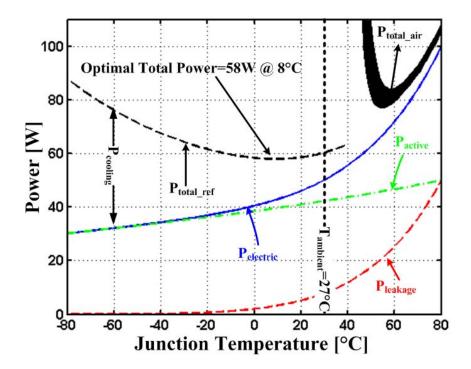

| Figure 3-1: Optimization results of the system with forced-air and refrigerated cooling at                                 |

| Pleakage/Pelectric=50% @ 80°C. 43                                                                                          |

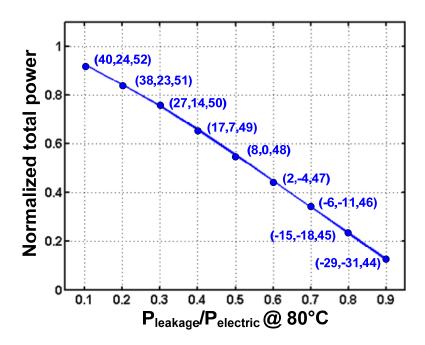

| Figure 3-2: The dependence of the P <sub>leakage</sub> /P <sub>electric</sub> ratio on the optimal total power based on    |

| the simulation using the model. $(x,y,z)$ correspond to optimal operating points of $T_{junction}$                         |

| [°C], $T_{cold}$ [°C] , and the percent of Carnot [%], respectively                                                        |

| Figure 3-3: The dependence of the P <sub>electric0</sub> and leakage ratio on the optimal total power                      |

| based on the simulation using the model. (x,y,z) correspond to junction temperature before                                 |

| refrigeration $T_{junction0}$ [°C], optimal operating points of $T_{junction}$ [°C] , and the percent of                   |

| Carnot [%], respectively                                                                                                   |

| Figure 3-4: Contours of the percentage of power reduction for different $P_{leakage}/P_{electric}$ and                     |

| $P_{\text{electric0}}$ before any refrigeration. (x,y) correspond to $T_{\text{junction0}}$ [°C] before refrigeration, and |

| optimal junction temperature after refrigeration T <sub>junction</sub> [°C], respectively47                                |

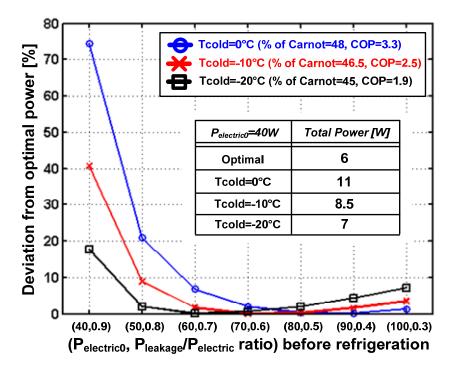

| Figure 3-5: Effect on the overall system performance when T <sub>cold</sub> is kept to a fixed                             |

| temperature. Varying fixed temperatures are used. The COP at each T <sub>cold</sub> corresponds to the                     |

| achievable COP of that temperature. The table shows the total power after refrigeration                                 |

|-------------------------------------------------------------------------------------------------------------------------|

| when P <sub>electric0</sub> is 40W. 49                                                                                  |

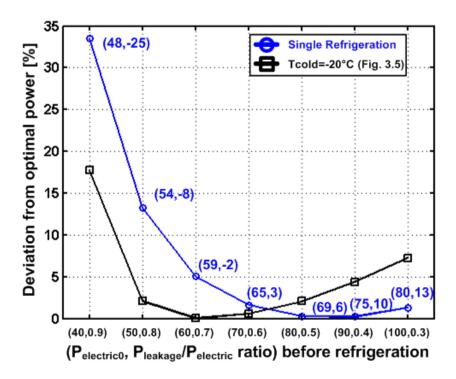

| Figure 3-6: The effect on the overall system performance, assuming single refrigeration                                 |

| system is being used. $(x,y)$ correspond to junction temperature before refrigeration $T_{junction0}$                   |

| [°C], adapted T <sub>junction</sub> [°C] using single refrigeration system. 51                                          |

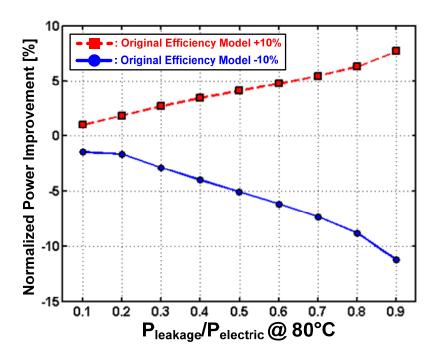

| Figure 3-7: The sensitivity of the power to a change in refrigeration efficiency data. The                              |

| results are normalized with respect to Figure 3.2. 52                                                                   |

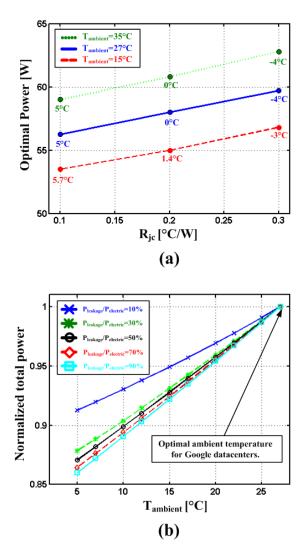

| Figure 3-8: (a) System performance while varying R <sub>jc</sub> and T <sub>ambient</sub> at P <sub>electrio0</sub> and |

| $P_{leakage}/P_{electric}$ =50%. The corresponding optimal $T_{cold}$ are also shown. (b) The effect on the             |

| overall performance from varying T <sub>ambient</sub> . Normalization is done with respect to the total                 |

| power when T <sub>ambient</sub> is at 27°C. 54                                                                          |

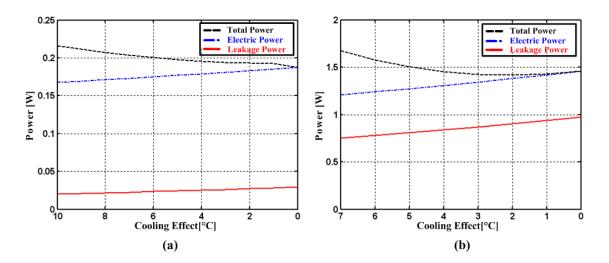

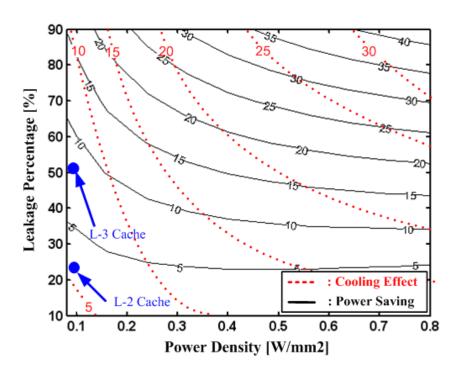

| Figure 4-1: Optimization results of localized cooling (a) Branch Predictor and (b) L-3                                  |

| Cache. 58                                                                                                               |

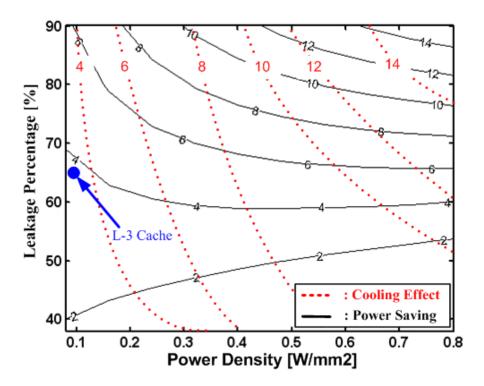

| Figure 4-2: Contours of the percentage of power reduction and amount of cooling effect for                              |

| different P <sub>leakage</sub> /P <sub>electric</sub> and power before any refrigeration.                               |

| Figure 4-3: Effect on the overall system performance to obtain 10 degree of cooling effect                              |

| using eTEC with thermoelectric material of ZT=0.5.                                                                      |

| Figure 4-4: Contours of the percentage of power reduction and amount of cooling effect for                              |

| different P <sub>leakage</sub> /P <sub>electric</sub> and power before any refrigeration with ZT=162                    |

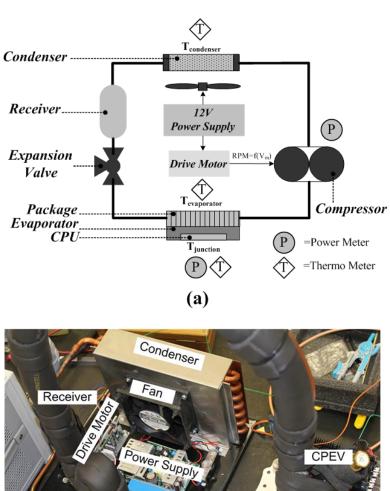

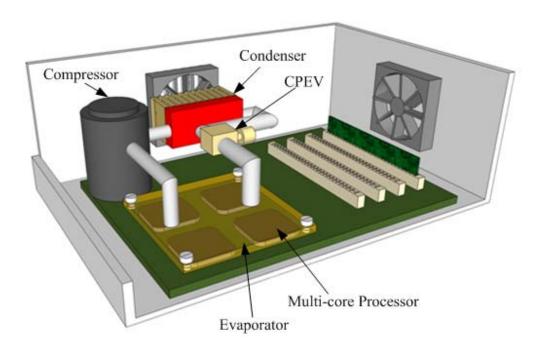

| Figure 5-1: (a) Layout and (b) photograph of the refrigeration system for electronic cooling.                           |

| 69                                                                                                                      |

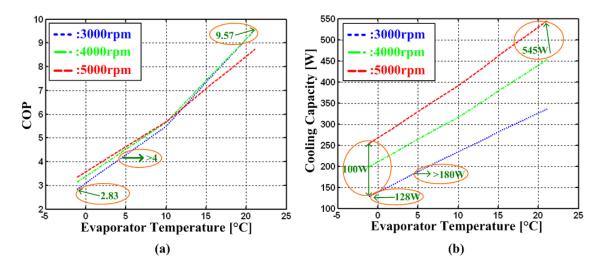

| Figure 5-2: (a) COP and (b) Cooling capacity versus evaporator temperature at various                     |

|-----------------------------------------------------------------------------------------------------------|

| compressor speeds for condenser temperature of 27°C                                                       |

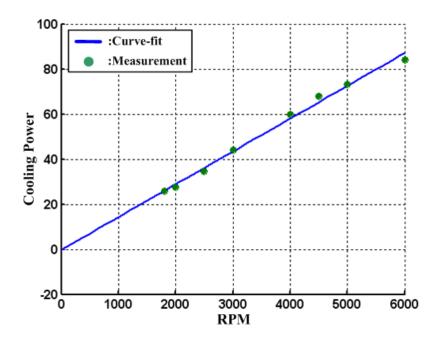

| Figure 5-3: Cooling power versus RPM. 73                                                                  |

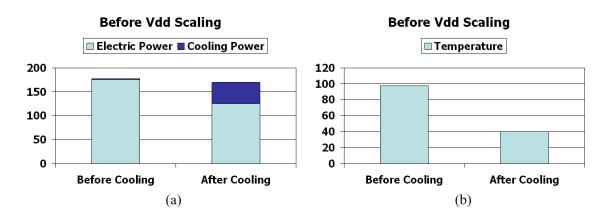

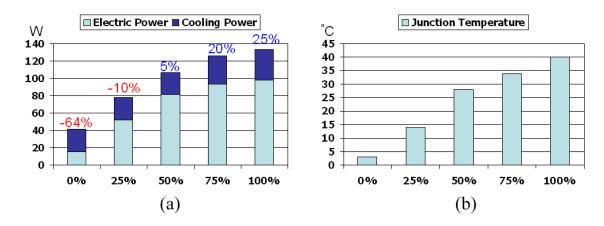

| Figure 5-4: Measurement results of the refrigerated cooling system before $V_{dd}$ scaling 75             |

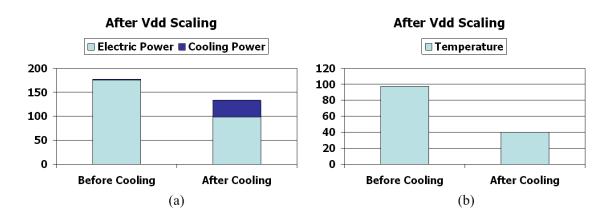

| Figure 5-5: Measurement results of the refrigerated cooling system after $V_{dd}$ scaling76               |

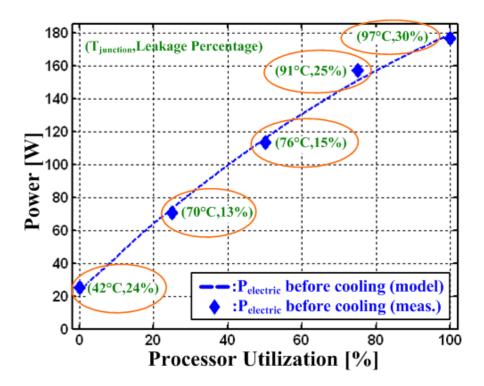

| Figure 5-6: Power and operating junction temperature (T <sub>junction</sub> ) at different utilization    |

| percentage before refrigeration. (x,y) correspond to operating T <sub>junction</sub> [°C] and the percent |

| of leakage power [%], respectively                                                                        |

| Figure 5-7: Measurement results of refrigeration cooling at different processor utilization.              |

|                                                                                                           |

| Figure 5-8: Result of the simulation of the total power at different processor utilization                |

| using the model from Section 2.1                                                                          |

| Figure 6-1: Configuration of a multi-processor computing server unit with a refrigerated-                 |

| cooling. 82                                                                                               |

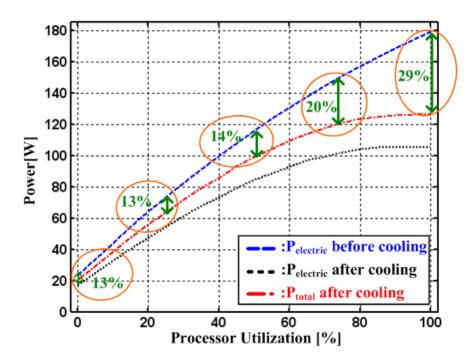

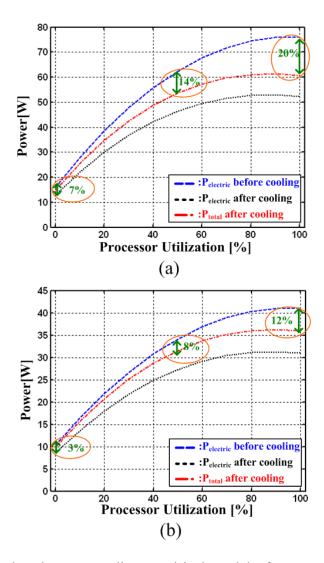

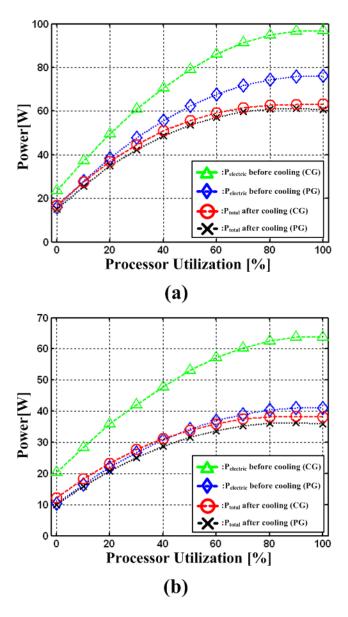

| Figure 6-2: Measured and corresponding empirical model of power consumption before                        |

| and after cooling across different processor utilization levels when (a) 2, or (b) 1 core out of          |

| the 4-core processor is powered up. The associated power savings after electronic cooling is              |

| also shown in the figure                                                                                  |

| Figure 6-3: Power consumption across different utilization level before and after cooling                 |

| using PG and CG as the core stopping techniques for (a) 2-core and (b) 1-core processor. 86               |

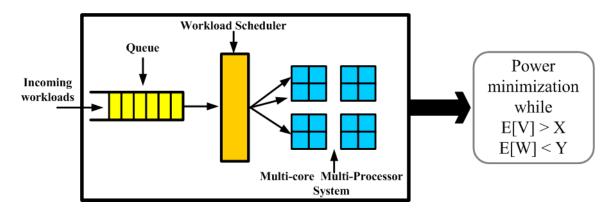

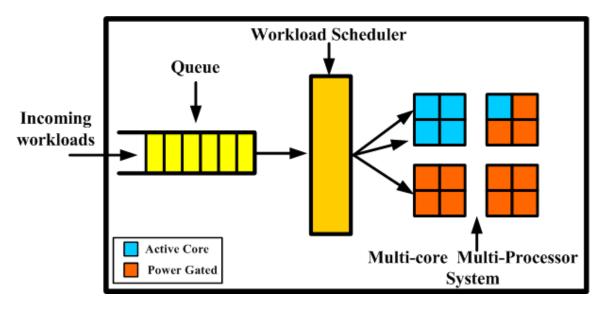

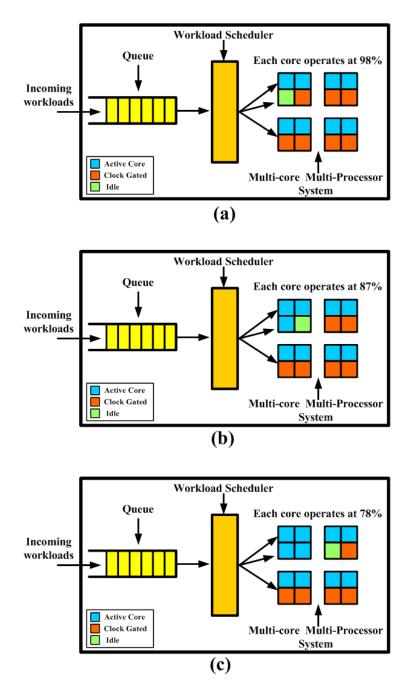

| Figure 6-4: Generic workload scheduling management for multi-core multi-processor                         |

| computing system87                                                                                        |

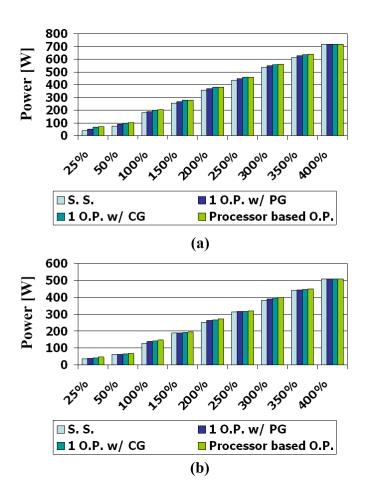

| Figure 6-5: Power at different utilization (a) before and (b) after electronic coo | oling for     |

|------------------------------------------------------------------------------------|---------------|

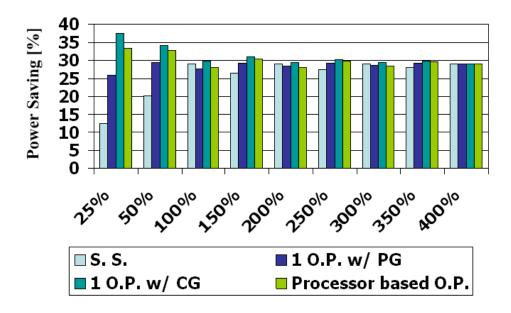

| different methodologies.                                                           | 89            |

| Figure 6-6: Associated power savings at different utilization level from electro   | nic cooling   |

| for different workload assignment methodologies.                                   | 90            |

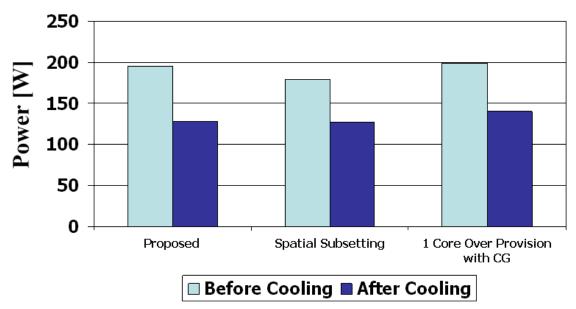

| Figure 6-7: Proposed methodology.                                                  | 91            |

| Figure 6-8: Proposed methodology compared with (B) spatial subsetting and (        | C) 1 core     |

| over-provision with CG.                                                            | 91            |

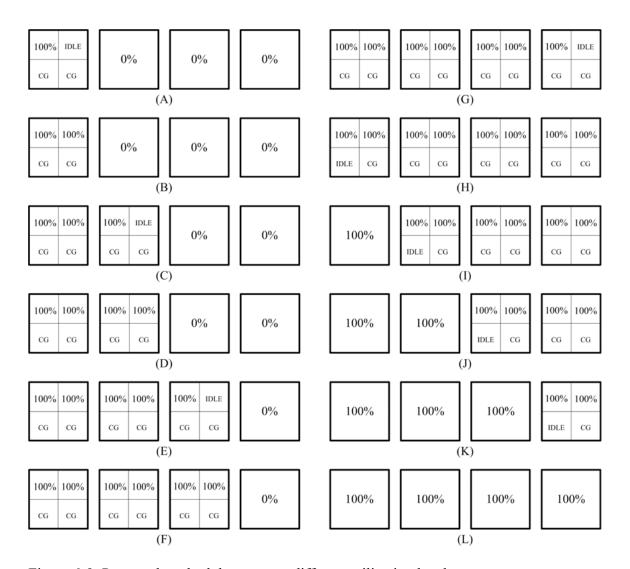

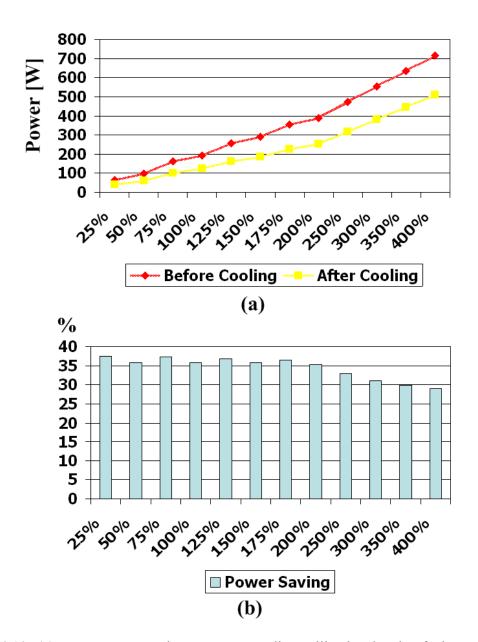

| Figure 6-9: Proposed methodology across different utilization levels               | 92            |

| Figure 6-10: (a) Power consumption at corresponding utilization levels of Figure   | ire 6.9. (b)  |

| The associated power saving from electronic cooling                                | 93            |

| Figure 6-11: Required utilization level across different number of processors (l   | M) for the    |

| proposed methodology.                                                              | 95            |

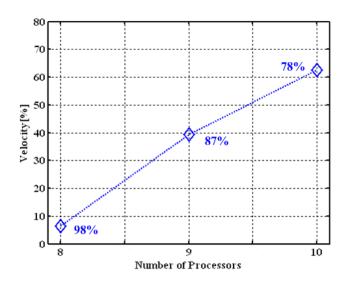

| Figure 6-12: Execution velocity vs. number of processors. Number in the figure     | e represents  |

| required utilization level.                                                        | 96            |

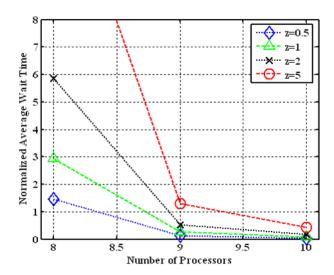

| Figure 6-13: Normalized average wait time vs. number of processors as function     | on of         |

| workload variability z=0.5, 1.0, 2.0, 5.0.                                         | 96            |

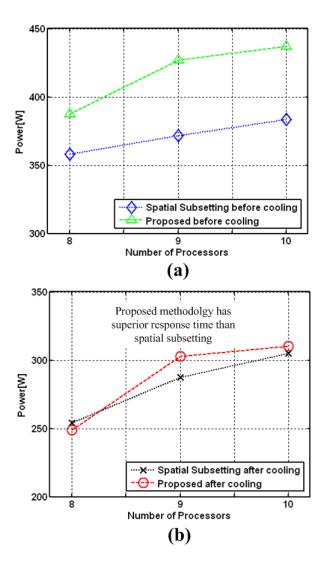

| Figure 6-14: Power consumption vs. number of processors (a) before and (b) a       | fter cooling. |

|                                                                                    | 97            |

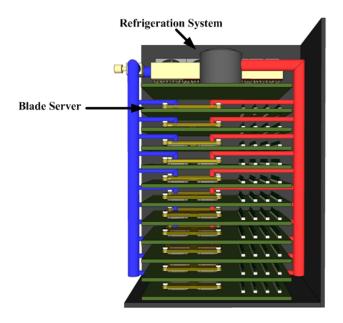

| Figure 7-1: Configuration of a server rack with refrigerated-cooling               | 103           |

| Figure 7-2: Future datacenters with refrigerated server racks                      | 105           |

# LIST OF TABLES

| Table 2.1 International Technology Roadmap for Semiconductors 2008. ( ¹:Normalized to        |

|----------------------------------------------------------------------------------------------|

| Full-Chip leakage power dissipation in 2007)                                                 |

| Table 2.2: Leakage percentage (a) for various functional blocks within a                     |

| microprocessor [28] and (b) for various types of integrated circuits                         |

| Table 3.1: The model parameters used in the example of Section 3.1                           |

| Table 4.1: Simulation result of fine-grain cooling each of the functional blocks from Figure |

| 2.8                                                                                          |

| Table 4.2: Overall power saving [%] of cooling L-2 and L-3 cache at different technology     |

| nodes65                                                                                      |

| Table 5.1: Performance summary of the microprocessor using a conventional forced-air         |

| convection cooling                                                                           |

# ACKNOWLEDGMENTS

I would like to thank my advisor, Professor Chih-Kong Ken Yang, for his continuous guidance and patience throughout the course of my research and thesis.

### VITA

2005 B.S. in Electrical Engineering

Korea University

Seoul, Korea

2008 M.S. in Electrical Engineering

University of California, Los Angeles

Los Angeles, California, USA

2006-2012 Graduate Student Researcher

High-Performance Mixed-Mode Circuit Design Group

Department of Electrical Engineering University of California, Los Angeles

Los Angeles, California, USA

Summer 2006 Intern, Samsung Advanced Institute of Technology, Inc,

Kihung, Korea

Summer 2008 Intern, Samsung Semiconductors, Inc, Hwasung, Korea

Summer Intern, Texas Instruments, Dallas, Texas, USA

2009 & 2010

2011 - Present Intern, Pluribus Networks, Palo Alto, California, USA

### **PUBLICATIONS**

Won Ho Park, Tamer Ali, C.K. Ken Yang, "Analysis of Refrigeration Requirements of Digital Processors in Sub-ambient Temperatures," Journal of Microelectronics and Electronic Packaging, vol. 7, no. 4, 4<sup>th</sup> Qtr 2010

Won Ho Park, C.K. Ken Yang, "Analysis of Total System Power Efficiency Using Embedded Thermoelectric Coolers," International Microsystems, Packaging, Assembly, and Circuits Technology Conference, 2011

Won Ho Park, C.K. Ken Yang, "Total System Power Reduction Using a Refrigeration System for Electronic Cooling," International Microsystems, Packaging, Assembly, and Circuits Technology Conference, 2011

Won Ho Park, C.K. Ken Yang, "Effects of Using Advanced Cooling Systems on the Overall Power Consumption of Processors," in revision for IEEE Transactions on Very Large Scale Integration

Won Ho Park, C.K. Ken Yang, "Effects of Cooling on Workload Management in High Performance Computing Processors," in revision for IEEE Transactions on Computers

### **CHAPTER 1**

### Introduction

Aggressive CMOS technology scaling over the last few decades led to the tremendous growth in the semiconductor industry. The ability to integrate billions of transistors of into a single chip increased computational capacity. However, besides the traditional performance constraint, power dissipation and thermal issues have been identified as key limitations for the design of high performance computing (HPC) microelectronic chips. The limitations are due to increasing power density with technology scaling, and operating processors for HPC applications near maximum power limit in order to maximize server performance. As a result, reducing the operating temperature using refrigeration systems for electronic cooling has attracted recent interest as a possible option that offers solutions to both the power and thermal problems.

This chapter begins with describing some trends in system power dissipation as motivation behind this dissertation. We show the problem of power consumption in current data centers and servers and how reducing operating temperature of HPC microprocessors can potentially address the problem. This dissertation focuses on using a refrigeration system for electronic cooling can not only be used to improve performance but also to realize overall power improvement that includes the cost of cooling power. The outline of the thesis is presented in the second section.

### 1.1 Motivation

Increase in energy consumption due to the tremendous growth in the number, size, and uses of data centers presents a whole new set of challenges in maintaining energy-efficient infrastructure. While data centers' energy consumption had accounted for 2% of the total energy budget of the U.S. in 2007, it is expected to reach 4% by the year 2011. This number is equivalent to \$7.4 billion per year on electric power where this number is a 60% increase since year 2006 [1]. Worldwide trend of energy consumption in data centers tracks with the trend of the U.S [2].

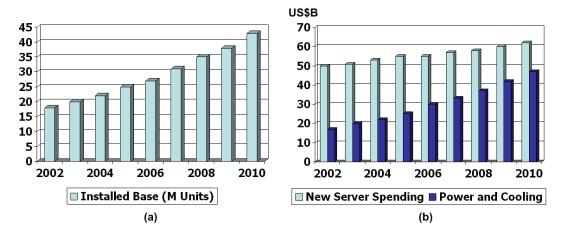

Figure 1-1: (a) Number of worldwide installed bases of data center. (b) Worldwide spending on new servers and operation cost.

Figure 1.1 shows the number of installed bases of data centers, worldwide new server spending, and electric power and cooling costs. Despite the dramatic increase of installed base of data centers over the last decade, new server spending has stayed relatively constant

due to the decrease in electronic costs. As the data center infrastructure becomes more dense, power density has been increasing by approximately 15% annually [3], raising the electric energy consumption for operating its servers and cooling system. This energy consumption is reflected in the electricity bill, where the Figure 1.1.b shows the amount of electric bill consumed by data centers. In fact, the cost has been increasing by approximately \$4 billion per year. If this problem is not properly addressed, it is evident that IT operation cost will soon outweigh the installation cost.

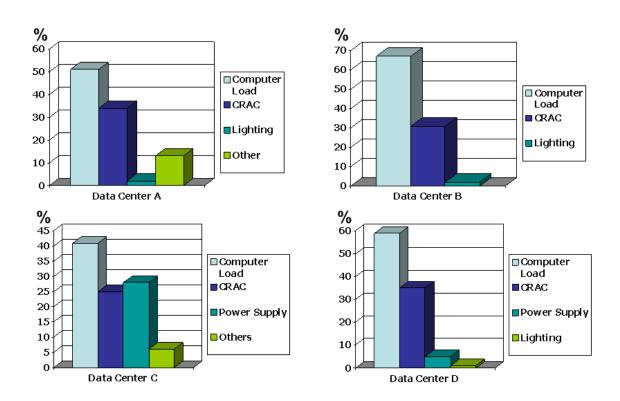

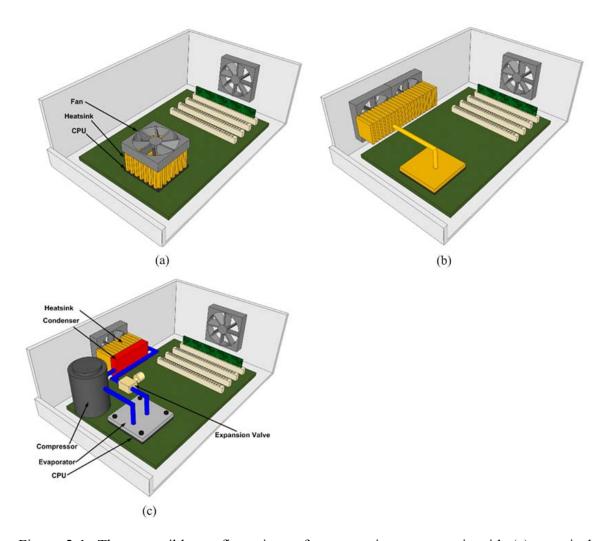

Figure 1-2: Energy breakdown of different data centers.

Detailed energy breakdown of different types of data centers is shown in Figure 1.2 [2], [4] - [6]. Relative percentage of various contributors to energy usage varies considerably among data centers, but up to 90% of the total energy is attributed to the energy dissipated by the computer load and the energy required by the Computer Room Air Conditioner (CRAC) unit, which removes the heat generated by the computer load. Therefore, reducing energy of both the computing and cooling is imperative in minimizing energy usage of data centers. Furthermore, there exists a strong coupling between the energy consumed by the computer load and CRAC units since any reduction in electronic heat can be compounded in the cooling system. For example, CRAC energy efficiency of data centers can increase by 1% per Celsius [2].

Figure 1-3: Power breakdown of different types of servers.

Data centers consists of hundreds or even thousands of server racks where each rack can draw more than 20kW of power; inability to meet such enormous power requirements have resulted in over 40% of customers reporting that the power demand is outstripping their power supply [3]. This situation creates an unprecedented demands for minimizing power consumption of high performance servers. Consequently, optimizing energy usage of multi-server systems is an interest across multiple disciplines, with the energy efficiency being a major research interest.

The focus of most efforts on energy/power saving in multi-server systems is on processor elements [7] - [10], [44]. Power breakdown on different components of various

server types is shown in Figure 1.3 [2]. The distribution of power consumption varies with the server class and also depends on the configuration and usage. However, it is clear that processors are the dominant source of power consumption, reaching up to 60% for petaflop supercomputer node designs.

Approaches for energy saving often adopt both the software-based energy-aware workload scheduling and hardware-based circuit and architectural power management techniques to effectively optimize energy usage. A typical software-based workload scheduling algorithm controls energy by distributing workloads to processors in a way to reduce both the electric and cooling costs. Often the software utilizes special hardware supports offered by HPC processors, such as stopping a processor, dynamic voltage frequency scaling [11] - [13], thread migration [14]. Although these special hardware support can be used to reduce power consumption, these techniques often require some transition time in and out of different power states and imply some performance degradation.

Along with these techniques, actively cooling the processors using refrigeration systems have attracted recent interest as a practical option to ease the power problems in HPC processors for sever type applications [15] - [17]. The main benefit of lowering temperature is to allow the system to maintain a low junction temperature while operating with high performance. Often, active cooling results in increased overall power dissipation due to the combined electronic power and refrigeration power.

Although reduced temperature operation of CMOS circuits improve the electronic performance, there has been little work that synthesizes the cooling power consumption in

order to quantify the overall benefit to the system. For instance, the improved speed performance can be trade-off into a power reduction with constant performance by reducing the supply voltage,  $V_{dd}$ . The research in this dissertation is toward the analysis and design of electronic system with refrigerated system for electronic cooling to investigate whether the system offers an overall power reduction over the non-cooled design. Particularly, we focus on two types of electronic cooling systems: embedded thermoelectric coolers and vapor compression refrigeration system. In order to achieve this goal, a realistic system-level model that includes both the electronic and the refrigeration systems is introduced. The model is used to explore the optimal operating temperatures and the amount of total power reduction at reduced temperatures.

Developing a highly-efficient miniature-scale refrigeration system for electronic cooling is one key element of this research. We have developed a refrigeration system that operates at low temperatures with high efficiency. This refrigeration system is used to experimentally demonstrate the amount of total power saving for processors at various operating conditions. Based on the measured results, a model that captures different relations and parameters of multi-core processor and the refrigeration system is presented. Finally, this model is extended to illustrate the results of optimizing the power of multi-core multi-processor systems under the actively cooled environment and to investigate different methodologies of workload scheduling to maximize power efficiency while minimizing performance degradation. Results presented in this dissertation suggest that there exists an efficient methodology under the actively cooled environment that optimizes power efficiency.

## 1.2 Organization

The dissertation starts with an introductory chapter and is then divided into four parts that deal with system modeling, analysis, implementation, and different power minimizing techniques. Chapter 2 describes the mechanisms for power dissipation of digital CMOS ICs and the benefits of reduced temperature operation. The chapter also introduces a performance metric of two different types of refrigeration systems. The models of such cooling systems are combined with the electronics model and are discussed in Section 2.1 and 2.2, respectively. The basic power saving techniques of multi-core multi-processor systems are also briefly discussed in Section 2.3.

Chapter 3 includes the analysis to support the feasibility of using vapor compression refrigeration system for electronic cooling. We explore the impact on overall system power, desired operating temperatures, and the dependence of the refrigerated performance on the power profile of the electronics. In Section 3.1, the benefits of microprocessors at subambient temperatures are discussed in a case study. Dependence on the characteristics of the electronics and refrigeration systems is presented in Section 3.2 and 3.3, respectively. From these results, performance requirements for the refrigeration are discussed for different electronic power-dissipation characteristics.

Chapter 4 explores the amount of total power reduction using embedded thermoelectric coolers (eTECs). Recent advances in eTECs provide possibility of mitigating thermal problems in HPC systems. The effects of localized cooling on different functional blocks are explored using a model that incorporates both a real-world microprocessor and

thermoelectric cooling systems as discussed in Section 2.2. Our analysis in Section 4.1 indicates that an optimal operating point exists and depends on the parameters of electronics and cooling systems. In Section 4.2, we provide our simulation results of localized spot cooling various blocks of a high performance microprocessor.

Our discussion on system level modeling and analysis ends in Chapter 4. While our analysis in Chapter 3 provides the analysis to support the feasibility of using refrigeration systems for electronic cooling in terms of overall power performance, obtaining this goal requires a highly-efficient refrigeration system. In Chapter 5, a refrigeration system is developed and experimentally tested to demonstrate that cooling the high performance microprocessor can indeed lead to overall system power improvement. Overall system description and our experimental setup is discussed in Section 5.1. We go on to describe the performance of the refrigeration system in Section 5.2. Measurement results validate our analysis of Chapter 3 and is discussed in Section 5.3. The chapter then concludes with a discussion of future refrigeration system for electronic cooling.

Chapter 6 explores an energy-efficient workload scheduling methodology for multicore multi-processor systems under the actively cooled environment that improves the overall system power performance with minimal response time degradation. Using our miniature-scale refrigeration system from Chapter 5, we show that active-cooling by refrigeration on a per-server basis not only leads to substantial power-performance improvement, but also improves the overall system performance without increasing the overall system power including the cost of cooling. In Section 6.1, the measured results are used to establish a power model for a multi-core processor based on varying levels of activity under an actively cooled environment. Section 6.2 applies various workload scheduling algorithms to this model to explore the best approach to maximize energy efficiency. The proposed methodology is further combined with the G/G/m-model to investigate the trade-off between the total power and target SLA requirements, and is discussed in Section 6.3. Finally, Chapter 7 concludes this dissertation with discussions for future work.

### **CHAPTER 2**

## **Background**

Several key power and technology attributes for semiconductor ICs from the 2009 International Technology Roadmap for Semiconductors (ITRS) are listed in Table 2.1 [18]. The power dissipation for single-chip packages in high-performance systems is predicted to rise to 161W in 2011 while the maximum junction temperature is restricted to 85°C or lower. If temperature and power are not properly managed, both the chip and package level performance and reliability are critically affected. In order to meet both requirements, the overall junction-to-ambient thermal resistance needs to decrease. Table 2.1 shows that the required overall junction to ambient thermal resistance for high-performance ICs for ambient temperature of 45°C must be substantially less than 0.3°C/W in the near future.

The use of cooling through active heat removal is being evaluated as a viable option that might offer solutions to both the power and thermal problems [19] - [21]. Such cooling leads to lower junction temperatures below the common forced-air cooling which in turn can alleviate thermally induced reliability issues. Cooling can also reduce power consumption and/or boost the speed performance of high-end microprocessors. Various refrigeration technologies for electronic cooling such as thermoelectric, cryogenics, and vapor compression with the associated advantages and disadvantages have been reported in [19] - [21]. Recently, two types of active cooling have been commonly discussed: eTECs [23] - [25] and highly-efficient vapor compression refrigeration systems [21] - [22]. The two different cooling technologies can be distinguished in how they can be applied in a

system. Embedded TECs have the potential to locally cool different portions within an IC (*localized spot cooling*). Refrigerated cooling in which the evaporator directly attaches to the processor package is often considered in the context of cooling the entire dice (*chip-level cooling*). This type of refrigerated systems can possibly be extended to directly cool multiple dice in multiple chassis depending on the size of the compressor. Thereby, the potential of power optimization of multi-core multi-processor systems under the cooled environment using miniature-scale refrigeration system can be investigated based on different workload scheduling methodologies.

This chapter focuses on combining an electronics model with a realistic active-cooling model of two different types of refrigeration systems: eTECs and vapor compression refrigeration systems. For a given set of parameters, the model can be used to determine the system power at various operating temperatures and power. Section 2.1 discusses the system model and reviews the well-known parameters for the electronic and vapor compression refrigeration systems. The model is used in the analysis in Chapter 3. A realistic system-level model that includes both the electronic characteristics of various functional blocks and the realistic performance of eTECs is introduced in Section 2.2. This model is used in the analysis of Chapter 4. Lastly, the model from Section 2.1 is extended to capture different relationships and parameters of our multi-core processor and the refrigeration system. Such model can be used to illustrate the potential of power optimization of multi-core multi-processor systems and investigate different methodologies of workload scheduling which is discussed in Chapter 6. Basic power saving techniques

and power-aware workload algorithms in multi-processor server systems are discussed in Section 2.3.

| Year                                             | 2008 | 2009 | 2010 | 2011 |

|--------------------------------------------------|------|------|------|------|

| Gate Length (nm)                                 | 29   | 27   | 24   | 22   |

| Allowable Maximum Power (W)                      | 146  | 143  | 146  | 161  |

| Power Density (W/mm <sup>2</sup> )               | 0.47 | 0.46 | 0.47 | 0.52 |

| Maximum Junction Temperature (°C)                | 85   | 85   | 85   | 85   |

| Required Thermal Resistance (°C/W)               | 0.27 | 0.28 | 0.27 | 0.25 |

| I <sub>d,sat</sub> : NMOS Drive Current (uA/um)  | 1006 | 1317 | 1370 | 1333 |

| I <sub>d,leak</sub> : NMOS Drive Current (uA/um) | 0.13 | 0.17 | 0.46 | 0.71 |

| Full Chip Leakage <sup>1</sup>                   | 1.5  | 2    | 2.5  | 2.75 |

Table 2.1 International Technology Roadmap for Semiconductors 2008. ( ¹:Normalized to Full-Chip leakage power dissipation in 2007)

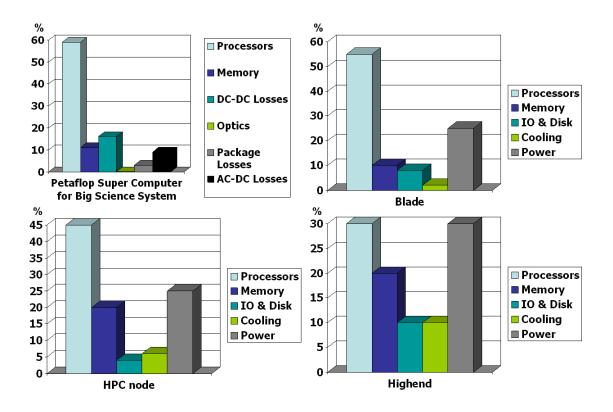

# 2.1 Electronic System with Vapor Compression Refrigeration

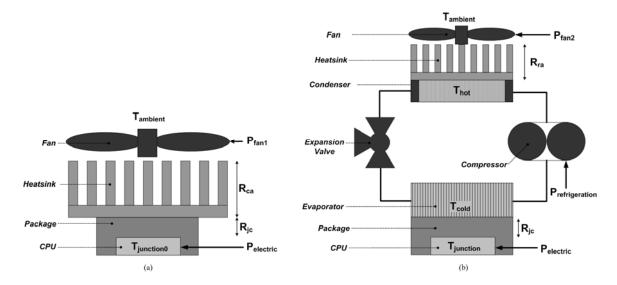

Figure 2.1 illustrates three possible configurations of a computing server unit. Figure 2.1.a is a common air-cooled system with a fan forcing air flow over all the electronics. The best-case scenario for air cooling the microprocessor is shown in Figure. 2.1.b where the microprocessor heat-sink is directly cooled with air from the ambient temperature. The corresponding refrigerated-cooling system would directly cool the heat-sink as shown in Figure. 2.1.c. A fan is included in the system to cool the condenser.

Figure 2-1: Three possible configurations of a computing server unit with (a) a typical configuration of a fan for the chassis, (b) dedicated fan-cooling for the processor, and (c) a refrigerated-cooling for the processor.

The power and heat model is illustrated in Figure 2.2. A digital processor is the heat load consuming power,  $P_{electric}$ . In Figure 2.2.a, the heat load is maintained at  $T_{junction0}$  by a forced-convection air cooler, which rejects  $P_{electric}$  to  $T_{ambient}$  through the junction-to-case thermal resistance ( $R_{jc}$ ) and case-to-ambient thermal resistance ( $R_{ca}$ ). The associated fan

power needed to obtain R<sub>ca</sub> is denoted by P<sub>fan1</sub>. With a given thermal resistance, the junction temperature of the system is determined by the total power consumption and the ambient temperature. The total power dissipation of this configuration, which is denoted by P<sub>total\_air</sub>, is given by the sum of P<sub>electric</sub> and P<sub>fan1</sub>. Figure 2.2.b shows the model of the same system with a refrigeration system. In this model, the heat load is being maintained at T<sub>junction</sub> (<T<sub>junction0</sub>). The cooling process is performed between hot-end temperature of the condenser (Thot) and cold-end temperature of the evaporator (Tcold) to allow the transfer of P<sub>electric</sub> to the ambient environment. The required power for refrigeration is represented by P<sub>refrigeration</sub>. Also the thermal resistance of refrigeration heatsink and its required fan power are modeled by R<sub>ra</sub> and P<sub>fan2</sub>, respectively. Here, the total power dissipation, P<sub>total\_ref</sub>, is obtained by the sum of P<sub>electric</sub>, P<sub>refrigeration</sub>, and P<sub>fan2</sub>. Various sources of power dissipation in the two systems are summarized. The following sub-sections review the relationship between power dissipation and temperature for electronics and for refrigeration. These relationships and the parameters that characterize the performance of the electronics and refrigeration are used in a model built in MATLAB. The model is used for the analysis and design in Chapters 3 and 5.

Figure 2-2: (a) Model of conventional air cooler. (b) Model of the same electric system using a refrigeration system.

### 2.1.1 Sources of Electronic Power

The total electronic power dissipation of a microprocessor can be approximated by the sum of active power and subthreshold leakage power [26], [58].

$$P_{\text{electronic}} \approx P_{\text{active}} + P_{\text{leakage}}$$

(2.1)

$$P_{\text{active}} = \alpha * C_{\text{switched}} * f_{\text{clk}} * V_{\text{dd}}^2$$

(2.2)

$$P_{\text{leakage}} = V_{\text{dd}} * I_{\text{leakage}} = V_{\text{dd}} * I_0 \exp\left(\frac{-V_{\text{th}}}{kT_{\text{junction}}/q}\right)$$

(2.3)

The active power,  $P_{active}$ , depends on the activity factor,  $\alpha$ , and the amount of power that dissipates charge/discharge capacitive nodes between the supply voltage ( $V_{dd}$ ) and ground when executing the logic,  $C_{switched}$   $f_{clk}$   $V_{dd}^2$ . At nanometer-scale technologies, the switches that implement the logic result in a leakage current to flow for each logic gate even when the logic is not active This leakage becomes a significant component of total chip power in modern era processors.

The leakage power,  $P_{leakage}$ , has an exponential relationship to the ratio of a transistor's ON/OFF threshold,  $V_{th}$ , and the thermal voltage,  $kT_{junction}/q$ . The  $P_{leakage}$  equation simplifies the dependences of leakage power by lumping (1) the number and size of logical switching paths in a computational unit, (2) the carrier properties in the transistor, and (3) dependence of leakage on the logical structure of each logic gate of a digital processor into a single constant  $I_0$ .

For a digital processor, power dissipation and computing performance are closely related [58]. The delay of logic switching is proportional to the switch and interconnection resistances and capacitances. Equation 2.4 shows this relationship for the delay of a logic gate. The current is a function of temperature and primarily depends on the carrier mobility ( $\mu \sim T^{-1}$ ). A designer can typically trade-off any improved speed performance into a power reduction with constant performance by reducing the supply voltage,  $V_{dd}$ .

Delay

$$\propto RC \propto \frac{V_{dd}}{I_{logic}}$$

(2.4)

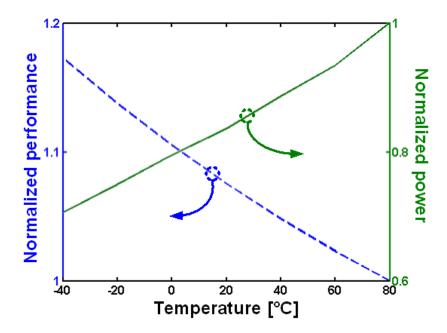

Lower temperatures lead to improved performance of electronic devices. Lower power and higher speed results from (1) an increase in carrier mobility and saturation velocity, (2) an exponential reduction in sub-threshold currents from a steeper sub-threshold slope (kT/q), (3) an improved metal conductivity for lower delay, and (4) better threshold voltage control enabling lower  $V_{th}$ . Figure 2.3 graphs the change in performance with temperature of a 65nm technology device. Figure 2.3 also shows the reduction in active and leakage electronic power with constant performance.

Figure 2-3: Normalized performance and power as a function of temperature of a 65nm technology device.

The percentage of electronic power due to its leakage and active components depends

on a number of factors. The transistor technology can determine the  $P_{leakage}/P_{electric}$  ratio at the level of the logic gates. Table 2.1 shows the ratio for an NMOS transistor for several different nanometer-scale technologies. With technology scaling, the supply voltage lowers to maintain device reliability and constrain power consumption. To compensate for this performance loss,  $V_{th}$  scales down correspondingly. Such scaling results in a dramatic increase of leakage power since leakage power depends exponentially on  $V_{th}$ . The leakage power is further exacerbated with technology scaling because of such problems as drain-induced barrier lowering (DIBL) and short channel effect.

The functionality of the digital block impacts P<sub>leakage</sub>/P<sub>electric</sub> ratio through the average activity factor, α. For instance, memory blocks have considerably different α compared to arithmetic units. Examples of the ratio are shown Table 2.1.a for several functional blocks. The implementation of a functional block also has impact through the activity factor. As an example, a highly parallelized design has a tendency to have a higher ratio than the one that is not parallelized. Different applications and architectures such as microprocessors and digital signal processors also have different ratios as shown in the bottom entries in Table 2.1.b. The ITRS roadmap projects (Table 2.1) that full-chip leakage power dissipation increases with device scaling. Specifically, analysis of microprocessor power consumption [27] shows average leakage power ratio increases with device scaling, reaching up to 50% from the 65nm technology generation and beyond. Finally, the ratio in the table is typically an average value. The ratio changes dynamically depending on the instantaneous activity of the digital block. Leakage can dominate when the system is in stand-by, whereas active power is typically dominant with high-levels of logic activity.

As seen above, leakage power becomes important for high performance ICs. Due to its exponential dependence on temperature,  $T_{junction}$  in turn, is determined by the total power consumption and system packaging technology. As a result of this strong coupling between  $T_{junction}$  and leakage power, temperature-aware power modeling becomes necessary for appropriate thermal management and accurate performance optimization/estimation.

| Functional Unit | Leakage Percentage (%) |

|-----------------|------------------------|

| IntExec         | 24                     |

| Bpred           | 44                     |

| L2 Cache        | 53                     |

|                 | (a)                    |

| Application             |                 | Leakage Percentage (%) |  |

|-------------------------|-----------------|------------------------|--|

| DSP [29]                |                 | 48                     |  |

| DSP [30]                |                 | 25                     |  |

| SRAM [31]               |                 | 53                     |  |

| Processor [32]          |                 | 36                     |  |

| 16 Core Processor [33]  | @ Maximum Power | 12                     |  |

| Processor Leakage Trend | [27]            | 50                     |  |

| (b)                     |                 |                        |  |

Table 2.2: Leakage percentage (a) for various functional blocks within a microprocessor [28] and (b) for various types of integrated circuits.

#### 2.1.2 Cooling Power and Refrigeration Efficiency

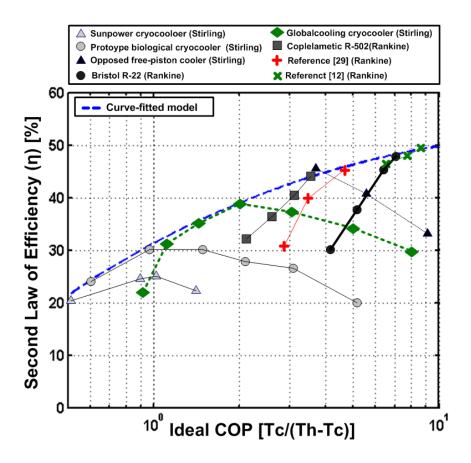

Figure 2-4: The performance of different refrigeration systems.

The power cost of cooling to a desired junction temperature includes the power cost of the refrigeration and fans and the thermal resistances [34] - [35]. Refrigeration power which accounts for the Carnot cycle and compressor power is modeled using the coefficient-of-performance ( $COP_{real}$ ). This work uses the COP data from [21], [36] - [39]. The refrigeration power can be expressed in terms of the  $COP_{real}$  and the COP of the Carnot cycle with the well-known Equations (2.5) and (2.6) where  $T_{cold}$  is the cold-end temperature

of the evaporator (<T<sub>junction</sub>), T<sub>hot</sub> is the temperature at the condenser (>T<sub>ambient</sub>),  $\eta$  is the second-law efficiency, and P<sub>electric</sub> is the power dissipation of the heat source [57].

$$\frac{P_{\text{electronic}}}{P_{\text{refrigeration}}} = COP_{\text{real}} = \eta COP_{\text{carnot}} = \eta \frac{T_{\text{cold}}}{T_{\text{hot}} - T_{\text{cold}}}$$

(2.5)

$$P_{\text{refrigeration}} = \frac{P_{\text{elctronic}}}{\eta} \cdot \left(\frac{T_{\text{hot}}}{T_{\text{cold}}} - 1\right) \quad (2.6)$$

Using the COP data, Figure 2.4 shows the efficiency data of different refrigeration products at different temperature ranges. Each system is optimally designed to function in the temperature ranges of various commercial applications. The COP of each system degrades as the temperature deviates from the optimal operating point. Since the analyses in Chapter 3 explore the optimal temperature across a broad temperature range, instead of using a single refrigeration system, a curve is fitted based on the optimal efficiency points across a number of the refrigeration products spanning the temperature range. In other words, this curve is a realistic upper bound for the achievable refrigeration efficiency at each temperature.

While it is difficult to simulate a complete system that perfectly matches the real environment and circuit/system impairments, the methodology presented above allows a quick yet accurate simulation that reflects the impact on different parameters on the overall

system performance. Our model serves as a useful tool to evaluate overall system performance at different operating conditions. Performance requirements for the refrigeration systems can also be discussed for different electronic characteristics. The results enable a designer to best choose or design the cooling system for the application. The overall system power consumption that includes the cost of cooling power is used to illustrate the performance comparison throughout this dissertation.

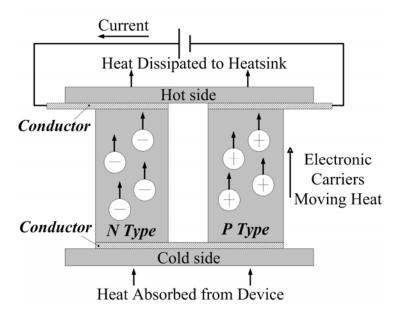

## 2.2 Electronic System with Embedded Thermoelectric Coolers

Since cooling using vapor compression refrigeration system is performed at the chip level, a single temperature setting for the entire IC may not result in the optimum operating point for individual functional blocks within the integrated circuit. This is because each functional block within a processor can have considerably different power dissipation and power density. Integrated eTECs for localized cooling have been discussed and shown in [23] - [25]. A thermoelectric cooler (Figure 2.5) is a small electronic heat pump that has the advantage of no moving parts and silent operation. Thermoelectric cooling uses the *Peltier* effect to create a heat flux between the junctions of dissimilar materials. By adjusting DC current, heat flow can be proportionally modified allowing precise control of the junction temperature. The movement of heat provides a cooling capability that is well-suited for applications where temperature stabilization or direct cooling is required. Cooling research has been investigating using eTEC to locally and selectively cool an area with high power density to resolve thermal problems in integrated circuits. It is well known that cooling heat

flux of a TEC is inversely proportional to the thickness of the element. Accordingly, microfabrication allows eTECs to have high heat flux capability. Unlike chip-level cooling, it is possible for each functional block on an IC to be cooled independently to its desirable temperature setting. Electronic characteristics of various functional blocks and a simple model that captures characteristics of eTECs are discussed in this section.

Figure 2-5: Schematic of a thermoelectric cooler.

#### 2.2.1 Electronic Profile of Modern Microprocessors

Applying the simple transistor level model to a processor can be challenging. Each functional block is comprised of a large number of logic elements from thousands to millions of logic gates. The amount of power dissipated is an aggregate of the power of each element. Furthermore, the percentage of electronic power due to its leakage and active

components depend on the functionality of digital blocks. The functionality impacts this ratio through the average activity factor,  $\alpha$ . For instance, logic blocks such as an instruction decoder may have considerably different  $\alpha$  as compared to memory blocks. Due to high-levels of logic activity under smaller area, logic blocks tend to have high power density with small percentage of leakage power. On the other hand, memory blocks attribute a large portion of its power to leakage. In this dissertation, McPAT, an integrated power, area, and timing modeling framework simulator, is used to explore to verify these electric characteristics. This simulator has shown results that modeled numbers track well with the published data for microprocessors [40].

Figure 2-6: Electronic parameters of three different types of processors with (a) power density of core and last-level cache block at 70°C and 100°C and (b) leakage power ratio of core and last-level cache block at 70°C and 100°C.

Figure 2.6 illustrates power density and leakage percentage of a microprocessor's execution core and last level cache units for the 180nm Alpha 21364 processor [41], the 90nm Niagara processor [42], and the 65nm Xeon processor [43]. Clearly, core blocks have higher power density that is approximately 4 to 10 times higher than the last level cache blocks. Due to lower level of activity, last level cache dissipates a significant portion of its power to leakage with at least 30% and up to 60% of leakage at 100°C. The junction temperature of each block is determined by the total power density and the ambient

temperature through a given thermal resistance. The figure shows the results at two different temperatures to account for the possibility of different thermal resistances.

The floorplan of the Xeon processor is shown in Figure 2.7 where the processor has two cores and a 16-MB shared L3 cache. Each core has a unified 1-MB L2 cache [43]. Note that approximately 70% of the total area is consumed by L-2 cache and L-3 cache. A more fine-grained breakdown of power density and leakage percentage of major functional components in the core block of the Xeon processor are shown in Figure 2.8. As expected, different functional blocks operate with different leakage and power density. Similarly, in general, blocks with high power density tend to have low leakage power percentage. The analyses in Chapter 4 use the data in Figure 2.6 and 2.8 to explore the impact of localized cooling on functional blocks.

Figure 2-7: Floorplan of the Xeon processor. (Adapted from [43]).

Figure 2-8: Electronic parameters of major function components in the core block of the Xeon processor with (a) power density at 70°C and 100°C and (b) leakage power ratio at 70°C and 100°C.

#### 2.2.2 Embedded Thermoelectric Coolers

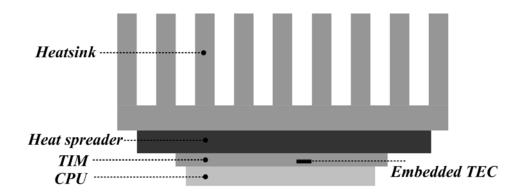

A configuration of microelectronic system with localized cooling is composed of a silicon wafer, a thermal interface material (TIM) with eTECs, a heat spreader, and a heatsink as shown in Figure 2.9. Conceptually, it is possible for the eTEC to be applied with fine granularity for each functional block of a processor. More realistically, the eTEC can be applied across coarse regions on an IC because of the substantial design overhead

associated with using a large number of independent eTECs such as increased manufacture/package cost, additional power pins for cooling power, etc. This research considers both scenarios to explore whether substantial benefits can be garnered through a fine-grained temperature control.

Figure 2-9: View of a microelectronic system with embedded TEC locally cooling a functional block.

Thermoelectric materials are characterized by their figure of merit ZT, defined by

$$ZT = \frac{S^2T}{RK} (2.7)$$

where

S = Seebeck constant

R = electrical resistivity

K = thermal conductivity

#### T =temperature

Thermoelectric material needs to obtain low thermal conductivity in order to prevent heat losses through heat conduction between the hot and cold side. The material also needs high electrical conductivity to minimize Joule heating. A TEC absorbs dissipated electric power (P<sub>electric</sub>) that is compensated by the heat conduction and Joule heating losses. Each of these components are shown as

$$P_{\text{electric}} = ST_{c}I - K\Delta T - \frac{1}{2}I^{2}R \qquad (2.8)$$

where  $T_c$  is the cold side temperature of the device, I is the electric current flowing through the device, and  $\Delta T$  is the temperature difference between the cold and hot side. The input power of a TEC device is equal to

$$P_{\text{cooling}} = SI\Delta T + I^2 R \tag{2.9}$$

These parameters that characterize the performance of the eTEC are merged into a single model with the electronic power dissipation of a microprocessor as shown in Section 2.2.1. This single model considers the interdependence between the electronic and eTEC

systems. With this model, we evaluate the impact of localized cooling on the power dissipation of functional blocks.

#### 2.2.3 Performance of eTEC

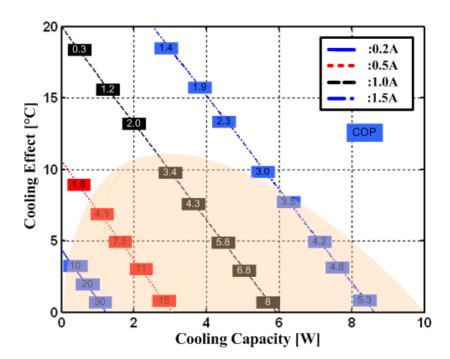

Figure 2-10: The performance curves of an embedded thermoelectric cooler with height and area of 100um and 6.25mm<sup>2</sup>, respectively. (Adapted from[24])

As described in Section 2.1.2, refrigeration efficiency of any refrigeration cycle is measured by COP, defined by the ratio of the heat removed to the required power to remove the heat. In thermoelectric coolers, COP depends on operating conditions of I and  $\Delta T$  as well as device parameters of K, R, and S as seen by the following equation.

$$COP = \frac{P_{electric}}{P_{cooling}} = \frac{ST_{c}I - K\Delta T - \frac{1}{2}I^{2}R}{SI\Delta T + I^{2}R}$$

(2.10)

We use parameters (Seebeck coefficient, electrical resistivity, and thermal conductivity) provided by [24], which has effective ZT of approximately 0.5. By adjusting the amount of current flow, the COP for different cooling capacity and associated cooling effect is obtained as shown in Figure 2.10 where cooling effect represents the amount of temperature difference obtained with cooling. The shaded area in the figure represents the range in which a high COP can be obtained using this particular device. Increase in input power allows the cooler to have a higher cooling capacity and cooling effect at the expense of efficiency. It is worthwhile to note that Figure 2.10 provides performance curves of the eTEC with the footprint area of 6.25mm² and the length of 100um. This dissertation investigates the effect of localized cooling on various types of blocks with different areas. Hence, we adjust the model of the eTEC depending on the size of the block under investigation. We also extrapolate from this data to model a hypothetical eTEC with higher performance that have effective ZT of 1.0 and 2.0 to explore the potential improvement through a better eTEC. The effectiveness of the thermoelectric modules can be improved by lowering electrical contact resistance and thermal contact conductance [23] - [25].

Using this model, Chapter 4 investigates whether localized spot cooling can lead to an overall system power saving when the cooling cost of eTECs is factored in. As the model includes the power dissipation for each block within a processor, we also investigate how

much of an effect cooling has upon different types of blocks in terms of overall system power and temperature. This model serves as a useful method to evaluate the performance requirements of eTECs for electronic cooling.

# 2.3 Common Power Saving Techniques in Multi-Core Multi-Processor Systems

Minimizing power consumption of integrated circuits has been a hot topic in recent years. Along with reducing power consumption for mobile devices, significant amount of research has been directed towards power conservation for clusters of large-scale multi-server systems due to the tremendous growth in the number, sizes, and uses of data centers.

Using our system model from Section 2.1 and a highly efficient miniature-scale refrigeration system for electronic cooling, we illustrate the potential of power optimization of multi-core multi-processor systems based on different workload scheduling methodologies and power saving techniques. Results presented in this dissertation suggest that there exists an optimal methodology under the actively cooled environment that maximizes power efficiency while minimizing performance degradation. Furthermore, we combine our proposed methodology with the G/G/m-models to reduce the total power while meeting target SLA requirements by judicious capacity planning. This section reviews the basic power saving techniques in multi-core multi-processor systems and the G/G/m model from queueing theory.

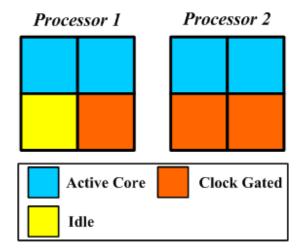

#### 2.3.1 Basic Power Saving Techniques

Powering-off cores that are not being used is the simplest way to reduce power consumption in multi-core processors. Stopping can be achieved in two ways. Most aggressive option is to save the architectural state and to completely power off the processor. This method is often known as power gating. Power gating the processor dissipates no power at all, but using this type of technique to power on/off comes at a price of long response time degradation since powering up a processor that is completely shut down requires up to 1000 cycles [44].

On the other hand, a simpler way to stop a core with minimal response time degradation of few clock cycles is to clock gate the core. This power saving technique stops active power dissipation, but since power is not entirely cut-off, the core continues dissipating leakage power. Advantages and disadvantages of using these two techniques at reduced temperature are explored in Chapter 6. Other special hardware supports for managing power in HPC processors exist, such as dynamic voltage frequency scaling, or thread migration, but this dissertation primarily focuses on the core stopping techniques.

Along with hardware-based power management techniques, energy usage of servers in the data centers can also be controlled through model-based energy-aware workload scheduling algorithms that distribute workloads to processors in a way to reduce both the electric and cooling costs. The basis of these approaches relies on powering-off servers that are not utilized by concentrating the workload on a subset of the servers. This method is known as *spatial subsetting*, and has been shown to successfully tackle the issue of idle

server power consumption [45] - [46]. Moreover, energy savings from the off-power servers is compounded in the cooling systems that consume power to remove the heat dissipated in the servers. While this approach significantly reduces idle power, it raises a concern of degraded response time in computing systems, due to the power-latency trade off.

To address the problem of degraded response time in *spatial subsetting*, one solution is to employ an *over-provisioning* scheme [47] - [48]. The over-provisioning algorithm can be considered as a power and response time optimization problem. By predicting how many servers are required to service the requested workload, the workload management software assigns a subset of processors to remain at idle state to absorb sudden increases in the load. Determining the number of server to operate at a certain utilization level to meet certain requirements often relies on a good model that successfully plans capacity depending on the upcoming workloads. For instance, *General Arrival Process / General Service Process / Multiple Server* (G/G/m) model from queueing theory have been used to obtain useful measures to support capacity and workload planning of multi-processor systems in order to satisfy target Service Level Agreement requirements [49].

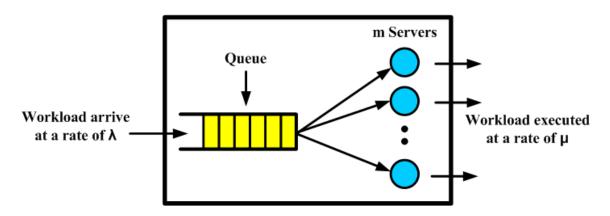

#### 2.3.2 G/G/m Model for Capacity Planning

Execution Velocity and Normalized Wait Time are often used to obtain measures to support capacity planning of multi-processor systems. Figure 2.11 can be used to illustrate

a generic G/G/m model for multi-server system, where each workload enters the queue of m-server system at an arrival rate of  $\lambda$  and leaves the system at a service rate of  $\mu$ .

Figure 2-11: A Generic G/G/m model for multi-server systems.

The term *Execution Velocity* (E[V]) is used to describe the average ratio for the total amount of workload units that are served without any delay and is defined by Equation 2.11. The value of E[V] ranges from 0 to 100 where the value 100 means that the workload does not encounter any wait delays for the system resources while the value 0 means that all work is delayed.

$$E[V] = 100 \times (1 - P[W > 0])$$

(2.11)

The waiting probability, P[W>0], represents the probability that workload has to wait in the system from the delayed task. P[W>0] in G/G/m model can be approximately calculated by Equation 2.12.

$$P[W > 0] = \frac{(m\rho)^2}{m!(1-\rho)} \cdot P_0$$

(2.12)

, where m is the total number of servers,  $\rho$  is the utilization ratio defined as  $\lambda/m\mu,$  and  $P_0$  is the probability for the empty G/G/m system defined as

$$P_{0} = \left[ \sum_{k=0}^{m-1} \frac{\left(m\rho\right)^{k}}{k!} + \frac{\left(m\rho\right)^{m}}{m!} \frac{1}{1-\rho} \right]^{-1}$$

(2.13)

Next, we consider *Normalized Average Wait Time* (E[W]) where the term is used to describe the average wait time in the queue of the system normalized with respect to the service time of unit length of one unit. Several approximation formulas exist, but here we use the Allen/Cunneen formula [49].

$$E[W] = \frac{P[W > 0]}{1 - \rho} \cdot \frac{C_A^2 + C_B^2}{2m}$$

(2.14)

where  $C_A^2 + C_B^2$  represents workload variability

Figure 2-12: (a) Execution velocity and (b) normalized average wait time at different utilization for m=8 and m=16 processors.

As an example, Figure 2.12.a and 2.12.b show the results of execution velocity and wait time for 8 and 16-server system at different utilization. Notice how the number of the processors impacts execution velocity and wait time. Increasing the number of processors allows the system to operate at a superior performance at the expense of extra power dissipation. Underutilization of the system can also improve the performance. This results in a trade-off between high utilization of the processors (energy-conscious provisioning) and the target SLA requirements. Detailed analysis of minimizing overall power consumption of multi-core multi-processor systems while meeting target SLA requirements is presented in Chapter 6.

## 2.4 Summary

As the amount of power density continuously increases with the pace of technology scaling, the use of cooling through active heat removal is one potential option to combat both the power and thermal problems in HPC processors. Such cooling allows electronic systems to operate at a lower junction temperatures below the common forced-air cooling which in turn can alleviate thermally induced reliability issues and also reduce power consumption. A realistic system-level model that includes both the electronic characteristics and realistic performance of refrigeration systems is discussed in this chapter. The model is used to quantify the overall power consumption of a system that includes both the electronic and cooling power. This chapter focused primarily on two types of active cooling systems for electronic cooling: eTECs and vapor compression refrigeration systems. The two different cooling technologies differs in how they are applied in a system. Using eTECs have the benefit of full integration and provide flexibility of spot cooling different functional blocks within the processor. On the other hand, vapor compression refrigeration systems is more efficient than TECs. Physical size of this type of refrigerated system could be a limiting factor for certain applications, but refrigerated systems that fit within the small space of electronic chassis have been demonstrated [21] -[22]. Furthermore, this type of cooling system can often be extended to directly cool multiple dice in multiple chassis depending on the size of the compressor.

The model from Section 2.1 is extended to capture different relations and parameters of multi-core processor and the refrigeration system. Combining different power saving techniques, the model can potentially be used for minimizing power of multi-core multi-processor systems and investigate different workload scheduling methodologies. We also

combine this model with the G/G/m-model to reduce both total power and response time degradation while meeting target SLA requirements. The overall simulator framework is shown in Figure 2.13. Our simulator provides overall system power consumption at different workload scheduling schemes for a given SLA requirements.

Figure 2-13: Overall simulator framework.

The next chapter explores the amount of obtainable power savings, optimal operating temperatures, and sensitivity to parameters of the electronic and refrigeration systems. Such analysis determines the feasibility of using refrigeration systems for electronic cooling.

#### **CHAPTER 3**

### **Analysis of Refrigeration Requirements for Electronic Cooling**

Benefits of reduced temperature operation of CMOS circuits have been demonstrated in [50] - [51]. Lowered system temperatures have been extensively used for improving maximum operational frequency of high performance system but without optimizing for power. While the speed improvement can be traded for lower power dissipation of the electronics, the cost of cooling can limit the overall system power performance. The impact of cooling on nanometer-scale electronic systems has been recently discussed in [53] but uses a simple cooling model. This chapter describes analysis that indicates the feasibility of using refrigeration systems for electronic cooling using our compact model as described in Section 2.1.

In this chapter, various parameters that affect the overall power performance are discussed. Section 3.1 describes results from the model in a case study. Interestingly, the results from the analysis indicate an optimal operating temperature lie in the range of domestic refrigeration. Dependence on the characteristics of the electronics is presented in Section 3.2. From these results, performance requirements for the refrigeration are discussed for different electronic power-dissipation characteristics. Furthermore, sensitivity to ambient temperature, refrigeration efficiency, and thermal resistance of the package is presented in Sections 3.3. Finally, Section 3.4 summarizes the important findings and concludes with a brief discussion of the potential of refrigeration-assisted systems. The

results from this chapter enable a designer to best choose or design the cooling system for the application.

## 3.1 Cooling a Microprocessor

This section uses the model in an example using a microprocessor as the heat load. The microprocessor operates at 3 GHz and dissipates 100W of power (Pelectrico) using a 1.2V power supply at 80°C (T<sub>junction0</sub>) without forced air cooling, which is summarized in Table 3.1. As in the microprocessor example in Table 2.2(b), P<sub>leakage</sub>/P<sub>electric</sub> is assumed to be 50% at this operating point. The local ambient temperature (T<sub>ambient</sub>) and the thermal characterization parameter of R<sub>jc</sub> are 27°C and 0.2°C/W, respectively. Thermal resistance, R<sub>ca</sub>, depends on whether it is air cooled or not. The refrigeration and fan performances and the relationship between thermal resistance and fan power are based on the data described in Section 2.1. Finally, the device parameters required for our simulator are extracted from BSIM model based on a 90nm CMOS technology process.

| Parameter                           |     |

|-------------------------------------|-----|

| Initial T <sub>junction0</sub> [°C] | 80  |

| $ m V_{dd0}  [V]$                   | 1.2 |

| Operating Frequency [GHz]           | 3   |

| Leakage Percentage [%]              | 50  |

| P <sub>electric0</sub> [W]          | 100 |

| R <sub>ic</sub> [°C/W]              | 0.2 |

Table 3.1: The model parameters used in the example of Section 3.1.

Figure 3-1: Optimization results of the system with forced-air and refrigerated cooling at Pleakage/Pelectric=50% @ 80°C.

Total power is analyzed while sweeping the junction temperature and keeping the operating frequency constant. The result of the analysis is shown in Figure 3.1. The performance of forced-air cooling is plotted for comparison with refrigerated cooling. The analysis uses the assumption that the junction temperature is  $80^{\circ}$ C. The performance curve for forced-air cooling is shown as a family of curves to account for the various possible fan size and  $R_{ca}$ . Decrease in  $R_{ca}$  at the cost of  $P_{fan1}$  shifts the curve to lower power. However, the amount of power reduction is limited by the obtainable  $R_{ca}$ . The optimal forced-air operating point for this particular heat load is roughly 77W at  $55^{\circ}$ C.

Forced-air cooling is limited in the achievable  $T_{junction0}$ . As shown in the figure, refrigerated-cooling allows  $T_{junction}$  to reach  $T_{ambient}$  and below. Due to the increase in cooling cost at lower temperatures, the minimum power of 58W is obtained at 8°C. This performance is 45% better than the reference design and 25% better than the best-case forced-air cooled design. At this operating temperature, the active power is reduced by reducing the  $V_{dd}$  1.1V. The most significant effect from cooling is the exponential decrease in the leakage power shown in Figure 3.1.

Analysis of the thermal circuit shows that  $T_{cold}$  of the refrigeration is 0°C at the optimal  $T_{junction}$ . At this temperature, the refrigeration efficiency is 48% of Carnot efficiency or COP of 3.33. If efficiency can exceed the bounds of the fitted curve in Figure 2.4, power savings can improve further. Similarly, the ratio of different workload ( $P_{electric}$ ) and  $P_{leakage}/P_{electric}$  can impact the optimal temperature and efficiency substantially. These two scenarios are explored in the next two sections.

## 3.2 Varying P<sub>leakage</sub>/P<sub>electric</sub> Ratios

In this section, the effectiveness of cooling at different  $P_{electric0}$  and  $P_{leakage}/P_{electric}$  ratios is analyzed. Two different analyses are performed. The first analysis maintains the  $P_{electric0}$  while varying  $P_{leakage}/P_{electric}$  ratio and the second analysis both varies the  $P_{electric0}$  and the  $P_{leakage}/P_{electric}$  ratio. Other parameters associated with the analyses are same as in Table 3.1.

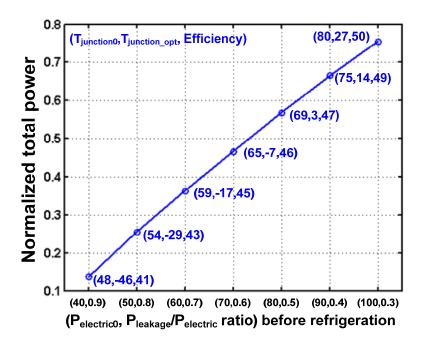

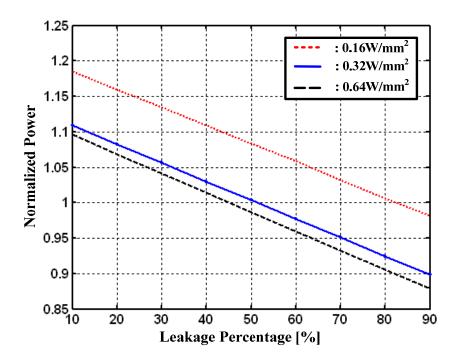

Figure 3-2: The dependence of the  $P_{leakage}/P_{electric}$  ratio on the optimal total power based on the simulation using the model. (x,y,z) correspond to optimal operating points of  $T_{junction}$  [°C],  $T_{cold}$  [°C], and the percent of Carnot [%], respectively.

In the first scenario, the total P<sub>electric0</sub> is maintained at 100W with T<sub>junction</sub> at 80°C with forced air cooling to correspond to the current practice of constraining the maximum power of the digital processor. The results of the analysis are shown Figure 3.2. Each data point indicates the power normalized to 100W. The figure includes the cold-end temperature, the junction temperature and the efficiency of the refrigeration system for each point. The power savings is roughly proportional to the percent of leakage. Figure 3.1 helps explains the nearly linear relationship. Because of the exponential relationship between

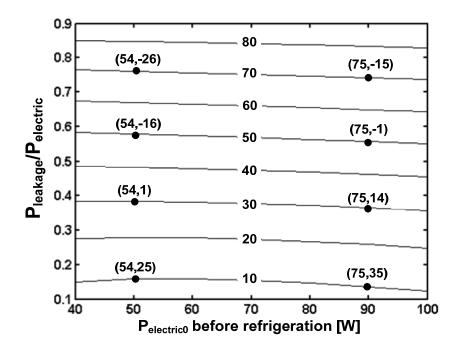

Figure 3-3: The dependence of the  $P_{electric0}$  and leakage ratio on the optimal total power based on the simulation using the model. (x,y,z) correspond to junction temperature before refrigeration  $T_{junction0}$  [°C], optimal operating points of  $T_{junction}$  [°C], and the percent of Carnot [%], respectively.

leakage power and temperature, most of the power saved at the optimal temperature is due to the leakage power. The analysis indicates only a modest power improvement when the system power is entire due to active power. The power savings due to active power is essentially offset by the cooling power. Note that the optimal operating temperature is lower for the system with higher leakage power.