## UC San Diego UC San Diego Electronic Theses and Dissertations

#### Title

Design of millimeter-wave power amplifiers using InP heterojunction bipolar transistors

**Permalink** https://escholarship.org/uc/item/0z87t0m5

**Author** O'Sullivan, Tomás

Publication Date 2009

Peer reviewed|Thesis/dissertation

#### UNIVERSITY OF CALIFORNIA, SAN DIEGO

#### Design of Millimeter-wave Power Amplifiers using InP Heterojunction Bipolar Transistors

A dissertation submitted in partial satisfaction of the requirements for the degree Doctor of Philosophy

in

Electrical Engineering (Electronic Circuits and Systems)

by

Tomás O'Sullivan

Committee in charge:

Professor Peter M. Asbeck, Chair Professor Robert Bitmead Professor William Griswold Professor Lawrence Larson Professor Gabriel Rebeiz

2009

Copyright

Tomás O'Sullivan, 2009

All rights reserved.

The dissertation of Tomás O'Sullivan is approved, and it is acceptable in quality and form for publication on microfilm and electronically:

Chair

University of California, San Diego

2009

#### DEDICATION

For Anu, whose endless love and support

inspires me everyday.

#### TABLE OF CONTENTS

| Signatu                             | re Page                   | 9                                                                             | iii                                        |

|-------------------------------------|---------------------------|-------------------------------------------------------------------------------|--------------------------------------------|

| Dedicat                             | ion                       |                                                                               | iv                                         |

| Table o                             | f Conte                   | ents                                                                          | v                                          |

| List of ]                           | Figures                   |                                                                               | vii                                        |

| List of '                           | Tables                    |                                                                               | Х                                          |

| Acknow                              | ledgem                    | ents                                                                          | xi                                         |

| Vita an                             | d Publi                   | ications                                                                      | xiii                                       |

| Abstrac                             | t of the                  | e Dissertation                                                                | xiv                                        |

| Chapter<br>1.1<br>1.2<br>1.3<br>1.4 | Millim<br>InP H<br>Design | roduction                                                                     | $\begin{array}{c}1\\2\\4\\6\\7\end{array}$ |

| Chapter                             | r 2 InF<br>tion           | P HBT Measurement and Modeling for Millimeter-wave Applicans                  | 10                                         |

| 2.1                                 |                           | rement of discrete devices - the need for de-embedding                        | 10                                         |

| 2.1<br>2.2                          |                           | bedding DC measurements                                                       | 11                                         |

| 2.3                                 |                           | bedding RF measurements                                                       | 13                                         |

|                                     | 2.3.1                     | Open-Short De-embedding                                                       | 14                                         |

|                                     | 2.3.2                     | TRL De-embedding                                                              | 15                                         |

|                                     | 2.3.3<br>2.3.4            | EM Simulation based comparison technique                                      | 17                                         |

|                                     |                           | De-embedding                                                                  | 21                                         |

|                                     | 2.3.5                     | Conclusions of De-embedding Study                                             | 26                                         |

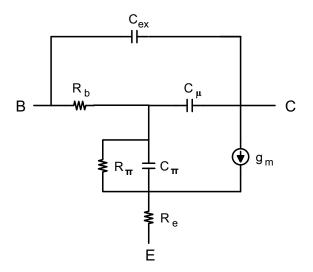

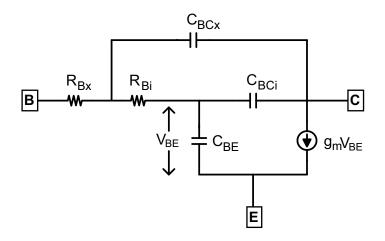

| 2.4                                 | Comp                      | act Model Choice for High Speed InP HBT Applications                          | 28                                         |

| 2.5                                 | Measu                     | rement Setup and Required Measurements                                        | 29                                         |

| 2.6                                 |                           | ction Procedure for the Agilent HBT Model                                     | 30                                         |

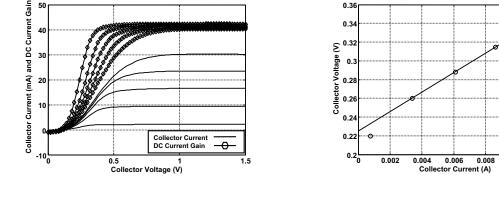

|                                     | 2.6.1                     | Device Burn-in                                                                | 31                                         |

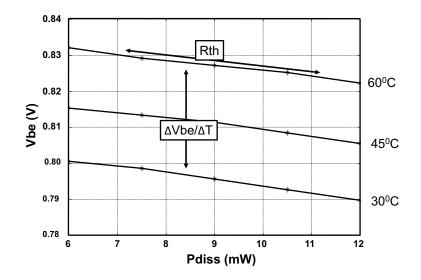

|                                     | 2.6.2                     | Thermal Resistance $(\mathbf{R}_{th})$                                        | 32                                         |

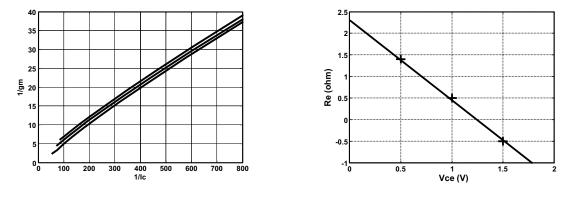

|                                     | 2.6.3                     | Emitter Resistance $(\mathbf{R}_e)$                                           | 33                                         |

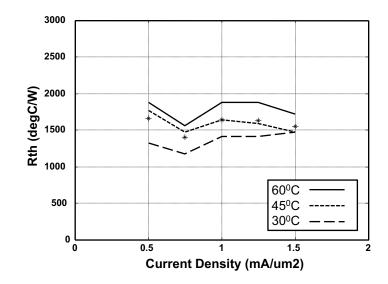

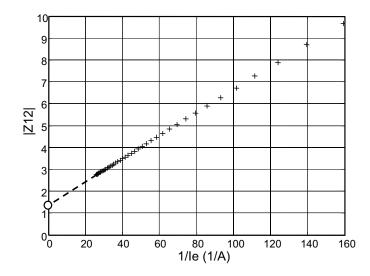

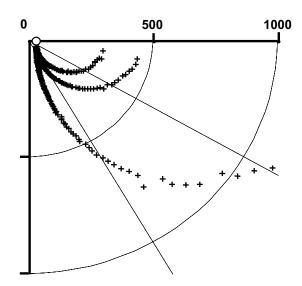

|                                     | 2.6.4                     | Base Resistance $(\mathbf{R}_b)$                                              | 35                                         |

|                                     | 2.6.5                     | Collector Resistance $(\mathbf{R}_c)$                                         | 37                                         |

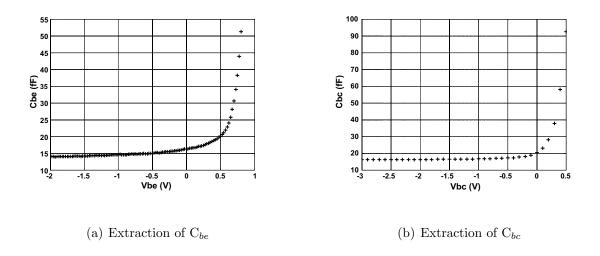

|                                     | 2.6.6                     | Base-Emitter and Base-Collector Capacitances $(C_{be} \text{ and } C_{bc})$ . | 39                                         |

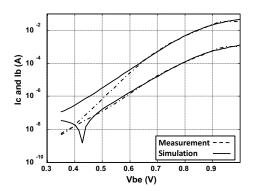

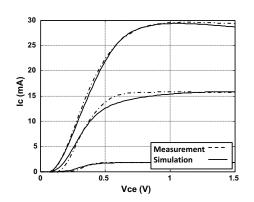

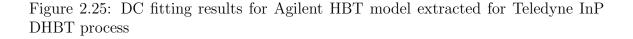

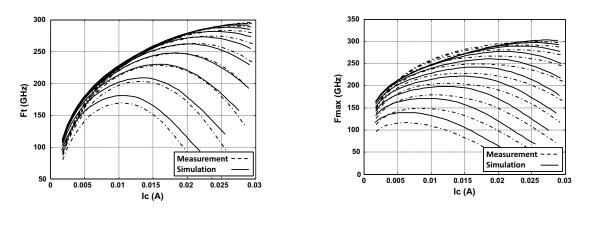

|         | 2.6.7 DC and RF Parameter Fitting                                 | 40           |

|---------|-------------------------------------------------------------------|--------------|

| 2.7     | Conclusion                                                        | 42           |

| Chapter | 3 Design of Millimeter-wave Power Cells                           | 43           |

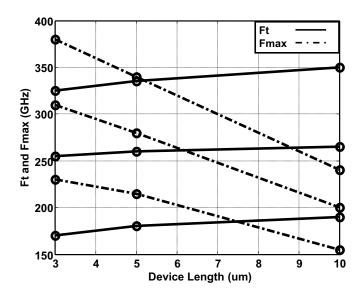

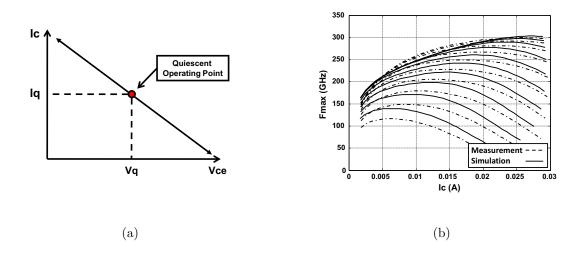

| 3.1     | Device sizing and operating current density                       | 44           |

| 3.2     | Choice of Amplifier Configuration: Common Emitter, Common Base    |              |

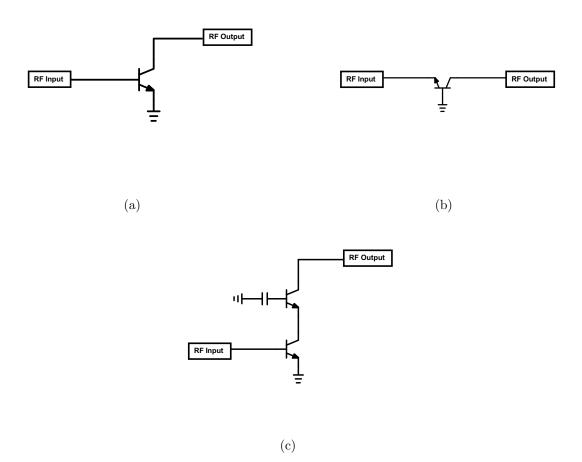

| 0.0     | and Cascode                                                       | 47           |

| 3.3     | Ballasting for Cascode Power Cells                                | 53           |

| 3.4     | AC Ground Impedance at Base of Common Base Stage of Cascode Cell  | 58           |

| 3.5     | Powercell Design, Simulation and Measurement                      | 61           |

| 3.6     | Conclusion                                                        | 68           |

| Chapter | 4 Power Amplifier and Power Combiner Design                       | 69           |

| 4.1     | Millimeter-wave Power Amplifier Topology                          | 70           |

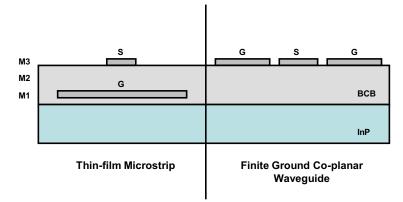

|         | 4.1.1 Transmission Line Choices - Thin Film Microstrip Versus Co- |              |

|         | Planar Waveguide                                                  | 71           |

|         | 4.1.2 Matching Network Design and Simulation                      | 75           |

|         | 4.1.3 20dBm Amplifier Design, Simulation and Measurement          | 81           |

|         | 4.1.4 Analysis of Amplifier Efficiency performance                | 92           |

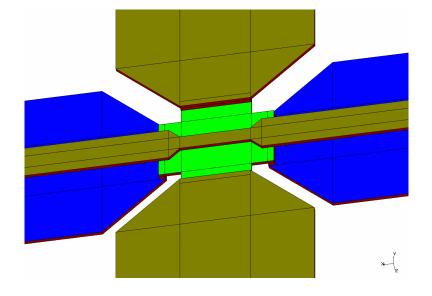

| 4.2     | Power Combiner Design - On-Chip Radial Power Combiner             | 94           |

|         | 4.2.1 Choice of Power Combiner Topology                           | 95           |

|         | 4.2.2 Radial Power Combiner Overview and Operation                | 97           |

|         | 4.2.3 Transmission Line Design                                    | 98           |

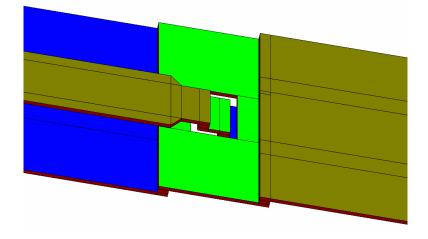

|         | 4.2.4 Inverted Microstrip to Microstrip Transition                | 100          |

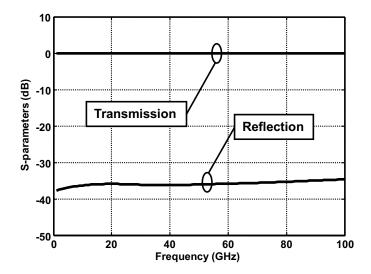

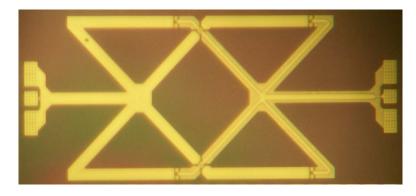

|         | 4.2.5 Microstrip Crossover                                        | 101          |

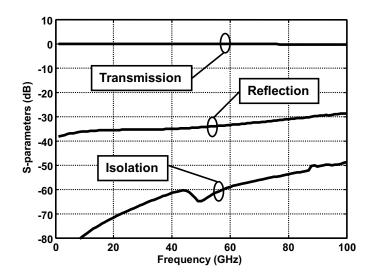

|         | 4.2.6 Back to Back Results                                        | 102          |

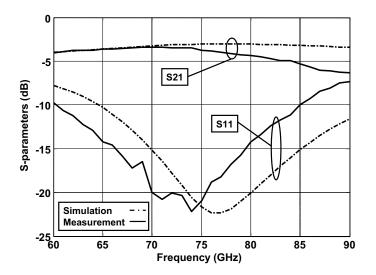

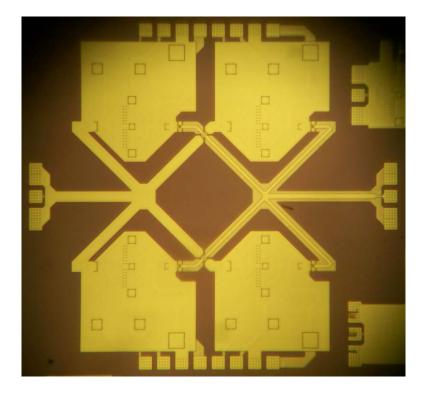

| 4.3     | Planar Radial Power Amplifier Design                              | 105          |

| 4.4     | Conclusion                                                        | 109          |

| Chapter | 5 Conclusion and Future Work                                      | 112          |

| 5.1     |                                                                   | 112          |

| 0.1     |                                                                   | 113          |

|         |                                                                   | 114          |

|         | 0                                                                 | $114 \\ 115$ |

| 5.2     | - 0                                                               | 116          |

| 0.2     |                                                                   | 110          |

| Bibliog | aphy                                                              | 118          |

#### LIST OF FIGURES

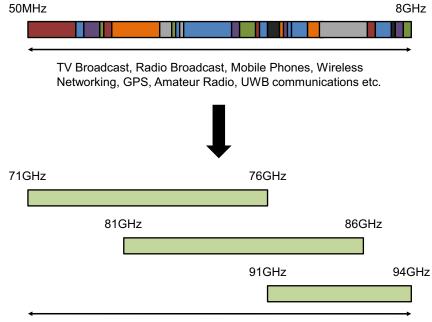

| Figure 1.1: Channel bandwidth comparison between E-band radios and sub<br>8 GHz communication systems | 2             |

|-------------------------------------------------------------------------------------------------------|---------------|

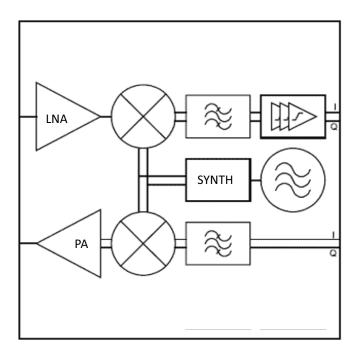

| Figure 1.2: Simplified transceiver block diagram                                                      | $\frac{2}{4}$ |

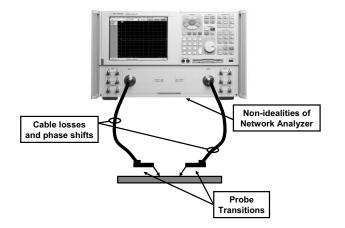

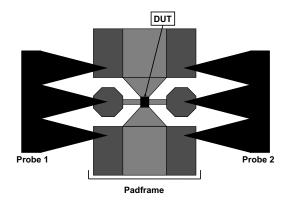

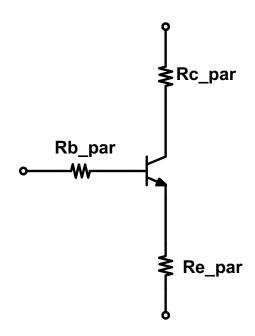

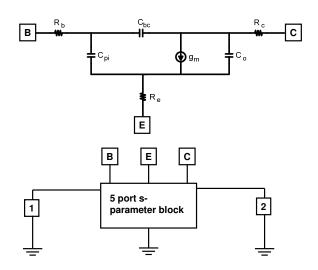

| Figure 2.1: Parasitics introduced in the measurement of devices                                       | 12            |

| Figure 2.2: Parasitic resistances to be de-embedded for DC data                                       | 13            |

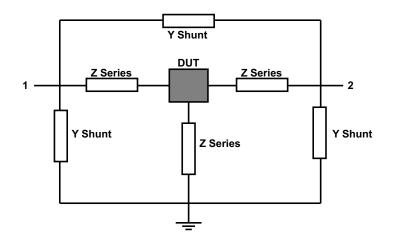

| Figure 2.3: Padframe parasitics as represented in Open-Short technique                                | 15            |

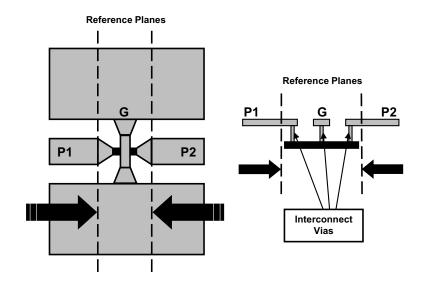

| Figure 2.4: Illustration of reference planes after TRL de-embedding with un-                          |               |

| deembedded inductance shown                                                                           | 16            |

|                                                                                                       | 18            |

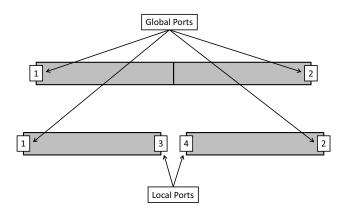

| · · · ·                                                                                               | 19            |

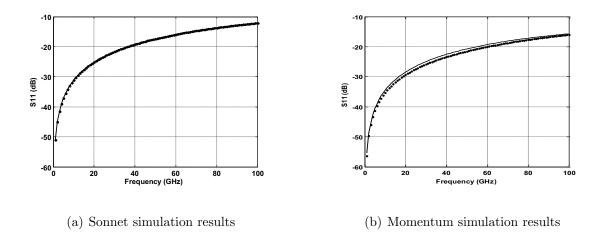

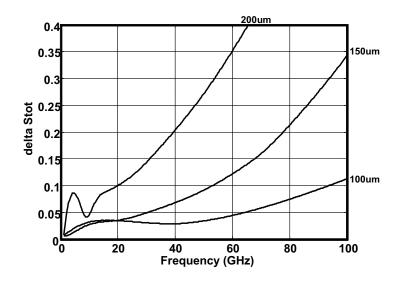

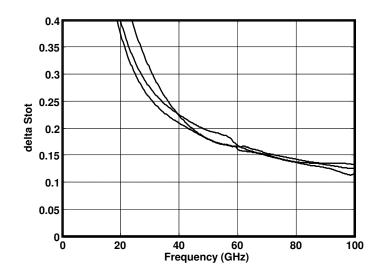

| Figure 2.7: GLG de-embedding simulation study results for both solvers (solid:                        |               |

|                                                                                                       | 20            |

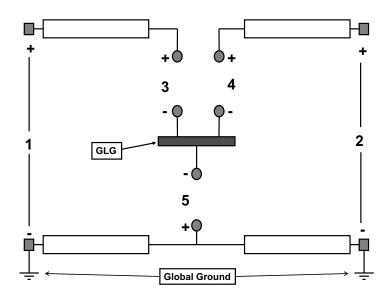

|                                                                                                       | 21            |

| · · · · ·                                                                                             | 22            |

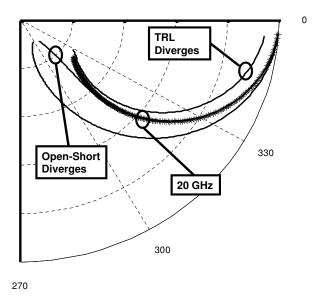

| 0 0 1                                                                                                 | 23            |

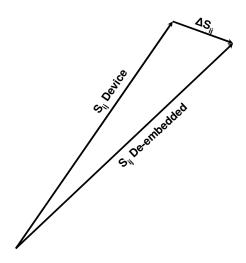

|                                                                                                       | 24            |

|                                                                                                       | 25            |

| · · · · · ·                                                                                           | 26            |

|                                                                                                       | 27            |

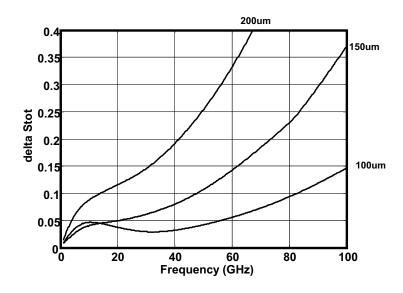

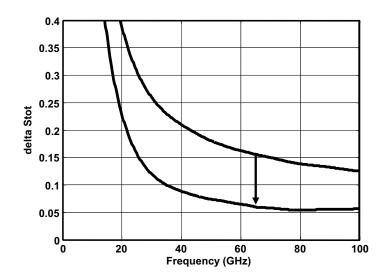

| Figure 2.15: Reduction in $\Delta S_{TOT}$ for TRL algorithm when via inductance is                   |               |

|                                                                                                       | 29            |

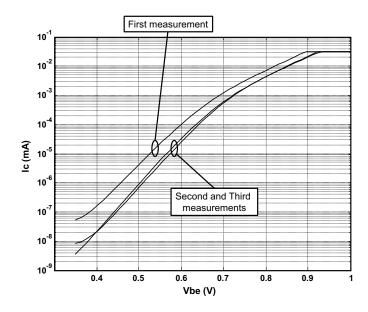

|                                                                                                       | 31            |

| 0                                                                                                     | 33            |

|                                                                                                       | 34            |

| · · · · · · · · · · · · · · · · · · ·                                                                 | 35            |

| · ·                                                                                                   | 36            |

| •                                                                                                     | 37            |

| Figure 2.22: Extraction of Base Resistance using modified circle impedance                            |               |

| -                                                                                                     | 38            |

| Figure 2.23: Representative plots for Forced Beta method for Collector Resis-                         |               |

|                                                                                                       | 39            |

|                                                                                                       | 40            |

| Figure 2.25: DC fitting results for Agilent HBT model extracted for Teledyne                          |               |

|                                                                                                       | 41            |

| Figure 2.26: RF fitting results for Agilent HBT model extracted for Teledyne                          |               |

|                                                                                                       | 42            |

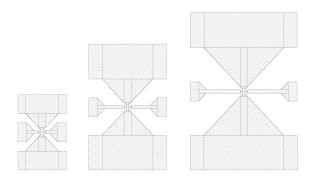

| Figure 3.1: Variation of Ft and Fmax with finger length                                               | 44            |

| 0 0                                                                                                   | 46            |

| Figure 3.3: (a) Loadline swing for class A operation with quiescent operating                         | 10            |

| point shown (b) Variation of Fmax with collector current and voltage                                  | 47            |

| Figure 3.4: Common emitter (a), common base (b) and cascode (c) amplifier                                                                            |   |

|------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| topologies $\ldots \ldots 48$               | 8 |

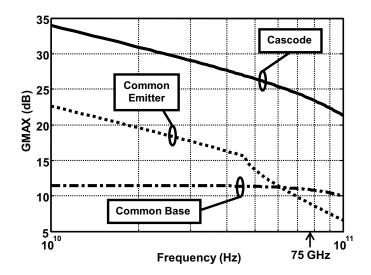

| Figure 3.5: Comparison of Maximum Gain for different amplifier configurations 49                                                                     | 9 |

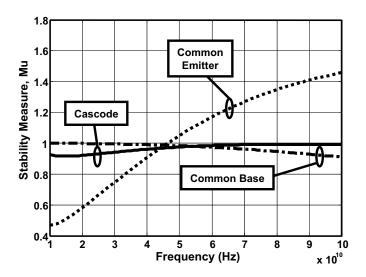

| Figure 3.6: Comparison of Stability Measure for different amplifier configura-                                                                       |   |

| tions $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ 50                                                            | 0 |

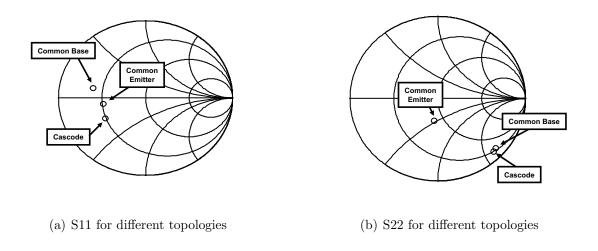

| Figure 3.7: Input and output impedances presented by the devices in the three                                                                        |   |

| different topologies                                                                                                                                 | 2 |

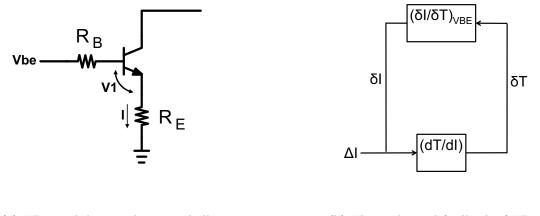

| Figure 3.8: Figures for calculation of HBT ballast resistance                                                                                        | 4 |

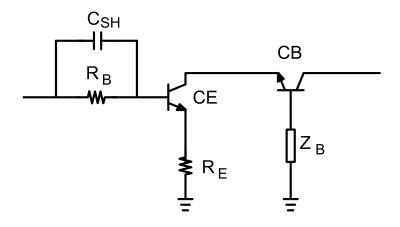

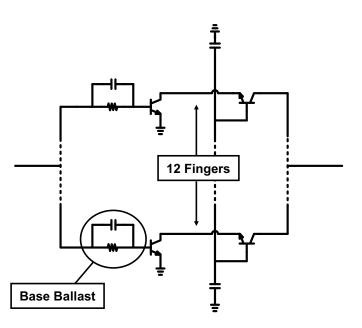

| Figure 3.9: Cascode cell schematic with base and emitter ballasting 5                                                                                | 5 |

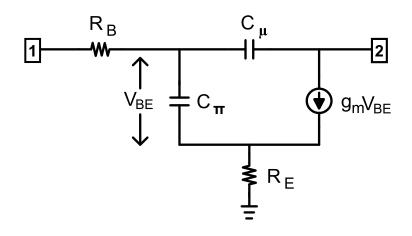

| Figure 3.10: Small signal model for stability analysis                                                                                               | 6 |

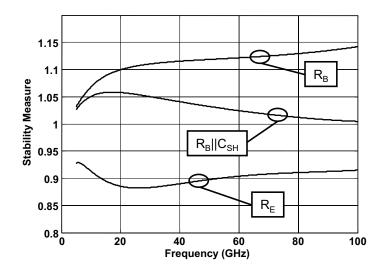

| Figure 3.11: Stability measure $(\mu)$ versus frequency for different ballasting con-                                                                |   |

| figurations                                                                                                                                          | 8 |

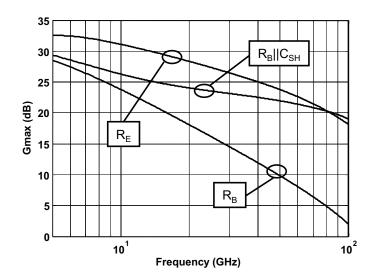

| Figure 3.12: Maximum gain versus frequency for different ballasting configu-                                                                         |   |

| rations $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $59$                                                                 | 9 |

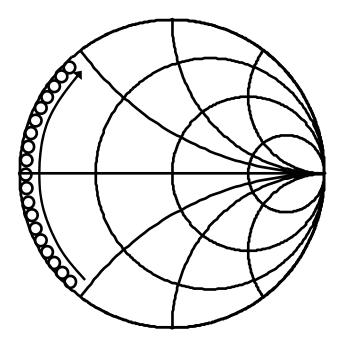

| Figure 3.13: Variation of Impedance Presented at base of CB stage of cascode                                                                         |   |

| $\operatorname{cell} \ldots $ | 0 |

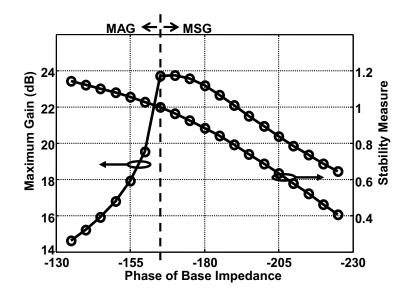

| Figure 3.14: Maximum Gain (Gmax) and stability measure $(\mu)$ versus impedance                                                                      |   |

| variation at base of CB stage of cascode cell                                                                                                        | 1 |

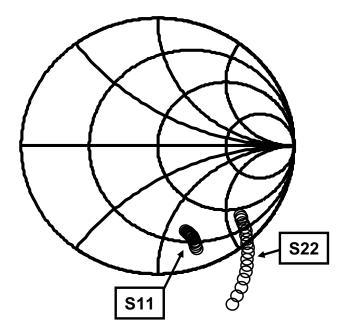

| Figure 3.15: S11 and S22 at 75 GHz versus impedance variation at base of CB                                                                          |   |

| stage of cascode cell                                                                                                                                | 2 |

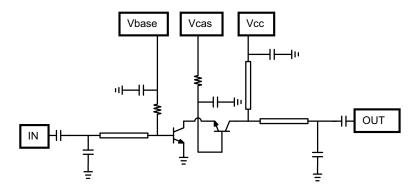

| Figure 3.16: Schematic view of 12 finger millimeter-wave power cell 65                                                                               |   |

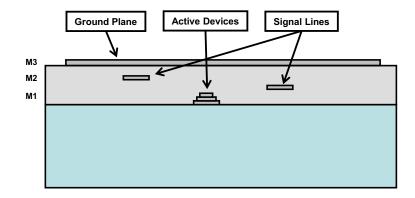

| Figure 3.17: Cross section of inverted microstrip transmission line topology . 64                                                                    |   |

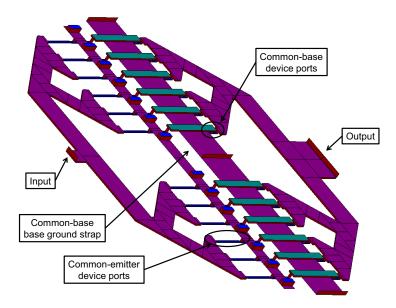

| Figure 3.18: EM simulation schematic view of millimeter-wave power cell 65                                                                           |   |

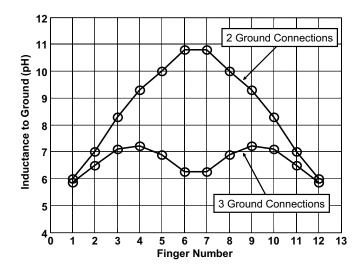

| Figure 3.19: Variation of Inductance to ground at base of CB stage across array 6                                                                    |   |

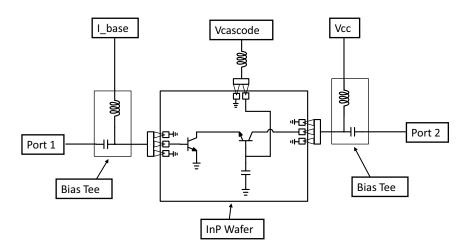

| Figure 3.20: Measurement setup for cascode power cell test                                                                                           |   |

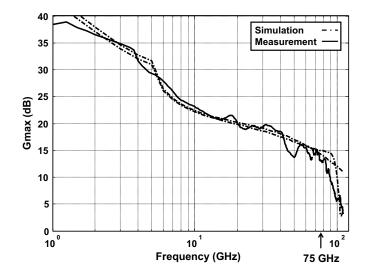

| Figure 3.21: Simulated and measured Gmax of 12 finger cascode power cell . 66                                                                        |   |

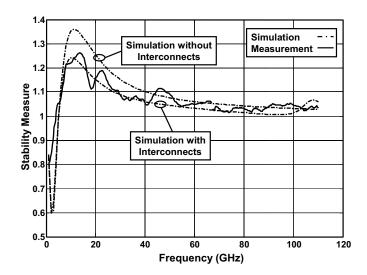

| Figure 3.22: Simulated and measured stability measure of 12 finger cascode                                                                           | 0 |

| power cell                                                                                                                                           | 7 |

|                                                                                                                                                      | ' |

| Figure 4.1: Simplified schematic overview of millimeter-wave power amplifier 70                                                                      | 0 |

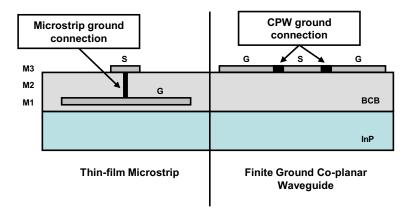

| Figure 4.2: Topology comparison of Microstrip and Co-planar Waveguide                                                                                |   |

| Transmission Lines                                                                                                                                   | 2 |

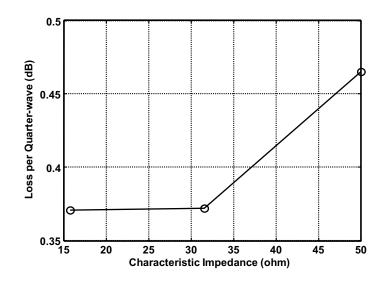

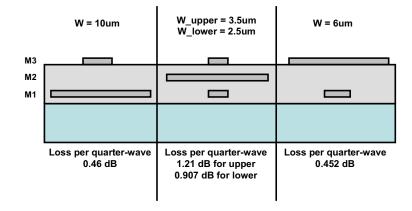

| Figure 4.3: Variation in loss per quarter wavelength at 75GHz for Microstrip                                                                         |   |

| line $\ldots$ $74$                                                                                                                                   | 4 |

| Figure 4.4: Comparison of ground connections for microstrip and CPW trans-                                                                           |   |

| mission lines                                                                                                                                        | 5 |

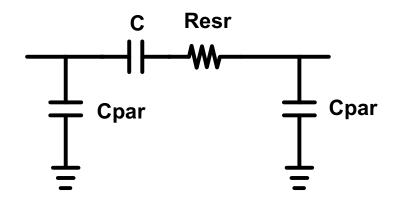

| Figure 4.5: Lumped element model of MIM capacitors                                                                                                   | 6 |

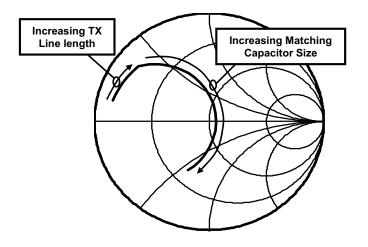

| Figure 4.6: Impedance transformation contour of compact LC input matching                                                                            |   |

| $network \dots \dots$                          | 7 |

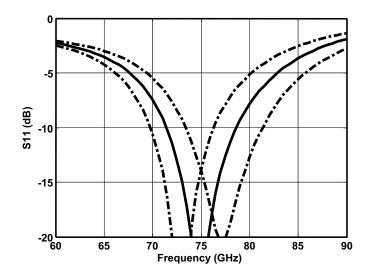

| Figure 4.7: Variation of S11 as input matching capacitor varies $+/-15\%$ from                                                                       |   |

| its nominal value (nominal - solid, capacitor variation - dashed) . 78                                                                               | 8 |

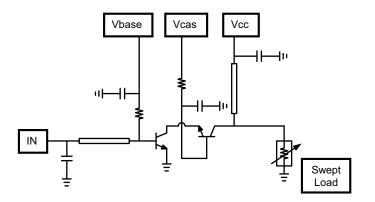

| Figure 4.8: Load-pull simulation setup to determine maximum output power                                                                             |   |

| impedance condition                                                                                                                                  | 9 |

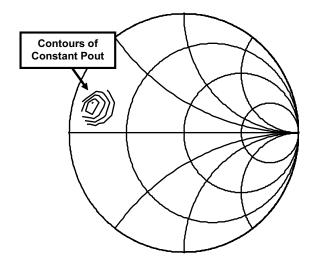

| Figure 4.9: Load-pull simulation results showing contours of constant output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| power                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

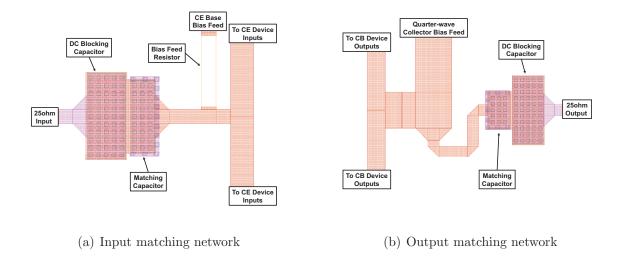

| Figure 4.10: Layout of input (a) and output (b) matching networks (M3 top layer removed for clarity)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

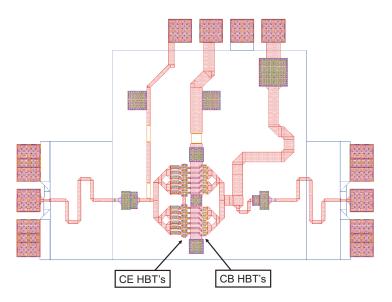

| Figure 4.11: Final layout image of unit power amplifier - chip dimensions in-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| cluding pads 1140um x 770um                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

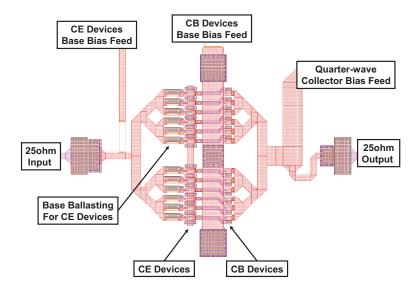

| Figure 4.12: Layout image of core of unit power amplifier - core dimensions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 520um x 370um                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

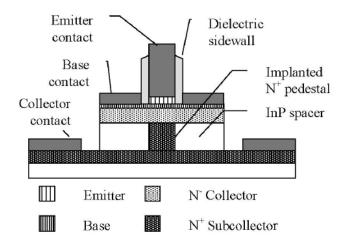

| Figure 4.13: Teledyne InP DHBT device cross-section                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

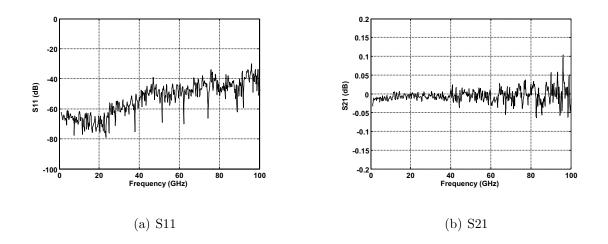

| Figure 4.14: Measurement of $50\Omega$ transmission line after SOLT calibration (a)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| S11 (b) S21 $\ldots$ S11 (c) S21 ( |

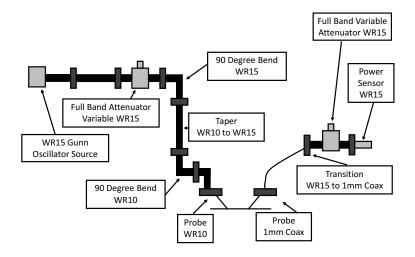

| Figure 4.15: Measurement setup for millimeter-wave power sweeps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

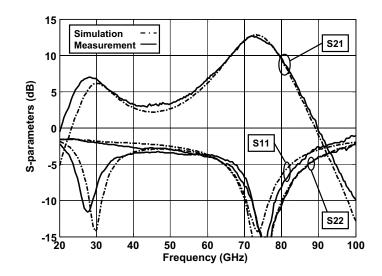

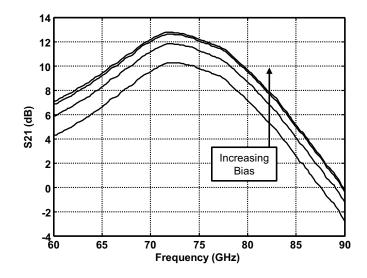

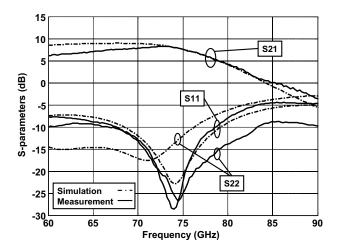

| Figure 4.16: Small signal performance of unit power amplifier - simulation and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| measurement results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

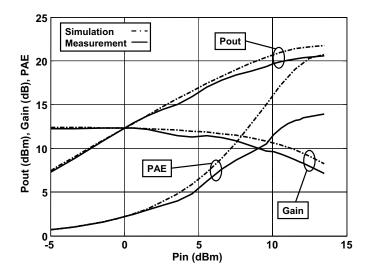

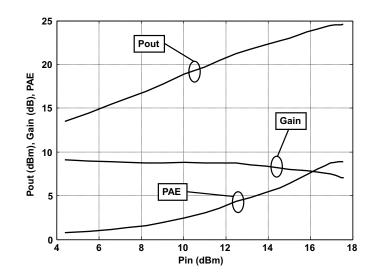

| Figure 4.17: Large signal power sweep of unit power amplifier at 71 GHz -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| simulation and measurement results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

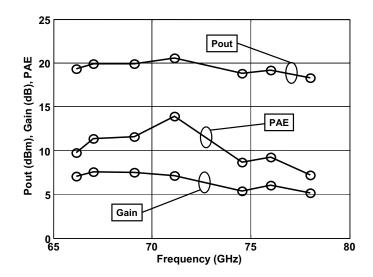

| Figure 4.18: Saturated output power performance of unit power amplifier from                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 66-78 GHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Figure 4.19: Change in amplifier gain versus bias current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Figure 4.20: Variation in amplifier gain across wafer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

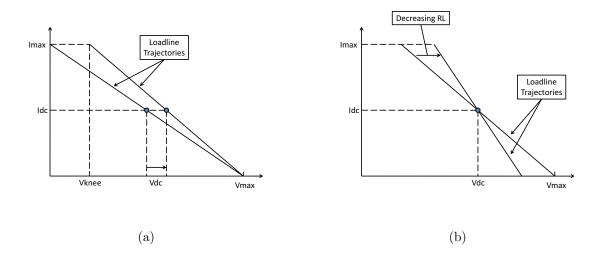

| Figure 4.21: Effect of (a) increasing knee voltage and (b) reducing load resis-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| tance on load-line swing $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

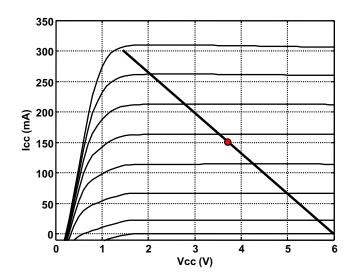

| Figure 4.22: Simulated I-V characteristics of powercell with optimum loadline                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| overlaid                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

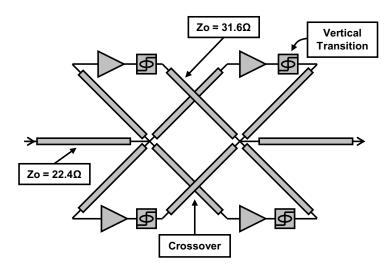

| Figure 4.23: Schematic overview of 4-way planar radial splitter/combiner layout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Figure 4.24: Transmission line losses for various microstrip configurations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

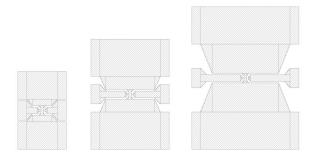

| Figure 4.25: Vertical inverted microstrip to microstrip transition 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |