## **UCLA**

## **UCLA Electronic Theses and Dissertations**

#### **Title**

A System-Level Analysis of a Wireless Low-Power Biosignal Recording Device

#### **Permalink**

https://escholarship.org/uc/item/1836k3z4

#### **Author**

Chandler, Rodney James

## **Publication Date**

2012

Peer reviewed|Thesis/dissertation

# University of California Los Angeles

# A System-Level Analysis of a Wireless Low-Power Biosignal Recording Device

A dissertation submitted in partial satisfaction of the requirements for the degree Doctor of Philosophy in Electrical Engineering

by

Rodney James Chandler

$\ \, \bigcirc$  Copyright by Rodney James Chandler 2012

#### Abstract of the Dissertation

# A System-Level Analysis of a Wireless Low-Power Biosignal Recording Device

by

## Rodney James Chandler

Doctor of Philosophy in Electrical Engineering University of California, Los Angeles, 2012 Professor Jack W. Judy, Chair

Development of brain-machine interfaces and treatment of neurological diseases can benefit from analysis of recorded data from implanted electrodes. Existing wireless neural recording systems are often bulky, dissipate too much heat to be implanted, or only have a small number of channels. Furthermore, advances in micro-machined electrodes provide the possibility of high-density recordings, but the companion electronics do not provide enough simultaneous channels with low enough power, wireless telemetry, or a small form-factor. A system level view of wireless recording-circuitry which could overcome these deficiencies is described in this work. The overall system comprises of an analog front end (AFE), digital signal processing (DSP), and transmitter (TX). Each block is analyzed, and system-level specifications are derived. Based on these specifications, each block can be optimized for low power and small area. The analog front-end uses open-loop amplifiers to support lower voltage operation than previously published work. A prototype amplifier was also fabricated to measure performance in a 65-nm CMOS process that is needed for low-power digital signal processing. The amplifier performance was comparable to other recently published amplifiers with 2.5  $\mu$ V noise in 10 kHz bandwidth while dissipating 17.2  $\mu$ V from a low 1 V supply. The use of programmable bias currents in the amplifier, to exploit the trade-off between noise and power, was proposed to set each individual amplifier's noise level (and power) to meet

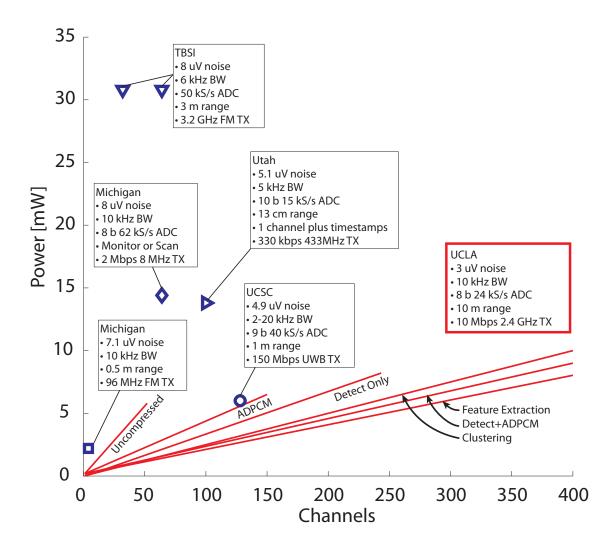

requirements for accurate spike detection. Literature reviews of digital-signal processors and transmitters are used to construct approximate models of power versus performance. These models are then used to investigate the overall system power with different levels of digital processing. With a target application of neural spike recording, four modes (raw data, spike detection, feature extraction, and clustering) were analyzed. A system that uses feature extraction yields the lowest overall power, supports 400 channels with a practical wireless link, and consumes approximately 8 mW.

The dissertation of Rodney James Chandler is approved.

Hugh T. Blair

Dejan Marković

Sudhakar Pamarti

Jack W. Judy, Committee Chair

University of California, Los Angeles 2012

To Karen...

## Table of Contents

| 1 Introduction |                  |                                                                            | 1  |

|----------------|------------------|----------------------------------------------------------------------------|----|

|                | 1.1              | Background                                                                 | 1  |

|                | 1.2 Applications |                                                                            | 2  |

|                |                  | 1.2.1 Clinical Application: Epileptic-Seizure Mapping                      | 3  |

|                |                  | 1.2.2 Preclinical Application: Brain-Computer Interfaces                   | 4  |

|                |                  | 1.2.3 Preclinical Application: Recording of Brain Activity in Enriched En- |    |

|                |                  | vironments                                                                 | 5  |

|                | 1.3              | System Description                                                         | 7  |

|                | 1.4              | Proposed Solution                                                          | 11 |

|                | 1.5              | Organization                                                               | 11 |

|                | 1.6              | Acknowledgments                                                            | 12 |

| 2              | Lite             | erature Review                                                             | 13 |

|                | 2.1              | Introduction                                                               | 13 |

|                | 2.2              | Classification of Recording Systems                                        | 15 |

|                | 2.3              | Summary                                                                    | 20 |

| 3              | Blo              | ck Level Design                                                            | 23 |

|                | 3.1              | Introduction                                                               | 23 |

|                | 3.2              | Neurons and Electrodes                                                     | 23 |

|                | 3.3              | Analog Front-End Amplifier                                                 | 27 |

|                |                  | 3.3.1 Differential Amplifier Configuration                                 | 27 |

|                     | 3.3.2  | Existing Neural Amplifiers                              | 29 |

|---------------------|--------|---------------------------------------------------------|----|

|                     | 3.3.3  | Amplifier Design                                        | 33 |

|                     |        | 3.3.3.1 Noise Contributions                             | 33 |

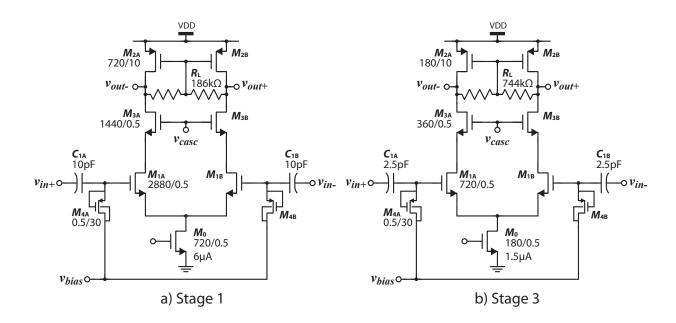

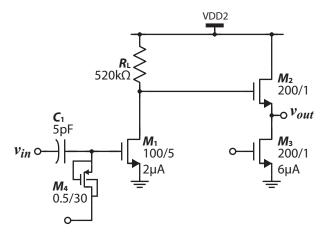

|                     | 3.3.4  | Transistor-Level Design                                 | 35 |

|                     | 3.3.5  | Optimization                                            | 38 |

|                     |        | 3.3.5.1 Optimal Bias Current                            | 38 |

|                     | 3.3.6  | Accounting for Flicker Noise                            | 44 |

|                     | 3.3.7  | Adjustable Biasing                                      | 45 |

|                     | 3.3.8  | Summary of the Design Methodology                       | 47 |

| 3.4                 | Analog | g-to-Digital Converters                                 | 48 |

| 3.5 Spike Detection |        |                                                         | 50 |

|                     | 3.5.1  | Spike-Detection Algorithms                              | 51 |

|                     | 3.5.2  | Modes of Operation                                      | 52 |

|                     | 3.5.3  | Analog Spike Detection                                  | 53 |

|                     |        | 3.5.3.1 Absolute-Value Threshold Detector               | 53 |

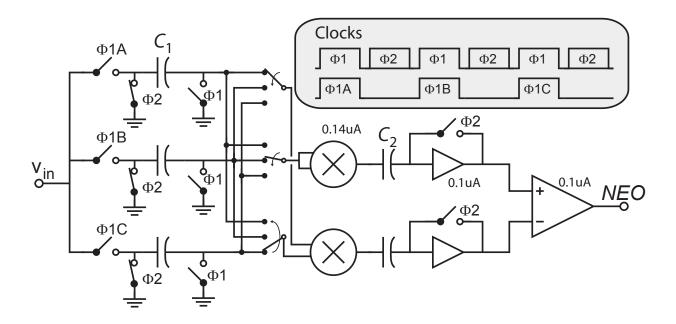

|                     |        | 3.5.3.2 Analog Nonlinear Energy Operator (NEO) Detector | 54 |

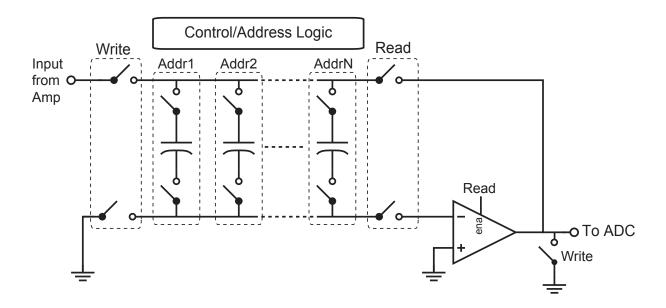

|                     |        | 3.5.3.3 Analog Memory                                   | 56 |

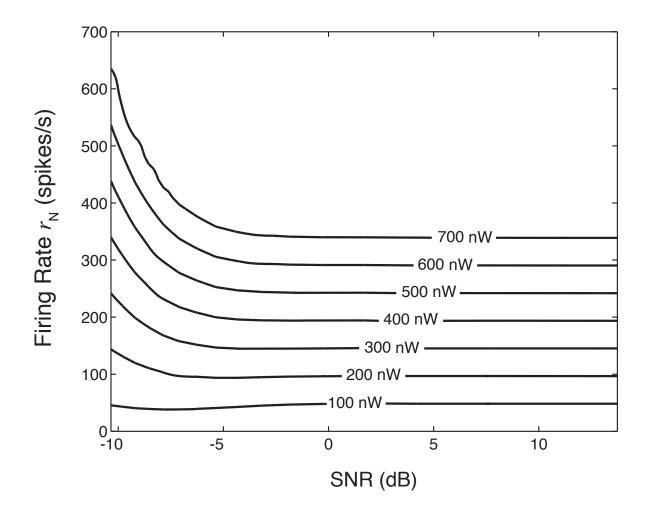

|                     | 3.5.4  | Effect of SNR and Firing Rate on Analog Detection Power | 57 |

|                     | 3.5.5  | Digital Spike Detection                                 | 58 |

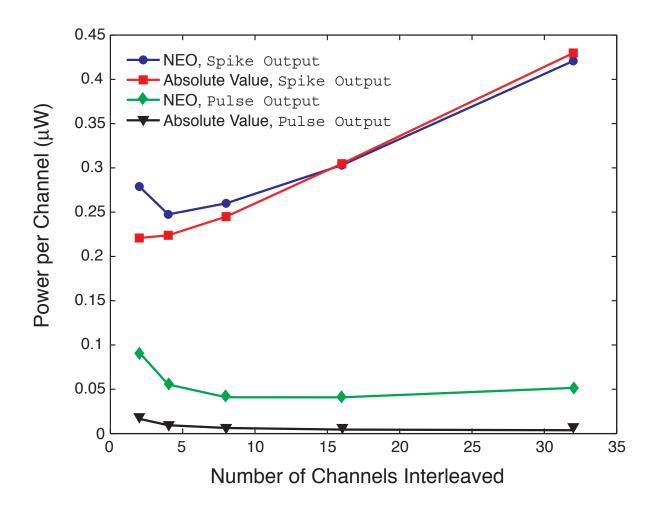

|                     | 3.5.6  | Results                                                 | 60 |

|                     | 3.5.7  | Summary of Spike Detection                              | 63 |

| 3.6                 | Digita | l Signal Processing                                     | 65 |

| 27                  | Wirele | ogg Transmitter                                         | 66 |

|              | 3.8  | Conclusion                               | 68         |

|--------------|------|------------------------------------------|------------|

| 4            | Syst | tem Design                               | <b>7</b> 0 |

|              | 4.1  | Introduction                             | 70         |

|              |      | 4.1.1 System Candidates                  | 70         |

|              |      | 4.1.1.1 Output Modes                     | 72         |

|              |      | 4.1.1.2 Transmitter Operation            | 74         |

|              |      | 4.1.1.3 System Summary                   | 76         |

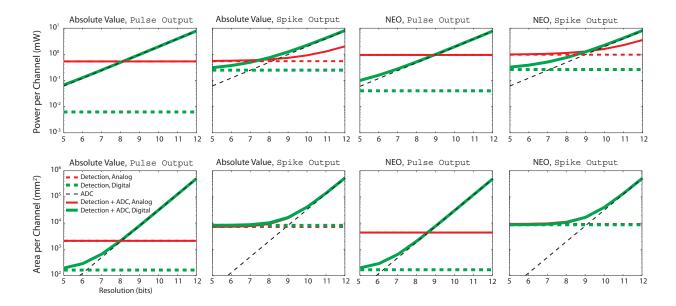

|              | 4.2  | System Power Estimates                   | 76         |

|              | 4.3  | Conclusion                               | 82         |

| 5            | Imp  | Dementation                              | 34         |

|              | 5.1  |                                          | 84         |

|              |      | 5.1.1 Test PCB                           | 86         |

|              | 5.2  |                                          | 88         |

|              | 5.3  |                                          | 90         |

| 6            | Con  |                                          | 95         |

| $\mathbf{A}$ | A S  | hort Summary of EKV Model                | 97         |

|              | A.1  | $I_{ m S}$ Definition                    | 97         |

|              | A.2  | Transconductance                         | 97         |

|              | A.3  | Capacitance                              | 98         |

|              | A.4  | Saturation Voltage $V_{\mathrm{DS,sat}}$ | 99         |

|              | A.5  | Modelling of Transistors versus $IC$     | OC         |

| References |  | 102 |

|------------|--|-----|

|------------|--|-----|

## LIST OF FIGURES

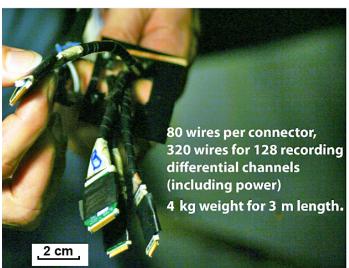

| 1.1  | (left) Connector and cable detail. (right) Ceiling mounted commutator and         |    |

|------|-----------------------------------------------------------------------------------|----|

|      | video cameras, attached to headstage amplifiers via 3 m cable                     | 9  |

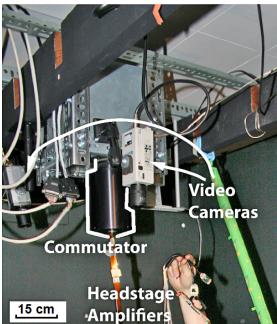

| 2.1  | Different system configurations for wireless neural recording: (a) analog record- |    |

|      | ing (b) spike detection (c) digital signal processing                             | 14 |

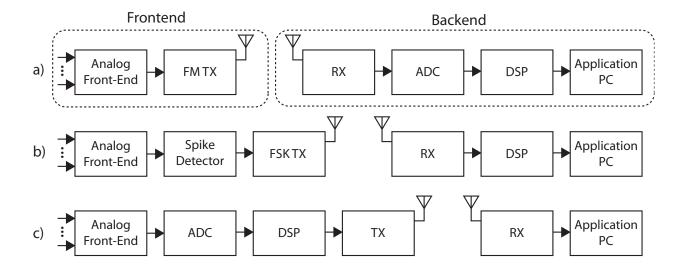

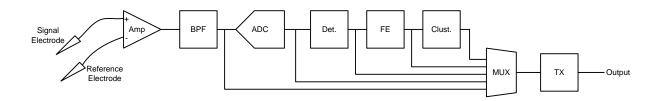

| 3.1  | Block diagram of biological signal recording system                               | 23 |

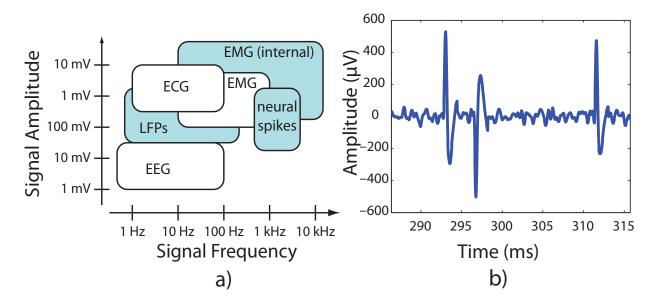

| 3.2  | (a) Characteristics of different biosignals, (b) A recording of a neural spike    | 24 |

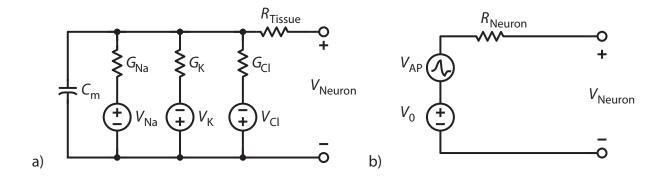

| 3.3  | An Electrical Model of a Neuron                                                   | 25 |

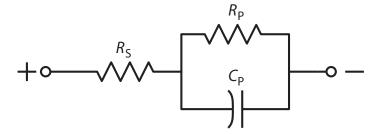

| 3.4  | Electrode Model                                                                   | 26 |

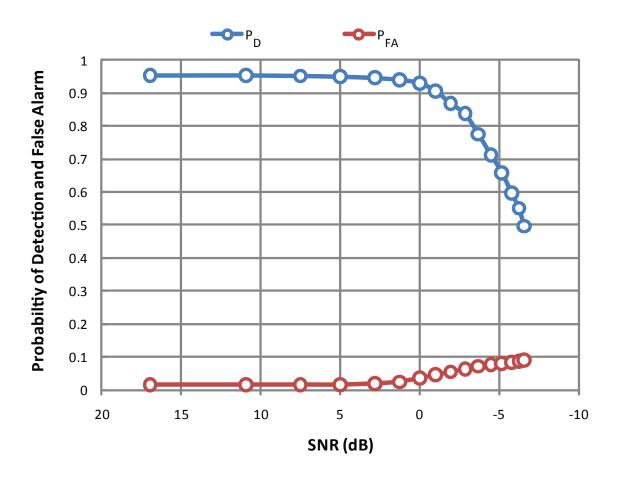

| 3.5  | Required SNR of different spike detection algorithms                              | 30 |

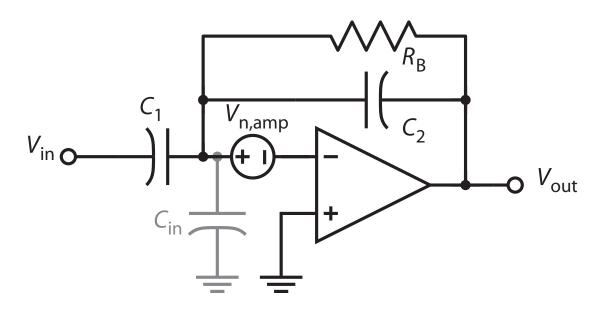

| 3.6  | Capacitively Coupled Amplifier. $v_{\rm n,amp}$ is the noise of the amplifier     | 31 |

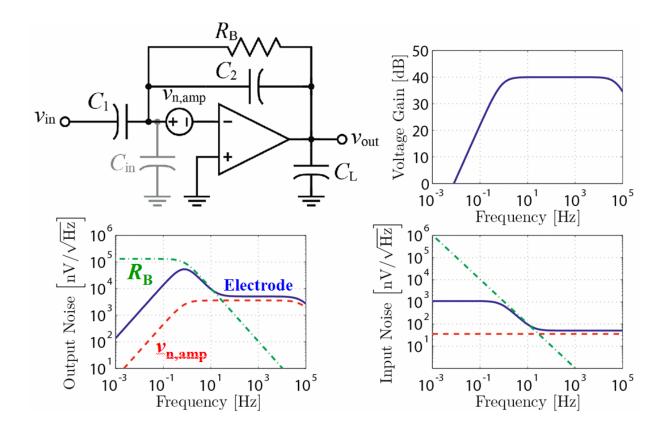

| 3.7  | Noise contributions for an ac-coupled neural spike amplifier                      | 34 |

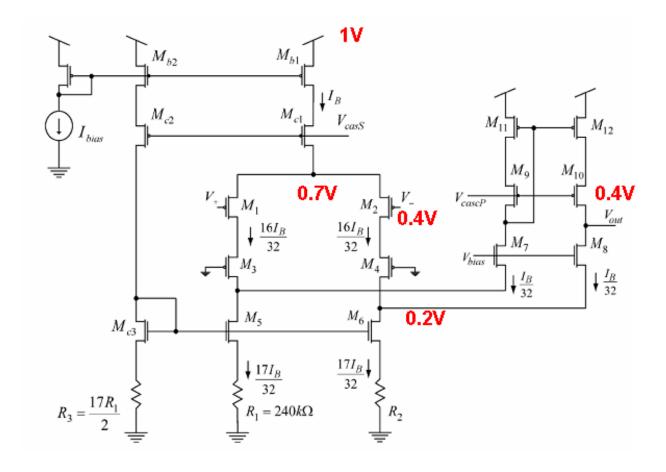

| 3.8  | Amplifier bias voltages with 1 V supply                                           | 36 |

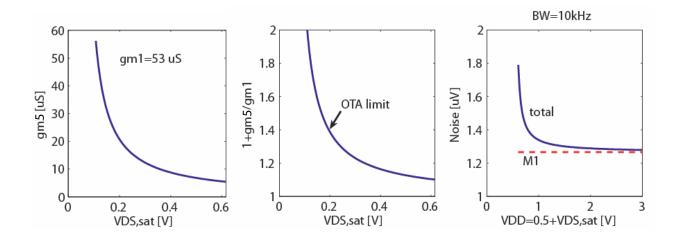

| 3.9  | Relative noise from $M_5$ as a function of $V_{\rm ds,sat}$ and $VDD$             | 37 |

| 3.10 | Cascaded Amplifiers to replace using Op Amps, when using a low supply             |    |

|      | voltage                                                                           | 37 |

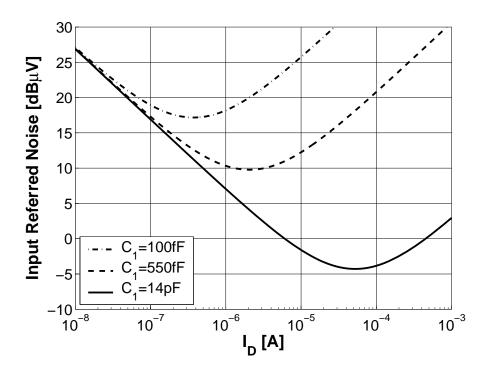

| 3.11 | Plot of Input Referred Noise for different $C_1$ values. For a Neural Spike       |    |

|      | Amplifier, 14 pF is required. (With $IC$ =0.1 and an NMOS input.)                 | 41 |

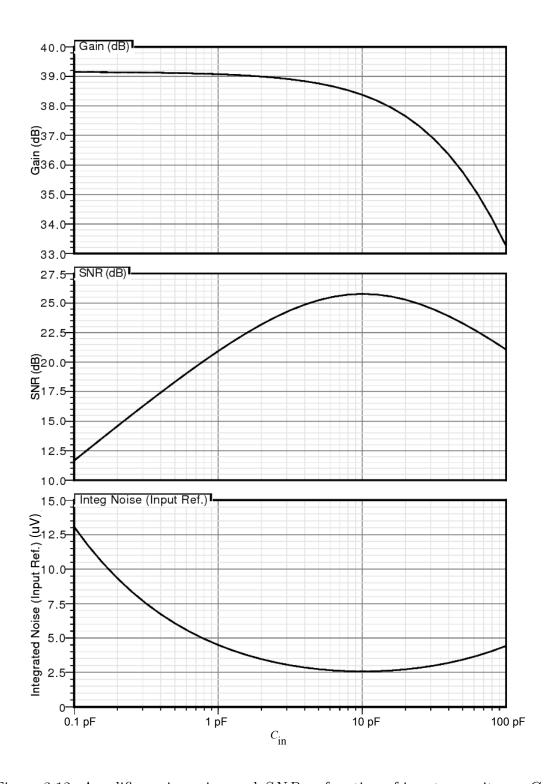

| 3.12 | Amplifier gain, noise, and $SNR$                                                  | 43 |

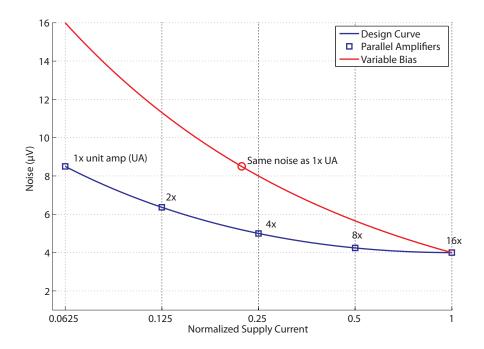

| 3.13 | Adjustable bias with parallel amplifiers or variable bias current. Parallel am-   |    |

|      | plifiers give a better noise-power tradeoff                                       | 46 |

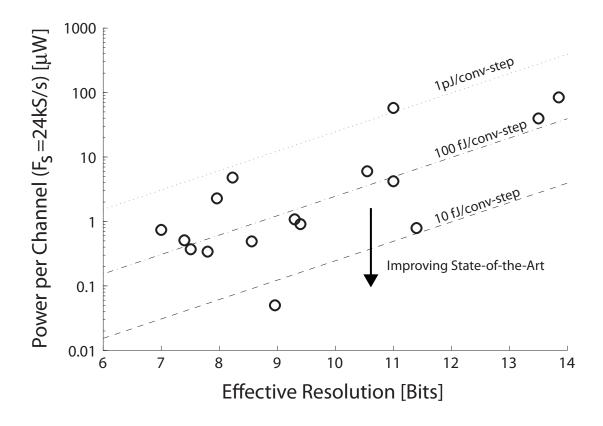

| 3.14 | Plot comparing of recent low-power ADCs                                           | 49 |

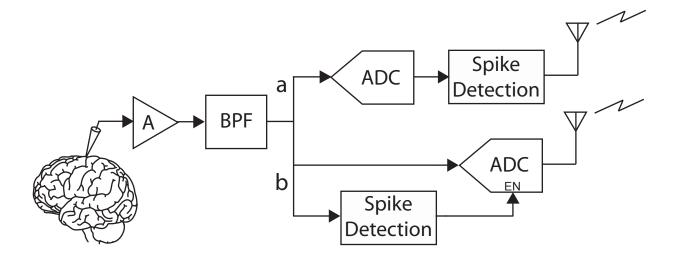

| 3.15 | Block diagram for (a) digital spike detection and (b) analog spike detection.                         | 51 |

|------|-------------------------------------------------------------------------------------------------------|----|

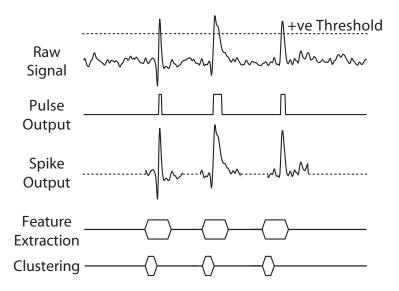

| 3.16 | Spike detector outputs                                                                                | 52 |

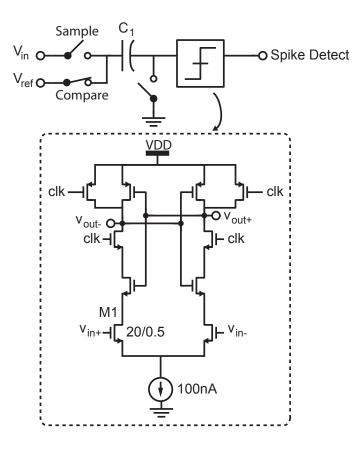

| 3.17 | Schematic for a low-power dynamic comparator                                                          | 54 |

| 3.18 | Implementation of the Non-Linear Energy Operator algorithm in the discrete-                           |    |

|      | time analog domain.                                                                                   | 55 |

| 3.19 | Implementation of analog memory for storing the signal before a spike has                             |    |

|      | been detected                                                                                         | 56 |

| 3.20 | Variation in power dissipation of analog NEO spike detection                                          | 59 |

| 3.21 | Power estimates obtained from Synopsys for NEO, Spike Output mode. The                                |    |

|      | total power $(P_{\text{total}})$ is divided into switching power $(P_{\text{switching}})$ and leakage |    |

|      | power $(P_{\text{leakage}})$                                                                          | 61 |

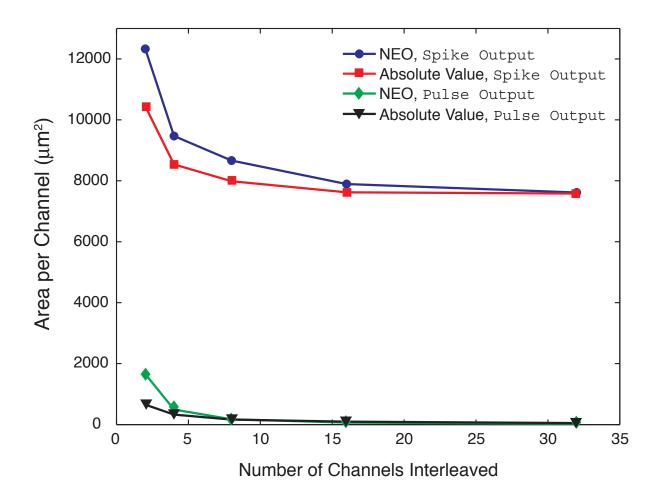

| 3.22 | Area estimates for NEO, Spike Output mode, obtained from Synopsys as a                                |    |

|      | function of the number of channels interleaved                                                        | 62 |

| 3.23 | Detector power and area per channel                                                                   | 64 |

| 4.1  | Schematic diagram of a wireless biosignal telemetry system, showing options                           |    |

|      | for different output signal modes. Digital detection is shown                                         | 70 |

| 4.2  | System configurations                                                                                 | 76 |

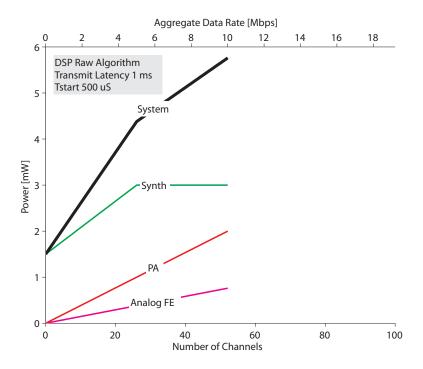

| 4.3  | Raw streaming                                                                                         | 78 |

| 4.4  | DSP-detection mode                                                                                    | 79 |

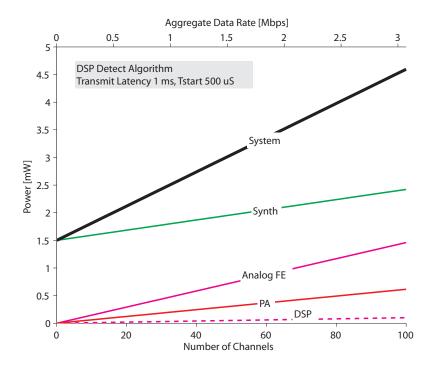

| 4.5  | Power dissipation of feature extraction and clustering modes                                          | 80 |

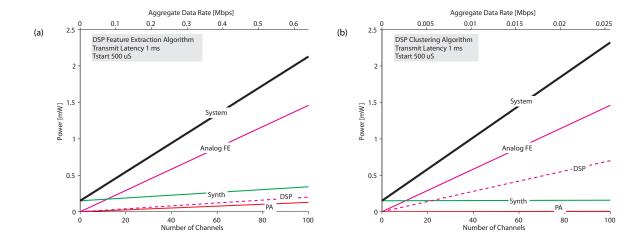

| 4.6  | Performance of open-loop LC oscillator                                                                | 81 |

| 4.7  | Comparison to existing wireless neural recording systems                                              | 83 |

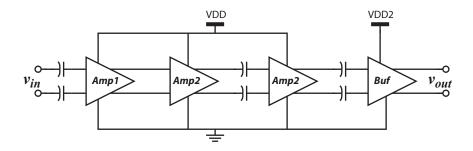

| 5.1  | Architecture of cascaded amplifiers                                                                   | 85 |

| 5.2  | Stages 1–3 of the designed amplifier                                                  | 85  |

|------|---------------------------------------------------------------------------------------|-----|

| 5.3  | Stages 4 of the designed amplifier                                                    | 86  |

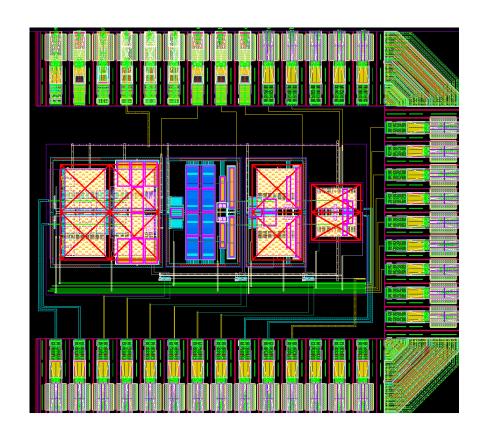

| 5.4  | Layout of a cascaded open-loop amplifier topology. Total area is 0.2 $\mathrm{mm}^2.$ | 87  |

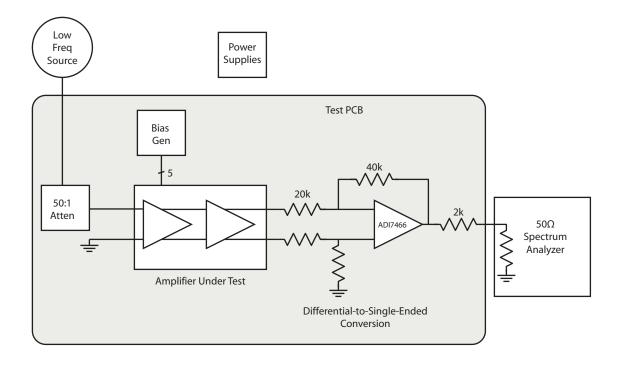

| 5.5  | Schematic diagram of the printed circuit board and test equipment                     | 88  |

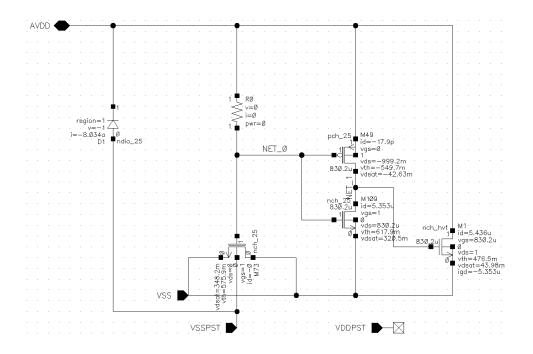

| 5.6  | Supply leakage current through M1 of approximately 5.5 $\mu A.$                       | 89  |

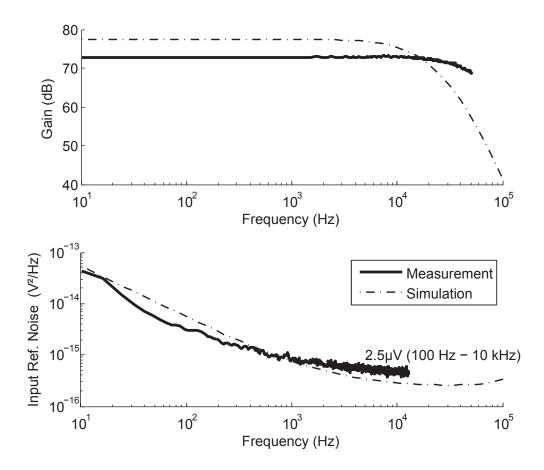

| 5.7  | Measured gain and noise compared to simulation, for 17 $\mu\mathrm{A}$ supply current | 90  |

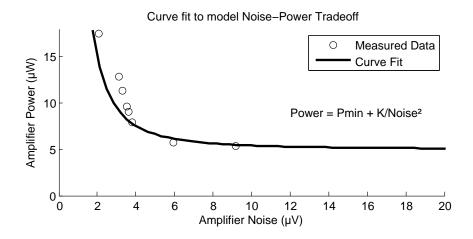

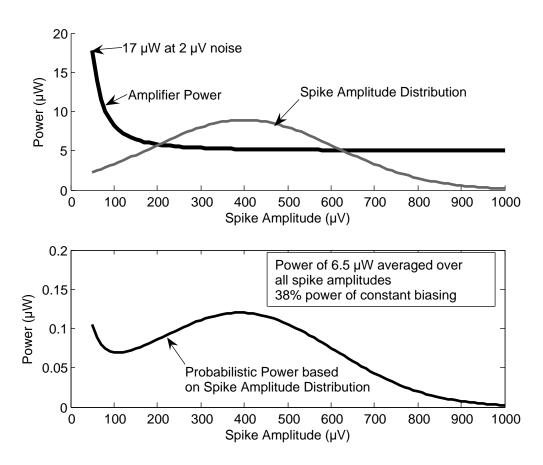

| 5.8  | Noise versus amplifier power                                                          | 91  |

| 5.9  | Estimated power saving for optimal bias currents based on spike amplitude             | 92  |

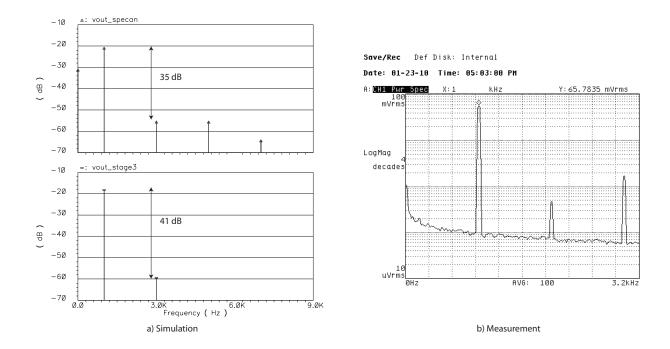

| 5.10 | Third harmonic distortion comparison between simulation and measurement.              | 93  |

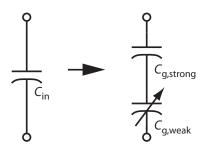

| A.1  | Interpolation of Strong and Weak Inversion capacitances                               | 99  |

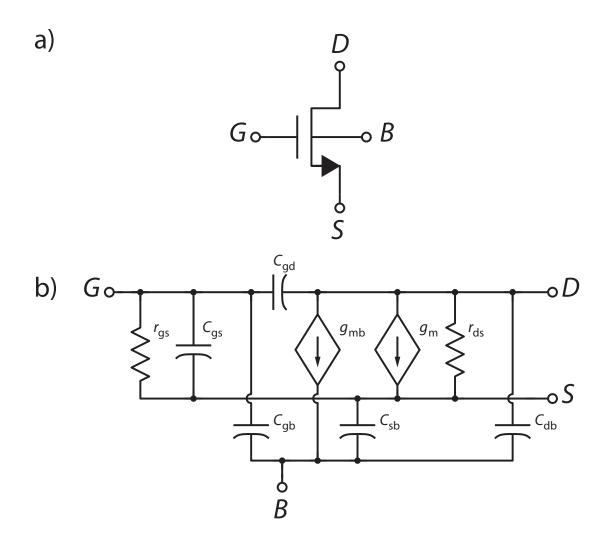

| A.2  | Small-Signal model of a MOSFET                                                        | 100 |

## LIST OF TABLES

| 2.1 | Summary of existing wireless neural recording systems   | 19  |

|-----|---------------------------------------------------------|-----|

| 3.1 | Noise Contributions for 5 dB $SNR$                      | 29  |

| 3.2 | Spike Amplifier Specifications                          | 31  |

| 3.3 | DSP Power for Different Levels of Processing            | 66  |

| 3.4 | Simple RF Link Budget                                   | 69  |

| 4.1 | Data rates for different modes                          | 75  |

|     | Power for each block                                    |     |

|     |                                                         |     |

| 5.1 | Performance comparison with other amplifiers            | 94  |

| A.1 | Constants and Variables used to characterize Amplifiers | 101 |

#### ACKNOWLEDGMENTS

I would like to thank Professor Jack Judy for advising me over the course of the Ph.D. program. His thorough criticism and word-smithing of my work has been beneficial, and has helped me to communicate my ideas more effectively.

I would also like to thank Professors Sudhakar Pamarti, Tad Blair, and Dejan Marković for serving on my committee, and for their valuable comments in refining this manuscript. In particular, I give many thanks to Professor Marković for virtually serving as my co-advisor while Professor Judy was on sabbatical, and supporting joint chip tapeout for this work.

I also thank my friends at UCLA. Shahin Farschi, Rocco Tam, Sarah Gibson, Victoria Wang, Mansour Rachid, Cathal McCarthy and David Murphy are just a few of the people that I've been fortunate to meet. I am grateful for the many technical discussions that take place in Professor Judy's group, particularly with June Isobe, Frank Zee, and Jere Harrison. I am indebted to Beverley Eyre for explaining many LATEX techniques.

I greatly appreciate the continuous help and support from Kyle Jung, Deeona Columbia, Martha Contreras, Alice Brook and Ilhee Choi. They were always very helpful with numerous urgent requests.

Lastly, I thank my wife, Karen, for her endless love, support and proofreading. I could not have done this without her.

# VITA

| 1998      | B.E., Electrical and Electronic (Honours I),              |

|-----------|-----------------------------------------------------------|

|           | The University of Queensland                              |

| 1999      | Graduate Student Researcher, The University of Queensland |

| 2000-2003 | IC Design Engineer, Radiata/Cisco Systems, Sydney         |

| 2003-2010 | Graduate Student Researcher,                              |

|           | University of California at Los Angeles                   |

| 2007      | IC Design Engineer, Analog Devices, Wilmington, MA        |

| 2008      | M.Sc., Electrical Engineering,                            |

|           | University of California at Los Angeles                   |

| 2010-2011 | IC Design Engineer, MaxLinear, Carlsbad, CA               |

| 2012-     | IC Design Engineer, Broadcom, San Diego, CA               |

### **PUBLICATIONS**

- R. Chandler, S. Gibson, V. Karkare, S. Farshchi, D. Markovic, and J. W. Judy, "A System-Level View of Optimizing High-Channel-Count Wireless Biosignal Telemetry," in Proc. Int. IEEE Engineering in Medicine and Biology Conf., Sept. 2009.

- S. Gibson, R. Chandler, V. Karkare, D. Markovic, and J. W. Judy, "An Efficiency Comparison of Analog and Digital Spike Detection," in Proc. 4th Int. IEEE EMBS Conf. on Neural Engineering, May 2009.

- D. Huber, **R. Chandler**, and A. A. Abidi, "A 10b 160MS/s 84mW 1V Subranging ADC in 90nm CMOS," in IEEE Solid-State Circuits Conference, 2007.

## CHAPTER 1

## Introduction

## 1.1 Background

Neuroscience research is required for several reasons. This work, in particular, has been influenced by the desire for (a) treatments for neurological disorders requiring measurement and monitoring of abnormal behavior of the brain, (b) developing models for the normal function of the brain, so that synthetic circuits can be devised to restore function to damaged regions, and (c) develop brain-computer interfaces (examples are implementing brain-controlled prosthetic limbs for amputees, more intuitive, natural, machine-control interfaces, and restoring motor control to stroke victims).

All the above examples rely on monitoring brain signals. These signals can be monitored in a variety of ways, from electroencephalography (EEG), which requires electrodes placed on the scalp, to micro-electrode implantation in the brain. Depending on the technique employed, the data gathered will range from the ensemble response of millions of neurons (EEG), down to the behavior of a handful of individual neurons per implanted electrodes. EEG-based monitoring is suitable for systems that can be trained to detect high-level behavior such as blinking or the intention to move in a certain direction. On the other hand, it is theorized that signals recorded from implanted electrodes can be used to obtain more precise information. One study of the combined network interaction from hundreds of neurons is led by Blair et. al.. The specific aims of Blair's work are to (a) measure how position and velocity are encoded in the rat brain, within specialized neuronal networks known as

grid- and place-cells, and (b) develop mathematical models for this behavior. Furthermore, long-term goals include applying their results, based on the mapping of physical quantities such as position and velocity, to more abstract concepts such as how one navigates through a lifetime of memories.

As many preclinical trials use small-animals such as mice and rats, the size and power of the system must be minimized. A small, low-power system facilitates a broad range of applications (from first-order preclinical small-animal trials to primate experiments). All applications require similar processing, but differ greatly in their power, size, and weight constraints. Therefore, it behooves us to develop the system with the tightest constraints in mind. A platform that is flexible enough to be used in many neuroscience applications, such as the one proposed in this dissertation, would encourage the sharing of collective experiences, and assist in developing best practices for neural recording, while also allowing neuroscientists to focus on the experiment itself.

Before describing the requirements of the proposed system, a few applications will be presented to set the stage.

## 1.2 Applications

Successfully developing the proposed technology will make it possible to routinely perform wireless high-channel-count and high-bandwidth neural recording in freely moving test subjects. Such a capability has important clinical (e.g., epileptic seizure mapping) and preclinical (e.g., brain-computer-interface development and recording within enriched environments) applications.

#### 1.2.1 Clinical Application: Epileptic-Seizure Mapping

Epilepsy and its development in the intact brain are poorly understood. The gross features of the disease are known, but the nuances of its workings, its development, and its natural triggers remain largely obscure. In broad strokes, an epileptic seizure occurs when neurons in a small area of the brain begin to fire in synchrony. This firing overwhelms other necessary brain functions and results in a complete shutdown of the central nervous system and a loss of consciousness in extreme cases. Epilepsy affects millions in the United States alone — according to some estimates as much as 1 to 2% of the population [1]. Epileptic insults range in their effects from the facial twitching and momentary blankness of expression typical of petit mal seizures, to the emotional outbursts, hallucinations, and flashbacks of temporal-lobe seizures, to the loss of consciousness and violent convulsions seen in grand mal seizures. Causes of epilepsy include genetics, head trauma, and various brain disorders. Epilepsy is normally treated with medications designed to inhibit neuronal activity by increasing the effectiveness of the inhibitory neurotransmitters. There is also on-going research into using electrical stimulation to manage the disease.

Scientifically, one of the most important questions to answer relates to the process by which the brain develops the capacity for epileptic insults, before any overt signs of epilepsy are present. Clinically, the goal is to localize the source of drug-resistant seizure activity to enable surgical intervention. When such localization cannot be performed with non-invasive imaging technologies, direct brain electrophysiology may be used. Presently, patients are admitted to the epilepsy ward, surgery is performed to attach a grid of many electrodes to the cortex or to implant electrodes into the brain, and continuous recordings are performed in the clinic until enough seizure activity is recorded to enable accurate source localization. Unfortunately, a well-known fact is that seizure frequency during such clinical experiments is far less than normal. As a result, patients often must stay in the hospital for up to two weeks for enough data to be obtained [1]. Such a long hospital stay with many (~100) transcranial

and percutaneous wires is a great burden to the patient and increases their health risks. A hypothesis for the cause of reduced seizure activity observed in the clinical setting is the fact that the physical activity and behavior of patients is greatly reduced and altered due to being tethered to the bed. In addition, the wired nature of existing systems means that recordings are not obtained when the patient moves away from the bed (e.g., moving between rooms, etc.) and it is possible that the already infrequent seizure activity may be missed. A wireless system capable of recording from ~100 channels may provide substantial benefits to the patient. Although typically the system may only need to record signals with a sampling rate of <1000 Hz, a system capable of sampling at higher rates (~20 kHz) would enable the same system to simultaneously record from implanted micro-electrodes. Furthermore, the ability of the mobile wireless system to perform local signal processing could enable the early detection of seizure onset, which would also have clinical benefits (i.e., prepare the patient and care provider for the seizure so that the data obtained can be of the highest value).

#### 1.2.2 Preclinical Application: Brain-Computer Interfaces

The development of brain-computer interfaces (BCI) is an active area of research based on multi-channel EEG [2] or single-unit electrophysiological recordings [3–9]. A goal of BCI research is to restore movement to those who have lost a limb, or link a computer interface to the brains of those suffering from cerebral palsy or Lou Gehrigs disease. By recording the electrical activity from the brain, a computer can be programmed to deduce the intention of movement and control a robotic device or prosthetic. Although the early work performed with rodent models used a fair number of electrodes (~16), there has been a drive towards using even larger numbers. For example, there has been success with BCI systems operating with ~100 channels non-invasively with humans, and invasively with a higher-order preclinical animal model (i.e., primate) [9]. Although a wired system is acceptable for such experiments that are typically performed acutely and in a configuration that is physically constraining, there are experimental motivations for a wireless neural-recording system. One motivation is

to study the long-term performance of invasive neural-electronic interfaces, which are known to degrade with time sometimes slowly (over months) and sometimes quickly (sub-second) [10]. Another motivation is to perform synchronous and asynchronous BCI experiments in mobile test subjects, initially in animals [5] [6] but then eventually in humans. With non-invasive BCI recording systems, a low sampling rate (<1000 Hz) is sufficient to capture EEG activity and the level of signal processing varies.

With invasive BCI recording systems, a high sampling rate (~20 kHz) is needed to capture spike activity, but there is also interest in recording local field potentials with the same system. Although some researchers may configure systems that record spike activity to simply stream the full waveform to the receiver, others may prefer the mobile system to perform substantial signal processing as well (e.g., event/spike detection and spike sorting). The ability of our proposed system to be reconfigured through software to employ a wide range of sampling rates, resolutions, and user-defined signal-processing algorithms, will make it extremely useful for the diverse BCI community, and not just for those using smaller animal models.

# 1.2.3 Preclinical Application: Recording of Brain Activity in Enriched Environments

The influence of an enriched environment on brain development, plasticity, and recovery is known to be critical but is poorly understood. The environment in which the animal lives and is studied, from the moment it is born, plays a critical role in initial and ongoing brain development.

Several paradigms have been used to demonstrate the effects of environment on lowerorder animal models (e.g., rodents). The best characterizations of these differences have been reported in maternal behaviors [11], light-dark rearing [12], exercise [13] [14], diet [13–16], and environmental complexity [17–20] all of which induce lasting changes in brain anatomy and/or function. One of the oldest models of experience-dependent plasticity is housing in an enriched environment. Bennett et al. were the first to report that rearing rats in complex housing conditions resulted in changes in brain weight and cortical thickness [19], as well as in behavior. In general, enriched-environment rearing provides frequent novel stimuli to test subjects in the form of toys, exercise devices, spatial arrangements, handling, social interactions, and sometimes even smells and sounds. When rats reared in an enriched environment are compared to those reared in standard laboratory conditions, or to those reared in "impoverished" conditions, the enriched-environment animals consistently demonstrate changes in neuroanatomy (e.g., increases in brain weight [19][21], cortical thickness [22], dendritic arbors [23], glial number [20], brain capillaries [24][25], and even hippocampal neurogenesis [26]), changes in behavior (e.g., superior cognitive performance on tasks of spatial learning, including Morris water maze [26, 27] and the radial arm maze [28]), and changes in pathological processes with high clinical relevance, including the recovery from a stroke or head trauma, to epilepsy, to the effects of pre-natal alcohol exposure.

It has long been contended that standard laboratory-animal-housing conditions are actually impoverished, when compared to 'wild type' surroundings [29]. In fact, it may be argued that comparison of experimental effects in standard-housed animals provides only part of the picture, particularly when attempting to extrapolate such results to the human condition. Important conclusions derived from such research demonstrate that differences in brain signaling as a function of the animal environment are sufficient to call into question conclusions made from research that is not done in an enriched environment [30].

An enriched environment is one that consists not only of a greater number of objects (e.g., wheels, tunnels, rocks, and toys), but also of an enriched social setting with additional animals. The optimal environment from a neuroscientific point of view is not the one with the most stimuli or animals, but the one that most resembles the natural environment of an animal in the wild. Overcrowding degrades neural development in much the same manner as does a lack of social interaction. Neurons in brain slices prepared from animals exposed to

an enriched environment show a dramatic increase in cell proliferation, dendritic branching, and expression of the genes that lead to receptor formation [30]. In most societies, it is fair to consider the normal human condition to be one of considerable 'enrichment', with complex social interactions, educational programs, language, art, and recreational opportunities. In the laboratory, it is likely that subtle but important impairment of "higher-level" functions will be missed by experimental paradigms that reduce animal behavior to the lowest common denominator.

A wireless neural-recording system that could be used to perform preclinical experiments with lower-order animals models as small as a rat, could be used to ascertain the importance of an enriched environment on conditions of clinical relevance (e.g., recovery from a stroke or head trauma, epilepsy, the effects of pre-natal alcohol exposure). Such a wireless neural-recording system may not initially need to record from a high channel count, but the availability of micromachined microprobe arrays makes it increasingly common to perform high-channel count experiments even in rats. Thus, the expandable performance of our proposed telemetry system is likely to be highly valuable. In addition, the frequency range of neural signals of interest in such experiments varies from <100 Hz (e.g., theta waves) to ~6 kHz (e.g., single units). The ability of the same miniature neural-recording system to be reconfigured in terms of channel count, resolution, sampling rate, and extent of signal processing would enable a greater range of experiments to be performed in an enriched environment.

## 1.3 System Description

Advances in miniaturization of microelectrode arrays have made it possible to chronically implant hundreds (or even thousands) of extracellular electrode tips into the nervous tissue of animal or human subjects in order to monitor the activity of dozens or hundreds of individual neurons in real time. In principle, it should be possible to gather data from these minia-

turized electrode arrays while unrestrained subjects move freely about their environment, thus capturing neural activity during normal behaviors. But in practice, this potential for high-density neural monitoring in unrestrained subjects has yet to be fully realized, because with hundreds or thousands of electrode channels implanted in a single subject, it becomes necessary to transmit very large volumes of real-time data from the brain to a machine that can process and store the data. A reliable high-bandwidth data-transmission bus is needed for relaying all of this data from brain to machine. In many cases, exquisitely miniaturized electrodes must still be connected to recording and monitoring equipment by large, bulky cables that restrict the ability of subjects to move and behave freely. Unavailability of interface circuitry that can multiplex hundreds of channels of data in a small form with low power have prevented miniaturized electrode arrays from being used to their full potential in applications such as brain-machine-interface devices for controlling robotic prosthetics in movement-disabled patients, and in laboratory research investigating how populations of neurons encode information and regulate behavior in freely behaving animals.

Many existing systems use a fully parallel data bus: a multiconductor cable in which each channel of data is relayed from brain to machine via a separate wire (Figure 1.1(left)). However, there are several major drawbacks to this solution. First, with hundreds or thousands of channels, the multiconductor cable can become very large and bulky, especially for small experimental animals like mice and rats. Second, the connectors that join these cables to the implanted microelectrode array are a very vulnerable point in the circuit, often consisting of hundreds of very small and fragile connector pins that can be easily broken during the process of connecting and disconnecting the cable to the subject (especially animal subjects, such as a squirming rat). If even a single connector pin is broken, a repair job costing hundreds of dollars and several man hours becomes necessary. Third, the connector cable tethers the subject to the data acquisition equipment, thereby restricting the subject's ability to move around and behave freely without twisting or breaking the cable. This problem can be partially ameliorated by using a rotational commutator, but such commutators

Figure 1.1: (left) Connector and cable detail. (right) Ceiling mounted commutator and video cameras, attached to headstage amplifiers via 3 m cable.

become very large and expensive for cables consisting of hundreds of conductors (Figure 1.1 (right)).

To solve these problems, we will develop a high-bandwidth, miniaturized wireless data transmission system for relaying large volumes of electrophysiological data from implanted electrode arrays to a data acquisition system. In collaboration with experienced users of existing technology, we have identified the major technological hurdles that must be overcome before such a wireless neural recording system can become truly practical and useful. Our system will solve these problems by incorporating a miniaturized, wearable data-acquisition computer system that can be remotely programmed by the experimenter at any time. We are confident that this system will make it possible, for the first time, to achieve ultra-high-density electrophysiological monitoring (hundreds or thousands of channels) of single-unit electrodes in fully unrestrained human and animal subjects.

The hardware to perform the neuroscience research described above has the following minimum requirements: (a) high-fidelity, simultaneous recording from hundreds of electrodes, (b) relaying the recorded signals to a digital-signal processor to perform experiment-dependent operations, such as detection, alignment, feature extraction, and classification, and (c) transferring the neural information to an archive server, or generating a electrical feedback signal.

To make the system implementable in practice, the following requirements are also introduced:

The system must be low power, to avoid tissue damage from heating, and to allow a low-weight battery for a given operational lifetime. Specifically, the total power dissipation must be less than 80 mW/cm<sup>2</sup>. For a 100 channel, 1 cm<sup>2</sup> integrated circuit (IC), this upper-power limit corresponds to a power dissipation of less than 800  $\mu$ W per channel. For a system weight of 10 g, assuming 50% is due to the battery with a energy density of 120 W·hr/kg (typical for lithium ion batteries), and a target experiment duration of 1 hour, the maximum power per channel is 120 W·hr/kg × 5 g / 100 channels, or 6  $\mu$ W. In this example, we are limited by the power source, rather than limits due to potential tissue damage. Providing power over an inductive link is unsuitable because of its short range (~10 cm).

While it is arguable whether the system *must* be wireless, the key benefit of a wireless approach is the elimination of the wiring harness and the connectors. This harness and connectors are problematic because the system must be physically small, the wiring harness consists of low-gauge wire, and miniature connectors are fragile. The main problems that arise are (a) damaging the connector after numerous reconnections and (b) the weight and limited movement due to the wiring itself. A small, squirming rat only adds to the likelihood of a damaged wired link. As expensive, custom circuitry and hand-made housings are presently used in the experiment, time-consuming repairs are undertaken instead of replacement. As surgery to implant electrodes is also time-consuming and expensive, it is imperative to minimize damaging the hardware attached to the implants. The heavy cable

must also be towed by the rat, which impedes the extent of their mobility, and eliminates the possibility for experiments using *enriched* environments including tunnels and complex mazes. A rotational commutator improves mobility, but ideally, the rat would be untethered.

## 1.4 Proposed Solution

This work aims to deliver a device that is small, yet capable of wirelessly transmitting as much information as possible with a given battery. Some investigators seek real-time, raw neural signals captured with high-fidelity (i.e., at least 8-bit resolution and 30 kS/s sampling rates), while others are only interested in the spike waveforms and/or events. The ability to transmit over distances up to 10 m, operate for up to 24 hrs, and yet weigh less than 10 g, would facilitate unencumbered movement for the subject, longer experimental sessions, and the ability to use the system with small animals, respectively. A system that can achieve these goals has the potential of broad appeal to the neuro-scientific community.

## 1.5 Organization

The remainder of the thesis is organized as follows. Chapter 2 summarizes previously published systems. In order to facilitate system level analysis, each building block is analyzed in Chapter 3. Next with the block estimates, the system level performance can be calculated for different configurations, and the optimal configuration determined. One of the key blocks is the analog front-end amplifiers, and the implementation of these amplifiers is described in Chapter 5. Finally, conclusions and future work are summarized in Chapter 6.

## 1.6 Acknowledgments

Work presented in Chapters 3 and 4 includes contributions from Sarah Gibson and Vaibhav Karkare for the algorithm and digital system design, which have previously been published as conference papers [31,32]. We also thank the National Science Foundation for financial contributions (Grant No. DBI-0456125 and EECS-0824275).

## CHAPTER 2

### Literature Review

#### 2.1 Introduction

Each wireless biosignal recording system is composed of several key parts: electrodes, amplifiers, detection and signal processing, and a transmitter. A complete system is configured by using a certain approach for each of the blocks, and partitioning the system into a front-end and a back-end. The front-end performs basic signal processing, and the back-end performs additional processing and archival of data. The resulting system partition leads to a certain level of performance in terms of power, noise, range, area, and datarate. Signal fidelity (e.g., distortion of the amplifiers and spike detection accuracy) is also important, but not always reported, and so it is not included here. Integrated circuits are low in weight, which indicates that the total system weight is mostly due to the battery, antennae and printed circuit boards. The required battery weight is related to power dissipation and experiment duration, so this constraint is implicitly captured. In this Chapter, we will review some existing systems in terms of these performance metrics. In Chapter 3, we will examine these performance trade-offs, e.g. power versus noise, in more detail.

Existing wireless neural-recording systems range from fully integrated analog transmitters [33],[34], to analog transmitters with threshold-based spike detection [35], [36], [37] to digital application-specific integrated circuits (ASICs) [38], to microcontroller-based embedded systems [39], to commercial-off-the-shelf (COTS) PC-based systems [40]. Fully integrated transmitters and ASICs benefit from being very small (several mm<sup>2</sup>) and low power (sev-

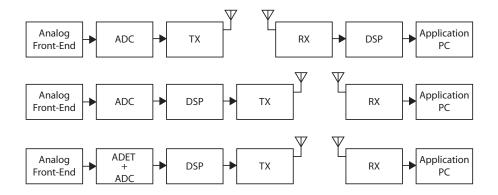

Figure 2.1: Different system configurations for wireless neural recording: (a) analog recording (b) spike detection (c) digital signal processing.

eral mWs), thus enabling them to be implanted with the electrode and inductively powered (when an external power source can be worn).

In the interest of increasing channel count and sampling rate while maintaining reasonable battery life, some groups have demonstrated solutions with some on-board signal-processing capability, such as thresholding as demonstrated in [35] and [36]. Unfortunately, these threshold-based systems typically cannot differentiate spikes from artifacts, and require circuit redesign to modify the spike-detection algorithms. The limited adoption of existing wireless neural recoding systems by the neuroscientific community may be an indicator that users could benefit from a greater degree of flexibility in terms of methods for spike detection. Chae has published a system in [41] that also includes feature extraction and clustering, and a high datarate transmitter. Such a system, with the capability to provide spike event data along with many channels of raw data, is a step closer to providing the needed flexibility.

## 2.2 Classification of Recording Systems

Figure 2.1 shows systems that use (a) analog recording, (b) spike detection, and (c) using a digital-signal processor (DSP) for feature extraction and/or clustering. Each system is comprised of two parts. The first part shown is the frontend, which includes the blocks from the analog frontend (AFE) to the transmitter (TX). The frontend takes inputs from several electrodes and applies the appropriate gain and frequency-band selection, and combines the multiple electrode signals into a single stream. The combined stream is transmitted wire-lessly to the backend receiver. As the frontend is intended to be battery powered and/or implanted, it must be low power and have a small size, and any increase in frontend complexity must be balanced against these constraints. One of the key goals of this dissertation is to determine the optimal frontend complexity and explore the performance tradeoffs for different applications. The backend, which includes the blocks from the receiver (RX) to the application PC, does not have these constraints, so the design of the backend is relatively trivial compared to the frontend. The backend receiver can use off-the-shelf components, which suggests that the frontend transmitter should be able to interface standard components.

For the analog recording case (Fig. 2.1a), time-division multiplexing is used to interleave multiple electrode channels. Analog recording system examples have been published by Mohseni [33] and TBSI [42]. The basic architecture is shown in Figure 2.1a. The advantage of this type of system is simplicity. The amplifier increases the signal level from a few millivolts to approximately 1 V to drive an FM modulator. Because the output is an analog modulation, any noise and interference that is incident on the receiver can reduce the signal quality. Since there is no signal processing, it is not possible to detect spikes or other events in the frontend – signal processing occurs after the backend receiver. If a feedback signal is required (e.g. to control a prosthetic limb), it must to calculated in the backend, and transmitted back to the frontend. If the system included signal processing in the front-end,

it is feasible that the feedback signal could be generated locally. For this reason, analog recording has limited applications for applications that also include stimulation.

A spike detection system (Fig. 2.1b) is comprised of the following blocks. The amplifier and bandpass filter processes the signal to remove the energy outside the wanted band and increases the signal amplitude to be larger than the noise floor of subsequent blocks. A simple analog comparator then compares the instantaneous amplitude to a predetermined threshold and generates a pulse if the amplitude is higher. The output is now a 1-bit sequence, and this digital data can drive an FSK modulator instead of an FM modulator. Because the output is low resolution (1 bit), the transmitter complexity is low but the waveform has been reduced to a 1-bit representation. The data from multiple spike detectors are interleaved and synchronization markers are added before being wirelessly transmitted to the backend. Since the waveform is reduced to a single bit, no analog-to-digital converter (ADC) is required for the spike detection system. Examples have been published by Sodagar [43] and Harrison [35], which use a simple form of spike detection. Their spike detection operates by comparing instantaneous amplitude with a predetermined threshold. The threshold is set by measuring the average amplitude over an extended time period, which is a measure of the system noise floor, and setting the threshold to be larger than this noise floor. The threshold is typically programmable, and can be set by circuitry operating in the background [44], or by user intervention. How accurately can an actual spike event can be detected in the presence of noise? Analysis of this topic has been performed by Gibson [45], and it was shown that simple thresholding has inferior spike detection performance in high background noise environments. In turn, this leads to higher power dissipation of the frontend analog amplifiers to keep their own noise low. For this discussion, the key disadvantage to note is that spike detection should be as accurate as possible, and not use an inferior algorithm, in order to encourage widespread adoption of the system in neuro-scientific community. Incorporating a range of spike detection algorithms is one solution, as is including the ability to keep more raw data. Both Harrison and Sodagar include the capability to transmit the complete digitized

waveform of a user-selectable channel (with 8- or 12-bit resolution), in addition to 1-bit spike detection data. Adding the high-resolution waveform data to the thresholded outputs increases the data-rate that the transmitter must support at the cost of performance, but is a good compromise between only having 1-bit data for a high number of channels, or a small number of channels with high resolution. Furthermore, the single high-resolution channel can be used during initial setup and training to observe which electrodes have useful data and to set the threshold of the comparators. Spike detection relies on the fact that it is sufficient to record the time of a spike event, and discard the spike waveform details as unimportant. However, false alarms or missed detections will occur; this behavior needs to be acceptable to the experimenter, and the complexity (i.e. power and area) of the detector must be balanced with spike detection accuracy. If one compares analog recording and spike detection, spike detection allows a reduction in datarate required of the wireless transmitter or a higher number of channels to be transmitted. For these reasons, spike detection is a useful technique in reducing the power dissipation of the system. On the other hand, analog recording keeps the complete spike waveform and the background noise (which can be required for certain experiments) but it is more difficult to create a system with a high channel-count.

Finally, Fig. 2.1c shows a system that includes some form of digital-signal processing to process the raw data to obtain a reduction in the amount of data sent to the transmitter. This reduction in datarate is required for high-channel-count systems to keep the transmitter feasible within a limited power budget. Spike detection is performed first and then additional processing is performed. Feature extraction measures the key features of a spike waveform such as peak, slope, and duration. Clustering is an additional step that, based on certain waveform metrics, maps a spike waveform to a certain event or a single neuron. Feature extraction and clustering are computationally expensive, and need high resolution digitization to be accurate. Typically 10 to 14 bit resolution is used depending on the application. Feature extraction and clustering can be considered as a form of application-specific lossy

compression and they reduce the data-rate required of the transmitter; other compression general purpose techniques could be used but would be less efficient. For a high-channel-count wireless system, if the data is not processed on chip, the outgoing data-rate can be high. In the system published by Chae [41], the data-rate per channel is 180 kbps, or 18 Mbps for 100 channels. Generally, transmitters that have power dissipation limited to a few tens of milliwatts can achieve up to 10 Mbps in indoor environment. The ultra-wideband (UWB) transmitter implemented in [41] claims a peak data-rate of 90 Mbps, which is enough for 500 channels of raw data, over a short transmit range, while consuming 6 mW from the power supply.

There are three interesting claims in Chae's publication: (a) with optimization and lowpower design techniques it is possible to produce a system with a high-channel count without resorting to compression and keeping the total system power around 6 mW, (b) it is possible to design a high data-rate transmitter that has a low power of 1.6 mW and a capacity of 90 Mbps to support a high-channel count, and (c) feature extraction in the frontend can also have a low power of 1.5 mW for 100 channels. Overall, it shows that a lowpower neural recording system is feasible based on (a) and (c). Regarding (b) however, the implementation of the wireless link and transmitter may be difficult. My own opinion is that the UWB transmitter performance may be sensitive in realistic settings. In particular, our goal is to have a range of approximately 10 m to allow untethered recording of freelymoving subjects. It is unclear if the UWB link is robust enough to supply high data-rate that is claimed at longer range and with other potential wireless interference nearby. Since the Federal Communication Commission dictates that UWB transmit power levels should be low, there may be issues with achievable link quality. Furthermore, widespread adoption of UWB technology in general consumer markets has been limited, with other non-UWB radio products satisfying the need for high datarate wireless communications. One possible reason for the lack of UWB adoption is that it may be difficult achieve high data-rates in real-world situations. Furthermore, obtaining off-the-shelf components for a UWB receiver

Table 2.1: Summary of existing wireless neural recording systems.

| Author                  | TBSI   | Mohseni | Sodagar   | Harrison  | Chae | Walker |

|-------------------------|--------|---------|-----------|-----------|------|--------|

| Year                    | 2007   | 2005    | 2007      | 2007      | 2008 | 2011   |

| Ref.                    | [42]   | [33]    | [43]      | [35]      | [41] | [46]   |

| Type                    | Analog | Analog  | Spike/DSP | Spike/DSP | DSP  | Analog |

| Channels                | 62     | 4       | 64        | 100       | 128  | 96     |

| Power (mW)              | 30.8   | 2.2     | 14.4      | 13.8      | 6.0  | 6.5    |

| Area (mm <sup>2</sup> ) | 25     | 4.8     | 19        | 28        | 63   | 25     |

| Noise $(\mu W)$         | 10     | 7.1     | 8         | 5.1       | 4.9  | 2.2    |

| Bandwidth (kHz)         | 3      | 10      | 10        | 5         | 20   | 10     |

| Datarate (Mbps)         | 4      | 4       | 0.50      | 0.33      | 90   | 30     |

| Transmitter             | FM     | FM      | FSK       | FSK       | UWB  | N/A    |

| Range (m)               | 3      | 0.5     | 0.02      | 0.13      | 1    | N/A    |

may be more expensive than non-UWB options. Based on these concerns, I feel that it may still be necessary to use some form of data compression to keep the wireless link more robust and power dissipation reasonable.

Although the system does not provide wireless capability, Walker [46] has recently demonstrated a 96-channel system with a power dissipation of 6.5 mW while providing 10-bit raw data for all channels over wired serial connection. The design achieved low-power and noise by optimized analog amplifiers, and its techniques are applicable to all neural signal acquisition systems.

A summary of published solutions is shown in Tab. 2.1. In the next section, the performance of the each of published systems will be summarized, and compared to our goals for a low-power wireless neural recording system.

# 2.3 Summary

Key examples of wireless telemetry systems have been described in this Chapter. For this summary, we will examine several performance metrics: power, area, noise, and range. For power and area, we will calculate the approximate per-channel value by dividing by the number of channels. This is not the most accurate model as certain shared blocks such as reference voltage generators and local oscillators may not need to be scaled per channel. Noise is a measure of the minimum signal that can be detected, and is primarily set by the analog front end, i.e. power and area would increase if the noise is lowered. Noise often scales inversely with the square of power and area. We will consider noise in a qualitative manner in this section, and defer detailed analysis for Chapter 3. Range is also very application specific, as some systems only require a very short range if an intermediate relay stage is added between the frontend and backend. Other systems, on the other hand, were designed from the outset to be capable of longer range. Nonetheless, we can still obtain a qualitative assessment for what has been achieved to date. Our discussion focuses on scaling these systems to a large number of channels, hence we need to estimate the performance for a single channel. A summary of performance is given in the following list:

• Power: The analog recording systems in Table 2.1 use approximately 0.5 to 1 mW of power per channel. Mohseni uses approximately 140  $\mu$ W per channel, plus 1.5 mW for the frequency modulator. Sodagar uses 225  $\mu$ W per channel for the spike detection system. The FSK modulator in Harrison's system uses 6.9 mW, plus 69  $\mu$ W per channel. The lowest power system is by Chae and dissipates 1.6 mW in the transmitter and 34  $\mu$ W per channel. If we consider the per-channel power and examine Chae's system, we find that circuit techniques to disable blocks when their output is not sampled is used to reduce overall power; the effect switching in the signal path is not understood however and we feel that further analysis is required. Secondly, the UWB transmitter is much lower power per bit transmitted. Conservative estimates

would place the transmitter power between these extremes, and we expect around 5 mW for our transmitter. Our expected per-channel power, i.e. the amplifier and signal processing, is around 50  $\mu$ W. Even in systems that use extensive digital signal processing, most of the power is used by the analog frontend and transmitter. For this reason, we will focus on reducing the power of these blocks and it may be advantageous to use additional DSP to reduce the power required of the amplifiers and transmitter.

- Area: The area-per-channel ranges from 1.2 mm² to 0.29 mm², and process technologies range from 1.5 μm to 90nm CMOS. The largest area-per-channel is from Mohseni with its unoptimized area as shown in the published prototype, is excluded from this area discussion. The smallest is by Harrison at 0.29 mm² despite it having the having the lowest noise, which implies that it is a well-optimized design. Both of the spike detection systems have small area, which is not surprising since they do not include the ability to digitize all channels simultaneously. The analog recording system by TBSI and the feature extraction system by Chae have areas of 0.40 mm² and 0.49 mm² respectively. Since the digital-circuitry area of all these systems is not dominant, process scaling (i.e. 65-nm CMOS) is of limited benefit. In fact the smallest area-per-channel system is implemented in 350 nm CMOS by Harrison. It is difficult to identify a clear trend from this data, and we summarize the following: the expected area is between 0.3 and 0.49 mm² per channel.

- Noise: The amplifier performance sets the limit on achievable noise, and can be traded off with power and area. The systems in Table 2.1 show 5 to 10  $\mu$ V of noise. We will dissect this specification thoroughly in Section 3.3.

- Range: The range achievable is a function of power transmitted from the antenna and the data-rate, and will be examined in Section 3.7. The transmitter power dissipation has two main components, from the oscillator and upconverter/power amplifier circuits. Increasing range is primarily a function of the power amplifier, while the oscillator

power is set by required phase noise of the modulation scheme used.

One final point is that these systems have often been designed with a fairly specific application in mind. This makes a direct comparison difficult. One outcome of this dissertation will be to gain a better understanding of the implications of circuit imperfections such as analog circuit noise and distortion, ADC resolution, and feature extraction algorithms, on the overall quality of the recorded data.

In this Chapter we have examined system published to date to determine stat-of-the-art performance and generate some rough estimates of performance for our system. Chapter 3 deals with the optimization of individual blocks where these estimates will be scrutinized, while Chapter 4 deals with the overall system optimization.

# CHAPTER 3

# Block Level Design

## 3.1 Introduction

In this chapter we review the power and area estimates for each of the major blocks in the wireless biosignal telemetry system. Each of the blocks (neurons and electrodes, amplifier, analog-to-digital converter, digital-signal processors, and transmitter) shown in Figure 3.1 will be discussed in the following sections. The key concerns are also listed for each block.

### 3.2 Neurons and Electrodes

This section discusses the electrical characteristics of neurons and the electrodes used to sense their activity.

There are several classes of biological signals that can be measured, with different fre-

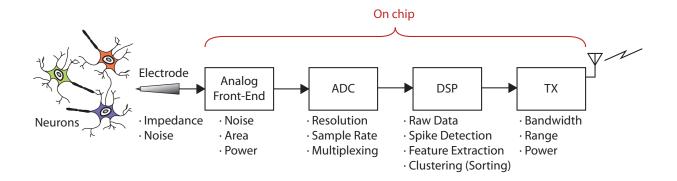

Figure 3.1: Block diagram of biological signal recording system.

quency content and amplitudes. Each type of signal use specialized electrodes, yet the signal level is still too small for signal processing. Amplifiers provide two main benefits: (a) a low level signal can be corrupted by additional noise in the signal processing blocks if gain is not applied and (b) the amplitude must also be increased to be compatible with the ADC full scale.

Figure 3.2: (a) Characteristics of different biosignals, (b) A recording of a neural spike.

Figure 3.2a shows commonly measured biological signals as described by Harrison in [47]. These signals are

- EEG: Electroencephalography is the recording of the ensemble behavior of tens of thousands of neurons within a brain, typically on the scalp. EEG is a large-scale observation of brain activity, and has poor spatial resolution.

- LFP: Local-field potentials are recorded from implanted electrodes, and sense the activity of neurons up to 3 mm from the electrode. A 300 Hz filter is used to remove higher frequency components.

Figure 3.3: An Electrical Model of a Neuron.

- ECG/EMG: Electrocardiograph and Electromyography record the electrical activity of cardiac and skeletal muscles respectively.

- Neural spikes are recorded from an implanted electrode, capture the activity of a small number of neurons. Specifically, neural spikes refer to extracellular action potentials. Recording neural spikes is the main goal of this research. An example of a neural spike, after bandpass filtering to remove unwanted signals such as LFP, is shown in Fig. 3.2b. Two (possibly three) neurons can be identified by their spike shapes. The spike recording data was taken from Rutishauser et. al. [48].

From an electrical perspective, a neuron is comprised of a number of voltage-controlled ion channels, such as sodium, potassium, and chlorine. Each ion has an associated electrical potential, and conductance from inside the cell to outside. From a circuit perspective, the neuron is simply modeled by a voltage source with a dc offset  $V_{\rm O}$  and an action-potential waveform  $V_{\rm AP}$ . There is also a resistance associated with the neuron from the average conductance during a spike event, and a spreading resistance from the neuron to the electrode through the intervening ionic solution.

A simple electrical model of neuron is shown in (Fig. 3.3). The different ions channels are shown in (a). The ion channel conductances are voltage dependent, and the reaction time of these channels determines the shape of the action potential (also known as a spike).

Figure 3.4: Electrode Model

A lumped model which reduces the network in (a) to an offset voltage, a transient voltage source, and a source resistance is shown in (b). It is assumed that  $R_{\text{Neuron}}$  is small compared the electrode resistances. For circuit modeling, (b) is adequate.

While the electrode itself is ideally little more than a conductor in most cases, the interaction between the electrode and electrolytic solution surrounding it requires modeling of the electrochemical interactions. Firstly, the electrode has a finite surface area, which introduces a resistive path  $R_{\rm S}$  from the electrolyte to the electrode. Secondly, the charged ions at the interface form a voltage gradient, and this charge-storage can be modeled as a capacitor  $C_{\rm P}$ , with a dc voltage across the capacitor representing the electrochemical interaction of the ions at the interface. The voltage across the interface can be up to 1-2 V [49],[50]. Proper selection of the ground electrode for the circuit can help cancel this offset voltage, and keep the inputs within the input-common-mode range of the amplifier.

Differential sensing also reduces the offset to the dc mismatch between the reference and sensing electrode. A resistive leakage path  $(R_{\rm P})$  also exists in parallel with the capacitor, but is typically negligible when considering the frequency response of the probe. However, it does show the dc offset of the electrode/electrolyte interface is coupled to the amplifier input. It should be noted however that the electrode interface is actually a complex non-linear system, and the model shown here is a simplification to enable circuit design. More

details can be found in [51].

# 3.3 Analog Front-End Amplifier

# 3.3.1 Differential Amplifier Configuration

In general terms, the neural amplifier must

- reject large dc offset voltages that occur at the tissue-electrode interface,

- provide enough frequency selectivity of the small neural signal of interest

- amplify the small signal to levels used by subsequent signal processors

- reject unwanted signals such as ac mains and other common-mode disturbances

- provide selectable reference potentials

- be able to drive the following stages (typically an ADC)

- have low input-referred noise

The dc offset voltage arises due to two main effects. The electrochemical half-cell that occurs around the conductive electrode in the ionic inter-cellular fluid gives rise to a voltage between approximately  $\pm 1.5$  V depending on the electrode material [50]. Since we detect the differential voltage between the desired electrode and a reference electrode, which helps ensure that the signal received by the amplifier is within its common-mode range, the amplifier only sees a fraction of the half-cell potential. The reference electrode must be connected to an appropriate potential. The potential outside a nerve cell also depends on the concentrations of the ions inside and outside of the membrane, and this resting potential is around -60 mV [52]. The combined effect of these dc offsets results in a few hundred millivolts of

dc offset at the amplifier input which must be removed before amplification, otherwise the linear range of the amplifier will be exceeded, and distortion and/or saturation will occur.

As seen in Fig. 3.2a, different signals occupy different frequency bands. To extract spike information efficiently, other signals such as LFP must be removed to minimize the required dynamic range of the amplifier. Spike frequency content is approximately within 1 kHz to 10 kHz. A filter profile with a high-pass corner frequency of 100 Hz and a low-pass corner of 10 kHz is used. As spike amplitudes for extra-cellular recording are typically between 50- $500 \,\mu\text{V}$ , and ADC full-scales voltages are on the order of 0.5 V, we require a maximum voltage gain of 10,000 to match the ADC's full-scale. As the amplifier input is high impedance, it is susceptible to coupling of undesired signals such ac mains (50 or 60 Hz). For robust operation, amplifier operation should be largely unaffected by a 10 m $V_{\rm p-p}$  common-mode signal at 60 Hz. Specified another way, this signal should result in no more than 5% of the amplifier full-scale output swing, which gives a common-mode gain requirement of less than -52 dB. The amplifier should also provide a multiplexer to select different reference potentials. Such flexible configurations allow for optimizing common-mode noise rejection by choosing a reference electrode judiciously. This is because it is common to have access to a choice of reference electrodes, and it is not generally known in advance what combination of electrode and reference will give the cleanest signal. The amplifier must also be able to drive the ADC input impedance, which is typically a few picofarads for ADCs in the 8-12 bit resolution range.

Finally, the amplifier should have low input-referred noise. As noise and power are tightly linked, the noise specification will be carefully examined. The SNR is defined as

$$SNR = 20 \log_{10} \left( \frac{V_{\text{p-p,spike}}}{6 \cdot v_{\text{n,tot}}} \right)$$

(3.1)

where  $V_{\rm p-p,spike}$  is the peak-to-peak voltage amplitude of the spike waveform, and  $v_{\rm n,tot}$  is the input referred rms noise voltage of the system (of which the dominant sources are the electrode and amplifier stages).

Based on system level studies [53], an SNR of greater than 5 dB is required (Fig. 3.5), which in turn, specifies that for a 50  $\mu$ V spike the total noise of the system should be less than 4.7  $\mu$ V. Electrode resistance of 45 k $\Omega$  (per electrode in the signal/reference pair) gives 3.9  $\mu$ V thermal noise integrated over a 10 kHz bandwidth, which then leads to an amplifier noise requirement of less than 2.5  $\mu$ V. The noise contributions for 5 dB SNR for a low and high amplitude spike are shown in Table 3.1. The table also shows that a high amplitude spike can tolerate a much higher amplifier noise  $v_{\rm n,in}$  for the same SNR. The associated power-noise trade-off will be explored in Section 3.3.7, where we consider a technique to minimize power dissipation.

Table 3.1: Noise Contributions for 5 dB SNR

|                     | Low Amp. | High Amp. | Unit    |

|---------------------|----------|-----------|---------|

| BW                  | 10000    | 10000     | Hz      |

| SNR                 | 5        | 5         | dB      |

| $V_{\rm p-p,spike}$ | 50       | 500       | $\mu V$ |

| $v_{ m n,tot}$      | 4.69     | 46.86     | $\mu V$ |

| $v_{ m n,elec}$     | 3.92     | 3.92      | $\mu V$ |

| $v_{ m n,in}$       | 2.56     | 46.70     | $\mu V$ |

Finally, the amplifier should operate from a low supply-voltage to be compatible with the digital signal processing and a single-cell battery.

Table 3.2 summarizes the amplifier specifications.

#### 3.3.2 Existing Neural Amplifiers

Most neural spike amplifiers implemented to date use a capacitively-coupled amplifier to remove the dc offset voltage and implement large impedances for low-frequency signals in a small area. Furthermore, the passband voltage gain of this amplifier is well-defined by

Figure 3.5: Required SNR of different spike detection algorithms. For a NEO detector, 5-dB is the minimum SNR for good detection and false-alarm probabilities. Based on data from [53].

Table 3.2: Spike Amplifier Specifications

| Input Referred Offset Voltage | <1 mV              | Input Referred Noise Voltage  | $<2.5~\mu\mathrm{V}$ |

|-------------------------------|--------------------|-------------------------------|----------------------|

| Filter Corner (High-Pass)     | 100 Hz             | Filter Corner (Low-Pass)      | 10 kHz               |

| Voltage Gain (Differential)   | 80 dB              | Voltage Gain<br>(Common-Mode) | -52 dB               |

| Output Swing                  | 1 V <sub>p-p</sub> | Output Load                   | 2 pF                 |

Figure 3.6: Capacitively Coupled Amplifier.  $v_{\rm n,amp}$  is the noise of the amplifier.

the ratio of the two capacitors  $C_1$  and  $C_2$ . The high-pass corner frequency is  $1/(R \cdot C_1)$ . When the resistance is implemented by a pseudo-resistor [54], a giga-ohm resistance can be implemented in a small area. However it is non-linear, so cannot be used for the signal path if distortion is a concern. The low-pass pole is constructed by the finite bandwidth of the amplifier. A capacitor-based feedback network also achieves high input impedance with physically small components – using resistors for a similar input impedance would introduce a large parasitic capacitance which would increase power consumption and area. As the electrode capacitance is typically greater than 200 pF, which is much larger than  $C_1$  used in typical integrated circuit implementations, the frequency response from a neuron to the output of the amplifier is determined solely by the circuit elements shown in Figure 3.6. Examples of this amplifier architecture can be found in [41,49,55–59]. Alternate approaches such as chopper stabilization [60] and dc stabilization [61] are also used but the most powerefficient designs to date use ac-coupled amplifiers. AC coupled amplifiers also completely isolate the dc offset from the amplifier (though transient disturbances still mandate the use of a mechanism to reset the low frequency (i.e. slow settling) bias network). As the dc offset is difficult to predict, ac coupling is preferred for this work. Furthermore, dc isolation between the biological tissue and electronics is required to avoid chemical interaction, even under fault conditions.

#### 3.3.3 Amplifier Design

#### 3.3.3.1 Noise Contributions

The input-referred noise contributions for the amplifier configuration shown in Figure 3.6 are summarized by Eqs. 3.2 and 3.3. As the high-pass corner  $f_1$  is pushed lower, the noise contributed by the feedback resistor  $R_B$  (used for dc biasing) contributes less noise. However the corner cannot be made arbitrarily low as the achievable resistance has an upper limit, and unwanted signals such as ac mains and LFP will also be amplified if the corner is made too low. The value of  $R_B$  is fixed after the capacitor size  $C_1$  and  $f_1$  are chosen, and  $R_B$  does not appear in Eq. 3.3 explicitly. As  $f_1$  is essentially determined by application requirements, the key variable for optimization is  $C_1$  in the familiar kT/C form.

$$\overline{v_{\text{in,amp}}^2} = \left[ \frac{1 + s \cdot R_{\text{B}} \cdot (C_1 + C_2 + C_{\text{in}})}{1 + s \cdot R_{\text{B}} \cdot C_1} \right]^2 \cdot v_{\text{n,amp}}^2$$

(3.2)

$$\overline{v_{\rm in,res}} = \sqrt{\frac{2}{\pi}} \frac{1}{A_{\rm V}} f_{\rm l} \cdot \sqrt{\frac{kT}{C_{\rm l}}} \cdot \frac{1}{f} \cdot \Delta f \tag{3.3}$$

As the gain is given by Eq. 3.4, and the electrode noise is injected at the input of the circuit, the electrode noise has the same frequency response as the amplifier itself. The resistance of the electrode therefore sets the minimum achievable noise (along with the background noise of thousands of neurons near the electrode). As frequency dependence of electrodes is often negligible for neural spike amplifiers, modeling the electrode as a single capacitor is appropriate, and there is no additional frequency dependence (Eq 3.5).

$$H(s) = \frac{V_{out}}{V_{in}} = \frac{s \cdot R_{\rm B} \cdot C_1}{1 + s \cdot R_{\rm B} \cdot C_2}$$

$$(3.4)$$

$$\overline{v_{\text{elec}}^2} = 4 \cdot k \cdot T \cdot R_{\text{E}} \cdot |H(s)|^2 \Delta f \tag{3.5}$$

Figure 3.7: Noise contributions for an ac-coupled neural spike amplifier.

The noise equations given are for a single-ended circuit, with two times the noise power present in differential implementations. Fig. 3.7 shows that the electrode noise is the dominant noise source. As previously mentioned, the noise generated by the electrode is outside the control of the circuit designer. In Fig. 3.7, a more sophisticated electrode model has been used which causes the noise peaking around 1 Hz. The next largest noise source is the amplifier contribution, and will be the focus of subsequent optimization.

### 3.3.4 Transistor-Level Design

We now consider the design of the operational amplifier. The lowest power design to-date uses a folded-cascode operational transconductance amplifier (OTA) [59], and is shown in Figure 3.8. Approximate dc bias voltages are also shown, assuming that the input and output common-mode voltages are equal (as is the case when a resistor from output to input is used to set the common mode input level).

Because of the tall stack of transistors required to implement an op-amp, operation at low-voltage is difficult. We will look at an open-loop amplifier with a minimum number of stacked transistors to compare the power efficiency.

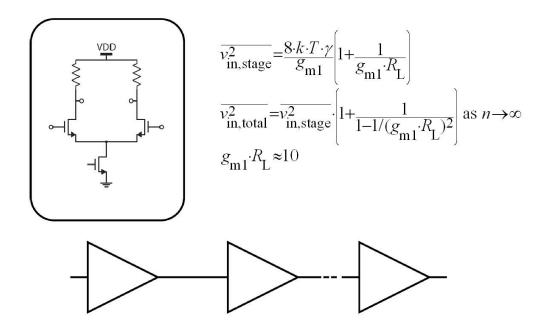

The total noise power, when input referred, can be given approximately by  $v_{\rm n,M1}^2 \cdot (1 + g_{\rm m5}/g_{\rm m1})$ . Using Equations A.11 and A.12, the total noise can be plotted as a function of  $V_{\rm ds,sat}$  and hence supply voltage (Figure 3.9). For the minimum VDD calculation, it is assumed that 0.5 V is sufficient for the other transistors, and  $V_{\rm ds,sat}$  is allocated to  $M_5$ .