# UC San Diego UC San Diego Electronic Theses and Dissertations

## Title

Adaptive Test Cost and Quality Optimization Through An Effective Yet Efficient Delivery of Chip Specific Tests

**Permalink** https://escholarship.org/uc/item/19b44955

**Author** Arslan, Baris

**Publication Date** 2013

Peer reviewed|Thesis/dissertation

### UNIVERSITY OF CALIFORNIA, SAN DIEGO

Adaptive Test Cost and Quality Optimization Through An Effective Yet Efficient Delivery of Chip Specific Tests

A dissertation submitted in partial satisfaction of the requirements for the degree Doctor of Philosophy

in

**Computer Science**

by

Baris Arslan

Committee in charge: Professor Alex Orailoglu, Chair Professor Chung-Kuan Cheng Professor Sadik Esener Professor Yoav Freund Professor William E. Howden

2013

Copyright

Baris Arslan, 2013

All rights reserved.

The Dissertation of Baris Arslan is approved, and it is acceptable in quality and form for publication on microfilm and electronically:

Chair

University of California, San Diego

2013

### DEDICATION

To my parents.

# TABLE OF CONTENTS

| Signature  | ignature Pageiii                                                   |      |

|------------|--------------------------------------------------------------------|------|

| Dedicatio  | on                                                                 | iv   |

| Table of   | Contents                                                           | v    |

| List of Fi | gures                                                              | viii |

| List of Ta | ables                                                              | X    |

| Acknowl    | edgements                                                          | xi   |

| Vita       |                                                                    | xiii |

| Abstract   | of the Dissertation                                                | XV   |

| Chapter 1  | I Introduction                                                     | 1    |

| 1.1        | Test Cost and Quality Optimization                                 | 7    |

| 1.1.       | 1 Test Effectiveness and Efficiency Exploration                    | 7    |

| 1.1.2      | 2 Variable Test Resource Allocation                                | 10   |

| 1.1.3      | 3 Test Compression                                                 |      |

| 1.2        | Constraints and Challenges                                         | 14   |

| 1.2.1      | 1 Defect Clasification                                             | 14   |

| 1.2.2      | 2 Functional Constraints                                           | 16   |

| 1.2.3      | 3 Algorithmic Challenges                                           | 17   |

| 1.3        | Thesis Summary                                                     | 19   |

| Chapter 2  | 2 Previous Work                                                    |      |

| 2.1        | Scan Compression                                                   |      |

| 2.2        | Static Test Optimization Techniques                                |      |

| 2.3        | Adaptive Test Optimization Techniques                              |      |

| Chapter 3  | 3 Adaptive Test Optimization through Test Effectiveness Assessment |      |

| 3.1        | Motivation                                                         | 35   |

| 3.2        | Approach                                                           | 39   |

| 3.3        | Test Effectiveness Assessment through Dynamic Test Flow            |      |

| 3.3.       | 1 Test Vector Defect Detection Information                         |      |

| 3.3.2      | 2 Test Vector Order Correlation                                    | 44   |

| 3.3.3      | 3 Test Effectiveness Identification                                |      |

| 3.4     | Ada            | aptive Test Cost Optimization                                              | 49    |

|---------|----------------|----------------------------------------------------------------------------|-------|

| 3.4     | 4.1            | Ineffective Test Vector Elimination                                        | 49    |

| 3.4     | 4.2            | Test Cost/Quality Tradeoff                                                 | 51    |

| 3.4     | 4.3            | Adaptivity to Defect Mechanism Shifts                                      | 55    |

| 3.5     | Exp            | perimental Results                                                         | 57    |

| 3.6     | Cor            | nclusions                                                                  | 66    |

| Chapter | r 4 Tra        | cing the Best Test Mix through Multi-Variate Test Quality Tracking         | 68    |

| 4.1     | App            | proach                                                                     | 70    |

| 4.2     | Mu             | Iti-Variate Test Quality Optimization                                      | 73    |

| 4.2     | 2.1            | Test Quality Estimation                                                    | 73    |

| 4.2     | 2.2            | Optimal Test Set Selection                                                 | 76    |

| 4.3     | Ada            | aptive Sample Size Optimization                                            | 77    |

| 4.4     | Exp            | perimental Results                                                         | 79    |

| 4.5     | Cor            | clusions                                                                   | 83    |

| Chapter | r 5 Chi        | ip-Specific Delay Test Resource Allocation                                 | 85    |

| 5.1     | Mo             | tivation                                                                   | 86    |

| 5.2     | Del            | ay Test Time Allocation                                                    | 88    |

| 5.2     | 2.1            | Delay Test Quality Estimate                                                | 90    |

| 5.2     | 2.2            | Delay Variation Modeling                                                   | 92    |

| 5.3     | Ana            | alytical Framework                                                         | 94    |

| 5.4     | Exp            | perimental Results                                                         | 97    |

| 5.5     | Cor            | nclusions                                                                  | . 101 |

| Chapter | r 6 Tes        | st Resource Allocation and Scheduling for Multiple Frequency Domains       | . 103 |

| 6.1     | Ove            | erview                                                                     | . 106 |

| 6.2     | Del            | ay Test Quality Estimation                                                 | . 110 |

| 6.3     | Opt            | imal Test Time Allocation                                                  | . 112 |

| 6.4     | Tes            | t Time Allocation and Scheduling                                           | . 115 |

| 6.4     | 4.1            | Test Time Allocation and Scheduling with Test Time and Concurrency         |       |

|         |                | nts                                                                        |       |

|         | 4.2<br>onstrai | Test Time Allocation and Scheduling with Test Time, Concurrency and Points |       |

| 6.4     | Exp            | perimental Results                                                         | . 129 |

| 6.5     | Cor            | nelusions                                                                  | . 134 |

| Chapter 7 | CircularScan: A Scan-Based Test Architecture for Test Cost Reduction | 136 |

|-----------|----------------------------------------------------------------------|-----|

| 7.1       | Motivation                                                           | 137 |

| 7.2       | Proposed Addressing Scheme                                           | 140 |

| 7.3       | Addressing Space Search                                              | 144 |

| 7.4       | Test Application                                                     | 148 |

| 7.5       | Experimental Results                                                 | 152 |

| 7.5       | Conclusions                                                          | 155 |

| Chapter 8 | 3 Conclusions                                                        | 157 |

| Bibliogra | phy                                                                  | 163 |

## LIST OF FIGURES

| Figure 1.1 Test cost vs. overall cost                                             | 3    |

|-----------------------------------------------------------------------------------|------|

| Figure 1.2 Fault model effectiveness                                              |      |

| Figure 3.1 Test vector effectiveness.                                             | . 37 |

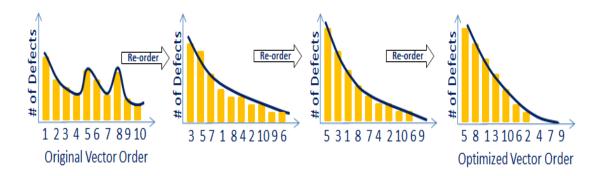

| Figure 3.2 Dynamic test vector re-ordering                                        | . 41 |

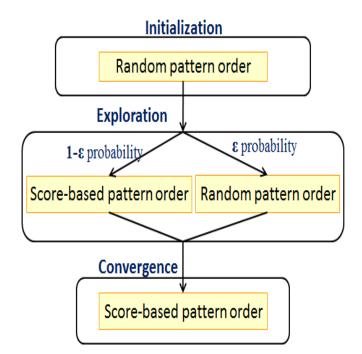

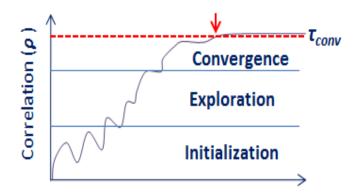

| Figure 3.3 Test effectiveness learning phases                                     |      |

| Figure 3.4 Correlation throughout the learning phases                             | . 47 |

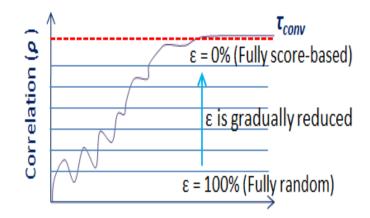

| Figure 3.5 Correlation as ε is reduced                                            |      |

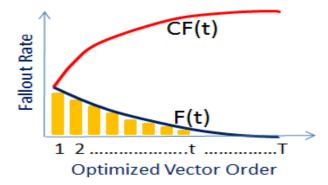

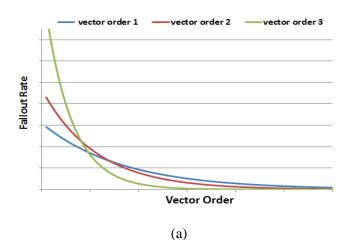

| Figure 3.6 Vector failure rate and cumulative failure rate                        | . 50 |

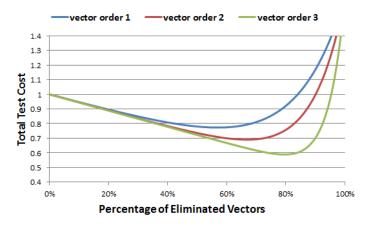

| Figure 3.7 Test cost as more vectors are eliminated                               | . 54 |

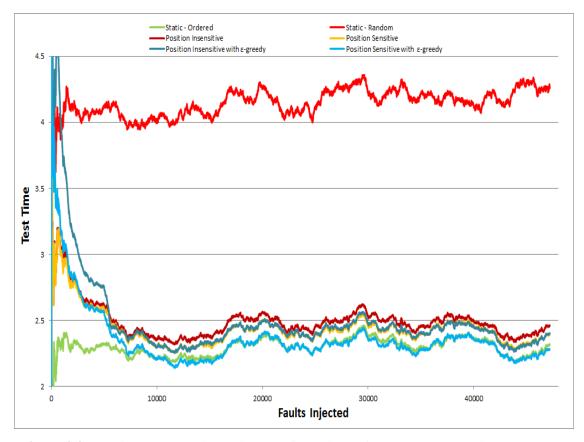

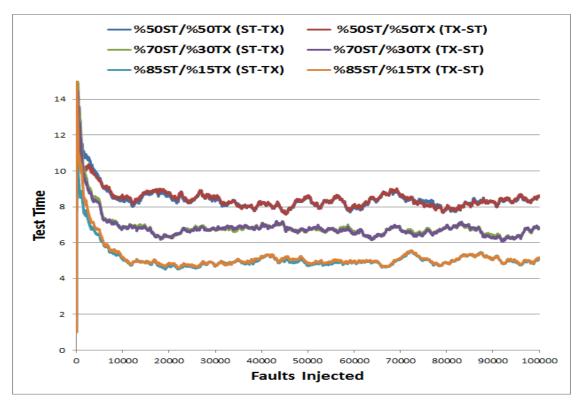

| Figure 3.8 Test time change with various configurations of the proposed learning  |      |

| process                                                                           | . 58 |

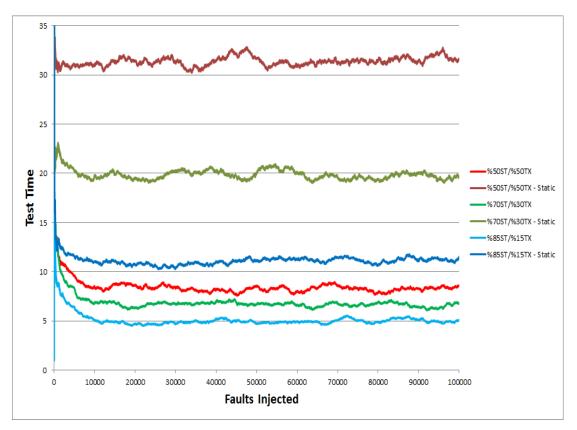

| Figure 3.9 Test time change when the stuck-at tests precede the transition tests  |      |

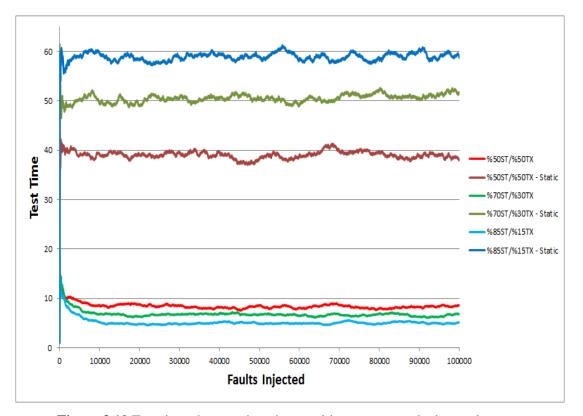

| Figure 3.10 Test time change when the transition tests precede the stuck-at tests | . 61 |

| Figure 3.11 Test time for a variety of initial orderings                          | . 62 |

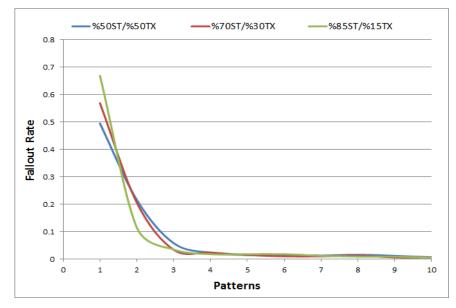

| Figure 3.12 Failure rate after convergence                                        |      |

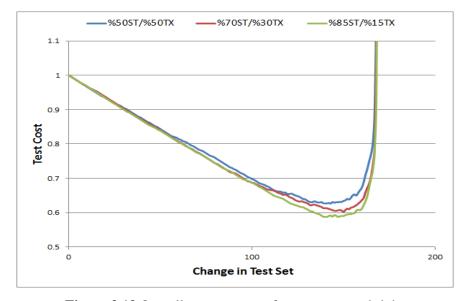

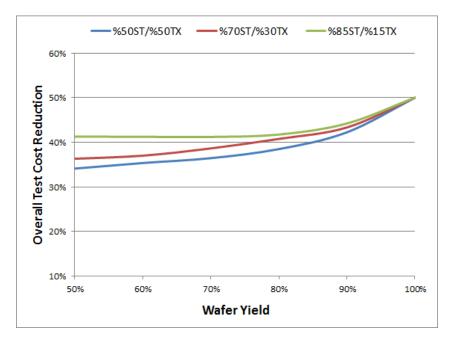

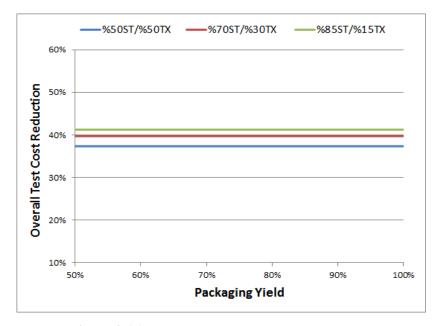

| Figure 3.13 Overall test cost as wafer-sort test set shrinks                      | . 64 |

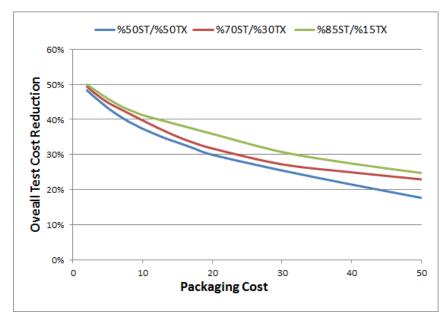

| Figure 3.14 Test cost reduction vs. packaging cost                                |      |

| Figure 3.15 Test cost reduction vs. wafer yield                                   | . 65 |

| Figure 3.16 Test cost reduction vs. packaging yield                               | . 66 |

| Figure 4.1 Test quality vs. test cost                                             | 71   |

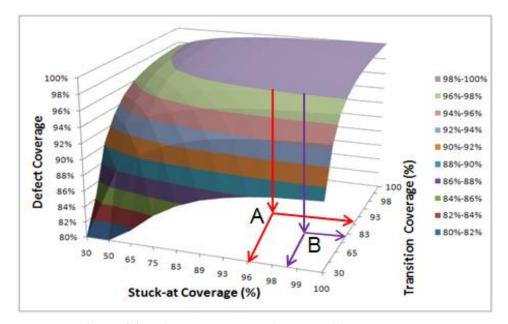

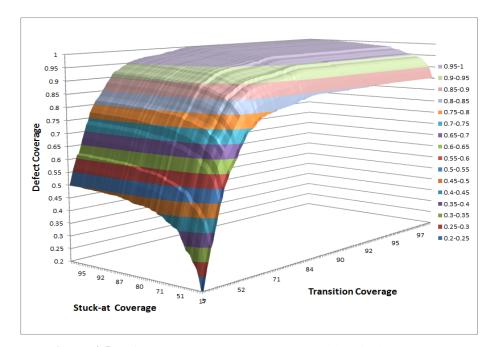

| Figure 4.2 Defect coverage as a function of fault coverages                       | . 75 |

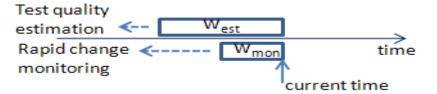

| Figure 4.3 Two windows for accuracy and adaptivity                                | . 79 |

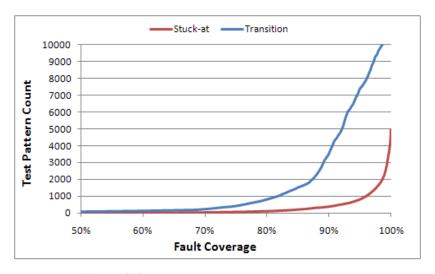

| Figure 4.4 Test pattern count vs. fault coverage                                  | . 79 |

| Figure 4.5 Defect coverage vs. stuck-at & transition fault coverages              | . 80 |

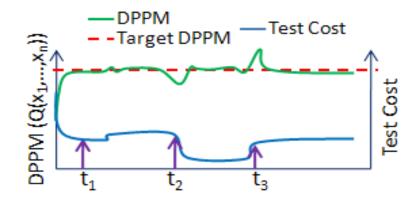

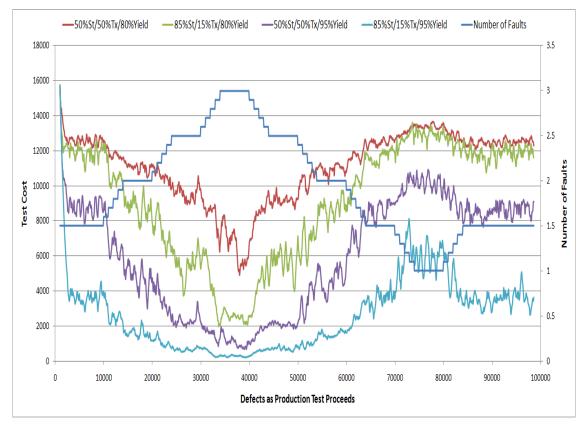

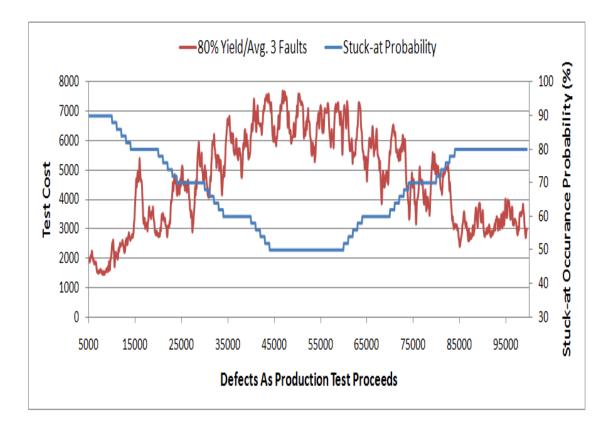

| Figure 4.6 Test cost as defect characteristics evolve                             | . 82 |

| Figure 4.7 Test cost vs. stuck-at/transition fault occurrence ratio               | . 83 |

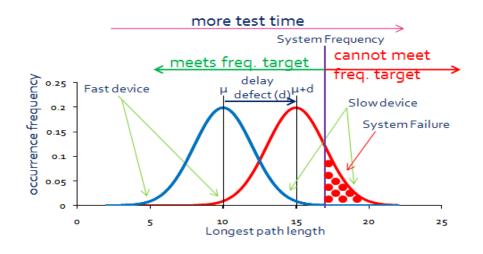

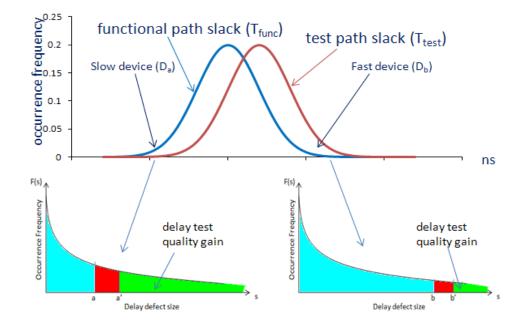

| Figure 5.1 Delay defects and process variation effect                             | . 87 |

| Figure 5.2 Proposed process-aware delay test flow                                 |      |

| Figure 5.3 Process-aware test time allocation                                     | . 89 |

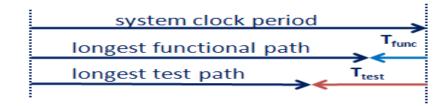

| Figure 5.4 Functional and test path slacks                                        |      |

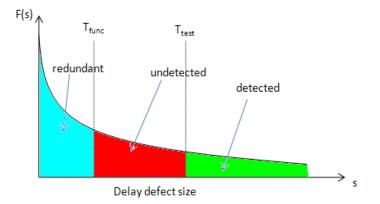

| Figure 5.5 Delay defect distribution                                              | 92   |

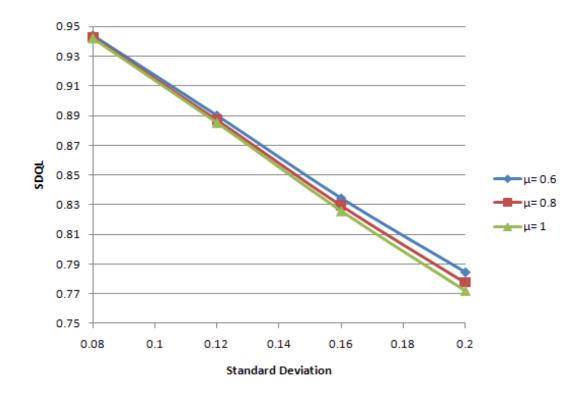

| Figure 5.6 Process variation and its effect on test quality                       |      |

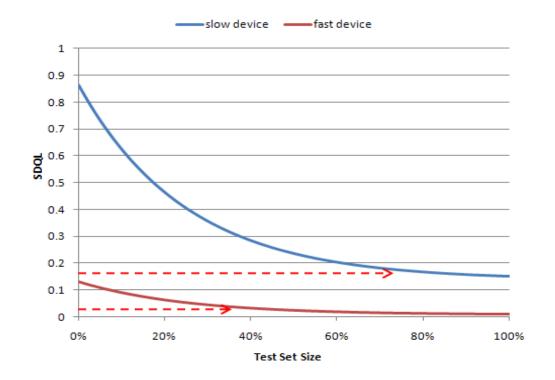

| Figure 5.7 Test quality change as test time is increased                          |      |

| Figure 5.8 Delay test quality improvement                                         |      |

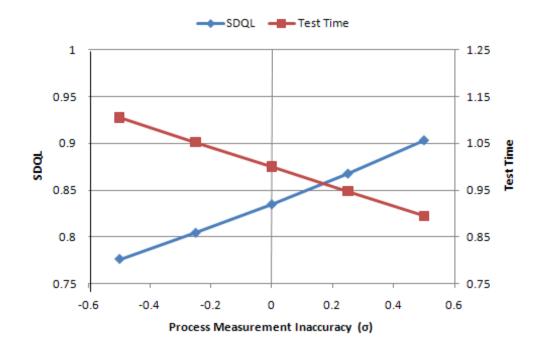

| Figure 5.9 The effect of process measurement error                                | 100  |

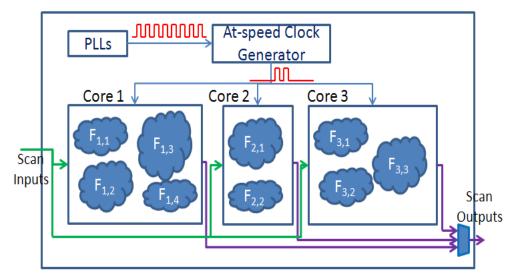

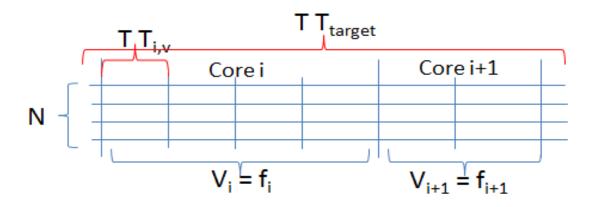

| Figure 6.1 Core-based SOC test architecture                                       | 106  |

| Figure 6.2 Concurrent delay testing of domains                                    |      |

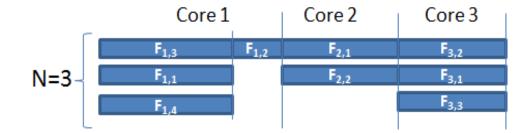

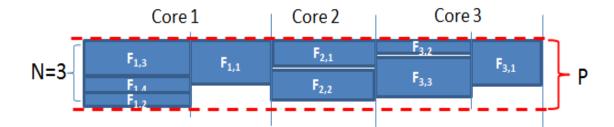

| Figure 6.3 Concurrency limits by power constraints                                |      |

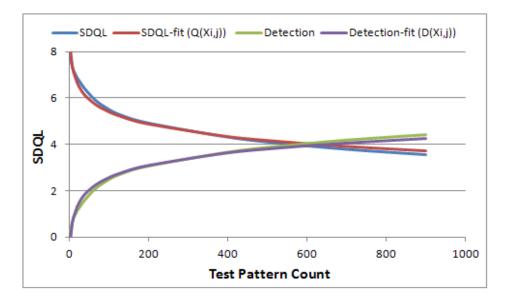

| Figure 6.4 SDQL vs. test pattern count                                            |      |

| Figure 6.5 Horizontal and vertical test resources                                 |      |

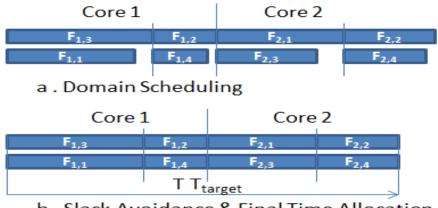

| Figure 6.6 Domain scheduling and final test time                                  |      |

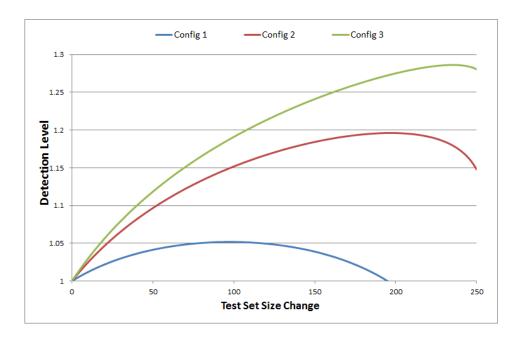

| Figure 6.7 Detection level change as test time allocation altered                 |      |

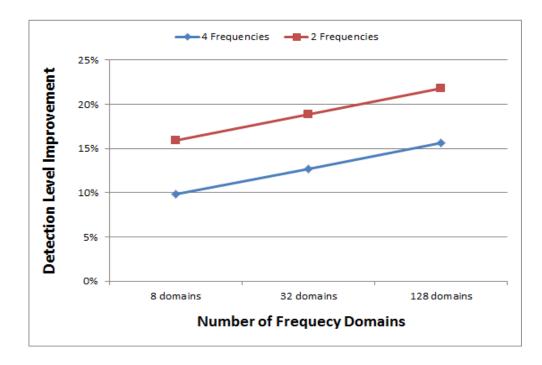

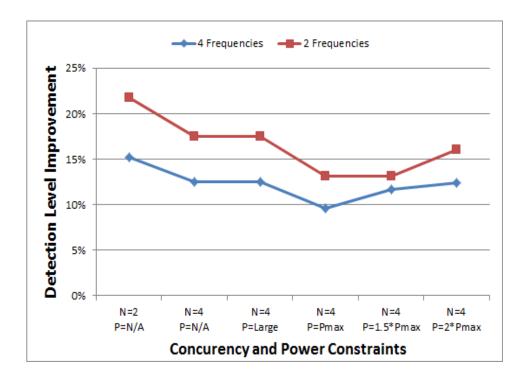

| Figure 6.8 Quality improvement for various SOC configurations                     |      |

| Figure 6.9 Quality improvement with concurrency                                   |      |

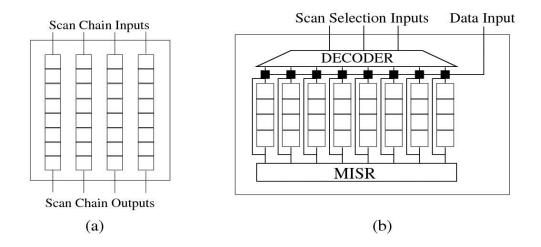

| Figure 7.1 Traditional and <i>CircularScan</i> architecture                       | 138  |

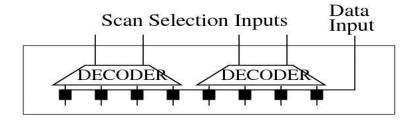

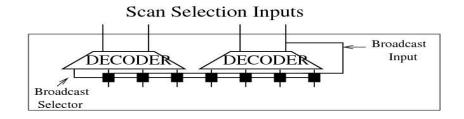

| Figure 7.2 Multiple decoder addressing mechanism | 141 |

|--------------------------------------------------|-----|

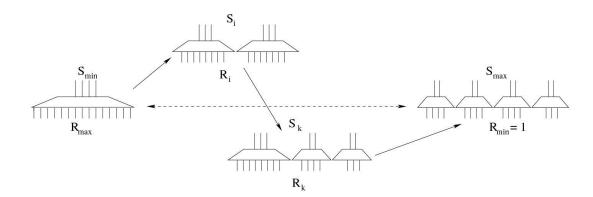

| Figure 7.3 Addressing space                      | 143 |

| Figure 7.4 Proposed configuration                | 144 |

| Figure 7.5 Test vectors                          | 149 |

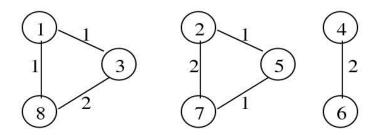

| Figure 7.6 Weighted incompatibility graph        | 150 |

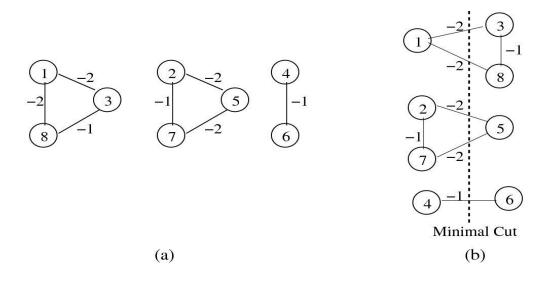

| Figure 7.7 Minimal cut partitioning              | 151 |

## LIST OF TABLES

| Table 4.1 Defective chips detected on ATE vs. fault coverages | 74  |

|---------------------------------------------------------------|-----|

| Table 6.1 Domain configurations                               |     |

| Table 7.1 Benchmark info and test cost reduction              |     |

| Table 7.2 Comparison with test set independent methods        | 154 |

| Table 7.3 Comparison with test set dependent methods          | 155 |

### ACKNOWLEDGEMENTS

Chapter 3, in part, is a reprint of the material as it appears in *B. Arslan and A. Orailoglu, "Adaptive Test Optimization through Real-time Learning of Test Effectiveness", Design, Automation and Test in Europe Conference, 2011*; and in *B. Arslan and A. Orailoglu, "Aggressive Test Cost Reductions Spanning Multiple Levels of Test Flow through Continuous Test Effectiveness Assessment", submitted to IEEE Transactions on Very Large Scale Integration Systems.* The dissertation author was the primary investigator and author of these papers.

Chapter 4, in part, is a reprint of the material as it appears in *B. Arslan and A. Orailoglu, "Adaptive Test Framework for Achieving Target Test Quality at Minimal Cost", Asian Test Symposium, 2011*; and in *B. Arslan and A. Orailoglu, "Tracing the Best Test Mix through Multi-Variate Quality Tracking", VLSI Test Symposium, 2013.* The dissertation author was the primary investigator and author of these papers.

Chapter 5, in part, is a reprint of the material as it appears in *B. Arslan and A. Orailoglu, "Delay Test Quality Maximization through Process-aware Selection of Test Set Size", International Conference on Computer Design, 2010;* and in *B. Arslan and A. Orailoglu, "Full Exploitation of Process Variation Space for Continuous Delivery of Optimal Delay Test Quality", Asia and South Pacific Design Automation Conference, 2013.* The dissertation author was the primary investigator and author of these papers.

Chapter 6, in part, is a reprint of the material as it appears in *B. Arslan and A. Orailoglu, "Delay Test Resource Allocation and Scheduling for Multiple Frequency Domains", VLSI Test Symposium, 2012*; and in *B. Arslan and A. Orailoglu, "Power-Aware Delay Test Quality Optimization for Multiple Frequency Domains", submitted to IEEE*

*Transactions on Computer-Aided Design of Integrated Circuits and Systems.* The dissertation author was the primary investigator and author of these papers.

Chapter 7, in part, is a reprint of the material as it appears in *B. Arslan and A. Orailoglu, "CircularScan: A Scan Architecture for Test Cost Reduction", Design, Automation and Test in Europe Conference, 2004*; in *B. Arslan and A. Orailoglu, "Design Space Exploration for Aggressive Test Cost Reduction in Circular Scan Architectures", International Conference on Computer-Aided Design, 2004*; and in *B. Arslan and A. Orailoglu, "Test Cost Reduction through A Reconfigurable Scan Architecture", International Test Conference, 2004.* The dissertation author was the primary investigator and author of these papers.

### VITA

| 2000      | Bachelor of Science, Computer Engineering & Information Science<br>Bilkent University, Ankara, Turkey                 |

|-----------|-----------------------------------------------------------------------------------------------------------------------|

| 2001-2005 | Teaching Assistant, Department of Computer Science and Engineering<br>University of California, San Diego, California |

| 2002      | Master of Science, Computer Science<br>University of California, San Diego, California                                |

| 2002-2004 | Research Assistant, Department of Computer Science and Engineering<br>University of California, San Diego, California |

| 2005-2006 | DFT Engineer<br>Intel Corporation, Chandler, Arizona                                                                  |

| 2006-2007 | DFT Engineer<br>Marvell Semiconductor Inc., Chandler, Arizona                                                         |

| 2007-2013 | Staff Engineer<br>Qualcomm Inc., San Diego, California                                                                |

| 2013      | Doctor of Philosophy, Computer Science<br>University of California, San Diego, California                             |

### PUBLICATIONS

B. Arslan and A. Orailoglu, "Tracing the Best Test Mix through Multi-Variate Quality Tracking", *VLSI Test Symposium*, pp. 1-6, 2013.

B. Arslan and A. Orailoglu, "Full Exploitation of Process Variation Space for Continuous Delivery of Optimal Delay Test Quality", *Asia and South Pacific Design Automation Conference*, pp. 552-557, 2013.

B. Arslan and A. Orailoglu, "Delay Test Resource Allocation and Scheduling for Multiple Frequency Domains", *VLSI Test Symposium*, pp. 114-119, 2012.

B. Arslan and A. Orailoglu, "Adaptive Test Framework for Achieving Target Test Quality at Minimal Cost", *Asian Test Symposium*, pp. 323-328, 2011.

B. Arslan and A. Orailoglu, "Adaptive Test Optimization through Real-time Learning of Test Effectiveness", *Design, Automation and Test in Europe Conference*, pp. 1430-1435, 2011.

B. Arslan and A. Orailoglu, "Delay Test Quality Maximization through Process-aware Selection of Test Set Size", *International Conference on Computer Design*, pp. 390-395, 2010.

B. Arslan and A. Orailoglu, "CircularScan: A Scan Architecture for Test Cost Reduction", *Design, Automation and Test in Europe Conference*, pp. 1290-1295, 2004.

B. Arslan and A. Orailoglu, "Test Cost Reduction through a Reconfigurable Scan Architecture", *International Test Conference*, pp. 945-952, 2004.

B. Arslan, O. Sinanoglu and A. Orailoglu, "Extending the Applicability of Parallel-Serial Scan Designs", *International Conference on Computer Design*, pp. 200-203, 2004.

B. Arslan and A. Orailoglu, "Design Space Exploration for Aggressive Test Cost Reduction in Circular Scan Architectures", *International Conference on Computer-Aided Design*, pp. 726-731, 2004.

B. Arslan and A. Orailoglu, "Extracting Precise Diagnosis of Bridging Faults from Stuck-at Fault Information", *Asian Test Symposium*, pp. 230-235, 2003.

B. Arslan and A. Orailoglu, "Perfect Conservation of Diagnostic Information in Aggressive Reduction of SOC Test Bandwidth and Use", *European Test Workshop*, pp. 13-14, 2003.

B. Arslan and A. Orailoglu, "Aggressive SOC Test Response Compaction with Full Diagnostic Information Conservation", *International Test Synthesis Workshop*, 2003.

B. Arslan and A. Orailoglu, "Fault Dictionary Size Reduction through Test Response Superposition", *International Conference on Computer Design*, pp. 480-485, 2002.

### PUBLICATIONS UNDER REVIEW

B. Arslan and A. Orailoglu, "Power-Aware Delay Test Quality Optimization for Multiple Frequency Domains", *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems*.

B. Arslan and A. Orailoglu, "Aggressive Test Cost Reductions Spanning Multiple Levels of Test Flow through Continuous Test Effectiveness Assessment", *IEEE Transactions on Very Large Scale Integration Systems*.

### ABSTRACT OF THE DISSERTATION

Adaptive Test Cost and Quality Optimization Through An Effective Yet Efficient Delivery of Chip Specific Tests

by

Baris Arslan

Doctor of Philosophy in Computer Science

University of California, San Diego, 2013

Professor Alex Orailoglu, Chair

The higher levels of integration and process scaling imposes failure behaviors which are challenging to interpret, necessitating the continuous augmentation of fault models and test vectors in the hopes of taming the defect escape rate. The subsequent inflation in the number of test vectors coupled with the constant increase in the size of each test vector continuously boosts test cost. The economics of particularly the competitive consumer marketplace however require a constant vigilance at the test cost while ensuring a satisfactory test quality. While the inclusion of new fault models helps boost test quality, the non-uniform distribution of various defect types and the defect coverage overlaps between fault models imply variable effectiveness of fault models and test vectors, resulting in the inclusion of a large number of ineffective vectors in test flow. A static derivation of test effectiveness however remains problematic in practice as it is well known that defect characteristics are prone to drifts throughout the product lifecycle. Furthermore, the increasing process variation and the integration of hundreds of domains within a chip result in increasingly distinct domains and individualized chip instances with diverse test resource requirements. The conventional test method of a static application of an identical test set to all chips consequently struggles to satisfy the demanding test cost and quality constraints in the face of the evolving defect behaviors and the increasing diversification in test resource requirements.

This thesis addresses the simultaneous necessity for satisfactory test quality and low test cost through an adaptive test cost and quality optimization framework. The proposed methodologies not only adaptively assess the effectiveness of fault models and test vectors but also evaluate the variable test resource requirements of the chips and domains based on their distinct characteristics, enabling an effective yet efficient test through the selection of the most effective vectors and a carefully crafted allocation of test resources. The proposed methodologies are tailored for a broad set of application scenarios through the consideration of different defect classes and defect characteristic drift types while incorporating the test data gathering and delivery constraints and overcoming the associated algorithmic challenges.

# Chapter 1

# Introduction

VLSI testing is performed subsequent to the manufacturing of the integrated circuit (IC) to screen out the defective chips caused by the imperfections in the manufacturing process, ensuring the delivery of high quality chips to the customers. The VLSI test field is however continuously challenged by aggressive advances in the IC manufacturing process. Higher levels of integration and continuous process scaling, fueled by the intense competition for market share in the semiconductor industry, enable the manufacturing of increasingly low power and high performance integrated circuits at a lower cost. Yet ambitious manufacturing technology leaps magnify the failure rates and engender failure behaviors which are challenging to interpret and test, necessitating rigorous and costly test methods.

Fault model based structural testing coupled with scan-based test architecture, which configures the flops of an IC as serially accessible shift registers, have gained wide acceptance in industry as a *de facto* test standard in the last couple of decades as a way of keeping test generation complexity and test cost of today's large System-On-A-Chip (SOC) within practical limits while delivering an acceptable test quality. Conventionally, a small set of fault models, such as stuck-at, transition and IDDQ, is targeted during the test generation process and the resulting test sets are applied identically to each chip during manufacturing testing through a static test flow. Fault coverage, such as stuck-at coverage, is used as a primary

metric to assess the quality of the test set. As numerous years of experience in structural testing have showed, fault model based structural test has proved to be very effective in screening defects in earlier process nodes.

As semiconductor manufacturing has moved to deep submicron (DSM) process nodes, subtle defects that effect the parametric attributes such as timing came into prominence as a result of shrinking geometries and tighter design margins, diminishing the effectiveness of the traditional fault models such as the stuck-at fault and IDDQ. The decline in the effectiveness of the existing test tests subsequently necessitates the continuous piling of new fault models and the corresponding test vectors in the hopes of taming the defect escape level, measured as defective parts per million (DPPM), at an increasingly higher cost. Various new fault models and test methods such as N-detect, gate-exhaustive, timing-aware delay test and faster-than-at-speed delay test have been proposed to keep DPPM within acceptable limits as discussed in Chapter 2.

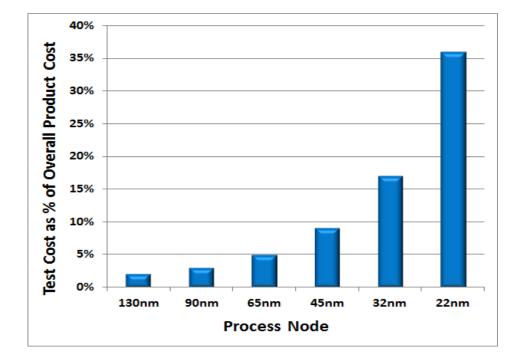

Not only the sheer number of test vectors due to the inclusion of emerging test types, but also, as a result of the serial access mechanism of scan-based test architecture, the size and subsequently the cost of each individual test vector is quickly growing as the complexity and the size of SOCs increase, further boosting test cost. Test cost subsequently constitutes with each new process node an increasingly larger fraction of overall product cost as illustrated in Figure 1.1 based on the data reported by a semiconductor company [1]. Although the actual percentages may vary for different semiconductor companies and product families, the trend of the continuous increase of test cost as a fraction of overall cost as shown in this figure applies across the semiconductor industry, quickly heading to the point of the cost of test exceeding the cost of manufacturing in the near future. The results of an extensive survey reported in the International Technology Roadmap for Semiconductors (ITRS) 2011 edition [2] show that 85% of the survey participants expect the cost of test to become their biggest concern going forward in the VLSI test field. In the face of newly emerging defect types in DSM process nodes and the continuous increase in the complexity of the chips, advance test methodologies are required to tame the rapid increase in test cost. Reductions in the number of test vectors and in the cost of each individual test vector can equivalently help to alleviate the concern of continuously increasing test cost.

Figure 1.1 Test cost vs. overall cost

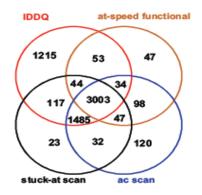

The effectiveness of fault models is typically analyzed by design of experiments (DOEs) with numerous results having been reported in the past [3], [4]. These experiments collect defective device detection data for each fault model on a sample of production chips and results are typically reported in a Venn diagram as depicted in Figure 1.2 [3]. The focus of these experiments predominantly has been the identification of the unique defects detected by each fault model, evaluating the additional DPPM improvement by a fault model. However, a defect may manifest itself in a number of distinct ways, leading to the detection of the same

defect by multiple fault models, resulting in defect coverage overlaps between fault models and the corresponding test vectors. As highlighted in Figure 1.2, a tremendous amount of defect detection overlap among fault models exists in practice, resulting in numerous ineffective test vectors. It is reported in [5] that ineffective patterns constitute 70% to 90% of the test sets, based on studies from major semiconductor companies. Furthermore, due to the non-uniform distribution of various defect types, different fault models and test vectors achieve distinct defect coverage levels as underscored by distinct numbers of defective devices detected by each fault model in Figure 1.2.

Figure 1.2 Fault model effectiveness

Consequently, while the introduction of new fault models helps boost test quality, appropriate attention needs to be paid to the effectiveness of each test vector, promoting the use of a proper mixture of test vectors from these fault models based on test vector effectiveness assessment in order to attenuate test cost. The economics of particularly the competitive consumer marketplace lend themselves to a rigorous test effectiveness assessment and a subsequent test cost and quality tradeoff analysis. As the intense competition in the consumer marketplace shrinks the profit margins, a constant vigilance at the test cost while ensuring a satisfactory test quality is required. The assessment of test effectiveness enables the exploration of test cost and quality tradeoff, resulting in the selection of a lowest cost test suite

while meeting the quality goals based on test economics. Furthermore, since the test is performed at multiple levels such as wafer-sort and package test, a test effectiveness assessment paves the way for test cost and quality optimization across multiple test levels.

Today, SOCs integrate numerous cores, ranging from multiple microprocessors, digital signal processing cores, and graphics processing units to multi-mode modems, consisting of hundreds of unique domains. The aggressive integration of a diverse set of cores in an SOC results in the cohabitation of various domains with distinct parametric attributes such as timing. Similarly, the increasing magnitude of process variation implies the individualization of each manufactured chip with distinct parametric profiles. The highlighted diversification across the domains and the chips exposes a major inefficiency of conventional test methods, namely, the application of an identical test set, selected based on fault coverage, to all chips. The detection of the subtle defects that effect parametric attributes necessitates not only the satisfaction of the logical defect defection distinct conditions but also the violation of target values such as frequency in the face of the activated defect when the tests are applied. Such parametric targets and the accompanying design margins vary across domains and chips depending on design and process parameters. The fault coverage, utilized to select the test sets, however quantifies the test quality only in terms of the satisfaction of logical fault detection conditions. Sole fault coverage based test quality assessment subsequently fails to provide an accurate picture of test quality as it overlooks the effect of the parametric attributes in defect detection. Similarly, distinct parametric profiles of chips as a result of process variation lead to an identical test with the same fault coverage delivering distinct test quality for each chip. Consequently, the conventional way of applying a fixed test set, selected by fault coverage based test quality assessment, fails to satisfy the cost and quality goals of VLSI test in the face of the evolving defect behaviors in DSM process modes and the increasing diversification within and across the chips.

The simultaneous demand of satisfactory test quality and low test cost in VLSI test evidently necessitates a paradigm shift from the conventional test techniques. New methodologies are required to assess the effectiveness of fault models and individual test vectors, resulting in the identification of a proper mixture of fault models and test vectors to deliver the desired test quality at a low cost. Furthermore, a variable allocation of the available test resources to each domain and to each individualized chip based on their distinct parametric attributes is necessary to extract the highest test quality, forgoing the long lasting practices of the solely fault coverage based test selection and the application of identical test set to each chip.

The static derivation of test effectiveness and test resource allocation in the process of test cost and quality optimization however imposes inordinate challenges in practice. The design and process parameters effect the occurrence frequency of various defect types and their distribution across chips, subsequently influencing the effectiveness of the fault models and the test vectors. The aforementioned defect characteristics (i.e. the type of defects and their distribution) may shift throughout the production life cycle due to the change in manufacturing environment and process parameters, precluding a static derivation of test effectiveness. Adaptivity is subsequently required in order to learn the effectiveness of the fault models and the test vectors and continuously explore and adjust the test quality and cost tradeoff points as the defect characteristics evolve.

Although adaptive test effectiveness assessment and variable test resource allocation can enable the exploration of the test quality and cost tradeoff and help to extract the highest test quality at a lower cost, they fall short of addressing the pressing issue of the continuously increasing individual test vector cost as a result of the serial access mechanism of scan-based test architecture. The reduction in the cost of each test vector through a test compression method can proportionally provide an immediate relief in the overall test cost and enable test quality improvement within the test cost budget. Naturally, the importance of this particular component of test cost is also steadily growing. The cost of each test vector can be reduced in a scan-based test architecture by decreasing the number of test cycles required to apply a test vector through the serial access mechanism. The number of chip I/O pins used for test access should be limited as well due to the higher cost of testers with a large set of pins. An aggressive test compression technique in scan-based architectures that substantially reduces the number of test application cycles for each pattern while limiting chip I/O usage is subsequently necessary.

In the next section, a detailed overview of the motivation for paradigm shift in testing and the subsequent test strategy and architecture advancements needed for test cost and quality optimization are provided. Constraints and challenges are discussed in Section 1.2. A summary of the thesis is subsequently provided in Section 1.3.

# **1.1 Test Cost and Quality Optimization**

### **1.1.1 Test Effectiveness and Efficiency Exploration**

As the effectiveness of traditional fault models and the corresponding test sets such as stuck-at and IDDQ diminishes in DSM defect detection, the research community and industry alike are shifting their focus to new fault models. While the continuous trend of inclusion of new fault models in the test flow helps to improve test quality, it also frequently results in the inclusion of a significant number of ineffective test vectors in the test flow, reported to be in the range of 70% to 90% [5], at a high test cost yet with no concomitant defect coverage benefit.

The use of simplistic fault models such as stuck-at for test generation efficiency and also due to challenges in modeling and generating targeted tests for all possible defects is one

of the reasons for the inefficiency in the test flows. The lack of a direct correlation between fault models and the actual defects results in the generation of some test vectors with no or insignificant defect coverage. Secondly, defect occurrence rate variation across the chip as a result of design margin variations and systematic process issues implies that some test vectors are more effective than others in defect detection even within a test set generated by a single fault model. The inclusion of multiple fault models further exacerbates the level of inefficiency in the test flows. The manifestation of a defect in possibly multiple distinct ways, coupled with the use of higher level fault models, leads to the detection of the same defect with multiple test vectors from different fault models. The resulting defect coverage overlaps among the fault models and the corresponding test vectors underscores the existence of a significant level of ineffective vectors in the test flows. Furthermore, a non-uniform distribution of various defect types implies that different fault models deliver distinct defect coverage levels, leading to a variation in the defect detection effectiveness of different fault models.

The necessity of tailoring test suites and a test strategy to be *effective* in defect detection (i.e. delivering satisfactory defect escape levels) while performing the job *efficiently* within a short test time (i.e. acceptable test cost) requires an understanding of the effectiveness of test vectors in the test flow and a consequent test effectiveness & efficiency tradeoff. A test effectiveness assessment process needs to quantify the effectiveness of fault models and test vectors while considering the coverage overlaps in defect detection. As the effectiveness of individual fault models diminishes, necessitating in turn the addition of an increasingly larger number of fault models, it can be expected that the sheer number of test vectors with insignificant defect coverage will grow further. A test cost and quality optimization through the assessment of test effectiveness and a subsequent selection of the best test mixture from

various fault models and test vectors promises a tremendous opportunity in delivering an effective yet efficient test suite.

While the derivation of an effective yet efficient test suite through the identification and selection of the effective tests from a variety of fault models is certainly a desirable goal, it faces inordinate challenges in practice. The lack of a direct correlation between fault models and the actual defects, coupled with the dependency of the defect types and their distributions on the variable design and process parameters, severely limits the possibility of a pre-silicon exploration of test cost and quality tradeoff. Furthermore, even if a fault-defect coverage relationship while considering defect coverage overlaps is established based on a limited post-silicon data analysis, the defect characteristics (i.e. the type of defects and their distribution) that play an essential role in the quality of a test set may shift throughout the production life cycle. Process improvements to increase yield, process variation across lots and manufacturing environment and equipment updates are among the main causes of defect characteristics shifts. Consequently, not only test effectiveness assessment and the subsequent test cost and quality exploration should be performed based on the existing defect characteristics but it also should be adaptive as the defect characteristics evolve. This goal necessitates the collection and utilization of real time data from the production test flow and a subsequent dynamic alteration of the test flow, breaking away from the conventional static test flows. Furthermore, the data collection constraints of the production test environment due to the cost and data management challenges, particularly in external test houses, may preclude the availability of full test data. In order to promote a widespread applicability, adaptive test effectiveness assessment and the test cost-quality exploration process in order to deliver an effective yet efficient test flow should be capable of extracting the necessary information from the limited test data.

### **1.1.2 Variable Test Resource Allocation**

While constraining distinct chip designs to an identical test resource would be a highly confounding practice, the idea of subjecting various manufacturing instances of the same design to an identical set is a well-accepted part of conventional test flows. The process variation during manufacturing however results in chips with distinct characteristics, effectively implying the individualization of each manufacturing instance of the same design. Nowhere is this individualization more pronounced than when it comes to delay effects, resulting in chips with distinct timing margins and consequently each chip's vulnerability to random delay defects exhibiting significant variations. The conventional approach of devoting an identical test resource to the highly individualized chips is subsequently starting to fray as the process variation intensifies with each new process node.

Similarly, the higher level of integration enables the coexistence of the hundreds of domains with distinct characteristics in the same chip. In particular, it is not uncommon to have various domain frequencies ranging from very low speeds to GHz levels. The resulting timing margin variations across the domains effectively imply that the domains exhibit variable vulnerability to random delay defects.

While the manifestation of distinct chip and domain characteristics impacts not only timing margins but also other parametric attributes such as power, it is particularly appropriate to focus on an examination of its influence on timing and delay test. Partly, this emphasis is due to the increasing occurrence frequency of subtle delay defects as the unceasing process scaling continues, preventing the operation of the circuit in the target frequencies. Delay testing consequently carries a big burden in delivering high quality chips to the customers, steadily increasing its share in overall test cost. Furthermore, conventional delay test flows are unable to provide a satisfactory answer as to how to effectively test for delay defects. Since the emergence and wide acceptance of fault model based structural testing, fault coverage has been used as a primary metric to assess the quality of the test sets. As the numerous years of experience in structural testing show, fault coverage is indeed an effective metric to measure the test quality for static defects that only require logical activation and propagation of erroneous behavior. However, the increasing importance of parametric attributes such as delay throws into stark relief the limitations of fault coverage based test quality measurements. In order to detect a delay defect for example, not only is it required that a logical fault detection condition be satisfied by generating a transition at the faulty location and propagating it to an observation point, but it is furthermore imperative that the faulty behavior be propagated to an observation point within a time period determined by the target frequency. Evidently, actual signal propagation time depends on path lengths and the additional delay incurred by the delay defect. Although fault coverage considers the satisfaction of the logical detection condition, parametric attributes, such as frequency, path lengths and defect size, that have direct effect on delay test quality, go unnoticed.

Consequently, in an era of pronouncedly individualized chip instances and the hundreds of distinct domains within a chip, the conventional delay test method of applying an identical test set to each chip, determined solely based on fault coverage, fail to satisfy the cost and quality goals of VLSI test. The chips from the slower corners of the process variation space, for example, exhibit diminished timing margins in comparison to the ones from the faster corners, consequently exhibiting reduced tolerance to delay defects. Similarly, the higher frequency domains with smaller timing margins have reduced tolerance to delay defects than the slower frequency domains. Evidently, a variable test resource allocation strategy based on chip and domain characteristics is necessary to optimize test quality while keeping the test cost within acceptable levels.

The major challenges in effective test resource allocation are the estimation of test quality based on chip and domain characteristics and the algorithmic advances necessary to efficiently identify the optimal allocation of available resources in order to extract highest test quality. Furthermore, test architectures of state-of-the-art SOCs support the concurrent testing of the domains, proving an opportunity for a substantial reduction in test cost. The variable resource allocation strategy should therefore be compatible with the concurrent domain testing, identifying in the process the best schedule of the concurrently tested domains while ensuring that test power limits are not exceeded due to an aggressive exploitation of test concurrency.

## **1.1.3 Test Compression**

The higher level of integration continuously boosts the complexity of SOCs by enabling the placement of enhanced functionality into a single chip, increasing test generation complexity as well in the process. Scan-based test architectures have emerged as a widely accepted solution to keep the test generation complexity of SOCs within practical limits. The scan-based test architecture configures the flops of a circuit as shift registers, referred to as scan chains. Consequently, the circuit can be set to any state by serially shifting in the desired values (i.e. test patterns) and the current state of the circuit (i.e. test responses) can be observed by serially shifting out the values of the flops. The enhanced controllability and observability delivered by scan-based test architectures help increase the maximally attainable levels of fault coverage. Furthermore, since all state elements can be controlled and observed, it reduces the complexity of test generation by eliminating the necessity for sequential test generation. However, as a result of the serial access mechanism, test application time is inevitably increased, resulting in elevated test cost. While the aforementioned test effectiveness assessment and variable test resource allocation help to optimize test cost and quality through an effective test selection and a judicious distribution of test resources, the increasing cost of individual test patterns dictated by a scan-based test architecture imposes a strict limitation on the attainable level of test cost and quality optimization. In order to achieve the goal of an effective yet efficient test and to fully enjoy the benefits of scan-based designs, the high test cost of individual patterns needs to be reduced through test compression (commonly referred to as scan compression) in an era where scan-based test architectures has become a *de facto* standard.

In scan-based test architectures, the number of test application cycles for a test pattern is equal to the maximum length of the scan chains. The use of the multiple scan chains, reducing the average scan chain length, emerges as a natural solution for reducing the test application time. Nevertheless, the extra scan I/O pins required by the increased number of scan chains necessitate the use of high cost testers with a large set of pins, precluding the scalability of the utilization of an increasingly larger set of scan I/O pins.

In practice, the scan-based test patterns generally consist of a small number of specified bits, reported to be in the range of 1%-5%. Although the specified bit density of the test patterns is quite low, the traditional scan-based test architecture does not allow the exploitation of this property. The unspecified bits of the test patterns are randomly set and subsequently both the specified and the randomly set bits are serially loaded. The major challenge of test compression in scan-based test architectures is to ensure the usage of a limited set of scan I/O pins while enabling the efficient delivery of the specified bits through the use of a set of reduced length scan chains to alleviate the cost of the serial shift mechanism.

# **1.2** Constraints and Challenges

The delivery of the adaptive test strategy advancements needed for test cost and quality optimization in face of the increasing inefficiencies of the conventional test flow and test architecture as outlined in Section 1.1 requires an answer to the question of how to overcome a number of constraints and challenges. The continuous evolution of defect characteristics is one of the key drivers in the development of advanced test strategies, necessitating an understanding of the classification of the defects and their effect on an adaptive test strategy. The functional constraints of the test flow and test architecture determines the level of flexibility and information available to new test strategies, raising the question of how to deal with these constraints. Finally, a set of algorithmic challenges, partly driven by defect characteristics and functional constraints, needs to be addressed to achieve the goal of adaptive test cost and quality optimization.

### **1.2.1 Defect Clasification**

The characteristics of the defect play a key role in the development of test strategies since the early days of the field of VLSI test. The defects can be random in nature or can have regularity based on design and process parameters. The defects such as a short to the ground that have dominated the defect population in earlier process nodes tend to occur randomly. Parametric defects such as delay defects however depend on design margins and process variation, showing a regularity based on design and process parameters.

Randomness or regularity of a defect type has a profound impact on the development of adaptive test cost and quality optimization strategy. The randomness of a defect type severely limits the possibility of a pre-silicon analysis in the exploration of test cost and quality tradeoff. Since the random nature of defects precludes a ranking of defects based on their criticality, the pre-silicon test generation phase of test strategies naturally aims at providing the highest possible coverage for the target fault models at a high cost. However, despite the randomness of some defect types, not only the occurrence rates of distinct random defects in the manufactured chips differ, but also the multiple test vectors from various test types may cover the same defect, resulting in a distinct effectiveness of each test vector in defect detection. Furthermore, the defect characteristics such as the distribution of defects may shift throughout the production lifecycle due to changes in the manufacturing process and environment as discussed in Section 1.1.1, resulting in a continuous change in test vector effectiveness. Consequently, an adaptive test strategy for random defect types needs to rely on a post-silicon analysis based on the test data collected from the production test flow in order to rank the effectiveness of the test vectors in defect detection and track the subsequent changes in test vector effectiveness based on defect characteristic shifts.

The defect types that exhibit regularity based on process and design parameters however lend themselves to a meticulous analysis during the pre-silicon phase. For example, the susceptibility of each net in the chip to the delay defects can be assessed based on a timing analysis, raising the possibility of a pre-silicon evaluation of test effectiveness to optimize the test cost and quality. Regularity in a defect type subsequently promotes the integration of static information obtained by a pre-silicon analysis in the adaptive test cost and quality optimization process. While an adaptive post-silicon decision making process is still required to obtain process information from the chip under test and to track the process variation changes, a pre-silicon analysis not only significantly reduces the burden of post-silicon analysis but also increases the accuracy and efficiency of the test optimization process.

### **1.2.2 Functional Constraints**

The development of adaptive test strategies driven by the classification of defects as discussed in Section 1.2.1 is heavily influenced by the functional properties and constraints of test flow and test architecture. Since an adaptive test methodology, particularly for random defects, requires an intensive post-silicon data collection, the data gathering constraints of test flow have a profound effect on the test strategy. Similarly, the constraints of the test delivery method dictate the limits of test cost optimization.

Conventional static test flows stop at the first failing test to reduce the cost of test for defective devices. As the testing of multiple chips in parallel becomes a more common practice, the stop-at-failure requirement can be relaxed without incurring significant additional test cost, particularly for high yield products. However, due to cost and challenges associated with collecting and managing full failure information for all failing tests throughout the product lifecycle, particularly in external test houses, it is not uncommon in the industry to bin the failing devices based on the first failing vector, resulting in the collection of only first failing test data for each defective chip. The severely limited test data availability constitutes an enormous obstacle to the post-silicon test data driven adaptive test methodology development, necessitating new techniques to boost the available test data content without incurring a significant test cost. A dynamic adjustment of test flow while still collecting only first failure data provides an opportunity to extract more information from a test flow with no increase whatsoever in test cost. Additionally, a minor expansion of the test data collection with a minimal increase in test cost can open up the possibility of the development of a more accurate and efficient adaptive test method. An adaptive test strategy subsequently needs to answer the question of how to maximize the available information through the use of a dynamic test flow or a minimal expansion of the test data collection.

In addition to test data gathering constraints, the test architecture and methodology imposes test delivery constraints, necessitating the development of test strategies to extract the highest level of test optimization under these constraints. Test architectures can provide capabilities to perform concurrent testing of domains within a chip, presenting an opportunity for a substantial test cost reduction. However, the level of attainable concurrency is constrained by not only an architectural concurrency limit but also a test power limit. Consequently, the maximization of the level of test cost optimization necessitates the development of methodologies to find the optimal schedule of the concurrently tested domains under architectural and power constraints.

As discussed in Section 1.1.3, a conventional scan-based test architecture substantially increases the delivery cost of an individual test vector due to serial access mechanism, setting a hard limit on test cost reduction. Test vectors consist of a large set of unspecified bits, resulting in the use of valuable test resources for the delivery of non-essential test bits. A possible reduction of the highlighted inefficiency in test vector delivery can have a proportional reduction on overall test cost. Subsequently, in order to alleviate a major limitation on test cost optimization, test architecture advancements are required to enable the efficient delivery of test vectors through the reduction of gratuitous test cycles.

### **1.2.3** Algorithmic Challenges

An adaptive test cost and quality optimization methodology development poses a number of algorithmic challenges, partially driven by the defect characterization and functional constraints. Since the defect characteristics shift throughout the production life cycle, the type of the drift has a profound effect on the adaptive test methodology, imposing a set of algorithmic challenges for test effectiveness learning and defect characteristic tracking. In the initial deployment phase of a new process node and during the product ramp-up period, the defect characteristics are exposed to frequent and sharp drifts as a result of frequent tweaking of the manufacturing process parameters in order to increase the manufacturing yield. Once the process matures, the defect characteristics are however mostly stable or very slowly drifting, only infrequently punctuated by sharp changes, primarily from lot to lot.

An adaptive test optimization strategy, particularly for defects that are random in nature, aims at assessing the effectiveness of test vectors based on the gathered test data, extracting the underlying model of test effectiveness. The allowable change in test flow during adaptive optimization to overcome the test data gathering constraints depends considerably on the type of drift, heavily influencing the fidelity of the extracted model of test effectiveness. Mostly stable defect characteristics punctuated by infrequent sharp drifts as observed in mature processes permit a more intensive learning process and aggressive changes in test flow in the process of the extraction of test effectiveness model. Although the model may suffer inaccuracies in the earlier stages of the test effectiveness learning, long stretches of stable defect characteristics provide an opportunity to converge to a stable model of test effectiveness. However, subsequent to the infrequent sharp changes in defect characteristics, much of the previously collected information that is still relevant needs to be retained to prevent the repetition of a lengthy learning process, necessitating an incremental update of the model to reflect the changes and the preservation of the fidelity of the model in the process.

The frequent and sharp drifts in defect characteristics as observed in the product rampup period however do not allow the application of a lengthy learning process as a result of rapidly changing test effectiveness, necessitating a quick test effectiveness learning process at a cost of a sub-optimal test effectiveness assessment. Furthermore, the necessity for preserving the fidelity of the learned test effectiveness model precludes aggressive dynamic changes in the test flow during the learning process due to the frequent drifts in defect characteristics, requiring a relaxation of test data gathering constraints through a slightly expanded test data collection at a minuscule increase in test cost. Consequently, the adaptive test optimization strategy needs to strike a balance between efficiency and effectiveness while ensuring the preservation of the fidelity of the learned test effectiveness model.

A fundamental component of an adaptive test optimization strategy is the method for the tracking of defect characteristic drifts. The type of drifts similarly plays a crucial role in determining the constraints of the tracking method. The stability characteristics of the underlying model of test effectiveness that is learned based on the analysis of the gathered test data is a powerful indicator for defect behavior shift for the type of drifts where infrequent sharp changes follow the long stretches of mostly stable defect characteristics. Subsequently, an efficient and accurate methodology is required to measure and track the stability of the test effectiveness, highlighting sharp fluctuations in the stability characteristics. Frequent and sharp drifts in defect characteristics on the other hand impose distinct challenges. Due to frequent changes in the stability of the underlying model of test effectiveness, a balance needs to be struck between the accuracy of the test effectiveness model and the fast adaptivity to the frequent drifts. The larger the set of test data used for the extraction of the test effectiveness model is, the slower the reaction to the frequent drifts in defect characteristics is. Conversely, the use of a smaller set of test data diminishes the accuracy of test effectiveness analysis.

In sum, adaptive test cost and quality optimization strategy not only needs to be tailored based the different classes of defects as discussed in Section 1.2.1, but also should address the functional constraints and algorithmic challenges as outlined in Sections 1.2.2 and 1.2.3, respectively.

# **1.3 Thesis Summary**

In this thesis, we address the urgent necessity for an effective yet efficient VLSI test process in the intensely competitive semiconductor industry. An adaptive test cost and quality optimization framework consisting of various novel techniques and test architecture advancements is proposed to meet the customer expectations in test quality while bounding the test cost within an economically acceptable level. We question the feasibility of the conventional test flows to deliver the demanding test cost and quality goals as the defect behaviors evolve and as the variation within and across chips increases with each DSM process node, advocating instead a fundamental paradigm shift in VLSI test. Namely, as discussed in Section 1.1, the conventional way of the continuous piling of test vectors from various fault models and the identical application of the resulting test set to all chips with no consideration of chip and domain characteristics fails to satisfy the evolving needs of VLSI test, resulting in an inefficient utilization of test resources and struggling to deliver the acceptable quality goals within the limited test cost budgets. The proposed methods have been tailored to address a broad set of application scenarios through the consideration of different defect classes and defect characteristic drift types while overcoming the data gathering and delivery method constraints and the algorithmic challenges as outlined in Section 1.2.

The proposed techniques capture the criticality of not only fault models and test vectors but also individual chips and frequency domains and, subsequently, exploit the variation in the criticality to deliver an effective yet efficient test through an adaptive selection of most effective vectors and a carefully crafted variable allocation of test resources. Furthermore, a novel scan-based test architecture is proposed to enable a cost-effective application of the resulting test set.

The first set of the proposed methods tackles the challenging goal of the adaptive test effectiveness assessment for particularly the defect types that are random in nature and the subsequent selection of the most efficient test set while dynamically adjusting the test effectiveness information and the resulting test set as the underlying defect characteristics shift as discussed in Section 1.1.1. Since not only the effectiveness of fault models but also the effectiveness of the vectors within a fault model can vary due to the systematic defects and the variations in manufacturing process, an effectiveness assessment at an individual vector level is necessary for an optimal exploration of test cost and quality tradeoff. An adaptive individual test effectiveness assessment methodology that overcomes the data gathering constraints of the conventional test flow by allowing a dynamic re-ordering of test vectors in the test flow is subsequently proposed. The proposed methodology prioritizes the test vectors according to their defect detection effectiveness based on the real time feedback from the production flow. The stability characteristics of test vector order is utilized not only to check the fidelity of the test vector priority information but also to track the defect characteristic drifts, enabling adaptivity to the drifts. A number of algorithmic advances subsequently enables the exploration of test effectiveness and efficiency tradeoff not only at a single test level but also across the multiple test levels through the utilization of the vector priority information as a foundation stone.

While the effectiveness assessment at the individual vector level enables a finegrained optimization, the intensive learning process makes it more suitable for mature processes with infrequent sharp drifts in defect characteristics. In the production ramp-up phase and at the earlier phases of each new process node, frequent and sharp drifts in defect characteristics are observed as the manufacturing process is continuously adjusted to eliminate systematic issues and subsequently improve the yield as discussed in Section 1.2. In order to effectively optimize the test cost and quality for this type of drifts, a test effectiveness assessment methodology that can quickly learn and adjust is crucial, promoting a need for a coarse-grained yet fast fault model level effectiveness assessment methodology while maintaining the fault coverage based vector order within the test set of each fault model in order to ensure the fidelity of the learned test effectiveness information. Subsequently, an adaptive methodology that represents and continuously adjusts test quality as a function of fault coverages of multiple fault models based on the failure information from a small set of recently tested defective chips is proposed. The data gathering constraints of the test flow are slightly relaxed to obtain first failing test information per fault model at a minuscule increase in test cost. The continuously updated representation of test quality as a multi-variate function of fault coverages enables the selection of an optimal mixture from various fault models while quickly adapting to the defect characteristic shifts through the utilization of the failure data from a small sample of recently failed chips. The selection of sample size is carefully orchestrated to address both fast adaptivity and test effectiveness assessment accuracy requirements.

The second set of proposed methods addresses the question of the optimal use of test resources through a carefully crafted allocation of delay test resources based on chip and domain characteristics as discussed in Section 1.1.2. The proposed methods exploit the regularity of the delay defects to incorporate a pre-silicon test effectiveness analysis into the test cost and quality optimization framework. First, a chip-specific test resource allocation method that captures the effect of the individualization of chips on test quality through a pre-silicon statistical analysis of the test quality changes across the process variation space is proposed. An analysis through the use of the resulting statistical test quality model subsequently identifies the test resource allocation for each chip based on its position in the process variation space, enabling an adaptive selection of test resources by extracting process information from the chip under test.

The coexistence of the hundreds of domains with distinct frequencies within the same chip necessitates not only an effective allocation of delay test resources based on domain characteristics to optimize the test quality but also a careful exploitation of the concurrent test support. While concurrent test is capable of delivering substantial test cost reduction, the level of attainable concurrency is bounded by not only the architectural concurrency constraints but also the constraints on simultaneous power utilization. A test resource allocation and domain scheduling method, that simultaneously identifies the best allocation of test resources and the schedule of which domains are to be tested in parallel while complying with architectural and power related concurrency constraints, is subsequently proposed. An optimization formulation as well as efficient algorithms based on convexity and fast concurrent test scheduling techniques through the utilization of test quality estimation based on domain characteristics are provided.

Finally, a novel scan architecture, denoted as *CircularScan*, is proposed to alleviate the test delivery constraints of a conventional scan architecture, reducing the exceedingly high test delivery cost due to the serial access mechanism through the compression of test patterns. The proposed architecture exploits the low specified bit density of scan-based test patterns, enabling a fast application of the specified bits through a circular configuration of scan chains while utilizing only a small set of scan I/O pins. The circular configuration of scan chains enables the use of the captured responses of the previously applied pattern as a template for the subsequent test pattern. A small set of scan I/O pins is utilized as an addressing mechanism to pinpoint and quickly update the positions on the template that conflict with the corresponding specified bits of the next pattern, substantially reducing the test application cycles required to apply a test pattern.

We start the presentation of proposed test cost and quality optimization framework with an overview of the related work in Chapter 2. Chapter 3 presents the adaptive individual test effectiveness assessment and the subsequent effectiveness and efficiency exploration process. The multi-variate test quality tracking as a function of fault coverages and the adaptive selection of the best test mix from multiple fault models is presented in Chapter 4. Chip-specific test resource allocation based on chip characteristics to maximize delay test quality is presented in Chapter 5. The test cost and quality optimization across multiple frequency domains through delay test resource allocation and concurrent test scheduling based on domain characteristics is presented in Chapter 6. The *CircularScan* test architecture for test compression is presented in Chapter 7. Conclusions are drawn in Chapter 8.

# Chapter 2

# **Previous Work**

While the higher level integration and continuous process scaling enables the increasingly complex and high performance designs, the accompanying necessity for rigorous test strategies in order to achieve a satisfactory test quality at an acceptable test cost continuously challenges academia and industry alike to develop innovative test methodologies. The development of new fault models and test generation techniques has become the main vehicle in the test community to improve test quality. Stuck-at tests [6], [7], which assume that each net in the design can permanently get stuck at logic 0 or 1, and IDDQ tests [8], which evaluate whether the steady state current (i.e. quiescent current) of the chip is within the expected level, have been in production test flows for a long time.

Bridging fault model based tests [7], [9], which assume the existence of possible shorts between the nets in the design, are frequently included in test flows, albeit in a limited capacity due to the exceedingly large set of possible bridging fault candidates. Delay tests [10], which target timing related defects, have become an indispensable part of test flows in recent years. The transition fault model [10], [11], which assumes that each net in the design can have a delay defect that effects the timing of rising and falling transitions, and the path delay fault model [12], which specifies the exact paths and tests the cumulative effect of possible delay defects on these paths, are the most commonly used delay test fault models.

Due to the sheer volume of possible paths in a large circuit, only a small set of critical paths can be typically targeted by the path delay test, aiming at identifying the chips at the tail end of the process variation distribution. Transition fault test remains the main test used to target the random delay defects due to its topological coverage of the design and its compact test set size although effectiveness suffers at small delay defect detection as test generation tends to favor short activation and propagation paths.

As the delay defect occurrence frequency exacerbates with continuous process scaling, various new delay test generation techniques have been recently proposed to improve transition delay test quality. Timing-aware delay test methods [13], [14], [15], [16], [17] utilize timing information during test generation to test the faults through the longer paths, increasing small delay defect coverage. Faster-than-at-speed delay test methods [18], [19], [20] run the tests at a speed higher than the target frequency to reduce the timing margins, consequently increasing the small delay defect coverage.

Furthermore, in order to alleviate the issue of the lack of a direct correlation between faults and defects that is inherent in high level fault model usage for test generation, new test generation methods that aim at boosting the likelihood of defect detection have been proposed. N-detect test generation method [21], [22] strives to detect each target fault such as stuck-at and transition multiple times, increasing the possibility of fortuitously activating a possible defect located at the target fault location. Gate-exhaustive test generation [23], [24] aims at exhaustively covering all input states of each cell, boosting the coverage of intra-cell defects.

While the emergence of new fault models and test methods helps to boost test quality, test cost is inevitably increased in face of continuous piling of new test types. Not only the sheer number of test vectors, but also the size of each test vector is continuously growing due to the increasing size of SOCs. The taming of ever increasing test cost has become one of the

focal points of research in the test community. Reductions in the run time of each individual test vector or in total test vector count can yield corresponding reductions in test cost.

Automatic test pattern generation (ATPG) methods [6], [10], that are utilized in fault model based test generation, target a fault and generate an initial test pattern (denoted as a *test cube*) while only specifying the bits required for the fault detection, leaving the majority of the bits unspecified. A subsequent test cube compaction process [6] that aims to reduce the number of test patterns by merging test cubes has been a standard component of ATPG tools for a long time. Test cube compaction methods can be classified as static and dynamic compaction methods. Static test cube compaction [25], [26], [27] commences subsequent to the completion of test generation, merging compatible test cubes and also eliminating the redundant ones. Dynamic test cube compaction [28], [29], [30] is concurrently performed with the test generation process, enabling the generation of test cubes that are compatible with the existing ones and also paving the way for the fault simulation of the merged test cubes during test generation in order to identify the additional faults detected.

In addition to the customary test compaction methods, various techniques have been proposed to tame the test cost. Test compression techniques in scan-based test architectures (referred to as scan compression techniques hereafter) have drawn tremendous attention in the last decade and have shouldered the responsibility of delivering a major reduction in test cost. Static test optimization techniques through various approaches such as effective test generation, test selection and vector ordering continue to emerge at a steady pace. Adaptive test optimization techniques are recently gaining popularity in test cost and quality optimization. An overview of scan compression techniques is provided in the next section. Static test optimization techniques are briefly summarized in Section 2.2. Adaptive test optimization techniques are discussed in Section 2.3.

## 2.1 Scan Compression

Scan test compression techniques came into prominence in the last decade as scanbased test architectures have gained a wide acceptance. Numerous combinational and sequential scan compression methods have been proposed, commercialized by EDA vendors and are commonly used in industry ICs. Research in this area continues to strive for more aggressive scan compression techniques. A survey and a study of the historical evolution of scan test compression techniques can be found in [31], [32].

Scan test compression techniques can be broadly divided into 3 categories; namely, code-based, broadcast-based and linear-decompressor-based schemes [31]. Code-based schemes typically employ off-the-shelf data compression techniques to compress test data. Various compression algorithms such as statistical coding [33], Golomb code [34], Huffman code [35], [36], [37], frequency-directed run-length code [38], [39], nine-coded compression [40] and multi-dimensional pattern run-length code [41] have been explored. These methods exploit the variable occurrence frequencies of test pattern blocks to efficiently compress the test data while the decompression is being performed on chip.

Broadcast-based schemes rely on the concept of broadcasting scan-in data to a larger set of internal scan chains. A single pin is used in [42] to broadcast the test data to multiple scan chains and the remaining undetected faults are tested by reconfiguring the scan chains as a single chain. The use of two different scan chain configurations is proposed in [43] to improve on [42] and a feedback architecture is presented in [44] to eliminate the serial vectors. The methodology in [45] provides multiple broadcast configurations, wherein the configuration can be changed at each test cycle. [46] extends the concept of broadcast to the scan chain segments by constructing tree-shaped scan designs, wherein the scan data is broadcast at each tree node to the branches of the node. Linear-decompressor-based schemes utilize combinational or sequential XOR networks to compress the scan data. Prominent examples of this widely used technique can be found in [47], [48], [49], [50], [51], [52] which use either combinational XOR or sequential LFSR- based networks to encode the test data as a linear combination of input scan data.