## UC Santa Barbara

**UC Santa Barbara Previously Published Works**

## Title

Design, Automation, and Test for Low-Power and Reliable Flexible Electronics

## Permalink

https://escholarship.org/uc/item/1sw9d29x

## Journal

Foundations and Trends® in Electronic Design Automation, 9(2)

**ISSN** 1551-3939

## **Authors**

Huang, Tsung-Ching Huang, Jiun-Lang Cheng, Kwang-Ting

# **Publication Date** 2015

2015

## DOI

10.1561/100000039

Peer reviewed

Foundations and Trends<sup>®</sup> in Electronic Design Automation

Vol. 9, No. 2 (2015) 99–210

© 2015 T.-C. Huang, J.-L. Huang, and K.-T. Cheng DOI: 10.1561/100000039

## Design, Automation, and Test for Low-Power and Reliable Flexible Electronics

Tsung-Ching (Jim) Huang Hewlett-Packard Laboratories, Palo Alto tsung-ching.huang@hp.com

Jiun-Lang Huang National Taiwan University, Taiwan jlhuang@cc.ee.ntu.edu.tw

Kwang-Ting (Tim) Cheng University of California, Santa Barbara timcheng@ece.ucsb.edu

## Contents

| 1 | Intr | oduction                                    | 100 |

|---|------|---------------------------------------------|-----|

|   | 1.1  | Plastic Electronics Revolution              | 101 |

|   | 1.2  | Large-Area Applications                     | 102 |

|   | 1.3  | Differences from Silicon Electronics        | 103 |

|   | 1.4  | Challenges for Circuit and System Design    | 105 |

|   | 1.5  | Summary                                     | 106 |

| 2 | Mai  | nufacturing Methods for Large-Area          |     |

|   | Flex | tible Electronics                           | 107 |

|   | 2.1  | Ink-Jet Printing                            | 108 |

|   | 2.2  | Screen Printing                             | 112 |

|   | 2.3  | Gravure Printing                            | 115 |

|   | 2.4  | Summary                                     | 118 |

| 3 | Thi  | n-Film Transistors                          | 119 |

|   | 3.1  | Hydrogenated Amorphous Silicon (a-Si:H) TFT | 120 |

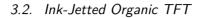

|   | 3.2  | Ink-Jetted Organic TFT                      | 125 |

|   | 3.3  | Self-Assembled-Monolayer (SAM) OTFT         | 130 |

|   | 3.4  | Metal-Oxide TFT                             | 135 |

|   | 3.5  | Impact of Physical Strains                  | 138 |

|   | 3.6  | Summary                                     | 141 |

| 4             | Circ | uit Design                                                                                                                                     | 143          |  |

|---------------|------|------------------------------------------------------------------------------------------------------------------------------------------------|--------------|--|

|               | 4.1  | Digital Circuit                                                                                                                                | 144          |  |

|               | 4.2  | Analog and Mixed-Signal Circuit                                                                                                                | 149          |  |

|               | 4.3  | Summary                                                                                                                                        | 151          |  |

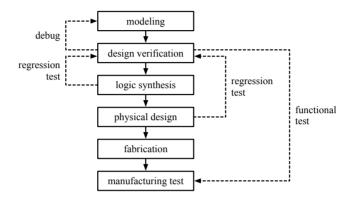

| 5             | Des  | ign Automation and Test                                                                                                                        | 152          |  |

|               | 5.1  | Need of Design and Test Automation                                                                                                             | 153          |  |

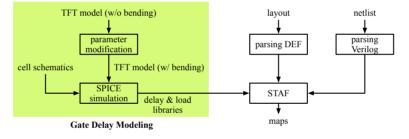

|               | 5.2  | Timing Analysis                                                                                                                                | 155          |  |

|               | 5.3  | Cell Placement                                                                                                                                 | 157          |  |

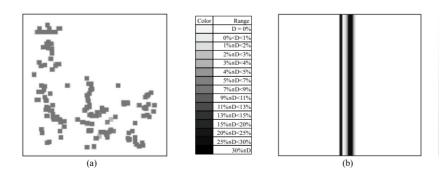

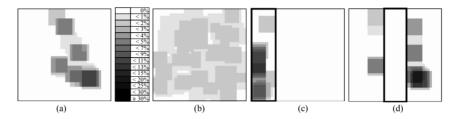

|               | 5.4  | Manufacturing Testing                                                                                                                          | 161          |  |

|               | 5.5  | Yield Optimization for Flexible Analog/Mixed-Signal Circuit                                                                                    | <b>s</b> 164 |  |

|               | 5.6  | Summary                                                                                                                                        | 167          |  |

| 6             | Reli | ability Simulation                                                                                                                             | 168          |  |

|               | 6.1  | Transistor Degradation                                                                                                                         | 169          |  |

|               | 6.2  | Reliability Simulation                                                                                                                         | 174          |  |

|               | 6.3  | Simulation Time Reduction                                                                                                                      | 178          |  |

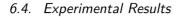

|               | 6.4  | Experimental Results                                                                                                                           | 179          |  |

|               | 6.5  | Summary                                                                                                                                        | 182          |  |

| 7             | Flex | tible Photovoltaics                                                                                                                            | 183          |  |

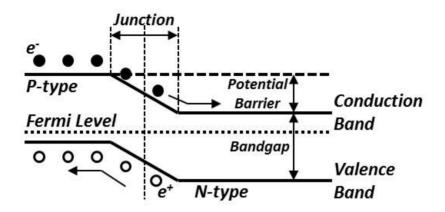

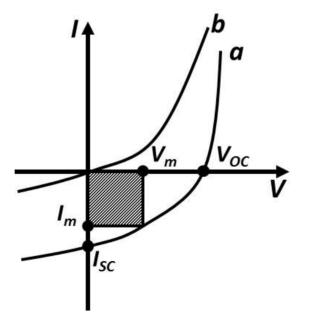

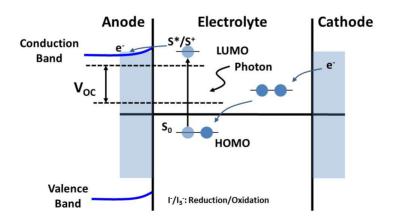

|               | 7.1  | The Basic Principle                                                                                                                            | 184          |  |

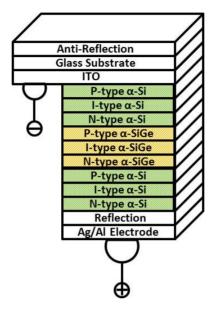

|               | 7.2  | Silicon Solar Cell                                                                                                                             | 185          |  |

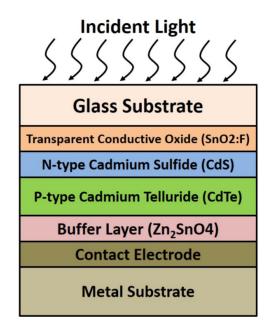

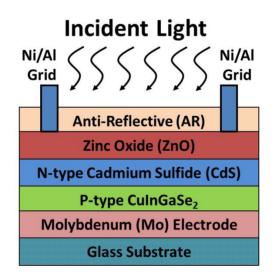

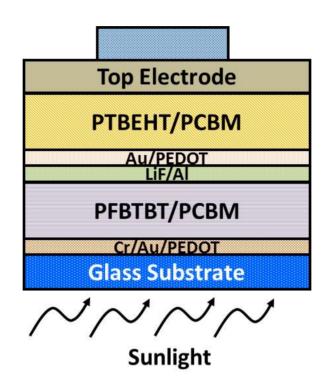

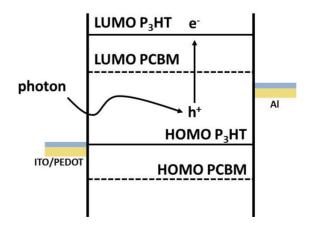

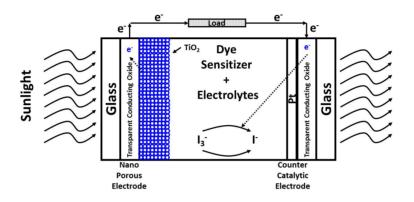

|               | 7.3  | Compound Semiconductor Solar Cell                                                                                                              | 189          |  |

|               | 7.4  | Organic Solar Cell                                                                                                                             | 192          |  |

|               | 7.5  | $Summary \ldots \ldots$ | 195          |  |

| 8             | Con  | clusion                                                                                                                                        | 198          |  |

| References 20 |      |                                                                                                                                                |              |  |

iii

#### Abstract

Flexible electronics are emerging as an alternative to conventional Si electronics for smart sensors, disposable RFID tags, and solar cells. By utilizing inexpensive manufacturing methods such as ink-jet printing and roll-to-roll imprinting, flexible electronics can be made on low-cost plastic films just like printing newspapers. However, the key elements of flexible electronics, thin-film transistors (TFTs), have slower operating speeds and are less reliable than their Si electronics counterparts. Furthermore, TFTs are usually mono-type – either p- or n-type – devices. Making air-stable complementary TFT circuits is very challenging or sometimes not feasible to most TFT technologies. Existing design methodologies for Si electronics, therefore, cannot be directly applied to flexible electronics. Other factors such as high supply voltage, large process variation, and lack of trustworthy device modeling also make designing larger-scale and robust TFT circuits a significant challenge.

The objective of this article is to provide an in-depth overview of flexible electronics from their applications, manufacturing processes, device characteristics, to circuit and system design solutions. We first introduce the low-cost fabrication methods for flexible electronics, including ink-jet printing, screen printing, and gravure printing. The device characteristics and compact modeling of several major TFT technologies will be illustrated. We will then give an overview of digital and analog circuit design from basic logic gates to a microprocessor, as well as design automation tools and methods, for designing flexible electronics. We also describe a reliability simulation framework that can predict TFT circuits' performance degradation under bias-stress. This framework has been validated using the amorphous-silicon (a-Si) TFT scan driver for TFT-LCD displays. Finally, we will give an overview of flexible thin-film photovoltaics using different materials including amorphous silicon, CdTe, CIGS , and organic solar cells.

T.-C. Huang, J.-L. Huang, and K.-T. Cheng. *Design, Automation, and Test for Low-Power and Reliable Flexible Electronics.* Foundations and Trends<sup>®</sup> in Electronic Design Automation, vol. 9, no. 2, pp. 99–210, 2015. DOI: 10.1561/1000000039.

# 1

### Introduction

In 1947, Shockley, Bardeen, and Brattain invented the first transistor at Bell Labs, which opened the era of solid-state electronics. In 1958, Jack Kilby of TI invented the first integrated-circuit (IC) in which he successfully assembled several electronic components to form a miniature circuit. In 1965, Intel co-founder Gordon Moore published a paper in the Electronics magazine which predicted that the number of transistors per IC would double about every two years, later known as the Moore's Law Moore [April 19, 1965]. In 1971, Federico Faggin of Intel successfully demonstrated the world's first microprocessor, Intel 4004, running at a clock rate of 108 KHz with 2,300 transistors in a  $10-\mu m$ pMOS technology. In the last 40 years, we have witnessed the tremendous impact of the IC technology that has brought to the world since its debut. The abundant computing power that comes from faster and cheaper transistors has made our world today very different from what it was 40 years ago. For the future of the semiconductor industry, the ongoing debate has been centered around questions like: "Is the Moore's law going to continue?" and "Will the rigid and disc-like silicon wafer and the printed circuit-board (PCB) continue to be the dominant ways to make electronics for future applications?"

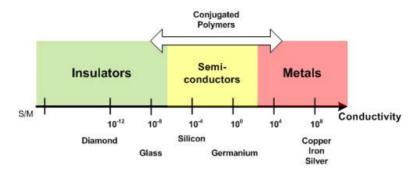

Figure 1.1: Conductivity of conjugated polymers

#### 1.1 Plastic Electronics Revolution

In 1977, 30 years after the first transistor was invented, Heeger, MacDiarmid, and Shirakawa published their discovery of conductive polymer in Shirakawa et al. [1977] and received their Nobel Prize in Chemistry in 2000. Plastic, which is made of polymer, is usually viewed as an insulator and not conductive to electron transportation. In their discovery, however, by proper doping or oxidation, polymers can also be as conductive as metals if the conjugated chains can be properly aligned. The conductivity of polymers is shown in Figure 1.1. This discovery creates alternatives of making electronics, which is not limited to hard and rigid silicon wafers and PCBs. As of today, thousands of semiconducting materials are suitable to make flexible electronics, which brings our imagination of many sci-fi gadgets closer to reality. For example, amorphous-Si, organic and transparent metal-oxide thinfilm transistors (TFTs) are considered promising candidates for flexible electronics. We will give an in-depth overview of TFTs in Chapter 3. Although the carrier mobility of organic materials is still significantly slower  $(10^{-2} \sim 10^{-3} \text{X})$  than that of crystalline and poly-crystalline Si, the steady pace of improvement to their mobility has made organic digital and analog circuits feasible, which can complement to, or may eventually compete with, silicon electronics for certain applications.

#### 1.2 Large-Area Applications

One of the key advantages of flexible electronics is its low manufacturing cost on large-area substrates. Since most organic materials can be converted to a liquid phase, which can be used as functional "inks", manufacturing organic circuits is similar to printing newspapers for which roll-to-roll or ink-jet printing can be used. An overview of the manufacturing methods will be described in Chapter 2. For these lowcost manufacturing methods, several kinds of flexible substrates, such as thin-glass, metal foil, and plastic films, can be used. The manufacturing cost per unit area can be as low as one hundredth of that of silicon electronics. On the other hand, in contrast to silicon electronics that often require sophisticated heterogeneous integration of silicon VLSI chips, discrete passive elements, and ceramic packages on rigid epoxyresin glass fabric printed circuit boards (PCBs), flexible electronics can be made through homogeneous integration of active printed circuits, encapsulation, and thin-film (< 100  $\mu$ m in thickness) substrates, which can be fabricated with a much simpler process and material treatment. This advantage in integration can significantly reduce manufacturing costs. Furthermore, since semiconductor materials for flexible electronics do not require high process temperature and high vacuum that are indispensable for conventional silicon electronics, the energy consumption and the material cost of fabricating flexible electronics are much lower than those for silicon electronics. Sakurai(2007) shows a comparison of cost per unit area between organic and silicon VLSIs indicating that the manufacturing cost of organic ICs is only one hundredth of silicon VLSIs for a 10cm by 10cm area and it can be even lower for high-volume production.

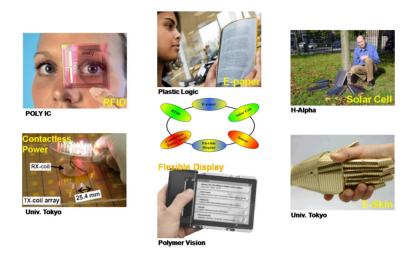

The low manufacturing cost on large-area flexible substrates enables many applications that are not economically practical or mechanically infeasible with conventional silicon electronics. Figure 1.2 shows several applications of flexible electronics, ranging from low-cost RFID tags, flexible displays, artificial skins for robotics, solar cells, to large-area wireless power-sheets. Instead of using multi-billion-dollar foundries for fabrication, electronics for these applications can be mass-produced

#### 1.3. Differences from Silicon Electronics

Figure 1.2: Typical applications of flexible electronics

on large-area flexible substrates using simple printing facilities. This is particularly advantageous for those applications that require fast prototyping, demand customization, or have a small volume such as wearable sensors, disposable biochemical testers as well as personalized healthcare devices. With low capital investment and high flexibility in configuring printing facilities, the manufacturers will be able to easily adjust their production lines as simple as changing the printed contents and quickly deliver new electronic products to meet fast-changing tastes of the consumers.

#### 1.3 Differences from Silicon Electronics

Thin-film transistors (TFTs), the key elements of flexible electronics, can be fabricated using simple process steps (usually less than 5 masks) at a low process temperature on inexpensive flexible substrates such as Polyethylene Terephthalate (PET) plastic films, which help lower the manufacturing costs. An overview of TFT technologies will be described in Chapter 3. Compared with MOSFETs, printed TFTs have larger feature sizes ( $\sim 10^3$ X) due to their low-cost printing processes, which inevitably introduce larger layout-dependent parasitic resistance and

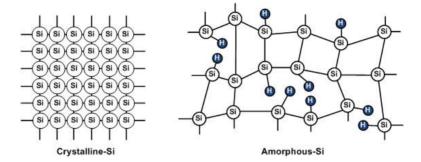

Figure 1.3: Atomic structure of single crystalline-Si and amorphous-Si

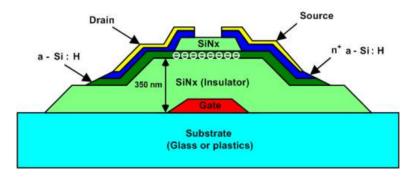

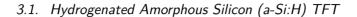

**Figure 1.4:** Device structure of a hydrogenated amorphous silicon (a-Si:H) TFT. (The white circles show that the high density of defects can trap carriers near the semiconductor and insulator interface).

capacitance and therefore limit their operating speeds. On the other hand, although low process temperature can reduce the manufacturing cost and energy consumption, semiconductor materials made with this low process temperature are usually amorphous and have many dangling bonds as illustrated in Figure 1.3. This amorphous atomic structure limits the carrier mobility and causes reliability concerns during the operation because the carriers could be trapped in the dangling bonds and alter the device properties.

#### 1.4 Challenges for Circuit and System Design

In addition to the reliability concerns, the high supply voltage (> 20V)and mono-type device (only either p- or n-type, but not both, is available) also make designing low-power TFT circuits a challenging task. Figure 1.4 shows a typical device structure of a-Si:H TFT, in which the gate insulator material is hundreds-nanometer thick amorphous siliconnitride (a-SiNx). The a-SiNx material has many advantages in manufacturing such as low process temperature, high uniformity across a large area with plasma-enhanced chemical-vapor-deposition (PECVD), and a relatively high dielectric constant ( $\epsilon_r \sim 7$ ). In order to suppress the gate leakage problem, however, the a-SiNx layer needs to be kept sufficiently thick due to its inferior quality to the thermally-grown SiO<sub>2</sub> gate insulator in Si-MOSFET. As a result, a high supply voltage is required. On the other hand, unlike Si-MOSFET, in which the device-type (por n-type) can be determined by doping either p-type (ex. Boron) or n-type (ex. Phosphorus) materials into intrinsic Si, the device-type of TFTs is determined by the majority carrier of the material. For instance, a-Si:H and metal-oxide materials (ex. InGaZnO and ZnO) are n-type, in which the majority carrier is the electron, while most organic materials, including small-molecule and polymer, are p-type and their major carrier is the electron hole. With only mono-type TFTs, the widely-used CMOS design cannot be directly applied to TFT circuit design. This attribute causes many challenges in circuit design for achieving high noise margin and low leakage power which are required for large-scale circuits.

Furthermore, unlike mature single crystalline-Si manufacturing of which the process variation is well-controlled (often less than 5%), process variation of flexible electronics using these low-cost manufacturing methods is very significant. This adds extra challenges for designing flexible circuits and a fabricated circuit could have substantial deviation from its target performance. Other factors such as the processtemperature dependent dimension deformation (ex. shrinking or expanding) of flexible substrates and environmental instability (ex. chemical degradation due to moisture or oxygen contents in the ambient air) also make realizing a robust flexible circuit a very challenging task.

For flexible electronics applications, system-level solutions to build a reliable system based on unreliable devices are equally important to, if not more important than, device- and circuit-level solutions. For example, a system-level solution to electronic textiles (*e*-textiles) was proposed in Park et al. [2002], Marculescu et al. [2003], Stanley-Marbell et al. [2003]. *E*-textiles are computational fabrics that form a largearea, flexible, and conformable information system for both consumer electronics and aerospace/military applications. A *Model of Colloidal Computing* Marculescu and Marculescu [2002] is introduced to provide mechanisms for extracting useful work out of the unreliable elements. Two techniques, *code migration* and *remote execution*, are proposed to provide feasible means of adapting to failures in the presence of redundancy Marculescu et al. [2003], Stanley-Marbell et al. [2003].

#### 1.5 Summary

With rapid advances of flexible semiconducting materials, the performance of TFT circuits has been improving significantly and the concerns of their ambient stability have been alleviated to a great extent in the past few years. After a brief introduction to flexible electronics, this chapter highlights its key difference from silicon electronics, and the challenges and opportunities of circuit design for emerging applications such as wearable electronics, personalized healthcare, and flexible displays. While the main objective of this overview article is on the design, EDA and test issues, we also offer brief technical reviews on TFT technologies, manufacturing methods, and flexible photovoltaics for the purpose of providing a more comprehensive introduction of this emerging field.

## 2

## Manufacturing Methods for Large-Area Flexible Electronics

To realize inexpensive printed circuits on large-area flexible substrates, many patterning techniques that were used to print newspaper can also be good candidates to deposit the functional material (ex. liquid-phase organic semiconductor) onto flexible substrates to pattern desired features. Most of these patterning/printing methods can be used under the room temperature without any vacuum chamber required. To successfully apply these printing techniques for flexible electronics, however, many details in ink preparation such as ink viscosity and surface tension play critical roles in the final quality of the printed circuits. However, discussions of such issues are beyond the scope of this article. In this chapter, we give a brief overview of three different printing methods that are considered promising and suitable for mass-production of large-area flexible electronic circuits. Manufacturing Methods for Large-Area Flexible Electronics

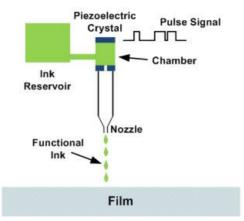

Figure 2.1: The drop-on-demand (DOD) ink-jet printing system

#### 2.1 Ink-Jet Printing

#### 2.1.1 Principle of Operation

An ink-jet printing system used to make flexible electronics is essentially the same as an ink-jet printer used for paper-printing at home or office. The industrial material ink-jet printer today can achieve the precision of and the droplet size of 1 pico-liter(pl). The typical specifications of an industrial-level material printing system is listed in Table 2.1. Similar to a paper-printing ink-jet printer, the material ink-jet printing system is connected to a computer that controls the printer head to move around according to pre-defined patterns. Figure 2.1 shows the typical setting of an ink-jet printing system. There are a wide variety of applicable "inks", ranging from many water-based solvents to liquid-phase gold or silver-nanoparticles that can form the interconnects after a drying process. The piezo-electric crystal (PZT) is a material that can expand or contract depending on the electric potential applied on PZT. In the "droplet-on-demand (DOD)" ink-jet printing system, the droplet can be produced by applying electric pulses to PZT, which will then expand or contract to eject the ink from the chamber through the nozzle hole. The electric pulses are generated

#### 2.1. Ink-Jet Printing

| Ink-Jet Printing System      | Specifications       |  |

|------------------------------|----------------------|--|

| System footprint (mm)        | 650 x 600 x 400      |  |

| Printable area (mm)          | 200 x 320            |  |

| Operation temperature (°C)   | ambient $\sim 60$    |  |

| Cartridge capacity (ml)      | 1.5                  |  |

| Number of nozzles            | $128 \;({\rm max.})$ |  |

| Diameter of nozzle $(\mu m)$ | 20                   |  |

| Droplet size (pl)            | 1 (min.)             |  |

| Precision $(\mu m)$          | $\pm 25$             |  |

| Throughput ( $\mu$ l/s)      | 5                    |  |

Table 2.1: Typical specifications of a material ink-jet printing system Fujifilm [2008]

109

from the computer; therefore, changing the deposited patterns is similar to printing different contents with the paper-printing ink-jet printers. Depending on the hydrophilic property of the substrates and the evaporation rate of the solvents, the deposited patterns will be slightly different from each other. To increase the throughput of an ink-jet printing system, more than one nozzles can operate simultaneously to reduce the printing time. For instance, an industrial ink-jet printing system that is used to produce the color-filters for the TFT-LCD displays has 128 nozzles working together with a precision as high as tens of micro-meters.

#### 2.1.2 Advantages

#### **Additive Process**

Ink-jet printing is an "additive" process, which is different from the "subtracting" process used in silicon electronics manufacturing. For instance, spin-coating is a common technique to deposit the material (ex. photo-resist) on the top of the silicon wafer with good uniformity. During this process, however, only 5% of the material is left on the wafer and 95% of the material is wasted, which inevitably causes the water pollution problem. On the other hand, the ink-jet printing system only

#### Manufacturing Methods for Large-Area Flexible Electronics

deposit a required amount of materials at each target location and the process leaves more than 95% of the materials on the substrates. Such a process not only reduces the manufacturing cost, but also is more environmental friendly.

#### Flexibility

By changing the "inks" in the cartridge, we can deposit virtually any materials required to make flexible circuits. Together with the precision-control on the printed patterns from the computer, every single circuit can be made different from each other if an unique bit-map file is applied. Therefore, it is very suitable for one-time use or for disposable applications such as tickets or a biological tester, which also can be made recyclable after use if we can wash away the deposited patterns.

#### Surface Compatibility

Since the substrates used in this ink-jet printing system do not have interaction with the deposited materials, the applicable substrates can virtually be any surfaces such as low-cost plastics or papers. On the other hand, the printable area can be as small as a business card or as large as a poster. This means that for the same printing system, we can produce a wide variety of circuit or substrate combinations for various applications and obtain a similar printing quality.

#### Scalability to Mass-Production

For an ink-jet printing system, the more nozzles it has, the faster it can produce the printed circuits. As long as the desired pattern for printing can be divided into independent segments, multiple nozzles can deposit simultaneously to complete the desired pattern collaboratively. Furthermore, if different nozzles are linked to different ink cartridges, then different types of inks can be deposited simultaneously at different locations or even mixed together if multiple nozzles deposit inks at

#### 2.1. Ink-Jet Printing

the same location. Therefore, the ink-jet printing system has a good scalability from a laboratory use to mass-production such as the color-filter manufacturing in TFT-LCD business.

#### 2.1.3 Disadvantages

#### **Cross-Contamination**

Since the ink-jetted materials are in the liquid-phase, the materials compatibility between different layers becomes critical to ink-jetted TFT performance. Special care should be taken in order to avoid the chemical reaction between the deposited and subsequent materials. The quality of interface between different functional layers of the TFTs will directly affect the reliability and performance. This could also result in degraded performance (ex. carrier mobility  $\mu$ ) in ink-jetted TFTs.

#### Via-Less Process

In modern VLSI, vias are used to connect different layers of metal wires vertically. To make a via in printed electronics, a material that can etch through the insulating layer without damaging the other layers would be required. By additively ink-jetting the conductive material in a well-controlled manner, a VIA sized by tens of micro-meter in diameter can be created for vertical connection between differen layers. Or alternatively we can use a  $CO_2$  laser to drill through the insulating layer for vias. A via made with these methods, unfortunately, has a poor quality (ex. high resistivity) and a large size. Therefore, it is very challenging to make complex circuits that require many layers of vias.

#### **Coffee-Ring Effect**

The so called "coffee-ring" can be observed in a drying droplet. Instead of leaving a uniform spot, a drying droplet will leave a ring of the solute of deposits on the surface. This phenomenon is known due to the Marangoni flow Hu and G. [2006]. This coffee-ring effect makes

Manufacturing Methods for Large-Area

Flexible Electronics

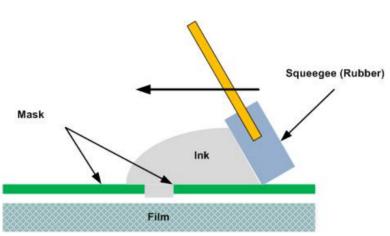

Figure 2.2: A schematic cross-section view of screen printing process

the deposited materials such as conductive polymers non-uniform and leaves uneven edges to subsequent ink-jetted materials. Therefore, the ink-jetted pattern must be carefully designed to make it smooth and straight to avoid non-uniformity due to the coffee-ring effect.

#### 2.2 Screen Printing

112

#### 2.2.1**Principle of Operation**

Figure 2.2 shows the screen printing process that utilizes a "screen" as the mask to define the desired patterns for the material deposition. There are three elements in a screen printing process including: 1) a screen, 2) a squeegee, and 3) the ink. The screen is used to carry the image to the substrate. The squeegee is usually made from polyurethane compound and is used to generate necessary hydrodynamic pressure to transfer the ink flow through the screen. The ink is deposited on the upper surface of the screen before the printing process. During the printing process, the screen is held slightly above the substrates as shown in Figure 2.2, which is known as the off contact gap Claypole [2004]. To print, the squeegee blade is brought down forcing the screen into contact with the substrate. The movement of the squeegee

#### 2.2. Screen Printing

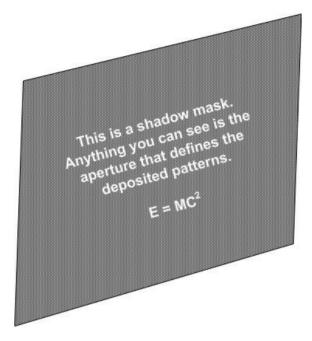

Figure 2.3: A shadow mask for material deposition

over the screen surface forces the ink through the screen onto the substrates. At the end of the printing process, the squeegee blade is raised and returned to its starting position. This technique has been used in manufacturing printed wiring boards (PWBs) for electronic components. A typical shadow mask made of metal foil to define the desired patterns of deposition is shown in Figure 2.3.

### 2.2.2 Advantages

#### Flexibility

The biggest advantage of the screen printing is the flexibility of the process. The screen printing method can be used from a low volume laboratory samples to a high volume industrial production under the clean room conditions. Depending on the resolution of the screen, the screen printing can be used to print the desired patterns down to a

#### Manufacturing Methods for Large-Area Flexible Electronics

micrometer range. The ink films can also range from sub-micrometer to hundreds of micrometer thick.

#### Wide Range of Printable Inks

Unlike other printing techniques that have certain criteria for printable inks, the ink that can be used in the screen printing process has a wide range of viscosity, from 0.5 to 50 poise, compared with 0.01 to 0.012 poise for ink-jet printing (a larger number means more viscous). Therefore, most functional material inks can be used in screen printing with various resolutions and throughput, depending on the screen resolution and ink-viscosity.

#### 2.2.3 Disadvantages

#### Solvent Absorption

Since most squeegees are made from polyurethane compound, it is possible that when the surface of the squeegee is abraded, the organic ink materials can diffuse into the squeegee. This can cause the hardening or softening of the squeegee and affect the printing quality. This problem can be addressed by utilizing a more chemically-resistant polyurethane compound to make the squeegee.

#### Squeegee Bending

Since the squeegee is used to force the ink flow onto the substrates, the rigidity of the squeegee must be able to withstand the hydrodynamic and drag forces imposed on the squeegee. On the other hand, the squeegee must also be sufficiently compliant to absorb the stresses created by the substrates and the screen surface roughness. If excess force is applied to the squeegee, the tip of the squeegee will deform and result in a change in the hydrodynamic pressure and hence ink transfer Claypole [2004]. Various squeegee designs have been developed to enhance the robustness of the squeegee tip for less process variations.

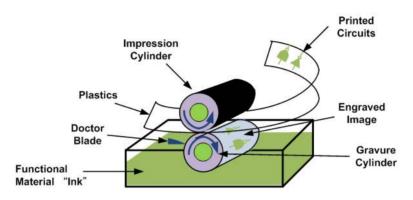

Figure 2.4: A typical gravure printing unit

#### 2.3 Gravure Printing

#### 2.3.1 Principle of Operation

The gravure printing system is comprised of an engraved metal image carrier (an engraved cylinder), a rubber covered impression cylinder, a sharp blade called "doctor blade", and an ink tank.

The system setting is shown as in Figure 2.4. The engraved cylinder is wetted with the ink and the desired pattern or image can be transferred onto the substrate (ex. plastics) by pressing the substrate against the impression cylinder. Before physical impressing, the doctor blade wipes out excess inks from the engraved cylinder and leaves only inks in the recessed image that will then be transferred as desired patterns on the substrates. Since the gravure printing process is more robust compared with other printing processes and can have a very high throughput, it has been widely used in printing magazines, stamps, and folding cartons, etc. The ways to engrave cylinders to create desired patterns/images include: 1) chemical etching, 2) electromechanical engraving, and 3) laser engraving. Among these engraving methods, electromechanical engraving is the most commonly used and the laser engraving has the fastest engraving speed (~10X) of any other engraving methods.

### Manufacturing Methods for Large-Area Flexible Electronics

| Gravure Printing                          | Specifications         |  |

|-------------------------------------------|------------------------|--|

| Film thickness $(\mu m)$                  | 30                     |  |

| Minimum line resolution $(\mu m)$         | 50 (typical)           |  |

| Ink viscosity (Pa.s)                      | $0.05 \sim 0.20$       |  |

| Substrates                                | Paper, board, plastics |  |

| Speed (fpm)                               | Up to 3,000            |  |

| Cost of gravure press (USD)               | > \$150,000            |  |

| Cost of gravure cylinder (USD)            | $1,000 \sim 10,000$    |  |

| Typical registration tolerances $(\mu m)$ | $\pm 50$               |  |

Table 2.2: Typical specifications of a gravure printing system Brollier [2004]

#### 2.3.2 Advantages

116

#### **Consistency and High Quality**

Since the gravure printing process is accomplished in a fashion that only the cylinder rotation is the required movement, the printing quality can be easily controlled and the consistency can also be guaranteed. This advantage makes gravure printing robust to variations in surface roughness and ink viscosity and is suitable for mass production.

#### **High Throughput**

Table 2.2 shows the typical specifications of a gravure printing system. The speed of printing can be up to 3,000 films per minute (fpm), compared with a single digit for an ink-jet printing system ( $\sim 5 fpm$ ).

#### 2.3.3 Disadvantages

#### **High Capital Investment**

As shown in Table 2.2, the capital investment for an industrial-level gravure printing press is high. To fill each ink reservoir for a larger gravure printing unit requires 20-30 gallons of inks. For expensive ma-

#### 2.3. Gravure Printing

terials, this will be a considerable amount of costs. In addition to the ink cost, the cost of engraving cylinders is not cheap (>\$1,000) which will be a significant factor for applications that require frequent updates of the contents.

#### Inflexibility

The gravure printing can only be used in high-volume printing because the preparation process before printing such as ink-filling, cylinder engraving, and substrate registration incurs a considerable amount of time and cost. Therefore, gravure printing is not suitable for experimental samples that usually will require frequent changes of the inks and engraved images.

#### **Difficulty in Large-Area Printing**

For printing a larger-size image/pattern onto the substrate, the cylinder must be engraved accordingly. The current engraving techniques such as chemical etching and electromechanical engraving, however, are unable to make a large-size image while maintaining the resolution. These patterns, therefore, must be divided into smaller cells and assembled later when applied to the engraving cylinder. These assembled patterns, unfortunately, are usually not continuous. This is fine if only a coarse resolution is required such as wiring in a printed circuit. To print a fine structure of transistors, however, the un-even edges and not-so-straight lines could induce large variations among transistors.

#### **Cross-Contamination**

Since the printing of transistors requires many layers that are comprised of several different functional layers, the same substrate will then pass through several different gravure printing units in which the inks are different. During the printing process, the substrates and the engraving cylinders will have physical contact and one functional material is likely to be carried through this mechanism to another ink

#### Manufacturing Methods for Large-Area Flexible Electronics

reservoir. This causes the cross-contamination problem between different ink reservoirs. If the purity of the materials affects the performance of the transistors, such as organic semiconducting materials, then this cross-contamination can cause detrimental effects to the manufactured transistors.

### 2.4 Summary

This chapter introduces three types of low-cost patterning methods on large-area flexible substrates. Each of these methods has its advantages and limitations, and thus the best choice depends on the target applications. For rapid prototyping of early-stage products or laboratory samples, ink-jet printing and screen printing are viable solutions with the advantages of low-cost and flexibility. For mass production, ink-jet printing is limited by the number of nozzles that can work collaboratively, which in turn limits its throughput to a single digit of films per minute (fpm). Screen printing can achieve a greater throughput but the pattern resolution is usually limited by the shadow mask. It is challenging to make fine features (<10  $\mu$ m) with screen printing. On the other hand, gravure printing can achieve a much greater throughput (ex. >1000 fpm) but with little flexibility for minor adjustment. It is therefore most suitable for mass-production of high-volume products such as RFID tags and flexible displays.

## 3

### **Thin-Film Transistors**

Thin-film transistors (TFTs) first appeared in 1960s Weimer [1962] and competed with the single crystalline-Si MOSFET. Due to the rapid advancement in MOSFET and the difficulty in consistently producing high-quality TFTs, TFTs were not a serious contender for integrated circuits at that time. However, the research on TFTs for displays was never stopped. With tremendous improvement of large-area manufacturing of TFTs in 1980s and 1990s, the hydrogenated amorphous silicon (a-Si:H) TFTs began to be widely used for mass-producing the pixels of liquid-crystal (LC) displays Luo [1981], Matsuura et al. [1982]. Besides a-Si:H TFTs, research on various kinds of TFTs has revived recently because of the strong demand on thin-film, low-cost and flexible applications in consumer electronics. With the advancement of organic materials and printing technologies, low-cost large-area printing techniques as stated in Chapter 2 can be used to manufacture TFTs as alternatives to the standard clean-room manufacturing. The key features of major types of TFTs are revisited in Table 3.1.

Thin-Film Transistors

| Device type (TFT)      | a-Si:H                       | Metal-Oxide                  | Organic        |

|------------------------|------------------------------|------------------------------|----------------|

| Process temperature    | $\sim 200^{\circ}\mathrm{C}$ | $\sim 150^{\circ}\mathrm{C}$ | Room temp.     |

| Process technology     | lithography                  | roll-to-roll(r2r)            | r2r & ink-jet  |

| Minimum size $(\mu m)$ | 10                           | 8                            | 50             |

| Substrates             | glass/plastics               | wafer/plastics               | wafer/plastics |

| Device type            | N-type                       | N-type                       | P-type         |

| Supply voltage (V)     | 20                           | 20                           | 40             |

| Mobility $(cm^2/Vs)$   | 1                            | 10                           | 0.5            |

Table 3.1: Comparison between different TFT technologies

### 3.1 Hydrogenated Amorphous Silicon (a-Si:H) TFT

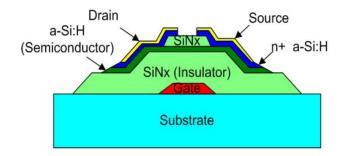

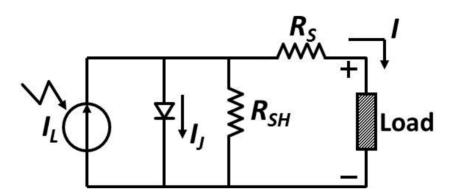

The device structure of a-Si:H TFTs is shown in Figure 3.1. The gate is located at the bottom because of the consideration of structural compatibility for TFT-LCD displays. The a-Si:H TFT behaves as a parallel plate capacitor in which the carriers (electrons) are accumulated by applying positive gate voltage  $V_{GS}$  to the gate terminal. The conduction current between source and drain metals is dependent of the applied gate voltage  $V_{GS}$ . Since the negative charges are accumulated close to the gate terminal (at the bottom side of a-Si:H layer), the carriers need to flow through the vertical thickness of the a-Si:H layer to form a conduction channel between source and drain terminals. This inevitably increases the channel resistance and lowers the conduction current, in comparison with the crystalline MOSFET. Figure 3.2 Servati and Nathan [2002] shows a typical relationship between the drain current  $(I_D)$  in the log scale and the applied gate voltage  $(V_{GS})$ . For the gate dielectrics, since the high process temperature to grow a good quality  $SiO_2$  layer exceeds the glass transition temperature  $T_q$ , the gate dielectric layer  $(SiN_x)$  is usually deposited using plasma-enhanced chemical-vapor-deposition (PECVD). This dielectric layer has many defects that can trap charges particularly near the interface between the a-Si:H and SiNx layers, which causes the reliability concerns that will be discussed in a later section.

Figure 3.1: A typical bottom gate structure of a-Si:H TFTs

Figure 3.2: Log-scale plot of drain current versus gate voltage Servati and Nathan [2002]

Thin-Film Transistors

#### 3.1.1 Device Basics

#### 3.1.2 Device Manufacturing

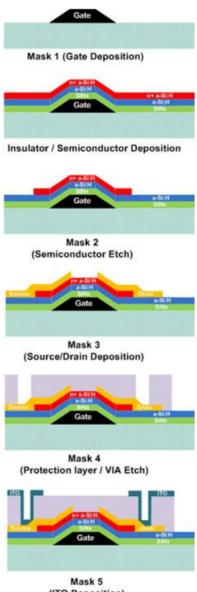

Figure 3.3 shows a 5-mask fabrication process of a typical bottom gate a-Si:H TFT. Mask 1 is used to define the gate metal made of tungsten molybdate (MoW). After the gate metal deposition, the insulator (SiNx) is then deposited using plasma-enhanced chemical-vapordeposition (PEVCD) because of its fast deposition speed and no requirement for high vacuum and process temperature. SiNx is also a passivation material that is not active to many chemical solvents used in the process. The semiconductor a-Si:H is then deposited using mask 2 on top of the insulator SiNx layer and then the heavily doped n-type a-Si:H layer with PECVD. The purpose of this heavily doped a-Si:H layer to form an ohmic contact between the semiconductor a-Si:H layer and the source/drain contacts. The source/drain metal layer made of Al-Nd is deposited using mask 3. Finally SiNx is deposited again on top of the source/drain metal layer as a protection layer. For driving display pixels, another layer of transparent metal made of Indium-Tin-Oxide (ITO) will be deposited as the last layer using mask 5. The details of TFT-LCD displays manufacturing can be found elsewhere (ex. Kagan and Andry [2003], Kuo [2004], Tai [2006]).

#### 3.1.3 Device Modeling

The drain-source current  $I_{DS}$  of a-Si:H TFTs can be recognized to have four regimes depending on the bias: above threshold, forward subthreshold, reverse subthreshold, and front subthreshold (Poole-Frenkel) as shown in Figure 3.2. The details of these different operation regimes can be found in Servati and Nathan [2002]. In the above-threshold regime, when  $V_{DS} < \alpha_{sat}(V_{GS} - V_{TH})$ , the TFT operates in the linear region, in which  $I_{DS}$  depends on the both  $V_{GS}$  and  $V_{DS}$ . On the other hand, when  $V_{DS} \ge \alpha_{sat}(V_{GS} - V_{TH})$ , the TFT operates in the saturation region in which the mobile carriers at the drain side of the channel reduces to zero (the pinch-off condition). The equation for above-

(ITO Deposition)

Figure 3.3: A typical 5-mask fabrication steps of a-Si:H TFTs

Thin-Film Transistors

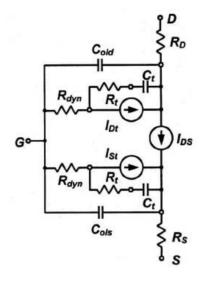

Figure 3.4: An equivalent model for a-Si:H TFTs Servati and Nathan [2002]

threshold linear and saturation regions can be found in Equations 3.1 and 3.2. A complete a-Si:H TFT model for both static and dynamic characteristics is shown in Figure 3.4. In this model,  $R_S$  and  $R_D$  are used to model the contact resistance of S/D contacts and the series resistance of the conduction channel. Other capacitance and resistance are responsible for a-Si:H TFT's dynamic characteristics.

$$I_{DS} = \left\{ \mu_{FET} C_i \frac{W}{L} \left( V_{GS} - V_{TH} - \frac{V_{DS}}{2\alpha_{sat}} \right) \cdot V_{DS} \right\}$$

(3.1)

when  $V_{DS} < \alpha_{sat}(V_{GS} - V_{TH})$

$$I_{DS} = \left\{ \mu_{FET} C_i \frac{W}{L} \left( V_{GS} - V_{TH} \right)^2 \cdot \frac{\alpha_{sat}}{2} \right\}$$

$$when \quad V_{DS} \ge \alpha_{sat} (V_{GS} - V_{TH})$$

$$(3.2)$$

where  $\mu_{FET}$  is the field effect mobility,  $C_i$  is the gate insulator capacitance per unit area,  $V_{TH}$  is the threshold voltage, and  $\alpha_{sat}$  is the saturation parameter, typically  $\alpha < 1$ .

#### 3.2. Ink-Jetted Organic TFT

#### 3.1.4 Degradation Mechanism

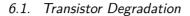

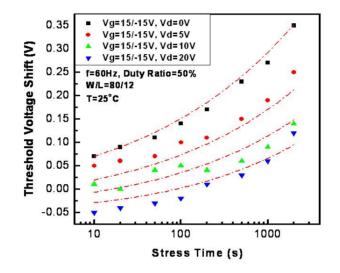

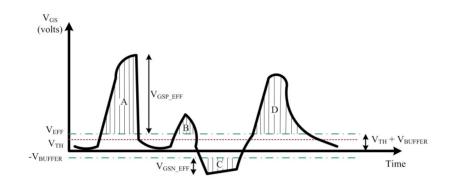

Unlike crystalline-Si MOSFETs, a-Si:H TFTs exhibit a bias-induced metastability phenomenon that causes both threshold voltage  $(V_{TH})$ and subthreshold slope (S.S.) to change over time Powell [1983], Jackson and Moyer [1987]. There are two mechanisms that are responsible for this electrical instability. First is carrier trapping in the gate insulator SiNx layer. This is due to the high density of defects of the PECVDgrown SiNx layer in which the charges are easily trapped when the gate undergoes a bias-stress. The charges are initially trapped within the interfacial states at the a-Si:H/a-SiNx:H boundary and then thermalize to deeper energy states inside the insulator layer. Another mechanism responsible for this electrical instability is point defect creation in the a-Si:H layer or at the a-Si:H/a-SiNx:H interfaces. The defects are created when weak silicon-silicon bonds break into silicon dangling bonds in the presence of a bias-stress. This phenomenon is similar to photogenerated carriers that result in dangling-bond creations Kuo [2004], Stutzmann et al. [1985]. Both mechanisms cause a positive shift in the threshold voltage ( $\Delta V_{TH}$ ). The charge-trapping mechanism manifests itself in high gate bias-voltages and long stress times while defect state creation happens at lower stress voltages and shorter stress time.

### 3.2 Ink-Jetted Organic TFT

#### 3.2.1 Device Basics

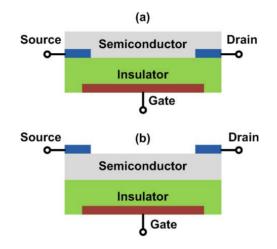

The device structures of an organic TFT (OTFT) have several variants as shown in Figure 3.5. Because the organic semiconducting material is much more fragile than the insulating material, it is easier to deposit the semiconductor layer on top of the insulator layer than the converse Klauk [2006]. In the bottom contact structure, the S/D contacts are deposited on top of the insulator. Since the conduction channel is formed at the bottom side of the semiconductor layer, which is closer to the S/D contacts, the contact resistance is usually less than the that of top contact structure as shown in Figure 3.5. On the other hand, in

Figure 3.5: A schematic view of the structure of organic TFTs. (a)Bottom Contact; (b)Top Contact.

the top contact structure, the S/D contacts are deposited on top of the semiconductor layer, which inevitably causes larger contact resistance between the source and drain terminals. The merit of this structure is a cleaner interface between the organic semiconductor layer and the insulator layer, which helps improve the alignment of the organic molecules of the semiconductor layer for better conductivity and carrier mobility.

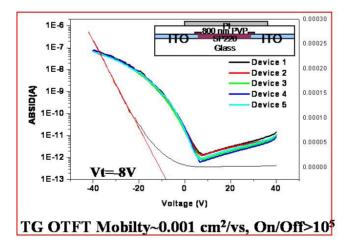

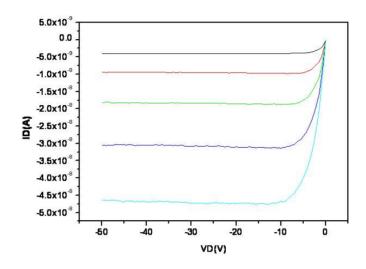

Many low-cost printing methods such as ink-jet printing can be used to fabricate organic TFTs. The device structure of an ink-jetted organic TFT (OTFT) is shown in Figure 3.6. The typical drain current  $I_{DS}$ versus gate voltages of an ink-jetted organic TFT (OTFT) can be found in Figure 3.7 and the  $I_{DS}$  versus drain voltages plot is also shown in Figure 3.8. Although the charge transport mechanism of organic TFTs is still under active research, a popular model has been proposed by Vissenberg and Matters Vissenberg and Matters [1998]. They assume that the variable range hopping in an exponential distribution of traps is the major mechanism of charge transport in the organic semiconductor. This model explains the well-known mobility dependence on the gate voltages for organic TFTs. When the gate voltage increases, the injected charge-carriers fill more traps in the semiconductor that makes the charge-trapping less efficient and improves the charge transport.

126

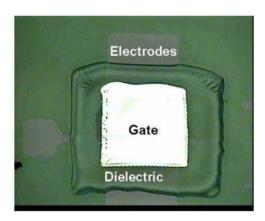

Figure 3.6: A device photo of an ink-jetted OTFT (photo courtesy of ITRI-FETD)

**Figure 3.7:** A log scale plot of drain current  $I_{DS}$  versus gate voltage  $V_{GS}$  of a inkjetted OTFT. In this figure top-gate structure is used. Pt is for GATE contact and ITO is for SOURCE and DRAIN metal contacts. SP220 is a commercially available organic semiconducting material. (courtesy of ITRI-FETD)

Thin-Film Transistors

**Figure 3.8:** A linear scale plot of drain current  $I_{DS}$  versus drain-source voltage  $V_{DS}$  of a ink-jetted OTFT (courtesy of ITRI-FETD)

#### 3.2.2 Device Manufacturing

Ink-jet printing is considered as a promising candidate for manufacturing organic TFTs and has been used for making organic light-emitting diodes (OLEDs) Hebner et al. [1998] and full-color displays Yokoyama [2003]. In this particular ink-jetted OTFT, the device is accomplished by using a material ink-jet printer, which can achieve a 20um resolution, to deposit different functional and liquid-phase "inks" on the desired locations. Due to the high sensitivity of the semiconducting material (ex. SP220) to the ambient air (ex. oxygen and water vapor), the top-gate structure is applied in which the gate dielectrics will be deposited on top of the semiconductor layer and form a protection layer to prevent the semiconductor layer from exposing to the ambient air. Since most soluble materials for ink-jet printing is polymers and the complete inkjet printing process is accomplished under the room-temperature, the semiconducting material is usually amorphous and has lower carrier mobility (  $0.001 \ cm^2/vs$ ) than small-molecule organic materials.

#### 3.2. Ink-Jetted Organic TFT

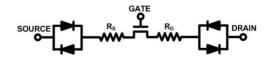

Figure 3.9: An equivalent circuit model of organic TFTs.  $R_S$  and  $R_D$  are used to model contact resistance and the diode-pairs are for non-linearity of contact resistance.

#### 3.2.3 Device Modeling

Figure 3.9 shows the equivalent circuit model of organic TFTs, in which only DC model is shown here. Similar to a-Si:H TFTs, the organic TFTs can be modeled as a parallel plate capacitor that accumulates holes (p-type) as charge carriers. The device model of organic TFTs can be described using the percolation model Vissenberg and Matters [1998]for charge transport in the accumulation channel. Equation 3.3 describes the drain current  $I_{DS}$  in the saturation region when  $|V_D| > |V_G - V_T|$ while Equation 3.4 describes the drain current in the sub-threshold region when  $|V_G - V_T| \sim 0$ V Klauk [2006].

$$I_{DS}^{acc,1} = -\frac{\mu_0 W C_i}{L(2+\gamma)} [[[-V_G + V_T]]^{2+\gamma} - [[-V_G + V_T + V_D]]^{2+\gamma}]$$

$$I_{DS}^{acc,2} = I_{DS}^{acc,1} \cdot min \left(1 + \kappa [[V_D]], 1 + \kappa [[-V_G + V_T]]\right)$$

$$I_{DS}^{acc,total} = I_{DS}^{acc,2} + \lambda \frac{W^{\frac{1}{3}}}{L} \left([[V_G - V_T - V_D]] \cdot |I_{DS}^{acc,2}|_{V_D} = V_G - V_T\right)^{\frac{2}{3}}$$

(3.3)

$$I_{DS}^{sub} = I_0 |V_D|^{\sigma} \cdot exp \left[ \frac{ln10}{S} [[V_G - V_T]] \right]$$

(3.4)

where  $\mu_0$  is the carrier mobility,  $C_i$  is the gate capacitance, W is the gate width, L is the gate length,  $\gamma$  is the mobility exponent,  $\kappa$  is the linear correction parameter,  $\lambda$  is the channel-shortening term, S is the inverse subthreshold slope, and  $I_0$  and  $\sigma$  are fitting terms.

#### Thin-Film Transistors

#### 3.2.4 Degradation Mechanism

There are two major instability mechanisms – electrical and chemical instabilities – that can cause the device characteristics to shift over time. Oxygen, for instance, is the major cause of chemical instability. Oxygen is suggested as a dopant for a variety of semiconducting polymers such as P3HT and PQT-12 and will interact with the semiconductor materials to change their properties. Encapsulation methods to prevent semiconducting polymers from exposing to the ambient air are available and proven useful to extend the shelf-lifetime of polymeric TFTs in practical applications. The chemical instability, therefore, seems to be a solvable problem.

On the other hand, the electrical instability caused by bias-stress is much harder to get rid of. In most organic TFTs, which are p-channel accumulation devices, negative shifts of threshold voltage ( $\Delta V_{TH}$ ) can be observed after applying negative gate voltages (i.e. bias-stress) to TFTs. Charge-trapping is the major mechanism to be responsible for this phenomenon and is proportional to  $C_{OX}|V_G - V_T|$ . Chargetrapping can happen in the gate dielectric, in the localized states at the semiconductor-dielectric interface, or in the deep states in the semiconductor. These immobilized charges shield the gate voltages to accumulate mobile charges and hence reduce the conduction currents Salleo and Street [2003]. An analytical model of the threshold voltage shift of PQT-12 polymeric TFTs is shown in Equation 3.5.

$$|\Delta V_T| = A(V_G - V_T^0)^n \cdot t^\gamma \tag{3.5}$$

where A, n, and  $\gamma$  are fitting parameters,  $V_T^0$  represents the initial threshold voltage of the TFT, and t is the bias-stress time.

#### 3.3 Self-Assembled-Monolayer (SAM) OTFT

#### 3.3.1 Device Basics

The high operation voltage is one of the major challenges for organic TFTs. To explore a low-voltage operation capability, a research group in University of Tokyo has demonstrated 2V organic TFTs that can share

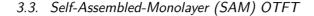

Figure 3.10: A schematic sideview of a 2V SAM OTFT. (photo courtesy of Someya group, Univ. of Tokyo)

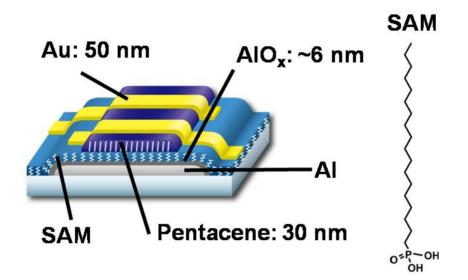

the same voltage source with the 0.18um CMOS ICs Ishida et al. [2009]. Self-assembled-monolayer (SAM) dielectric is an organic solution that can help form a good quality semiconductor-dielectric interface for organic TFTs. With SAM-modified gate dielectrics, the gate leakage can be improved significantly, which opens the opportunity of using thin dielectric layers. As shown in Figure 3.10, a thin layer (~6nm) of thermally-grown aluminum-oxide  $AlO_X$  is applied as the gate dielectric and the interfacial control is accomplished by immersing the whole substrate into the SAM solution to form a thin SAM layer. The airstable organic semiconductor *Pentacene* is then thermally-evaporated on top of the SAM-modified dielectric layer. This thin-layer gate dielectric enables a low-voltage operation (~2V) without introducing the gate leakage problem. Figure 3.11 shows a typical multi-finger SAM OTFT that is used to build integrated circuits that will be discussed in Chapter 4.

Thin-Film Transistors

**Figure 3.11:** A device photo of a 2V SAM OTFT with multiple fingers. Center yellow part is the GATE metal, orange part is semiconductor Pentacene, and yellow fingers on the two sides are S/D metals. (photo courtesy of Someya group, Univ. of Tokyo)

# 3.3.2 Device Modeling

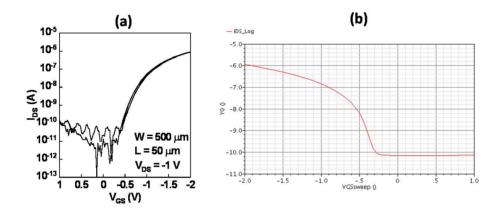

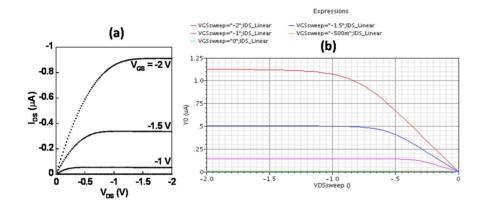

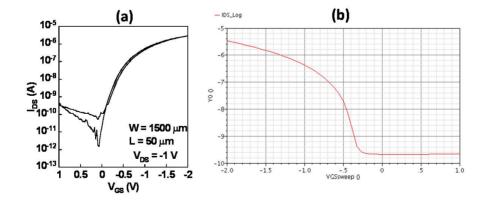

To perform circuit simulation for SAM-OTFT based circuits, Verilog-A based device models have been developed that can be integrated into major circuit simulators such as *HSPICE* and *Cadence Virtuoso*. The model is evolved from the model of field-effect transistors and has taken into account the carrier mobility dependence on the gate voltage  $V_{GS}$ . The comparison of  $I_{DS}$  and  $V_{GS}$  relationship between measurement and simulation can be found in Figure 3.12. Likewise, the  $I_{DS}$  and  $V_{GS}$  relationship can also be found in in Figure 3.13. To examine the model for multiple-finger devices, larger-size SAM OTFTs (W = 1500 um) are also used for comparison and can be seen in Figures 3.14 and 3.15. The mobility dependence on the gate overdrive voltage ( $V_{GS} - V_T$ ) is described in Equation 3.6 and the saturation drain-source current  $I_{SAT}$  is shown in Equation 3.7. Similar to silicon field-effect transistors, in the overdrive voltage but is independent of the drain-

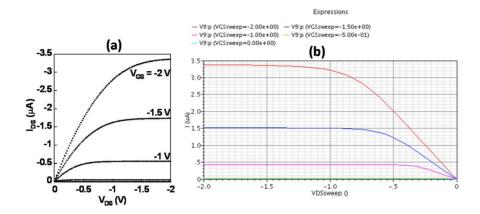

**Figure 3.12:** (a) A log scale plot of drain current  $I_{DS}$  versus gate voltage  $V_{GS}$  of a 2V SAM OTFT.(courtesy of Someya group, Univ. of Tokyo);(b) ID-VGS SAM OTFT device model using verilog-A.

source voltage  $V_{DS}$ . In the linear region, the drain-source current  $I_{DS}$  is dependent on  $V_{DS}$  as can be seen in Equation 3.8.

$$\mu = \mu_0 \cdot |V_{GS} - V_T|^{\gamma}$$

$$V_{GTE} = \frac{S}{2} \left| 1 + \frac{V_{GS} - V_T}{S} + \sqrt{\delta^2 + \left(\frac{V_{GS} - V_T}{S} + 1\right)^2} \right|$$

$$I_{SAT} = \frac{1}{2} \mu C_{ox} \frac{W}{L} V_{GTE}^{2+\gamma}$$

(3.6)

(3.7)

$$V_{DSE} = \left[1 + \left(\frac{\mu C_{ox} \frac{W}{L} \cdot V_{DS}}{I_{SAT}}\right)^{\alpha}\right]^{\frac{1}{\alpha}}$$

$$I_{DS} = \mu C_{ox} \frac{W}{L} V_{GTE}^{1+\gamma} \cdot \left(1 + \frac{\lambda V_{DS}}{V_{DSE}}\right) \cdot V_{DS}$$

(3.8)

where  $V_{GTE}$  is the  $V_{GS}$  smoothing function, S,  $\delta$ , and  $\alpha$  are fitting parameters,  $\mu_0$  is the mobility pre-factor,  $\gamma$  is the mobility exponent,  $C_{ox}$  is the gate capacitance, and  $\lambda$  is the channel-shortening term.

Thin-Film Transistors

**Figure 3.13:** (a) A linear scale plot of drain current  $I_{DS}$  versus drain-source voltage  $V_{DS}$  of a 2V SAM OTFT (courtesy of Someya group, Univ. of Tokyo); (b)ID-VDS SAM OTFT device model using verilog-A.

**Figure 3.14:** (a) A log scale plot of drain current  $I_{DS}$  versus gate voltage  $V_{GS}$  of a 2V SAM OTFT (W=1500 um).(courtesy of Someya group, Univ. of Tokyo);(b) ID-VGS SAM OTFT device model using verilog-A.

**Figure 3.15:** (a) A linear scale plot of drain current  $I_{DS}$  versus drain-source voltage  $V_{DS}$  of a 2V SAM OTFT (W=1500 um). (courtesy of Someya group, Univ. of Tokyo); (b)ID-VDS SAM OTFT device model using verilog-A.

# 3.4 Metal-Oxide TFT

## 3.4.1 Device Basics

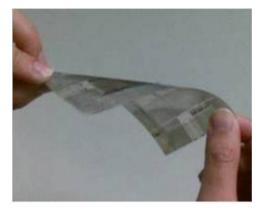

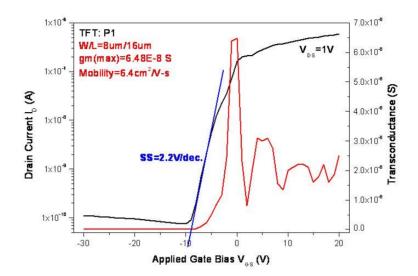

Figure 3.16 shows IGZO TFTs on low-cost flexible substrates such as polyimide plastics. Metal-oxide TFTs such as IGO TFTs are emerging as a promising candidate in replacement of a-Si:H TFTs in display and imaging applications because of the following reasons: 1) higher carrier mobility, 2) better transparency, and 3) better reliability. Metal oxide TFTs have higher carrier mobility ( $\sim 10 \text{ cm}^2/\text{Vs}$ ) than a-Si:H TFTs  $(\sim 1 \text{ cm}^2/\text{Vs})$ . This means that as a pixel switch, it can switch faster to provide a better quality of dynamic images or videos than conventional a-Si:H TFT-LCDs. It can also provides higher conduction current to support future-generation organic LED (OLED) displays that usually need a higher driving current to provide a better contrast ratio and dynamic response than conventional LCD displays. Thanks to the wide bandgap of the semiconductor materials ( $\sim$ 3eV), most of the visible light can pass through the device, which makes the metal-oxide such as ZnO and IGZO TFTs transparent to human eyes. This is beneficial for display applications since metal-oxide TFTs can provide a better

### Thin-Film Transistors

**Figure 3.16:** A device photo of transparent metal-oxide (IGZO) TFTs. (Photo courtesy of ITRI-FETD)

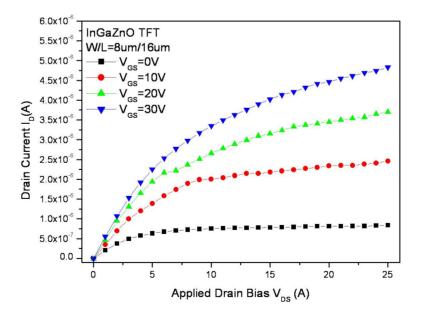

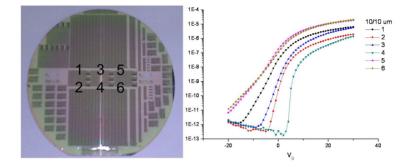

aperture ratio that lets more back-light pass through and therefore less light-intensity is needed for the same brightness than conventional a-Si:H TFT-LCD displays. This also saves a significant amount of energy. Threshold voltage shifts  $(\Delta V_{TH})$  is common for a-Si:H TFTs and limits a-Si:H TFTs from being used in a wider spectrum of applications than display pixels. (other applications such as a scan driver for displays require a careful design style to prevent significant degradations over a short period of time). Recent reports of metal-oxide TFTs stability Cross and Souza [2006], Oh et al. [2008] suggest that with proper treatments in the device fabrication (ex. annealing), the metal-oxide TFTs can exhibit excellent stability and can fulfill reliability and lifetime requirements. Figures 3.17 and 3.18 show the relationship of drain-source currents  $(I_{DS})$  versus gate voltage  $V_{GS}$  in the log-scale and versus  $V_{DS}$  in the linear scale for IGZO TFTs. As we can find in Figure 3.17 that the threshold voltage  $V_{TH}$  of this test device is slightly negative, which suggests that this TFT is a n-type depletion-mode device. The uniformity data of IGZO TFTs on a 6-inch wafer-shape plastic can be found in Figure 3.19.

**Figure 3.17:** A log scale plot of drain current  $I_{DS}$  versus gate voltage  $V_{GS}$  of a IGZO TFT (courtesy of ITRI-FETD)

**Figure 3.18:** A linear scale plot of drain current  $I_{DS}$  versus drain-source voltage  $V_{DS}$  of a IGZO TFT (courtesy of ITRI-FETD)

Thin-Film Transistors

**Figure 3.19:** IGZO TFT testkeys on a 6-inch wafer-shape plastic and their IDS-VGS curves in log-scale. Number 1 to 6 represent testkeys on different locations. (Courtesy of ITRI-FETD)

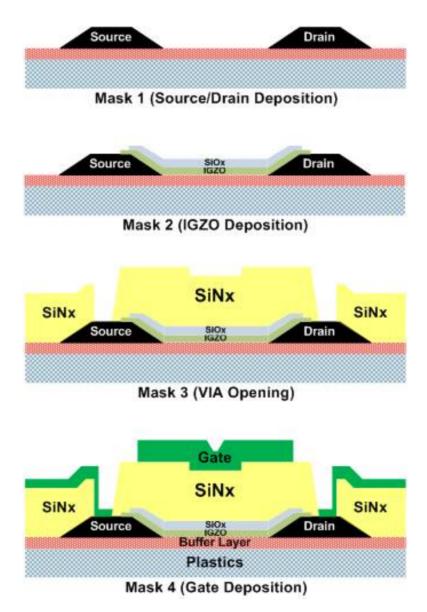

# 3.4.2 Device Manufacturing

Figure 3.20 shows the process flow of IGZO TFTs. The standard photolithography is utilized to define the desired patterns of TFT circuits. To be compatible with flexible substrates such as polyimide and PET plastics, the process temperature is controlled within 150 degree C by using RF magnetron sputtering with a low vacuum chamber to deposit gate dielectrics and semiconductors (ex. ZnO and IGZO). To ease the sample handling, the plastic substrate is first attached to a 6-inch silicon wafer as the base throughout all process steps. This plastic substrate can then be detached from the silicon wafer after circuit fabrication and the silicon wafer can be re-used for next samples.

# 3.5 Impact of Physical Strains

Flexible electronics are subject to bending; it is important to understand the TFT performance during and after mechanical stress.

In Gleskova et al. [2002], the electrical performance of back-channel etch a-Si:H TFTs fabricated on 25- $\mu$ m thick Kapton foil is evaluated. The transistors are strained by either bending or stretching. Inward cylindrical bending (Figure 3.21a) produces compression (neg-

Figure 3.20: IGZO TFT process flow with 4 photo masks

Figure 3.21: The inward (a) and outward (b) bending, and the neutral strain position (c).

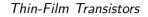

Figure 3.22: Relative mobility under different strains: (a) Gleskova et al. [2002], (b) Cheon et al. [2008].

ative strain), and outward bending (Figure 3.21b) produces tension (positive strain). Stretching, on the other hand, only produces tensile strain due to the tester setup. Figure 3.22a shows the relative mobility  $(\mu/\mu_0)$  under different strain  $(\varepsilon) - \mu$  and  $\mu_0$  correspond to the linear mobility under the imposed strain and the initial linear mobility, respectively, and  $\varepsilon$  ranges from a compressive strain of -0.01 (at the bending radius of 1.6 mm) to a tensile strain of 0.002. It is observed that the mobility decreases under compression but increases under tension; a linear fit of the measurements gives

$$\mu/\mu_0 = 1 + 26 \times \varepsilon. \tag{3.9}$$

It is also concluded that the on and leakage currents did not change.

Cheon et al. [2008] investigated the performance of strained poly-Si TFTs that are fabricated on  $50-\mu m$  flexible metal foil. Figure 3.22b shows the impact of strain on relative mobility; the trend is opposite to that in Gleskova et al. [2002] and can be expressed by

$$\mu/\mu_0 = 1 - 0.44 \times \varepsilon \tag{3.10}$$

## 3.6. Summary

when the strain is  $|\varepsilon| \leq 1\%$ . It is observed that the threshold voltage and gate voltage swing remain unchanged under mechanical strain. In Münzenrieder et al. [2011], the impact on flexible IGZO TFTs on 50-µm Kapton foil is studied. When measured in the darkness, the measured parameters, including mobility, threshold voltage, and the subthreshold swing change linearly with the applied strain, from -0.003 (at about 9 mm bending radius) to 0.003. Among them, the normalized linear mobility can be expressed by

$$\mu/\mu_0 = 1.005 + 0.062 \times \varepsilon. \tag{3.11}$$

Note that the impact of bending increases substantially when the TFTs are illuminated.

One way to relieve the mechanical strain induced performance variation is to embed the TFT's at a neutral strain position Sekitani et al. [2005]. In Sekitani et al. [2005], the pentacene FETs are fabricated on a 13- $\mu$ m polyimide film and encapsulated by passivation layers of polychloro-para-xylylene with the same thickness; this places the FETs at the neutral strain position (Figure 3.21c). With a bending radius as small as 2 mm, the change in mobility is less than 3% on compressive and tensile strains which exhibits a significant reduction compared to cases without the encapsulation layer.

## 3.6 Summary

In this chapter, we give an overview of several TFT technologies, ranging from conventional amorphous silicon TFTs, organic TFTs, to transparent metal-oxide TFTs, and discuss their device characteristics, models, and degradation mechanisms. In general, inorganic TFT technologies, such as amorphous silicon and metal-oxide TFTs, have better carrier mobility, smaller feature size, and greater ambient stability, while require a higher process temperature and have worse physical flexibility than the organic TFT counterparts. These TFTs are therefore more suitable for applications that require long-term reliability and fine features such as high-resolution displays used in consumer electronics such as TVs, tablets and smartphones. Organic TFTs usually have much better physical flexibility and lower capital investment for

# Thin-Film Transistors

printing facilities. Among organic TFT technologies, the carrier mobility of SAM-organic TFT is an order of magnitude or better than that of ink-jet printed organic TFT, but it requires a vacuum deposition process for the organic semiconductor. This inevitably increases the manufacturing costs and reduces the throughput. Studies of new organic materials, that are suitable for ink-jet printing and can achieve sufficiently high performance for emerging applications such as electronics in wearable sensors and smart tags, have been an active research subject with significant progresses.

# 4

# **Circuit Design**

Thin-film transistors (TFTs) are an essential element of circuit design for flexible electronics. The major technological challenges for TFTs, however, are their lack of complementary type devices Klauk et al. [2007], poor long-term stability Gomes et al. [2004], and the requirement of a high supply voltage. To address some of these challenges, significant innovations in device and material engineering have been made Umeda et al. [2007], Ling et al. [2007], Wager [2007] to improve TFT performance. However, relatively less research efforts have been made at higher levels of design abstraction, including the circuit, architecture and system levels, which are equally critical for addressing such challenges. In this chapter, we describe some advances in TFT-based circuit design. Although there are many types of TFT technologies that can also used to construct flexible circuits, this chapter emphasizes organic and metal-oxide TFT circuits since they attract the majority of recent research efforts to solve the circuit design challenges.

Circuit Design

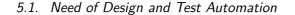

# 4.1 Digital Circuit

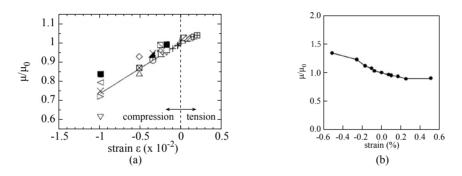

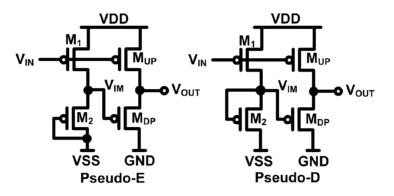

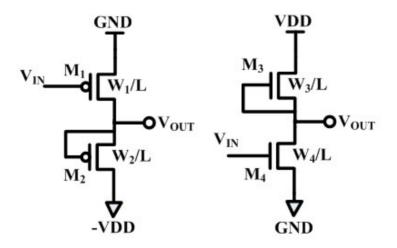

Conventional mono-type digital design styles such as the diode-load and resistive-load designs Rabaev et al. [2003] often suffer from high static power consumption and poor noise margin due to their ratioedlogic nature. NMOS-logic had been widely used for designing Si digital circuits in 1980s when PMOS was not yet mature for implementing CMOS-logic Rabaey et al. [2003]. In the past ten years, inverter designs using mono-type TFTs Cantatore et al. [2007], Gamota et al. [2004], Myny et al. [2009, 2010] have been proposed by several groups to resolve this problem but they usually require dedicated TFT characteristics and manipulations (ex. depletion-mode Cantatore et al. [2007], dual-gate Myny et al. [2010, 2011], and dual- $V_T$  TFTs Nausieda et al. [2009]). Complementary TFT inverters have been demonstrated using both p- and n-type organic TFTs De Vusser et al. [2006], Blache et al. [2009], Klauk et al. [2007] or inorganic-organic hybrid channel integration such as a combination of n-type solution-processed metal-oxide and p-type organic semiconductors Oh et al. [2007], Mvny et al. [2012, 2014] to achieve low-power consumption and high noise-margin for complex digital circuits such as microprocessors on a plastic film Myny et al. [2014]. In order to achieve excellent noise-margin without increasing process complexity such as dual-gate or dual- $V_T$  TFTs, a novel design style *Pseudo-CMOS* Huang et al. [2011] using only mono-type single- $V_T$  TFTs was proposed in which a level-shifter is built-in to the digital circuits such as inverters to shift  $V_{TRIP}$  (trip point) by means of a tuning voltage VSS. This unique feature provides several advantages including post-fabrication tunability and better noise-margin as well as higher small-signal gain Huang et al. [2011], Ishida et al. [2011, 2013]. The schematic and measured transfer functions of Pseudo-CMOS inverters are shown in Figures 4.1 and 4.2. Pseudo-CMOS inverters show the record-high small-signal gain for organic circuits (>300) and the ring-oscillator shows capability of the low-voltage operation (0.5V)Fukuda et al. [2011], Yokota et al. [2012]. Further analysis can be found in Cantatore et al. [2007], Huang and Cheng [2009], Myny et al. [2010], Huang et al. [2011], Fukuda et al. [2011], Yokota et al. [2012].

## 4.1. Digital Circuit

**Figure 4.1:** Two varieties of Pseudo-CMOS inverter designs using only p-type single- $V_T$  TFTs. The differences between Pseudo-E and Pseudo-D inverters are the gate connection of  $M_2$  and the  $M_1/M_2$  pair channel width sizing ratio  $\frac{W_1}{W_2}$ . Huang et al. [2011]

#### 4.1.1 Zero-VGS Inverter

The inverter design with zero-VGS load has been implemented for RFID tags in Cantatore et al. [2007], Myny et al. [2008] because of its low power consumption. Figure 4.3 shows the zero-VGS inverter using either only p-type or only n-type TFTs. In order to increase the pulldown force and improve the asymmetric characteristics, these p-type TFTs are engineered to have positive  $V_T$ , i.e.  $V_T > 0V$ , and the output voltage is determined by the sizing ratio between  $W_1$  and  $W_2$ . When the input level is high (i.e. GND), due to positive  $V_T$ , both  $W_1$  and  $W_2$  are conducting and the output level is gradually pulled to close to low (i.e. -VDD) because of a large  $W_2/W_1$  ( $W_2 \gg W_1$ ) sizing ratio. When the input level is low,  $M_1$  provides a strong pull-up force and pulls the output level to close to high. Despite the advantages such as low-power consumption and simplicity of the design, the drawbacks for this design include: 1) poor noise margin due to asymmetric transfer characteristics, 2) slow switching speed, 3)  $V_T$  engineering required to have normally-on TFTs, and 4) output voltage level dependence on the  $W_2/W_1$  sizing ratio.

Circuit Design

Figure 4.2: Measured inverter voltage transfer curve (VTC) of the Pseudo-E and Pseudo-D inverters based on 2V self-assembly-monolayer (SAM) organic TFTs. Each curve represents VTC with different tuning voltage VSS. The maximal achievable inverter gain is tunable and can reach >20 for Pseudo-D inverters in this case and the highest gain > 300 is reported in Fukuda et al. [2011].

Figure 4.3: Inverters with zero- $V_{GS}$  load using p- or n-type TFTs.

## 4.1. Digital Circuit

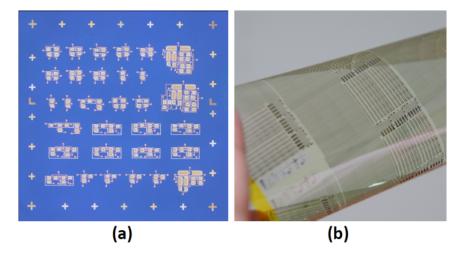

**Figure 4.4:** Pseudo-CMOS circuits implemented in (a) 2V SAM OTFTs on a silicon wafer, and (b) transparent IGZO TFTs on a plastic substrate. Huang et al. [2011]

# 4.1.2 Pseudo-CMOS Inverter

Figure 4.4 shows the fabricated Pseudo-CMOS cell-library based on 2V p-type SAM-organic TFTs on a silicon wafer and 20V n-type metaloxide TFTs on a plastic film. Characteristics of these TFTs have been discussed in Chapter 3.

While being used to build larger digital building blocks such as a frequency divider or a binary counter for a complete system such as in Ishida et al. [2011, 2013], the high noise-immunity and robustness against process variations of *Pseudo-CMOS* provides a superior circuit yield particularly under low-voltage operations.

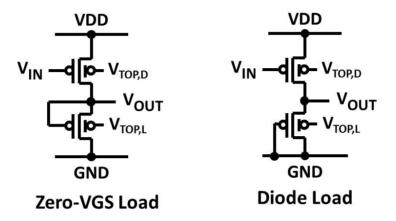

# 4.1.3 Dual-Gate Inverter

Since large process variations are inherent in low-cost printing process and difficult to minimize, new TFT structures such as dual-gate organic TFTs that consist of both top and bottom gate TFTs are proposed to control  $V_T$  Myny et al. [2010, 2011] even after the circuit fabrication, which is an effective method to improve the overall circuit

Circuit Design

Figure 4.5: Dual-gate inverters with Zero-VGS and diode loads.

yield while fabricating large-scale organic circuits such as RFID tags or microprocessors with thousands of organic TFTs. Figure 4.5 shows the dual-gate inverters with Zero-VGS and diode loads. While the bottom gate acts as the normal gate terminal, the top gate is used as the tuning knob to control  $V_T$ . The 64b organic RFID can be operated at maximum 4.3kb/s data rate with the dual-gate diode-load design and at 522b/s data rate with the dual-date Zero-VGS load with 20V supply voltageMyny et al. [2010].

## 4.1.4 Complementary Inverter

While complementary design, i.e. with both p- and n-type devices, is prevailing in modern silicon VLSI, it is not the case for flexible TFT circuits since not both types of TFTs are readily available with equivalent performance and long-term reliability. P-type organic TFTs, for example, have better carrier mobility ( $\sim 10X$ ) as well as long-term material reliability than their n-type counterparts. Instead of directly constructing complementary organic TFT circuits, recent advances in solution-processed n-type metal-oxide TFTs make the hybrid integration of n-type metal-oxide and p-type organic TFTs to implement largescale complementary TFT circuits an attractive solution. In Myny et al.

## 4.2. Analog and Mixed-Signal Circuit

[2012], an HF hybrid organic/solution-processed metal-oxide RFID tag that consists of 368 metal-oxide and 365 organic pentacene TFTs is reported to achieve 1200 bits/s data rate. The same group also reports an 8b microprocessor that consists of 1752 metal-oxide and 1752 organic TFTs with more than 400 inkjet-printed organic TFTs in a  $P^2ROM$ memory Myny et al. [2014].

# 4.2 Analog and Mixed-Signal Circuit

Analog TFT circuitry is inherently more challenging than its digital counterpart because the analog circuit performance is strongly dependent on the TFT characteristics that have high parametric variability of the TFT printing process. Key design parameters in analog circuits such as transconductance  $g_m$  and cut-off frequency  $f_T$  is also severely limited in TFT technologies due to its low carrier mobility and large parasitic capacitance. Various design techniques Marien et al. [2010], Xiong et al. [2010], Abdinia et al. [2013], Fuketa et al. [2013, 2014], Raiteri et al. [2013] as well as novel floating-gate TFT structures Ishida et al. [2011], Yokota et al. [2012] are proposed to mitigate the impact of process variations to the circuit performance. In the following, we focus on key analog building blocks such as analog-to-digital converters (ADCs) and operational amplifiers to illustrate recent advances in analog TFT circuits.

## 4.2.1 Analog-to-Digital Converter (ADC)

In Huang et al. [2008], to explore the feasibility of high-speed analog and mixed-signal circuit design, a 3b 1.25KS/s Flash ADC based on amorphous silicon TFTs has been implemented. The flash ADC architecture is advantageous in its fast conversion speed for sensing and display applications. The comparator core is composed of a *Pseudo-CMOS* latch by which the high small-signal gain can provide shorter regeneration time and better signal resolution than conventional negative- $g_m$ comparator core. In order to tackle the process variations to ADC performance deviations, a successive-approximation (SAR) ADC Xiong

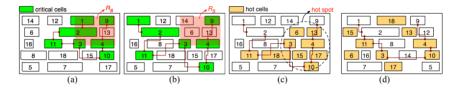

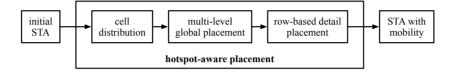

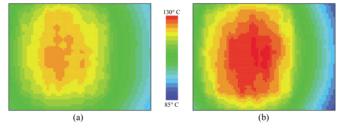

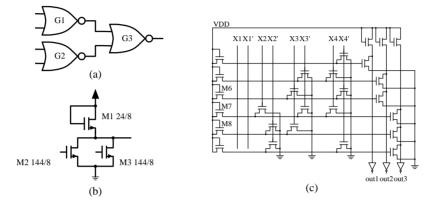

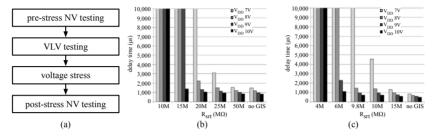

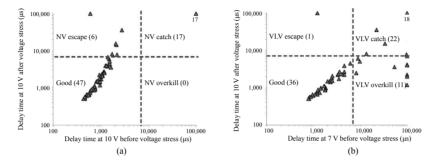

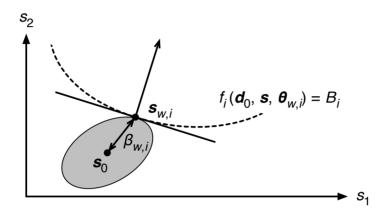

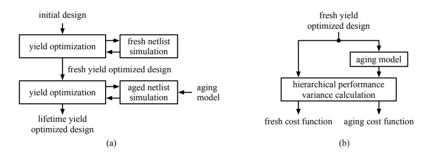

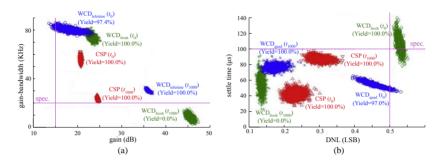

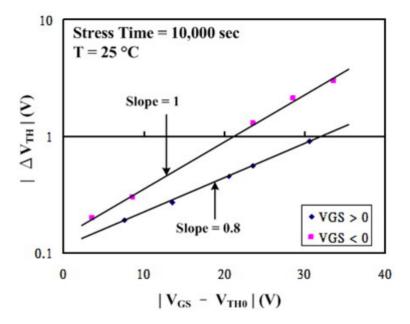

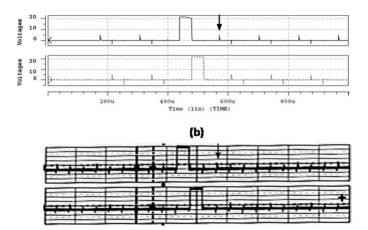

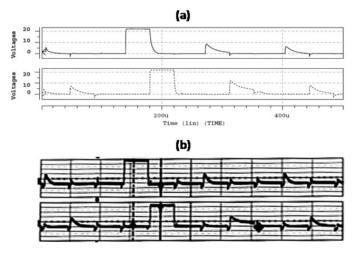

## Circuit Design