# UC San Diego UC San Diego Electronic Theses and Dissertations

## Title

Analysis and design of reliable nanometer circuits

## Permalink

https://escholarship.org/uc/item/1tw1z5sd

### Author Zhao, Chong

# Publication Date 2007

Peer reviewed|Thesis/dissertation

UNIVERSITY OF CALIFORNIA, SAN DIEGO

# Analysis and Design of Reliable Nanometer Circuits

A dissertation submitted in partial satisfaction of the

requirements for the degree Doctor of Philosophy

in

Electrical Engineering (Computer Engineering)

by

Chong Zhao

Committee in Charge:

Professor Sujit Dey, Chair Professor Chung-Kuan Cheng Professor Rajesh Gupta Professor Bill Lin Professor Curt Schurgers

2007

Copyright Chong Zhao, 2007

All rights reserved

The dissertation of Chong Zhao is approved, and it is acceptable in quality and form for publication on microfilm:

Chair

University of California, San Diego

2007

| SIGNATURE   | E PAGE iii                                                    |

|-------------|---------------------------------------------------------------|

| TABLE OF C  | CONTENTS iv                                                   |

| LIST OF FIG | URES ix                                                       |

| LIST OF TAI | BLES xii                                                      |

| ACKNOWLE    | EDGEMENTS xiii                                                |

| VITA        | xvi                                                           |

| ABSTRACT    | xviii                                                         |

| CHAPTER 1.  | INTRODUCTION1                                                 |

| 1.1 R       | ELIABILITY CONCERNS IN NANOMETER CIRCUITS1                    |

| 1.2 R       | ADIATION-INDUCED SINGLE-EVENT-UPSET (SEU)4                    |

| 1.2.1       | Basic Mechanism of Particle Strikes on Semiconductor Devices  |

| 1.2.2       | A Brief History                                               |

| 1.2.3       | Technology Trends7                                            |

| 1.3 S       | EU IN CMOS DIGITAL CIRCUITS8                                  |

| 1.3.1       | SEU in Combinational Logics                                   |

| 1.3.2       | SEU in Sequential Elements                                    |

| 1.3.3       | Inherent SEU Immunity of Digital Circuits – Masking Effects11 |

| 1.4 P       | REVIOUS SEU-RELATED RESEARCH WORK                             |

| 1.4.1       | SEU Modeling and Analysis14                                   |

| 1.4.2       | SEU Mitigation15                                              |

| 1.4.3       | Limitations of the Previous Works                             |

| 1.5 0       | VERVIEW OF RESEARCH CONTRIBUTIONS                             |

| 1.5.1       | Scope and Applicability                                       |

| 1.5.2       | Basic Approaches                                              |

# TABLE OF CONTENTS

| 1.5.3   | Dissertation Outline                                   |    |

|---------|--------------------------------------------------------|----|

| CHAPTER | 2. SOFT SPOT ANALYSIS                                  | 27 |

| 2.1     | INTRODUCTION                                           | 27 |

| 2.2     | MULTIPLE NOISE SOURCE AND THEIR COMPOUND EFFECTS       | 29 |

| 2.3     | SOFT SPOT ANALYSIS                                     |    |

| 2.3.1   | Timing Masking                                         |    |

| 2.3.2   | Electrical Masking                                     |    |

| 2.3.3   | Logic Masking                                          |    |

| 2.3.4   | Evaluating Softness and Identifying Soft Spots         | 40 |

| 2.4     | EXPERIMENTAL RESULTS                                   |    |

| 2.4.1   | Accuracy and Efficiency                                |    |

| 2.4.2   | Improved Accuracy via Curve Shift                      | 45 |

| 2.4.3   | Scalability and Softness Distribution                  | 46 |

| 2.5     | CONCLUSION                                             | 49 |

| 2.6     | ACKNOWLEDGEMENT                                        | 49 |

| CHAPTER | 3. NOISE IMPACT ANALYSIS                               | 51 |

| 3.1     | INTRODUCTION                                           | 51 |

| 3.2     | SINGLE-EVENT-TRANSIENT IN STATIC CMOS DIGITAL CIRCUITS | 54 |

| 3.3     | TRANSIENT ERROR TOLERANCE OF DIGITAL CIRCUITS          | 56 |

| 3.3.1   | Timing Masking                                         | 56 |

| 3.3.2   | Electrical Masking                                     |    |

| 3.3.3   | Logic Masking                                          | 59 |

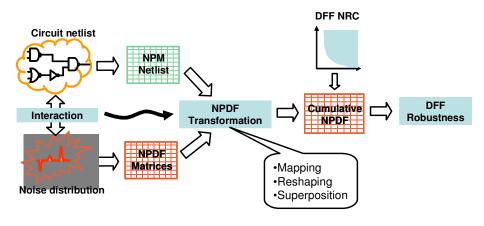

| 3.4     | NOISE IMPACT ANALYSIS USING NPDF TRANSFORMATION        | 60 |

| 3.4.1   | NPDF Mapping                                           | 60 |

| 3.4.2   | NPDF Reshaping                                         | 62 |

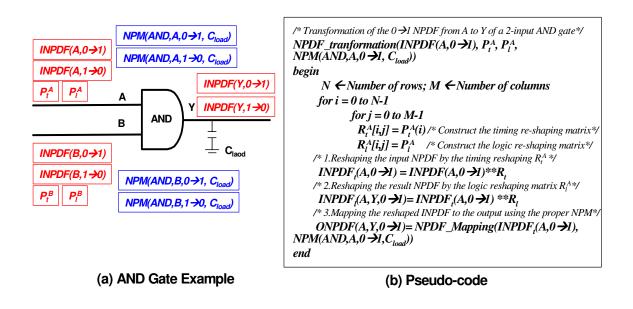

| 3.4.3                                                                                                                                                                           | NPDF Transformation                                                                                                                                                                                                                                                                                               | 63             |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

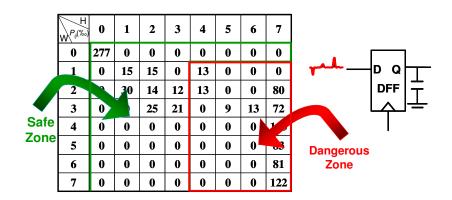

| 3.4.4                                                                                                                                                                           | Calculating DFF Noise Capture Ratio                                                                                                                                                                                                                                                                               | 65             |

| 3.5 E                                                                                                                                                                           | XPERIMENTAL RESULTS                                                                                                                                                                                                                                                                                               | 67             |

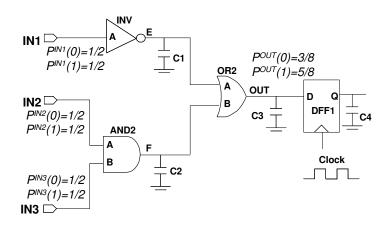

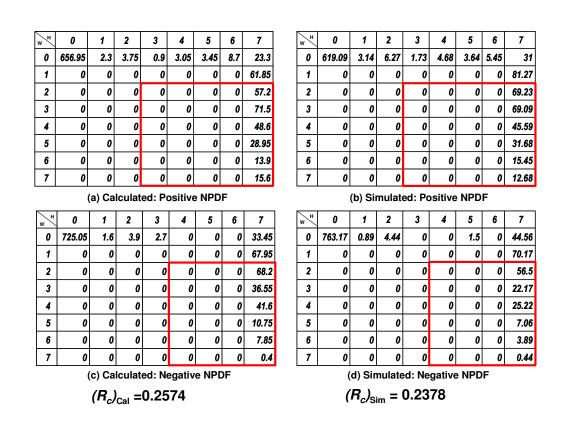

| 3.5.1                                                                                                                                                                           | Experiment I: One Simple Circuit                                                                                                                                                                                                                                                                                  | 67             |

| 3.5.2                                                                                                                                                                           | Experiment II: Two Larger Circuits                                                                                                                                                                                                                                                                                | 69             |

| 3.5.3                                                                                                                                                                           | Experiment III: Scalability                                                                                                                                                                                                                                                                                       | 71             |

| 3.6 C                                                                                                                                                                           | ONCLUSION                                                                                                                                                                                                                                                                                                         | 72             |

| 3.7 A                                                                                                                                                                           | CKNOWLEDGEMENT                                                                                                                                                                                                                                                                                                    | 73             |

| CHAPTER 4.                                                                                                                                                                      | INTELLIGENT ROBUSTNESS INSERTION                                                                                                                                                                                                                                                                                  | 75             |

| 4.1 In                                                                                                                                                                          | ITRODUCTION                                                                                                                                                                                                                                                                                                       | 75             |

| 4.2 E                                                                                                                                                                           | RROR-RESILIENT SEQUENTIAL CELL DESIGN                                                                                                                                                                                                                                                                             | 78             |

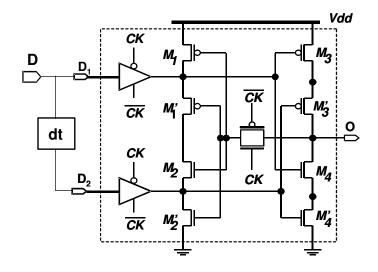

| 4.2.1                                                                                                                                                                           | The Robust Separate-Dual-Transistor (SDT) Latch Design                                                                                                                                                                                                                                                            | 78             |

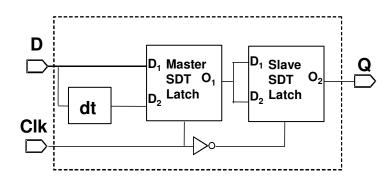

| 4.2.2                                                                                                                                                                           | Design and Characterization of SDT Flip-Flops (SDT-DFF)                                                                                                                                                                                                                                                           | 80             |

|                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                   |                |

|                                                                                                                                                                                 | OBUSTNESS CALIBRATION                                                                                                                                                                                                                                                                                             | 82             |

| 4.3 R                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                   |                |

| 4.3 R                                                                                                                                                                           | OBUSTNESS CALIBRATION                                                                                                                                                                                                                                                                                             | 85             |

| 4.3 R<br>4.4 C                                                                                                                                                                  | OBUSTNESS CALIBRATION                                                                                                                                                                                                                                                                                             | 85             |

| 4.3 R<br>4.4 C<br>4.4.1                                                                                                                                                         | OBUSTNESS CALIBRATION<br>ONSTRAINT-AWARE ROBUSTNESS INSERTION<br>Problem Formulation                                                                                                                                                                                                                              | 85<br>85<br>88 |

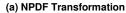

| 4.3 R<br>4.4 C<br>4.4.1<br>4.4.2<br>4.4.3                                                                                                                                       | OBUSTNESS CALIBRATION<br>ONSTRAINT-AWARE ROBUSTNESS INSERTION<br>Problem Formulation<br>A Dynamic Programming Solution                                                                                                                                                                                            | 85<br>85<br>   |

| 4.3 R<br>4.4 C<br>4.4.1<br>4.4.2<br>4.4.3                                                                                                                                       | OBUSTNESS CALIBRATION<br>ONSTRAINT-AWARE ROBUSTNESS INSERTION<br>Problem Formulation<br>A Dynamic Programming Solution<br>Implementation Framework                                                                                                                                                                | 85<br>85<br>   |

| 4.3 R<br>4.4 C<br>4.4.1<br>4.4.2<br>4.4.3<br>4.5 E                                                                                                                              | OBUSTNESS CALIBRATION<br>ONSTRAINT-AWARE ROBUSTNESS INSERTION<br>Problem Formulation<br>A Dynamic Programming Solution<br>Implementation Framework<br>XPERIMENTAL RESULTS                                                                                                                                         | 85<br>85<br>   |

| 4.3 R<br>4.4 C<br>4.4.1<br>4.4.2<br>4.4.3<br>4.5 E<br>4.5.1                                                                                                                     | OBUSTNESS CALIBRATION<br>ONSTRAINT-AWARE ROBUSTNESS INSERTION<br>Problem Formulation<br>A Dynamic Programming Solution<br>Implementation Framework<br>XPERIMENTAL RESULTS<br>STD-DFF Construction and Characterization                                                                                            |                |

| <ul> <li>4.3 R</li> <li>4.4 C</li> <li>4.4.1</li> <li>4.4.2</li> <li>4.4.3</li> <li>4.5 E</li> <li>4.5.1</li> <li>4.5.2</li> </ul>                                              | OBUSTNESS CALIBRATION<br>ONSTRAINT-AWARE ROBUSTNESS INSERTION<br>Problem Formulation<br>A Dynamic Programming Solution<br>Implementation Framework<br>STD-DFF Construction and Characterization<br>Full Case Analysis on CUT0                                                                                     |                |

| <ul> <li>4.3 R</li> <li>4.4 C</li> <li>4.4.1</li> <li>4.4.2</li> <li>4.4.3</li> <li>4.5 E</li> <li>4.5.1</li> <li>4.5.2</li> <li>4.5.3</li> <li>4.5.4</li> </ul>                | OBUSTNESS CALIBRATION<br>ONSTRAINT-AWARE ROBUSTNESS INSERTION<br>Problem Formulation<br>A Dynamic Programming Solution<br>Implementation Framework<br>STD-DFF Construction and Characterization<br>Full Case Analysis on CUT0<br>Experiments on More Circuits                                                     |                |

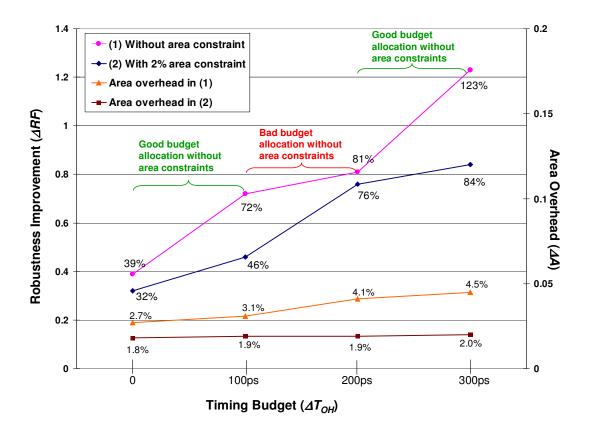

| <ul> <li>4.3 R</li> <li>4.4 C</li> <li>4.4.1</li> <li>4.4.2</li> <li>4.4.3</li> <li>4.5 E</li> <li>4.5.1</li> <li>4.5.2</li> <li>4.5.3</li> <li>4.5.4</li> <li>4.6 C</li> </ul> | OBUSTNESS CALIBRATION<br>ONSTRAINT-AWARE ROBUSTNESS INSERTION<br>Problem Formulation<br>A Dynamic Programming Solution<br>Implementation Framework<br>XPERIMENTAL RESULTS<br>STD-DFF Construction and Characterization<br>Full Case Analysis on CUT0<br>Experiments on More Circuits<br>Robustness-Cost Trade-off |                |

| 5.1     | INTRODUCTION1                                                     | 02 |

|---------|-------------------------------------------------------------------|----|

| 5.2     | REVIEW OF SOFT SPOT ANALYSIS1                                     | 04 |

| 5.3     | GATE CLONING1                                                     | 06 |

| 5.4     | CELL RESIZING1                                                    | 11 |

| 5.5     | ROBUSTNESS CLOSURE1                                               | 14 |

| 5.6     | EXPERIMENTAL RESULTS1                                             | 17 |

| 5.7     | CONCLUSION                                                        | 21 |

| 5.8     | ACKNOWLEDGEMENT1                                                  | 22 |

| CHAPTE  | R 6. TRANSIENT ERROR ANALYSIS CONSIDERING PROCESS VARIATIONS1     | 23 |

| 6.1     | INTRODUCTIONS1                                                    | 23 |

| 6.2     | MODELING THE SINGLE-EVENT-TRANSIENT (SET)1                        | 25 |

| 6.3     | MODELING TRANSIENT GENERATION AND PROPAGATION CONSIDERING CHANNEL |    |

| LENGT   | TH VARIATION                                                      | 29 |

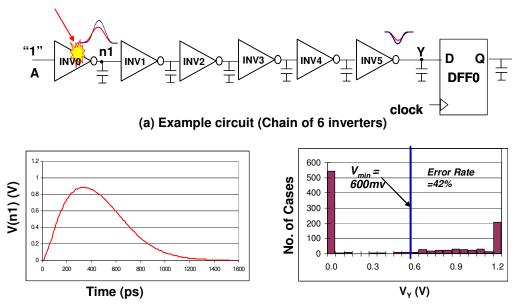

| 6.3.1   | 1 An Example: Inverter Chain                                      | 30 |

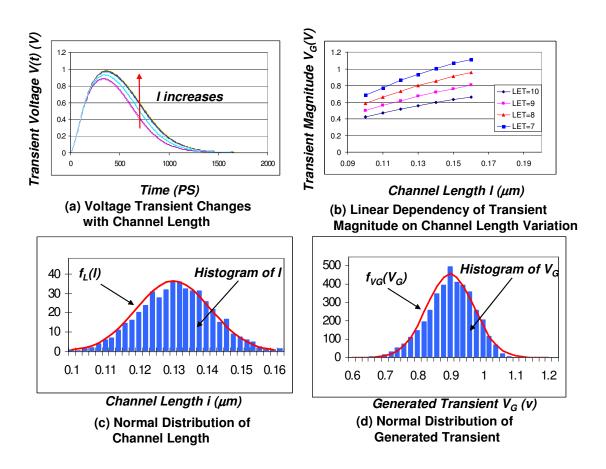

| 6.3.2   | 2 Modeling Transient Generation                                   | 31 |

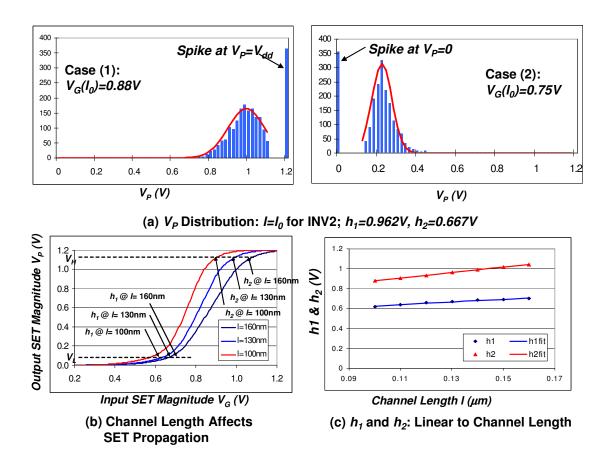

| 6.3.3   | 3 Modeling Transient Propagation1                                 | 33 |

| 6.3.4   | 4 Case Study: Inverter Chain                                      | 37 |

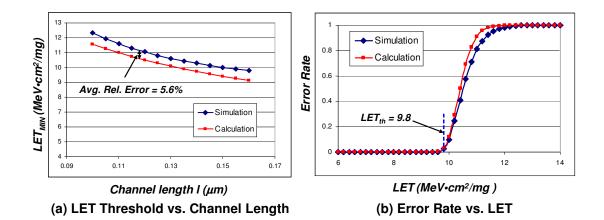

| 6.4     | EXPERIMENTAL RESULTS                                              | 41 |

| 6.4.1   | 1 Modeling of Transient Generation and Propagation1               | 42 |

| 6.4.2   | 2 Case Study: Inverter Chain                                      | 45 |

| 6.5     | CONCLUSIONS                                                       | 47 |

| 6.6     | ACKNOWLEDGEMENT1                                                  | 47 |

| CHAPTER | R 7. CONCLUSION AND FUTURE RESEARCH DIRECTION1                    | 48 |

| 7.1     | SUMMARY OF RESEARCH CONTRIBUTIONS1                                | 48 |

| 7.2     | DIRECTION OF FUTURE RESEARCH                                      | 51 |

| 7.2.1    | Improvement of the Reliability Optimization Framework | 151 |

|----------|-------------------------------------------------------|-----|

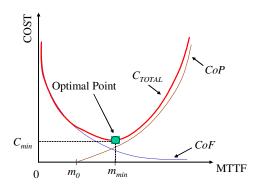

| 7.2.2    | Reliability-Cost Metric                               | 152 |

| 7.2.3    | Integrated Design-for-Robustness Framework            | 156 |

| 7.3      | SUMMARY                                               | 158 |

| BIBLIOGI | ХАРНҮ                                                 | 159 |

# LIST OF FIGURES

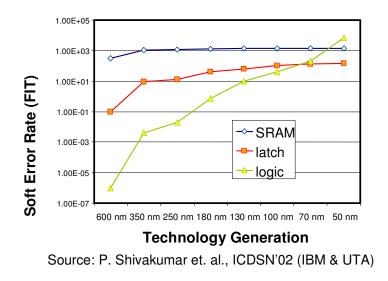

| Figure 1-1 SEU Technology Trend                                             | 8  |

|-----------------------------------------------------------------------------|----|

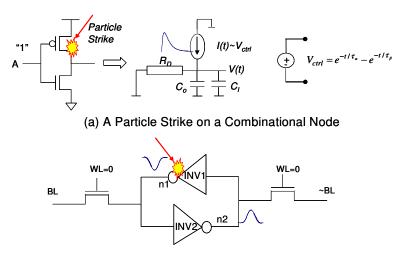

| Figure 1-2 Particle Strikes in Digital Circuits                             | 10 |

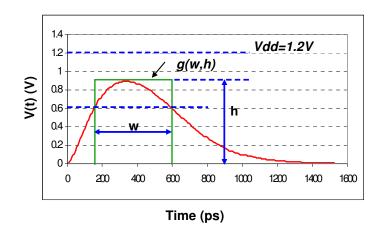

| Figure 1-3 Transient Voltage and The Square-Glitch Model $g(w,h)$           | 11 |

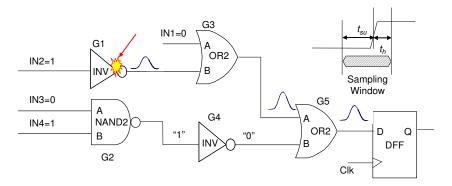

| Figure 1-4 Masking Effects in Digital Circuits                              | 13 |

| Figure 1-5 Traditional SEU Mitigation Techniques                            | 16 |

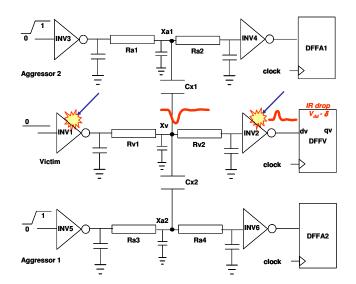

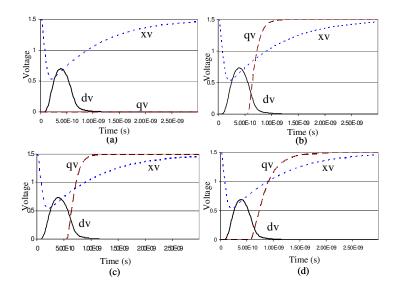

| Figure 2-1 Compound Noise Effects: Example Circuit                          |    |

| Figure 2-2 Compound Noise Effects: HSPICE Simulation                        |    |

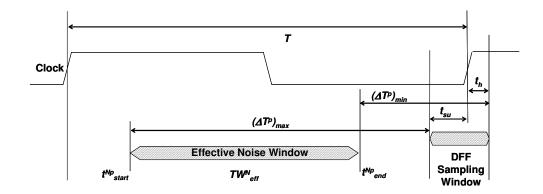

| Figure 2-3 Calculating Effective Noise Window                               |    |

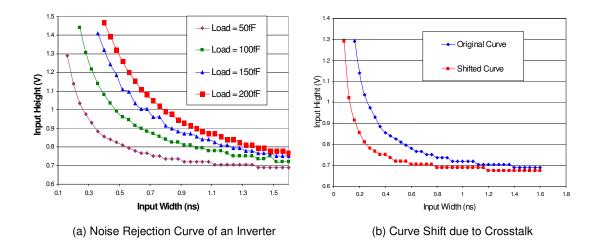

| Figure 2-4 Noise Rejection Curve and Curve Shift                            | 35 |

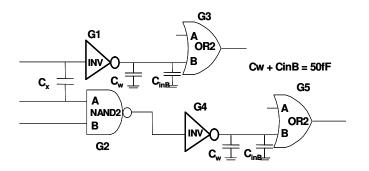

| Figure 2-5 Circuit Example - Curve Shift                                    | 36 |

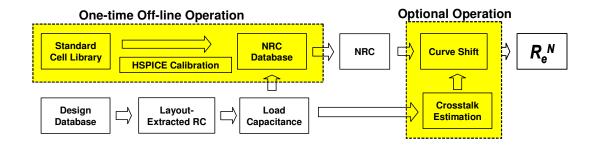

| Figure 2-6 Calculating $R_e^N$ in Cell-Based Designs                        |    |

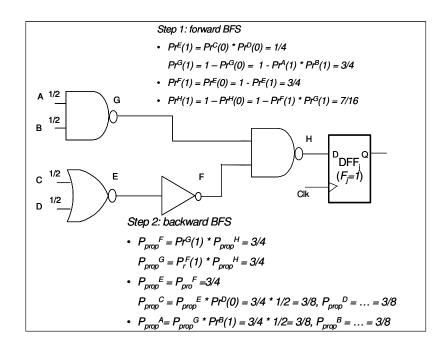

| Figure 2-7 Example Circuit: Calculating Logic Masking Factor                |    |

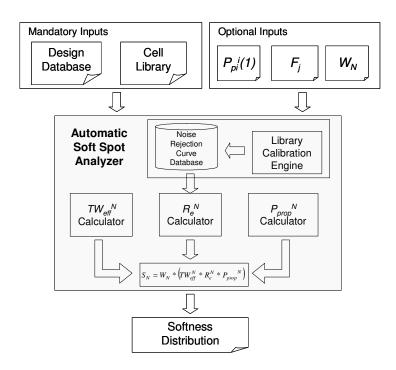

| Figure 2-8 Automatic Soft Spot Analyzer (ASSA)                              | 41 |

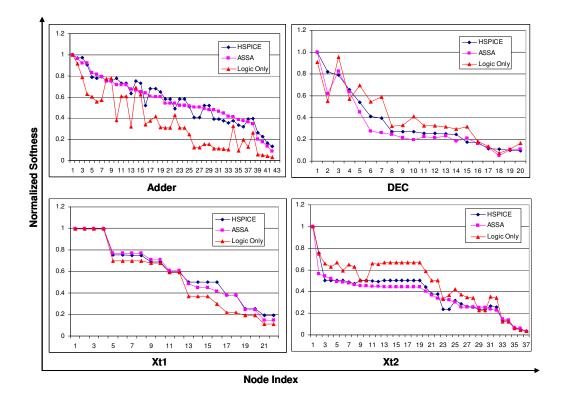

| Figure 2-9 ASSA Results Compared with HSPICE Simulation                     | 45 |

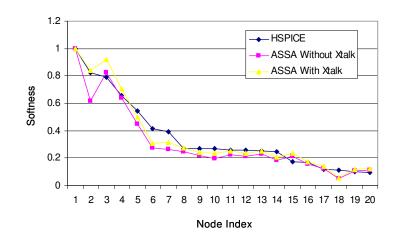

| Figure 2-10 Effect of Considering Curve Shift Caused By Crosstalk           | 46 |

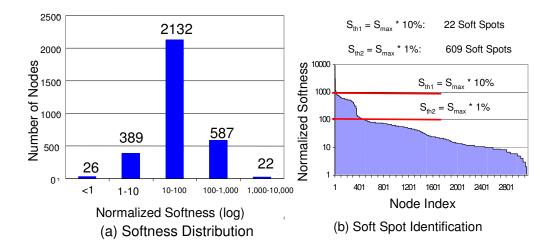

| Figure 2-11 Softness Distribution and Soft Spot Identification in Design EX | 48 |

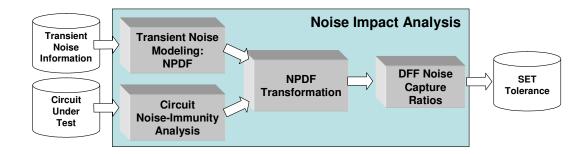

| Figure 3-1 Noise Impact Analysis Framework                                  | 54 |

| Figure 3-2 Examples of NPDF and NPM                                         | 55 |

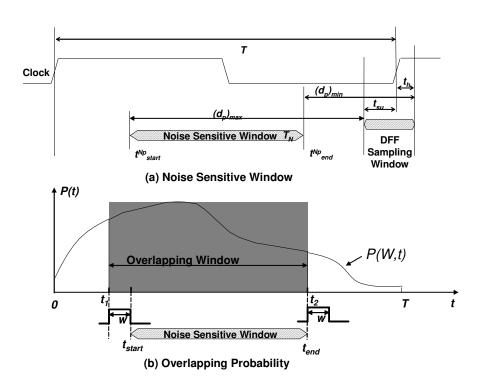

| Figure 3-3 Sensitive Window and Overlapping Probability                     | 57 |

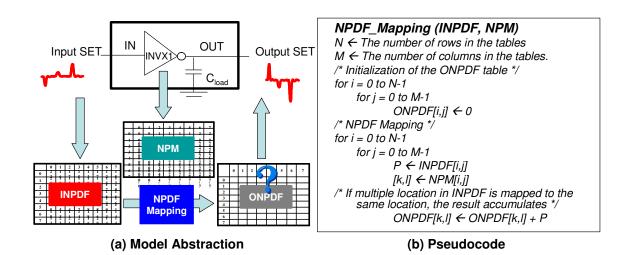

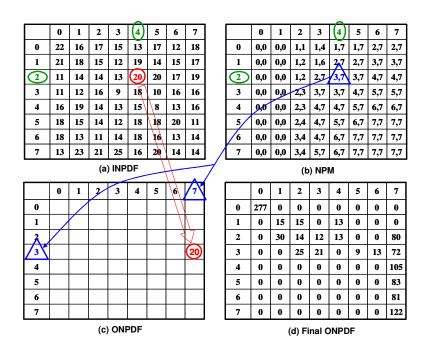

| Figure 3-4 NPDF Mapping                                                     | 61 |

| Figure 3-5 NPDF Mapping Example                                             | 62 |

| Figure 3-6 NPDF Transformation                                              | 64 |

| Figure 3-7 DFF Dangerous Zone in NPDF                                       | 66 |

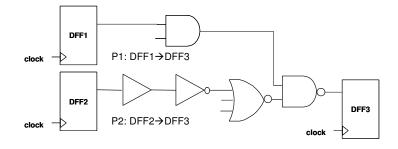

| Figure 3-8 Simple Circuit used in Experiment I                              | 68 |

| Figure 3-9 Experiment I Results                                                                 | 69  |

|-------------------------------------------------------------------------------------------------|-----|

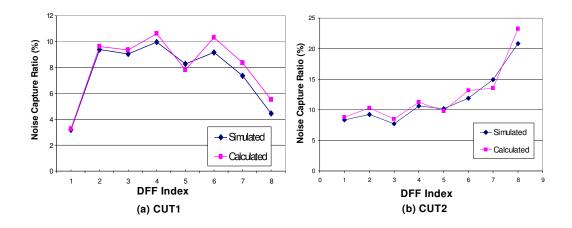

| Figure 3-10 <i>R<sub>c</sub></i> Comparison with SPICE                                          | 71  |

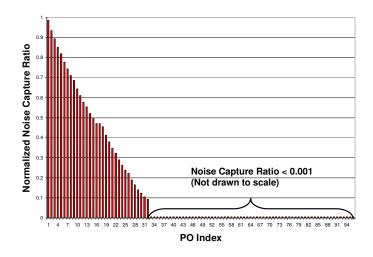

| Figure 3-11 <i>R<sub>c</sub></i> Distribution in Design EX                                      | 72  |

| Figure 4-1 Separate-Dual-Transistor Latch Design                                                | 79  |

| Figure 4-2 SDT Flip-Flop Design                                                                 | 80  |

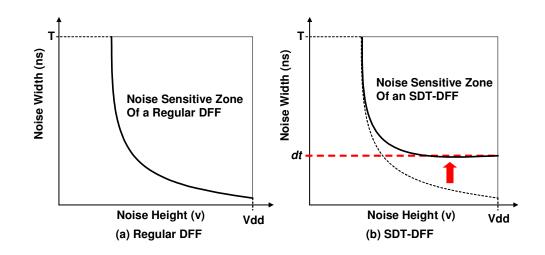

| Figure 4-3 Noise Rejection Curve and Noise Sensitive Zone                                       | 81  |

| Figure 4-4 Robustness Calibration                                                               | 84  |

| Figure 4-5 Pseudo-Code: Robustness Optimization                                                 | 89  |

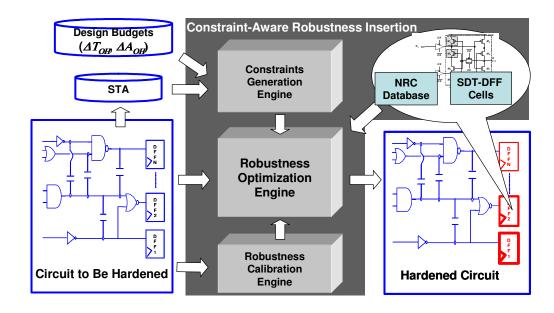

| Figure 4-6 Constraint-Aware Robustness Insertion Framework                                      | 91  |

| Figure 4-7 Robustness-Cost Trade-off in CUT5                                                    | 98  |

| Figure 5-1 The Limitation of FF Hardening                                                       | 102 |

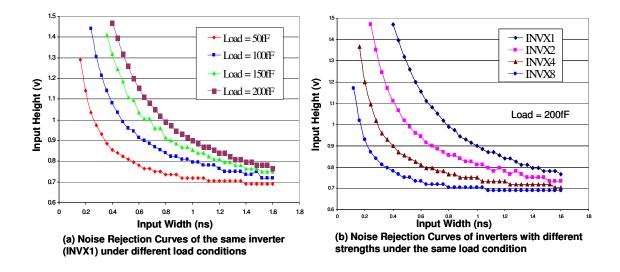

| Figure 5-2 Noise Rejection Curves                                                               | 105 |

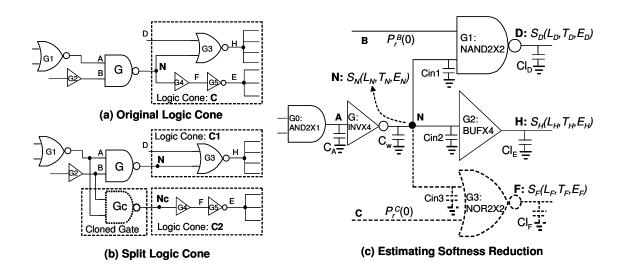

| Figure 5-3 Gate Cloning                                                                         | 106 |

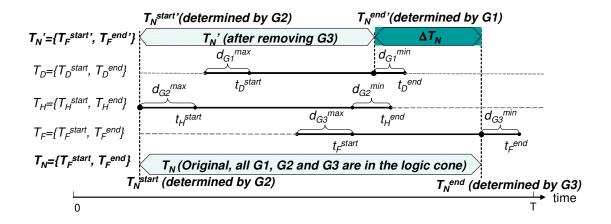

| Figure 5-4 Timing window change                                                                 | 109 |

| Figure 5-5 Pseudo-code: SplitLogicCone                                                          | 112 |

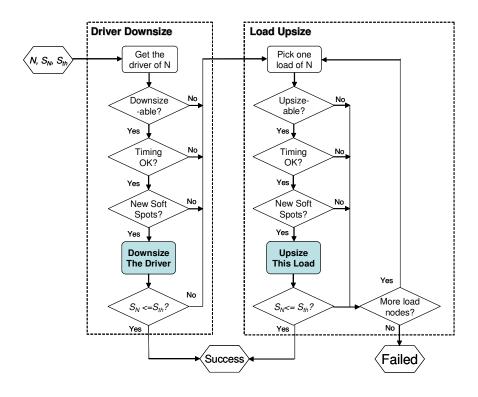

| Figure 5-6 Cell Resizing flow                                                                   | 114 |

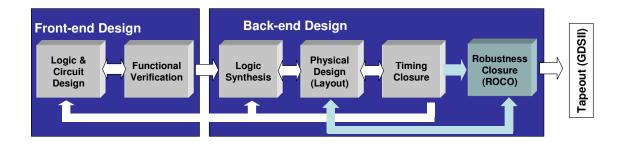

| Figure 5-7 Robustness Closure in design flow                                                    | 115 |

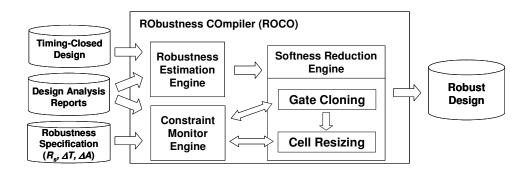

| Figure 5-8 RObustness COmpiler (ROCO)                                                           | 116 |

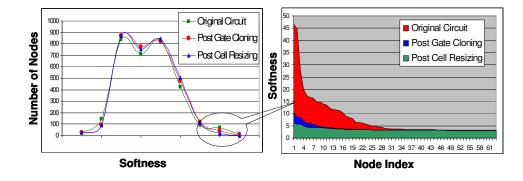

| Figure 5-9 Softness redistribution in CKT3                                                      | 121 |

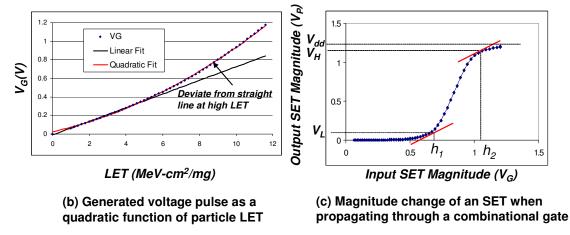

| Figure 6-1 Single-Event Transient Modeling                                                      | 127 |

| Figure 6-2 SET Generation and Propagation                                                       | 128 |

| Figure 6-3 An Inverter Chain Example                                                            | 130 |

| Figure 6-4 Modeling the Variation of Transient Generation                                       | 132 |

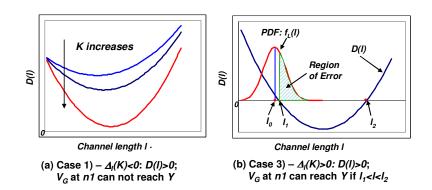

| Figure 6-5 Modeling the Variation of Transient Propagation                                      | 134 |

| Figure 6-6 Transient Error Probability Dependency on <i>LET</i> and channel length ( <i>l</i> ) | 139 |

| Figure 6-7 Experiment Results of the Inverter Chain Example                                     | 146 |

| Figure 7-1 The Integrated Framework of Reliability Optimization | 149 |

|-----------------------------------------------------------------|-----|

|                                                                 |     |

| Figure 7-2 The Reliability-Cost Curve                           | 155 |

# LIST OF TABLES

| Table 2-1 Sample Circuits and Simulation Time                                      | 44  |

|------------------------------------------------------------------------------------|-----|

| Table 2-2 ASSA Runtime on Circuit EX                                               | 47  |

| Table 3-1 CUT1: R <sub>c</sub> Comparison with SPICE                               | 70  |

| Table 4-1 Area and Timing Overhead of SDT-DFFs                                     | 92  |

| Table 4-2 Robustness Calibration and Constraint Setting of CUT0                    | 93  |

| Table 4-3 Table Growth of the Robustness Function: CUT0                            | 94  |

| Table 4-4 Robustness Optimization Results                                          | 96  |

| Table 5-1 SPICE Simulation Results: Gate Cloning                                   | 118 |

| Table 5-2 SPICE Simulation Results: Cell Resizing                                  | 118 |

| Table 5-3 Robustness specifications                                                | 119 |

| Table 5-4 ROCO execution results                                                   | 120 |

| Table 6-1 Parameter Characterization                                               | 143 |

| Table 6-2 Modeling SET Generation and Propagation: Distribution of $V_G$ and $V_P$ | 144 |

#### ACKNOWLEDGEMENTS

First and foremost, I would like to thank Prof. Sujit Dey for being an excellent research advisor. Thank you for guiding me to this fascinating research topic, for teaching me how to be an independent researcher as well as a constructive team player, for introducing me to the best in the field, and for being the support I can always count on. I would also like to thank my thesis committee members, Professor Chung-Kuan Cheng, Professor Rajesh Gupta, Professor Bill Lin, Professor Curt Schurgers, for providing valuable feedbacks to this work.

I am fortunate to be a member of the Embedded System Design, Test, and Automation Lab (ESDAT) at UC San Diego. Graduate school is a unique experience that enriches one's life. My friends at ESDAT have made this experience fun and memorable. Thank you, Dr. Yi Zhao, Dr. Li Chen, Dr. Xiaoliang Bai, Dr. Kanishka Lahiri, Dr. Dong-Gi Lee, Dr. Kanishka Lahiri, Dr. Krishna Sekar, Dr. Clark Taylor, Shoubhik Mukhopadhyay, Debashis Panigrahi, Naomi Ramos, Saumya Chandra, Myank Tiwari, for many discussions and laughter, and for making me feel the warmth of a big family. Special thanks to Cathy MacHutchin, for being a wonderful friend and for being amazingly organized and efficient in administrative work.

I would like to acknowledge the Gigascale Silicon Research Center (GSRC) for providing financial support for part of this work.

The text of the following chapters, in part or in full, is based on material that has been published in conference proceedings or journals, or is pending publication in

conference proceedings or journals. In particular, Chapter 2 is based on material in the published paper: Chong Zhao, Xiaoliang Bai, Sujit Dey, "Soft Spot Analysis: A Scalable Methodology Targeting Compound Noise Effects in Nano-meter Circuits", IEEE Design & Test of Computers, Volume 22, Issue 4, July-Aug. 2005, pp. 362-375, and material in the published paper: Chong Zhao, Xiaoliang Bai, Sujit Dey, "A Scalable Soft Spot Analysis Methodology for Compound Noise Effects in Nano-meter Circuits," in Proceedings of 41st Design Automation Conference (DAC), pp. 894-899, June 2004, San Diego, California, USA. Chapter 3 is based on material in the published paper: Chong Zhao, Xiaoliang Bai, Sujit Dey, "A Static Noise Impact Analysis Methodology for Evaluating Transient Error Effects in Digital VLSI Circuits", in Proceedings of International Test Conference 2005 (ITC), pp. 40.2, October, 2005, Austin, Texas, USA, and material in the published paper: Chong Zhao, Xiaoliang Bai, Sujit Dey, "Evaluating transient error effects in digital nanometer circuits", IEEE TRANSACTIONS ON RELIABILITY, VOL. 56, NO. 3, SEPTEMBER 2007, pp. 381-391. Chapter 4 is based on material in the published paper: Chong Zhao, Yi Zhao, Sujit Dey, "Constraint-Aware Robustness Insertion for Optimal Noise-Tolerance Enhancement in VLSI Circuits," in Proceedings of 42nd Design Automation Conference (DAC), pp. 190-195, June 2005, Anaheim, California, USA, and material in the paper accepted by IEEE Transactions on Very Large Scale Integration Systems (TVLSI): Chong Zhao, Yi Zhao, Sujit Dey, "An Intelligent Robustness Insertion Methodology for Optimal Transient Error Tolerance". Chapter 5 is based on material in the published paper: Chong Zhao, Sujit Dey, "Improving Transient Error Tolerance of Digital VLSI Circuits Using RObustness COmpiler (ROCO)", in Proceedings of 7th International Symposium on Quality

Electronic Design (ISQED), pp. 133-138, March 2006, San Jose, California, USA. Chapter 6 is based on material to be published in the Proceedings of International Conference on Computer Design (ICCD), 2007, Lake Tahoe, California, USA: Chong Zhao, Sujit Dey, "Modeling Soft Error Effects Considering Process Variations". I was the primary researcher and author of each of the above publications, and the co-authors listed in these publications collaborated on, or supervised the research which forms the basis for these chapters.

### VITA

#### **EDUCATION**

| 1990 – 1995 | B.S., Department of Physics, Peking University, Beijing, P. R. China                                |

|-------------|-----------------------------------------------------------------------------------------------------|

| 1996 – 1997 | M.S., Department of Electrical Engineering, University of Southern California, Los Angeles, CA, USA |

| 1995 – 1997 | M.A., Department of Physics and Astronomy, University of Southern California, Los Angeles, CA, USA  |

| 2003 - 2007 | Ph.D., University of California at San Diego, La Jolla, CA, USA                                     |

### WORK EXPERIENCE

| 1997 – 1998            | Sony Electronic, Rancho Bernardo, CA, USA       |

|------------------------|-------------------------------------------------|

| 1998 – 1999            | Conexant Systems Inc. San Diego, CA, USA        |

| 1999 – 2002            | Mindspeed Technologies, Inc. San Diego, CA, USA |

| June 2003 – Sept. 2003 | Intern, Intel Corporation, Santa Clara, CA, USA |

### JOURNAL PUBLICATIONS

- Chong Zhao, Xiaoliang Bai, Sujit Dey, "Soft Spot Analysis: A Scalable Methodology Targeting Compound Noise Effects in Nano-meter Circuits", IEEE Design & Test of Computers, Volume 22, Issue 4, July-Aug. 2005, pp. 362-375.

- 2. Chong Zhao, Xiaoliang Bai, Sujit Dey, "Evaluating transient error effects in digital nanometer circuits", IEEE TRANSACTIONS ON RELIABILITY, VOL. 56, NO. 3, SEPTEMBER 2007, pp. 381-391.

- 3. Chong Zhao, Yi Zhao, Sujit Dey, "An Intelligent Robustness Insertion Methodology for Optimal Transient Error Tolerance", accepted by IEEE Transactions on Very Large Scale Integration Systems.

### **CONFERENCE PUBLICATIONS**

- 4. Chong Zhao, Xiaoliang Bai, Sujit Dey, "A Scalable Soft Spot Analysis Methodology for Compound Noise Effects in Nano-meter Circuits," in Proceedings of 41st Design Automation Conference (DAC), pp. 894-899, June 2004, San Diego, California, USA.

- 5. Chong Zhao, Yi Zhao, Sujit Dey, "Constraint-Aware Robustness Insertion for Optimal Noise-Tolerance Enhancement in VLSI Circuits," in Proceedings of 42nd Design Automation Conference (DAC), pp. 190-195, June 2005, Anaheim, California, USA.

- Chong Zhao, Xiaoliang Bai, Sujit Dey, "A Static Noise Impact Analysis Methodology for Evaluating Transient Error Effects in Digital VLSI Circuits", in Proceedings of International Test Conference 2005 (ITC), pp. 40.2, October, 2005, Austin, Texas, USA.

- Chong Zhao, Sujit Dey, "Improving Transient Error Tolerance of Digital VLSI Circuits Using RObustness COmpiler (ROCO)", in Proceedings of 7th International Symposium on Quality Electronic Design (ISQED), pp. 133-138, March 2006, San Jose, California, USA.

- 8. Chong Zhao, Sujit Dey, "Evaluating and Improving Transient Error Tolerance of CMOS Digital VLSI Circuits," in Proceedings of the International Test Conference 2006 (ITC), pp. 29.1, October 2006, Santa Clara, California, USA.

- 9. Chong Zhao, Sujit Dey, "Modeling Soft Error Effects Considering Process Variations", to be presented on the International Conference on Computer Design (ICCD), October 2007, Lake Tahoe, California, USA.

# **Analysis and Design of Reliable Nanometer Circuits**

by

Chong Zhao Doctor of Philosophy in Electrical Engineering (Computer Engineering) University of California, San Diego, 2007 Professor Sujit Dey, Chair

As CMOS technology advances to the nanometer scale, semiconductor industry is enjoying the ever-increasing capability of integrating more and more devices and elements on a single die. Meanwhile, the reliability of the integrated circuit (IC) product is being severely challenged, as many previously negligible noise effects are becoming more prominent, causing significant performance and reliability degradations of nanometer integrated circuits.

In particular, radiation-induced transient error is quickly evolving to a serious limiting factor in the circuit reliability. Unfortunately, it has not been sufficiently and successfully addressed in previous technology generations, especially in cost-sensitive mainstream applications. Due to tight design constraint, budget and application requirement, traditional redundancy-based techniques that have been exploited in space and mission-critical applications are no longer applicable. There is an urgent need for cost-effective techniques, methodologies and flows to facilitate the development of reliable IC products.

This dissertation is dedicated to the quest for solutions in the analysis, design and optimization of highly error-tolerant nanometer circuit systems. As will be elaborated and demonstrated throughout the entire dissertation, all developed techniques and methodologies share distinguished characteristics of being novel, accurate, economical, practical and scalable, as compared to other existing works. Together they form a unified and automated reliability optimization framework that will enrich the legacy of the IC design industry.

# **Chapter 1. Introduction**

Silicon technology has advanced relentlessly following the Moore's law (i.e., doubling of the chip density every 1.5 years) [1] for the past four decades. This trend is likely to continue for the next decade in spite of the enormous investment needed in the manufacturing facilities and great difficulties anticipated in extending the CMOS scaling to its ultimate limits. As CMOS technology evolves into the nanometer regime, advanced manufacturing technology and comprehensive computer-aided design (CAD) techniques enable multi-million transistors to be manufactured on a single die, and multiple components to be integrated onto a single chip to become a "System-on-Chip (SoC)". Meanwhile, the semiconductor industry has to cope with two major challenges: the everincreasing design complexity and complicated physical effects inherent from the nanoscale technology. Many previously negligible effects are becoming prominent and the reliability of cutting-edge nanometer circuits are being severely endangered.

### **1.1 Reliability Concerns in Nanometer Circuits**

In digital circuits, information is encoded and processed as signals in the form of logic 1 and 0 (corresponding to different voltage levels), which are transmitted through logic gates and interconnects. During this process, disturbances in the forms of current and voltage variations, or "*noise*", may potentially damage the original signal, resulting in distorted or erroneous data to be generated or transmitted. Fortunately, these signals

possess a certain level of resilience to various noise sources, so that they may be safely decoded back to the intended data even in a noisy environment. However, if signal distortions exceed the device noise margin, the correct values might not be able to be restored. In this dissertation, "*reliability*" is a term used to describe the tendency of the circuit to restore the distorted signals and its ability to operate properly with the presence of noise interferences.

Complementary Metal Oxide Semiconductor (CMOS) digital circuits are believed to have high reliability due to their exceptional capability of restoring distorted signals (as compared to their analog counterparts). For this very reason, noise had always been considered as secondary effects in the previous technology generations and designers have been relying on this inherent tolerance of the circuit to self-protect or self-rescue from various noise interferences. Consequently, the objective of chip design and implementation has been primarily set on making the products capable of performing expected functionalities under certain design constraints including speed, area and power, whereas reliability have not been included in the design metric.

With the feature size shrinks to nanometer scale, reliability degradation has become a serious design concern that may cause significant yield loss and performance impact if not properly addressed. Several factors collectively contribute to the reliability degradation. First, as the device dimension becomes comparable to the atoms in the semiconductor material, many noise sources become significantly more prominent than ever. Second, as the supply voltage reaches sub-volt range, noise margin of the semiconductor devices has been greatly reduced, which means the required noise level to cause irreversible distortions is much lower. Third, the number of devices on a single die is increasing exponentially with the integration capability, and they are operating at a muck faster rate as the operating frequency reaches multi-GHz range. This results in stronger and more frequent interactions among adjacent devices that lead to stronger error effects and higher failure rate.

Due to these technology trends, the reliable functioning of VLSI circuits is being greatly threatened. If the potential vulnerabilities are not properly addressed during the design phase, the manufactured chip may be highly unreliable. Therefore, more comprehensive and improved reliability criteria should be implemented into the design flow via different levels of abstraction. In their 2005 edition, the International Technology Roadmap for Semiconductors (ITRS) [2] predicts that "Design-for-Reliability" (DFR) will become an important practice to achieve a high level of error tolerance; and reliability-aware design will become indispensable in the current and next technology generation.

Failures experienced by nanometer circuits can be either permanent or transient [19]. A permanent failure causes irreversible damage and malfunction of the chip. Examples of noise sources that cause permanent failures include time-dependent dielectric breakdown (TDDB), hot carrier injection (HCI), negative bias temperature instability (NBTI) in transistors and electromigration in interconnects. In contrast to permanent failures, transient failures occur occasionally because of temporary environmental conditions and last only for a short period of time. Examples of noise sources that cause transient failures include power supply and interconnect noise,

electromagnetic interference, electrostatic discharge and radiation-induced soft errors. Among them, the radiation-induced soft error has become one of the most serious transient failures in nanometer circuits. It is caused by highly energetic particles striking the sensitive regions in semiconductor devices and is often referred to as a "single-eventupset (SEU)".

SEU will not cause permanent chip damage and its error effects will not persist as the noise source disappears. Because of the unpredictable nature of the particle activities (in cosmic rays or semiconductor materials), it is extremely difficult to detect, diagnose and prevent such transient error effects. Due to its low occurrences, until recent technology generation, SEU has been only a concern in space and mission-critical applications, where reliability is the most important performance requirement and cost is not a limiting factor. The most commonly adopted SEU mitigation techniques involve using redundancy at various abstraction levels to provide extra protections. As the technology reaches nanometer scale, as was mentioned above and will be elaborated in detail later, SEU has become a non-negligible error source even in mainstream applications (such as consumer electronics), whose cost-sensitive nature prohibits the extensive use of redundancy. Furthermore, as the circuit complexity and level of integration significantly increase, efficient yet economical SEU detection and prevention pose great challenges to the semiconductor industry.

### **1.2** Radiation-Induced Single-Event-Upset (SEU)

The remaining part of this chapter gives an overview of SEU, including the basic mechanism of particle strikes in semiconductor devices, a brief history of SEU-related

research work, and its impacts on the functionality of VLSI circuits. It also reviews the contributions and limitations of previous research efforts on SEU detection and prevention.

### **1.2.1** Basic Mechanism of Particle Strikes on Semiconductor Devices

When a cosmic particle enters a semiconductor material, it deposits charges by freeing electron-hole pairs along its path as it loses energy. The particle of particular interest is the heavy neutron, which constitutes ~92% of all particles in the terrestrial environment [37]. The energy level considered is in the range of 1-10 MeV, because particle strikes with higher energy occur with significantly low probability and they usually cause permanent failure instead of transient upsets. The *linear energy transfer* (LET) is frequently used to relate the energy of the incident particle to the charge deposition in a particular type of material. LET is defined as the energy loss of the particle per unit path length in the material and has the unit of  $MeV-cm^2/mg$ . In bulk silicon, a typical charge collection depth  $\lambda_c$  is ~2µm for an LET of 1 MeV-cm<sup>2</sup>/mg, and an ionizing particle deposits  $q_d = 10.8$  fC of charge along each micron of its track. Thus a particle with LET of  $1MeV-cm^2/mg$  deposits ~21.6fC of charge [46].

The most sensitive regions to collect the deposited charge in the struck device are the reverse-biased p/n junctions. The high field present in a reverse-biased junction depletion region can efficiently collect the particle-induced charge through drift processes, leading to a transient current at the junction contact [50]. This transient current may potentially damage signals generated and propagated in a circuits, and eventually lead to erroneous circuit behavior and observable error effects. The exact error impact depends on the type of the struck device as well as the nature of the affected circuit and will be discussed in more detail in section 1.3.

Natural particle activities has strong timing, geographical and altitude dependencies: for a specific orbit during a certain period of time, it is characterized by the *LET spectrum*  $\Phi(LET)$ , defined as the number of particles detected on a unit area per unit time as a function of the particle's LET [49]. In the atmosphere, particle flux is typically in the range of  $10^{-5}$ - $10^{1}$  cm<sup>-2</sup> day<sup>-1</sup>, and there is a sharp knee in the natural LET spectrum at an LET ~30 and particles with LET above 30 are exceedingly rare [9].

### **1.2.2 A Brief History**

The first SEU-related work was published in 1962 [51], forecasting the eventual occurrence of SEU in microelectronics due to cosmic rays. The first confirmed report of cosmic-ray-induced upsets in space was presented at the NSREC in 1975 [52], which reported four observed upsets in 17 years of operation in a communication satellite. Because the numbers of errors observed was so small, it had been several years before the importance of SEU was fully recognized. In the late 1970s, evidence continued to mount that cosmic-ray-induced upsets were indeed responsible for errors observed in satellite memory subsystems, and the first models for predicting system error rates were formulated [54]. In the 1980s, research on SEU continued to increase and methods for hardening ICs to SEU were widely developed [55] [56]. Studies of SEU in random logics appeared in the late1980s, but were often overshadowed by the volume of work

addressing memory upset [57] [58]. In the 1990s, a surge of interest in random logic SEU emerged, fueled by several factors including: 1) a perception that the memory soft error was controllable with advanced technologies and error detection and correction (EDAC) techniques [59]; 2) a growing concern that technology scaling could lead to an inversion between the relative significance of memory and logic on observed soft error rates [60]; and 3) observations that clock speeds were driving up core-logic error rates [61].

As the semiconductor industry enters the 21<sup>st</sup> century, the SEU sensitivity of IC products is expected to continuingly increasing. SEU vulnerability has become a mainstream product reliability metric of IC industry, as outlined by the SEMATECH National Industry Association Roadmap [62]. The feasibility of traditional SEU-hardening techniques is becoming questionable; while circuit designs that are inherently radiation resistant, known as "hardening by design" (HBD), are receiving considerable attention [63]. Methodologies of cost-effective SEU resilient circuit and system design have drawn tremendous research interest recently in the nanometer scale IC products.

#### **1.2.3 Technology Trends**

With the technology scaling, soft error rate (SER) in VLSI circuits drastically increases. In particular, random logic SER increases at a higher rate than memory SER. In [27], it has been concluded that when the feature length decreases from  $0.6\mu m$  to  $0.1\mu m$ , soft error rate (SER) in memory chips (in the unit of FIT/bit, where FIT="Failure-In-Time", gives the number of failure in  $10^9$  hours) remains constant but the number of bits on a die increases quadratically over each technology generation so the number of failures

experienced by a single die increases moderately. Meanwhile, random logic SER has increased by a factor of  $10^7$ , and is expected to surpass SER in unprotected memories in the year of 2011. Furthermore, memory devices can be effectively protected by various schemes, such as error correction code (ECC) [64]. Therefore, for products that use ECC to protect the on-chip memories, logic will quickly become the dominant error source.

**Figure 1-1 SEU Technology Trend**

### **1.3 SEU in CMOS Digital Circuits**

In COMS digital circuits, when a particle penetrate both the source and drain of the struck transistor in a circuit elements, it results in a significant (but short-lived) source-drain current that mimics the "ON" state of the transistor and causes a temporary voltage swing around the struck node. There are two types of elements in static CMOS digital circuits: sequential elements, such as flip-flops (FFs), have the capability to store (or "memorize") logic values; whereas combinational elements can only alter the logic level of the incoming signals as they propagate through. The particle-induced voltage swing may lead to different error behavior in different types of elements.

### **1.3.1 SEU in Combinational Logics**

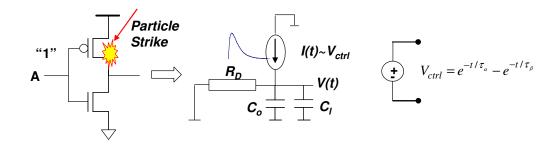

Figure 1-2(a) shows the situation when a particle strikes the PMOS transistor in a CMOS inverter and the corresponding linear RC modeling.  $R_D$  is the equivalent resistor of the NMOS transistor network. The transient current from the source to the drain of the PMOS transistor caused by the strike has a double-exponential form [42]:

$$I(t) = \frac{Q}{(\tau_{\alpha} - \tau_{\beta})} (e^{-t/\tau_{\alpha}} - e^{-t/\tau_{\beta}})$$

(1.1)

where  $Q = LET^* \lambda_c * q_d$ , is the total deposited charge;  $\tau_a$  is called the "collection time constant"; and  $\tau_\beta$  is called the "ion track establishment time constant". In the current technology node, typical values are ~1.64x10<sup>-10</sup> sec for  $\tau_\alpha$  and ~5x10<sup>-11</sup> sec for  $\tau_\beta$ . This transient current can be realized as a voltage controlled current source, and the independent voltage source provides the double-exponential term.

When the input to the inverter is "1", the nominal output is "0", and the PMOS transistor is in its "OFF" state. However, as the result of this current flow, the PMOS transistor will be temporarily shorted and a transient voltage pulse V(t) (called a "Single-Event-Transient", or a "SET") will appear at the output. In [48], an approximate closed-form expression of V(t) was obtained:

$$V(t) = \frac{Q}{C_n \tau_{\alpha}} e^{-t/\tau_n} \left( \frac{e^{t/\tau_n} \cdot e^{-t/\tau_{\alpha}} - 1}{1/\tau_n - 1/\tau_{\alpha}} \right)$$

(1.2)

where  $\tau_n = C_n * R_D$ ;  $C_n$  is the total capacitance (sum of the output capacitance  $C_o$  and the load capacitance  $C_l$ ). In the above equation, the contribution of  $\tau_\beta$  is ignored as it is relatively small compared to that of  $\tau_{\alpha}$ .

(b) A Particle Strike inside a Feedback Loop

#### **Figure 1-2 Particle Strikes in Digital Circuits**

Figure 1-3 shows the transient waveform V(t) measured at the output of the inverter in Figure 1-2(a). It is usually modeled as a square shaped glitch g(w,h) with certain duration w and amplitude h. The duration w is measured at the 50% of supply voltage  $V_{dd}$ ; whereas the amplitude h is measured as the maximum deviation from the nominal voltage level. This glitch caused by strikes on a combinational node is often referred to as a "single-event-transient (SET)".

### **1.3.2 SEU in Sequential Elements**

If a particle strikes a transistor in a sequential element with a regenerative feedback (e.g. a flip-flop), the generated transient voltage can strengthen itself through the

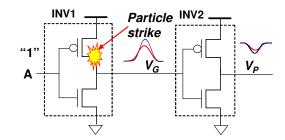

propagation in the feedback loop and eventually stabilize as a static error. Figure 1-2(b) shows an example of a strike on a typical cell with a feedback loop: when the word line (WL) is low, the cell is holding its stored data. If a particle strike on INV1 causes node n1 to transition, the disturbance may propagate forward through INV2 and cause a transition on node n2. The feedback loop will cause both nodes to flip and the memory cell will reverse its state to a wrong value. Once the cell flips, it will not be recovered unless it is rewritten via the bitlines. Furthermore, when the WL is high, an external transient may be able to reach the feedback look and become a stable error. Therefore, sequential elements play a crucial role in SEU error rate in digital circuits.

Figure 1-3 Transient Voltage and The Square-Glitch Model *g*(*w*,*h*)

### 1.3.3 Inherent SEU Immunity of Digital Circuits – Masking Effects

Compared to direct particle strikes in the sequential elements, transient errors caused by strikes in combinational gates are much more difficult to analyze. First, the strength of the incurred voltage swing depends on not only the incident energy, but also the property and dimension of the struck transistor, as well as the supply voltage and the loading condition. Second, a SET will not become a stable error unless it is later captured by a FF. There exists three "masking effects" (electrical masking, latching-window masking and logic masking) that can prevent a transient from being captured. Therefore, the observable error rate depends on the electrical, timing and structural properties of the entire combinational logic.

The example circuit shown in Figure 1-4 illustrates the three masking effects: a particle strikes the PMOS transistor in the inverter G1 and incurs a positive transient glitch g[w,h] at its output node.

1) Electrical masking: the amplitude of the generated transient has to be larger than the input noise margin of a subsequent gate in order to continue its propagation as a legitimate digital pulse. In the example, the glitch can possibly propagate to the output of G3 only if its amplitude h is higher than the input noise margin of G3.

2) Logic masking: the generated transient has to be located on a sensitized logic path to reach the endpoint FF. If it reaches a logic gate whose output value is completely decided by controlling value of the gate on the side inputs, it will cease to further propagate. In the example, if IN1=1, the glitch will not reach the output of G3; even when IN1=0, if both IN2 and IN3 equal to 1, the input B to the OR gate G5 will be 1, so the glitch at input A of G5 will still be logically masked. It is easily found that the only occasions that the glitch can reach the FF are  $\{IN2, IN3, IN4\} = 101, 110, or 100$ .

3) Latching-window masking: the generated transient has to arrive at the input of a FF within a timing window ("sampling window") to be captured because a FF

is insensitive to any signal arrives outside the sampling window. The sampling window is bounded by the setup time  $(t_{su})$  and the hold time  $(t_h)$ . Since the glitch will be phase delayed as it propagates through the intervening gates en route to the DFF, to arrive at the DFF within its sampling window, the glitch at the original struck gate has to meet certain timing requirement.

Figure 1-4 Masking Effects in Digital Circuits

The strengths of the three masking effects are purely determined by the electrical, logic and timing structure of the circuit and independent of the external particle activities. Therefore, digital circuit is considered to have inherent tolerance to single event transient.

### **1.4 Previous SEU-Related Research Work**

Error effects caused by the particle-induced transient current are non-persistent – they will not be able to be detected when the noise source disappears. This makes SEU detection, diagnosis and correction extremely difficult. Ever since the discovery of the SEU effect, researchers in semiconductor companies and universities have spent tremendous efforts and resources on the methodologies and techniques to prevent it from causing damage to electronic products.

### **1.4.1 SEU Modeling and Analysis**

The SEU effects can be studied at various levels and through either dynamic fault simulation or static analysis.

At the device-level, the most commonly used formalism in simulation is the driftdiffusion models [69] [70], where the semiconductor device equations are derived from the Boltzmann transport equation using numerous approximations. The equations to be solved are the Poisson equation and the current continuity equations. Although devicelevel simulations provide the most accurate modeling, they are extremely time-consuming and computationally intensive so they can not be used directly as the SEU vulnerability metric without higher-level abstraction.

Stepping up in the hierarchical view, these models can be incorporated into macro-models of the devices interconnected in a sub-circuit, where the charge collection in individual device junctions is related to changes in the circuit currents and voltages. A common circuit model for the charge collection at a junction due to direct funneling or diffusion is the double-exponential, time-dependent current pulse [42] [72]. Deterministic circuit simulation of logic circuitry has been effectively performed in the circuit domain using industry standard tools such as Synopsys HSPICE, Orcad PSPICE, Cadence Spectre. Methods to track radiation vulnerability at the circuit level have emerged primarily in the realm of random logic. For example, [71] presented a probabilistic description of single-event fault generation, propagation, and logic error events using a high-level HDL circuit description.

Although simulation-based analysis is generally accurate and easy to implement, as circuits grow exponentially in density and complexity, comprehensive circuit simulation is becoming impractical; and method based on dynamic simulations inevitably faces the scalability challenge. Naturally, static method of SEU analysis has become the target of many research works. [73] [74] both have presented analytical descriptions of core logic soft error vulnerability based on the "window of vulnerability" of in-data-path static and dynamic latch elements, the synchronous clock, and other deterministic elements. Method for the identification of SEU vulnerabilities have also been developed [36] [68].

### **1.4.2 SEU Mitigation**

Traditionally, SEU has been only a concern in space applications because the density of cosmic particles in outer space is exceedingly higher than at the ground level so the soft error rate observed in ground applications is negligibly small. For example, in 0.6 $\mu$ m technology, the soft error rate in typical unprotected SRAM at ground level is in the order of  $10^2$ - $10^4$  FIT/Mbit [7]. For a typical 64Kbit SRAM, one failure may occur at most every  $1.7 \times 10^2$  years. However, reliability is the most critical requirement in space applications and even a low transient error rate is unacceptable. In contrast, cost is at most a secondary concern to system reliability. Therefore, significant amount of resources can be spent to achieve a high level of SEU tolerance. Many early SEU mitigation techniques adopted in space applications are at high level of design abstraction such as the module level or even system level because they are easy to implement and more flexible.

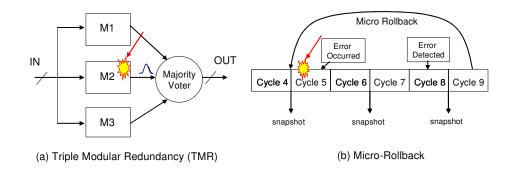

Triple modular redundancy (TMR) [38] has been a popular module-level scheme to detect and correct soft errors. As shown in Figure 1-5(a), the module under protection has three identical instances (M1, M2 and M3) that perform the same functionality simultaneously. If M2 endures a particle strike, its output may differ from the other two, but the correctness of the module will be guaranteed by a "Majority Voter". TMR will almost ensure the correctness of the protected module because the probability of two modules suffering a strike at the same time is infinitesimal. An area overhead of 300% is the protection cost of TMR. In extremely critical components, the protected module can be as large as an entire microprocessor chip.

**Figure 1-5 Traditional SEU Mitigation Techniques**

Micro-rollback is a system-level soft error mitigation technique [65] that is able to correct the transient error effect by bringing the system back a state prior to the occurrence of the error. In order to be able to perform such an operation, it is necessary to save "snapshots" of some states of the system. As shown in Figure 1-5(b), in case of an earlier error (during cycle 5) being detected (during cycle 8), the error can be corrected by overwriting the current state (cycle 9) with a snapshot (cycle 4) taken in the past. Micro-rollback not only has high spatial overhead due to the additional storage needed to save

the snapshots as well as extra circuitry to detect the error and to execute the rollback, but also needs temporal overhead due to the halt and rewind in the instruction sequence.

Although high-level protection schemes have significant protection penalty in area, timing and power, they have been extensively adopted in space applications, as well as other mission-critical applications, such as life-saving device (pace makers, etc.) and safety-proof equipment (automobile breaking systems, etc).

With the technology scaling, soft error in mainstream applications at ground level is gradually becoming a serious concern. For mainstream applications, low-cost is the major objective while intermittent occurrence of transient errors is not necessarily disastrous. Hence, techniques such as TMR and micro-rollback are most probably not applicable due to their extremely high spatial and/or temporal overheads. The objective of SEU mitigation shifts from ensuring 100% SEU tolerance regardless of cost to achieving a desirable level of tolerance with reasonable cost.

The most fundamental method for hardening against SEU is to reduce charge collection at sensitive nodes. This can be accomplished in the material or device level by introducing extra doping layers to limit substrate charge collection [66], or using siliconon-insulator (SOI) substrates to reduce the sensitive area of the device [67]. However, their invasive nature requires fundamental changes in the manufacturing process so the cost of their implementation is prohibitively high. On the contrary, techniques at the circuit level provide acceptable tradeoff between the implementation cost and the level of protection. In cell-based ASIC design flow, standard cells are the basic circuit-building block. Many previous works have been focused on designing SEU-hardened standard cells by inserting spatial and/or temporal redundancies. For example, [10] proposed design of SEU-hardened latches and FFs based on a "Separate-Dual-Transistor (SDT)" structure that uses both temporal and spatial redundancies to increase its transient error tolerance. The detailed operation of an SDT DFF and its application will be further explored in Chapter 4. Designs of hardening cells using similar concepts and approaches can also be found in many other published works [12] [13] [14].

SEU-hardened standard cells provide the basic building block of SEU-tolerant digital circuits. In reality, the tight design constraints usually prohibit global application of these specially designed cells due to the associated timing/area overhead. Most realistically, SEU-hardened cells can be only used at selected locations. Technologies focusing on the optimization of hardening cell insertions can be found in many research works [32] [68].

SEU mitigation can also be achieved during the chip synthesis [33] since the logic implementation and gate sizing can significantly affect the generation and capturing of the transient glitches in the combinational netlist. The advantages of these gate-level techniques include: (1) the optimization does not necessarily incur design overhead; and (2) the application of the techniques can be merged into the existing chip physical design flow. However, similar metrics of SEU vulnerability have also to be developed to guide the SEU-aware synthesis process.

#### **1.4.3** Limitations of the Previous Works

As the objective of SEU mitigation shifts from ensuring 100% SEU tolerance regardless of cost to achieving a desirable level of tolerance with reasonable cost, existing State-of-the-art EDA tools and previous design/testing methodologies are not geared towards handling transient interference in an economic and efficient way. Chip designers are left no choice but relying on empirical guidelines and manual efforts, resulting in lengthened design cycle and increased non-recurring engineering (NRE) cost; and the products are potentially highly susceptible to particle strikes during their field operation. This section lists some limitations of the previous works introduced above from a highlevel viewpoint:

• Traditionally, attacking the reliability problem starts with separately analyzing each individual noise source. As chips become more complex and take on more functionality, one of the biggest challenges lies not in modeling the behavior of the chip itself, but rather in modeling the behavior of the noise sources. Many noise sources co-exist and interact with each other to aggravate their error effects. In addition, various types of process and environmental variations will add extra uncertainties to the chip reliability. Consequently, techniques that target on individual noise sources inevitably face great difficulties because the amount of work involved in analyzing all noise sources; further more, they can not accurately and quickly consider the compound effects, leading to overly optimistic analysis result.

• Traditional design, verification and test methodologies are predominantly deterministic in nature, such as vector-based simulation, static timing analysis, formal equivalency check and automatic test pattern generation. Ensuring circuit correct functionality and certain level of reliability primarily count on exercising different corner cases. However, SEU is causes by strikes of cosmic particles whose activities are totally random and unpredictable and can not be modeled deterministically. As result, traditional techniques are not capable of analyzing SEU effects and improving circuit SEU-tolerance.

• Traditional SEU mitigation techniques in mission critical applications have been relying on costly redundancy-based approaches because cost has been of secondary concern. As SEU become a reliability concern in cost-sensitive mainstream applications, existing techniques can not be directly applied due to the tight design constraint and budget.

• The majority of SEU analysis methodologies have been relying on dynamic simulation or intensive computation. Due to increasing chip complexity and tightened design requirements, they are no longer scalable or viable solutions.

• SEU analysis and mitigation have existed mainly as a secondary task and isolated from the design flow. The shortcomings are two-sided: on one hand, necessary SEU analysis can not easily executed in the early design phase to identify the potential vulnerability; on the other hand, the analysis results can not be directly utilized to guide the SEU mitigation efforts. The consequence is not only insufficient SEU protection to be built in the design, but also unnecessary

design resource and engineering cost.

• As has been widely accepted, circuit-level redundancy insertion is one promising solution to SEU mitigation. However, its applicability may be severely limited in low-power, high-speed and cost-effective IC product due to the associated penalty in timing, area and power. In order to achieve high reliability with acceptable cost, the redundancy insertion has to be judiciously applied. This requires accurate and convenient reliability metric as guidelines, which, unfortunately, has not been successfully developed in existing works.

#### **1.5** Overview of Research Contributions

Facing the challenges stated above, it is imperative that revolutionary methodologies, techniques and flows be developed to facilitate the SEU analysis and mitigation, and the design and optimization of highly reliable nanometer circuit systems. This constitutes the primary objective of the research works presented in this dissertation.

## **1.5.1 Scope and Applicability**

SEU-related research is an extremely widespread field so it is impractical to cover the entire space. Based on the previous discussions on the challenges and technology trend, the research work presented in this dissertation will be focused on SEU analysis and mitigation of random logics in products targeting the mainstream applications. The applicability of the methodologies and techniques is limited to static digital CMOS circuits. The selection of this particular scope is due to three reasons. First, the severity of the transient error effects in this scope is becoming dominantly significant. Second, the quest for proper solutions in this scope is particularly challenging. Third, the need to successfully address the problem is becoming increasingly urgent. In this scope, viable solutions have to be low-cost, static and constraint-aware. In addition, they have to be compatible and integratible with the existing design flow.

Within the specified scope, "reliability" is exclusively used to refer to the "SEU tolerance" of a static digital CMOS circuit, i.e. the ability of the circuit to resist the transient errors caused by cosmic particle strikes and to maintain its functional correctness. Another term, "robustness", is used interchangeably with "reliability".

#### **1.5.2 Basic Approaches**

In the previous technology generation, reliability did not draw enough attention and was not included in the design sign-off metric. As a result, the manufactured VLSI circuits might have certain level of reliability defects, or "vulnerabilities", in the circuit structure that might lead to chip malfunction if attacked by particle strikes. As reliability has become a serious design concern, these vulnerabilities have to be identified and strengthened during the chip design phase. In order to improve the productivity and reduce the cost, these efforts have to be automated in an integrated design flow. This section overviews the ideas and approaches presented in the dissertation.

Fundamentally different from the existing approaches that set their viewpoints on one or more of the noise sources, the proposed approaches start the efforts by focusing on the VLSI circuit itself. The inherent transient error tolerance of CMOS digital circuits is solely determined by their logical, structural and electrical properties and independent of the external and/or internal noise interferences. Hence, it is much more realistic to analyze the transient error tolerance and identify the most vulnerable regions during the early design phase, when the behaviors of the external noise sources are largely unknown.

Once these vulnerabilities have been identified, the circuit behavior in the presence of noise interferences can be accurately and quickly determined. Instead of estimating the impact of the potential noise source on the circuit behavior, a better approach is studying the impact of the inherent circuit tolerance on the behaviors of potential noise sources. Conceptually, the circuit is viewed as a transfer function that transforms any given noise description to a corresponding error rate. Once the transfer function is obtained, it can be applied to arbitrary noise sources to evaluate its specific error effect.

The next step is to utilize these analysis results to guide the efforts of improving the circuit reliability. Under these guidelines, circuit hardening techniques can be applied most efficiently and it is possible to achieve maximum improvement while minimizing the penalty. In digital circuits, reliability enhancing techniques need to be developed for both the combinational and sequential logics.

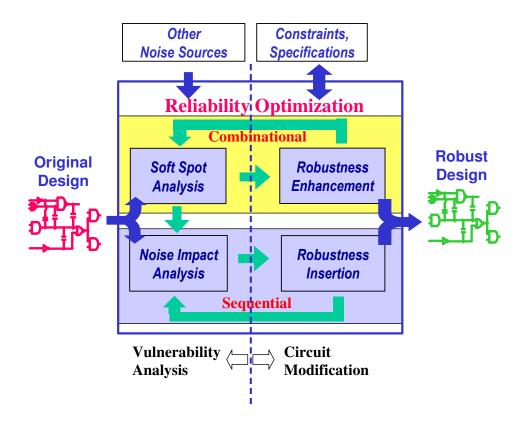

These three steps together form a complete reliability optimization flow. In order to maximize the efficiency, it is necessary to integrate the reliability analysis and enhancement efforts in a single framework. In addition, it is desirable to merge these efforts into the existing chip design flow, not only to avoid redundant works, but also to maintain the level of required performance and cost.

In summary, *accuracy*, *cost*, *scalability* and *integration* are the key words that best describe the requirement for a viable and promising reliability optimization solution. These aspects motivate all the research works presented in the following chapters.

Taking one step forward, knowing that the existence of other types of variations and noise will unavoidably aggravate the transient error effects, this compound effect will be studied using two examples. The first one is the circuit vulnerability analysis that considers the interactions between transient error and signal integrity problems (such as crosstalk). The second is the impact of process variations on this particular type of environment variations. These efforts on the compound effects add another dimension to the unified reliability optimization framework.

## **1.5.3 Dissertation Outline**

The rest of this dissertation is organized as follows:

Chapter 2 presents a "soft spot analysis" methodology. It is a static technique to identify the most vulnerable regions in the combinational circuits. The analysis is purely based on the electrical, timing and logic structure of the circuit without the necessity of being aware of the external noise disturbances. It discovers that a small portion in the design have significantly high vulnerability, i.e. noise at these so called "soft spots" will potentially cause high functional impact when suffering external attack. The result can be used to guide cost-effective reliability optimization of the combinational circuits.

Chapter 3 presents a "noise impact analysis" methodology. It is a static technique to identify the most vulnerable sequential elements in the circuits. The analysis is based on not only the circuit property, but also the knowledge of external noise information. It discovers that only a small percentage of all sequential elements have high probability of being affected by transient errors. The result can be used to guide the judicious insertion of SEU-hardened sequential elements.

Chapter 4 presents a "constraint-aware robustness insertion" technology. Based on the noise impact analysis result, using a cost-effective SEU-hardened standard cell, it is an optimization algorithm that automatically find the optimal scheme to protect the sequential elements under the given design constraints and budgets.

Chapter 5 presents a robustness enhancement technique. Based on the soft spot analysis results, it selects the most vulnerable combinational circuit nodes as the target of applying various circuit-tuning techniques to suppress the generation, propagation and capture of transient errors in the combinational circuits. As a result, the overall observable error rate can be significantly reduced.

Chapter 6 presents the modeling of transient error effects considering process variations. This work collectively considers two types of variability in nanometer digital circuits and demonstrates that the presence of process variation can greatly aggravate the environment variations; as a result, ignoring the process variation may lead to large analysis inaccuracy. It developed a statistical modeling of the generation and propagation of transient errors in the combinational circuits that can be used to accurately and quickly evaluate the transient error behavior.

Chapter 7 summarizes the major contributions of research works presented in this dissertation. By integrating all pieces of individual work in a unified and self-contained framework, a promising flow that realizes cost-effective and intelligent reliability optimization will be depicted. This chapter also provides the directions of future research.

# **Chapter 2. Soft Spot Analysis**

Nanometer circuits are becoming increasingly vulnerable to interferences from multiple noise sources, including the radiation-induced soft errors. A desirable approach to ensure reliable functioning of chips is to first identify regions in the circuit that are most susceptible to multiple noise sources (called "soft spots"), and then to "harden" these soft spots using various techniques. This chapter presents a scalable technique to evaluate the circuit vulnerability. A "*softness*" of the circuit is defined as an important vulnerability measurement. Several key factors affecting the *softness* value are examined and an efficient Automatic Soft Spot Analyzer (ASSA) is developed to evaluate the *softness*. The proposed methodology provides guidelines not only to reduction of severe noise effects caused by aggressive design in the pre-manufacturing phase, but also to selective insertion of protection schemes to achieve high degree of on-line robustness. The quality of the proposed soft-spot analysis technique is validated by HSPICE simulation, and its scalability is demonstrated on a commercial embedded processor.

#### 2.1 Introduction