# **UC San Diego**

# **UC San Diego Electronic Theses and Dissertations**

#### **Title**

Static timing analysis in VLSI design

#### **Permalink**

https://escholarship.org/uc/item/1ww8c4b4

#### **Author**

Zhou, Shuo

# **Publication Date**

2006

Peer reviewed|Thesis/dissertation

# UNIVERSITY OF CALIFORNIA, SAN DIEGO

# Static Timing Analysis in VLSI Design

A dissertation submitted in partial satisfaction of the requirements for the degree Doctor of Philosophy

in

Computer Science

by

Shuo Zhou

# Committee in charge:

Professor Chung-Kuan Cheng, Chair Professor Paul M. Chau Professor Fan Chung Graham Professor Ronald Graham Professor Tajana Rosing

Copyright

Shuo Zhou, 2006

All rights reserved.

| The dissertation of Shuo Zhou is approved, and it is ac-   |

|------------------------------------------------------------|

| ceptable in quality and form for publication on microfilm: |

|                                                            |

|                                                            |

|                                                            |

|                                                            |

|                                                            |

|                                                            |

|                                                            |

|                                                            |

|                                                            |

|                                                            |

|                                                            |

| Chair                                                      |

University of California, San Diego

2006

# TABLE OF CONTENTS

|    | Signature Page ii                                                   |

|----|---------------------------------------------------------------------|

|    | Table of Contents                                                   |

|    | List of Figures vi                                                  |

|    | List of Tables                                                      |

|    | Acknowledgements                                                    |

|    | Vita, Publications, and Fields of Study xi                          |

|    | Abstract xii                                                        |

| Ι  | Introduction                                                        |

|    | I.B Spectrum of Chip Analysis                                       |

|    | I.D. Problem Formulation                                            |

|    | I.D.2 The Problem of Multi-cycle Paths                              |

|    | I.D.3 The Problem of Hierarchical Timing Analysis                   |

| II | Background and Previous Works                                       |

|    | II.B Static Timing Analysis Overview                                |

|    | II.B.1 Timing Graph                                                 |

|    | II.B.2 Delay Models                                                 |

|    | II.B.3 Timing Constraints                                           |

|    | II.B.4 Static Timing Analysis Algorithms                            |

|    | II.C Previous Works on Timing Analysis Dealing with False Paths and |

|    | Multi-cycle Paths                                                   |

|    | II.C.1 General Rule and Exceptional Rules                           |

|    | II.C.2 Timing Analysis with Tags                                    |

|    | II.C.3 Node Splitting Approach                                      |

|    | II.C.4 Multi-clock Domain Analysis with Edge-Masks 2                |

|    | II.D Abstract Timing Model Reduction                                |

|    | II.D.1 Terminology                                                  |

|    | II.D.2 Timing Model Reduction                                       |

| III | Timing Analysis with False Paths                                      | 32  |

|-----|-----------------------------------------------------------------------|-----|

|     | III.A Introduction                                                    | 32  |

|     | III.B Motivation                                                      | 33  |

|     | III.C Rule Collection Minimization                                    | 34  |

|     | III.C.1 Main Flow of Rule Collection Minimization                     | 36  |

|     | III.C.2 Intersection of Prefix Rule Collections with Suffix Rule Sets | 37  |

|     | III.C.3 Bipartite Graph and Biclique Covering                         | 38  |

|     | III.C.4 Rule Collection Propagation                                   | 41  |

|     | III.C.5 Theoretical Improvement Ratio                                 | 43  |

|     | III.C.6 Correctness                                                   | 45  |

|     | III.D Experimental Results                                            |     |

|     | III.E Acknowledgement                                                 | 49  |

| IV  | Unified Framework Dealing with False Paths and Multi-Cycle Paths      | 50  |

|     | IV.A Introduction                                                     | 50  |

|     | IV.B Unified Framework Processing False Paths and Multi-cycle Paths . |     |

|     | IV.B.1 Subgraph Expansion                                             | 52  |

|     | IV.B.2 Rule Sets Based Unified Framework                              |     |

|     | IV.C Rule Collection Minimization                                     | 59  |

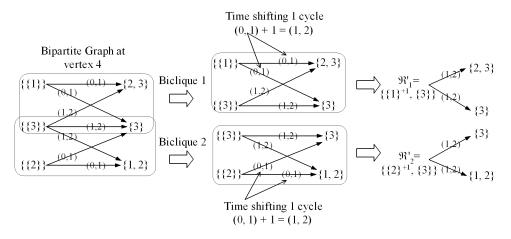

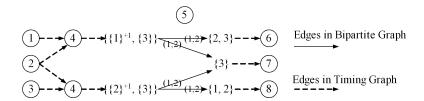

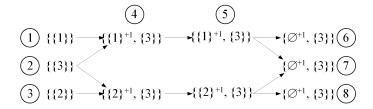

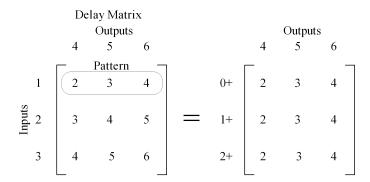

|     | IV.C.1 Time Shifting Example                                          |     |

|     | IV.C.2 Main Flow of Rule Collection Minimization                      | 60  |

|     | IV.C.3 Intersection of Rule Collection with Suffix Rule Set and Bi-   |     |

|     | partite Graph                                                         |     |

|     | IV.C.4 Time Shifting and Biclique Covering                            |     |

|     | IV.C.5 Rule Collection Propagation                                    | 67  |

|     | IV.C.6 Timing Analysis with Rule Collections                          | 70  |

|     | IV.C.7 Special Cases of False Subgraph Rules                          | 71  |

|     | IV.D Experimental Results                                             | 72  |

|     | IV.E Acknowledgement                                                  | 75  |

| V   | Timing Model Reduction for Hierarchical Timing Analysis               |     |

|     | V.A Introduction                                                      |     |

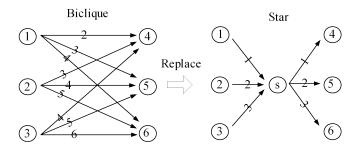

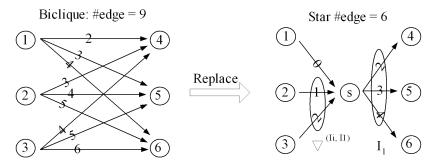

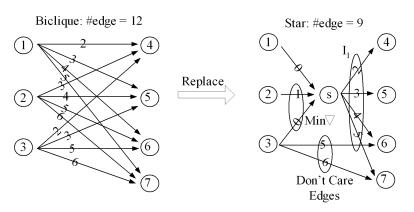

|     | V.B Biclique-Star Replacement                                         |     |

|     | V.B.1 Replacement Covering All Edge Delays                            |     |

|     | V.B.2 Replacement Allowing Don't Care Edges                           |     |

|     | V.C Timing Model Reduction Based on Biclique-Star Replacements        |     |

|     | V.C.1 Main Flow of Bipartite Timing Model Reduction                   |     |

|     | V.C.2 Biclique Search in Bipartite Timing Model                       |     |

|     | V.C.3 Edge Reduction Evaluation                                       | 93  |

|     | V.C.4 Iterative Timing Model Reduction                                |     |

|     | V.D Timing Model Reduction with False Paths and Multi-cycle Paths     | 102 |

|     | V.E. Experimental Results                                             | 103 |

| VI | Conclusion                     |

|----|--------------------------------|

|    | VI.A Dissertation Contribution |

|    | VI.B Future Works              |

|    | Bibliography                   |

# LIST OF FIGURES

| I.1<br>I.2<br>I.3<br>I.4<br>I.5      | Spectrum of Chip Analysis                                                             | £ 6                                                                |

|--------------------------------------|---------------------------------------------------------------------------------------|--------------------------------------------------------------------|

| II.11                                | Timing Graph                                                                          | 121<br>141<br>152<br>202<br>223<br>253<br>264<br>293<br>300<br>311 |

| III.2<br>III.3<br>III.4              | $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                  | 35<br>39<br>42<br>43<br>44                                         |

| IV.2<br>IV.3<br>IV.4<br>IV.5<br>IV.6 | Subgraph Expansion: False subgraph of rule 0 is expanded Unified Rule Set Computation | 53<br>56<br>60<br>62<br>63<br>66<br>68                             |

|                                      | at vertex 5                                                                           | 69                                                                 |

| V.1  | Biclique-Star Replacement                                        | 80  |

|------|------------------------------------------------------------------|-----|

| V.2  | Biclique-Star Replacement Based on Delay Pattern                 | 84  |

| V.3  | Biclique-Star Replacement Allowing Don't Care Edges              | 88  |

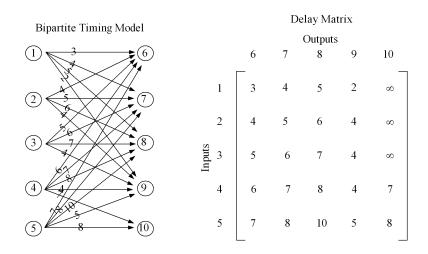

| V.4  | Bipartite Timing Model and the Delay Matrix Example              | 93  |

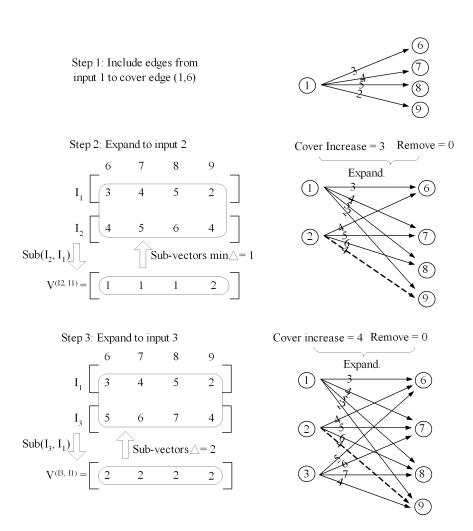

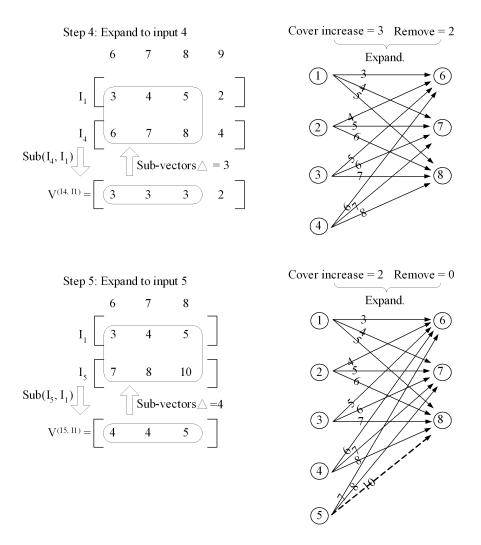

| V.5  | Biclique Expansion Starting from Edge (1,6) in Bipartite Timing  |     |

|      | Model (Fig.V.4): Steps 1 to 3                                    | 94  |

| V.6  | Biclique Expansion Starting from Edge (1,6) in Bipartite Timing  |     |

|      | Model (Fig.V.4): Steps 4 and 5. $\dots$                          | 95  |

| V.7  | All Bicliques in Bipartite Timing Model (Fig.V.4)                | 96  |

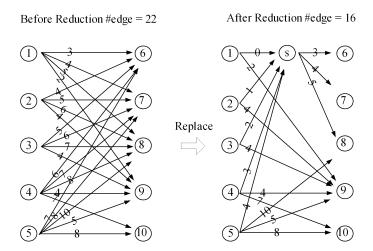

| V.8  | Bipartite Timing Model (Fig.V.4) Reduction : The number of edges |     |

|      | is Reduced from 22 to 16                                         | 97  |

| V.9  | Bicliques Crossing Multiple Bipartite Partitions                 | 98  |

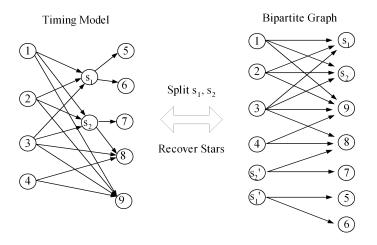

| V.10 | Vertex Splitting and Star Recover                                | 100 |

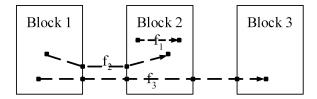

| V.11 | Hierarchical Blocks Containing False Paths                       | 102 |

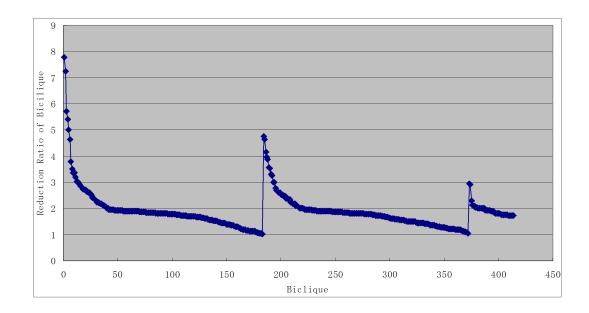

| V.12 | Reduction Ratios of Replaced Bicliques                           | 105 |

# LIST OF TABLES

| III.1 Intersections of Rule Collections and Suffix Rule Sets at Vertex $v \;$ . | 38  |

|---------------------------------------------------------------------------------|-----|

| III.2 Tag Minimization on $100 \times 100$ Mesh                                 | 48  |

| III.3 Tag Minimization on Industry Test Cases                                   | 49  |

| III.4 Tag Minimization Run Time                                                 | 49  |

| IV.1 Intersections of Rule Collections and Suffix Rule Sets at Vertex $4$ .     | 62  |

| IV.2 Intersections of Rule Collections and Suffix Rule Sets at Vertex $5$ .     | 67  |

| IV.3 Tag Minimization on $100 \times 100$ Mesh                                  | 73  |

| IV.4 Tag Minimization on Industry Test Cases                                    | 74  |

| ${\rm IV.5~Run~Time~of~Static~Timing~Analysis~Using~Rule~Collection~Tags}$      | 74  |

| V.1 Edge Reduction with Error Bounds                                            | 105 |

#### ACKNOWLEDGEMENTS

First of all, I would like to thank my advisor, Professor Chung-Kuan Cheng for his encourage, support, and insightful guidance. I learned from him not only the knowledge of the field but also the wisdoms of life. I wish to thank my dissertation committee members, Professor Ronald Graham, Professor Tajana Simunic Rosing, Professor Fan Chung Graham and Professor Paul Chau for their time and efforts. I would like to express my appreciation to Mike Hutton at Altera for technical discussions and his advices and reviews of my papers.

I am grateful to all the graduate students in the UCSD VLSI CAD group for making the group a fun place to work. Special thanks to Zhengyong Zhu, Bo Yao, Hongyu Chen, Jianhua Liu, Rui Shi, He Peng, Haikun Zhu, Yuanfang Hu, Yi Zhu, Ling Zhang, Renshen Wang, and Wanping Zhang. In particular, I would like to thank Hongyu Chen, Yi Zhu and Yuanfang Hu for technical discussions.

I am deeply thankful to Michael Jackson and Alan Lam at Synopsys, and Rick Pier at Mentor Graphics. They provided me valuable intern opportunities and exposed me to a different field that complements my research work in school.

I would like to thank my parents and brother for their support and care. In particular, I own a lot of thanks to my father for his guidance on my career and constant encourage ever since my childhood. My final thanks go to my husband, Shengrong Lin, for his love, care and patience. My Ph.D. study could not have been completed without him.

The research presented in this dissertation was supported by grants from the California MICRO program and Altera Corporation. Their support is greatly acknowledged.

The text of chapter III, in full, is a reprint of the material as it appears in Proc. Intl. Conf. on Computer-Aided Design 2005, Shuo Zhou, Bo Yao, Hongyu Chen, Yi Zhu, Chung-Kuan Cheng, Mike Hutton, Truman Collins, Sridhar Srinivasan, Nanchi Chou, and Peter Suaris, "Improving the Efficiency of Static Timing

Analysis with False Paths", ICCAD 2005. The text of chapter IV, in full, is a reprint of the material as it appears in Proc. Asia and South Pacific Design Automation Conf. 2006, Shuo Zhou, Bo Yao, Hongyu Chen, Yi Zhu, Chung-Kuan Cheng, and Mike Hutton, "Efficient Static Timing Analysis Using a Unified Framework for False Paths and Multi-Cycle Paths", ASP-DAC 2006. The dissertation author was the primary researcher and author and the co-authors listed in these publications directed and supervised the research which forms the basis for this chapter.

#### VITA

| 1976 | Born, Beijing, China                                                           |

|------|--------------------------------------------------------------------------------|

| 1999 | B.S. in Computer Science and Technology<br>Tsinghua University, Beijing, China |

| 2001 | M.S. in Computer Science and Technology<br>Tsinghua University, Beijing, China |

| 2006 | Ph.D. in Computer Science<br>University of California, San Diego               |

#### **PUBLICATIONS**

- S. Zhou and B. Yao and H. Chen and Y. Zhu and C.-K. Cheng and M. Hutton, Efficient Static Timing Analysis Using a Unified Framework for False Paths and Multi-Cycle Paths, ASP-DAC 2006, pp. 73-78

- S. Zhou and B. Yao and H. Chen and Y. Zhu and C.-K. Cheng and M. Hutton and et al., Improving the efficiency of Static Timing Analysis with False Paths, ICCAD 2005, pp. 527-531

- S. Zhou, B, Yao, J. Liu, C.-K. Cheng, Integrated Algorithmic Logical and Physical Design of Integer Multiplier, ASP-DAC 2005, pp. 1014- 1017

- J. Liu, S. Zhou, H. Zhu, C.-K Cheng, An Algorithmic Approach for Generic Parallel Adders, ICCAD 2003, pp. 734-740

#### FIELDS OF STUDY

Major Field: Computer Science Studies in VLSI CAD. Professor Chung-Kuan Cheng

#### ABSTRACT OF THE DISSERTATION

Static Timing Analysis in VLSI Design

by

#### Shuo Zhou

Doctor of Philosophy in Computer Science University of California, San Diego, 2006 Professor Chung-Kuan Cheng, Chair

The increasing complexity of digital designs and the requirement of timing measurements in various design stages make static timing analysis critical. Each design stage utilizes static timing analysis to evaluate the system performance, and then optimizes the design accordingly. An accurate and efficient timing analysis package is crucial for the success of the whole design process. We studied three important problems in static timing analysis: false paths, multi-cycle paths, and hierarchical timing analysis.

Static timing analysis should deal with false paths and multi-cycle paths to produce accurate timings. Previous published works focused on dealing with false paths in static timing analysis. There are several approaches, such as labeling algorithm and node-splitting approach, using tags to label and eliminate false path timings. A large number of tags need to be created and propagated. Thus, the efficiency is deteriorated. For hierarchical timing analysis, timing analysis iteratively performed on flatten circuits suffers from low efficiency because of increasing design complexity.

Inspired by the gap between challenges and current sub-optimal solutions, we proposed three new techniques:

- A two-direction propagation is proposed which minimizes the number of tagged false path timings using a biclique covering approach. We proved that all the non-false paths are covered and all the false paths are removed.

A polynomial heuristic to perform the biclique covering minimization in minimal degree order is also introduced.

- 2. A framework unified processing false paths and multi-cycle paths is proposed which expands the tag-based approach for false paths to cover multi-cycle paths. Following the biclique covering approach for false paths, we devise time shifting for multi-cycle paths to improve the efficiency. We prove that the unified framework produces accurate timings.

- 3. An abstract timing model reduction technique is proposed for hierarchical timing analysis. We introduce an iterative biclique-star replacement technique to minimize the abstract timing model, thus improving the efficiency.

Combined the techniques proposed above, we provide an accurate and efficient static timing analysis package, which can be used in hierarchical design methodology.

# I Introduction

#### I.A Introduction

Efficient chip analysis becomes essential in nowadays circuit design due to the increasing design complexity and rapid technology change. Moore's law predicts that the number of transistors integrated on a die would be doubled every 18 to 14 months. With exponential growth in the number of transistor per chip, the design complexity keeps increasing. Meanwhile, the rapid technology change shortens product life cycles and makes time-to-market a critical issue. As a result, efficient chip analysis in early design stage is essential for reducing the number of design iterations in spite of increasing complexity.

Timing analysis is crucial for high performance digital circuit design as a part of chip analysis. Traditionally, high-performance integrated circuits are characterized by the clock frequency at which they operate. The timing analysis algorithm gauges the ability of a circuit operating at the specified speed. Two methods are used for timing analysis: dynamic simulation and static timing analysis. Dynamic simulation methods perform circuit level simulation, which suffers from high complexity when the circuit is large. Compared with dynamic simulation, static timing analysis is input vector independent. By performing worst case analysis, the analysis complexity is linear. Therefore, in early design stages static timing analysis is the widely used mechanism for timing measurement.

Motivated by the gap between challenges of increasing design complexity and limited accuracy and efficiency, our dissertation focused on three problems in static timing analysis: false paths, multi-cycle paths and hierarchical timing analysis.

The remainder of the chapter is organized as follows. Section I.B introduces the spectrum of chip analysis. Section I.C introduces static timing analysis in VLSI design flow. Section I.D formulates the problems of false paths, multi-cycle paths, and hierarchical timing analysis. Section I.E is the dissertation organization.

## I.B Spectrum of Chip Analysis

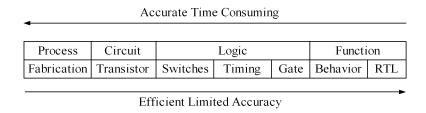

Chip analysis is performed on various levels to verifies circuit function and measures circuit timing. Fig.I.1 illustrates the analysis spectrum. Ordered from high-level to low-level, the simulations become more accurate, but they also become progressively more complex and time consuming.

**Function Analysis** Function level analysis includes behavior simulation and RTL simulation. The behavior of circuit module is modeled and tested. Gate delays and interconnect delays are ignored.

Logic Analysis Logic level analysis is used to verify both circuit functions and circuit timings. The circuit is extracted into models on various levels. Based on the models, analysis are performed on various levels including static timing analysis, gate-level simulation and switch-level simulation. Static timing analysis algorithms compute circuit timing without considering circuit functions. Gate-level simulator treats Boolean gates as black box which models both function and delay information. Switch-level simulator models transistors as switches. It is more accurate than gate-level simulation.

Circuit Analysis Circuit level analysis is used to simulate the electrical behavior of circuit based on circuit theories. The simulator requires models of transistors, describing their nonlinear voltage and current characteristics.

Fabrication Process Simulation Process simulation is used to simulate major

process steps in modern semiconductor fabrication technology based on physical models for diffusion, implantation, oxidation, silicidation and epitaxy.

Figure I.1 Spectrum of Chip Analysis

# I.C Static Timing Analysis in Design Flow

Static timing analysis algorithms evaluate circuit timing with linear complexity. Compared with dynamic simulation, static timing analysis is input vector independent. The circuit is formulated into a directed acyclic graph. On the graph, the worst case circuit timings, that is, the longest and shortest timing propagation paths in the circuit, are computed and verified with specified clock cycle. As a result, the analysis complexity is linear with respect to the number of edges in the timing graph.

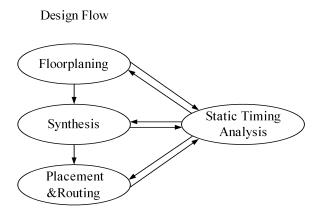

Static timing analysis plays a vital role in nowadays design flow. Besides longest and shortest timing propagation paths, static timing analysis can be used to compute arrival times, required arrival times and slacks at all points in the circuit, which are useful inputs for circuit optimizations. Therefore, each design stage, from floorplaning, logic synthesis, to placement and routing, utilizes static timing analysis to evaluate system performance, and then optimizes the design accordingly (Fig.I.2). For example, in performance-driven placement, the static timer reports critical paths, i.e., the paths violating the expected timing constraints, and slacks of non-critical paths to the placement step. Based on the timing reports, the placement optimization would optimize critical paths while sacrificing non-critical paths. Most of contemporary EDA companies develop static timing engines, such

as Prime Time [2] of Synopsys and incremental common timing engine (CTE) [1] of Cadence. These timing engines are used across the entire synthesis/place-and-route flow.

Figure I.2 Static Timing Analysis in the Design Flow

In this scenario, a successful design process relies on the accuracy and efficiency of static timing analysis. Traditional static timing analysis has limited accuracy due to the use of simplified delay models. Because the function of the circuit is not considered, static timing analysis may include false paths, which are paths not logically existing in the circuit. As a result, the optimization may wrongly focus on false paths and miss the real critical path. In general, conservative timing analysis leads to over-design, which increases the product cost. Meanwhile, as part of the inner loop of the optimization, the efficiency of static timing analysis becomes crucial. The improvement on accuracy should not deteriorate the efficiency.

#### I.D Problem Formulation

This section introduces the problems in static timing analysis we studied.

#### I.D.1 The Problem of False Paths

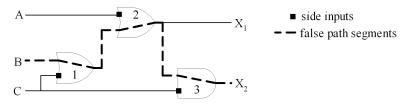

Static timing analysis should process false paths to produce accurate timings. A path which never be activated by any input vector is called *false path*. A false path example is shown in Fig.I.3. The path  $B->1->2->3->X_2$  is a false path. In order to allow the signal go through the path from input B to output  $X_2$ , the side inputs of the gates along the path should have non-dominant values, i.e., 0 for OR gates and 1 for AND gates. As a result, for OR gate 1 the logic value of input C should be 0, and for AND gate 3, the logic value of input C to be 1. Since there is a conflict, the signal can not go through path  $B->1->2->3->X_2$  to reach the output  $X_2$  under any input vector. As a result, the path will never be activated.

Figure I.3 False Path

False path problem has been studied extensively and a number of algorithms have been proposed to detect and eliminate false paths. The false problem was first addressed in [4], and the NP-completeness of the problem was proved in [32]. The criterions of false paths were presented in [7,8,11–13,31]. A number of algorithms have been proposed to detect and eliminate false paths from timing analysis. The satisfiability based heuristic algorithms were proposed in [7,8,22]. Based on the idea of data/control separation on primary inputs proposed in [45], an approximation scheme was proposed in [29], which controls the size of SAT problems.

We focused on the problem of timing analysis with specified false paths, which was first formulated and analyzed in [3].

Timing Analysis with Specified False Paths Problem Given the timing graph

of a circuit and a set of false paths, compute signal arrival times, required times and slacks at every vertex in the timing graph while disregarding false paths timings.

This problem is useful for several reasons. In many cases, users may know certain paths in circuits are false. Therefore, we should allow user to specify false paths and remove false path timing during analysis. Furthermore, based on a loose criterion defined in [du93], one can prove that delays in circuits will not be underestimate if false paths detected before analysis are removed from consideration during a series of physical optimization steps. Therefore, for repeatedly invoked timing analysis, there is no need to re-determine false paths during optimization.

#### I.D.2 The Problem of Multi-cycle Paths

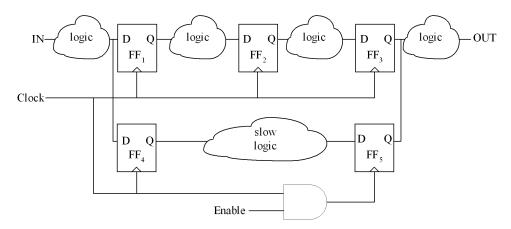

A multi-cycle path is a path that signals propagate longer than one clock cycle. Fig.I.4 illustrates a multi-cycle path. The paths from flip flop  $FF_4$  to flip flop  $FF_5$  are designed to be two-cycle paths, thus allowing the signals propagate through the slow logic.

Figure I.4 Multi-cycle Path

There are several published works dealing with multi-cycle paths. In [30], multi-cycle paths are considered as false paths in sequential circuits and ignored in minimum cycle computation. Various techniques were presented to detect and

eliminate multi-cycle false paths using sequential path tracing [17], state encoding [19], and non-false multi-cycle paths traversal [35]. Furthermore, multi-cycle false path elimination is exploited in performance optimization [37, 40].

Similarly as the problem of false paths, we can formulate timing analysis with specified multi-cycle paths as follows.

Timing Analysis with Multi-cycle Paths Given the timing graph of a circuit and a set of multi-cycle paths, compute signal arrival times, required times and slacks at every vertex in the timing graph while constraining multi-cycle paths using multi-cycle required time.

## I.D.3 The Problem of Hierarchical Timing Analysis

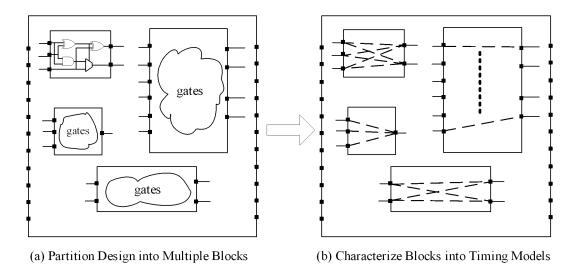

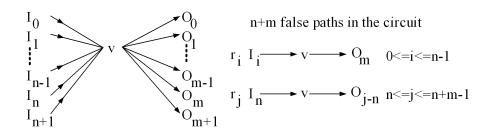

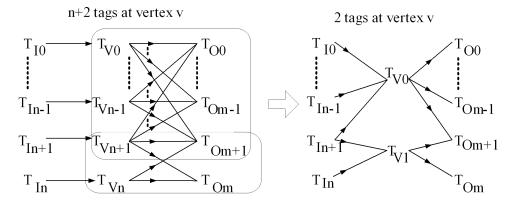

Hierarchical timing analysis approach can substantially reduce the computational complexity. A design is divided into multiple blocks Fig.I.5.(a) and each block is characterized into a timing model Fig.I.5.(b). For linear delay model, the timing calculation can be separated according to the boundary of the partitions. Assume the timing relations inside each block are fixed. By using pre-calculated timing models in timing analysis, we hide the details inside the blocks, thus reducing the analysis complexity.

Previous works on hierarchical timing analysis focused on characterizing accurate timing model using functional information. Conditional delay matrix was presented to characterize the timing model with timing propagation conditions [44]. Multiple modes of operation were considered in [46,47]. The idea of data/control separation on primary inputs was proposed in [45] to reduce the characterization complexity. A tighter sensitization criterion was used for false paths elimination [28].

Our research is mainly about abstract timing model reduction. After characterizing a functional block into a abstract timing model, the analysis complexity is linear to the number of edges in the abstract timing model for timing propagation. Therefore, our objective is to minimize the number of edges in the

Figure I.5 Hierarchical Timing Analysis

timing model.

Abstract Timing Model Reduction Given a hierarchical block, characterize an abstract timing model covering the longest and shortest path delays between any pair of input and output pins of the hierarchical block that minimizes the number of edges in the timing model.

# I.E Dissertation Organization

The remainder of the dissertation is organized as follows.

Chapter II reviews static timing analysis process, including the timing graph, timing constraints, delay models, the arrival and required arrival time propagation. The previous works on false paths and multi-cycle paths are also introduced.

In chapter III, we introduce efficient timing analysis dealing with false paths. We present a two-direction propagation technique which minimizes tagged false path timings using a biclique covering approach. We prove that the proposed approach can cover non-false path timings while eliminating false path timings. Finally, the experimental results are presented.

Chapter IV presents a unified framework for false paths and multi-cycle paths. The framework processes false paths and multi-cycle paths by a tag-based approach. We follow the biclique covering approach for false paths to minimize the number of tagged timings. The approach is efficient according to the computational complexity analysis. In the end, the correctness is proved and the experimental results are presented.

In chapter V, we talk about abstract timing model reduction. We introduce a biclique-star replacement technique to minimize the number of edges for timing propagation. Based on the biclique-star replacement technique, an iterative timing model reduction algorithm is presented. We apply the unified framework presented in chapter IV to cover false paths and multi-cycle paths in timing model. Finally, the experimental results are given.

Chapter VI gives conclusions and discusses future works.

# II Background and Previous

# Works

#### II.A Introduction

In this chapter, we briefly review static timing analysis algorithms and introduce previous works on the problems we studied. We first introduce the concepts evolved in static timing analysis including the timing graph, the interconnect and device model and the setup/hold time constraints. Based on these concepts, we introduce static timing analysis algorithms of the arrival time, required time and slack computation. In the end, we review several previous works on timing analysis with specified false paths and multi-cycle paths, and timing model reduction for hierarchical timing analysis.

# II.B Static Timing Analysis Overview

In static timing analysis, digital circuits are transformed into timing graph, and then the delays of the paths are verified with the corresponding timing constraints. We first review the concepts evolved in timing analysis, and then introduce the static timing analysis algorithm.

#### II.B.1 Timing Graph

The timing graph is a directed acyclic graph  $G = \{V, E\}$ , where V is a set of vertices and E is a set of edges. Each edge (u, v) is an ordered pair from vertex u to vertex v. The timing graph is acyclic because cyclic sequential paths are broken into combinational circuit segments align flip flops, and all the segments are folded into one clock cycle.

The input degree of vertex v,  $d^-(v)$ , is the number of edges ending at v. The output degree of v,  $d^+(v)$ , is the number of edges starting at v. The primary input set  $B = \{v|v \in V, d^-(v) = 0\}$  is the set of primary input vertices. The primary output set  $D = \{v|v \in V, d^+(v) = 0\}$  is the set of primary output vertices.

The primary inputs of graph G correspond to (1) primary inputs of the circuit, (2) outputs of flip flops, and (3) outputs of memories. The primary outputs of graph G correspond to (1) primary outputs of the circuit, (2) inputs of flip flops, and (3) inputs of memories. All other vertices correspond to inputs and outputs of combinational gates in the circuit. For gates in the circuit, there are edges from inputs to outputs. For nets in the circuit, there are edges from pins as drivers to pins as fan-outs.

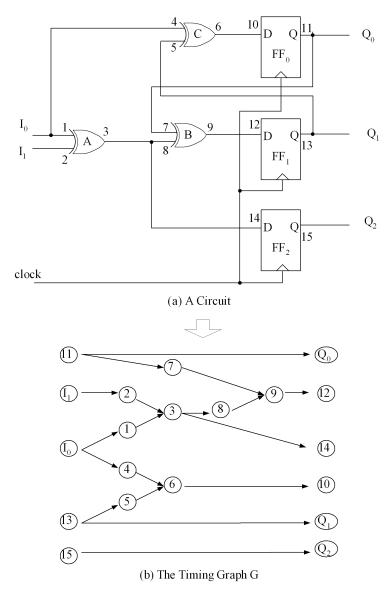

Fig.II.1 illustrates an example of the timing graph. A circuit is shown in Fig.II.1.(a). In the circuit, there are two primary inputs, i.e.,  $I_0$  and  $I_1$ , three primary outputs, i.e.,  $Q_0$ ,  $Q_1$ , and  $Q_2$ , and three flip flops, i.e.,  $FF_0$ ,  $FF_1$  and  $FF_2$ . The input and output pins of gates and flip flops are labeled. For example, the inputs and output of XOR gate A are labeled as 1, 2 and 3. Fig.II.1.(b) illustrates the timing graph G. Each vertex represents a pin in the circuit with the same label. For example, vertex 1 represents pin 1. In the timing graph, the primary input set contains five vertices  $I_0$ ,  $I_1$ , 11, 13, and 15, i.e.,  $B = \{I_0, I_1, 11, 13, 15\}$ . The primary output set contains six vertices  $Q_0$ ,  $Q_1$ ,  $Q_2$ , 10, 12 and 14, i.e.,  $D = \{Q_0, Q_1, Q_2, 10, 12, 14\}$ . For gates except flip flops, there are edges from inputs to outputs. For example, there are edges from the inputs to the output of XOR gate A, i.e., edge (1,3) and (2,3). For nets, there are edges from the vertex

as the driver to the vertices as the fanouts. For example, there are edges from the output of XOR gate A to the input of XOR gate B, i.e., edge (3,8).

Figure II.1 Timing Graph

A path p in graph G is a sequence of vertices and edges. We can represent the path p by only the edges in the path [21]. Each vertex v separates path p into a head and a tail. Since G is directed acyclic, all the paths in G are simple. A path starting from a vertex in the primary input set B is termed a prefix path  $p^-$ . A path ending at a vertex in the primary output set D is termed a suffix path  $p^+$ . A complete path is both a prefix and a suffix path, which starts from a vertex in the primary input set B, and ends at a vertex in the primary output set D. The prefix cone  $P^-(v)$  of a vertex v contains all the prefix paths ending at v. The suffix cone  $P^+(v)$  of v contains all the suffix paths starting at v.

In Fig.II.1, the prefix cone of vertex 3,  $P^{-}(3)$ , contains two prefix paths,  $\{(I_1, 2), (2, 3)\}$  and  $\{(I_0, 1), (1, 3)\}$ . The suffix cone of vertex 3,  $P^{+}(3)$ , contains two suffix paths,  $\{(3, 8), (8, 9), (9, 12)\}$  and  $\{(3, 14)\}$ . Path  $\{(I_0, 1), (1, 3), (3, 8), (8, 9), (9, 12)\}$  is a complete path from vertex  $I_0$  to vertex 12.

#### II.B.2 Delay Models

We use interconnect and device models to approximate the delay of gates and nets. The delay of a wire segment, i.e., the delay from a driver pin to a fan-out pin in a net, can be estimated using Elmore model. The delay from an input pin to an output pin of a gate can be evaluated using various device models. In linear delay model, the delay is described with explicit expression including two terms: a fixed intrinsic delay and a propagation delay. The intrinsic delay is independent of the output load. The propagation delay is the portion contributed by the load [9].

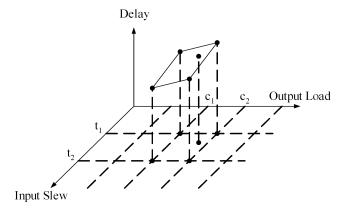

The nonlinear delay model uses two-dimension look-up-table to evaluate the gate delay [9]. The index of the first dimension is the output load capacitance, and the index of the second dimension is the input transition times, which is the time period between the 10% and 90% of the waveform.

Given a pair of load  $C_L$  and input transition time  $t_{in}$ , we find the adjacent pair of indexes with corresponding capacitances  $C_1$ ,  $C_2$ , and transition times  $t_1$ ,  $t_2$  that bound  $C_L$  and  $t_{in}$  from both sides, i.e.,  $C_1 \leq C_L \leq C_2$  and  $t_1 \leq t_{in} \leq t_2$  (Fig.II.2). Let  $D_i$ ,  $(1 \leq i \leq 4)$  be the delays at the four points, i.e.,  $D_1 = D(C_1, t_1)$ ,  $D_2 = D(C_2, t_1)$ ,  $D_3 = D(C_1, t_2)$ ,  $D_4 = D(C_2, t_2)$ . Based on  $D_i$ ,  $(1 \leq i \leq 4)$ , we approximate delay  $D(C_L, t_{in})$  using interpolation. The details of the interpolation can be found in [9].

Figure II.2 Two-dimensional Table-lookup Device Model

#### II.B.3 Timing Constraints

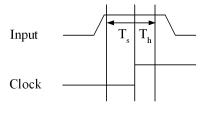

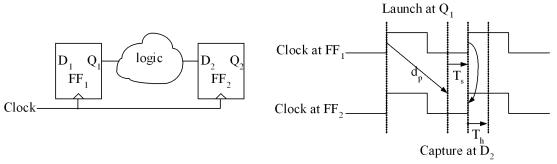

We verify the path delays with setup time and hold time constraints [26]. The setup time  $T_s$  is the minimum time period before the clocking event during which the signal must be stable to be validly captured. The hold time  $T_h$  is the minimum time period after the clocking event during which the input signal must be stable to be validly captured (Fig.II.3.(a)). The path delay  $d_p$  should satisfy the expressions as follows.

$$d_p < T_{period} - T_s$$

(II.1)

$$d_p > T_h, (II.2)$$

where  $T_{period}$  is the clock cycle.

Fig.II.3.(b) illustrates the setup and hold time constraints on path delays. The signal is launched at the output of flip flop  $FF_1$  by clock i and captured at the input of flip flop  $FF_2$  by clock i + 1. The longest path should be shorter than one clock cycle minus the setup time. The shortest path should be longer than the hold time. Otherwise, the new value will appear at the input of flip flop  $FF_2$  before  $FF_2$  has chance to catch the previous value from  $FF_1$ .

(a) Setup and Hold Times

(b) Relations between the Setup/Hold Time and the Path Delay

Figure II.3 Setup and Hold Time Constraints on Path Delays

## II.B.4 Static Timing Analysis Algorithms

There are two categories of timing analysis techniques: path enumeration techniques and block oriented analysis techniques. Path enumeration starts from a primary output PO in timing graph G and traces back through G until reaching a primary input PI. By doing so, the information of the path from PI to PO is complete. We compute the delays of the gates and nets on the path. As a result, the delay of the whole path equals the sum of all gate and net delays [25,38,41,43]. Since path enumeration techniques enumerate all the paths in the timing graph, it suffers from long run time because the number of paths in the circuit grows exponentially with the size of the circuit. However, by enumerating the paths, it's easier to ignore certain paths in circuits which are never activated.

Block oriented analysis performs longest and shortest path search on the timing graph [20,24]. It starts from primary inputs PI. At each PI, earliest and latest signal available times are denoted as signal arrival time  $Arr_{min}$  and  $Arr_{max}$ ,

respectively. Timing analysis propagates  $Arr_{min}$  and  $Arr_{max}$  to all the vertices in the timing graph. The earliest and latest arrival times at vertex v are computed as follows:

$$Arr_{min}(v) = \min(Arr_{min}(u) + d(u, v)), \tag{II.3}$$

$$Arr_{max}(v) = \max(Arr_{max}(u) + d(u, v)), \tag{II.4}$$

where d(u, v) is the delay of input edge (u, v) of v. Note various interconnect and device models can be used to estimate d(u, v). The Arrival-Time-Propagation algorithm is as follows.

#### Algorithm: Arrival-Time-Propagation

1. For each vertex v

If v is primary input add v into To-Compute vertex list;

- 2. Repeat

- (a) Get v from To-Compute list

- (b) If v is primary input  $Arr_{min}(v) = 0$ ,  $Arr_{max}(v) = 0$ ;

- (c) else

For each input edge (u, v)

A.

$$Arr_{min}(v) = min(Arr_{min}(v), Arr_{min}(u) + d(u, v));$$

B.

$$Arr_{max}(v) = max(Arr_{max}(v), Arr_{max}(u) + d(u, v));$$

- (d) For each output edge (v, w)

- i. Ready = 1;

- ii. For each input edge (x, w) of vertex wIf arrival times of vertex x not available Ready = 0;

- iii. If Ready add vertex w into To-Compute list;

- iv. Remove v from To-Compute list;

- 3. Until To-compute list is empty;

The algorithm calculates arrival times at all vertices in linear time. The computation is performed in topological order, i.e., a vertex v is added into a To-Compute vertex list only when the arrival times of vertices before v are available. By doing so, the arrival times of each vertex is only updated once. Thus, the complexity of timing analysis is linear to the number of edges in the graph. Because the timing graph is acyclic, all the vertices are updated.

The second step involves propagating the required times from primary outputs in a backward pass. At each primary output PO, based on the setup and hold times, the latest required time  $Req_{max}$  and earliest required time  $Req_{min}$  are as follows:

$$Req_{max} = T_{period} - T_s,$$

(II.5)

$$Req_{min} = T_h,$$

(II.6)

where  $T_s$  is setup time,  $T_h$  is hold time, and  $T_{period}$  is the clock cycle.

During backward propagation,  $Req_{max}$  and  $Req_{min}$  at vertex v are computed as follows:

$$Req_{min}(v) = \max(Req_{min}(u) - d(v, u)),$$

(II.7)

$$Req_{max}(v) = \min(Req_{max}(u) - d(v, u)),$$

(II.8)

where d(v, u) is the delay of output edge (v, u) of v. The Required-Time-Propagation algorithm is as follows.

#### Algorithm: Required-Time-Propagation

#### 1. For each vertex v

If v is primary output add v into To-Compute vertex list;

#### 2. Repeat

- (a) Get v from To Compute list

- (b) If v is primary output  $Req_{max} = T_{period} T_s$ ,  $Req_{min} = T_h$ ;

(c) else

For each output edge (v, u)

A.

$$Req_{min}(v) = max(Req_{min}(v), Req_{min}(u) - d(v, u));$$

B.

$$Req_{max}(v) = min(Req_{max}(v), Req_{max}(u) - d(v, u));$$

- (d) For each input edge (w, v)

- i. Ready = 1;

- ii. For each output edge (w, x) of vertex wIf required times of vertex x not available Ready = 0;

- iii. If Ready add vertex w into To-Compute list;

- iv. Remove v from To-Compute list;

- 3. Until To-compute list is empty;

With arrival times and required times, the timing slacks at vertex v are defined as follows:

$$slack_{min}(v) = Arr_{min}(v) - Req_{min}(v)$$

(II.9)

$$slack_{max}(v) = Req_{max}(v) - Arr_{max}(v).$$

(II.10)

If  $slack_{max}(v)$  is negative, the path violates the setup constraint II.1. If  $slack_{min}(v)$  is negative, the path violates the hold constraint II.2.

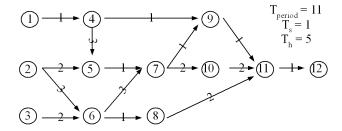

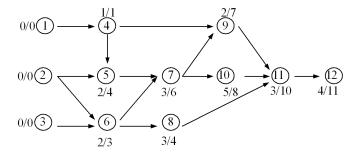

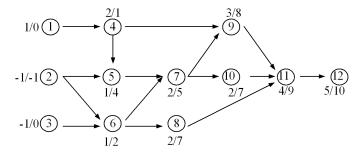

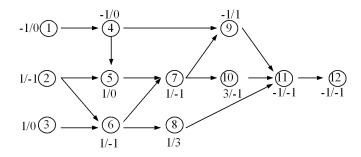

In Fig.II.4, we use an example to show the timing analysis process. Fig.II.4.(a) illustrates the timing graph with clock cycle  $T_{period} = 11$ , setup time  $T_s = 1$ , and hold time  $T_h = 5$ . The values attached on edges are delays. Fig.II.4.(b) illustrates the earliest and latest arrival times  $Arr_{min}(v)/Arr_{max}(v)$  by every vertex v. For example by vertex 5,  $Arr_{min}(5) = \min(Arr_{min}(4) + 3, Arr_{min}(2) + 2) = 2$  and  $Arr_{max}(v) = \max(Arr_{max}(4) + 3, Arr_{max}(2) + 2) = 4$ .

Fig.II.4.(c) illustrates the earliest and latest arrival times  $Req_{min}(v)/Req_{max}(v)$ by every vertex v. For primary output 12, the earliest required time  $Req_{min}(12) = T_h = 5$  and the latest required time  $Req_{max}(12) = T_{period} - T_s = 10$ . For internal vertex 7, the earliest required time  $Req_{min}(7) = \max(Req_{min}(9) - 1, Req_{min}(10) - 2) = 2$ , and the latest required time  $Req_{max}(7) = \min(Req_{max}(9) - 1, Req_{max}(10) - 2) = 5$ .

Fig.II.4.(d) illustrates the slacks  $Slack_{min}(v)/Slack_{max}(v)$  by vertices. For example, by vertex 7,  $Slack_{min}(7) = Arr_{min}(7) - Req_{min}(7) = 1$  and  $Slack_{max}(7) = Req_{max}(7) - Arr_{max}(7) = -1$ . Since  $Slack_{max}(7)$  is negative, we trace the negative slack to get the path violating the setup time constraint, i.e., path  $\{(2,6), (6,7), (7,10), (10,11), (11,12)\}$ . Similarly, we can trace the negative  $Slack_{min}$ s to get the path violating the hold time constraint, i.e., path  $\{(1,4), (4,9), (9,11), (11,12)\}$ .

# II.C Previous Works on Timing Analysis Dealing with False Paths and Multi-cycle Paths

In this section, we first introduce the exceptional rules on timing graph for false paths and multi-cycle paths. Then, we reviews previous works dealing with specified false paths and multi-cycle paths in static timing analysis, i.e., tagbased approach [3, 16] and node-splitting approach [5, 6], and edge-mask based approach [23].

#### II.C.1 General Rule and Exceptional Rules

The general rule on graph G is that the complete path p in G satisfies the short-path and long-path delay constraints in equation II.2 and II.1, i.e.,  $T_h < d_p < T_{period} - T_s$ , where  $d_p$  is the path delay,  $T_{period}$  is the clock cycle,  $T_h$  and  $T_s$  are hold and setup time constraints.

An exceptional rule r is represented by a subgraph  $G_r = \{V_r, E_r\}$ , a pair of hold and setup time  $(h_r, s_r)$ , and a priority  $p_r$ .

Hold and Setup Time The hold and setup time correspond to the short-path and long-path delay constraints. For a k-cycle subgraph,  $(h_r, s_r)$  is the k-

(a) The Timing Graph: Delays Attached on Edges.

(b) Earliest and Latest Arrival Times at Vertices

(c) Earliest and Latest Required Times at Vertices

(d) Slacks for Hold and Setup Times at Vertices

Figure II.4 Static Timing Analysis Algorithm Computing Arrival Times, Required Times and Slacks

cycle hold and setup time defined as follows.

$$h_r = (k-1) \times T_{period} + T_h \tag{II.11}$$

$$s_r = k \times T_{period} - T_s.$$

(II.12)

For the false subgraph, the hold time and setup time are unbounded, i.e.,  $-\infty$  and  $+\infty$ , respectively.

Subgraph Subgraph  $G_r$  describes a set of false paths or multi-cycle paths governed by rule r. The input set of rule r, denoted as  $B_r$ , is a set of vertices in  $G_r$  which have no input edges in  $E_r$ . The output set of rule r, denoted as  $D_r$ , is a set of vertices in  $G_r$  which have no output edges in  $E_r$ . A path in  $G_r$  starting from a vertex in  $B_r$  is termed a prefix path in  $G_r$ . A path in  $G_r$  ending at a vertex in  $D_r$  is termed a suffix path in  $G_r$ . If a path in  $G_r$  is both a prefix path and a suffix path in  $G_r$ , the path is a complete path in  $G_r$ . A path p is a false path or multi-cycle path governed by rule r if the intersection of p and  $E_r$  is a complete path in subgraph  $G_r$ . All the paths governed by rule r are constrained by an inequality  $h_r \leq delay(p) \leq s_r$ .

**Priority** If a path is governed by a set of rules, rule r with the highest priority  $p_r$  supersedes others.

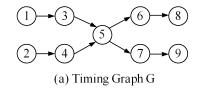

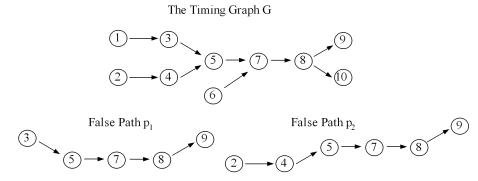

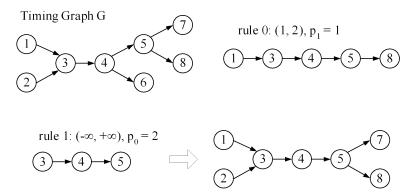

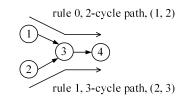

Fig.II.5 illustrates a timing graph and two rules represented by a false subgraph  $G_0$  and multi-cycle subgraph  $G_1$ . The input set of rule 0 contains vertex 3, i.e.,  $B_0 = \{3\}$ , and the output set of rule 0 contains vertices 6 and 9, i.e.,  $D_0 = \{6,9\}$ . Path  $\{(1,3), (3,5), (5,6), (6,8)\}$  is a false path because it contains a complete path  $\{(3,5), (5,6)\}$  in subgraph  $G_0$ . Another path  $\{(2,4), (4,5), (5,7), (7,9)\}$  is a 2-cycle path because it belongs to the subgraph  $G_1$ . Complete path  $\{(1,3), (3,5), (5,7), (7,9)\}$  belongs to both  $G_0$  and  $G_1$ . Because the priority of rule 0, i.e.,  $p_0 = 2$ , is higher than the priority of rule 1, i.e.,  $p_1 = 1$ , the complete path is a false path.

We formulate rule sets at every vertex and edge in graph G to extract the rules:

rule 0:  $G_0$ ,  $(h_0, s_0) = (-\infty, +\infty)$ ,  $p_0 = 2$  rule 1:  $G_1$ ,  $(h_1, s_1) = (1, 2)$ ,  $p_1 = 1$ (3)

(5)

(7)

(9)

(b) False and Multi-cycle Subgraph Rule

Figure II.5 False and Multi-cycle Subgraph Rules: False subgraph rule 0 and multi-cycle subgraph rule 1

- Starting Rule set  $F(v) = \{r | v \in B_r\}$  contains the rules starting from vertex v;

- Ending Rule set  $T(v) = \{r | v \in D_r\}$  contains the rules ending at vertex v;

- Edge Rule set  $I(u,v) = \{r | (u,v) \in E_r\}$  contains the rules covering edge (u,v).

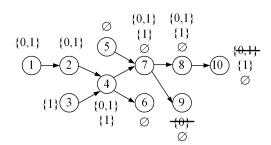

In Fig.II.5, vertex 3 has starting rule set  $F(3) = \{0\}$ , ending rule set  $T(3) = \emptyset$ . For vertex 9, starting rule set  $F(9) = \emptyset$ , and ending rule set  $T(9) = \{0,1\}$ . The edge rule set of edge (5,7) contains rules 0 and 1, i.e.,  $I(5,7) = \{0,1\}$ .

#### II.C.2 Timing Analysis with Tags

The overall procedure of the tag-based approach is the same as the Arrival-Time-Propagation process except that tags are computed for false path timing during the propagation. Each tag is a rule set of false subgraphs. According to the false path information in the tags, false path timings are distinguished from non-false path timings, and removed after the timing propagation. Rule sets for prefix paths or suffix paths are defined as follows.

**Definition II.C.1** (Prefix and Suffix Rule Sets) Given a prefix path  $p^-$ , the

prefix rule set of  $p^-$  is  $R(p^-) = \{r|p^- \cap E_r \text{ is both a prefix path in } G_r \text{ and the tail}$  of  $p^-\}$ . Given a suffix path  $p^+$ , the suffix rule set of  $p^+$  is  $R(p^+) = \{r|p^+ \cap E_r \text{ is both a suffix path in } G_r \text{ and the head of } p^+\}$ .

Conceptually, the prefix or suffix rule set indicates whether the prefix or suffix path belongs to the false path of a rule. In Fig.II.6, the rule set of prefix path  $p_0^- = \{(2,3), (3,4), (4,5)\}$  contains rule 0 because  $p_0^-$  is the prefix of the false path  $\{(2, 3), (3, 4), (4, 5), (5, 7), (7, 9)\}$ . Another prefix path  $p_1^- = \{(2,3), (3,4), (4,5), (5,6)\}$  exits from the subgraph of rule 0 at vertex 5. Since vertex 5 is not an ending vertex of rule 0, prefix path  $p_1^-$  does not belong to the false path of rule 0. Therefore, rule set  $R(p_1^-)$  does not contain rule 0.

Figure II.6 Prefix Rule Sets

The following algorithm computes the arrival times and the rule sets at each vertex.

#### Algorithm Rule-Set-Computation(v)

- 1. If vertex v is a primary input produce a rule set  $R = \emptyset$  at vertex v;

- 2. else

For each edge (u, v)

For each rule set R at vertex u

(a)

$$R' = (R \cup F(u)) \cap I(u, v);$$

(b) if

$$(R' \cap T(v) = \emptyset)$$

i.

$$Arr_{max}(v, R') = max(Arr_{max}(v, R'), Arr_{max}(u, R) + d(u, v));$$

ii.

$$Arr_{min}(v, R') = min(Arr_{min}(v, R'), Arr_{min}(u, R) + d(u, v));$$

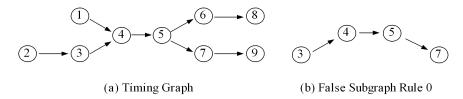

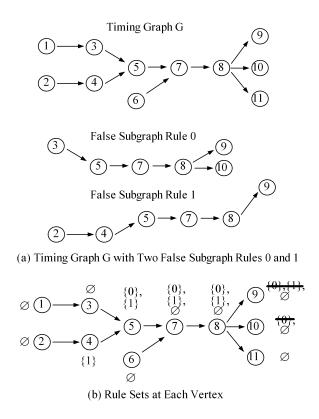

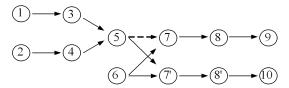

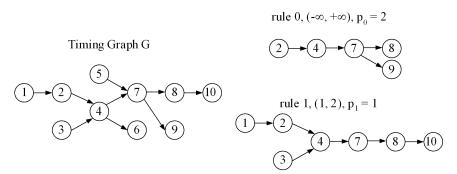

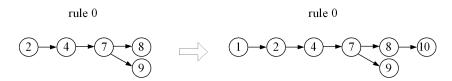

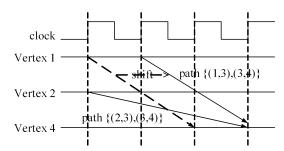

Fig.II.7.(a) illustrates timing graph G with two false subgraph rules 0 and 1. In Fig.II.7.(b), we compute the rule sets in a forward propagation. For example, the rule sets at several vertices are as follows:

- At the primary input vertices 1 and 2, the rule sets are  $\varnothing$ .

- At vertex 4, we propagate the rule set  $\varnothing$  of vertex 2 through the edge (2, 4) using the equation  $R' = (\varnothing \cup F(2)) \cap I(2,4)$ , where starting rule set  $F(2) = \{1\}$ , and edge rule set  $I(2,4) = \{1\}$ . We intersect the produced rule set  $R' = \{1\}$  with ending rule set T(4), where  $T(4) = \varnothing$ . Because the intersection is  $\varnothing$ , we compute the arrival time  $Arr_t(4, R')$ , where  $R' = \{1\}$ .

- At vertex 9, we first produce three rule sets  $\{0\}$ ,  $\{1\}$ , and  $\varnothing$  by propagating the rule sets at vertex 8. Because ending rule set  $T(9) = \{0, 1\}$ , intersection  $\{0\} \cap T(9)$  is  $\{0\}$ , which means vertex 9 is the ending vertex of the false path in rule 0. Therefore, we remove the rule set  $\{0\}$  and the false path arrival time  $Arr_t(9, \{0\})$ . Similarly rule set  $\{1\}$  and the false path arrival time  $Arr_t(9, \{1\})$  is also removed. Finally only the non-false path arrival time  $Arr_t(9, \varnothing)$  is produced at vertex 9.

The correctness of the algorithm is ensured by theorem II.C.1.

**Theorem II.C.1** After a forward Rule-Set-Computation, at each vertex v, the arrival times labelled by prefix rule sets cover the arrival times of prefix paths in prefix cone  $P^-(v)$ . After a backward Rule-Set-Computation, the arrival times labelled by suffix rule sets cover the arrival times of suffix paths in suffix cone  $P^+(v)$ .

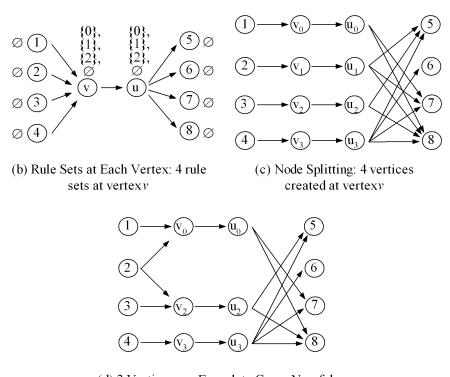

#### II.C.3 Node Splitting Approach

The node-splitting approach follows previous works [27, 39] to remove false paths from the timing graph using node splitting and edge removal [5,6]. On the false path, it splits the vertices with multiple input edges in topological order

Figure II.7 Rule Set Computation

until arriving at the last vertex with multiple output edges. Then the edges only belonging to false paths are removed.

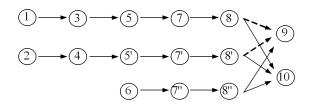

In Fig.II.8.(a), there is a timing graph including two false paths  $p_1$  and  $p_2$ . Fig.II.8.(b), illustrates the node splitting in topological order from the primary inputs to the primary outputs.

- Vertex 5 is the first vertex with multiple input edges, which is split into two vertices 5 and 5'.

- Vertex 7 has three input edges, (5, 7), (5',7), and (6, 7), after vertex 5 is split. Therefore, vertex 7 is split into three new vertices 7, 7', and 7".

- Finally vertex 8 is split into three new vertices. The edges (8, 9) and (8', 9) are removed, because they only belong to false paths.

Node splitting can also be performed in backward direction, which splits

(a) Timing Graph G including Two False Paths p<sub>0</sub> and p<sub>1</sub>

(b) Node Splitting from Primary Inputs to Primary Outputs

(c) Node Splitting from Primary Outputs to Primary Inputs

Figure II.8 Node Splitting

the vertices with multiple output edges. Fig.II.8 illustrates node splitting proceeding from primary outputs to primary inputs.

Conceptually, each newly created vertex corresponds to a rule set. For example, on the timing graph in Fig.II.8.(a), we consider false path  $p_1$  as rule 0, false path  $p_2$  as rule 1, and compute the rule sets. At vertex 5, rule sets are  $\{0\}$  and  $\{1\}$  which corresponds to new vertices 5 and 5' in Fig II.8.(b), respectively.

The node splitting approach identifies the optimal set of vertices for splitting. For example in Fig.II.8.(c), vertex 5 is not split because the false paths in rule 0 and rule 1 share the common suffix path  $\{(5, 7), (7, 8), (8, 9)\}$  starting at

vertex 5. As a result, removing the edge (5, 7) can remove both two false paths.

#### II.C.4 Multi-clock Domain Analysis with Edge-Masks

An edge-mask data structure is proposed to deal with specified false paths and multi-cycle paths in timing analysis [23]. The false paths and multi-cycle paths are seen to function as multi-clock domain cases. Each edge in the netlist is attached an edge-mask, which represents the reachability between multi-clock domains in the graph. By using edge-masks to filter standard analysis traversals in each abstract clock domain, unnecessary computation time is reduced.

#### II.D Abstract Timing Model Reduction

In this section, we first introduce the terminologies including the abstract timing model of a hierarchical block, the bipartite timing model and the delay matrix of a bipartite timing model. Then, we introduce previous works on timing model reduction.

#### II.D.1 Terminology

The timing graph of a hierarchical block H is a weighted graph, denoted as  $G_H$ . The weight of each edge (i, j), denoted as edge delay  $d_{i,j}$ , is the corresponding gate or interconnect delay estimated based on the linear delay model. The delay of a path from input i to output j, denoted as  $d_{p_{i,j}}$ , is the total delay of edges on the path. The shortest path delay from input i to output j in  $G_H$ , denoted as  $d_{H_{i,j}}^{min}$ , is the minimum of all path delays  $d_{p_{i,j}}$  in  $G_H$ . The longest path delay from input i to output j, denoted as  $d_{H_{i,j}}^{max}$ , is the maximum of all path delays  $d_{p_{i,j}}$  in  $G_H$ .

The timing model of a hierarchical block H is a weighted graph  $G_M$ , which has the same input set B and output set D as timing graph  $G_H$ . The shortest and longest path delays from input i to output j in  $G_M$  are equal to  $d_{H_{i,j}}^{min}$  and  $d_{H_{i,j}}^{max}$  in  $G_H$ . Note the internal vertices and edges in timing model  $G_M$  may or

may not be the same as those in timing graph  $G_H$ . A bipartite maximum delay model, denoted as  $G_M^{max}$ , is a timing model, in which any vertex is either an input or an output. On each edge (i,j) in  $G_M^{max}$  the attached edge delay  $d_{i,j}$  is equal to the longest path delay  $d_{H_{i,j}}^{max}$ . A bipartite minimum delay model, denoted as  $G_M^{min}$ , is a timing model, in which any vertex is either an input or an output. On each edge (i,j) in  $G_M^{min}$  the attached edge delay  $d_{i,j}$  is equal to the shortest path delay  $d_{H_{i,j}}^{min}$ .

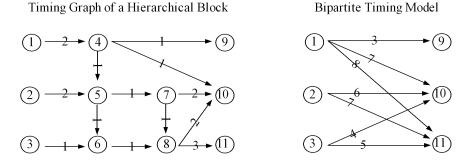

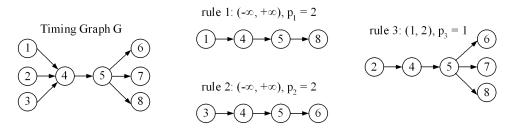

Fig.II.9.(a) illustrates a timing graph  $G_H$  of a hierarchical block and the corresponding bipartite maximum delay model  $G_M^{max}$ . The input set contains three inputs, i.e.,  $B = \{1, 2, 3\}$ . The output set contains three outputs, i.e.,  $D = \{9, 10, 11\}$ . On edges between connected inputs and outputs the longest path delays are attached. For example, the longest path from input 1 to output 10 is  $\{(1, 4), (4, 5), (5, 7), (7, 8), (8, 10)\}$  which has delay 7. Thus, the delay attached on edge (1, 10) is 7.

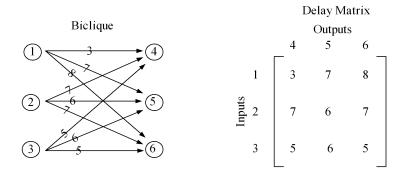

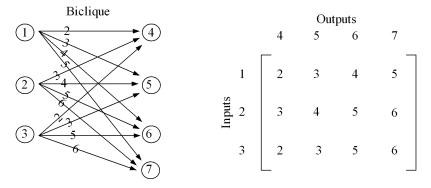

We formulate a delay matrix  $M(G_M^{max})$  based on the edge delays in bipartite maximum delay model  $G_M^{max}$ . The number of rows, denoted as r, is the number of inputs, i.e., r = |B|. The number of columns, denoted as c, is the number of outputs, c = |D|. The element on the ith row the jth column, denoted as  $m_{i,j}$ , is (1) edge delay  $d_{i,j}$  if edge  $(i,j) \in E$ , or (2)  $\infty$  if input i disconnects with output j. The input delay vector of input i, denoted as  $I_i$ , is a set of elements on the ith row in matrix M, i.e.,  $I_i = \{m_{i,j} | j \in [1..c]\}$ . The output delay vector of output j, denoted as  $O_j$ , is a set of elements on the jth column in matrix M, i.e.,  $O_j = \{m_{i,j} | i \in [1..r]\}$ . Similarly, we can formulate the delay matrix for the bipartite minimum delay model.

The delay matrix of the bipartite maximum delay model in Fig.II.9.(a) is shown in Fig.II.9.(b). Each row in the matrix contains the edge delays from one input to all the connected outputs. For example, the first row contains edge delays from input 1 to outputs 9, 10, and 11, i.e.,  $d_{1,9} = 3$ ,  $d_{1,10} = 7$  and  $d_{1,11} = 8$ . If the input is disconnected with an output, the delay is set to  $\infty$ . For example, input 2

is disconnected with output 9, thus, the element on the 2nd row the 1st column is set to  $\infty$ .

(a) Bipartite Timing Model based on a Timing Graph: Delays Attached on Edges

Outputs

$$9 \quad 10 \quad 11$$

$1 \quad 3 \quad 7 \quad 8$

$\infty \quad 6 \quad 7$

$0 \quad 0 \quad 7$

$0 \quad 0 \quad 0 \quad 0 \quad 0$

$0 \quad 0 \quad 0 \quad 0 \quad 0$

$0 \quad 0 \quad 0 \quad 0 \quad 0$

$0 \quad 0 \quad 0 \quad 0 \quad 0$

$0 \quad 0 \quad 0 \quad 0 \quad 0$

$0 \quad 0 \quad 0 \quad 0 \quad 0$

$0 \quad 0 \quad 0 \quad 0 \quad 0$

$0 \quad 0 \quad 0 \quad 0 \quad 0$

$0 \quad 0 \quad 0 \quad 0 \quad 0$

$0 \quad 0 \quad 0 \quad 0 \quad 0$

$0 \quad 0 \quad 0 \quad 0 \quad 0$

$0 \quad 0 \quad 0 \quad 0 \quad 0$

$0 \quad 0 \quad 0 \quad 0 \quad 0$

$0 \quad 0 \quad 0 \quad 0 \quad 0$

$0 \quad 0 \quad 0 \quad 0 \quad 0$

$0 \quad 0 \quad 0 \quad 0 \quad 0$

$0 \quad 0 \quad 0 \quad 0 \quad 0$

$0 \quad 0 \quad 0 \quad 0 \quad 0$

$0 \quad 0 \quad 0 \quad 0 \quad 0$

$0 \quad 0 \quad 0 \quad 0 \quad 0$

$0 \quad 0 \quad 0 \quad 0 \quad 0$

$0 \quad 0 \quad 0 \quad 0 \quad 0$

$0 \quad 0 \quad 0 \quad 0 \quad 0$

$0 \quad 0 \quad 0 \quad 0 \quad 0$

$0 \quad 0 \quad 0 \quad 0 \quad 0$

$0 \quad 0 \quad 0 \quad 0 \quad 0$

$0 \quad 0 \quad 0 \quad 0 \quad 0$

$0 \quad 0 \quad 0 \quad 0 \quad 0$

$0 \quad 0 \quad 0 \quad 0 \quad 0$

$0 \quad 0 \quad 0 \quad 0 \quad 0$

$0 \quad 0 \quad 0 \quad 0 \quad 0$

$0 \quad 0 \quad 0 \quad 0 \quad 0$

$0 \quad 0 \quad 0 \quad 0 \quad 0$

$0 \quad 0 \quad 0 \quad 0 \quad 0$

$0 \quad 0 \quad 0 \quad 0 \quad 0$

$0 \quad 0 \quad 0 \quad 0 \quad 0$

$0 \quad 0 \quad 0 \quad 0 \quad 0$

$0 \quad 0 \quad 0 \quad 0 \quad 0$

$0 \quad 0 \quad 0 \quad 0 \quad 0$

$0 \quad 0 \quad 0 \quad 0 \quad 0$

$0 \quad 0 \quad 0 \quad 0 \quad 0$

$0 \quad 0 \quad 0 \quad 0 \quad 0$

$0 \quad 0 \quad 0 \quad 0 \quad 0$

$0 \quad 0 \quad 0 \quad 0 \quad 0$

$0 \quad 0 \quad 0 \quad 0 \quad 0$

$0 \quad 0 \quad 0 \quad 0 \quad 0$

$0 \quad 0 \quad 0 \quad 0 \quad 0$

$0 \quad 0 \quad 0 \quad 0 \quad 0$

$0 \quad 0 \quad 0 \quad 0 \quad 0$

$0 \quad 0 \quad 0 \quad 0 \quad 0$

$0 \quad 0 \quad 0 \quad 0 \quad 0$

$0 \quad 0 \quad 0 \quad 0 \quad 0$

$0 \quad 0 \quad 0 \quad 0 \quad 0$

$0 \quad 0 \quad 0 \quad 0 \quad 0$

$0 \quad 0 \quad 0 \quad 0 \quad 0$

$0 \quad 0 \quad 0 \quad 0 \quad 0$

$0 \quad 0 \quad 0 \quad 0 \quad 0$

$0 \quad 0 \quad 0 \quad 0 \quad 0$

$0 \quad 0 \quad 0 \quad 0 \quad 0$

$0 \quad 0 \quad 0 \quad 0 \quad 0$

$0 \quad 0 \quad 0 \quad 0 \quad 0$

$0 \quad 0 \quad 0 \quad 0 \quad 0$

$0 \quad 0 \quad 0 \quad 0 \quad 0$

$0 \quad 0 \quad 0 \quad 0 \quad 0$

$0 \quad 0 \quad 0 \quad 0 \quad 0$

$0 \quad 0 \quad 0 \quad 0 \quad 0$

$0 \quad 0 \quad 0 \quad 0 \quad 0$

$0 \quad 0 \quad 0 \quad 0 \quad 0$

$0 \quad 0 \quad 0 \quad 0 \quad 0$

$0 \quad 0 \quad 0 \quad 0 \quad 0$

$0 \quad 0 \quad 0 \quad 0 \quad 0$

$0 \quad 0 \quad 0 \quad 0 \quad 0$

$0 \quad 0 \quad 0 \quad 0 \quad 0$

$0 \quad 0 \quad 0 \quad 0 \quad 0$

$0 \quad 0 \quad 0 \quad 0 \quad 0$

$0 \quad 0 \quad 0 \quad 0 \quad 0$

$0 \quad 0 \quad 0 \quad 0 \quad 0 \quad 0$

$0 \quad 0 \quad 0 \quad 0 \quad 0 \quad 0$

$0 \quad 0 \quad 0 \quad 0 \quad 0 \quad 0$

$0 \quad 0 \quad 0 \quad 0 \quad 0 \quad 0$

$0 \quad 0 \quad 0 \quad 0 \quad 0 \quad 0$

$0 \quad 0 \quad 0 \quad 0 \quad 0 \quad 0$

$0 \quad 0 \quad 0 \quad 0 \quad 0 \quad 0$

$0 \quad 0 \quad 0 \quad 0 \quad 0 \quad 0 \quad 0$

$0 \quad 0 \quad 0 \quad 0 \quad 0 \quad 0$

$0 \quad 0 \quad 0 \quad 0 \quad 0 \quad 0$

$0 \quad 0 \quad 0 \quad 0 \quad 0 \quad 0 \quad 0$

$0 \quad 0 \quad$

Figure II.9 Bipartite Timing Model and Delay Matrix

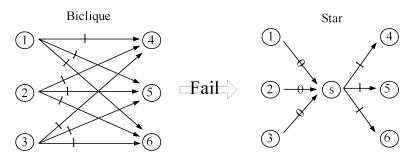

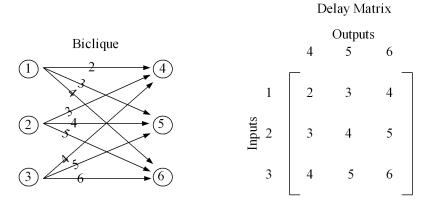

A biclique is a complete bipartite graph  $G_c = \{B_c, D_c, E_c\}$ , i.e.,  $\forall$  input i in input set  $B_c$  is connected with  $\forall$  output j in output set  $D_c$ , i.e.,  $E_c = \{(i,j)|i \in B_c, j \in D_c\}$ . Fig.II.10 illustrates a biclique and the corresponding delay matrix. Each pair of input and output is connected. In the delay matrix, there is no disconnected symbol  $\infty$ .

A star with a center vertex s is a weighted graph  $G_s = \{B_s, D_s, s, E_s\}$ , where  $B_s$  is the input set,  $D_s$  is the output set, s is the vertex at the center, and  $E_s$  is a set of edges from inputs to s and from s to outputs. Each edge has a weight. The weights of edges (i, s) and (s, j) are denoted as  $d_{i,s}$  and  $d_{s,j}$ , respectively.

Fig.II.11 illustrates a star. The vertex s at the center connects with all inputs and outputs. On each edge, a weight is attached, i.e., edge delay  $d_{i,s}$  or  $d_{s,j}$ . For example, edge delay  $d_{1,s}$  of edge (1,s) is 1.

Figure II.10 Biclique and the Delay Matrix

Figure II.11 Star

#### II.D.2 Timing Model Reduction

The previous published works on timing model reduction can be categorized into two groups: (1) reducing edges in timing graph  $G_H$ , and (2) constructing minimized model based on bipartite timing model  $G_M$ .

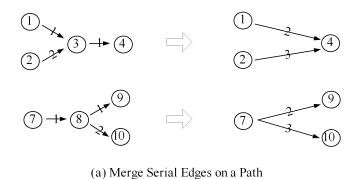

The reduction based on  $G_H$  starts from the original timing graph  $G_H$  of the block, and iteratively reduces the number of edges in the graph using graph transformations ([33,42]):

- 1. Simplify a path into one edge and attach the path delay on the edge (Fig.II.12.(a));

- 2. Merge edges sharing common input and output into one edge and attach the dominant delay on the edge (Fig.II.12.(b)).

The transformation is a greedy heuristic, which may not always produce the optimal solution. For example in Fig.II.12.(c), the heuristic fails to get the optimal.

Another category of methods tried to represent delay metrics into an abstract timing model and minimized the number edges in the abstract timing model. An optimal realization of a distance matrix problem is formulated as constructing a graph that preserves shortest-path distances while minimizing the total sum of edge weights [10,18]. In [14], the problem is studied on the case in which a collection of weighted graphs for compression are given. For the graph with unit edge weights, it's shown that the best compression can be achieved by replacing cliques by stars (Fig.II.12.(c)). The un-weighted bipartite graph compression is studied in [15]. The hardness of the graph compression problem is studied for the unit edge weights case [14].

(b) Merge Edges Sharing Common Input and Output

(c) Greedy Merging Edges Fails to Transform Biclique to Star

Figure II.12 Timing Model Reduction Based on Original Timing Graph

## III Timing Analysis with False Paths

#### III.A Introduction

In this chapter, we introduce a two-direction propagation approach to improve the efficiency of timing analysis with false paths. The tagged timings for false paths are collected when timing information can be shared. By doing so, we reduce the number tagged timings for timing propagation, thus improving the efficiency.

When false paths are dealt with in timing analysis, a large number of tags or vertices need to be created and propagated, thus, the analysis efficiency is deteriorated. Although there are techniques which reduce the number of timings with tags, the reduction depends on the timing values [16]. Because the timing values may change during the circuit optimization, the reduction is performed together with timing analysis, which induces a large run time penalty in the whole optimization process. The node splitting approach has the ability to identify the optimal set of nodes for splitting. However, it's not clear how to minimize the number of newly created tags when one vertex is split.

We propose a two-direction propagation technique which minimizes tags created at each vertex through a biclique covering approach. We follow the algorithm in [3] to compute prefix and suffix rule sets in two directions. By matching the prefix and suffix rule sets, we can achieve all non-false paths through the vertex. We cover the non-false paths using a biclique covering approach, and collect the prefix rule sets into rule collections. By doing so, the number of tagged false path timings is reduced. A formal proof ensures that we can propagate and keep merging the rule collections at every vertex in topological order, such that all the non-false paths are covered and all the false paths are removed.

Since computing the minimum biclique is NP complete [34, 36], we use a polynomial heuristic to perform the biclique covering minimization in minimal degree order. Because the minimization does not depend on the values of the timings, but depends on the false path specifications, the minimization is only incurred once as a preprocessing step. However, the benefit occurs repeatedly when timing analysis is called during the optimization.

We follow the experiments in [3] to test the proposed approach on the timing graph of a mesh. We also perform experiments on a set of industry test cases. For the industry test cases, comparing with the number of prefix rule sets, the number of the tags is reduced by 99%. Comparing with the node splitting approach, the improvement ratio is up to 48%. The run time of the minimization is only 380 seconds for the case with 533,224 nets.

The remainder of this paper is organized as follows. In section III.B, we use an example to explain the motivation of minimizing the number of tags. Section III.C introduces the two-direction propagation flow and the biclique covering approach. We prove that the algorithm can remove the false paths with minimized number of tags. The experimental results are presented in Section III.D.

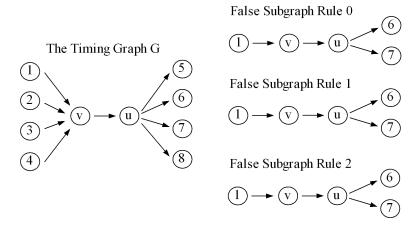

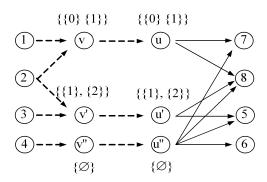

#### III.B Motivation

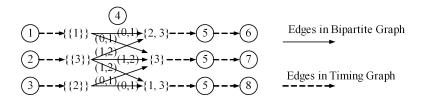

We observe the tag-based algorithms and find out that the number of tags can be reduced when the timing information can be shared. For example in Fig.III.1.(a), there are three rules: (1) rule 0 containing false paths from vertex 1, through vertices v and u, to vertices 5 and 6, (2) rule 1 containing a false path

from vertex 2, through vertices v and u, to vertex 6, and (3) rule 2 containing false paths from vertex 3, through vertices v and u, to vertices 6 and 7.

Suppose we follow the tag-based approach in [3] to scan from inputs toward outputs as shown in Fig.III.1.(b). We need four rule sets  $\{0\}$ ,  $\{1\}$ ,  $\{2\}$ , and  $\varnothing$  at vertex v to represent 4 distinct arrival times from inputs. If we follow the node splitting approach in [6], we need to split vertex v into four vertices  $v_0$ ,  $v_1$ ,  $v_2$ , and  $v_3$ . Fig.III.1 (c) illustrates the non-false paths after node splitting and edge removal. We can merge vertex  $v_1$  with vertices  $v_0$  and  $v_2$  as shown in Fig.III.1.(d) and still cover the time information of non-false paths from vertex 2 because the timing information on the common tails can be shared, i.e., 1) the non-false paths from vertex 2 to vertices 7 and 8 share common tails  $\{(v,u),(u,5)\}$  and  $\{(v,u),(u,8)\}$  with the non-false path from vertex 1 to vertices 7 and 8, and 2) the non-false paths from vertices 2 to vertices 5 and 8 share common tails  $\{(v,u),(u,7)\}$  and  $\{(v,u),(u,8)\}$  with the non-false paths from vertex 3 to vertices 5 and 8. Therefore, we reduce the number of split vertices from 4 to 3.

The example indicates some hints for the rule set minimization:

- The timing information labeled by rule sets can be shared when non-false paths contain common prefix or suffix paths.

- The rule set minimization requires information of complete non-false paths, while the forward sweeping or backward sweeping only provides information of prefix or suffix paths.

#### III.C Rule Collection Minimization

We propose a two-direction propagation to minimize the number of tags. We firstly use a backward propagation to produce rule sets for required arrival times. Then, we perform another forward propagation to produce rule sets for arrival times. When the timing information can be shared, we use a biclique covering approach to collect prefix rule sets into rule collections. Each distinct

(a) Timing Graph G with Three False Subgraph Rules 0, 1 and 2

(d) 3 Vertices are Enough to Cover Non-false Paths through Vertex *v*.

Figure III.1 Merging Rule Sets

arrival time needs a tag, which is a rule collection. Therefore, by minimizing the rule collections, we can reduce the number of tags of distinct arrival times, thus improving the efficiency of timing analysis.

In this section, we first define the rule collection and give the rule collection minimization algorithm. Then, we prove that the algorithm can remove the false paths without removing the non-false paths. The definition of the rule collection is as follows.

**Definition III.C.1** (Rule Collection) A rule collection at vertex v is a set of rule sets of prefix paths which ends at v, i.e.  $\Re(v) \subseteq \{R(p^-)|p^- \in P^-(v)\}$ , where  $P^-(v)$  is the prefix cone at v.

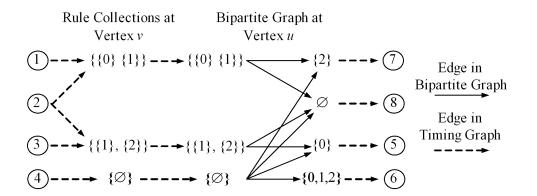

#### III.C.1 Main Flow of Rule Collection Minimization

The overall minimization flow is a two-direction propagation: a backward sweeping to compute suffix rule sets and another forward sweeping to minimize the rule collections. At each vertex, we compare the prefix and suffix rule sets to construct the non-false paths. After the construction, we use a biclique covering approach to cover non-false path timing with rule collections. Since each rule collection is the tag of a distinct arrival time, the primary object is to minimize the number of rule collections.

#### Main flow

- 1. Produce suffix rule sets by a backward sweeping;

- 2. For each vertex v in topological order

- (a) If vertex v is a primary inputs then produce an initial rule collection  $\{\emptyset\}$ ;

- (b) else

- i. for each edge (u, v)

for each  $\Re(u)$  Rule-Collection-Propagation  $(\Re(u), u, v)$ ;

#### ii. Rule-Collection-Minimization(v);

The Rule-Collection-Propagation  $(\Re(u), u, v)$  of step 2).b).i) computes the rule collections at vertex v by propagating the rule collections of vertex u, where edge (u, v) is an input of v. We will introduce the details of the routine in section III.C.4.

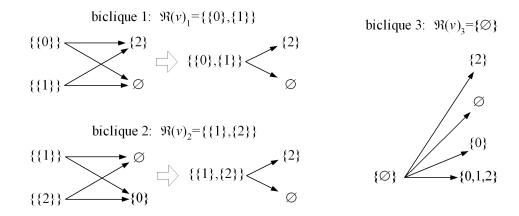

The Rule-Collection-Minimization (v) of step 2).b).ii) minimizes the rule collection in three steps: (1) performing intersections between rule collections and suffix rule sets, (2) constructing bipartite graph based on intersection results, and (3) covering edges in the bipartite graph with minimized number of bicliques. These three steps are introduced in section III.C.2 and III.C.3.

#### Algorithm: Rule-Collection-Minimization(v)

1. For each rule collection  $\Re(v)$  and suffix rule set  $R(p^+)$

Produce

$$Intersect(\Re(v), R(p^+)) = \{R(p^-)_i \cap R(p^+) | R(p^-)_i \in \Re(v)\};$$

- 2. Construct bipartite(v) based on the intersections;

- 3. Biclique-Covering(v);

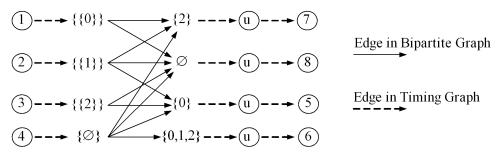

#### III.C.2 Intersection of Prefix Rule Collections with Suffix Rule Sets

We match prefix and suffix rule sets to achieve non-false paths through each vertex. Theorem II.C.1 ensures that the prefix and suffix rule sets at each vertex cover all prefix and suffix paths in the prefix and suffix cone. As a result, by matching false path information in the prefix and suffix rule sets, we can achieve all non-false paths while removing false paths.

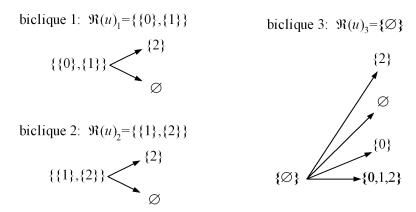

We use Rule-Set-Computation algorithm to compute the suffix rule sets at every vertex v [3]. For the case in Fig.III.1, the rule collections and suffix rule sets at vertex v are in the first column and first row of Table III.1. The suffix rule sets,  $\{0\}$ ,  $\{0, 1, 2\}$ ,  $\{2\}$ , and  $\varnothing$  correspond to the suffix paths,  $\{(v, u), (u, 5)\}$ ,  $\{(v, u), (u, 6)\}$ ,  $\{(v, u), (u, 7)\}$ , and  $\{(v, u), (u, 8)\}$ . The prefix rule sets,  $\{0\}$ ,  $\{1\}$ ,

$\{2\}$ , and  $\varnothing$  correspond to the prefix paths,  $\{(1,v)\}$ ,  $\{(2,v)\}$ ,  $\{(3,v)\}$ , and  $\{(4,v)\}$ . Without minimization, each prefix rule set produces a rule collection.

Table III.1 Intersections of Rule Collections and Suffix Rule Sets at Vertex v

|              |                   | $R(p^+)$          |                   |                   |                   |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|

|              |                   | {0}               | $\{0,1,2\}$       | {2}               | Ø                 |

|              | {{0}}}            | {{0}}             | {{0}}}            | $\{\varnothing\}$ | $\{\varnothing\}$ |

| $\{R(p^-)\}$ | {{1}}             | $\{\varnothing\}$ | {{1}}}            | $\{\varnothing\}$ | $\{\varnothing\}$ |

|              | {{2}}             | {Ø}               | {{2}}             | {{2}}             | $\{\varnothing\}$ |

|              | $\{\varnothing\}$ | $\{\varnothing\}$ | $\{\varnothing\}$ | $\{\varnothing\}$ | $\{\varnothing\}$ |

We intersect the prefix and suffix rule sets to gather the non-false paths through the vertex. Conceptually, the  $R(p^-) \cap R(p^+) = \emptyset$  means that the concatenation of the prefix path  $p^-$  and the suffix path  $p^+$  is a non-false path.

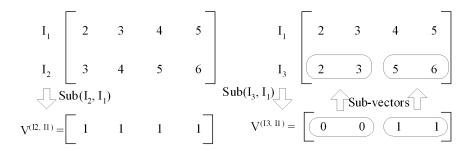

**Definition III.C.2** (Intersection of rule collection and rule set) The intersection between a rule collection  $\Re(v)$  and a suffix rule set  $R(p^+)$  intersects each prefix rule set in  $\Re(v)$  with  $R(p^+)$ , i.e.,  $Intersect(\Re(v), R(p^+)) = \{R(p^-)_i \cap R(p^+) | R(p^-)_i \in \Re(v)\}.$

Table III.1 shows the intersections at vertex v. For example, the second row contains the intersections of the rule collection  $\{R(p^-)\}=\{\{0\}\}$  with various suffix rule sets. The intersection with  $R(p^+)=\{0,1,2\}$  is  $\{\{0\}\}$ , which means the concatenation is a false path governed by rule 0. The intersection with  $R(p^+)=\{2\}$  is  $\{\varnothing\}$ , which means the concatenation is a non-false path.

#### III.C.3 Bipartite Graph and Biclique Covering

Based on the intersections, we construct a bipartite graph to cover the non-false paths through the vertex, and produce minimum biclique covering on the bipartite graph. By doing so, we can cover non-false paths with minimized number of rule collection tags.

The bipartite graph is constructed in two steps as follows.

• Add the prefix and suffix rule sets into the bipartite graph.

• If  $Intersection(\Re(v), R(p^+))$  only contains  $\varnothing$ , add an edge from  $\Re(v)$  to  $R(p^+)$  to represent the non-false path.