## UC San Diego UC San Diego Electronic Theses and Dissertations

## Title

Advanced CMOS circuits for microwave and millimeter-wave communications

**Permalink** https://escholarship.org/uc/item/2q76h2z4

**Author** Cetinoneri, Berke

Publication Date 2011

Peer reviewed|Thesis/dissertation

#### UNIVERSITY OF CALIFORNIA, SAN DIEGO

#### **Advanced CMOS Circuits for Microwave and Millimeter-Wave Communications**

A dissertation submitted in partial satisfaction of the requirements for the degree Doctor of Philosophy

in

Electrical Engineering (Electronic Circuits and Systems)

by

Berke Cetinoneri

Committee in charge:

Professor Gabriel M. Rebeiz, Chair Professor James F. Buckwalter Professor Gert Cauwenberghs Professor William S. Hodgkiss Professor Lawrence E. Larson

2011

Copyright Berke Cetinoneri, 2011 All rights reserved. The dissertation of Berke Cetinoneri is approved, and it is acceptable in quality and form for publication on microfilm and electronically:

Chair

University of California, San Diego

2011

### DEDICATION

To my parents, Ferdi and Sabahat

#### TABLE OF CONTENTS

| Signature Page    | e                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Dedication        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| Table of Contents |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| List of Figures   | svii                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| List of Tables    | xi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| Acknowledger      | nents                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| Vita and Public   | cations                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| Abstract of the   | Dissertation                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| Chapter 1         | Introduction11.1Thesis Overview1                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| Chapter 2         | W-Band Amplifiers with 6 dB Noise Figure and mW-Level 170-200 GHzDoublers in 45-nm CMOS2.1Introduction32.2Technology42.3W-Band Amplifier92.3.1Design92.3.2Measurements142.4W-to-G-Band Doubler162.4.1Design162.4.2Measurements202.5W-Band Amplifier and G-Band Doubler232.6Conclusion27Acknowledgement27                                                                                                                                                                              |  |  |  |

| Chapter 3         | Millimeter-Wave CMOS Switches       29         3.1       Introduction       29         3.2       Design       30         3.2.1       DC-70 GHz SP4T Switch       30         3.2.2       50-70 GHz SPDT and SP4T Switches       33         3.3       Implementation and Measurements       35         3.3.1       DC-70 GHz SP4T Switch       35         3.3.2       50-70 GHz SP4T Switch       35         3.3.4       Conclusion       41         3.5       Acknowledgement       46 |  |  |  |

| Chapter 4  | $8 \times 8$ and $4 \times 4$ Butler Matrices in 0.13- $\mu$ m CMOS | 47 |

|------------|---------------------------------------------------------------------|----|

|            | 4.1 Introduction                                                    | 47 |

|            | 4.2 8×8 Butler Matrix at 5–6 GHz                                    | 48 |

|            | 4.2.1 Design and Circuit Blocks                                     | 48 |

|            | 4.2.2 Measurements                                                  | 56 |

|            | 4.2.3 Extension to Full-Angle Scanning                              | 60 |

|            | 4.3 4×4 Butler Matrix at Ku-Band                                    | 60 |

|            | 4.3.1 Design                                                        | 60 |

|            | 4.3.2 Measurements                                                  | 64 |

|            | 4.4 Conclusion                                                      | 67 |

|            | 4.5 Acknowledgement                                                 | 70 |

| Chapter 5  | Conclusion                                                          | 71 |

| Appendix A | A Microwave-Based Gamma-Ray Detector                                | 74 |

|            | A.1 Introduction                                                    | 74 |

|            | A.2 Operation Principle                                             | 75 |

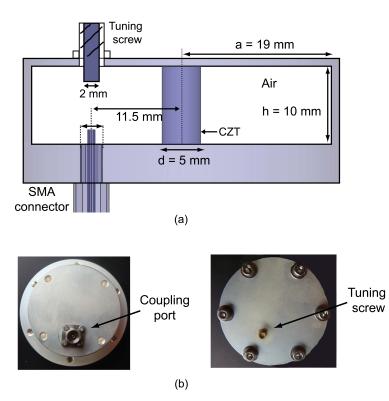

|            | A.3 Cylindrical Cavity Design                                       | 77 |

|            | A.4 Detector Design                                                 | 79 |

|            | A.5 Measurements                                                    | 81 |

|            | A.6 Cavity Designs for Improved Detection                           | 84 |

|            | A.7 Conclusion                                                      | 88 |

|            | A.8 Acknowledgement                                                 | 88 |

|            |                                                                     |    |

#### LIST OF FIGURES

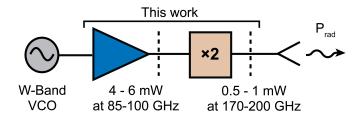

| Figure 2.1:  | Block diagram of W-to-G-band multiplier chain.                                                 | 4  |

|--------------|------------------------------------------------------------------------------------------------|----|

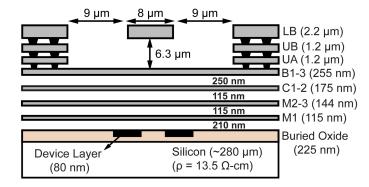

| Figure 2.2:  | 45-nm SOI CMOS process metal stack-up and 50 $\Omega$ T-line cross-section                     |    |

|              | (not to scale). All metal layers are copper except the aluminum top metal                      | 5  |

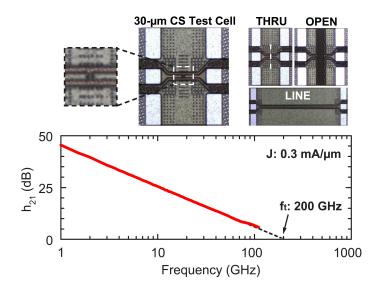

| Figure 2.3:  | Measured $f_t$ of a 30×1- $\mu m$ common-source transistor using a TRL calibration.            | 5  |

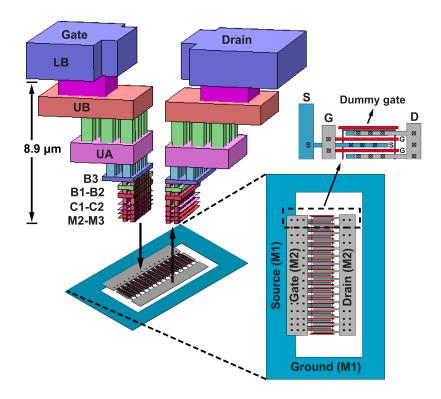

| Figure 2.4:  | Modeling of transition from top metal down to transistor level and simplified                  |    |

|              | layout of a $30 \times 1$ - $\mu$ m transistor.                                                | 7  |

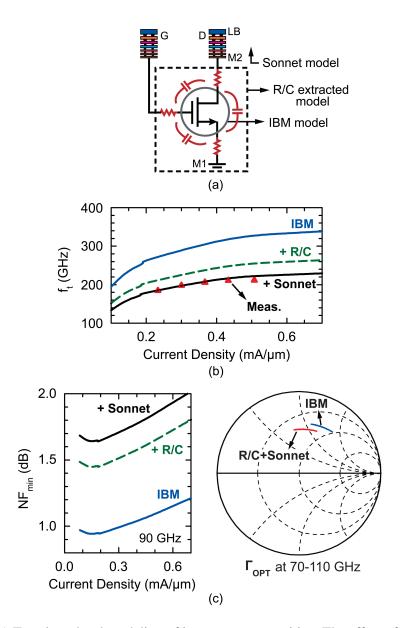

| Figure 2.5:  | (a) Transistor-level modeling of interconnect parasitics. The effect of para-                  |    |

|              | sitics (b) on $f_t$ and (c) on NF_{min} and $\Gamma_{\rm OPT}$ (30×1- $\mu m$ transistor used) | 8  |

| Figure 2.6:  | (a) Measured U, MAG, and MSG vs. frequency up to 110 GHz, and (b)                              |    |

|              | simulated and measured $f_{\max}$ vs. current density                                          | 10 |

| Figure 2.7:  | (a) The effect of parasitics on the MAG at 90 GHz, (b) measured MAG vs.                        |    |

|              | frequency for different current densities, and (c) measured MAG at 75 GHz.                     | 11 |

| Figure 2.8:  | The effect of different modeling scenarios on (a) $f_{\rm t},$ (b) $f_{\rm max},$ (c) MAG, and |    |

|              | (d) input impedance at 70-110 GHz                                                              | 12 |

| Figure 2.9:  | Schematic of the W-band amplifier.                                                             | 13 |

| Figure 2.10: | (a) Microphotograph of the W-band CMOS amplifier $(0.58 \times 0.55 \text{ mm}^2)$ and         |    |

|              | (b) measured S-parameters on three different samples (only $S_{21}$ is shown for               |    |

|              | the three samples).                                                                            | 15 |

| Figure 2.11: | Measured noise figure of the amplifier versus frequency and current density.                   | 16 |

| Figure 2.12: | Measured output power and PAE versus input power at 95 GHz                                     | 17 |

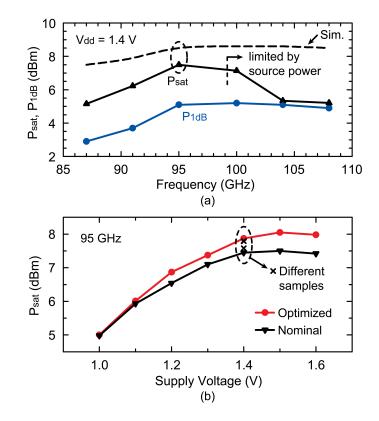

| Figure 2.13: | Measured (a) Psat and P1dB vs. frequency, (b) Psat vs. supply voltage                          | 17 |

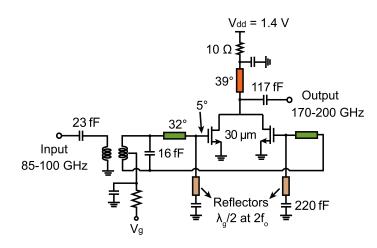

| Figure 2.14: | Schematic of the W-to-G-band balanced doubler.                                                 | 18 |

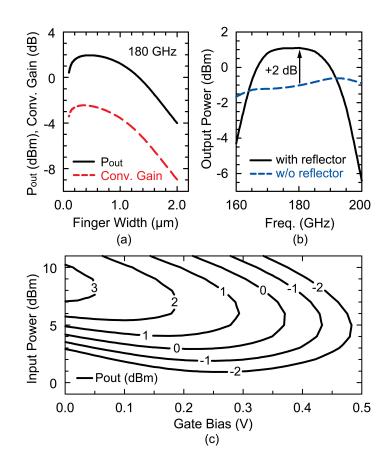

| Figure 2.15: | Simulations showing (a) output power and conversion gain of the doubler                        |    |

|              | vs. finger width (30- $\mu$ m wide transistors), (b) effect of reflector on the out-           |    |

|              | put power of the doubler, and (c) output power contours for different gate                     |    |

|              | bias voltages and input power levels.                                                          | 19 |

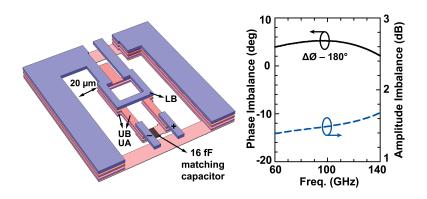

| Figure 2.16: | 3-D view of the doubler input balun and simulated phase/amplitude imbal-                       |    |

|              | ance between the differential ports                                                            | 19 |

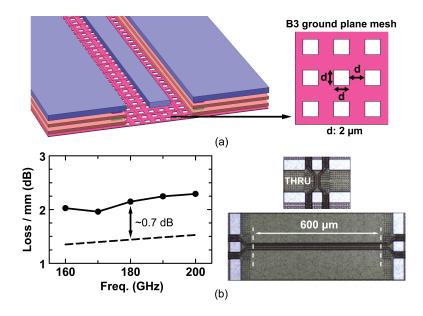

| Figure 2.17: | (a) CPW transmission line with ground plane meshing. (b) Measured (solid)                      |    |

|              | and simulated (dashed) line loss/mm for a 50 $\Omega$ T-line. A 600- $\mu$ m line and          |    |

|              | GSG thru pads are used for line loss measurements.                                             | 21 |

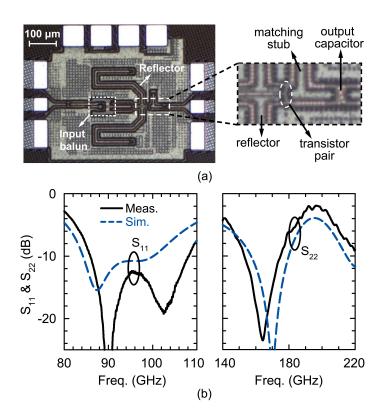

| Figure 2.18: | (a) Microphotograph of the doubler $(0.69 \times 0.49 \text{ mm}^2)$ and (b) measured S-       |    |

|              | parameters                                                                                     | 21 |

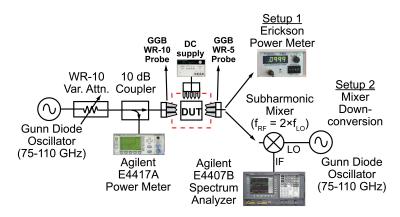

| Figure 2.19: | Measurement setup for doubler output power and gain characterization. An                       |    |

|              | all-waveguide setup is used for accurate power measurements                                    | 22 |

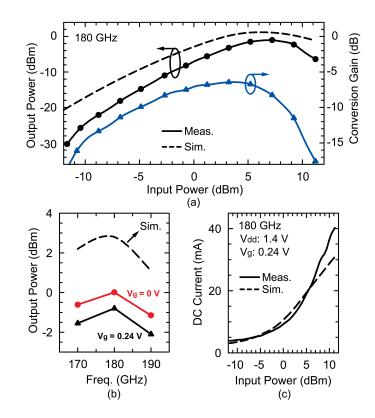

| Figure 2.20: | Measured (a) output power and gain of the doubler vs. input power at 180                       |    |

|              | GHz, (b) output power vs. frequency, and (c) DC current vs. input power                        | 22 |

| Figure 2.21: | Measured peak output power of the G-band doubler versus frequency for                          |    |

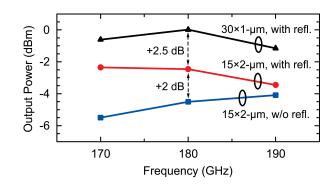

|              | different doubler designs.                                                                     | 23 |

| Figure 2.22: |                                                                                                |    |

|              | sured output return loss.                                                                      | 24 |

| Figure 2.23: | Down-converted 180 GHz signal at the output of the amplifier/doubler mea-                      |    |

|              | sured using a spectrum analyzer                                                                | 24 |

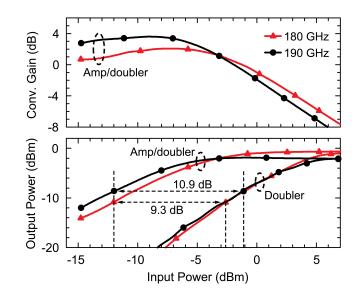

| Figure 2.24:                 | Measured conversion gain and output power of the amplifier/doubler at 180 and 190 GHz. Stand-alone doubler output power is also plotted for compar-<br>ison.                                 |

|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

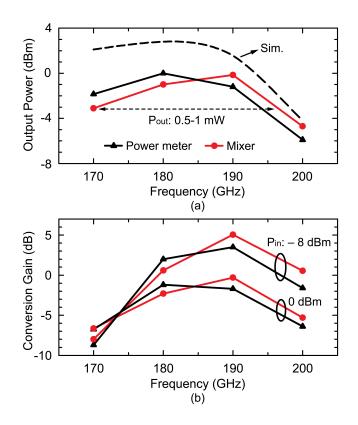

| Figure 2.25:                 | <ul><li>(a) Measured peak output power and (b) conversion gain of the amplifier/doubler versus frequency. Measurements done using a power meter and a mixer down-conversion setup.</li></ul> |

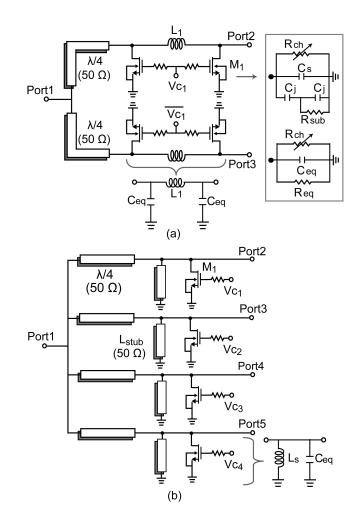

| Figure 3.1:                  | Schematic of series-shunt SP4T switch.                                                                                                                                                       |

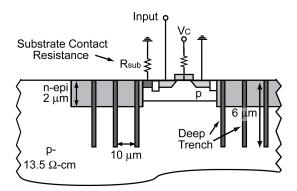

| Figure 3.2:                  | (a) Cross sectional view and (b) schematic of the SP4T switch using deep n-well nMOS transistors (only one branch is shown)                                                                  |

| Figure 3.3:                  | Simulated insertion loss and isolation of a series-shunt switch at 60 GHz versus the gate width.                                                                                             |

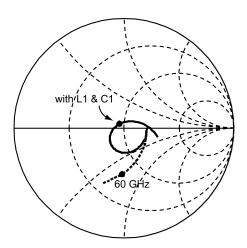

| Figure 3.4:                  | The input reflection coefficient at DC-80 GHz at the common node (dashed) and the input port (solid).                                                                                        |

| Figure 3.5:                  | Schematic of (a) SPDT and (b) SP4T switches.                                                                                                                                                 |

| Figure 3.6:                  | Cross sectional view of the shunt CMOS transistor with deep trenches, iso-<br>lation moat, and high $R_{SUB}$ contacts.                                                                      |

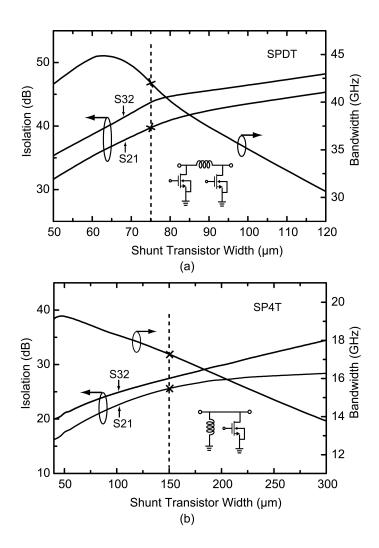

| Figure 3.7:                  | Simulated -10 dB return loss matching bandwidth, and isolation versus tran-<br>sistor width of (a) SPDT and (b) SP4T.                                                                        |

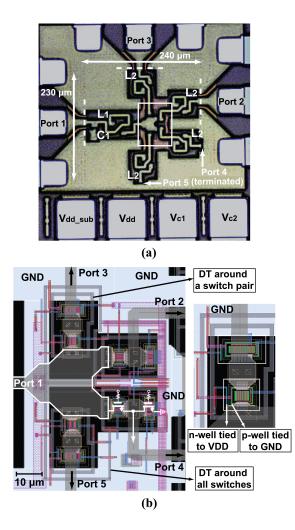

| Eigung 2.9.                  | Micro-photograph of the series-shunt SP4T switch.                                                                                                                                            |

| Figure 3.8:<br>Figure 3.9:   | Mero-photograph of the series-shuft SP41 switch                                                                                                                                              |

| U                            |                                                                                                                                                                                              |

| Figure 3.10:                 | Measured and simulated return loss of the series-shunt SP4T switch                                                                                                                           |

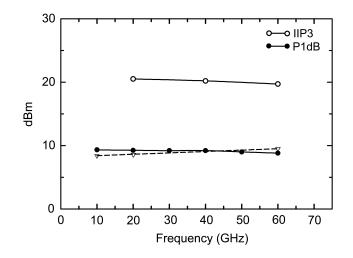

| Figure 3.11:<br>Figure 3.12: | Measured and simulated isolation of the series-shunt SP4T switch Measured (solid) and simulated (dashed) P1dB and IIP3 of the series-shunt SP4T switch                                       |

| Figure 3.13:                 | SP4T switch                                                                                                                                                                                  |

| Figure 3.14:                 | Micrograph of (a) SPDT and (b) SP4T switches (figures are not to the same                                                                                                                    |

| Figure 3.15:                 | scale)                                                                                                                                                                                       |

| <b>F</b> : 0.16              | SP4T switches.                                                                                                                                                                               |

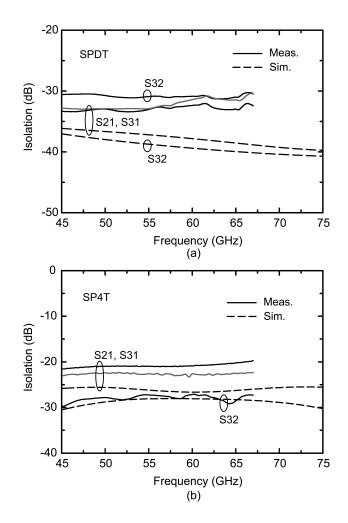

| Figure 3.16:                 | Measured and simulated isolation for (a) SPDT and (b) SP4T switches                                                                                                                          |

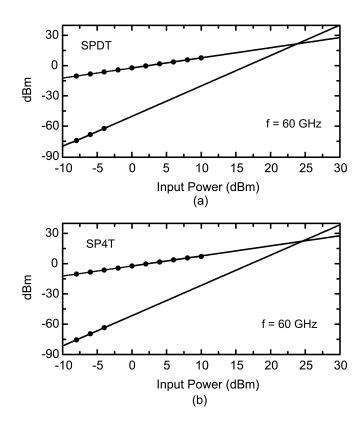

| Figure 3.17:                 | Measured IIP3 of (a) SPDT and (b) SP4T switches at 60 GHz                                                                                                                                    |

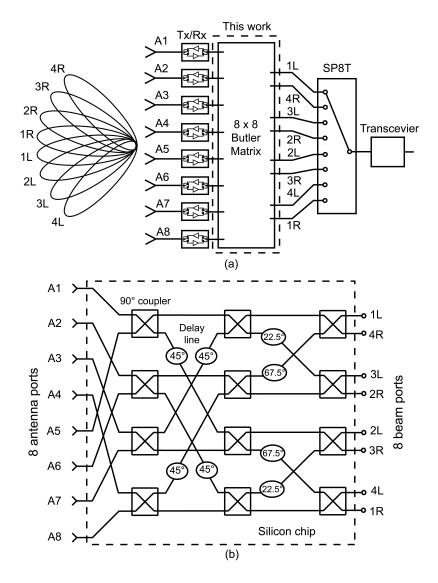

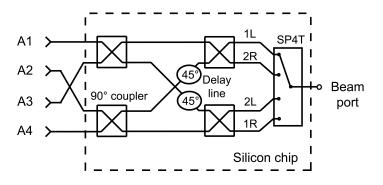

| Figure 4.1:                  | (a) Conceptual block diagram of Butler matrix used in a switched-beam system, and (b) circuit diagram of an $8 \times 8$ Butler matrix.                                                      |

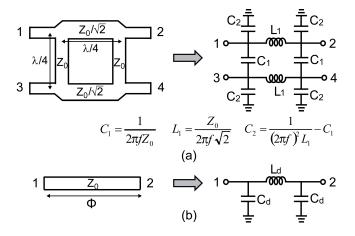

| Figure 4.2:                  | Transmission line and lumped element based (a) 90° coupler, and (b) phase delay cell.                                                                                                        |

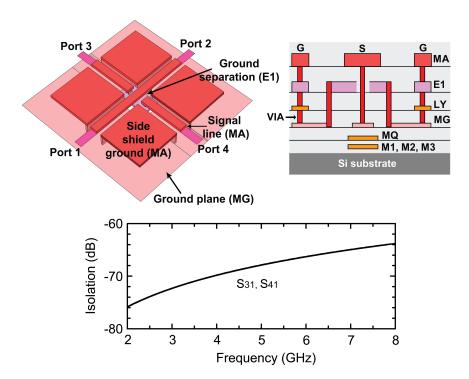

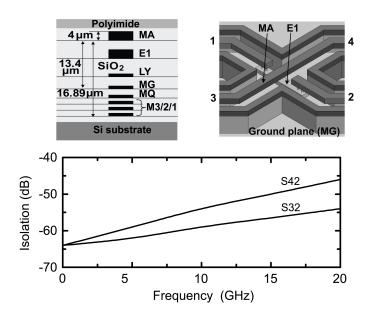

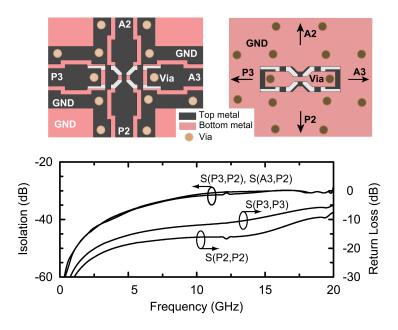

| Figure 4.3:                  | On-chip CPW crossover structure: top view, cross-sectional view, and simulated coupling between the ports.                                                                                   |

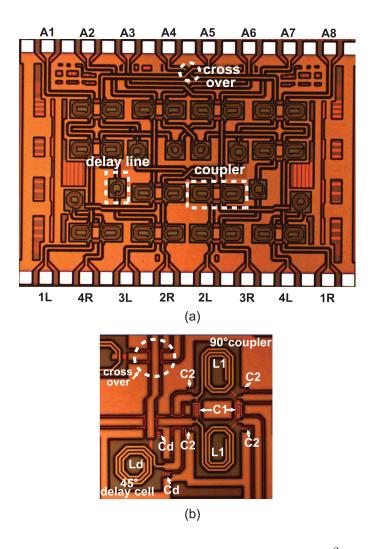

| Figure 4.4:                  | (a) Microphotograph of the $8 \times 8$ Butler matrix (2.5×1.9 mm <sup>2</sup> ), and (b) a $45^{\circ}$ phase delay cell with a 90° coupler.                                                |

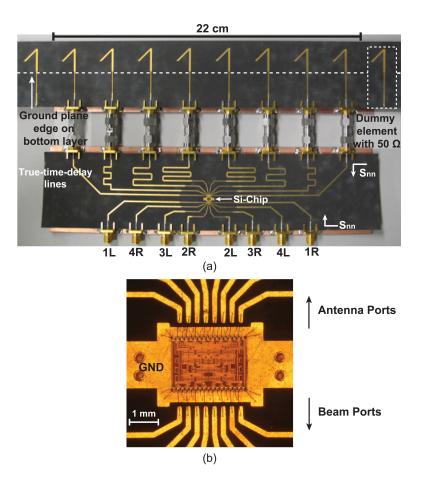

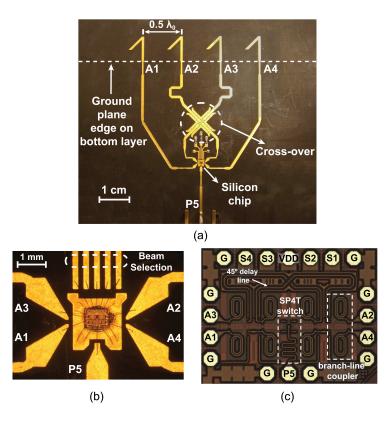

| Figure 4.5:                  | (a) Picture of the assembled $8 \times 8$ Butler matrix board, and (b) close-up view                                                                                                         |

| Eigene 4 C                   | of the silicon chip on a Teflon board.                                                                                                                                                       |

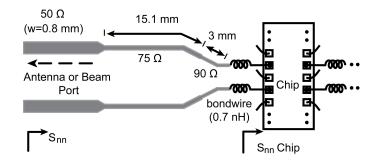

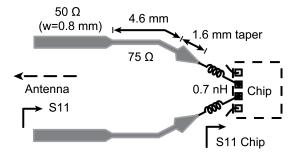

| Figure 4.6:                  | Matching network for the $8 \times 8$ Butler matrix chip. 8 of them are used on each side of the chip: antenna ports and beam ports.                                                         |

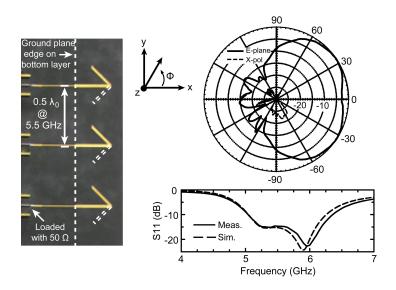

| Figure 4.7:   | 3-element layout of the angled-dipole antenna, the measured pattern at 5.5                                                                                     |    |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|               | GHz and return loss (center element shown).                                                                                                                    | 55 |

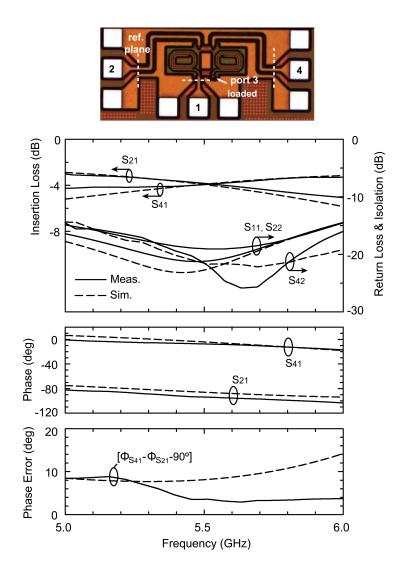

| Figure 4.8:   | Microphotograph and measured S-parameters of the quadrature coupler test                                                                                       |    |

|               | cell (Port 3 is loaded on-chip for measurement purposes)                                                                                                       | 57 |

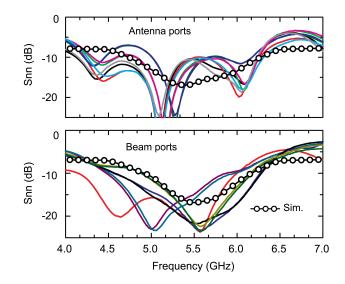

| Figure 4.9:   | Measured return loss: beam ports and antenna ports                                                                                                             | 58 |

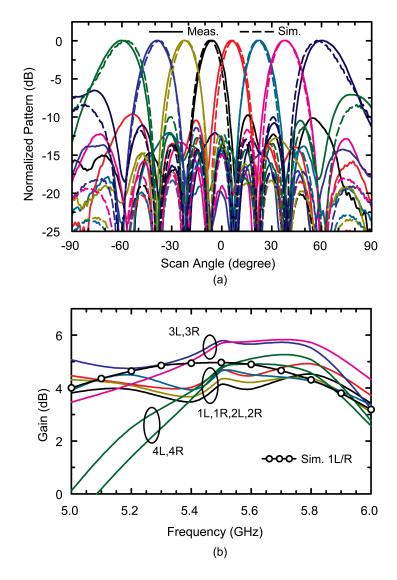

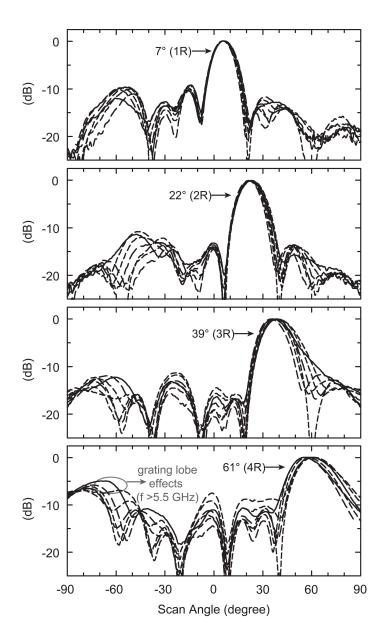

| Figure 4.10:  | (a) Measured normalized beam patterns at 5.5 GHz (4L-3L-2L-1L-1R-2R-                                                                                           |    |

|               | 3R-4R from left to right), and (b) measured gain vs. frequency                                                                                                 | 59 |

| Figure 4.11:  | · ·                                                                                                                                                            |    |

|               | Beams 1L-4L are symmetrical with beams 1R-4R and not shown                                                                                                     | 61 |

| Figure 4.12:  | Measured gain at $7^{\circ}$ (1R), $22^{\circ}$ (2R), $39^{\circ}$ (3R), and $61^{\circ}$ (4R) for different                                                   |    |

|               | beams resulting from the $8 \times 8$ Butler matrix                                                                                                            | 62 |

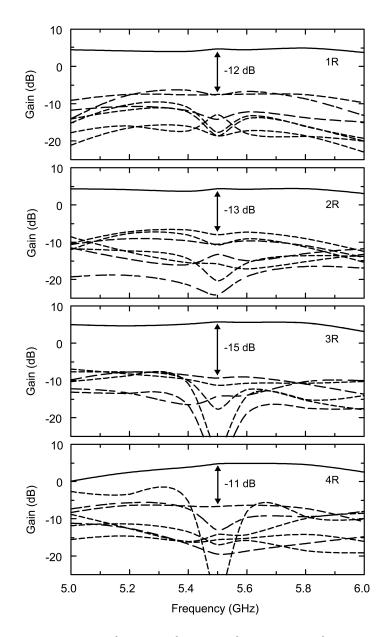

| Figure 4.13:  | (a) Modified Butler matrix block diagram for near continuous angular cov-                                                                                      |    |

|               | erage, and (b) simulated patterns with $0^{\circ}$ and $\Delta \Phi$ .                                                                                         | 63 |

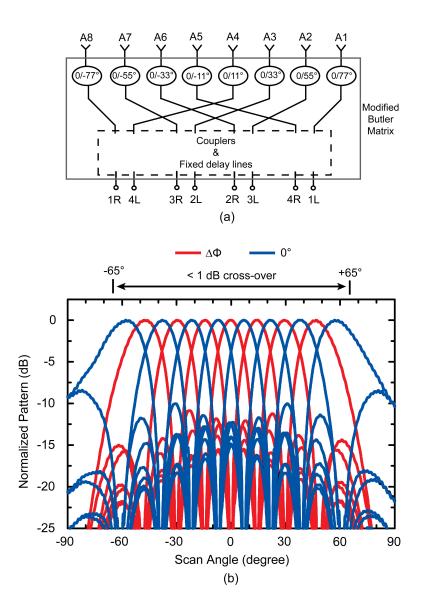

| -             | Block diagram of 4×4 Butler matrix.                                                                                                                            | 65 |

| Figure 4.15:  | IBM 8RF process stack-up, on-chip cross-over layout, and simulated isola-                                                                                      |    |

|               | tion between the different ports                                                                                                                               | 65 |

| Figure 4.16:  | (a) Picture of the assembled $4 \times 4$ Butler matrix board, (b) close-up view of                                                                            |    |

|               | the silicon chip on board, (c) microphotograph of the 12 GHz $4 \times 4$ Butler                                                                               |    |

|               | matrix chip (size: $0.85 \times 0.65 \text{ mm}^2$ )                                                                                                           | 66 |

| Figure 4.17:  | Layout and S-parameters of the cross-over on the Duroid board. Excellent                                                                                       |    |

|               | isolation is achieved using grounded CPW lines.                                                                                                                | 66 |

| Figure 4.18:  | Input matching network for the $4 \times 4$ Butler matrix. The output matching                                                                                 |    |

|               | network is similar and is not shown                                                                                                                            | 67 |

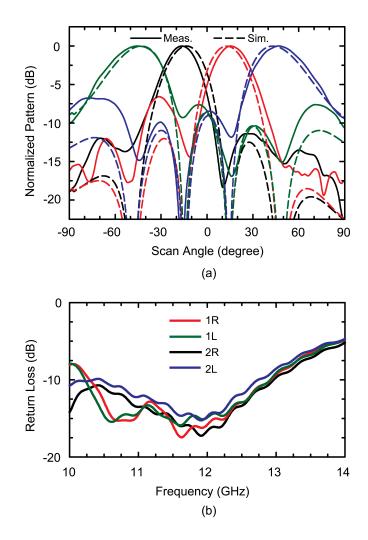

| Figure 4.19:  | (a) Measured beam patterns at 12 GHz, and (b) measured output return loss.                                                                                     | 68 |

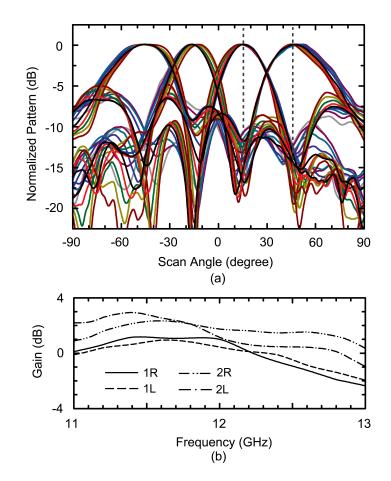

| Figure 4.20:  | (a) Measured patterns at 11-13 GHz and (b) measured gain                                                                                                       | 69 |

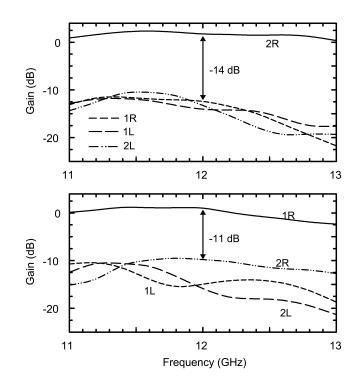

| Figure 4.21:  | Measured gain at (a) $49^{\circ}$ (2R), (b) $15^{\circ}$ (1R) for the different beams resulting                                                                |    |

|               | from the 4×4 Butler matrix.                                                                                                                                    | 70 |

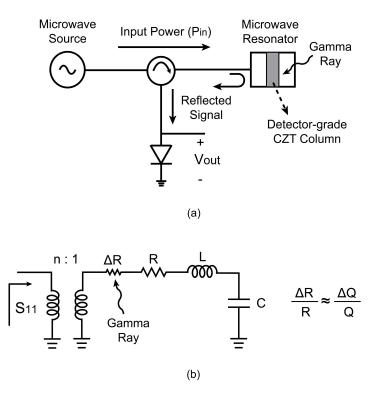

| Figure A.1:   | (a) Conceptual block diagram for a microwave-based $\gamma$ -ray detector, (b)                                                                                 |    |

|               | RLC circuit model                                                                                                                                              | 76 |

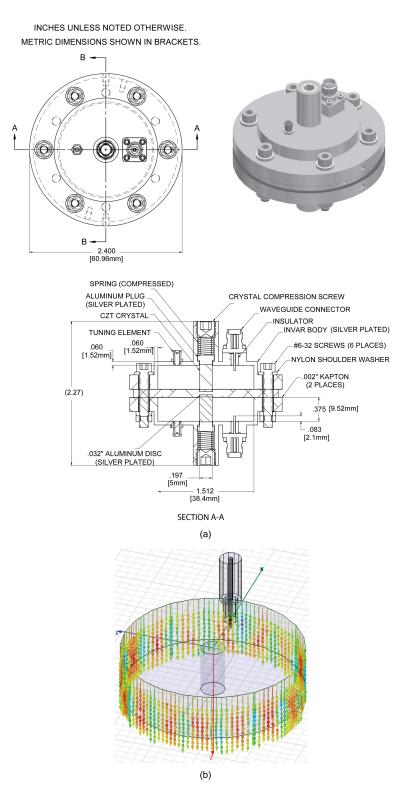

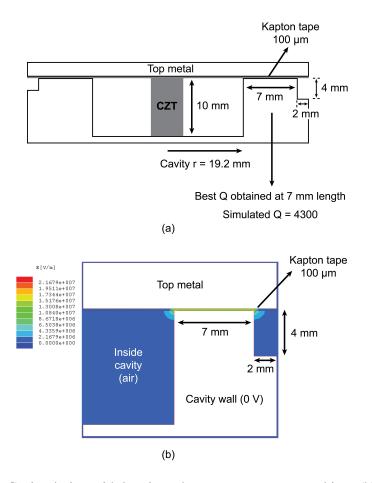

| Figure A.2:   | (a) Cross-sectional diagram and (b) top/bottom view of the fabricated 4.5                                                                                      |    |

|               | GHz cavity.                                                                                                                                                    | 78 |

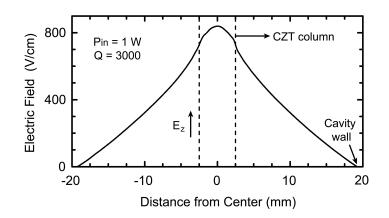

| Figure A.3:   | Simulated E-field inside the cavity for $TM_{010}$ mode. Note the discontinuity                                                                                |    |

|               | in the E-field slope at the air-CZT interface                                                                                                                  | 80 |

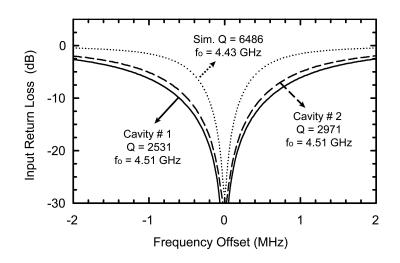

| Figure A.4:   | Measured resonance frequency $(f_0)$ and Q for two different cavities after manual tuning.                                                                     | 80 |

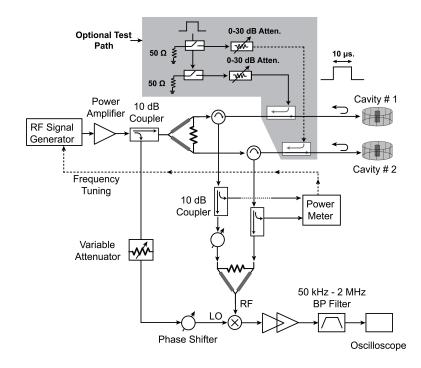

| Figure A.5:   | Block diagram of the differential gamma-ray detector with optional test path.                                                                                  | 82 |

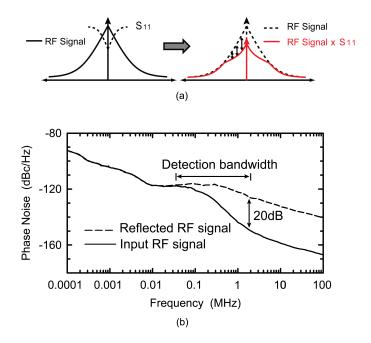

| Figure A.6:   | (a) Conceptual diagram of the close-in phase noise degradation due to cavity                                                                                   | 02 |

| 1 iguie 71.0. | (a) Conceptual diagram of the close in phase noise degradation due to early $S_{11}$ . (b) Measured RF signal phase noise before and after reflection from the |    |

|               | high-Q cavity.                                                                                                                                                 | 82 |

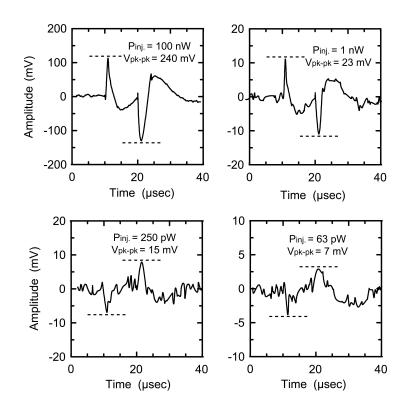

| Figure A.7:   | Injected power (10 $\mu$ s pulse) using matched switches and corresponding                                                                                     | 52 |

| - 19010 11.1. | measured signal at the scope.                                                                                                                                  | 83 |

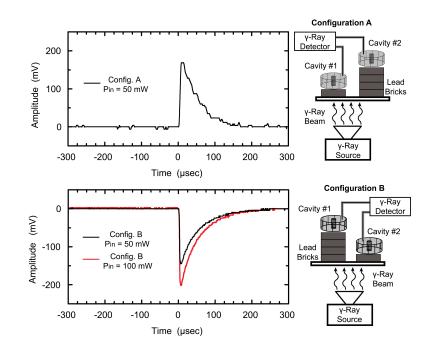

| Figure A.8:   | Test setup and measured response for the $\gamma$ -ray detector.                                                                                               | 84 |

| Figure A.9:   | (a) Initial dual-cavity design, (b) current distribution on the cavity walls.                                                                                  | 85 |

|               | (a) minute astar currey acording (c) content aroundation on the currey wants.                                                                                  | 55 |

| a) Cavity design with low-impedance quarter-wave matching. (b) Simula-        |               |

|-------------------------------------------------------------------------------|---------------|

| tion of the electric field distribution between the top and the bottom metals |               |

| of the cavity.                                                                | 87            |

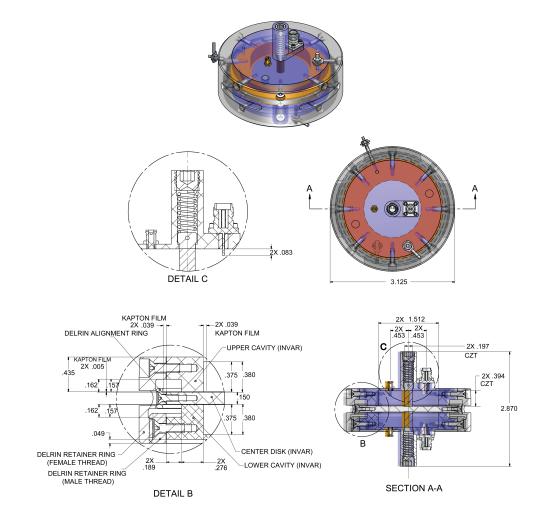

| Proposed dual-cavity resonator prototype for high Q and high voltage          | 89            |

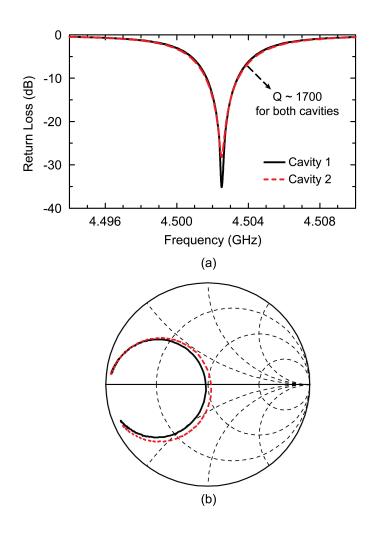

| Measured return loss of both cavity resonators (a) on dB scale and (b) on     |               |

| the Smith chart                                                               | 90            |

|                                                                               | of the cavity |

#### LIST OF TABLES

| Table 2.1:    | Performance Summary of W-Band CMOS Amplifiers                                           | 28 |

|---------------|-----------------------------------------------------------------------------------------|----|

| Table 2.2:    | Performance Summary of Doublers $> 130 \text{ GHz} \dots \dots \dots \dots \dots \dots$ | 28 |

| <b>TIL 21</b> |                                                                                         | 10 |

| Table 3.1:    | Comparison of Wideband Mm-Wave Switches.                                                | 46 |

| Table 4.1:    | Phase Distribution of an $8 \times 8$ Butler Matrix                                     | 50 |

|               |                                                                                         |    |

| Table 4.2:    | Gain of 8×8 Butler Matrix with Dipole Array at 5.5 GHz                                  | 58 |

#### ACKNOWLEDGEMENTS

I still remember the days that lead to my Ph.D. journey at UCSD. During my last year in college in Turkey, I was applying to multiple universities in the United States for admission to a graduate program in electrical engineering and sending e-mails to the professors in my area asking for funding. Only one of them answered my e-mail and that was Prof. Gabriel Rebeiz. By a great chance, he was coming to Istanbul to attend a MEMS conference and was willing to talk to me. We met at the lobby of the Marmara Hotel in Taksim Square on a snowy day and I told him about what I did as an undergraduate student. He seemed to be impressed by the work I did, especially my internship project about a power amplifier design that was done with Yusuf Atesal. This lead to our admission to UCSD and my journey has started.

During the first days, Yusuf and I were sitting at the far end of the meeting table in our  $6^{th}$  floor office, trying to understand what the people were talking about. At that time we did not know what we will be working on, so we were attending every RFIC, MEMS and antenna group meetings, going on for hours. Then, in about a year, the discussions started to make more sense as we took classes and learned more about our field. After working on many interesting yet challenging projects, we finally made our way to graduation from UCSD with a Ph.D. degree.

I would first like to thank my advisor Prof. Gabriel M. Rebeiz since he was the one who made this journey possible by accepting me to his research group at UCSD. He is a great advisor in many ways and I learned a lot from his experience. He trains his students not only in their technical field, but also in other aspects such as how to give a good presentation, and even how to talk and behave in professional environments. I truly understood the quality of my education when I was an intern at Qualcomm. Everything that he tries to teach is actually all you need to be successful in a company or in academia. His research lab is always made up of top quality state-of-the-art equipments that enable cutting-edge research. His broad technical insight, passion and enthusiasm in research lead to new ideas that result in major breakthroughs. I especially find two of his phrases very inspirational: "I want you to build the impossible!" and "Never give up!". All of these have been a great motivation for me to complete my degree without giving up and encourage me to undertake bigger challenges in my future career.

Next, I would like to thank my dissertation committee members, Prof. Larry Larson, Prof. James F. Buckwalter, Prof. Gert Cauwenberghs and Prof. William Hodgkiss for their time, interest, and valuable comments about my research. UCSD is a great school to get a Ph.D. in electrical engineering and the courses that are offered are very valuable. The multidisciplinary aspect of the distinguished faculty makes the learning experience much more enriching. I would also like to thank Prof. Yasar Gurbuz at Sabanci University, Istanbul, Turkey, who supported and encouraged both me and Yusuf to do a Ph.D. in the U.S.

As I mentioned at the beginning, I came to UCSD with Yusuf Atesal and we worked together in every project almost till the end. His technical knowledge and brightness made a great contribution to all of our projects, and his friendship made it possible to survive the sleepless and stressful tape-out periods. For this reason, I want to thank him first for being such a good companion in this long journey. I am sure that we will be working together again in the future.

Special thanks go to my closest friends Mehmet Uzunkol and Ozgur Inac, with whom I shared the same house for more than two years. We were "The Sabanci Mafia" in the group. I would also like to thank Mehmet Parlak for his friendship and support, and for inviting us to many of his fun events.

I would like to thank Yusuf Atesal, Jeong-Geun Kim, and Andy Fung for their contribution to the work in this thesis. I would also like to thank the team from U.S. Navy SPAWAR SSC Pacific in San Diego, namely, Dr. Richard A. Kroeger, Dr. Jon Losee, Dr. Charles Hicks, and Mr. Marc Rasmussen, for their contributions to the gamma-ray detector project in this thesis. Regarding the same project, my thanks also extend to Dr. Gary Tepper from Virginia Commonwealth University for his valuable comments and inputs.

There are many people in the TICS group that I would like to acknowledge here for their support and friendship: Michael Chang, Chris Galbraith, Carson White, Byung-Wook Min, Sang-June Park, Jeong-Geun Kim, Balaji Lakshminarayana, Kwang-Jin Koh, Mohammed El-Tanani, Tiku Yu, Jason May, Isak Reines, Alex Grichener, Dong-Woo Kang, Sang-Young Kim, Ramadan Alhalabi, Chirag Patel, Jen Edwards, Kevin Ho, Yusuf Atesal, Mehmet Uzunkol, Ozgur Inac, Fatih Golcuk, Ozan Dogan Gurbuz, Seyhmus Cacina, Tumay Kanar, Woorim Shin, Donghyup Shin, Yu-Chin Ou, Choul-Young Kim, Yi-Chyun Chiou, Chih-Chieh Cheng, Rashed Mahameed, Hojr Sedaghat Pisheh, Hosein Zareie and Chenhui Niu. I would also like to thank Romain Stefanini for making life enjoyable when he was with us in San Diego.

The support and encouragement of my parents, Ferdi and Sabahat Cetinoneri, was a great contributor in completing my Ph.D. degree. They have done everything to make sure that I get the best education since when I was a child and I always feel their good wishes and prayers for me when the times are tough. I can never forget their support, dedication and unending love throughout my life. They are a true blessing for me. I also thank to my close relatives for their great support and good wishes. I always see their excitement, warmth and love in their eyes

when I go back to Istanbul.

I would also like to thank George and Carol Hahn, who kindly hosted me and Yusuf by opening their home to us when we first arrived to San Diego, which started our friendship. They accepted both Yusuf and me as a part of their family, and I will always remember the great meals shared and times spent together. I am so happy that I got to know them. They became a part of my family.

The material in this dissertation is based on the following papers which are either published, or has been submitted for publication.

Chapter 2 is based on and mostly a reprint of the following paper:

- B. Cetinoneri, Y. A. Atesal, A. Fung, and G. M. Rebeiz, "W-band amplifiers with 6 dB noise figure and mW-Level 170-200 GHz doublers in 45-nm CMOS," submitted for publication in IEEE Trans. Microwave Theory and Tech., May 2011.

Chapter 3 is based on and mostly a reprint of the following papers:

- B. Cetinoneri, Y. A. Atesal, and G. M. Rebeiz, "A miniature DC-70 GHz SP4T switch in 0.13-μm CMOS," IEEE MTT-S Int. Microwave Symp. Dig., pp. 1093-1096, Jun. 2009,

- Y. A. Atesal, B. Cetinoneri, and G. M. Rebeiz, "Low-loss 0.13-μm CMOS 50-70 GHz SPDT and SP4T switches," IEEE Radio Frequency Integrated Circuits Symp., Jun. 2009, pp. 127-130.

Chapter 4 is based on and mostly a reprint of the following papers:

- B. Cetinoneri, Y. A. Atesal, and G. M. Rebeiz, "An  $8 \times 8$  Butler matrix in 0.13-  $\mu$ m CMOS for 5-6 GHz multibeam applications," IEEE Trans. Microwave Theory and Tech., vol. 59, no. 2, pp. 295-301, Feb. 2011.

- B. Cetinoneri, Y. A. Atesal, J.-G. Kim, and G. M. Rebeiz, "CMOS 4×4 and 8×8 Butler matrices," IEEE MTT-S Int. Microwave Symp. Dig., pp. 69-72, May 2010.

Appendix A is based on and mostly a reprint of the following paper:

B. Cetinoneri, Y. A. Atesal, R. A. Kroeger, G. Tepper, J. Losee, C. Hicks, M. Rasmussen, and G. M. Rebeiz, "A microwave-based gamma-ray detector," IEEE MTT-S Int. Microwave Symp. Dig., pp. 469-472, May 2010.

The dissertation author was the primary author of the work in these chapters, and coauthors (Prof. Gabriel M. Rebeiz, Dr. Yusuf A. Atesal, Dr. Jeong-Geun Kim, Dr. Andy Fung, Dr. Richard A. Kroeger, Dr. Gary Tepper, Dr. Jon Losee, Dr. Charles Hicks, and Mr. Marc Rasmussen) have approved the use of the material for this dissertation.

Berke Cetinoneri La Jolla, California May, 2011.

#### VITA AND PUBLICATIONS

| 2002 - 2006 | B. S. in Microelectronics Engineering, Sabanci University, Istanbul, Turkey                 |

|-------------|---------------------------------------------------------------------------------------------|

| 2006 - 2008 | M. S. in Electrical Engineering, University of California, San Diego, La Jolla, California  |

| 2008 - 2011 | Ph. D. in Electrical Engineering, University of California, San Diego, La Jolla, California |

B. Cetinoneri, Y. A. Atesal, A. Fung, and G. M. Rebeiz, "W-band amplifiers with 6 dB noise figure and mW-Level 170-200 GHz doublers in 45-nm CMOS," *IEEE Trans. Microwave Theory and Tech.*, submitted for publication, May 2011.

B. Cetinoneri, Y. A. Atesal, and G. M. Rebeiz, "An  $8 \times 8$  Butler matrix in 0.13- $\mu$ m CMOS for 5-6 GHz multibeam applications," *IEEE Trans. Microwave Theory and Tech.*, vol. 59, no. 2, pp. 295-301, Feb. 2011.

Y. A. Atesal, B. Cetinoneri, M. Chang, R. A. Alhalabi, and G. M. Rebeiz, "Millimeter-wave wafer-scale silicon BiCMOS power amplifiers using free-space power combining," *IEEE Trans. Microwave Theory and Tech.*, vol. 59, no. 4, pp. 954-965, Apr. 2011.

Y. A. Atesal, B. Cetinoneri, K. Ho, and G. M. Rebeiz, "A two-channel 8-20-GHz SiGe BiCMOS receiver with selectable IFs for multibeam phased-array digital beamforming applications," *IEEE Trans. Microwave Theory and Tech.*, vol. 59, no. 3, pp. 716-726, Mar. 2011.

B. Cetinoneri, Y. A. Atesal, J.-G. Kim, and G. M. Rebeiz, "CMOS 4×4 and 8×8 Butler matrices," *IEEE MTT-S Int. Microwave Symp. Dig.*, pp. 69-72, May 2010.

B. Cetinoneri, Y. A. Atesal, R. A. Kroeger, G. Tepper, J. Losee, C. Hicks, M. Rasmussen, and G. M. Rebeiz, "A microwave-based gamma-ray detector," *IEEE MTT-S Int. Microwave Symp. Dig.*, pp. 469-472, May 2010.

Y. A. Atesal, B. Cetinoneri, R. A. Alhalabi, and G. M. Rebeiz, "Wafer-scale W-band power amplifiers using on-chip antennas," *IEEE Radio Frequency Integrated Circuits Symp. Dig.*, pp. 469-472, May 2010.

Y. A. Atesal, B. Cetinoneri, K.-J. Koh and G. M. Rebeiz, "X/Ku-band 8-element phased arrays based on single silicon chips," *IEEE Int. Microwave Symp. Dig.*, pp. 1258-1261, May 2010.

B. Cetinoneri, Y. A. Atesal, and G. M. Rebeiz, "A two-channel Ku-band BiCMOS digital beamforming receiver for polarization-agile phased-array applications," *IEEE Radio Frequency Integrated Circuits Symp. Dig.*, pp. 127-130, Jun. 2009.

B. Cetinoneri, Y. A. Atesal, and G. M. Rebeiz, "A miniature DC-70 GHz SP4T switch in 0.13μm CMOS," *IEEE Int. Microwave Symp. Dig.*, pp. 1093-1096, Jun. 2009. Y. A. Atesal, B. Cetinoneri, and G. M. Rebeiz, "Low-loss 0.13-µm CMOS 50-70 GHz SPDT and SP4T switches," *IEEE Radio Frequency Integrated Circuits Symp. Dig.*, pp. 43-46, Jun. 2009.

G. M. Rebeiz, K. J. Koh, T. Yu, D. Kang, C. Y. Kim, Y. Atesal, B. Cetinoneri, S. Y. Kim, and D. Shin, "Highly dense microwave and millimeter-wave phased array T/R modules and Butler matrices using CMOS and SiGe RFICs," *IEEE Int. Symp. Phased Array Sys. and Tech.*, pp. 245-249, Oct. 2010.

W. Elsallal, D. Jensen, R. Palandech, J. Timmerman, J. West, Y. A. Atesal, B. Cetinoneri, and G. M. Rebeiz, "A SiGe-based Ku-band digital beamforming array for high speed on-the-move comm/radar system," *IEEE Int. Symp. Phased Array Sys. and Tech.*, pp. 868-875, Oct. 2010.

#### ABSTRACT OF THE DISSERTATION

#### Advanced CMOS Circuits for Microwave and Millimeter-Wave Communications

by

Berke Cetinoneri

#### Doctor of Philosophy in Electrical Engineering (Electronic Circuits and Systems)

University of California, San Diego, 2011

Professor Gabriel M. Rebeiz, Chair

The thesis presents advanced circuits in CMOS for microwave and millimeter-wave communications. First, low-noise W-band amplifiers and mW-level 170–200 GHz output doublers in 45-nm Semiconductor-On-Insulator (SOI) CMOS technology are presented. The transistors are modeled using R/C extraction and full electromagnetic modeling. The measured  $f_t$  of a  $30 \times 1$ - $\mu$ m transistor is 200–210 GHz at a bias current of 0.3–0.5 mA/ $\mu$ m. A 3-stage W-band amplifier shows a record noise figure of 6.0 dB and a saturated output power of 7.5–8.0 dBm with a power added efficiency of 9%, all at 95 GHz. The G-band balanced doubler results in an output power of 1 mW at 180 GHz. A W-band amplifier/G-band doubler chip is also demonstrated, with a peak output power of 0.5–1 mW at 170–195 GHz and a conversion gain of -2 – -1 dB. This work shows that 45-nm SOI CMOS, built for digital and mixed-signal applications, results in state-of-the-art performance at W-band and G-band.

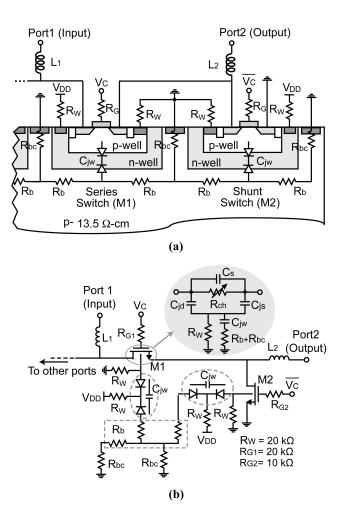

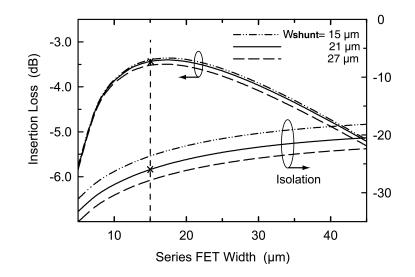

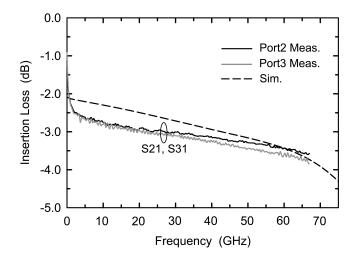

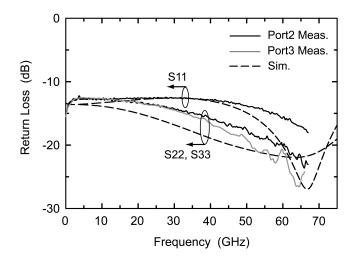

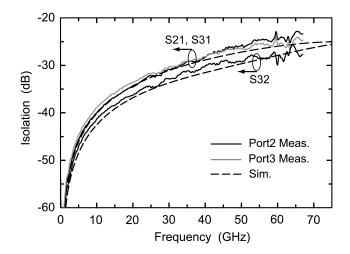

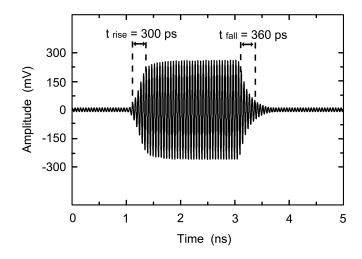

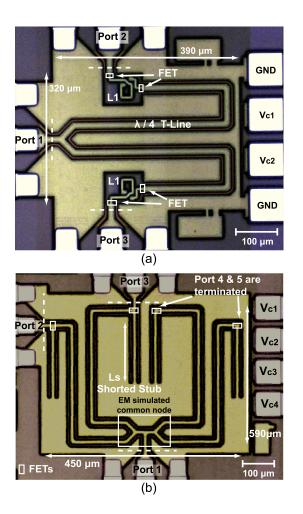

Next, a miniature DC-70 GHz single-pole four-throw (SP4T), 50-70 GHz single-pole double-throw (SPDT), and single-pole four-throw (SP4T) switches built in a low-cost 0.13- $\mu$ m CMOS process are presented. The DC-70 GHz SP4T switch is based on a series-shunt design with input and output matching circuits. Deep n-well (also called triple-well) CMOS transistors are used to minimize the substrate coupling. Also, deep trench isolation is used between the different ports to minimize the port-to-port coupling. The SP4T results in a measured insertion loss of less than 3.5 dB up to 67 GHz with an isolation of greater than 25 dB. The measured port-to-port coupling is less than 28 dB up to 67 GHz. The measured P1dB and IIP3 are independent of frequency and are 9-10 dBm and 20-21 dBm, respectively. The active chip area is  $0.24 \times 0.23$  mm<sup>2</sup>. When this work was published, it represented the widest bandwidth SP4T switch in any CMOS technology to-date.

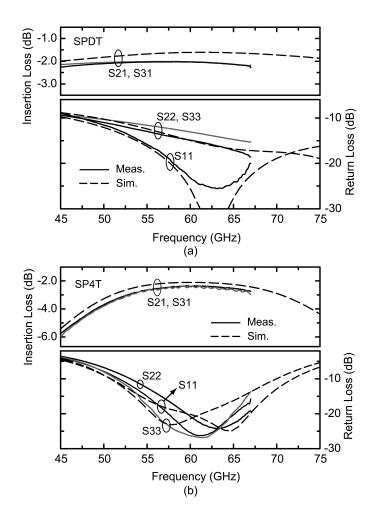

The 50-70 GHz single-pole double-throw (SPDT) and single-pole four-throw (SP4T) switches are based on tuned  $\lambda/4$  designs with output matching networks. High substrate resistance together with deep trenches and isolation moats are used for low insertion loss. The SPDT and SP4T switches result in a measured insertion loss of 2.0 and 2.3 dB at 60 GHz, with an isolation of > 32 dB and > 22 dB, respectively. The measured output port-to-port isolation is > 27 dB for both designs. The P1dB is 13-14 dBm with a measured IIP3 of > 23 dBm for both switches. Both designs have a return loss better than -10 dB at all ports from 50 to 70 GHz. The active chip area is  $0.39 \times 0.32$  mm<sup>2</sup> (SPDT) and  $0.59 \times 0.45$  mm<sup>2</sup> (SP4T). When this work was published, it presented the lowest loss 60 GHz SPDT and SP4T switches and also the highest isolation SPDT switch in any CMOS technology to-date.

In another project, 5–6 GHz 8×8 and Ku-band 4×4 Butler matrices are presented in a 0.13- $\mu$ m CMOS implementation. The 8×8 design results in an insertion loss of 3.5 dB at 5.5 GHz, with a bandwidth of 5-6 GHz and no power consumption. The chip area is 2.5×1.9 mm<sup>2</sup> including all pads. The 8×8 matrix is mounted on a Teflon board with 8-antennas, and the measured patterns agree well with theory and show an isolation of > 12 dB at 5–6 GHz. The 4×4 design results in an insertion loss of 2.4 dB at 12 GHz with a bandwidth of 11–13 GHz. The chip area is only 0.85×0.65 mm<sup>2</sup> including all pads, and the power consumption is ~0 mA from a 1.5 V power supply. The 4×4 matrix is mounted on a Teflon board with 4antennas, and the measured patterns agree well with theory and show an isolation of > 11 dB at 11–13 GHz. CMOS Butler matrices are an excellent candidate for MIMO systems, and can also replace small-element phased-array systems for high-gain transceivers. The applications areas are in high data-rate communications. Finally, a contactless, microwave-based gamma ray detector for detecting low-energy gamma ray photons is presented as an appendix. The detection is based on a microwave cavity perturbation method, and uses a reflection-type cavity resonator with a detector-grade CZT crystal. The reflected power from the cavity is measured and this monitors the changes in the photoconductivity of the CZT crystal in the presence of a gamma-ray. A gamma ray detection sensitivity of < 100 keV is achieved at room temperature. The proposed system can be used in homeland security or radioactive material characterization applications.

# **Chapter 1**

## Introduction

#### **1.1 Thesis Overview**

This thesis presents advanced circuits for microwave and millimeter-wave communications using CMOS technology. Millimeter-wave CMOS circuits are an active research topic in the past few years with a broad range of applications. Some essential components are the low-noise amplifier for receive applications, and a transmitter source which is capable of generating greater than 1 mW of power above 100 GHz. Hence, the second chapter is based on the demonstration of a low-noise W-band amplifier and mW-level 170–200 GHz output doublers. For a multi-band millimeter-wave transceiver system, high performance single-pole multiplethrow switches are required and various CMOS switches are presented which show a measured state-of-the-art insertion loss and isolation up to 67 GHz. The multi-band operation can be combined with multiple simultaneous beams, which is made possible by the use of Butler matrices, and  $8 \times 8$  and  $4 \times 4$  Butler matrices are presented at 5–6 GHz and at 12 GHz, respectively. As an appendix, an interesting project for detecting gamma-rays using microwave radiation is presented.

Chapter 2 presents a W-band low-noise amplifier with a record noise figure and balanced frequency doublers capable of high output power at 170–200 GHz range. These circuits are fabricated using IBM's 45-nm Semiconductor-On-Insulator (SOI) CMOS technology, which was developed for digital and mixed-signal circuits with an  $f_t$  of 485 GHz referenced to the transistor and therefore offers a lot of potential for 90–200 GHz applications. The chapter starts with an analysis of the SOI CMOS technology in detail and presents the measured and simulated transistor-level results. Then, the W-band low-noise amplifier design is discussed and the measured results are presented. Next, a balanced doubler design is demonstrated with simulations showing the doubler optimization and the measured results are discussed in detail. The amplifier and the doubler designs are eventually cascaded and the measured results show a peak output power of 0.5-1 mW at 170–195 GHz and a conversion gain of -2 - 1 dB. The chapter concludes with performance summary and comparison tables, which indicate that the circuits built using 45-nm SOI CMOS technology result in state-of-the-art performance at W-band and G-band.

Chapter 3 demonstrates millimeter-wave single-pole multiple-throw CMOS switches, which are becoming increasingly important for multi-band systems such as automotive radars, narrowband ISM and Giga-bit-per-second (Gbps) communication systems at 24 and 60 GHz. A miniature DC–70 GHz single-pole four-throw (SP4T), 50–70 GHz single-pole double-throw (SPDT), and single-pole four-throw (SP4T) switches are built using 0.13- $\mu$ m CMOS process. Several key transistor and CMOS technology features such as deep n-well transistors, high substrate contact resistance, and deep trench isolation are discussed. The DC-70 GHz SP4T switch is based on a series-shunt design with deep n-well CMOS transistors to improve the performance and occupies an active chip area of  $0.24 \times 0.23$  mm<sup>2</sup>. Next, 50–70 GHz single-pole double-throw (SPDT) and single-pole four-throw (SP4T) switches, which are based on tuned  $\lambda/4$  designs with output matching networks, are presented.

Chapter 4 presents 5–6 GHz 8×8 and Ku-band 4×4 Butler matrices in 0.13- $\mu$ m CMOS technology. The lumped-element design is discussed in detail with an emphasis on how the onchip cross-overs are realized with good isolation. The fabricated Butler matrix chips are mounted on a Teflon board with 8 or 4 antennas, and the input/output matching networks are designed by considering the bondwire transitions from the chip to the board. Complete pattern and gain measurements versus frequency are presented and the measured patterns agree very well with simulations. A modified 8×8 matrix is also shown, where the angular coverage can be improved by introducing phased delay before the antennas using switched CMOS L-C networks.

Appendix A demonstrates a microwave-based gamma-ray detector. The system is developed mainly for homeland security applications in order to detect low-energy gamma-ray photons at room temperature with high energy resolution and good efficiency. The operation principle and the system-level design is discussed in detail, and the measurement results are presented. Next, new cavity designs, which can achieve higher electric field by applying a high DC voltage, are presented with initial simulation results for low-energy single photon detection. The proposed microwave-based detection principle may result in an improved performance.

## Chapter 2

# W-Band Amplifiers with 6 dB Noise Figure and mW-Level 170-200 GHz Doublers in 45-nm CMOS

#### 2.1 Introduction

Millimeter-wave and Terahertz applications of SiGe and CMOS circuits are an active research topic in the past few years with applications in passive and active imaging systems [1–3], short-distance high-data rate communications [4], and sensing. Also, it is possible to integrate an efficient antenna in the SiGe and CMOS backend above 100 GHz, thereby removing the need for transitions in and out of the wafer, which are very lossy. SiGe has lead the way in this area due to the high  $f_t$  and more mature millimeter-wave back-end [5–7], and CMOS circuits are currently being demonstrated at 100–200 GHz [8]. Some essential components are the lownoise amplifier for receive applications, and a medium power amplifier or a source which is capable of generating mW level power in the 200 GHz range.

CMOS amplifiers at 90–150 GHz have been demonstrated using 90-nm and 65-nm technologies [9–11]. Also, CMOS oscillators were demonstrated at 200–600 GHz, but with very low power and poor phase noise [12, 13]. In fact, the phase noise of fundamental and harmonic CMOS oscillators is not quoted in all published papers. We believe that a better way to obtain RF power at 200–400 GHz is to use a low phase-noise mm-wave oscillator with a high performance PLL and an amplifier/multiplier chain (Fig. 2.1). The final phase noise increases by  $n^2$ , but is still much lower than oscillators which are operating close to  $f_{max}$ . Recently, 45-nm SOI CMOS,

Figure 2.1: Block diagram of W-to-G-band multiplier chain.

which was developed for digital and mixed-signal circuits with an  $f_t$  of 485 GHz referenced to the transistor [14], was used to obtain low-noise amplifiers with record noise figure of 3.3–5.7 dB at 45–85 GHz, respectively [15]. The 45-nm SOI CMOS technology has therefore a lot of potential for 90–200 GHz applications and this paper presents a low-noise amplifier with record W-band noise figure, and record output power at 170–200 GHz using balanced doublers.

#### 2.2 Technology

The IBM 45-nm SOI CMOS process cross-section is shown in Fig. 2.2. The transistor body is partially depleted and contained inside a 225-nm thick buried oxide, which isolates the transistor from the 13.5  $\Omega$ -cm silicon bulk. There are 11 metal layers above the device layer built using copper except the 2.2- $\mu$ m thick aluminum top metal LB. The shielded coplanar waveguide (CPW) transmission line is designed using LB for the signal line and B3 for the ground plane, and the LB side grounds are connected to B3 using UA and UB metal layers. A signal line width of 8  $\mu$ m with 9  $\mu$ m spacing to the side grounds results in a 50  $\Omega$  transmission line at millimeter-wave frequencies.

The floating-body NFET devices in the IBM model library are used in the amplifier and doubler designs. The SOI process offers a superior performance compared to the bulk CMOS technology due to reduced source/drain junction capacitances and improved device isolation. IBM reports a peak  $f_t$  of 485 GHz with a relaxed poly-pitch layout referenced to a 30- $\mu$ m device at the polysilicon layer [14]. However, the transistors in the available design kit have the minimum poly-pitch layout, which increases the terminal capacitances and lowers the peak  $f_t$  to 340 GHz. Furthermore, the transitions from the transistor up to the top metal result in added via resistance and capacitance, which significantly deteriorate the transistor performance. A  $30 \times 1-\mu$ m common-source transistor test cell is shown in Fig. 2.3 and is measured using a TRL calibration up to the reference planes. This measurement includes the transitions and associated parasitics from the top metal down to the transistor, and the measured  $f_t$  is 200 GHz at 0.3 mA/ $\mu$ m current

**Figure 2.2**: 45-nm SOI CMOS process metal stack-up and 50  $\Omega$  T-line cross-section (not to scale). All metal layers are copper except the aluminum top metal.

**Figure 2.3**: Measured  $f_t$  of a 30×1- $\mu$ m common-source transistor using a TRL calibration.

density.

The physical layout of a  $30 \times 1$ - $\mu$ m transistor is shown in Fig. 2.4. The transistors have dummy polysilicon gates at the outer edges for better device matching. The default transistor model from the IBM library does not fully account for the metal resistances and metal-metal/metal-poly parasitic capacitances since the process is developed for digital and mixed-signal applications. In particular, accurate modeling of the gate resistance is critical for the transistor gate and stability. Therefore, all of the metal and polysilicon layers at the transistor gate and drain are extracted up to M2 using an R/C parasitic extraction tool (Calibre [16]). Also, the source is extracted up to the surrounding M1 ground plane. Since the source connections are not included in the EM model and the parasitic inductances are not captured in the R/C extraction, extensive care is taken in the layout in order to establish a strong ground definition. Several blocks of stacked vias are used to connect the top level grounds (LB and B3 layers) to M1 and a wide M1 plane is used close to transistor source so as to minimize any undesired inductances that can degrade the device performance.

The vertical transition between the LB and M2 metal layers is 8.9  $\mu$ m, and both gate and drain sections are simulated together to include the parasitic electromagnetic (EM) coupling between them using a 2.5D EM solver (Sonnet [17]). The metal layers from LB down to B1 are modeled using the thick-metal model in Sonnet with multiple number of sheets. More than two sheets are used for the top metal layers, LB in particular, where the vertical thickness is comparable to the trace width. The metal and via resistances are taken into account as specified in the IBM process design manual.

Fig. 2.5 shows the effect of the parasitics on the transistor  $f_t$  and noise figure. The simulated peak  $f_t$  of the IBM transistor model is 300-340 GHz and decreases to 200–220 GHz at a bias current of 0.3–0.6 mA/ $\mu$ m when all transitions are modeled (Fig. 2.5a-b). The minimum noise figure (NF<sub>min</sub>) also shows a similar trend when the parasitics are included and the lowest NF<sub>min</sub> is achieved at 0.1–0.3 mA/ $\mu$ m current density (Fig. 2.5c). The added parasitics slightly change  $\Gamma_{opt}$  away from the r=1 circle on the Smith chart. As seen in Fig. 2.5b, there is not much improvement in  $f_t$  once the current density exceeds 0.3 mA/ $\mu$ m, so the transistor can be biased close to 0.3 mA/ $\mu$ m as a trade-off between high  $f_t$  and low noise figure. The measured  $f_t$  of the 30×1- $\mu$ m common-source test cell at 0.2–0.5 mA/ $\mu$ m current density is consistent with simulations.

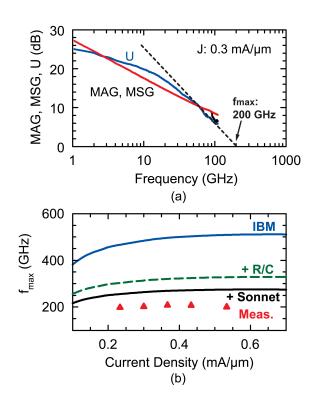

The unilateral power gain of the transistor is plotted in Fig. 2.6a together with the measured maximum available gain (MAG) and maximum stable gain (MSG). The transistor

**Figure 2.4**: Modeling of transition from top metal down to transistor level and simplified layout of a  $30 \times 1$ - $\mu$ m transistor.

**Figure 2.5**: (a) Transistor-level modeling of interconnect parasitics. The effect of parasitics (b) on  $f_t$  and (c) on NF<sub>min</sub> and  $\Gamma_{OPT}$  (30×1- $\mu$ m transistor used).

$f_{max}$  is calculated from the measured unilateral power gain (U) curve and is 200±5 GHz for a current density of 0.2-0.5 mA/ $\mu$ m [18] (Fig. 2.6b). This is lower than the IBM model (referenced to the transistor itself) which predicts an  $f_{max}$  of 460–480 GHz at this current density. The MAG and MSG curves show that the transistor becomes unconditionally stable above 90 GHz.

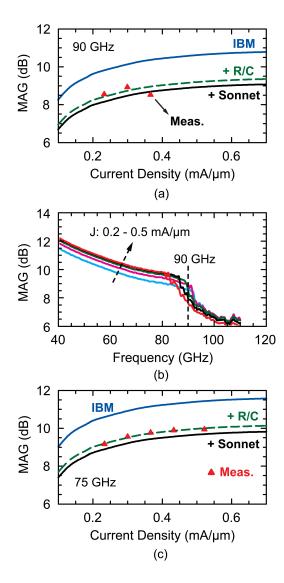

Fig. 2.7a presents the effect of parasitics on the MAG of the same transistor. The measured peak MAG is 9 dB with 0.3 mA/ $\mu$ m current density at 90 GHz, and agrees well with simulations. Fig. 2.7b is the measured MAG versus frequency at different current densities. As the current density increases, the MAG also increases, but it rolls off at a lower frequency. This is the reason for the decrease in MAG once the current density exceeds 0.3 mA/ $\mu$ m. For lower frequencies, the MAG smoothly increases as the current density is increased, and the simulated and measured MAG at 75 GHz is shown in Fig. 2.7c as an example.

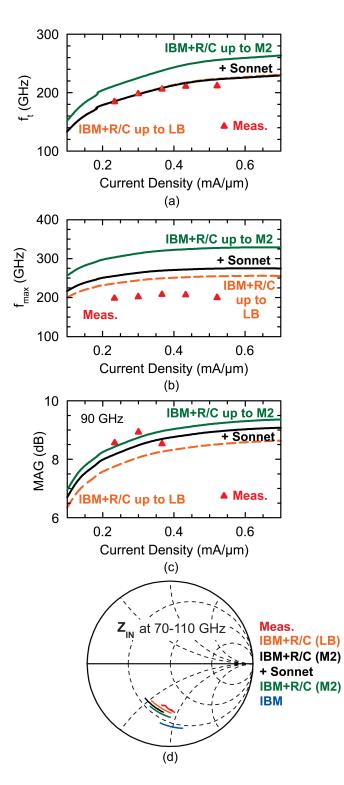

Another question that can arise about the transistor modeling is how the level of R/C extraction affect the transistor performance and what happens when all the metals up to the top metal layer are extracted without any Sonnet modeling. Fig. 2.8a-d shows how the  $f_t$ ,  $f_{max}$ , MAG, and the input impedance change for different R/C extraction scenarios, and how they compare to the Sonnet model. In Fig. 2.8a, the green curve is the IBM+R/C extraction up to M2 and the black curve is the Sonnet model applied on top of it. The orange curve is the IBM+R/C extraction up to top metal layer LB, which gives a nearly identical response compared to the Sonnet model. The R/C extraction up to the top metal yields slightly more pessimistic results for  $f_{max}$  and MAG (Fig. 2.8b-c). The input impedance is also affected by the level of extraction, and both the Sonnet and top metal R/C extraction are close to the measured impedance at 70-110 GHz (Fig. 2.8d). Based on these analyses, it can be concluded that the R/C extraction is sufficient to model the transitions from the transistor up to the LB metal without any Sonnet modeling.

#### 2.3 W-Band Amplifier

#### 2.3.1 Design

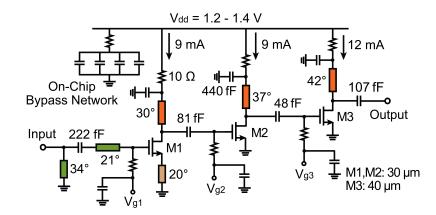

The W-band amplifier is shown in Fig. 2.9 and is based on a three-stage commonsource design using floating-body transistors. The first two stages are designed with  $30 \times 1$ - $\mu$ m transistors and the device size is increased to  $40 \times 1$ - $\mu$ m at the third stage for high output power. The current density is set to be 0.3 mA/ $\mu$ m for all stages under nominal bias conditions (discussed in Section 2.2).

Figure 2.6: (a) Measured U, MAG, and MSG vs. frequency up to 110 GHz, and (b) simulated and measured  $f_{\rm max}$  vs. current density.

**Figure 2.7**: (a) The effect of parasitics on the MAG at 90 GHz, (b) measured MAG vs. frequency for different current densities, and (c) measured MAG at 75 GHz.

Figure 2.8: The effect of different modeling scenarios on (a)  $f_t$ , (b)  $f_{max}$ , (c) MAG, and (d) input impedance at 70-110 GHz.

Figure 2.9: Schematic of the W-band amplifier.

All transmission lines and stubs are implemented using the 9-8-9  $\mu$ m (50  $\Omega$ ) grounded CPW lines with a loss of 1.1 dB/mm and a Q of 15 at 90–100 GHz according to Sonnet simulations. Shunt 440 fF capacitors, which are close to self-resonance at 90 GHz, are placed at the end of the matching stubs and provide a low impedance to ground at 80–100 GHz. Wideband on-chip bypass networks, composed of a 4  $\Omega$  polysilicon resistor in series with 0.3–2 pF thick-oxide capacitor banks, are implemented and connected to the power supply lines to prevent any oscillations due to interstage coupling. Also, 10  $\Omega$  resistors are placed in series with the drain matching stubs to further improve the stability at an expense of ~0.1 V at the drain node. These resistors are used as a conservative design measure since this was the first implementation of this process at 90–200 GHz. The gate biasing is done by using a 3 k $\Omega$  resistor, and a simple voltage divider is used at the bias pad to provide a high impedance path to ground and also decrease the sensitivity to the applied voltage (not shown).

A shorted stub is used at the source of the first-stage transistor and acts as a degeneration inductor, which increases the real part of the impedance seen at the gate. This results in two beneficial effects on the amplifier's RF performance. First, a wideband input impedance is achieved when combined with the low-Q matching sections at the input ( $S_{11} < -10$  dB at 84–103 GHz). Second,  $\Gamma_{opt}$  at the input of the first stage moves toward the 50  $\Omega$  region on the Smith chart and results in a simultaneous gain and noise figure match after the input matching network.

The high-pass interstage matching networks are composed of transmission lines at the  $V_{dd}$  paths and interstage capacitors. All of the capacitors are implemented using the vertical natural capacitor model (vncap) found in the IBM design kit. The capacitance is formed between the inter-digitated metal fingers composed of C1 to B3 metal layers. The lower metal layers are not used since they result in higher parasitic shunt capacitance per 1 fF of series capacitance,

which degrades the performance at millimeter-wave frequencies.

The simulated gain of the amplifier is 13.5 dB at 90 GHz with a 3-dB bandwidth of 85–101 GHz. The input and output return losses are wideband due to low-Q matching networks ( $S_{22} < -10$  dB at 82 – >110 GHz). The simulated NF is 5.3–4.6 dB at 90–100 GHz. The simulated saturated output power ( $P_{sat}$ ) and compression point ( $P_{1dB}$ ) at 90 GHz are 8.0 dBm and 5.5 dBm, respectively, with a peak power added efficiency (PAE) of 12% and a 1.4 V supply.

#### 2.3.2 Measurements

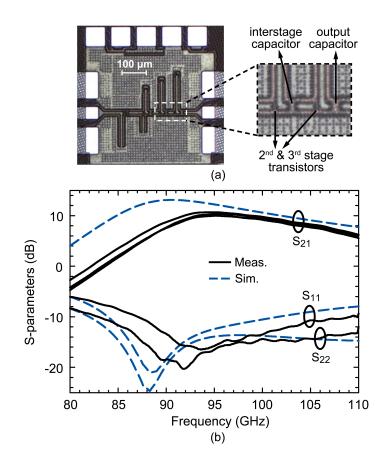

The chip microphotograph with an expanded view around the transistors is shown in Fig. 2.10a. The vertical dimension is determined by the input and output 100- $\mu$ m pitch GSG pads, hence, the transmission lines and stubs are not meandered. The resulting chip size is  $0.58 \times 0.55$  mm<sup>2</sup> including the pads.

The small-signal measurements of the W-band amplifier is performed using an Agilent network analyzer (PNA E8361A) with 75–110 GHz frequency extenders and 1-mm coaxial cables. The calibration is done up to the probe tips using an SOLT calibration substrate. The measured S-parameters are shown in Fig. 2.10b. The W-band amplifier has 10.7 dB gain at 95 GHz and a 3-dB bandwidth of 92–100 GHz for three different samples. Both input and output return losses are < -10 dB at 87–110 GHz and the measured reverse isolation (S<sub>12</sub>) is < -35 dB up to 110 GHz (not shown).

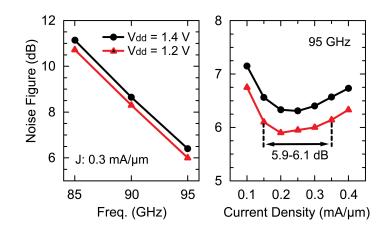

The noise figure (NF) is measured using an Agilent E4448A spectrum analyzer with a W-band noise source at the DUT input, and a waveguide amplifier/mixer down-conversion setup at the output port. The measured NF is 6.0 dB at 95 GHz as shown in Fig. 2.11 with nominal biasing (0.3 mA/ $\mu$ m) and is 5.9–6.1 dB over a wide range of bias current. NF measurements at 100 GHz could not be done since the W-band waveguide amplifier operated up to 96 GHz.

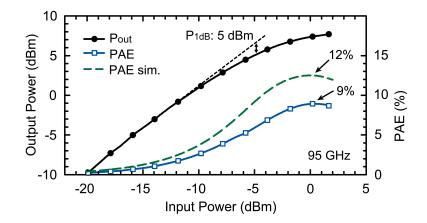

The large signal measurements are done with WR-10 waveguide components and a 1-mm coaxial setup. Agilent E8257D signal generator was used with a tripler to generate a W-band signal and a waveguide variable attenuator was used at the input for power sweeps. The measured output  $P_{1dB}$  and  $P_{sat}$  at 95 GHz are 5.2 and 7.5 dBm, respectively with a 1.4 V supply and the measured peak PAE is 9.0% at 95 GHz (Fig. 2.12). At  $P_{sat}$ , the current is 15 mA in the last stage which results in 0.15 V drop across the 10  $\Omega$  resistor and a drain voltage of 1.25 V.

The measured  $P_{sat}$  versus frequency is shown in Fig. 2.13a and is > 6 dBm at 90–100 GHz with nominal bias conditions.  $P_{sat}$  was also measured by varying the supply voltage at 95 GHz (Fig. 2.13b) and it can be increased up to 8 dBm with a 1.4 V supply by optimizing the

Figure 2.10: (a) Microphotograph of the W-band CMOS amplifier  $(0.58 \times 0.55 \text{ mm}^2)$  and (b) measured S-parameters on three different samples (only  $S_{21}$  is shown for the three samples).

Figure 2.11: Measured noise figure of the amplifier versus frequency and current density.

gate bias points. Two other amplifiers from different dies were also measured and they yielded a  $P_{sat}$  above 7.6 dBm with a 1.4 V supply at 95 GHz, showing that the amplifier can generate a high output power even with standard process variations.

## 2.4 W-to-G-Band Doubler

#### 2.4.1 Design

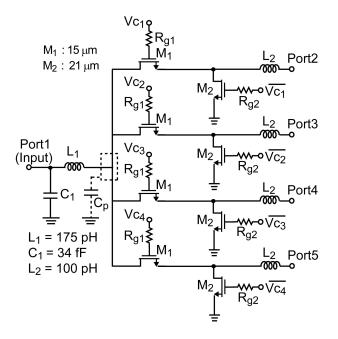

The doubler is an active balanced design as shown in Fig. 2.14. The single-ended input is converted to a differential signal using a passive balun and fed into the balanced transistor pair. The drain nodes are connected together which creates a broadband short circuit for the fundamental and odd harmonics, but the even harmonics are combined in phase. As the transistor size is increased, the doubler can yield more power, but a higher input power is required. The input power to the doubler is 6–7 dBm (see Section III) and a  $30 \times 1$ -µm transistor is simulated to achieve maximum conversion gain at this input power. Although a smaller finger width can achieve slightly more conversion gain, the finger width of 1 µm is chosen due to stability concerns (Fig. 2.15a). When the transistor is simulated without any parasitic extraction, it becomes unstable for finger widths  $\leq 1 \mu m$ . Since this was the first design trial in this process, a conservative approach is taken and the finger width is limited to 1 µm.

Second harmonic reflectors are used at the transistor inputs to further improve the doubler conversion gain [19, 20]. The 220 fF capacitors at the reflector end operate close to self-resonance, thus providing a very low impedance (0.6  $\Omega$ ) for the second harmonic at 180 GHz. The position and length of the reflectors are adjusted using EM simulations (Sonnet) to ensure

Figure 2.12: Measured output power and PAE versus input power at 95 GHz.

Figure 2.13: Measured (a) Psat and P1dB vs. frequency, (b) Psat vs. supply voltage.

Figure 2.14: Schematic of the W-to-G-band balanced doubler.

a simultaneous short circuit for the second harmonic and a high impedance for the fundamental tone at 90 GHz. Simulations show that the reflectors result in a 2 dB increase in the output power at 170–185 GHz (Fig. 2.15b).

The transistor bias condition is crucial for doubler efficiency since the conduction angle should be set correctly to maximize the second harmonic tone at the output [21]. If the drain current waveform is assumed to be a rectified cosine pulse, it can be represented by Fourier series expansion as:

$$I_{\rm d}(t) = I_0 + I_1 \cos(\omega_1 t) + I_2 \cos(\omega_2 t) + \dots$$

(2.1)

and the coefficients for  $n \ge 1$  are

$$I_{\rm n} = I_{\rm max} \frac{4t_0}{\pi T} \left| \frac{\cos(n\pi t_0/T)}{1 - (2n\pi t_0/T)^2} \right|,$$

(2.2)

where  $I_{max}$  is the maximum drain current,  $t_0$  is the duration of the pulse, and T is the period of fundamental frequency. When (2.2) is solved to maximize  $I_2$ ,  $t_0/T = 0.35$ , which corresponds to a conduction angle of 125°. Therefore, the transistor gates need to be biased below the threshold voltage ( $V_{th} = 270 \text{ mV}$ ) for optimum doubler operation and this is shown by the large-signal simulations in Fig. 2.15c.

The input balun is designed using Sonnet (Fig. 2.16). The magnetic coupling occurs vertically between the primary coil designed using the top metal LB and the secondary coil composed of stacked UB and UA metals. The distance to the ground plane is 20  $\mu$ m on each side and the trace width is 5  $\mu$ m. A 23 fF series capacitor at the input, the balun, and a 16 fF capacitor at the balun output form a multistage matching network and provide a wideband match at the doubler input (S<sub>11</sub> < -10 dB at 84–100 GHz). The simulated phase and amplitude

**Figure 2.15**: Simulations showing (a) output power and conversion gain of the doubler vs. finger width ( $30-\mu m$  wide transistors), (b) effect of reflector on the output power of the doubler, and (c) output power contours for different gate bias voltages and input power levels.

**Figure 2.16**: 3-D view of the doubler input balun and simulated phase/amplitude imbalance between the differential ports.

imbalance between the differential ports is  $< 5^{\circ}$  and < 1.5 dB at 80–100 GHz, respectively.

All the transmission lines and interconnects at the input and output of the doubler are modeled using Sonnet. Due to maximum metal density requirement for the lower metals, the B3 ground plane under the transmission-lines needs to be extensively meshed. Fig. 2.17a shows a shielded CPW line with a ground plane mesh designed for 75% maximum metal density. This effect can be captured in EM simulations and results in 0.1 dB increase in line loss per mm and a Q drop of 10% at 180 GHz. A 600- $\mu$ m long line was measured at 160–200 GHz, and the effect of the pads and the CPW transition were de-embedded using a GSG thru-section. The measured line loss is 2.2 dB/mm at 180 GHz, which is 0.7 dB higher than simulations (1.5 dB/mm) (Fig. 2.17b). The increase in line loss over simulations has been measured by several groups [10, 22] and is perhaps due to the thin Ta and W adhesion layers used in the fabrication process [23].

#### 2.4.2 Measurements

The chip microphotograph is shown in Fig. 2.18a and the DC bias for the gate and drain nodes is supplied using the top pads. The input and output pads are compatible with both 100- $\mu$ m and 80- $\mu$ m pitch GSG probes. The section after the input balun is designed symmetrically to maintain balanced operation and the transistors in the doubler core are placed in close proximity to each other so as to minimize the distance to the common drain node. The second harmonic reflectors are meandered to reduce the chip area and the total size is  $0.69 \times 0.49 \text{ mm}^2$  including the pads.

The S-parameter measurements of the doubler requires two different setups since the input and output are at different frequencies. The input return loss is measured with the same setup as the W-band amplifier and is < -10 dB at 86–108 GHz. The output return loss is measured using a 140–220 GHz (G-band) frequency extension setup and is < -10 dB at 153–175 GHz (Fig. 2.18b).

The large signal characterization is performed using a complete waveguide setup with WR-10 and WR-5 sections at the input and output, respectively (Fig. 2.19). All measurements are referenced to the GSG input and output pads. A mechanically tuned Gunn-diode oscillator is used at the input and is followed by a variable attenuator for controlling the input power. The input power is monitored using a 10-dB coupler and an Agilent E4417A power meter, and the output port is directly connected to an Erickson power meter [24]. The measured peak output power is -0.8 dBm at an input power of 6–7 dBm with -8.0 dB conversion gain at 180 GHz with a constant gate bias ( $V_g$ ) of 0.24 V for all input power levels (Fig. 2.20a). Fig. 2.20b

**Figure 2.17**: (a) CPW transmission line with ground plane meshing. (b) Measured (solid) and simulated (dashed) line loss/mm for a 50  $\Omega$  T-line. A 600- $\mu$ m line and GSG thru pads are used for line loss measurements.

**Figure 2.18**: (a) Microphotograph of the doubler  $(0.69 \times 0.49 \text{ mm}^2)$  and (b) measured S-parameters.

**Figure 2.19**: Measurement setup for doubler output power and gain characterization. An all-waveguide setup is used for accurate power measurements.

**Figure 2.20**: Measured (a) output power and gain of the doubler vs. input power at 180 GHz, (b) output power vs. frequency, and (c) DC current vs. input power.

**Figure 2.21**: Measured peak output power of the G-band doubler versus frequency for different doubler designs.

presents the measured output power at 170–190 GHz at two gate bias points. As the input power is increased, the gate bias needs to be reduced to maintain optimum conduction angle that maximizes the second harmonic generation ( $\sim$ 125°). The output power can be increased to 0 dBm by decreasing the gate bias to 0 V at 180 GHz with 3.0% drain efficiency. The DC current of the doubler is also monitored and is in good agreement with the simulations up to 7 dBm input power (Fig. 2.20c). Note that the 10  $\Omega$  resistor in Fig. 2.14 results in 0.2–0.3 V drop for Pin=5–8 dBm, and the drain voltage is  $\sim$ 1.1 V at the peak output power.

Apart from this doubler, two other doubler versions were designed and measured in order to verify the effect of finger width and the  $2^{nd}$  harmonic reflector. Fig. 2.21 shows the measured peak output power versus frequency for the three different designs. The main doubler design, which has  $30 \times 1$ - $\mu$ m transistors and an input reflector, yields the highest output power. The second version has  $15 \times 2$ - $\mu$ m transistors and results in 2.5 dB less output power due to increased gate resistance. The third version also uses  $15 \times 2$ - $\mu$ m transistors, but without the  $2^{nd}$  harmonic reflector. As predicted, the input reflector improves the output power by  $\sim 2$  dB.

# 2.5 W-Band Amplifier and G-Band Doubler

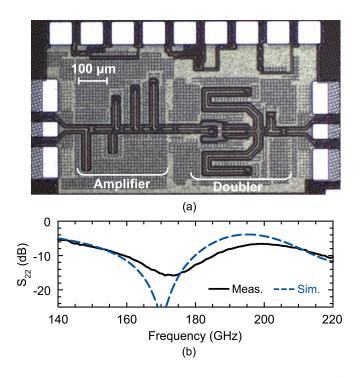

The amplifier/doubler is a cascade of the same amplifier and doubler designs discussed in the previous sections. The chip microphotograph is shown in Fig. 2.22a and the total size is  $1.0 \times 0.56 \text{ mm}^2$  including the pads. A single V<sub>dd</sub> and a single ground is used for the entire chip. The S-parameter measurement setup is same as in the case of the doubler. The input return loss is wideband and is the same as the amplifier S<sub>11</sub> (see Fig. 2.10b). The output return loss is well matched at 160–185 GHz (Fig. 2.22b), and shows a better performance than the doubler (Fig. 2.18b). The W-band amplifier has an effect on the doubler output impedance since it is not a

**Figure 2.22**: (a) Microphotograph of the amplifier/doubler  $(1.0 \times 0.56 \text{ mm}^2)$  and (b) measured output return loss.

**Figure 2.23**: Down-converted 180 GHz signal at the output of the amplifier/doubler measured using a spectrum analyzer.

wideband 50  $\Omega$  load.

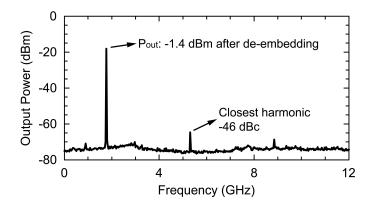

The same measurement setup of Fig. 2.19 is used for large-signal amplifier/doubler measurements. The mixer down-conversion setup is also used for verifying the results obtained by the power meter. The down-converted 180 GHz signal is shown in Fig. 2.23 with an output spectrum up to 12 GHz. The measured output power is -1.4 dBm after de-embedding the losses due to output probe, mixer, and output cable. The highest undesired tone is 46 dB lower with respect to the  $2f_0$  output signal and is due to the subharmonic mixer setup.