# UC San Diego UC San Diego Electronic Theses and Dissertations

# Title

Domain-specific translator and optimizer for massive on- chip parallelism

# Permalink

https://escholarship.org/uc/item/2tn305g1

# **Author** Unat, Didem

# Publication Date 2012

Peer reviewed|Thesis/dissertation

# UNIVERSITY OF CALIFORNIA, SAN DIEGO

### Domain-Specific Translator and Optimizer for Massive On-Chip Parallelism

A dissertation submitted in partial satisfaction of the requirements for the degree Doctor of Philosophy

in

**Computer Science**

by

Didem Unat

Committee in charge:

Professor Scott B. Baden, Chair Professor Xing Cai Professor Andrew McCulloch Professor Allan Snavely Professor Daniel Tartakovsky Professor Dean M. Tullsen

2012

Copyright Didem Unat, 2012 All rights reserved. The dissertation of Didem Unat is approved, and it is acceptable in quality and form for publication on microfilm and electronically:

Chair

University of California, San Diego

2012

# DEDICATION

To my mom, dad and sister.

### TABLE OF CONTENTS

| Signature Page  | ÷           |          | ••••••••••••••                            | iii    |

|-----------------|-------------|----------|-------------------------------------------|--------|

| Dedication      |             |          |                                           | iv     |

| Table of Conte  | nts .       |          |                                           | v      |

| List of Figures |             |          |                                           | ix     |

| List of Tables  |             |          |                                           | iii    |

| Acknowledger    | nents       |          |                                           | ٢v     |

| Vita            |             |          | xv                                        | ⁄ii    |

| Abstract of the | Disse       | ertation |                                           | iii    |

| Chapter 1       | Intro       | duction  |                                           | 1      |

| Chapter 2       | Moti<br>2.1 |          | nd Background                             | 5<br>5 |

|                 | 2.1         | 2.1.1    | General-Purpose Multicore Processors      | 7      |

|                 |             | 2.1.2    | Massively Parallel Single Chip Processors | 8      |

|                 |             | 2.1.3    | Graphics Processing Units                 | 8      |

|                 | 2.2         | Applica  | ation Characteristics                     | 11     |

|                 |             | 2.2.1    | Structured Grids                          | 15     |

|                 | 2.3         | Paralle  | Programming Models                        | 17     |

|                 |             | 2.3.1    | <b>OpenMP</b>                             | 18     |

|                 |             | 2.3.2    | CUDA 1                                    | 19     |

|                 |             | 2.3.3    | OpenCL                                    | 21     |

|                 |             | 2.3.4    | Annotation-based Models                   | 21     |

|                 |             | 2.3.5    | Domain-Specific Approaches                | 23     |

|                 | 2.4         | Summa    | ury                                       | 24     |

| Chapter 3       | Mint        | Program  | nming Model                               | 25     |

|                 | 3.1         | System   | Assumptions                               | 25     |

|                 | 3.2         | The Mo   |                                           | 27     |

|                 |             | 3.2.1    | Execution Model                           | 28     |

|                 |             | 3.2.2    | Memory Model                              | 28     |

|                 | 3.3         | The Mi   |                                           | 29     |

|                 |             | 3.3.1    | Parallel Region Directive                 | 29     |

|                 |             | 3.3.2    |                                           | 30     |

|                 |             | 3.3.3    |                                           | 31     |

|                 |             | 3.3.4    | Other Directives                          | 32     |

|                 |             | 3.3.5    | Reduction Clause                          | 33     |

|                 |             | 3.3.6    | Task Parallelism under Mint   3           | 33     |

|           | 3.4  | Mint Program Example                                               |

|-----------|------|--------------------------------------------------------------------|

|           | 3.5  | Performance Programming with Mint                                  |

|           |      | 3.5.1 Compiler Options                                             |

|           | 3.6  | Summary                                                            |

| Chapter 4 | Mint | Source-to-Source Translator                                        |

| -         | 4.1  | ROSE Compiler Framework    38                                      |

|           | 4.2  | Mint Baseline Translator                                           |

|           |      | 4.2.1 Memory Manager                                               |

|           |      | 4.2.2 Outliner                                                     |

|           |      | 4.2.3 Kernel Configuration                                         |

|           |      | 4.2.4 Argument Handler                                             |

|           |      | 4.2.5 Work Partitioner                                             |

|           |      | 4.2.6 Generated Host Code Example                                  |

|           |      | 4.2.7 Generated Device Code Example                                |

|           |      | 4.2.8 Chunking                                                     |

|           |      | 4.2.9 Miscellaneous                                                |

|           | 4.3  | Summary                                                            |

| Chapter 5 | Mint | Optimizer                                                          |

| <b>T</b>  | 5.1  | Hand-Optimization of Stencil Methods                               |

|           |      | 5.1.1 Stencil Pattern                                              |

|           |      | 5.1.2 GPU Parallelization of Stencil Methods                       |

|           |      | 5.1.3 Common Subexpression Elimination 60                          |

|           | 5.2  | Overview of the Mint Optimizer                                     |

|           | 5.3  | Stencil Analyzer                                                   |

|           |      | 5.3.1 Array Reference List                                         |

|           |      | 5.3.2 Shareable References                                         |

|           |      | 5.3.3 Shared Memory Slots                                          |

|           |      | 5.3.4 Access Frequencies                                           |

|           |      | 5.3.5 Selecting Variables                                          |

|           |      | 5.3.6 Offset Analysis                                              |

|           | 5.4  | Unrolling Short Loops                                              |

|           |      | Cache Configuration with PreferL1                                  |

|           | 5.6  | Register Optimizer                                                 |

|           | 5.7  | Shared Memory Optimizer                                            |

|           |      | 5.7.1 Declaration and Initialization of a Shared Memory Block . 72 |

|           |      | 5.7.2 Handling Ghost Cells                                         |

|           |      | 5.7.3 Replacing Global Memory References                           |

|           |      | 5.7.4 Shared Memory Code Example                                   |

|           | 5.8  | Chunksize Clause                                                   |

|           | 5.9  | Miscellaneous                                                      |

|           |      | Summary                                                            |

|           | 5.10 | Summary                                                            |

| Chapter 6 | Con  | nmonly U | Jsed Stencil Kernels                               | ••• | <br>80  |

|-----------|------|----------|----------------------------------------------------|-----|---------|

|           | 6.1  | Testbe   | ds                                                 | ••• | <br>80  |

|           |      | 6.1.1    | Triton Compute Cluster                             | ••• | <br>80  |

|           |      | 6.1.2    | GPU Devices                                        | ••• | <br>81  |

|           | 6.2  | Comm     | only Used Stencil Kernels                          | ••• | <br>83  |

|           |      | 6.2.1    | Performance Comparison                             | • • | <br>85  |

|           |      | 6.2.2    | Compiler-Assisted Performance Tuning               |     | <br>87  |

|           |      | 6.2.3    | Mint vs Hand-CUDA                                  |     | <br>92  |

|           | 6.3  | Summa    | ary                                                | ••• | <br>93  |

| Chapter 7 | Real | -World   | Applications                                       | ••• | <br>95  |

|           | 7.1  | AWP-0    | DDC Seismic Modeling                               | ••• | <br>95  |

|           |      | 7.1.1    | Background                                         |     | <br>95  |

|           |      | 7.1.2    | The AWP-ODC Model                                  |     | <br>97  |

|           |      | 7.1.3    | Stencil Structure and Computational Requirements . |     | <br>100 |

|           |      | 7.1.4    | Mint Implementation                                |     | <br>101 |

|           |      | 7.1.5    | Performance Results                                |     | <br>104 |

|           |      | 7.1.6    | Performance Impact of Nest and Tile Clauses        |     | 106     |

|           |      | 7.1.7    | Performance Tuning with Compiler Options           |     | 107     |

|           |      | 7.1.8    | Shared Memory Option                               |     | <br>108 |

|           |      | 7.1.9    | Chunksize Clause                                   |     | 110     |

|           |      | 7.1.10   | Analysis of Individual Kernels                     |     | 112     |

|           |      | 7.1.11   | Hand-coded vs Mint                                 |     | 114     |

|           |      | 7.1.12   | Summary                                            |     | 115     |

|           | 7.2  |          | Interest Point Detection Algorithm                 |     | 117     |

|           |      | 7.2.1    | Background                                         |     | 117     |

|           |      | 7.2.2    | Interest Point Detection Algorithm                 |     | 117     |

|           |      | 7.2.3    | The Stencil Structure and Storage Requirements     |     | 119     |

|           |      | 7.2.4    | Mint Implementation                                |     | 120     |

|           |      | 7.2.5    | Index Expression Analysis                          |     | 121     |

|           |      | 7.2.6    | Volume Datasets                                    |     | 121     |

|           |      | 7.2.7    | Performance Results                                |     | 123     |

|           |      | 7.2.8    | Performance Tuning with Compiler Options           |     | 124     |

|           |      | 7.2.9    | Summary                                            |     | 127     |

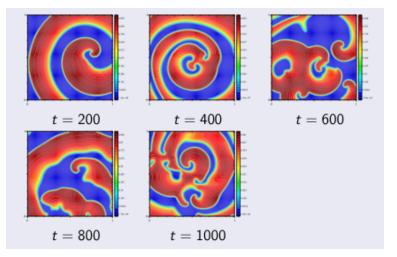

|           | 7.3  |          | Panfilov Model of Cardiac Excitation               |     | 129     |

|           |      | 7.3.1    | Background                                         |     | 129     |

|           |      | 7.3.2    | The Aliev-Panfilov Model                           |     | 129     |

|           |      | 7.3.3    | Stencil Structure and Computational Requirements . |     | <br>130 |

|           |      | 7.3.4    | Mint Implementation                                |     | 133     |

|           |      | 7.3.5    | Performance Results                                |     | 133     |

|           |      | 7.3.6    | Performance Tuning with Compiler Options           |     | 134     |

|           |      | 7.3.7    | Summary                                            |     | 136     |

|           | 7.4  |          | sion                                               |     | 136     |

|           |      |          |                                                    |     |         |

| Chapter 8    | Future Work and Conclusion            |

|--------------|---------------------------------------|

|              | 8.1 Limitations and Future Work       |

|              | 8.1.1 Multi-GPU Platforms             |

|              | 8.1.2 Targeting Other Platforms       |

|              | 8.1.3 Extending Mint for Intel MIC    |

|              | 8.1.4 Performance Modeling and Tuning |

|              | 8.1.5 Domain-Specific Translators     |

|              | 8.1.6 Compiler Limitations            |

|              | 8.2 Conclusion                        |

| Appendix A   | Mint Source Distribution              |

| Appendix B   | Cheat Sheet for Mint Programmers      |

| r r          | B.1 Mint Interface                    |

| Appendix C   | Mint Tuning Guide for Nvidia GPUs     |

|              | C.1 Tuning with Clauses               |

|              | C.2 Tuning with Compiler Options      |

| Bibliography |                                       |

### LIST OF FIGURES

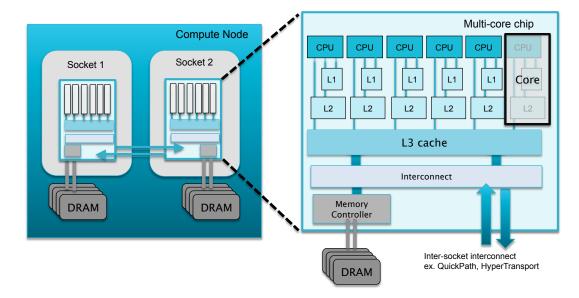

| Figure 2.1:  | Abstract machine model of a compute node containing two general-purpose multicore chips on two sockets, each with 6 cores.                                                                                                   | 6        |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

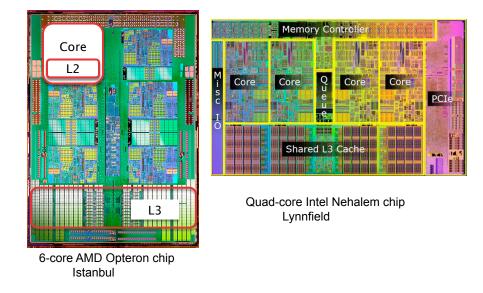

| Figure 2.2:  | Two examples for 45 nm process technology                                                                                                                                                                                    | 7        |

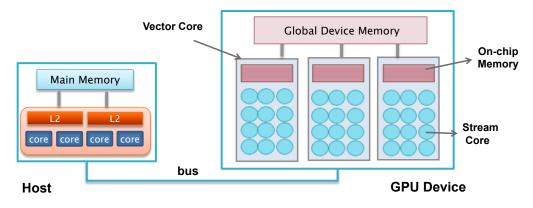

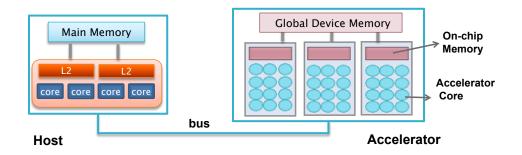

| Figure 2.3:  | Abstract machine model of a GPU device connected to a host processor                                                                                                                                                         | 9        |

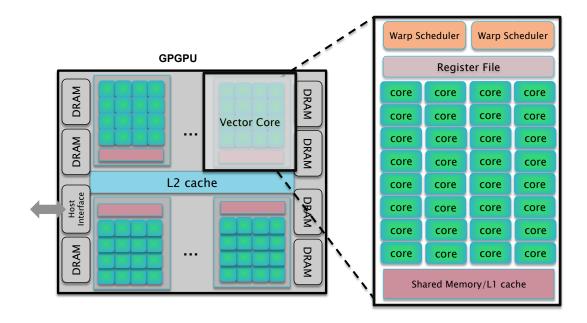

| Figure 2.4:  | Nvidia GPU architecture                                                                                                                                                                                                      | 10       |

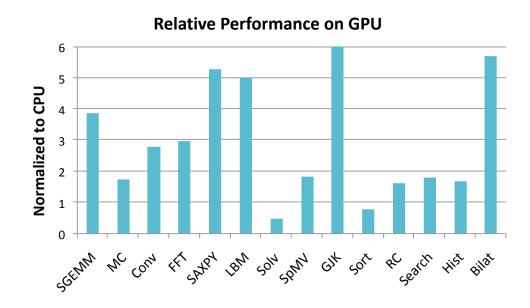

| Figure 2.5:  | Comparison between Core i7 and GTX 280 performance on various appli-<br>cations. The data was collected from Victor Lee et. al [LKC <sup>+</sup> 10]                                                                         | 12       |

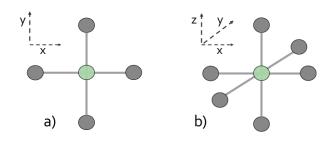

| Figure 2.6:  | a) 5-point stencil b) 7-point stencil                                                                                                                                                                                        | 15       |

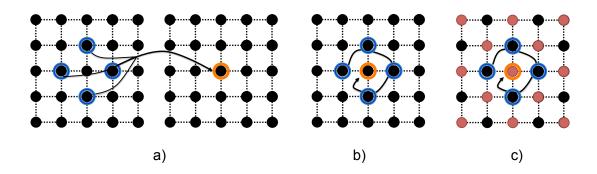

| Figure 2.7:  | Iterative Methods for Solving Linear Systems: a) Jacobi Method b) Gauss-Seidel Method c) Gauss-Seidel Red-Black Method                                                                                                       | 16       |

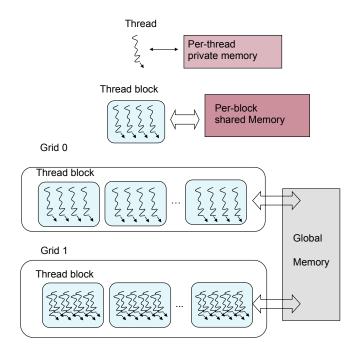

| Figure 2.8:  | Memory and thread hierarchy in CUDA                                                                                                                                                                                          | 20       |

| Figure 3.1:  | Abstract Machine Model viewed by the Mint Programming Model                                                                                                                                                                  | 26       |

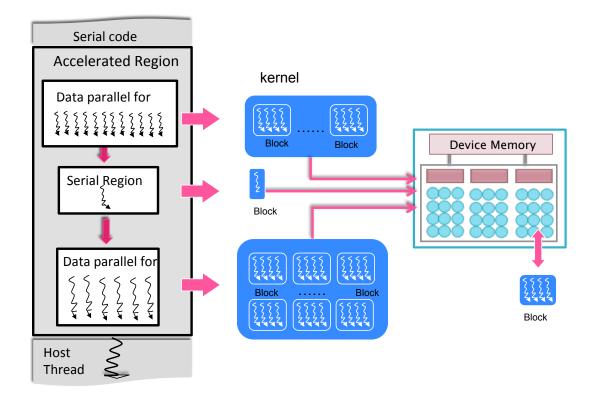

| Figure 3.2:  | Mint Execution Model                                                                                                                                                                                                         | 27       |

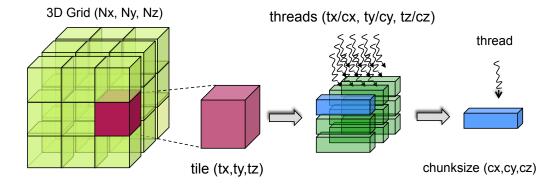

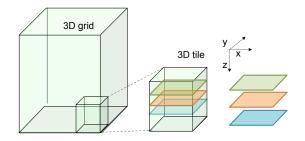

| Figure 3.3:  | A 3D grid is broken into 3D tiles based on the tile clause. A thread block computes a tile. Elements in a tile are divided among a thread block based on chunksize clause. Each thread computes chunksize many elements in a | 0.1      |

|              | tile                                                                                                                                                                                                                         | 31       |

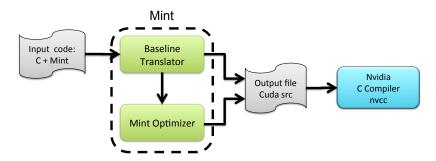

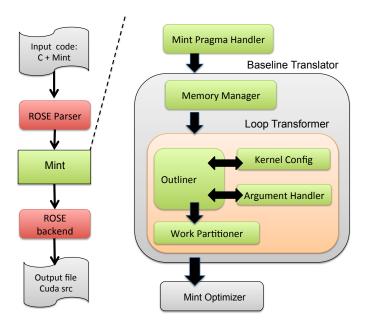

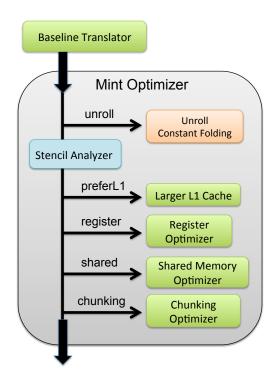

| Figure 4.1:  | Mint Translator has two main stages: Baseline Translator and Optimizer.<br>Mint generates CUDA source file, which can be subsequently compiled by                                                                            | 20       |

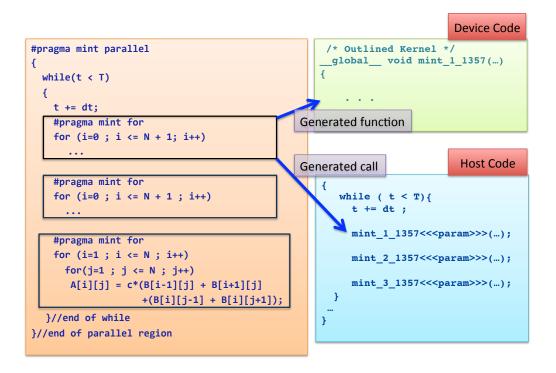

| Figure 4.2:  | the Nvidia C compiler                                                                                                                                                                                                        | 38<br>40 |

| Figure 4.3:  | Pseudo-code showing how Mint processes copy directives inside a parallel region                                                                                                                                              | 41       |

| Figure 4.4:  | Outliner outlines each parallel for-loop into a CUDA kernel.                                                                                                                                                                 | 43       |

| Figure 4.5:  | Pseudo-code for the work partitioner in the translator.                                                                                                                                                                      | 46       |

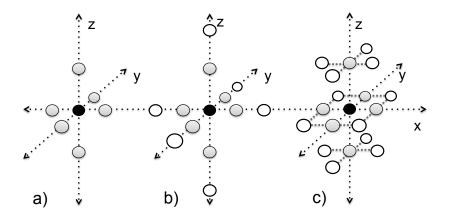

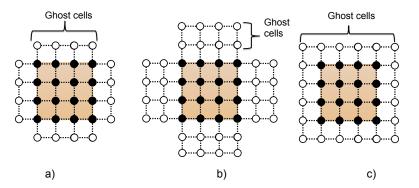

| Figure 5.1:  | A stencil contains a specific set of data points in a surrounding neighborhood. The black point is the point of interest. a) 7-point stencil, b) 13-point                                                                    |          |

|              | stencil, c) 19-point stencil                                                                                                                                                                                                 | 56       |

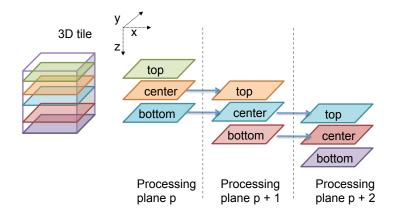

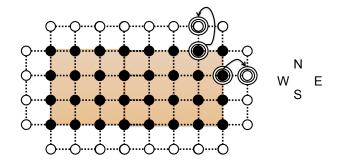

| Figure 5.2:  | Divide 3D grid into 3D blocks and process each block plane by plane                                                                                                                                                          | 57       |

| Figure 5.3:  | Ghost cells for a) 7-point stencil, b) 13-point stencil, c) 19-point stencil                                                                                                                                                 | 57       |

| Figure 5.4:  | Chunking for a three plane implementation. A plane starts as the bottom, continues as the center and then as the top.                                                                                                        | 58       |

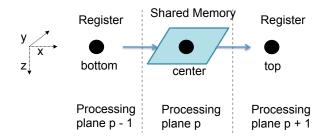

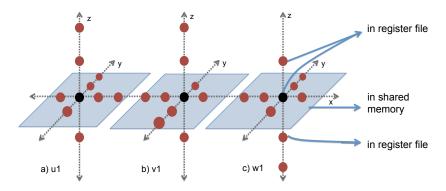

| Figure 5.5:  | In chunking optimization, a plane starts as the bottom in registers, continues as the center in shared memory and then as the top in registers.                                                                              | 60       |

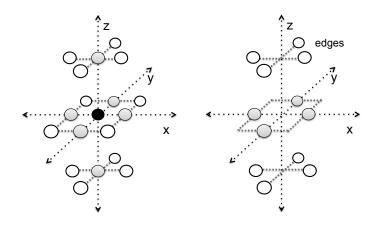

| Figure 5.6:  | Visualizing 19-point stencil on the left and its edges on the right. We reuse                                                                                                                                                | 00       |

| - 19410 0101 | the sum of the edges in top, center and bottom planes                                                                                                                                                                        | 61       |

| Figure 5.7:  | Workflow of Mint Optimizer                                                                                                                                                                                                   | 62       |

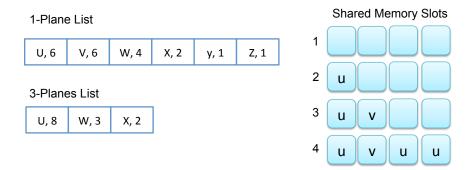

| Figure 5.8:  | Filling shared memory slots with selected variables                                                                                                                                                                          | 68       |

| Figure 5.9:  | Two threads and their respective ghost cell assignments.                                                                                                                                                                     | 73       |

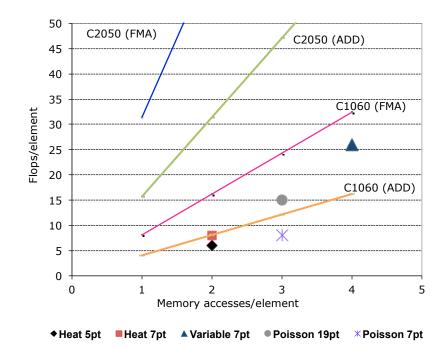

| Figure 6.1: | Flops/element and memory accesses/element of the kernels and flops:word ratios for the test devices.                                                                                                                                                                                                                                                                                                                                                                                                                                          | 84  |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

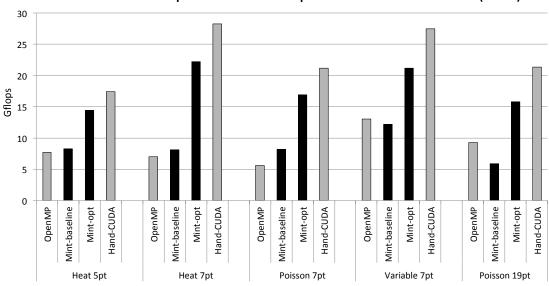

| Figure 6.2: | Performance comparison of the kernels. OpenMP ran with 8 threads on the E5530 Nehalem. Mint-baseline corresponds to the Mint baseline translation without using the Mint optimizer, Mint-opt with optimizations turned on, and Hand-CUDA is hand-optimized CUDA. The Y-axis shows the measured                                                                                                                                                                                                                                                |     |

| Figure 6.3: | Gflop rate. Heat 5-pt is a 2D kernel, the rest are 3D Performance comparison of the Tesla C1060 and C2050 on the stencil kernels. Mint-baseline corresponds to the Mint baseline translation without using the Mint optimizer, Mint-opt with optimizations turned on, and Hand-                                                                                                                                                                                                                                                               | 85  |

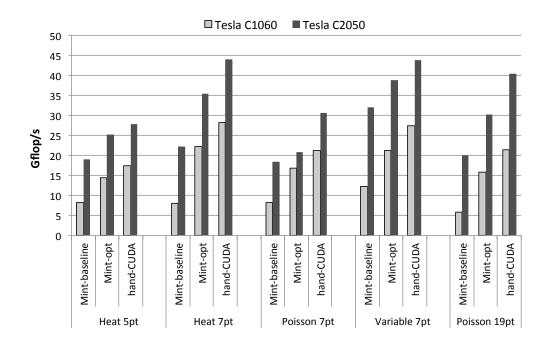

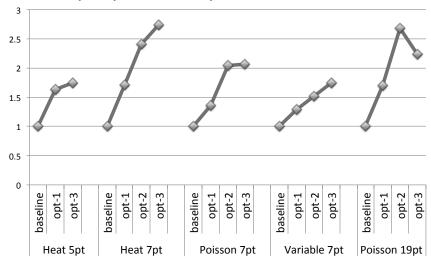

| Figure 6.4: | CUDA is hand-optimized CUDA. The Y-axis shows the measured Gflop rate. Heat 5-pt is a 2D kernel, the rest are 3D Effect of the Mint optimizer on the Tesla C1060. The baseline resolves all the array references through device memory. <i>Opt-1</i> turns on shared memory                                                                                                                                                                                                                                                                   | 86  |

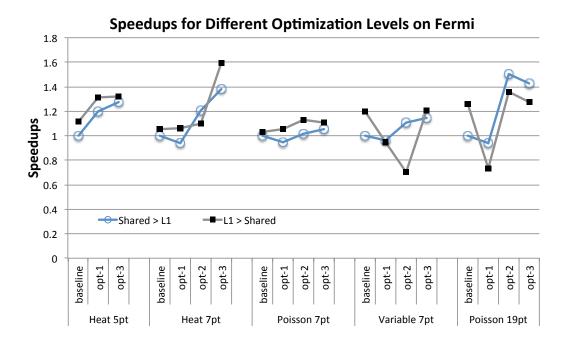

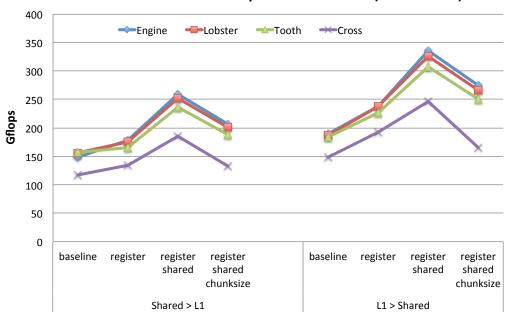

| Figure 6.5: | optimization ( <i>-shared</i> ). <i>Opt-2</i> utilizes the chunksize clause and <i>-shared</i> .<br><i>Opt-3</i> adds register optimizations ( <i>-shared -register</i> ) Effect of the Mint optimizer on the performance on the Tesla C2050. The baseline resolves all the array references through device memory. $L1 >$ <i>Shared</i> favors larger cache. <i>Shared</i> > $L1$ favors larger shared memory.                                                                                                                               | 88  |

|             | <i>Opt-1</i> turns on shared memory optimization ( <i>-shared</i> ). <i>Opt-2</i> utilizes the chunksize clause and <i>-shared</i> . <i>Opt-3</i> adds register optimizations ( <i>-shared -register</i> )                                                                                                                                                                                                                                                                                                                                    | 90  |

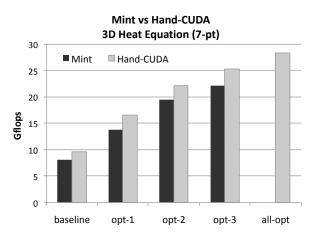

| Figure 6.6: | Comparing the performance of Mint-generated code and hand-coded CUDA. <i>All-opt</i> is the same as the Hand-CUDA variant used in Fig.6.2. <i>All-opt</i> indicates additional optimizations on top of Hand-CUDA <i>opt-3</i> . The results were obtained on the Tesla C1060.                                                                                                                                                                                                                                                                 | 92  |

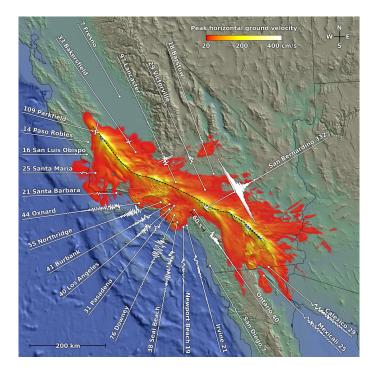

| Figure 7.1: | The colors on this map of California show the peak ground velocities for a magnitude-8 earthquake simulation. White lines are horizontal-component seismograms at surface sites (white dots). On 436 billion spatial grid points, the largest-ever earthquake simulation, in total 360 seconds of seismic wave excitation up to frequencies of 2 Hz was simulated. Strong shaking of long duration is predicted for the sediment-filled basins in Ventura, Los Angeles, San Bernardino, and the Coachella Valley, caused by a strong coupling |     |

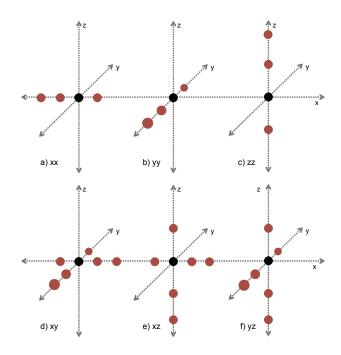

| Figure 7.2: | between rupture directivity and basin-mode excitation $[COJ^+10]$ Stencil shapes of the stress components used in the velocity kernel. The kernel uses a subset of asymmetric 13-point stencil, coupling 4 points from <i>xx</i> , <i>yy</i> and <i>zz</i> and 8 points from <i>xy</i> , <i>xz</i> and <i>yz</i> with their central point referenced                                                                                                                                                                                          | 96  |

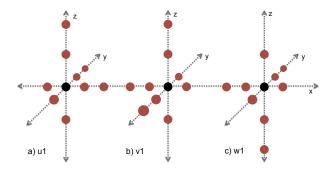

| Figure 7.3: | twice                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 100 |

| Figure 7.4: | $u_1, v_1$ and $w_1$ with central point accessed 3 times                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 101 |

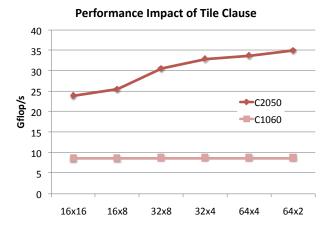

|             | mance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 106 |

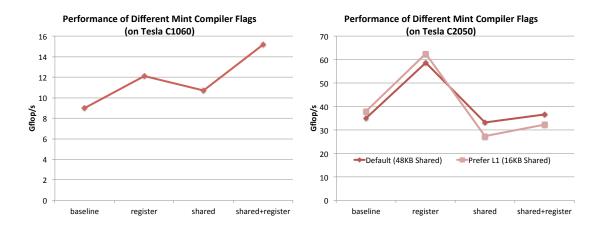

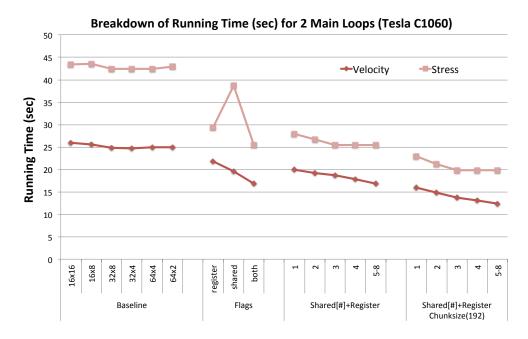

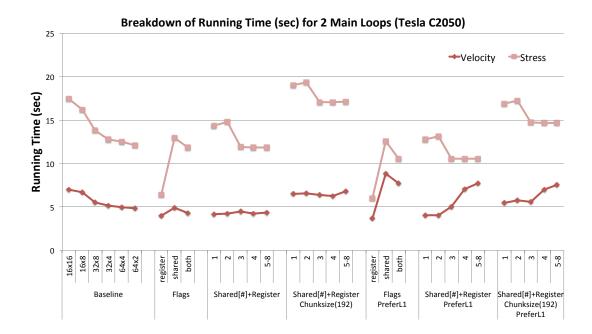

| Figure 7.5:   | On the C1060 (left), the best performance is achieved when both the shared           |     |

|---------------|--------------------------------------------------------------------------------------|-----|

|               | memory and register flags are used. The results are with the nest(all),              |     |

|               | tile(32,4,1) and chunksize(1,1,1) clause configurations. The shared                  |     |

|               | flag is set to 8. On the C2050 (right), the best performance is achieved             |     |

|               | when a larger L1 cache and registers are used. The results are with the              |     |

|               | <pre>nest(all), tile(64,2,1) and chunksize(1,1,1) configurations. The</pre>          |     |

|               | shared flag is set to 8                                                              | 107 |

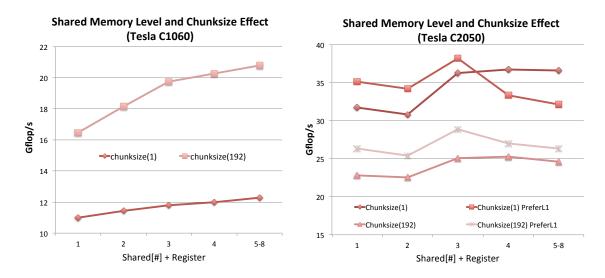

| Figure 7.6:   | On the C1060 (left), chunksize and shared memory optimizations improve               |     |

| C             | the performance but on the C2050 (right), these optimizations are counter-           |     |

|               | productive                                                                           | 109 |

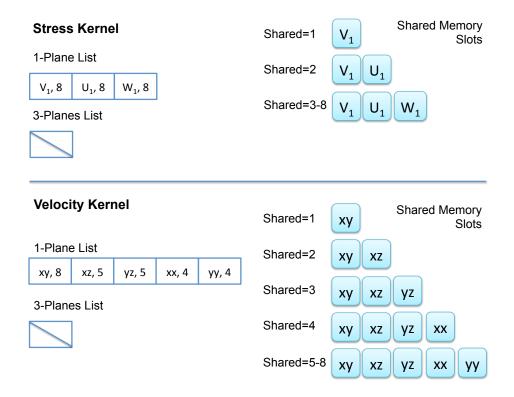

| Figure 7.7:   | Result of selection algorithm for shared memory slots                                | 110 |

| Figure 7.8:   | shows where the data is kept when both register and shared memory opti-              | 110 |

| 1 iguie 7.0.  | mizers are turned on and chunking is used.                                           | 111 |

| Eigura 7.0.   |                                                                                      | 111 |

| Figure 7.9:   | Running time (sec) for the most time-consuming kernels in AWP-ODC for                |     |

|               | 400 iterations on the Tesla C1060. Lower is better. The compiler flag "both"         | 110 |

|               | indicates shared+register. Lower is better.                                          | 112 |

| Figure 7.10:  |                                                                                      |     |

|               | 400 iterations on the 2050. Lower is better. The compiler flag "both" indi-          |     |

|               | cates shared+register. Lower is better.                                              | 113 |

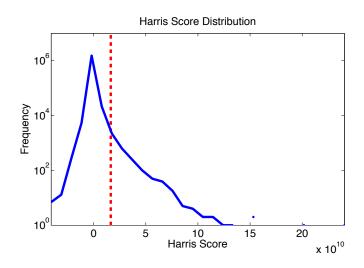

| Figure 7.11:  |                                                                                      |     |

|               | histogram of the Harris score. Large positive values are considered interest         |     |

|               | points or corner points, near zero points are flat areas, and negative values        |     |

|               | indicate edges. The dotted line shows the threshold                                  | 117 |

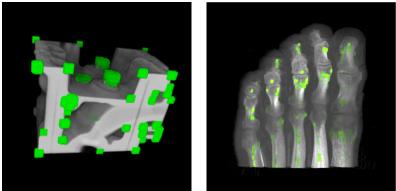

| Figure 7.12:  | The Harris corner detection algorithm applied to the Engine Block CT Scan            |     |

|               | from General Electric, USA and the Foot CT Scan from Philips Research,               |     |

|               | Hamburg, Germany. The algorithm identified the corners of the engine                 |     |

|               | block and around the joints in the foot image as interest points, shown with         |     |

|               | green squares.                                                                       | 118 |

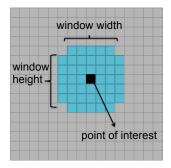

| Figure 7.13:  | Coverage of a Gaussian convolution for a pixel in a 2D image                         | 120 |

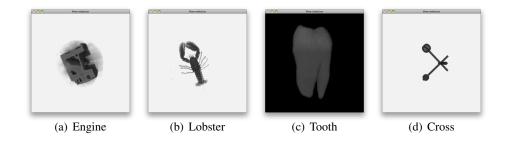

| -             | Four well-known volume datasets in volume rendering                                  | 123 |

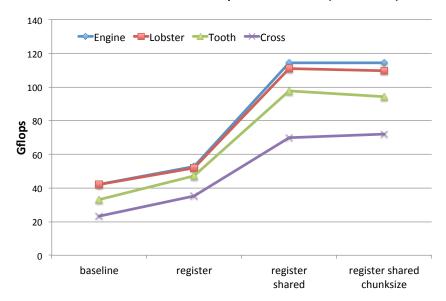

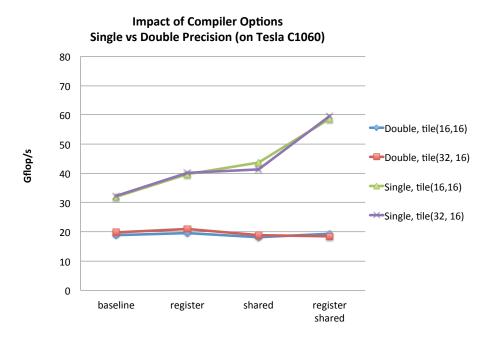

| •             | Impact of the Mint optimizer on the performance, running on the Tesla                |     |

| 0             | C1060. The best performance is achieved when register and shared memory              |     |

|               | are used.                                                                            | 125 |

| Figure 7 16.  | Performance impact of the Mint optimizer on the performance on the Tesla             | 120 |

| 1 iguie 7.10. | C2050. The best performance is achieved when register, shared memory,                |     |

|               | and large L1 cache are used. Shared > L1 refers to a larger shared memory            |     |

|               | (48KB) on the C2050 and L1 > Shared refers to a larger L1 cache (48KB).              | 126 |

| Eigung 7 17.  |                                                                                      | 120 |

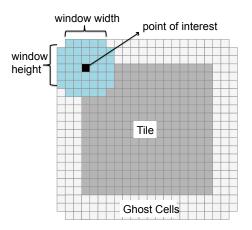

| Figure 7.17:  | A tile and its respective ghost cells in shared memory. The block point is the       |     |

|               | point of interest. The $5 \times 5$ region around the black point shows the coverage | 107 |

|               | of the Gaussian convolution.                                                         | 127 |

| Figure 7.18:  |                                                                                      | 129 |

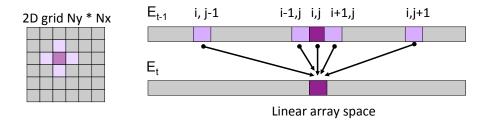

| Figure 7.19:  | The PDE solver updates the voltage $E$ according to weighted contributions           |     |

|               | from the four nearest neighboring positions in space using 5-pt stencil              | 131 |

| Figure 7.20:  | Effect of the Mint compiler options on the Aliev-Panfilov method for an              |     |

|               | input size N=4K. Double indicates double precision. Single indicates single          |     |

|               | precision.                                                                           | 134 |

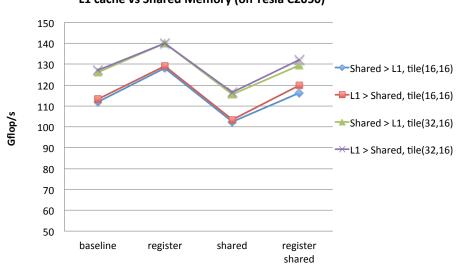

| Figure 7.21: | Effect of the Mint compiler options on the Aliev-Panfilov method for an                   |     |

|--------------|-------------------------------------------------------------------------------------------|-----|

|              | input size N=4K. The results are for single precision. $L1 > Shared$ corre-               |     |

|              | sponds to favoring a larger cache. Shared > $L1$ corresponds to favoring a                |     |

|              | larger shared memory.                                                                     | 135 |

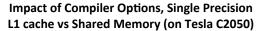

| Figure 7.22: | Effect of the Mint compiler options on the Aliev-Panfilov method for an                   |     |

|              | input size N=4K. The results are for double precision. <i>L1</i> > <i>Shared</i> favors a |     |

|              | larger cache. Shared > $L1$ favors a larger shared memory                                 | 137 |

| Figure 8.1:  | Integrated accelerator on the chip with the host cores. All cores share main              |     |

|              | memory but the memory is partitioned between the host and accelerator.                    | 140 |

### LIST OF TABLES

| Table 2.1:                                                          | Characteristics of the benchmarks and speedups of the GTX 280 over the Core i7.                                                                                                                              | 13             |

|---------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| Table 2.2:                                                          | Code for the 3D heat equation with fully-explicit finite differencing. $12_{unev}$ corresponds to $u^{n+1}$ and $12_u$ to $u^n$ and $c_0=1-6\kappa\Delta t/\Delta x^2$ and $c_1=\kappa\Delta t/\Delta x^2$ . | 17             |

| Table 3.1:<br>Table 3.2:<br>Table 3.3:                              | Mint program for the 7-point heat solverSummary of Mint Compiler OptionsSummary of Mint Directives                                                                                                           | 34<br>35<br>36 |

| Table 4.1:         Table 4.2:         Table 4.3:         Table 4.4: | Mint program for the 7-point 3D stencil                                                                                                                                                                      | 47<br>49<br>50 |

| Table 4.5:                                                          | for CUDA function arguments                                                                                                                                                                                  | 52<br>53       |

| Table 5.1:<br>Table 5.2:<br>Table 5.3:<br>Table 5.4:                | Algorithm computing array access frequencies                                                                                                                                                                 | 65<br>67<br>70 |

| Table 5.5:<br>Table 5.6:                                            | presented in Table 7.10                                                                                                                                                                                      | 71<br>73       |

| Table 5.7:                                                          | model presented in Table 7.10                                                                                                                                                                                | 75             |

| Table 5.8:                                                          | Swapping index variables.                                                                                                                                                                                    | 76<br>77       |

| Table 6.1:<br>Table 6.2:                                            | Device Specifications. SM: Stream Multiprocessor                                                                                                                                                             | 81             |

| Table 6.3:                                                          | width                                                                                                                                                                                                        | 82<br>83       |

| Table 7.1:                                                          | Description of 3D grids in the AWP-ODC code. $*r1 - r6$ hold temporal values during computations but they are not outputs.                                                                                   | 99             |

| Table 7.2:                                                          | Pseudo-code for the main loop, which contains the two most time-consuming loops, velocity and stress. $c_1$ , $c_2$ and $dt$ are scalar constants.                                                           | 102            |

| Table 7.3:             | Number of memory accesses, flops per element and flops:word ratio of the AWP-ODC kernels.                                                                           | 103 |

|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Table 7.4:             | Summarizes the lines of code annotated and generated for the AWP-ODC                                                                                                | 105 |

| 10010 7.4.             | simulation.                                                                                                                                                         | 104 |

| Table 7.5:             | Comparing performance of AWP-ODC on the two devices and a cluster of                                                                                                |     |

|                        | Nehalem processors (Triton). The Mint-generated code running on a single                                                                                            |     |

|                        | Tesla C2050 exceeds the performance of the MPI implementation running                                                                                               |     |

|                        | on 32 cores. Hand-CUDA refers to the hand coded (and optimized) CUDA                                                                                                |     |

| <b>T</b> 11 <b>T</b> ( | version.                                                                                                                                                            | 105 |

| Table 7.6:             | Main loop for the 3D Harris interest point detection algorithm.                                                                                                     | 122 |

| Table 7.7:             | Sizes of the volume datasets used in the experiment                                                                                                                 | 123 |

| Table 7.8:             | Comparing the running time in seconds for different implementations of the                                                                                          |     |

|                        | Harris interest point detection algorithm, using four volume datasets with a $5 \times 5 \times 5$ convolution window. The Tesla C2050 is configured as 48KB shared |     |

|                        | memory and 16KB L1 cache.                                                                                                                                           | 124 |

| Table 7.9:             | Instruction mix in the PDE and ODE solvers. Madd: Fused multiply-add.                                                                                               | 124 |

| 14010 7.9.             | *Madd contains two operations but is executed in a single instruction                                                                                               | 131 |

| Table 7.10:            | Mint implementation of the Aliev-Panfilov model                                                                                                                     | 131 |

| Table 7.11:            | Comparing Gflop/s rates of different implementations of the Aliev-Panfilov                                                                                          | 152 |

| 10010 /1111            | Model in both single and double precision for a 2D mesh size $4K \times 4K$ .                                                                                       |     |

|                        | Hand-CUDA indicates the performance of a manually implemented and op-                                                                                               |     |

|                        | timized version. Mint indicates the performance of the Mint-generated code                                                                                          |     |

|                        | when the compiler optimizations are enabled.                                                                                                                        | 133 |

| Table 8.1:             | Performance of non-stencil Kernels. MatMat: Matrix-Matrix Multiplication.                                                                                           | 143 |

| Table A.1:             | Mint source code directory structure. The lines of codes is indicated in paren-                                                                                     |     |

|                        | thesis.                                                                                                                                                             | 149 |

| T-1.1. D 1             |                                                                                                                                                                     | 151 |

| Table B.1:             | Contiguous memory allocation for a 3D array                                                                                                                         | 151 |

| Table B.2:             | Mint Directives and Supportive Clauses                                                                                                                              | 152 |

#### ACKNOWLEDGEMENTS

In the first place, I would like to thank my thesis advisor, Scott Baden, for his guidance, patience and support throughout this research. He is very generous with his time, allowed me to work at my own pace and encouraged my personal growth. His wisdom, principles, and commitment to the highest standards inspired me from the very beginning of this research. I am also grateful to my committee members: Xing Cai, Allan Snavely, Daniel Tartakovsky, Andrew McCulloch and Dean Tullsen. Xing Cai undertook to act as my mentor at Simula with a great interest and enthusiasm. His feedback has been always prompt and invaluable. Allan Snavely took time to provide much advice on my research direction. I am very thankful to Simula for the generous 4-year of funding for my research by the Center of Excellence grant from the Norwegian Research Council to the Center for Biomedical Computing at Simula Research laboratory. Although the financial support is hugely appreciated, the greatest benefit for me was the opportunity to visit the lab in Norway twice and work closely with researchers at the lab.

I would like to thank a number of people who were essential in my career path leading up to the Ph.D. program: Irfan Ahmad, Pinar Pekel, Can Ozturan, Reyyan Somuncuoglu, and Ilkay Boduroglu. I was lucky to share my office with Han, Yajaira, Tan, Pietro, and Alden and the visiting students; Mohammed, Alex, and Tor. They were very enthusiastic about having coffee and fro-yo breaks with me (especially when I got bored of writing my dissertation).

I would never have survived without the companionship of my friends. Special thanks goes to Tikir, who has been a "dost", brother, and a mentor. I would like to thank my coffee shop/hiking/biking/dining buddies; Amogh, Ahmet and Zibi. I am truly indebted to Marisol, Ozlem, Elif, and Mevlude for helping me through tough times over the years and to my roommates Sveta, Federico, and Erin. I gratefully acknowledge my neighbor's orange cat, Phoenix, for being so fluffy and comforting. I owe sincere thankfulness to Ian for caring about me and keeping me company. Many thanks for all the memories.

Finally, I would like to thank my parents and my sister who are the most dear to me: Thank you for letting me travel halfway across the world to pursue my career.

Portions of this thesis are based on the papers which I have co-authored with others.

• Chapter 3, Chapter 4 and Chapter 6, in part, are a reprint of the material as it appears in International Conference on Supercomputing 2011 with the title "Mint: Realizing CUDA performance in 3D Stencil Methods with Annotated C" by Didem Unat, Xing Cai and Scott B. Baden. I was the primary investigator and author of this paper.

- Section 7.1 in Chapter 7 is based on the material as it partly appears in Computing Science and Engineering Journal 2012 with the title "Accelerating an Earthquake Simulation with a C- to-CUDA Translator" by Jun Zhou, Yifeng Cui, Xing Cai and Scott B. Baden. Section 7.2 in Chapter 7 is based on the material as it partly appears in Proceedings of the 4th Workshop on Emerging Applications and Many-core Architecture 2011, with the title "Auto-optimization of a Feature Selection Algorithm" by Han Suk Kim, Jurgen Schulze and Scott B. Baden. Section 7.3 in Chapter 7 is based on the material as it partly appears in proceedings of the 4th Workshop on Emerging Applications and Many-core Architecture 2011, with the title "Auto-optimization of a Feature Selection Algorithm" by Han Suk Kim, Jurgen Schulze and Scott B. Baden. Section 7.3 in Chapter 7 is based on the material as it partly appears in State of the Art in Scientific and Parallel Computing Workshop 2010 with the title "Optimizing the Aliev-Panfilov Model of Cardiac Excitation on Heterogeneous Systems" by Xing Cai and Scott B. Baden. I was the primary investigator and author of these three papers.

- Chapter 5, in part, is currently being prepared for submission for publication with Xing Cai and Scott B. Baden. I am the primary investigator and author of this material.

#### VITA

| 2006 | Bachelor of Science, Boğaziçi University, İstanbul        |

|------|-----------------------------------------------------------|

| 2009 | Master of Science, University of California, San Diego    |

| 2012 | Doctor of Philosophy, University of California, San Diego |

#### PUBLICATIONS

D. Unat, J. Zhou, Y. Cui, X. Cai, and S. B. Baden. "Accelerating an Earthquake Simulation with a C- to-CUDA Translator", *Computing in Science and Engineering Journal, Special Issue on Scientific Computing with GPUs*, 2012.

H. S. Kim, D. Unat, S. B. Baden, and J. P. Schulze. "Interactive Data-centric Viewpoint Selection", *Conference on Visualization and Data Analysis*, Burlingame, CA, 2012.

D.Unat, X.Cai, and S. Baden. "Mint: Realizing CUDA performance in 3D Stencil Methods with Annotated C", *International Conference on Supercomputing*, Tucson, AZ, 2011.

D. Unat, H. S. Kim, J. P. Schulze, and S. B. Baden. "Auto-optimization of a Feature Selection Algorithm", *Proceedings of the 4th Workshop on Emerging Applications and Many-core Architecture*, San Jose, CA 2011.

D. Unat, X. Cai, and S. Baden. "Optimizing the Aliev-Panfilov Model of Cardiac Excitation on Heterogeneous Systems", *Para 2010: State of the Art in Scientific and Parallel Computing*, Reykjavik, Iceland, 2010.

D. Unat, T. Hromadka III, and S. Baden. "An Adaptive Sub-Sampling Method for in-memory Compression of Scientific Data", *Data Compression Conference*, Snowbird, Utah, 2009.

#### ABSTRACT OF THE DISSERTATION

#### Domain-Specific Translator and Optimizer for Massive On-Chip Parallelism

by

Didem Unat

Doctor of Philosophy in Computer Science

University of California, San Diego, 2012

Professor Scott B. Baden, Chair

Future supercomputers will rely on massive on-chip parallelism that requires dramatic changes be made to node architecture. Node architecture will become more heterogeneous and hierarchical, with software-managed on-chip memory becoming more prevalent. To meet the performance expectations, application software will undergo extensive redesign. In response, support from programming models is crucial to help scientists adopt new technologies without requiring significant programming effort.

In this dissertation, we address the programming issues of a massively parallel single chip processor with a software-managed memory. We propose the Mint programming model and domain-specific compiler as a means of simplifying application development. Mint abstracts away the programmer's view of the hardware by providing a high-level interface to low-level architecture-specific optimizations. The Mint model requires modest recoding of the application and is based on a small number of compiler directives, which are sufficient to take advantage of massive parallelism.

We have implemented the Mint model on a concrete instance of a massively parallel single chip processor: the Nvidia GPU (Graphics Processing Unit). The Mint source-to-source translator accepts C source with Mint annotations and generates CUDA C. The translator includes a domain-specific optimizer targeting stencil methods. Stencil methods arise in image processing applications and in a wide range of partial differential equation solvers. The Mint optimizer performs data locality optimizations, and uses on-chip memory to reduce memory accesses, particularly useful for stencil methods.

We have demonstrated the effectiveness of Mint on a set of widely used stencil kernels and three real-world applications. The applications include an earthquake-induced seismic wave propagation code, an interest point detection algorithm for volume datasets and a model for signal propagation in cardiac tissue. In cases where hand-coded implementations are available, we have verified that Mint delivered competitive performance. Mint realizes around 80% of the performance of the hand-optimized CUDA implementations of the kernels and applications on the Tesla C1060 and C2050 GPUs. By facilitating the management of parallelism and the memory hierarchy on the chip at a high-level, Mint enables computational scientists to accelerate their software development time. Furthermore, by performing domain-specific optimizations, Mint delivers high performance for stencil methods.

# Chapter 1

# Introduction

Within the next decade, it is hypothesized that High Performance Computing systems will contain exascale computers (10<sup>18</sup> operations/second) operating with a power budget of no more than 20 MW [BBC<sup>+</sup>08]. This power constraint will dictate drastic changes in architectural design. In order to achieve the exascale power and performance goals, it is projected that the biggest architectural change will occur within the node, rather than across nodes [SDM11]. In particular, a node architecture will become more heterogeneous with specialized computing units and will contain unconventional memory subsystems with incoherent caches and software-managed memory. We have already started seeing concrete instances of such node design in current supercomputers that combine a general-purpose processor with a special-purpose massively parallel processor such as Graphics Processing Units (GPUs).

The performance benefits of the heterogeneous architectural design come at the expense of software development time because they confound the application programmer with tradeoffs. In order to take advantage of the architecture, the programmer has to understand the subtleties of heterogeneity in compute resources and the partially exposed memory hierarchy, resulting in significant implications for programming. Unlike conventional cache architectures, a softwaremanaged memory requires the programmer to adopt unfamiliar programming style to explicitly orchestrate the data decomposition, allocation and movement in the software-level. Given the anticipated need for remapping applications to exascale systems, support from programming models is crucial.

This thesis addresses the programming issues of a massively parallel single chip processor with a software-managed memory and proposes a programming model, called Mint. The model abstracts the machine view from the programmer, and facilitates the mapping from the high-level interface to low-level architecture-specific optimizations. The model is based on compiler directives, requiring modest recoding. Mint employs just five directives to annotate input programs, and we demonstrated that these are sufficient to accelerate applications.

We have implemented the Mint programming model for a system using the Nvidia GPUs as the massively parallel single chip processor. The Mint source-to-source translator for GPUs accepts traditional C source with Mint annotations and generates optimized CUDA C. The translator parallelizes loop-nests, manages data movement and threads. It includes a domain-specific optimizer that targets stencil methods, an important problem domain with a wide range of applications such as partial differential equation solvers. By restricting the compiler optimizations to a certain problem domain, we can more easily allow guided and specialized performance optimizations. The Mint optimizer performs data locality optimizations and uses on-chip memory (e.g registers and shared memory) to reduce memory accesses, particularly useful for stencil methods. Thus, the optimizer delivers higher performance for stencil methods compared to general purpose compilers [LME09, Wol10a, UCB11].

The challenge when designing a custom programming interface for an application domain is to come up with a small set of parameters that significantly affect performance. We designed Mint in a way that these parameters are administered by *clauses* and *compiler options*, which are controlled by the programmer at a high level. The principal effort for the Mint programmer is to identify time-consuming loop nests and annotate them with tunable clauses. These clauses govern data and workload decomposition across threads and enable non-experts to tune the code without entailing disruptive reprogramming. In addition, the compiler options give the programmer the flexibility to explore different optimizations applied to the same program, saving significant programming effort. Even though our compiler targets the Nvidia GPUs, the programming model can be implemented for other massively parallel architectures that have heterogeneous compute resources and software-managed memory hierarchy. The optimization strategies of stencil methods are essentially the same but the implementation of the clauses and compiler options exhibits differences based on the target architecture.

In this thesis, we demonstrate the effectiveness of the Mint model and its compiler for a set of widely used stencil kernels. The representative kernels share a similar communication and computation pattern with large applications, but are less complex to analyze. Mint realized 80% of the performance obtained from aggressively hand-optimized CUDA on the 200- and 400-series of Nvidia GPUs. We believe this performance gap is reasonable in light of Mint's reduced learning curve compared with extensive changes needed to port the code by hand.

Mint is not only useful for simple stencil kernels, but also in enabling acceleration of whole applications. The first application that we accelerated by using Mint is the AWP-ODC, an earthquake-induced seismic wave propagation code. The resultant Mint-generated code realized about 80% of the performance of the hand-coded CUDA. The second application is a computer visualization algorithm which detects features in volume datasets. Mint enabled the algorithm to realize real time performance in 3D images, which previously had been intractable on conventional hardware. Lastly, we studied the Aliev-Panfilov system which models signal propagation in cardiac tissue. For the cardiac simulation, Mint achieved 70.4% and 83.2% of the performance of the hand-coded CUDA in single and double precision arithmetic, respectively.

#### **Thesis Contributions**

- We have introduced the Mint programming model, an annotation-based interface to facilitate programing on the massively parallel multicore. The model employs only five directives and requires modest amount of programming effort to accelerate applications. Mint programming model facilitates programming for computational scientists, so that they can smoothly adopt technologies that rely on massive parallelism on a chip.

- We have implemented a source-to-source translator and optimizer which implements the Mint model for the GPU-based systems. The translator relieves the programmer of a variety of tedious tasks such as managing device memory and constructing device kernels. The domain-specific optimizer detects the stencil structure in the computation and performs data locality optimizations using the on-chip memory resources.

- We have demonstrated the effectiveness of the Mint model and the compiler on commonly used stencil kernels as well as real-life applications. Mint generated codes realize about 80% of the performance of hand-coded CUDA.

- Finally, we have discussed the applicability of Mint to future architectures. Future architectures may or may not have GPUs as the building blocks but will have a high degree of on-chip parallelism and software-managed memory hierarchy. Mint can be tailored to address programmability issues of future systems.

#### **Thesis Outline**

• Chapter 2 provides motivation and background for the thesis. It describes the trend in computer architecture and processor technologies, and also discusses the characteristics

of scientific applications in general and stencil-based applications in depth. The chapter presents available programming models, languages and interfaces for the current systems.

- Chapter 3 introduces the Mint programming model. Before introducing the interface of the model, we discuss the underlying hardware assumptions. The chapter continues with the Mint execution and memory model. Next, it presents the details of each directive and provides a simple example to illustrate the purpose of the directives.

- Chapter 4 discusses the source-to-source translator that implements the Mint model. The translator has two main stages. This chapter presents the first stage, *Baseline Translator*, which transforms C source code with Mint annotations to unoptimized CUDA, generating both device and host codes.

- Chapter 5 discusses the second stage of the translator, which is the domain-specific optimizer targeting stencil methods. This chapter provides the details about the stencil analysis and on-chip memory optimizations to improve data locality. It gives several generated-code examples to demonstrate the impact of the compiler optimizations. To let the reader better comprehend the compiler optimizations, the chapter begins with an overview of the general optimization strategies for stencil methods.

- Chapter 6 demonstrates the effectiveness of the Mint translator by studying a set of widely used stencil kernels in two and three dimensions. The chapter first provides a discussion on the computer testbeds and software used throughout the thesis, then presents the performance results for commonly used stencil kernels.

- Chapter 7 presents case studies that validate the effectiveness of Mint on real-world applications coming from different problem domains. The first application is a cutting-edge seismic modeling application. The second comes from computer vision, the Harris interest point detection algorithm. The third study is a 2D Aliev-Panfilov model that simulates the propagation of electrical signals in the cardiac cells. After presenting background for each application, the chapter discusses the Mint implementation and the performance of the generated code along with performance tuning efforts.

- Chapter 8 discusses the limitations of the Mint model, future directions and concludes the dissertation.

# Chapter 2

# **Motivation and Background**

This chapter discusses why massive parallelism on a chip is inevitable and why software tools are needed to program them. It provides the background for the architectural trends and emerging massively parallel chip technologies in High Performance Computing in Section 2.1. We give special attention to Graphics Processing Units (GPUs), which provide an abundance of on-chip parallelism and have the potential to become the building blocks of an exascale system. Section 2.2 describes the common patterns in scientific applications with an emphasis on stencil computation. Section 2.3 presents programming environments in High Performance Computing systems such as libraries, languages, and programming models in the context of multicore processors.

#### 2.1 Trends in Computer Architecture

Gordon Moore stated that the number of transistors per integrated circuit will double every 18-24 months [Moo00]. Even though Moore initially predicted that the trend would continue for at least 10 years, his prediction guided semiconductor technology for almost half a century until chip vendors hit the "power wall" [Mud01]. The power consumption of processors exponentially increased, as processor designers kept increasing the microprocessor clock speeds and added more instruction-level parallelism (ILP) through pipelining, out-of-order execution and superscalar issue [OHL07, KAB<sup>+</sup>03]. Consequently, at the beginning of the 21st century, chip designers have started looking for new ways to improve processor performance. They switched to a new design paradigm, which integrates two or more processing cores on a single computing component. The chip area that used to be covered by a single large processor is now filled by a collection of smaller processors. The new technology, called *multicore*<sup>1</sup>, quickly became prevalent. According to the Top500 supercomputer rankings [Top], today more than 80% of the supercomputers rely on multicore processors.

The composition, purpose, and number of cores in multicore architectures show great variety. It is difficult to create a taxonomy because family members have distinct design features. We divide the multicore architectures into two categories based on their design philosophies even though the two categories may converge over time. The first is the general purpose multicore processor that is capable of running a wide variety of applications including the operating system. We will refer to this group as *general-purpose multicore* processors. Members of this group employ relatively complex CPUs, focus on single thread performance, and utilize ILP to some extent, compared to the second category, *massively parallel single chip* processors. A massively parallel chip consists of a relatively large number of simple and low power cores, tailored towards throughput computing with less focus on single-thread performance. In the next section we briefly go over the general-purpose multicore architectures and then introduce massively parallel single chip processors.

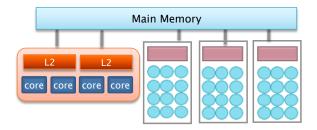

**Figure 2.1:** Abstract machine model of a compute node containing two general-purpose multicore chips on two sockets, each with 6 cores.

<sup>&</sup>lt;sup>1</sup> In this thesis, we use the term "multicore", to refer to cores manufactured on the same integrated circuit die.

#### 2.1.1 General-Purpose Multicore Processors

General-purpose multicores provide fast response time to a single thread. They are capable of running a wide variety of applications including operating systems and databases. Today, most high-end multicores are limited up to 10 cores (about 12 cores on a 2 die multichip module). Fig 2.1 shows an abstract machine model of a node containing two multicore chips, each with 6 cores. In a typical multicore chip, cores have private L1 and L2 caches but share L3 cache with the other cores on the same chip. Caches are coherent though it is unclear if future designs will remain cache-coherent because of the significant overhead [BBC<sup>+</sup>08]. Common network topologies for inter-core communication include crossbar, bus, and ring. The node typically implements NUMA architecture (Non-Uniform Memory Access), which maps different memory banks to different chips. In such a design, cores may have non-uniform access latencies to different regions of memory.

Figure 2.2: Two examples for 45 nm process technology

Fig 2.2 shows two examples of multicore processors available today. The first one is a hexa-core processor, code-named Istanbul from the AMD Opteron processor family. The 45 nm chip area includes 6MB shared L3 cache, 64KB private L1 and 512KB private L2 caches. The clock rate ranges from 2.2 to 2.8 GHz. This processor powers the Jaguar machine installed at Oak Ridge National Laboratory, which currently ranks 3rd in the Top500 list. The second chip (on the right) is a quad-core microprocessor from Intel. It is a Nehalem-based Xeon with 45 nm process technology, operating at 2.4-3.06 GHz. There is a 64KB private L1, 256KB private L2

and 8MB shared L3. Intel supports hyper-threading to improve parallelization on the chip by replicating certain parts of the processor [TEE<sup>+</sup>97]. The operating system can virtualize each physical core as two logical cores and schedule two processes simultaneously. For example, a chip containing four cores can scale to eight threads.

#### 2.1.2 Massively Parallel Single Chip Processors

Massively parallel single chips provide a significant performance boost in node performance and can be used in supercomputers. Typically each core on a massively parallel chip lacks some of the ILP components but has a large number of ALUs (arithmetic logic units) compared to a CPU core. This minimizes the control complexity and the area on the chip, improving power consumption [CMHM10]. However, today's massively parallel single chip processors are specialized for certain application domains because they restrict the types of computation that can be performed. Unlike CPUs, massively parallel chips execute many threads concurrently but each thread executes very slowly. As a result, they may be attached to a general-purpose CPU which runs an operating system and serves as the controller or they might be general-purpose but not as powerful in single thread performance as a general-purpose multicore.

Unfortunately, having more ALUs does not translate into a proportional increase in performance. Today's chips are able to perform arithmetic operations a lot faster than we can feed them with data. This creates a major obstacle to performance also known as the "memory wall" [WM95]. Massively parallel single chips address this problem by introducing a large register file and a software-controlled memory hierarchy together with high intra-chip bandwidth. Managing the on-chip memory, however, comes at the expense of added programming overhead.

Some of the massively parallel single chip processors available today are Tilera [Til, TKM<sup>+</sup>02], Clearspeed [Cle], Tensilica [KDS<sup>+</sup>11, DGM<sup>+</sup>10], FPGAs [CA07] and GPUs. Each of these is designed with its own objective and targeting a different market segment. We look into GPUs in depth because of their wide adoption in scientific computing. According to the Top500 supercomputing rankings released in November 2011 [Top], three out of the five fastest supercomputers contain GPUs as the horsepower.

#### 2.1.3 Graphics Processing Units

A **Graphics Processing Unit** (GPU) is specialized for *stream processing* [KDK<sup>+</sup>01] in which computations become a sequences of *kernels*, functions that run under the single instruction, multiple threads model. This highly data parallel structure of GPUs attracted interest from the scientific computing community and started the era of *GPGPU –General Purpose Computing on GPUs* [DLD<sup>+</sup>03, FQKYS04]. GPUs provide significant performance improvement not only in terms of arithmetic throughput but also in memory bandwidth for data parallel applications.

GPUs are not general-purpose processors. They require a general-purpose CPU as a *host*, to run an operating system and serve as a controller. Even though future systems may treat data motion differently, in current GPU-based systems, the host and device have physically distinct memories. The programmer controls the data motion between the two at the software level. Integrated GPUs are available in the market but they are usually far less powerful than those on a dedicated card.

Figure 2.3: Abstract machine model of a GPU device connected to a host processor

Fig. 2.3 abstracts the computing unit and memory hierarchy in a GPU. A GPU device comprises groups of *vector cores*, each containing multiple *stream cores*. A vector core is capable of managing thousands of concurrent hardware threads. The stream cores, each of which is equipped with arithmetic logic units, are responsible for executing kernels. A stream core operates on an independent data stream but executes the same instruction with the other stream cores in the same vector core. A GPU kernel runs a virtualized set of scalar threads that are organized as a group of threads. The hardware dynamically assigns each *thread group* to a single vector core. Each thread in a thread group executes on a single stream core. GPUs further break down the thread group into subgroups. A subgroup executes the same instruction at the same time.

The hierarchy of computing units is reflected in the memory hierarchy as well. There is an off-chip *global device memory*, which has a high access latency and is accessible by all threads. There are two types of low latency on-chip memory; *private* and *shared memory*. The private memory is typically a set of registers, which is specific to a thread, and not visible to

Figure 2.4: Nvidia GPU architecture

other threads. The shared memory is software and/or hardware-managed memory that is specific to a thread group, and accessible only by the threads belonging to that thread group.

The device can overlap computation with transfers to and from global memory. This is achieved by maximizing device *occupancy*, that is, the ratio of active threads to the maximum number of threads that a vector core supports. The common wisdom is that with sufficient occupancy, the processor effectively pipelines global memory accesses thereby masking their cost. The scarcity of on-chip memory constrains this goal, and the exact amount of realizable parallelism depends on the specific storage requirements of the kernel. The architecture requires the programmer find a good balance between the number of threads and their dataset size. A large number of threads have more potential to hide memory latency. But more threads mean fewer resources per thread. In addition to hiding transfer latency, it is important to avoid *thread divergence*. Threads within the same thread subgroup taking different branches cannot be executed in parallel on a vector core. They will be serialized.

The two largest dedicated graphics card designers, AMD and Nvidia, provide solutions for GPU-based High Performance Computing systems. Although both vendors have a similar device design, each vendor uses its own terminology for the computing and memory units. AMD refers to a vector core as a *compute unit* [AMD11] and Nvidia refers to it as a *streaming multi-processor* [NBGS08]. Different GPUs have different numbers of vector cores as well as different

number of stream cores in a vector core. For example, the ATI Radeon HD 5870 GPU has 20 vector cores, each with 16 stream cores. The Nvidia Tesla 2050 has 14 vector cores, each with 32 stream cores.

The private memory on both vendors' GPUs consists of a large register file. The AMD GPUs initially offered only L1 cache as the shared memory, which is shared by a thread group. AMD Evergreen GPUs include software-controlled scratchpad memory, called *local data store* [AMD11]. Nvidia's shared memory, called *shared memory*, is managed at the software level. In addition to software-managed on-chip storage, in its latest GPUs, Nvidia provides L1 cache on a vector core. Thread-private data that does not fit into registers is placed in the global memory which is three orders of magnitude slower to access. This global memory region, for lack of a better term, is called *local memory* by Nvidia. Fig. 2.4 shows the architectural overview of an Nvidia GPU.

The two vendors differ in the naming of the thread and thread groups although the thread hierarchy is essentially the same. AMD refers to a thread as a *work item* and thread group as a *work group*. The work-items that are executed together, or the subgroup, is called a *wavefront*. Nvidia refers to a thread as *CUDA thread*, (or simply thread) and thread group as a *thread block*. The collection of CUDA threads, or the subgroup, that execute the same instruction at the same time is called a *warp*. The latest generation of Nvidia GPUs provides two warp schedulers, which are capable of issuing two different instructions to the same vector core.

In this thesis we perform our experiments on the Nvidia GPUs and will adopt the Nvidia terminology for the computing and memory units. We leave the detailed description about the GPU testbeds employed in our performance results to Chapter 6.

### 2.2 Application Characteristics

Although it may seem that applications have various distinct characteristics, the underlying computational methods exhibit common patterns of computation and data movement. Phil Colella [Col04] identified seven patterns, called "Seven Dwarfs", in scientific computing. The Berkeley View [ABC<sup>+</sup>06] extended the 7 dwarfs to 13 "motifs" to characterize other patterns in and beyond scientific computing. Researchers have been studying the optimizations of the dwarfs over several years because the dwarfs are less complex to analyze than a whole application but representative enough to exhibit the same dependency pattern. Another merit of the classification is that these dwarfs can be used to benchmark computer architectures, programming models, and tools designed for scientific computing.

**Figure 2.5:** Comparison between Core i7 and GTX 280 performance on various applications. The data was collected from Victor Lee et. al [LKC<sup>+</sup>10].