# UC Santa Cruz

**UC Santa Cruz Electronic Theses and Dissertations**

## Title

Software-Hardware Co-Defined Network Switch (SHADES) for a Label Switching Protocol

**Permalink** https://escholarship.org/uc/item/3rq3v7d4

**Author** Karadeniz, Turhan

Publication Date 2015

## **Copyright Information**

This work is made available under the terms of a Creative Commons Attribution License, available at <a href="https://creativecommons.org/licenses/by/4.0/">https://creativecommons.org/licenses/by/4.0/</a>

Peer reviewed|Thesis/dissertation

## UNIVERSITY OF CALIFORNIA SANTA CRUZ

### SOFTWARE-HARDWARE CO-DEFINED NETWORK SWITCH (SHADES) FOR A LABEL SWITCHING PROTOCOL

A dissertation submitted in partial satisfaction of the requirements for the degree of

### DOCTOR OF PHILOSOPHY

$\mathrm{in}$

#### COMPUTER ENGINEERING

by

#### **Turhan Karadeniz**

September 2015

The Dissertation of Turhan Karadeniz is approved:

Prof. J.J. Garcia-Luna-Aceves, Chair

Prof. Katia Obraczka

Prof. Brad R. Smith

Tyrus Miller Vice Provost and Dean of Graduate Studies Copyright (C) by

Turhan Karadeniz

2015

# Table of Contents

| Li       | st of | Figure  | es                                     | vi   |

|----------|-------|---------|----------------------------------------|------|

| Li       | st of | Tables  | 5                                      | viii |

| Li       | st of | Algor   | ithms                                  | ix   |

| A        | bstra | ct      |                                        | xi   |

| D        | edica | tion    |                                        | xiii |

| A        | cknov | wledgn  | nents                                  | xiv  |

| 1        | Intr  | oducti  | on                                     | 1    |

| <b>2</b> | Mu    | lti-Roc | ot Interval Routing (MINT)             | 5    |

|          | 2.1   | Introd  | uction                                 | 6    |

|          | 2.2   | Relate  | ed Work                                | 8    |

|          | 2.3   | The A   | rchitecture & Algorithm                | 10   |

|          |       | 2.3.1   | Centralized Controller                 | 11   |

|          |       | 2.3.2   | Pruning of the BFS Trees               | 13   |

|          |       | 2.3.3   | DFS Ordering & Labeling                | 19   |

|          |       | 2.3.4   | Computing the Intervals                | 21   |

|          |       | 2.3.5   | Interval Table Minimization            | 21   |

|          |       | 2.3.6   | Data Plane Forwarding                  | 23   |

|          | 2.4   | Simula  | ation Results                          | 24   |

|          |       | 2.4.1   | Efficiency of BFS Pruning/DFS Labeling | 24   |

|          |       | 2.4.2   | Interval Table Compactness             | 26   |

|          |       | 2.4.3   | Interval Distribution per Root         | 28   |

|          |       | 2.4.4   | Performance: Delivery Ratio & Latency  | 29   |

|          | 2.5   | Conclu  | usion & Future Work                    | 29   |

| 3        | Soft | tware-Hardware Co-Defined Network Switch (SHADES) for a         | 1         |

|----------|------|-----------------------------------------------------------------|-----------|

|          | Lab  | oel Switching Protocol                                          | 33        |

|          | 3.1  | Introduction & Related Work                                     | 34        |

|          | 3.2  | Implementation                                                  | 37        |

|          |      | 3.2.1 Label Switched Routing                                    | 37        |

|          |      | 3.2.2 SHADES Top-Level System Architecture                      | 39        |

|          | 3.3  | Performance Results                                             | 42        |

|          |      | 3.3.1 Point-to-Point Round-Trip Delay Time                      | 42        |

|          | 3.4  | Conclusion                                                      | 45        |

| 4        | Har  | rdware Design and Implementation of a Network-on-Chip Based     | l         |

|          | Loa  | ad Balancing Switch Fabric                                      | <b>47</b> |

|          | 4.1  | Introduction                                                    | 48        |

|          | 4.2  | Related Work                                                    | 51        |

|          |      | 4.2.1 The Switch Fabric                                         | 51        |

|          |      | 4.2.2 Network-on-Chip $\ldots$                                  | 54        |

|          |      | 4.2.3 Network-on-Chip Based Switch Fabric                       | 56        |

|          | 4.3  | Hardware Design                                                 | 57        |

|          |      | 4.3.1 UDN and MDN Architectures & Algorithms                    | 57        |

|          |      | 4.3.2 Input Buffers (FIFOs)                                     | 60        |

|          |      | 4.3.3 Network Interface (NI)                                    | 61        |

|          |      | 4.3.4 UDN 3 I/O MR                                              | 61        |

|          |      | 4.3.5 MDN 4 I/O MR                                              | 62        |

|          |      | 4.3.6 Modulo XY Routing Algorithm                               | 63        |

|          |      | 4.3.7 Scheduling Algorithm                                      | 65        |

|          | 4.4  | Simulations, Execution & Results                                | 66        |

|          |      | 4.4.1 RTL Synthesis                                             | 66        |

|          |      | 4.4.2 On-Chip Packet Switching Latency                          | 69        |

|          |      | 4.4.3 Simulation                                                | 72        |

|          | 4.5  | Conclusion                                                      | 73        |

| <b>5</b> |      | New Approach to Switch Fabrics based on Mini-Router Grids       |           |

|          | and  | l Output Queueing                                               | 75        |

|          | 5.1  | Introduction                                                    | 76        |

|          | 5.2  | Related Work                                                    | 77        |

|          | 5.3  | MRG Based Switch Fabric Architecture                            | 81        |

|          |      | 5.3.1 Architecture Design Parameters                            | 81        |

|          |      | 5.3.2 WUDN 3 I/O Port Mini-Router                               | 84        |

|          |      | 5.3.3 Memory Organization for Output Queues                     | 84        |

|          |      | 5.3.4 Modulo XY Routing in the Mini-Router Grid                 | 85        |

|          | 5.4  | Analytical Model                                                | 89        |

|          |      | 5.4.1 Analysis of the Modulo Routing Algorithm                  | 91        |

|          |      | 5.4.2 Detailed Characterization of Traffic Distribution for MRs | 94        |

|    |       | 5.4.3   | Incoming Traffic Rate and Stability                   | 95  |

|----|-------|---------|-------------------------------------------------------|-----|

|    |       | 5.4.4   | State Distribution and Optimal Queue Size             | 96  |

|    | 5.5   | The M   | Todel & Simulations                                   | 98  |

|    |       | 5.5.1   | RTL & Functional Models                               | 98  |

|    |       | 5.5.2   | Simulation Parameters & Performance Metrics           | 99  |

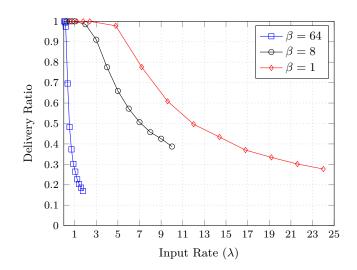

|    |       | 5.5.3   | Delivery Ratio under Variable Traffic Rates           | 99  |

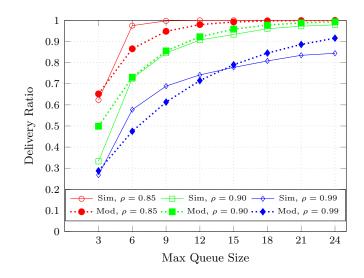

|    |       | 5.5.4   | Delivery Ratio as a Function of Queue Size            | 101 |

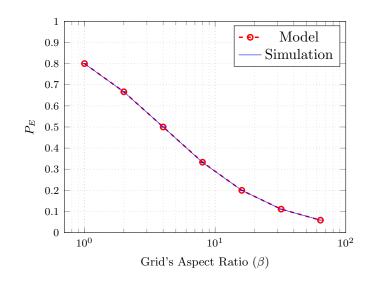

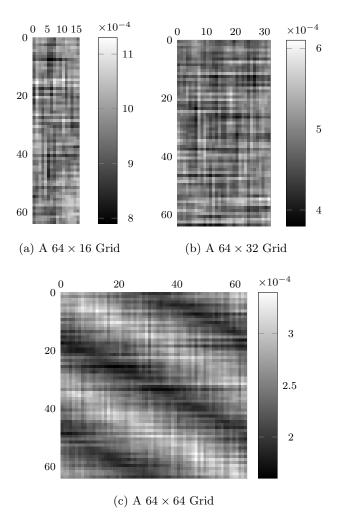

|    |       | 5.5.5   | Impact of Grid's Layout on Local Traffic Distribution | 101 |

|    |       | 5.5.6   | Global Distribution of Traffic Across the Grid        | 103 |

|    | 5.6   | Placen  | nent Considerations                                   | 105 |

|    | 5.7   | Compa   | arison & Discussion                                   | 106 |

|    | 5.8   | Conclu  | sion                                                  | 108 |

| 6  | Con   | clusior | 1                                                     | 109 |

| Bi | bliog | raphy   |                                                       | 115 |

# List of Figures

| 2.1  | Software Defined Network Topology                                             | 12 |

|------|-------------------------------------------------------------------------------|----|

| 2.2  | Uniformly distributed random network, divided in quadrants                    | 13 |

| 2.3  | Random uniform graph G                                                        | 14 |

| 2.4  | Tree $T$ , pruned from root node $r$ , with nodes $u, v, c$ and node clusters |    |

|      | U, V', V'' and $D$                                                            | 17 |

| 2.5  | Corner node as root. Heatmap shows empirical $\mu()$                          | 18 |

| 2.6  | Central node as root. Heatmap shows empirical $\mu()$                         | 18 |

| 2.7  | Node D is elected as corner 1                                                 | 20 |

| 2.8  | Node B is elected as corner 2                                                 | 20 |

| 2.9  | Node I is elected as corner 3                                                 | 20 |

| 2.10 | Node M is elected as corner 4                                                 | 20 |

| 2.11 | Intervals assigned to the ports of nodes B & G in C1 tree                     | 23 |

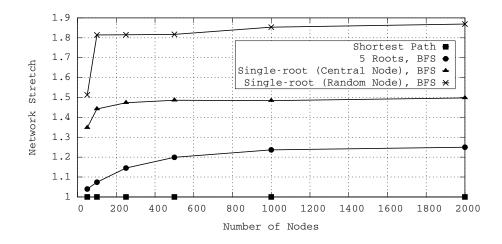

| 2.12 | Comparison of various interval labeling schemes                               | 25 |

| 2.13 | Comparison of BFS and DFS pruning                                             | 26 |

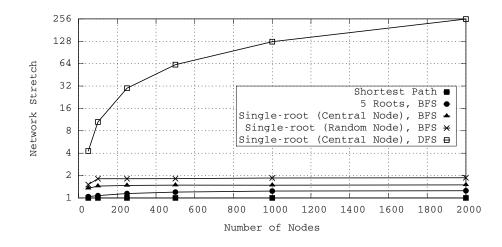

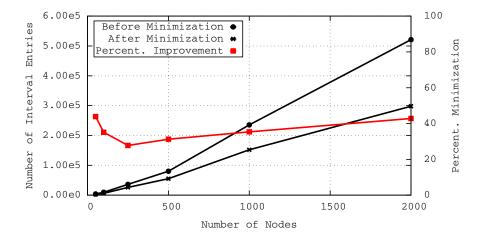

| 2.14 | Total number of interval entries before and after minimization                | 27 |

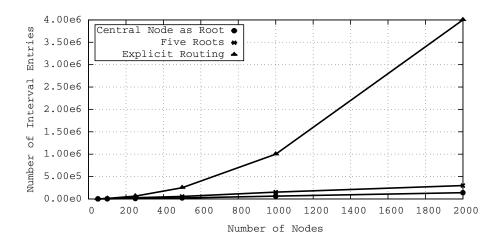

| 2.15 | Comparison of MINT vs. explicit routing algorithms                            | 28 |

| 2.16 | Percentage Distribution of Intervals over Roots                               | 28 |

| 2.17 | Performance Evaluation, Delivery Ratio                                        | 30 |

| 2.18 | Performance Evaluation, Latency (seconds)                                     | 31 |

| 3.1  | Comparison of Traditional Forwarding and SHADES                               | 38 |

| 3.2  | $Node_A$ Flow Table for HW Forwarding                                         | 39 |

| 3.3  | Hardware-Software Co-defined Network Switch (SHADES), Abstract                | 40 |

| 3.4  | Hardware-Software Co-defined Network Switch (SHADES), Imple-                  |    |

|      | mentation for Altera FPGA                                                     | 41 |

| 3.5  | Comparing RTT for SW and HW Forwarding                                        | 44 |

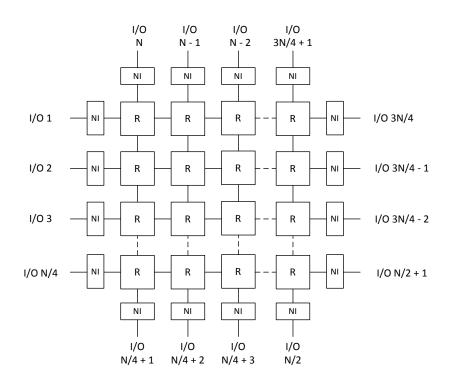

| 4.1  | NOC Switch Fabric                                                             | 54 |

| 4.2  | Buffered Crossbar and NOC Based Crossbar Switch Architectures .               | 56 |

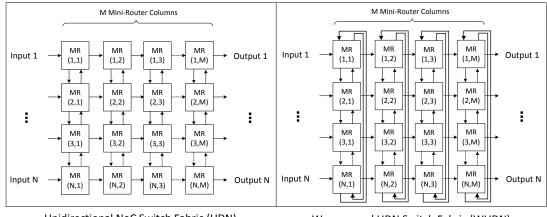

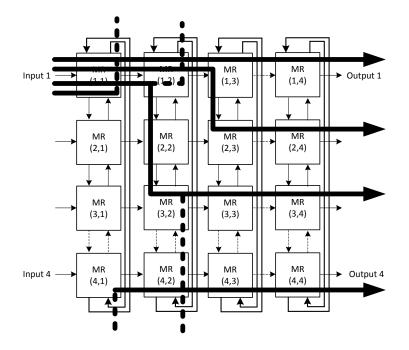

| 4.3  | UDN Architecture                                                              | 58 |

| 4.4  | MDN Architecture                                                              | 59 |

|      |                                                                               |    |

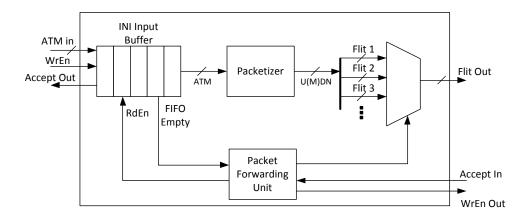

| 4.5  | Input Network Interface Block Diagram                                | 62  |

|------|----------------------------------------------------------------------|-----|

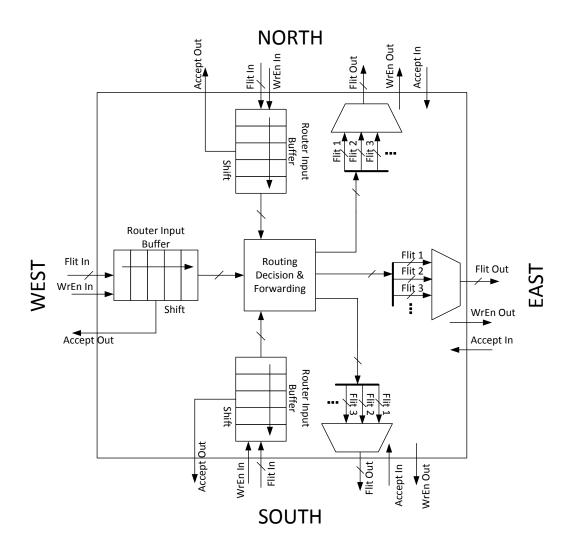

| 4.6  | 3 I/O Port UDN Router, Top-Level Block Diagram                       | 63  |

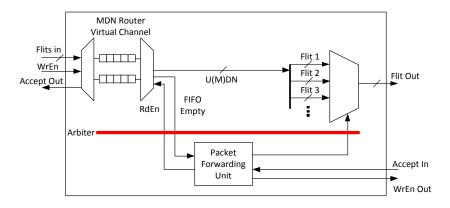

| 4.7  | Virtual Channel for an Input Ports of MDN Router                     | 64  |

| 4.8  | XY Modulo Routing                                                    | 64  |

| 4.9  | Bipartite Graph Matching Problem in UDN                              | 65  |

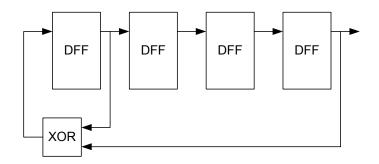

| 4.10 | Linear feedback shift registers (LFSR) for pseudo-random packet gen- |     |

|      | eration                                                              | 70  |

| 4.11 | Block diagram for the run-time on-chip testing environment. $\ldots$ | 70  |

| 5.1  | UDN / WUDN Architectures                                             | 79  |

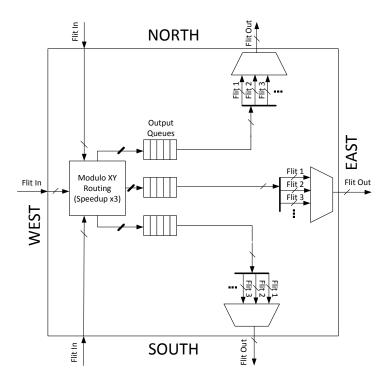

| 5.2  | 3 I/O Port WUDN MR, Top-Level Block Diagram                          | 83  |

| 5.3  | Modulo XY Routing for WUDN                                           | 85  |

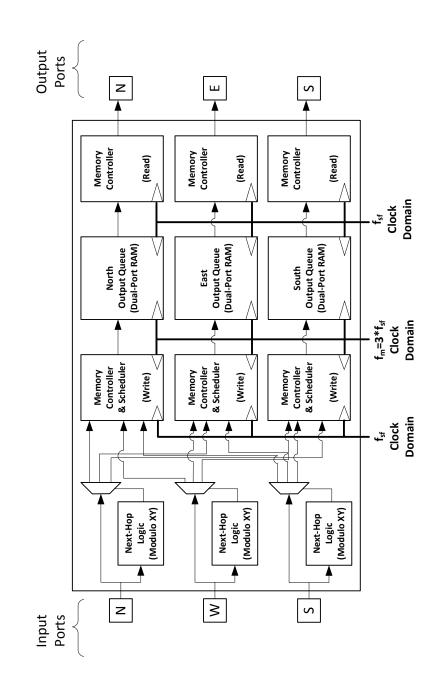

| 5.4  | Memory Organization for Output Queues                                | 90  |

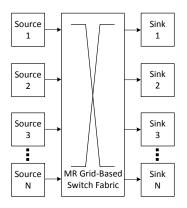

| 5.5  | Concurrent Source & Sink Modules, connected to the Switch Fabric     | 98  |

| 5.6  | Delivery Ratio Vs. Input Rate                                        | 100 |

| 5.7  | Delivery Ratio vs. Max Queue Size                                    | 102 |

| 5.8  | Probability of sending on east vs. grid's aspect ratio               | 103 |

| 5.9  | Heatmaps illustrating uniform distribution of the traffic across     |     |

|      | the grid                                                             | 104 |

| 5.10 | Placement of WUDN                                                    | 106 |

| 5.11 | UDN, Non-uniform Traffic                                             | 107 |

# List of Tables

| 2.1 | Total number of interval entries.                | 27  |

|-----|--------------------------------------------------|-----|

| 4.1 | Synthesis Results for individual UDN/MDN Modules | 67  |

| 4.2 | Comparison of Synthesis Results, I               | 68  |

| 4.3 | Comparison of Synthesis Results, II              | 69  |

| 6.1 | Contributions, Summary                           | 113 |

# List of Algorithms

| 1 | Algorithm for computing the intervals    | 22 |

|---|------------------------------------------|----|

| 2 | Modulo XY Algorithm for WUDN             | 86 |

| 2 | Modulo XY Algorithm for WUDN (continued) | 87 |

| 2 | Modulo XY Algorithm for WUDN (continued) | 88 |

#### Abstract

Software-Hardware Co-Defined Network Switch

#### (SHADES)

#### for a Label Switching Protocol

by

#### Turhan Karadeniz

The network switch is one of the core components of computer communications, functioning as the interconnect among ever increasing number of nodes and a variety of networks. Whether it is used in data centers for connecting large numbers of nodes with high storage and computational capacities, or in the Internet backbone as a core router carrying vast quantity of information among its users, or in medium to large sized local area networks including educational campuses and companies, the switches require ever increasing design needs for scalability, high delivery ratios, low latencies, and quality-of-service (QoS) guarantees.

We believe that switch design should be evaluated as a holistic aspect of network protocol design, since many metrics in protocol design and switch design are closely correlated. Moreover, designing a switch requires the integration of hardware and software, because different functionalities of the switch can be implemented in hardware, software or both depending on different design considerations.

Rapid increase in Software Defined Networks (SDN) related research denotes that the approach of abstracting the data plane from the control plane, thus achieving higher flexibility and architectural simplicity, accounts for a notable research problem. Furthermore, label switching based routing algorithms enable the forwarding layer to be implemented at hardware and thus inflict less per-hop latency. Introducing a hardware component into network protocol design might initially seem to combine two orthogonal design components, however the outcome is an architecture that achieves multiple levels of abstraction, flexibility, simplicity, scalability and high performance at once.

In this thesis, we propose a novel architecture with an emphasis on hardwaresoftware co-design paradigm, resulting in a scalable, flexible and high performance switch. We show that our design can be fully implemented on a Field-Programmable Gate Array (FPGA) based platform. Our system demonstrates an attempt to improve SDN, by taking the hardware component into account in the design flow, resulting in our Software-HArdware co-Defined nEtwork Switch (SHADES) for a label switched routing protocol, delivering load balancing, low latencies, and high delivery ratios. To my sunshine Kübra, my extraordinary parents Figen & Hasan, my amazing cousins Irem & Melis, my niece Pera,

and my magnificent grandmothers Tulay & Birsen.

#### Acknowledgments

First of all, I would like to thank my advisor Prof. J.J. Garcia-Luna-Aceves for his support, encouragement and guidance. His wisdom provided me a safe path on which to walk, and his amazing sense of humor allowed me to have the high energy and morale to finish what I started.

I would like to thank Prof. Katia Obraczka and Prof. Brad Smith for being on my defense committee, and for all their valuable feedback.

I have received all sorts of support from the most special people that surrounded me in the period of 5 years, Yusuf Goren, Kenan Sharpe, Serdar Sali, Doruk Sart, Ashok Masilamani, Ali Dabirmoghaddam, Emre Can Kara, Zeynep Mulayim, Dila Beksac, and Renato D'Orfani, who have always been there for me.

My colleagues and friends from CCRG whom I had the pleasure to meet and work with: Spencer, James, Sam, Alison, Yali, Maziar, Duy, Rumi, Ramesh, Ehsan and Nitish. They always came up with the best ideas and offered their help when I needed it the most.

Some mentors and colleagues that I had the pleasure to work with in the past include Nurdan Ugural, Nino Carella, Lou Ungemach Panetta, Cengiz Agalar, Deniz Baysal, Ahmet Demirelli, Ilker Hamzaoglu, Erkay Savas, Serkan Sahin, Georgi Gardadjiev, Onur Can Ulusel, Aydin Aysu, Ece Ercan, Berker Agir, Anil Usumezbas, Stavros Tzilis, Roi Uziel, and Kan Boonyanit. Thank you all!

Last but not least, I want to thank Emily Gregg, Tracie Tucker, Adrienne Bergenfeld, Carol Mullane, Jolinda Singleton and Arielle M.S. Freitas. The amount of patience you had with me is out of this world!

Probably there is a guardian angel as well, of some sorts. Thanks buddy!

# Chapter 1

# Introduction

In computer networks, the communication between nodes is realized by a broad and diverse body of electronic and optical technology. The network switch is one of the core components of computer communications, functioning as the interconnect among ever increasing number of nodes and in between a variety of networks of various sizes and properties. Whether it is used in data centers for connecting large numbers of nodes with high storage and computational capacities, as Internet backbone core routers carrying vast quantity of information among its users, or in medium to large sized local area networks including educational campuses or companies, the switches require ever increasing design needs for scalability, flexibility, high delivery ratios, low latencies, and load balancing properties.

We believe that switch design should be evaluated as a holistic aspect of network protocol design, since many parameters in protocol and switch design are closely correlated. Moreover, designing a switch requires the integration of hardware and software, because different functionalities of the switch can be implemented in hardware, software or in both depending on different design considerations. The design of a smart switch capable of handling novel routing protocols as well as the TCP/IP stacks, while still delivering high performance, is a problem that cannot be handled in a software or hardware only solution. We perceive the switch as a full embedded system, capable of running software on a microprocessor (µp), and at the same time, able to handle time critical and computationally intensive tasks in hardware.

Interval routing has been shown to minimize routing tables very effectively. In Chapter 2, we propose a feasible multi-root approach for interval routing, by electing the central node and the corner nodes in the network as roots. We show that our BFS pruned/DFS labeled multi-root approach offers  $\mathcal{O}(1)$  stretch. Furthermore, we present performance evaluation of our algorithm through simulation of both static and mobile ad-hoc networks. Multi-Root Interval Routing (MINT) achieves high delivery ratios and low latencies comparable to shortest-path based MANET routing protocol OLSR and much better than AODV, while reducing the routing table cost more than an order of magnitude, despite using multiple roots [1].

Software Defined Networking (SDN), as exemplified by OpenFlow, has been proposed as an approach that can simplify the way in which some wired networks operate and are managed. The topology of the network is virtualized at a controller node, which computes routes from sources to destinations using its network-wide view, and can instantiate the "flow state" at each switch of the network. The advantages of SDN are that: (a) signaling is reduced drastically by taking advantage of the global network view available at the controller; (b) switches can be greatly simplified by implementing signaling at the controller; and (c) the control plane is decoupled from the data plane, simplifying forwarding. However, SDN approaches have focused on wired networks operating in server rooms, where the controller is one link away from every switch, the signaling focuses solely on the network layer, and do not address the dynamic placement of content and services. We implement a centralized controller for wireless networks that uses MINT as the underlying routing protocol. MINT enables compact routing tables that facilitate the controller to download the flow state to every node in the network using wireless links. In comparison to MINT, downloading full-size explicit routing tables would be impossible due to wireless bandwidth, in a dynamic scenario.

In Chapter 3, we present our Software-Hardware Co-defined Network Switch (SHADES) for a Label Switching Protocol. Our design is implemented for FPGA platforms and successfully instantiates a switch that enables Layer 2 forwarding by using the communication channels between software routing layer and hardware forwarding logic. SHADES receives control packets including the flow state from the MINT's centralized controller, writes these to the flow tables, which can be then retrieved by the hardware logic, thus enabling Layer 2 forwarding. In this work, we use similar mechanisms to state of the art Cisco switches, which are used in wired networks, where the topology change is not an inherent aspect. Our approach is more dynamic, due to the mobile & dynamic nature of wireless routing, which requires the routing control layer to modify the flow tables dynamically. We present real-time emulation results that are in line with our claim that the point-to-point delays inflicted by both the hardware and software layers between the NIC and software routing layers can be avoided by integrating design principles from SDNs, label switching and HW/SW co-design.

In wired networks, switching latency becomes a major bottleneck and as a result needs to be handled at HW by using high cost specialized queueing and scheduling mechanisms. We implement a mini-router grid (MRG) based switch fabric architecture, which yields comparable performance to state-of-art crossbar switch fabrics. MRG switch fabric are scalable in the sense that the can decouple switch size from the cost growth, at the expense of performance, whereas crossbars always inflict an exponential cost growth. Moreover, the architecture allows the use of output queuing, by bounding the speedup by 3 and resulting in much smaller queuing memory than the current state of the art. Also, MRs naturally provide a highly pipe-staged structure, allowing very high frequency operation. The design consideration for our switches include high delivery ratios, low latencies and load balancing capabilities. In Chapter 4 and Chapter 5 we describe our Mini-Router Grids (MRG) based switch fabric architectures, which deliver these metrics with success [2][3].

Finally, Chapter 6 concludes the thesis.

Chapter 2

# Multi-Root Interval Routing (MINT)

## 2.1 Introduction

Interval routing is a distributed approach in routing protocol design that aims at storing routing tables at each node in a compact manner, by assigning labels to nodes in such a way that the destination addresses that use the same output ports are grouped together with consecutive labeling.

In [4], the authors distinguish between a valid interval labeling scheme and an optimum one, stating that the latter can be achieved when all the paths are shortest paths. Moreover, they describe a number of topologies for which an optimum interval labeling scheme exists. An optimum scheme valid for a uniformly distributed random communication network, however, is far from being achieved. Most of the current schemes use single root mechanisms, which result in low performance due to increased total network distance resulting and high stretch.

In this work, we present the Multi-Root Interval Routing (MINT) algorithm for uniformly distributed static and mobile ad-hoc networks of any size. MINT achieves total network distance comparable to shortest path, and as a result, O(1)stretch. Our approach improves upon the earlier works on interval routing by electing multiple roots, computing a BFS pruned/DFS labeled spanning tree for each root, and assigning interval labels at each node per root, such that the optimal path for forwarding the packets can be chosen from multiple sets of intervals.

Software Defined Networking (SDN), as exemplified by OpenFlow [5], has been proposed as an approach that can simplify the way in which some wired networks operate and are managed. The topology of the network is virtualized at a controller node, which computes routes from sources to destinations using its network-wide view, and can instantiate the "flow state" at each switch of the network. The advantages of SDN are that: (a) signaling is reduced drastically by taking advantage of the global network view available at the controller; (b) switches can be greatly simplified by implementing signaling at the controller; and (c) the control plane is decoupled from the data plane, simplifying forwarding. However, SDN approaches have focused on wired networks operating in server rooms, where the controller is one link away from every switch, the signaling focuses solely on the network layer, and do not address the dynamic placement of content and services. We implement a centralized controller for wireless networks that uses MINT as the underlying routing protocol. MINT enables compact routing tables that facilitate the controller to download the flow state to every node in the network using wireless links. In comparison to MINT, downloading full-size explicit routing tables would be impossible due to wireless bandwidth, in a dynamic scenario.

The proposed approach of implementing Multi-Root Interval Routing to enable compact routing tables attains comparable stretch to shortest path routing. Additionally, it yields greater scalability and performance compared to single root interval routing solutions. Using a centralized controller in order to virtualize the global network view and to download the flow tables to the nodes reduce control plane overhead and enable scaling to more than 500 nodes.

In Section 2, we outline the related literature. In Section 3, we describe the

controller operation and Multi-Root Interval Routing (MINT) algorithm. In Section 4, we present simulation results and compare MINT to other routing protocols such as OLSR and AODV. Finally, Section 5 concludes the chapter.

## 2.2 Related Work

In [6], the authors discuss enabling compact routing tables by a-priori labeling nodes and links, and compare their approach, namely implicit routing, to maintaining detailed routing information for all destinations at every node, namely explicit routing. In [7] and [4], Van Leeuwen and Tan explore the problem further and describe optimal interval routing schemes for a number of topologies. These approaches use depth-first-search (DFS) based ordering and labeling that implement valid labeling schemes. However, the resulting spanning trees induce high stretch. Similarly, in [8] and [9], Eilam et al. use DFS ordering, and by forcing extensive topology restrictions and assumptions, they achieve a stretch of 3 to 5.

In [10][11], the interval routing is achieved using breadth-first-search (BFS) ordering in order to improve the stretch. In comparison to shortest path routing, this approach improves upon the earlier approaches, however still fails to achieve low stretch.

In [12], [13] and [14], Tse and Lau provide analytical lower and upper bounds for interval routing. Their results show that even with a relatively large number of labels, interval routing still falls short of being optimal for arbitrary graphs.

In [15], the authors provide lower bounds on routing table compactness for interval routing, in an effort to relate the efficiency (measured by stretch factor) to space requirements (measured by compactness or total memory bits). In [16], Bakker et al. introduce multi-label interval routing schemes where links may contain more than one label in an effort to improve routing efficiency.

A number of proposals on using multiple spanning trees, including [17][18], use multiple roots in parallel, but they are not meant for interval routing nor similar label switching based algorithms.

Software Defined Networking (SDN) emerged as a novel computer networking paradigm to abstract the data plane from the control plane, and thus to achieve higher flexibility and architectural simplicity, by using a centralized controller in wired networks. OpenFlow [5][19] is one of the most renowned instantiations of SDN. NetFPGA [20] demonstrates a successful implementation of OpenFlow on FPGA based platforms.

In a number of works, including [21], [22], and [23], the authors propose applying SDN approach to wireless networks, by using a centralized controller to improve control plane overhead and increase scalability.

OLSR [24] is a shortest-path based MANET routing protocol that performs better both in terms of delivery ratio and latency in comparison to AODV [25], when network is composed of a large number of mobile nodes, whereas AODV is more efficient with small number of nodes and resource critical environments. In this work, we compare our interval routing based algorithm to OLSR and AODV in static and mobile scenarios with increasing number of nodes.

OLSR and AODV have been shown to be not loop-free in [26] and [27], respectively. We claim that applying breadth-first-search (BFS) pruning would be a better option for eliminating the looping edges. Moreover, BFS pruning results in wider trees with much smaller total network distance, in comparison to thin and long trees that would arise from DFS pruning. Latency, one of the most important performance metrics of computer networks, is a function of the total network distance. Takuya et al. [28] proposes a similar approach of network pruning.

In Garcia-Luna-Aceves et al. [29] and Sampath et al. [30], the authors propose incremental routing algorithms that use compact routing tables based on prefix labels rather than node identifiers. An important caveat of the algorithm is that prefix labels grow larger at every hop further away from the root node. The fact that the size of the prefix labels cannot be delimited as network size increases renders the approach unscalable. In comparison, interval routing provide fixed-size labels.

### 2.3 The Architecture & Algorithm

Algorithms that constitute Multi-Root Interval Routing (MINT) run on a centralized controller, connected to every network node on a communication channel orthogonal to the data channel. All nodes send *HELLO* messages to their 1-hop neighbors for network discovery. Following the discovery stage, nodes report their ID, GPS position and 1-hop neighborhood information to the controller, which in return builds a complete graph of the network, assigns pre-order labels (DFS) to nodes, computes intervals in a way that groups together all consecutively labeled nodes, and finally downloads label and interval information to flow tables at every network node.

In the following subsections, we describe the stages of the algorithm at the controller, followed by the final stage of the algorithm, data plane forwarding.

#### 2.3.1 Centralized Controller

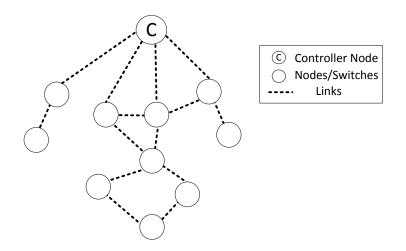

SDN topology comprises one controller node and other regular nodes, as shown in Figure 2.1, where Node C represents the controller. In short, the topology of the network is virtualized at the controller, which computes routes from sources to destinations using its network-wide view, and can instantiate the flow stat at each node/switch of the network. The advantages of SDN are that: (a) signaling is reduced drastically by eliminating multiple protocols running in parallel among peer nodes; (b) switches can be greatly simplified by having to implement only the signaling with the controller; and (c) the configuration and management of the network are simplified greatly by taking advantage of the global network view available at the controller.

The system architecture has several major activities, which we outline here.

Figure 2.1: Software Defined Network Topology

- 1. All nodes are assumed to be connected to the centralized controller, using a communication channel orthogonal to data plane.

- Network nodes monitor their one hop neighborhood information and periodically report it to the controller, as well as their global ID (GID) and global position (GPS).

- 3. The controller generates a graph based on the information it receives from the nodes, and then uses the algorithm outlined in the following subsections in order to compute the node labels and intervals. The controller selects five roots (four corners + the most central node) for building the spanning trees, using the GPS locations.

- 4. The controller proactively computes intervals and downloads the flow tables to the nodes.

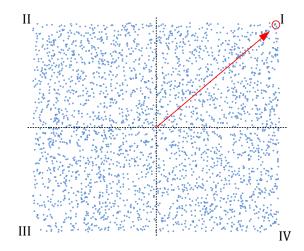

Figure 2.2: Uniformly distributed random network, divided in quadrants.

- 5. The nodes issue a Route Request (RREQ) to the controller for the destination labels. The controller will issue a Route Reply (RREP) in return, with destination label and root index.

- 6. The controller offloads most routing related signaling overhead from the network and uses its centralized computing power to compute the intervals. The controller also serves as the name/label resolution service.

#### 2.3.2 Pruning of the BFS Trees

Upon building a complete undirected graph based on the neighborhood information received from the nodes, our algorithm proceeds to electing five roots. Please note that one assumption made here is that every node has reported their GPS coordinates, such that the controller is able to compare the positions of the nodes to the origin on a virtual Cartesian plane. In Figure 2.2, we show how the

Figure 2.3: Random uniform graph G

controller divides the area into four quadrants, and elects the node with the greatest distance to the origin as a root in each quadrant. The origin is computed as the GPS position of the most central node in the graph, following the centrality algorithm in [31]; as a result it is not a spatial origin, but a logical one. The most central node is also elected as the fifth root.

Using BFS pruning starting from the root nodes, our algorithm builds five spanning trees. By using BFS pruning we achieve wide spanning trees yielding the smallest cumulative network distance.

The rationale behind electing the corner nodes and the most central node as the roots of the spanning trees is as follows:

Let's consider a uniformly distributed random network G of size N in a rectangular area, to be BFS pruned starting from a corner node r as the root, resulting in the BFS tree T. Every node in G is also a node in T. The function  $d_N(T, u, v)$  describes the network distance between nodes u and v in the tree T. We define

$$\mu(T, u) = \sum_{n \in T} d_N(T, u, n), \qquad (2.1)$$

where  $u \in T$  and the function  $\mu(T, u)$  is the sum of all network distances from node u to every other node in T.

The reason to define  $\mu(u)$  lies in the fact that it is a part of the stretch function,

$$STRETCH(u) = \left(\frac{\mu(T, u)}{\mu(G, u)}\right),$$

(2.2)

Because we are trying to show the effect of electing a node as the root of a BFS tree T in a given network G, the only variable part in Def.(2.2) is  $\mu(T, u)$ .

Our initial claim to support our rationale is as follows: We claim that if  $d_N(T, u, r) \leq d_N(T, v, r)$ , then  $\mu(T, u) \leq \mu(T, v)$  would also hold true. This claim implies that the nodes closer to the root retain more edges during pruning, and that the further a node is from the root node r, the more stretch it would inflict upon the tree and the network.

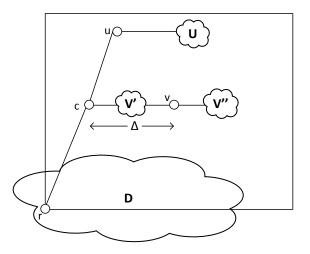

In Figure 2.4, let node c be the common ancestor of node u and v. More-

over,

$$d_N(T, u, r) = d_N(T, u, c) + d_N(T, c, r), \qquad (2.3)$$

$$d_N(T, v, r) = d_N(T, v, c) + d_N(T, c, r), \qquad (2.4)$$

Out initial claim stated that

$$d_N(T, u, r) \le d_N(T, v, r), \qquad (2.5)$$

From Defs.(2.3, 2.4, 2.5),

$$d_N(T, u, c) \le d_N(T, v, c), \qquad (2.6)$$

Also, it follows from Def.(2.6) that the difference  $\Delta$  as in Def.(2.7) is non-negative.

$$\Delta = d_N(T, v, c) - d_N(T, u, c), \qquad (2.7)$$

Computing  $\mu(T, m), m \in T$  statistically requires us to know the distribution of nodes over the tree. For example, if the size of the node cluster V''in Figure 2.4 is much greater than cluster U and/or D, our initial claim would not hold true;  $d_N(T, v, v''), v'' \in V''$  would not be effected by  $\Delta$ , while every  $d_N(T, e, v), e \in T - V''$  would incur  $\Delta$ , resulting in nodes in U and/or D to have greater  $\mu()$ 's.

Figure 2.4: Tree T, pruned from root node r, with nodes  $u,\,v,\,c$  and node clusters  $U,\,V',$  V'' and D

In [32] and [33], the authors prove analytically and empirically that breadthfirst-search pruning results in a degree distribution of  $\hat{p}_k \approx 1/k^{\tau}$ , where k is the node degree and  $\tau$  stands for the degree exponent of the network. The node distribution probability has a decay of  $\mathcal{O}(k^{\tau})$ , which implies that V'' cannot be greater than U and/or D in size. As a result,  $\mu(T, e)$  is an increasing function, as node e is moved further away from node r.

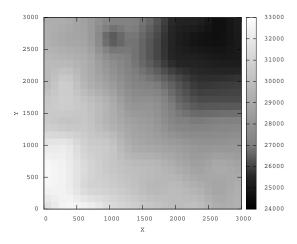

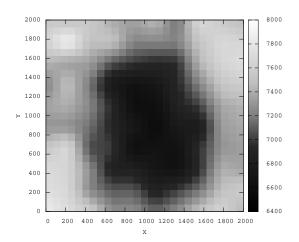

In order to capture this behavior, we simulate BFS pruning on a uniformly distributed random network, starting from a corner node and the most central node, as shown in Figure 2.5 and Figure 2.6, respectively. Empirical data is very much in line with our formal proof, showing the radially increasing behavior of the function  $\mu()$ .

When the resulting BFS pruned spanning trees are merged, by adding all

Figure 2.5: Corner node as root. Heatmap shows empirical  $\mu()$

Figure 2.6: Central node as root. Heatmap shows empirical  $\mu()$

of the edges from the five trees into a new graph and annotating which BFS tree they belong to, this juxtaposed graph would cover a greater percentage of the edges from the original graph, approaching the total network distance of shortest path routing (i.e. *stretch*  $\approx$  1), thus inflicting less latency at the forwarding layer.

#### 2.3.3 DFS Ordering & Labeling

After the loop-free BFS trees are pruned by removing the looping edges, the next step is to run DFS for labeling. DFS labels are required by the nature of the interval routing, since intervals are assigned to node ports according to their vertical positions with respect to the root node.

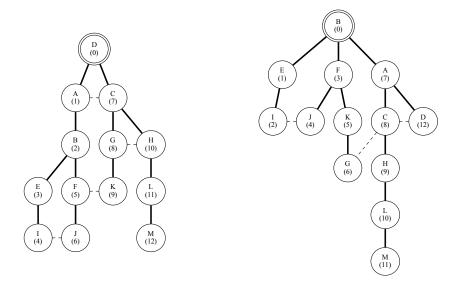

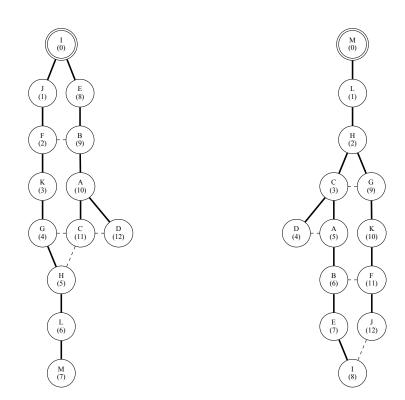

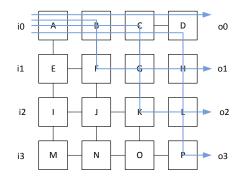

Figures 2.7-2.10 exemplify the procedure of BFS pruning and DFS ordering on Figure 2.3. Corner nodes C1 to C4 are elected as D, B, I and M; BFS spanning trees are ordered and pruned (removed looping edges are denoted by dashed lines); and finally the nodes are assigned the DFS labels (shown in parenthesis). From here and onwards, we will refer to these BFS pruned / DFS labeled trees as BFS/DFS trees.

In order to formulate the problem, we introduce the following notation: For each corner node  $C = \{C_1, C_2, C_3, C_4\}$ , we have a BFS/DFS tree with labels  $L = \{L_{C1}, L_{C2}, L_{C3}, L_{C4}\}$  and for each port per node we have a set of intervals  $I = \{I_{C1}, I_{C2}, I_{C3}, I_{C4}\}$ . These values are computed proactively at the controller when there is a new update from the nodes. This computationally intensive task, in return, is a trade-off for less signaling overhead within the ad-hoc network and

Figure 2.7: Node D is elected as corner 1.

Figure 2.8: Node B is elected as corner 2.

Figure 2.9: Node I is elected as corner 3. Figure 2.10: Node M is elected as corner 4.

much smaller routing tables.

#### 2.3.4 Computing the Intervals

At this stage in the algorithm, five BFS/DFS trees have been generated, which means each node has received five DFS labels, one per each root. Computing the intervals requires the traversal of the trees, such that we can assign intervals at each port of every node, per each root, as described in Algorithm 1. There can be multiple intervals assigned at a port per root. Moreover, we allow forward and reverse directions for intervals. All descendants will have forward intervals; whereas the nodes connecting a node to the root might have reverse intervals.

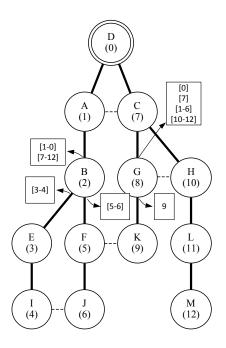

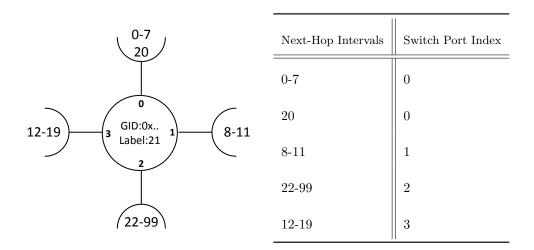

Figure 2.11 demonstrates the intervals assigned to some of the ports of C1 tree.

#### 2.3.5 Interval Table Minimization

The controller node will download a minimal set of intervals to the nodes, instead of the full five sets of intervals. The size of the interval tables can be reduced since some intervals are either exactly the same even in distinct trees, or they are a subset of one another. In order to determine the redundant intervals, we compare the set of intervals at each port of each node for each BFS/DFS tree, and if the labels point to the same set of nodes, one of the intervals is removed; if one is a subset of another, the smaller set is removed.

After the minimized interval information is downloaded to the nodes by

```

Algorithm 1 Algorithm for computing the intervals

1: Let r be the index variable for BFS/DFS trees.

2: Let n be the index for nodes.

3: Let p be the index for ports.

4: Let interval[r][n][p] be the interval lookup table, a list of lists.

5: Let labels_f wd be a temporary list of labels.

6: Let labels_r ev be a temporary list of labels.

7: Let currentNode be a temporary node pointer.

8: for r = BFS/DFS tree iterator; r + + do

for n = Nodes iterator; n++ do

9:

10:

for p = Ports iterator; p++ do

11:

if p connects the node n to the lower levels then

12:

Add all descendants through port p to labels_f wd. Sort. Append to

interval[r][n][p].

else

13:

\# comment: p points to n's parent node.

14:

currentNode = n

15:

while currentNode is not root do

16:

Iterate through lower-level ports of currentNode.parent, except the

17:

port connecting to currentNode.

18:

Add all descendants to labels_f wd. Sort. Append to interval[r][n][p].

Append currentNode to labels_r ev. Reverse Sort.

19:

currentNode = currentNode.parent()

20:

end while

21:

22:

Group consecutive labels in labels_r ev.

Append each group to

interval[r][n][p].

end if

23:

end for

24:

end for

25:

26: end for

```

Figure 2.11: Intervals assigned to the ports of nodes B & G in C1 tree.

the controller, the packets are simply forwarded by following the multi-root interval routing algorithm as explained in the next subsection.

#### 2.3.6 Data Plane Forwarding

Having decoupled the control plane from the data plane, our forwarding algorithm simply compares the destination label in the packet header to intervals at every port of the current node. Next-hop is computed incrementally at every node. The packet will either be in the source node, or a forwarding node in the source-destination path.

When destination label is compared with the intervals, the next-hop algorithm chooses between the five trees in order to forward the packet, by comparing the position of the destination label in the interval. In order to avoid loops, the previously selected tree's distance to destination is skewed to be one less than the actual value. Moreover, if there is a tie, we modulo the destination label to the number of trees and pick the closest tree whose index greater than or equal to the modulo value, as a tie-breaker.

### 2.4 Simulation Results

We run our simulations using NS-3 discrete event network simulator [34] and Boost Graph Library [35], on uniformly distributed mobile networks of various sizes. We use IEEE 802.11ac as the underlying PHY/MAC layers. Our test scenarios consist of networks with 50, 100, 250, 500, 1000, 2000 nodes, and were run over 10 distinct seeds. Finally, the simulation area has been expanded as the number of nodes are increased, in order to keep the average network degree constant.

### 2.4.1 Efficiency of BFS Pruning/DFS Labeling

In this subsection, we present the impact of BFS pruning on the network stretch, defined as the ratio of the total network distance of the subject algorithm to the total network distance of shortest path routing. Latency is proportional to the network stretch, which makes it an important metric in algorithm design.

In Figure 2.12-2.13, we present the comparison of the following schemes, in terms of stretch:

Figure 2.12: Comparison of various interval labeling schemes.

- 1. Shortest path: All edges are intact, and the distance between any two nodes is equal to the shortest path.

- 2. Single-root (Central Node), DFS: The tree resulting from the DFS pruning starting from the central node of the network.

- 3. Single-root (Random Node), BFS: The tree resulting from the BFS pruning starting from a random node of the network.

- 4. Single-root (Central Node), BFS: The tree resulting from the BFS pruning starting from the central node of the network.

- 5. Multi-root, BFS: Juxtaposition of BFS pruned trees resulting from choosing the four corner nodes and the central node as roots

The greater the stretch is, the greater the total network distance and latency are for the network. BFS pruned multi-root scheme has the smallest stretch

Figure 2.13: Comparison of BFS and DFS pruning.

compared to the other schemes, and thus it would achieve the lowest latency. The fact that the stretch saturates as the number of nodes is incremented is also a strong indication that our algorithm is practical even for large size networks. Furthermore, our results are in line with our findings in Figure 2.5 and Figure 2.6.

#### 2.4.2 Interval Table Compactness

We present the number of interval entries in the flow tables and how much they can be further minimized in Table 2.1 and Figure 2.14. The reported values are the sum of all entries in all the network nodes. Percentage improvement after minimization is between 28 to 44, with a standard deviation of 6.34%. The values demonstrate that the minimization algorithm effectively reduces the number of interval entries in the flow tables.

In Figure 2.15 we compare the MINT to explicit routing algorithms (i.e.

Table 2.1: Total number of interval entries.

| Network Size | Intervals | Minimized Intervals | Percentage Min. $\%$ |

|--------------|-----------|---------------------|----------------------|

| 50           | 4033      | 2262                | 43.91                |

| 100          | 9625      | 6242                | 35.14                |

| 250          | 36156     | 26117               | 27.76                |

| 500          | 80271     | 55206               | 31.22                |

| 1000         | 235506    | 152204              | 35.37                |

| 2000         | 521177    | 297994              | 42.82                |

Figure 2.14: Total number of interval entries before and after minimization.

in each node, there is an entry for every other node), in terms of number of routing table entries. In order to emphasize the overhead of our approach using multiple roots, we also include a single-root (central node) scenario. Both single root and five roots scenarios induce flow tables with only a fraction of the size explicit routing algorithms yield.

Figure 2.15: Comparison of MINT vs. explicit routing algorithms.

### 2.4.3 Interval Distribution per Root

Another important design metric for our interval routing algorithm is how balanced the distribution of intervals are per root. The distribution is a strong indicator of how well the load is distributed on various paths available within the network.

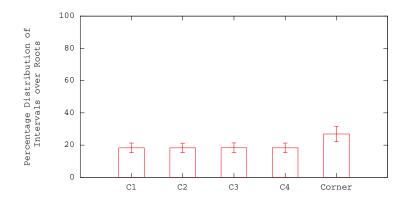

Figure 2.16: Percentage Distribution of Intervals over Roots.

In Figure 2.16, we present the distribution of minimized intervals over

roots. Our simulations show that the interval distribution is independent of the network size and has very small standard deviation.

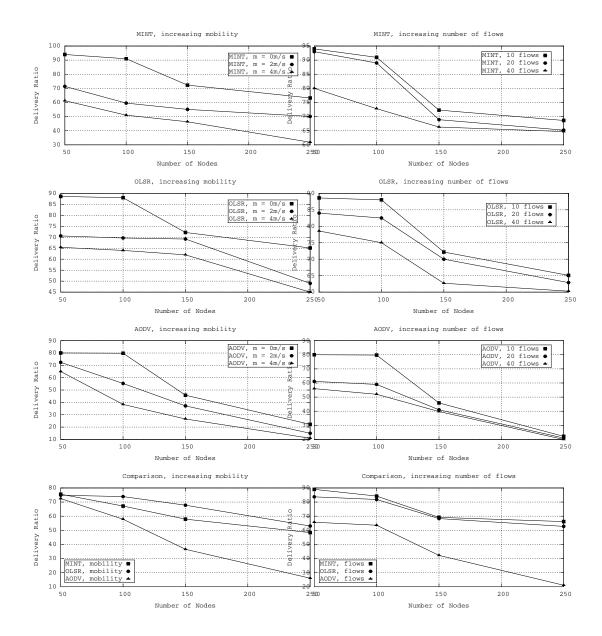

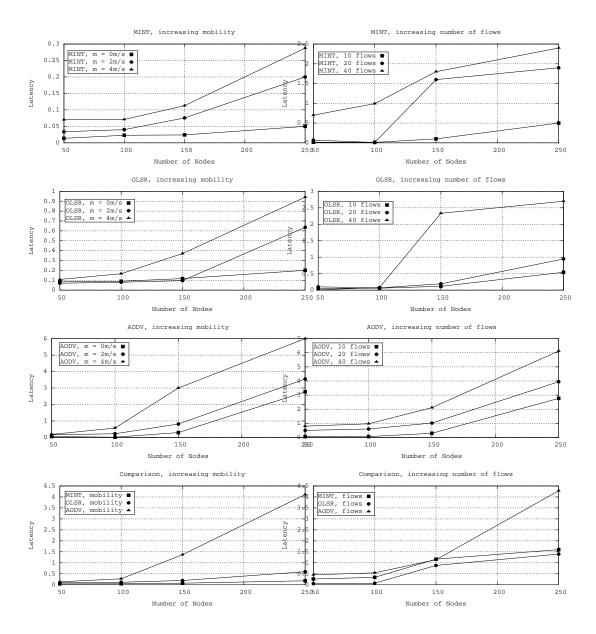

#### 2.4.4 Performance: Delivery Ratio & Latency

In this section, we present the performance evaluation in terms of delivery ratio and latency, by comparing MINT to routing protocols such as OLSR and AODV. MINT achieves high delivery ratios and low latencies comparable to OLSR, while performing much better than AODV, as presented in Figure 2.17 and 2.18

MINT incurs slightly higher end-to-end latency for data delivery compared to OLSR as the number flows increase, which is mostly due to the fact that packets may take routes that are slightly longer than the shortest paths attained with OLSR. However, as the mobility increases, MINT achieves slightly better latency.

## 2.5 Conclusion & Future Work

Interval routing is an approach in routing protocol design that aims at storing routing tables at each node in a compact manner. A number of topologies that have an optimum interval labeling scheme are described in various publications, however an optimum scheme for uniformly distributed random networks is far from being achieved.

In this work we proposed a feasible multi-root approach for interval routing, by electing the central node and the corner nodes as roots. Starting from each root we used BFS pruning and DFS labeling in order to assign labels to the network

Figure 2.17: Performance Evaluation, Delivery Ratio

Figure 2.18: Performance Evaluation, Latency (seconds)

nodes, as well as intervals to each port of every node. We showed that our BFS pruned/DFS labeled multi-root approach offers  $\mathcal{O}(1)$  stretch, by improving upon the single root interval routing approaches in earlier works.

We implemented a centralized controller for wireless networks that uses MINT as the underlying routing protocol. MINT enabled routing tables an order of magnitude smaller than explicit routing, that facilitate the controller to download the flow state to every node in the network using wireless links. In comparison to MINT, downloading explicit routing tables would be impossible due to the wireless bandwidth in a dynamic scenario. Using a centralized controller in order to virtualize the global network view and download the flow tables to the nodes reduced control plane significantly and enabled scaling to more than 500 nodes.

Furthermore, we presented performance evaluation of our algorithm on NS-3 simulator. Multi-Root Interval Routing (MINT) achieves high delivery ratios and low latencies comparable to shortest-path based MANET routing protocol OLSR and much better than AODV, while reducing the routing table size more than an order of magnitude.

For future work, we plan to incorporate an analytical model of routing tables compactness induced by our approach, in order to demonstrate the efficiency, in terms of the performance to compactness ratio, an important aspect of the interval routing design as described in [36]. Chapter 3

Software-Hardware Co-Defined Network Switch (SHADES) for a Label Switching Protocol

## 3.1 Introduction & Related Work

In this chapter, we present our Software-Hardware Co-defined Network Switch (SHADES) for a Label Switching Protocol. By taking the hardware component into account in the design flow, our system demonstrates a successful attempt to implement an Hardware-Software co-design embedded system instantiation for network switches.

Software Defined Networking (SDN) emerged as a novel computer networking paradigm to abstract the data plane from the control plane, and thus to achieve higher flexibility and architectural simplicity. This is implemented by computing the forwarding tables at the controller node, which are then disseminated to the other nodes. The data can be forwarded from a node to the next hops using these flow tables. In Section 2.3.1, we have explained in detail how a centralized controller can virtualize the network in order to compute the routes, thus remove the control plane overhead from the data plane links.

By using interval routing we have achieved compact routing tables, that can actually be disseminated to the flow tables in a wireless scenario. Other approaches using explicit routing tables dictate an order of magnitude more information to be downloaded over wireless links, which is not feasible given the low bandwidth of wireless communication. The benefits of using a multi-root interval routing approach has been described in detail in Chapter 2. Figure 2.15 clearly demonstrates that compact routing tables require much less information exchange, which makes this approach ideally suited to mobile scenarios. Using interval labels would enable forwarding to be handled at lower layers (Layer 2), instead of having to transmit the packet to the upper layers of hardware/software and examine the next hop information. IP (or any other routing protocol) data packets can be wrapped into label switched protocol packets, which then are forwarded to the next hops dictated by the label switched protocol.

Our proposal is to merge the SDN philosophy with label switching, which would enable the architecture to be implemented in a hardware-software co-design fashion. Introducing a hardware component into network protocol design might initially seem to combine two orthogonal design components, however the outcome is an architecture that achieves multiple levels of abstraction, flexibility, simplicity, scalability and high performance at once.

Kempf et al. [37] and Das et al. [38] describe extensions on OpenFlow that incorporate MPLS, and propose modification on NetFPGA [20] in order to implement a router for MPLS networks. Please note that this approach serves a different purpose than what we are trying to achieve by using label switching in order to introduce forwarding at lower layers and enable hardware acceleration.

State of the art switches use similar hardware-software co-design techniques for the implementation. In [39][40], Cisco Systems engineers describe the design effort that goes into Cisco switches, which rely on using flow tables written at the software routing layer; these flow tables then can be read by hardware logic components, and used for forwarding packets at Layer 2. Cisco switches also rely on FPGAs for easier hardware reconfigurability of some components; time-to-market is also another important reason for the use of these easily reconfigurable ICs. Moreover they implement Layer 2 processing of packet headers in order to retrieve the destination address and search for the next-hop information in the flow tables.

Another important aspect of using MINT as the underlying routing layer presents itself when the destination address is searched in the flow tables. Comparing the destination address to all entries in an explicit routing algorithm would be costly, either in terms of time (i.e. CAM) or hardware cost (i.e. TCAM). By using smaller routing state, MINT improves the cost and power for forwarding.

Please note that the software control of the flow tables in Cisco switches is different from what we want to achieve in our work, despite the fact that we are using similar mechanisms to implement it on hardware. Cisco switches are used in wired networks, where the topology change is not an inherent aspect. Our approach is more dynamic, due to the mobile & dynamic nature of wireless routing, which requires the routing control layer to modify the flow tables dynamically. Undoubtedly, achieving Layer 2 processing and forwarding is the common element between our work and state of the art switches.

Hardware-software co-design enables communication channels between hardware components and software that does not exist in regular computing systems. Our System-on-Chip (SOC) is implemented on an Altera Field-Programmable Gate Array (FPGA), using the soft core microprocessor NIOS II with MMU, such that our system supports multiprocessing capabilities at software networking stack. The operating system (OS) is a variant of uClinux [41] with MMU support and it has been modified and recompiled by our team in order to achieve a fully functional switch with four network interfaces (NIC).

We show that the point-to-point delay caused by both hardware and software components from the NIC to the software routing layers can be avoided by forwarding on Layer 2. Moreover, we validate that SHADES successfully supplements the controller and routing layer algorithm described in Chapter 2 by using the control packets received from the controller to populate the flow tables for data plane forwarding.

In Section 2, we describe SHADES architecture and its building blocks. In Section 3, we present our results and describe how SHADES perform better in comparison to components that constitute it. Finally, Section 4 concludes the chapter.

### **3.2** Implementation

### 3.2.1 Label Switched Routing

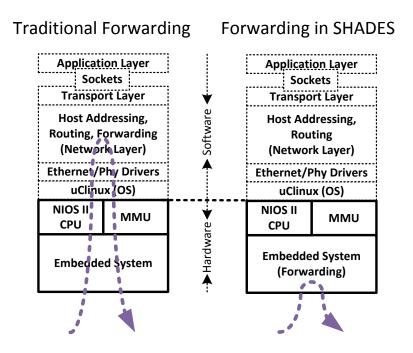

In Chapter 2 we show that multi-root approach has a stretch of  $\mathcal{O}(1)$  and proves to attain high delivery ratios and low latencies comparable to shortest path routing, both in static and dynamic networks. By computing the compact routing tables (i.e. intervals) at the controller node and disseminating them at every node, we achieve abstraction of the forwarding plane from control. The ability to realize

Figure 3.1: Comparison of Traditional Forwarding and SHADES

forwarding at the hardware layer has multiple benefits, such as low latency through the system, more computational resources for other tasks including control plane handling, and less congestion through the SOC bus (Figure 3.1).

Our architecture enables the forwarding function to be handled at the hardware layer by using a dual port/dual clock domain flow table memory, which contains the mapping of the intervals/labels to the next hop ports of the switch. In this way, we allow the software routing layer to modify the flow tables, while enabling the hardware forwarding layer to retrieve the next hop information without transmitting the frames/packets to higher layers.

Figure 3.2 demonstrates the interval label/port information within a node

Node<sub>A</sub>. When a new data packet arrives at the switch, SHADES engine determines if the frame (1) is intended for the current node/switch, and thus the packet is forwarded to upper software layers, (2) if it needs to be forwarded to another node/switch, or (3) if it is simply dropped. As for forwarding, the next-hop node will be determined by comparing the destination label to the intervals in the flow tables. Finally, the frame will be delivered through the corresponding port.

Figure 3.2:  $Node_A$  Flow Table for HW Forwarding

When a packet is received by the destination node, SHADES engine forwards it to the software layers, where the original Layer 3 packet is stripped from the label switching encapsulator.

### 3.2.2 SHADES Top-Level System Architecture

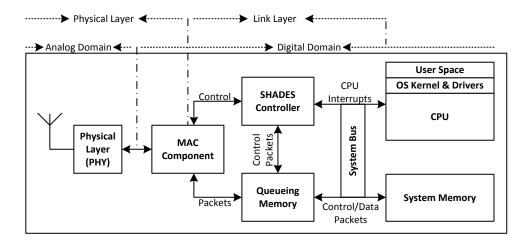

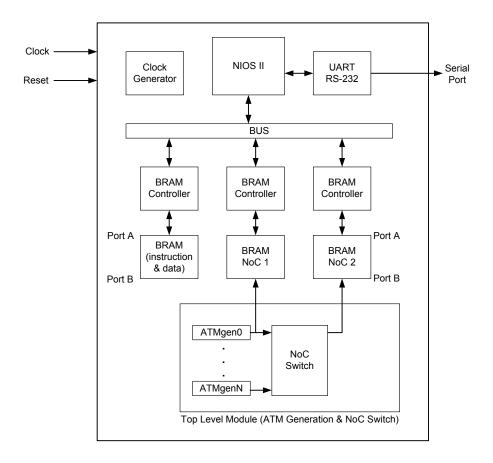

In this subsection, we present the top-level system design for SHADES. Figure 3.3 is the system-on-chip (SOC) block diagram that depicts the integration of various components of our switch.

Figure 3.3: Hardware-Software Co-defined Network Switch (SHADES), Abstract

Our understanding of a switch design requires a full system integration, capable of running software in a microprocessor ( $\mu$ p), while still being able to handle time critical and computationally intensive tasks in hardware. If a switch could distinguish control plane and data plane packets at the hardware, it would gain the capability of taking the decision to deliver them to higher layers or forward them to the next hop nodes/switches. This would enable hardware layer forwarding, thus greater performance. The imagining of such a switch necessitates the incorporation of a complete system-on-chip (SoC) approach, which consists of a  $\mu$ p, main memory, various accelerators, a mac controller, and routing related algorithms at both the software and hardware layers.

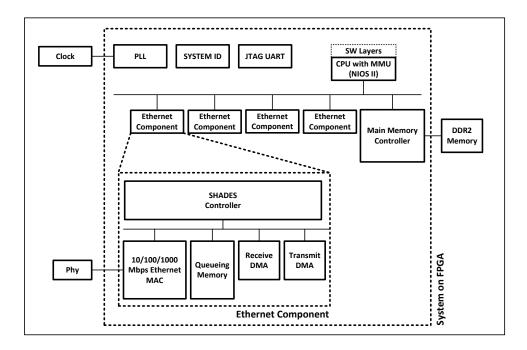

We implemented a four port switch using a Terasic DE4 board [42] with an

Figure 3.4: Hardware-Software Co-defined Network Switch (SHADES), Implementation for Altera FPGA

Altera Stratix IV GX FPGA (EP4SGX230KF40) [43] and we validated the component connectivity and functionality of all hardware components and software layers. We used the soft core microprocessor NIOS II with MMU to ensure that our system supports multiprocessing capabilities at software networking stack. Figure 3.4 demonstrates the same components from the previous figure, with the emphasis on design for FPGA environment.

We have used several reference designs from Altera, Terasic and other third parties, including [44], [45], [46], [47], [48], [49], [50], [51], and [52]. The operating system (OS) is a variant of uClinux [41] with MMU support and it has been modified and recompiled by our team in order to achieve a fully functional switch with 4 network interfaces (NIC). We have used tools such as SOPC Builder for system-level design, Quartus II for synthesis of the hardware, Modelsim for hardware simulation, Wireshark for capturing network packets, and GCC for miscellaneous compilation tasks, among a number of other tools.

## 3.3 Performance Results

We have carried out a number of performance evaluation tests with our hardware-software co-designed components, in order to demonstrate that our approach yields considerable improvements over current solutions. In Subsection 3.3.1 we implement a reverse loopback test in order to measure the delay our system would help avoiding when a frame is switched at the hardware layer.

### 3.3.1 Point-to-Point Round-Trip Delay Time

Forwarding the data packets at the hardware layer makes it possible to avoid the latency that would otherwise be inflicted by various hardware and software layers. The signals that are received by the PHY are deserialized into a frame at the MAC component. MAC Component will write the frame into the temporary Queueing Memory. SHADES Controller determines if the frame should be forwarded to the next hop or if it should be sent to the software layers.

If SHADES Controller did not exist, the frame would need to be transmitted to the DDR2 Memory by the Receive DMA component, through the BUS and the main memory controller. MAC would issue an interrupt to the microprocessor (NIOS II), and the interrupt would trigger the OS/driver routines, and that would initiate the reading of the packet from the main memory. Software Routing Layer would examine the header, make a routing decision, pass the command to the driver/OS layer that would in return issue an interrupt to the MAC component. DMA Transmit component would read the packet from the main memory (via the BUS) into the temporary Queueing Memory, from where the MAC component would serialize the frame and transmit it to the PHY.

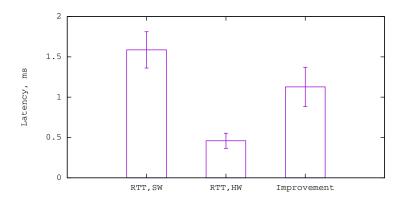

In order to measure the latency through the components/layers explained in the last paragraph, we execute the following scheme: We connect a computer  $Node_C$  to SHADES from one of the four ports, establishing a point-to-point connection. (i) Measuring the Round-Trip Delay Time (RTT) initiated from  $Node_C$ to SHADES and back, including all layers, (ii) Measuring the RTT initiated from  $Node_C$  to SHADES and back, bouncing the packet back at SHADES Controller using a reverse loopback mechanism, and finally (iii) computing the delta, we would obtain the latency through the aforementioned components/layers.

In many prominent publications including Carter and Crovella [53], Brik et al [54], and Obraczka and Silva [55], the authors rely on ICMP packets (PING tool) for RTT measurements. Especially in [55], the authors discuss how PING tool consumes few resources and is fast, and as a result it is a good candidate for reporting RTT.

We implement the reverse loopback mechanism based on the reference

Figure 3.5: Comparing RTT for SW and HW Forwarding

design in [45]. In both cases, we use Wireshark to monitor the packets and measure RTT. In the first test, the RTT values are exactly the same as reported by PING. In the second test, we observe that Wireshark catches the packets that were "bounced" by the reverse loopback circuitry, however PING will not accept them as reply packets, and as a result we only report the Wireshark measurements for both cases. In Figure 3.5 we present the RTT measurements as well as the improvement delta in milliseconds. As one can easily observe, most of the delay is caused by components above the MAC layer, and by combining label switching and hardware forwarding capabilities, this delay can be avoided. Please note that the reported value is per point-to-point connection, thus the approach would improve each hop through which a packet is forwarded. Also note that FPGA systems are slower in terms of clock frequency, and as a result this improvement would be a smaller value in an ASIC system, but would still remain a major percentage of the overall delay.

## 3.4 Conclusion

SHADES exploits the hardware-software co-design paradigm in order to enable Layer 2 forwarding using MINT routing and a centralized controller to disseminate flow tables to the nodes. We are using similar mechanisms to state of the art network switches in order to implement Layer 2 processing and forwarding capabilities in our switch.

Our approach enables dynamic modification of flow tables that is inherent to the mobile wireless routing. By using interval routing we have achieved compact routing tables, that can actually be disseminated to the flow tables in a wireless scenario. Other approaches using explicit routing tables dictate an order of magnitude more information to be downloaded over wireless links, which is not feasible given the low bandwidth of wireless communication.

We have showed that our design can be implemented and prototyped on a Field-Programmable Gate Array (FPGA) based platform. We present real-time emulation results that are in line with our claim that the point-to-point delays inflicted by both the hardware and software layers between the NIC and software routing layers can be avoided by integrating design principles from SDNs, label switching and HW/SW co-design. Chapter 4

Hardware Design and Implementation of a Network-on-Chip Based Load Balancing Switch Fabric

# 4.1 Introduction

In today's world, billions of users all over the world are connected through networks of different sizes, purposes and scopes. A network host might be one of the nodes in a local area network (LAN), the Internet backbone, the infrastructure nodes of a wireless network, or mobile devices in an ad-hoc network.

The communication between the nodes in a network is realized by a broad and diverse body of electronic and optical technology. The network switches in wired networks carry out the task of connecting two or more nodes (or networks), and perform the important functions of (i) determining the next destination of a packet that has been received by the router (control), and (ii) forwarding the data packets to the destination (forwarding). The switch fabric is a key building block of hardware based high-performance network switches, and they implement the second function. When a packet is injected into the router, it is stored in a buffering memory; the output port corresponding to the packet's destination is computed; and finally the packet is forwarded through the output port to its next hop in the network by following the rules in a scheduling algorithm. A switch fabric consists of buffering memories for temporary storage, scheduling unit(s) for forwarding, and other computational components that facilitate these tasks.

A high-performance switch for wired networks is required to support high bandwidths, in order not to become the bottleneck in the communication themselves. The switch fabric, being the key component in a router, constitutes an important part of the router design effort, and therefore it remains to be an open research problem. The switch fabric design consists of architectural design and scheduling algorithm design. The architectural design incorporates the interconnect topology and the buffering memory organization. The scheduling algorithm carries out the task of deciding which packet is to be forwarded, in case a number of packets compete for the same output port, resulting in contention; one of these packets will be forwarded, whereas others will need to be stored in the buffering memory, until later rounds.

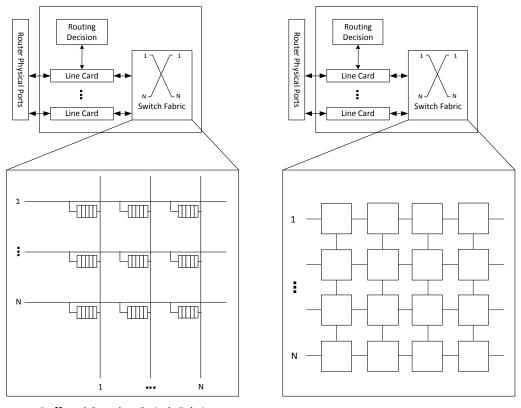

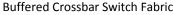

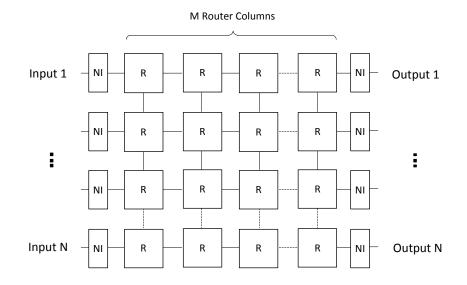

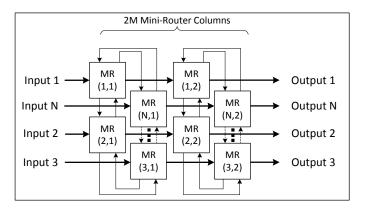

In this chapter, we propose two Mini-Router Grid based switch fabric architectures to replace the current state of the art crossbar architectures. Crossbars require both input queuing and crosspoint queuing, and as a result they have very high costs, despite the performance. Moreover, both the input and crosspoint queues are shown to require large size memories. Our proposal replaces the crossbar by following the Network-on-Chip (NOC) approach, in which the switch fabric resembles to a grid network that consists of tiny 3 input/output port Mini-Routers (MR). The connection links between MRs are very small, and the control signals that implement back-pressure are pipelined automatically due to the nature of the point-to-point communication between MRs. In this way, the critical path is very short, yielding high frequencies and throughput.

Our architectures, Unidirectional Network-on-Chip (UDN) and Multidirectional Network-on-Chip (MDN) require very small buffer sizes compared to crossbars, achieves 100% throughput for admissible traffic, and are at least as scalable as other architectures in terms of hardware cost. The switch fabric grid is composed of N rows, one for each input/output port, and M columns of MRs. The number of columns can be decreased at the expense of performance, and as a result the switch size is decoupled from the cost growth, which constitutes the main advantage of UDN and MDN over crossbars.

We (1) carry out feasible hardware implementations of the MRG switch fabrics for FPGAs; (2) execute performance tests, both via RTL simulations and actual execution on FPGA, under uniform traffic flows; and (3) present results in terms of throughput, average latency, and average bitrate.

The rest of the chapter is organized as follows: in Section 2, we present the background information and the related literature. This section includes the information on various architectures that historically have been the milestones in the network switch design. Also, the Network-on-Chip (NOC) related concepts are described. Moreover, we describe the rationale behind how our architecture compares to these milestone architectures. In Section 3, we present our switch fabric architecture and its corresponding hardware implementation; the organization of components such as the buffering memory, Network Interfaces (NI) and Mini-Routers (MR); the routing algorithm (among MRs); and finally the scheduling algorithm. In Section 4, we present the RTL synthesis, RTL simulation and the actual execution results on FPGA. Section 5 concludes the chapter.

### 4.2 Related Work

### 4.2.1 The Switch Fabric

The switch fabric is one of the most important building blocks of a network router. Moreover, it requires the implementation of a scheduling unit, which regulates and grants permission for the pairing of input-output ports and buffers in between.

The FIFO scheduling, perhaps the simplest scheduling scheme for input buffering suffers head-of-line (HOL) blocking, where a packet at the head of the queue cannot be delivered, and therefore blocks the others behind it, resulting in throughput decrease (58.6%), increased delays, and congestion. A number of algorithms/architectures were proposed in order to remediate this shortcoming, including PIM, RRM, iSLIP [56][57][58], based on virtual output queues (VOQ), claiming a theoretical 100% throughput.

Another proposal, the load-balancing switch [59], claims greater scalability. VOQ architectures do not scale optimally as the number of ports is increased, and therefore become impractical. The load-balancing switch architecture does not have a scheduler, at the cost of duplicating the packets within the switch fabric.

The main design challenges for implementing switch fabrics include bandwidth, latency, scheduling algorithms, interfacing, and routing algorithms as in NOC based solutions. Several switch fabric architectures have been proposed, including the crossbar [60], shared-bus [61] and shared-memory [62] switches, which deal with these design challenges in various ways. The crossbar switch is the dominant architecture in today's high-performance switches, due to a number of reasons: crossbar switch is more scalable than the shared-bus and shared-memory; this is due to the limitations in bus transfer bandwidth and memory access bandwidth, respectively. Crossbar switch provides point-to-point connections and non-blocking properties, as well as supporting multiple simultaneous transactions, increasing the bandwidth and speed of the router.

Various queuing schemes have been proposed for implementing a crossbar switch. Switch fabrics has evolved from the Output Queued (OQ) to Combined Input and Output Queued (CIOQ) and then to the Combined Input and Crosspoint Queued (CICQ) architecture. This is exemplified by the three generations of the IBM Prizma switch [63]. Also there are a number of other works that combine various queueing schemes, including [64], [65], and [66].

Output queues require a speedup of N, denoting the number of input/output ports, which does not scale with the switch size. CIOQ use complex centralized scheduling units that are not feasible implementation-wise. A number of crossbar switch implementations implement queueing memories only at the crosspoints [67], which proves to require more queuing memory than Combined Input and Crosspoint Queued (CICQ) architectures [68]. CICQ implements smaller crosspoint queues in conjunction with large input queues (usually replaced by large VOQs), which is shown to require smaller memory space with respect to queues at the crosspoint only [69]. CIOQ or CICQ, crossbar switch architecture also require N 1xN demultiplexers and N Nx1 multiplexers for crosspoints, which are very high-cost are logics and make the design unscalable. Moreover, multiplexers and demultiplexers are controlled by a centralized logic component, which yields  $N^2$  complexity for the decision logic. In [70], the authors demonstrate that 20-25 packet-sized queuing memory at each crosspoint is required to achieve 100% delivery ratio, under admissible traffic.

MRG based switch implements distributed control. Buffering and scheduling is handled within MRs. The only control is the backpressure mechanism that signalize the predecessor if there is an available buffer in the next MR; please note that this signal is the critical path of our design, and it is very short. Our architecture does not require any buffers outside the grid, unlike CIOQ or CICQ, and the buffer size is much smaller. In our simulations, every MR has 9 packet-sized queuing memory in total, and in Chapter 5 we analytically reaffirm our simulation results.

A number of papers analyze the power consumption in switch fabrics by analytical methods [71] and by simulation [72][73]. In [72], the breakdown of the power consumption is as follows: 33% for clocking, 22% for buffering memories, 17% on the links, and 15% for the switching activity. Clocking and link power is frequency and technology dependent, and as a result cannot be improved much by architectural design. However, by decreasing the buffering memory size, the system's power consumption can be improved. Our buffering mechanism would definitely be a step in the right direction.

### 4.2.2 Network-on-Chip

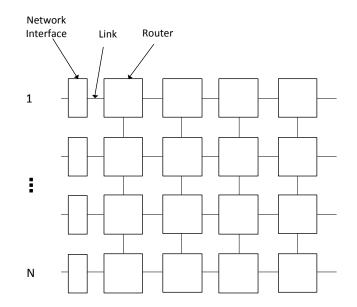

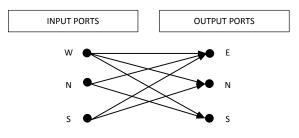

Figure 4.1: NOC Switch Fabric

Network-on-chip, a relatively new concept that emerged as a system-onchip (SOC) communication methodology, borrows many ideas from the computer networks, the domain in which the research on routers and packet switching has matured. However, they need to be adapted, since there is no direct translation of these methodologies.

Figure 4.1 represents a NOC router, in the form of a regular N-by-N minirouter (MR) grid. Computational cores in a SOC are connected to each other via this communication fabric, composed of network interfaces (NI), and MRs.

The NIs act as an abstraction layer between the computational cores and MRs. The data to be communicated in between these cores are packetized in NIs and transmitted to the next-hop router, in equally sized flits.