# UC Berkeley UC Berkeley Electronic Theses and Dissertations

# Title

Roll Printed Electronics: Development and Scaling of Gravure Printing Techniques

**Permalink** https://escholarship.org/uc/item/3tz7x1kn

Author de la Fuente Vornbrock, Alejandro

Publication Date 2009

Peer reviewed|Thesis/dissertation

Roll Printed Electronics: Development and Scaling of Gravure Printing Techniques

by

Alejandro de la Fuente Vornbrock

A dissertation submitted in partial satisfaction of the

Requirements for the degree of

Doctor of Philosophy

in

Engineering - Electrical Engineering and Computer Sciences

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Professor Vivek Subramanian, Chair

Professor Tsu-Jae King Liu

Professor David Dornfeld

Fall 2009

Roll Printed Electronics: Development and Scaling of Gravure Printing Techniques

© Copyright 2009 by Alejandro de la Fuente Vornbrock

#### Abstract

# Roll Printed Electronics: Development and Scaling of Gravure Printing Techniques by Alejandro de la Fuente Vornbrock Doctor of Philosophy in Engineering - Electrical Engineering and Computer Sciences University of California, Berkeley Professor Vivek Subramanian, Chair

To realize the potential cost savings promised by printed electronics, high-speed, large-volume manufacturing methods must be established. Rotary printing techniques such as those used in the graphic arts are ideal candidates. However, very little research has been done on utilizing these techniques for printed electronics because digital processes such ink-jet printing have offered researchers a low-cost flexible solution for demonstrating the printability of their materials, despite the fact that these processes may be difficult to scale for large-volume manufacturing.

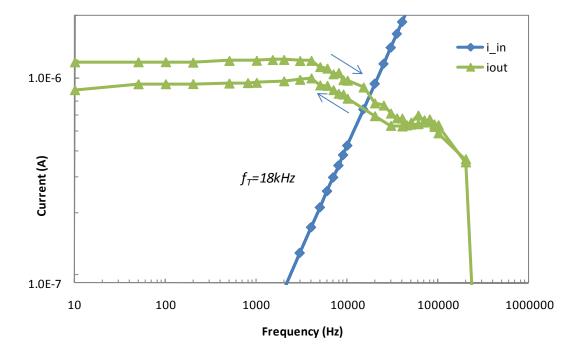

In this thesis, gravure, a printing process which offers the highest resolution, highest speed, and largest volume production in the graphic arts is demonstrated as a viable technique for printed electronics. In order to make laboratory-scale research with this technique possible, a custom table-top gravure printing press was designed. This press allows for small amounts of ink to be utilized during a print and enables multi-layer prints with a registration accuracy not seen in conventional gravure printing presses and suitable for printed electronics. With this press, printing processes to deposit functional materials for printed circuits are investigated with a focus on developing process modules to manufacture fully printed organic thin film transistors. Considerable effort is made to establish processes to deposit metallic lines with feature sizes below 20 µm and a total surface roughness below 20 nm, uniform thin films of polymer dielectrics with thicknesses as low as 70 nm, and high performance polymer semiconductors. These processes are then integrated to manufacture capacitors suitable for integrated circuit components and organic thin film transistors with operating frequencies as high as 18 kHz.

#### Acknowledgements

I have been told many times, always by older, much wiser people than me, that the best job is a job you enjoy, and that it is generally the people who make it enjoyable. Despite how challenging graduate school was at times, I can say I truly enjoyed it and I have a great group of friends and colleagues to thank for that.

There gravure project in general was an immense effort which involved a great number of people. Steve Molesa was my big brother in lab during my first years here at UC Berkeley and in great part this project got off the ground thanks to him. Here is to Steve for all of those days on the ink-jet printers. Early in the project I had the fortune of working with two great undergraduates, Li Li and Vincent Liu, who at one point where dubbed the "mad CADders" for the endless hours we spent designing the gravure printer. Li then went on to help me out with gravure roll patterning, and was a big help in getting over some hurdles with exposure and development. Another undergraduate, Jose Covarrubias, followed up by helping scale gravure feature sizes. Finally, I had the privilege to work with Donovan Sung. Donovan made great strides in advancing our patterning capability by making contacts with the gravure industry and getting some great collaborations set up all on his own. I owe him thanks and respect for the tenacity he has shown in pushing the project forward, getting things done, and meeting deadlines, especially when that meant he was sleeping on the couch.

Of course, there would be no gravure printer without a machine shop, and I owe special thanks to Warner Carlisle, Bob Amaral, Joe Gavazza, and Ben Lake. Joe was the head machinist on my project and was my main point of contact when technical issues came up. He was always helpful, patient and friendly. To Ben Lake, I owe the greatest thanks. From the very beginning he bent over backwards to give us a very competitive bid, to make sure our project was well taken care of, and to make adjustments when I came back (so many times) with design changes and outrageous requests. Not only has Ben an example of willingness to help, he's become a close friend. Also, I want to thank everyone for letting me sit with them and bother them with all sorts of obliquely work-related questions during their lunch breaks, it was great fun and I learned a lot from them.

There was also a great deal of external help on this project that I must recognize and thank. Soligie in Savage, MN funded much of the printer development and early print research. WRE/ColorTech here in Berkeley and in Greensboro, NC was very helpful in providing us with patterned rolls and contacts through the industry. Mark Richter from Rotadyne Decorative Technologies made this project come together, as his attention to detail and standards of quality gave us the best gravure rolls we have used. Dr. Guido Hennig started our collaboration with Daetwyler and put us in touch with Eric Serenius, John Fraser, Lynn Petterson, and Kent Seibel who have worked hard to bring us the next generation of high-resolution gravure rolls. Finally, Erika Hrehorova from Western Michigan and Jay Sperry from Clemson have generously shared their knowledge and expertise in conventional printing with me.

For their involvement with my thesis work I would like to thank Professors David Dornfeld, Tsu-Jae King Liu, Costas Grigoropoulos, and Costas Spanos. Professor Dornfeld has been of great help throughout the years especially in helping improve the quality of our gravure rolls, generously letting me use his equipment, and giving me hours of very fruitful discussion. I owe everything I know about precision design to him. Professor King has been a beacon of excellence for me, a great host during my first year, and has been incredibly generous in heading my qual committee and reading my thesis on such short notice.

My lab mates have been a great part of the experience, and in them I have found great role models and friends. Everyone there my first year was so inspirational, and I owe thanks to Steve Volkman, Paul Chang, Josei Chang, Frank Liao, Brian Mattis, Steve Molesa, David Redinger, Daniel

Huang, and Tuyen Le. I am quite sure I'll never forget Steve Volkman's creativity, Paul's intelligence, and Josei and Frank's efficiency. I also want to thank Shong Yin for being so generous and helpful these last few years, Huai-Yuan Tseng for the good times we spent printing together, and Dan Soltman for fruitful discussions on fluids. Through the years, though, I owe the most to Teymur Bakhishev, he has been a great lab mate and my best friend.

I would also like to give thanks to my class-mates and friends; to John Secord, who was my roommate and close friend, and to Drew Carlson, Daniel Huang, Pankaj Kalra, Matthew Schoenecker, and Joe Makin, all of whom I learned a lot about how to be a better student and person from; to Donovan Lee for being such a good friend, for helping me so much in the last few months, and for motivating me to finish strong; to Raúl Aguilar, Eva Chapa, Armando Solar, Raúl Howe, and Homero Lara, for the laughs, the love, and support.

I would have never gotten to Berkeley if it was not for a great undergraduate experience. I have to give special thanks to Prof. Richard Kiehl who took me under his wing since I was a sophomore at the University of Minnesota and taught me, much of it by personal tutelage, so much about science and research. My lab mates then were also very important and I owe thanks to Nikolai Nezlobin and Guanghua Xiao for being there to guide and help. I was also greatly inspired by my closest friends, Anthony Anderson and John McKeen, with whom I spent many hours talking about research and the wonders of science. Finally, I want to thank Prof. Anand Gopinath who had faith in me, and made me apply to the nation's top schools and the NSF Fellowship.

To my advisor, Prof. Vivek Subramanian, I owe my most sincere gratitude. He has always wished the very best for me, early on by encouraging me to think big and tackle problems that really matter, later, by teaching me that the purpose of the PhD is for me to exercise my leadership and take control over my own success, and throughout, by challenging me to strive for the highest level of quality. His vision has inspired me to always look for new uses for technology, and I give credit to him for the idea of using gravure. I am very grateful for the respect and the confidence he has placed in me, especially when that meant I would be standing in his place, or making him go and raise more funding. I only wish I could have done so much more for him.

Finally, I want to thank my family. I have been so blessed to have such loving and caring parents and sisters. They have taught me so much about ethics, caring for the greater good, putting others before me, and most importantly, love. Mom, Dad, Sabrina, and Priscilla, this is for you.

# Contents

| 1 | Introd         | uction                                                          | 1    |

|---|----------------|-----------------------------------------------------------------|------|

|   | 1.1            | The potential of printed electronics                            | 1    |

|   | 1.2            | Conventional Printing Methods                                   | 2    |

|   | 1.3            | Goals                                                           | 4    |

|   | 1.4            | Background                                                      | 4    |

|   | 1.5            | Organization                                                    | 5    |

|   | 1.6            | Works Cited                                                     | 5    |

| 2 | Gravu          | re                                                              | 7    |

|   | 2.1            | Introduction                                                    | 7    |

|   | 2.1.1          | Gravure printing fundamentals                                   | 7    |

|   | 2.1.2          | Table-Top Proof Presses and Laboratory Presses                  | 9    |

|   | 2.2            | A Laboratory Scale Gravure Printer for Printed Electronics      | 10   |

|   | 2.2.1          | Alignment Process and Sources of Error                          | . 12 |

|   | 2.2.2          | Experimental Position Repeatability and Alignment Accuracy      |      |

|   | 2.2.3<br>2.2.4 | Coupled Thermal Structural Analysis<br>HTM Analysis             |      |

|   | 2.2.4          | Discussion                                                      |      |

|   | 2.2.6          | Improvements                                                    |      |

|   | 2.2.7          | Error Analysis Summary                                          | . 31 |

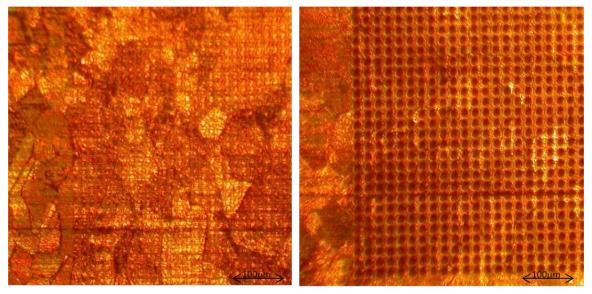

|   | 2.3            | Roll Patterning                                                 | 31   |

|   | 2.3.1          | Materials and manufacturing of a gravure roll                   |      |

|   | 2.3.2          | Improved photolithographic patterning                           |      |

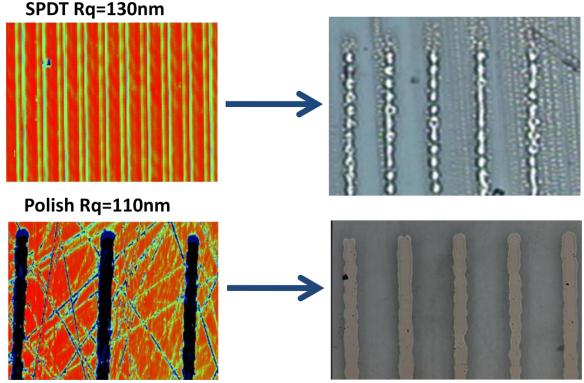

|   | 2.3.3          | Surface polishing and effects on wiping and pattern fidelity    |      |

|   | 2.4            | Summary                                                         |      |

| • | 2.5            | Works Cited                                                     |      |

| 3 |                | d Metal Lines                                                   |      |

|   | 3.1            | Performance criteria for metallic lines                         |      |

|   | 3.1.1          | Printed Circuit Boards                                          |      |

|   | 3.1.2<br>3.1.3 | Flexible Circuit Boards<br>Back-end interconnects               |      |

|   | 3.1.4          | Contacts to devices                                             |      |

|   | 3.2            | Types of metallic inks                                          | 41   |

|   | 3.3            | Roughness of printed metal films and lines                      |      |

|   | 3.3.1          | Roughness                                                       |      |

|   | 3.3.2          | Roughness of spun films                                         | . 48 |

|   | 3.3.3          | Roughness of printed lines                                      | . 52 |

|   | 3.4            | Nanoparticle Silver lines for interconnects and device contacts | 54   |

|   | 3.4.1          | Experimental                                                    |      |

|   | 3.4.2          | Discussion/Print Considerations                                 | . 57 |

|   | 3.4.3 | Results                                         | 58  |

|---|-------|-------------------------------------------------|-----|

|   | 3.4.4 |                                                 |     |

|   | 3.4.5 | 5                                               |     |

|   | 3.5   | Organometallic Silver lines for device contacts | 67  |

|   | 3.6   | Summary                                         |     |

|   | 3.7   | Works Cited                                     | 73  |

| 4 | Capac | citors                                          | 75  |

|   | 4.1   | Capacitor structure and role in ICs             | 75  |

|   | 4.2   | Dielectrics in Printed Electronics              | 77  |

|   | 4.3   | Gravure Printed Polymer Dielectrics             | 81  |

|   | 4.4   | Capacitors                                      | 83  |

|   | 4.5   | Improvement of Yield and Thickness Uniformity   | 86  |

|   | 4.6   | Conclusion                                      | 90  |

|   | 4.7   | Works Cited                                     | 92  |

| 5 | Gravu | are Printed Organic Thin Film Transistors       | 94  |

|   | 5.1   | The thin film transistor                        | 94  |

|   | 5.2   | pBTTT and other modern polymer semiconductors   | 96  |

|   | 5.3   | Model pBTTT TFTs on Silicon                     | 99  |

|   | 5.3.1 | ······································          |     |

|   | 5.3.2 |                                                 |     |

|   | 5.3.3 |                                                 |     |

|   | 5.3.4 | Ink-jet printed pBTTT                           | 111 |

|   | 5.4   | Fully Printed Devices                           | 113 |

|   | 5.4.1 | - · · · F · · · · F                             |     |

|   | 5.4.2 |                                                 |     |

|   | 5.5   | $f_T$ and performance                           | 125 |

|   | 5.6   | Conclusion                                      | 129 |

|   | 5.7   | Works Cited                                     | 129 |

| 6 | Outlo | ok and Conclusions                              | 132 |

# **1** Introduction

Electronics continue to grow as an integral part of our daily lives. Fueling this growth are advances in integrated circuits which become more powerful, smaller, and less expensive in every generation; and advances in electronic displays which make our interaction with electronics ever more pervasive and affordable. The rate at which we are adapting our social and personal practices to involve the use of electronics has begun to increase dramatically in the last few years as is evidenced by a shift in trajectories in the electronics industry from delivering ever faster and higher performance devices, to more portable, and less power-consuming devices. No better example of this can be found than in the cellular telephone market where Apple's iPhone has broken so many paradigms on the usability, practicality, portability, and power of an electronic device.

The iPhone and portable devices of its ilk have brought credence to the idea of "*Electronics Everywhere*" by allowing the user to bring an electronic device with them which can interact with almost every part of their life whether it be getting directions, finding food, meeting friends, or going to a movie. The ability of these devices to integrate into our lives is so good that some of their functions can be said to provide an augmented reality whereby the device is aware of our surroundings and can feed added information to us about almost anything of interest, from "How much cheaper can I get this box of cereal?" to "Who painted this piece of art?"

# **1.1** The potential of printed electronics

Printed electronics hopes to bring an even higher level of electronics everywhere by enabling devices that are as inexpensive as printed paper, as large as a billboard, and as flexible as a piece of plastic. None of these characteristics are feasible at present with conventional microelectronics, whether it be single crystal silicon integrated circuits, or amorphous silicon thin film transistor (TFT) displays. Though cost is universally a driver for any technology, enabling electronics to be made at the cost of printed paper would allow for the integration of electronics on nearly every product in existence. These electronics could provide some intelligence to a product making our lives better.

Take for example a carton of milk. Clearly, high expectations don't come to mind. However, if electronics became inexpensive enough to be integrated with the carton, a wide variety of features could be enabled. For example, the barcode on the carton of milk could be replaced with a radio frequency identification tag, which can wirelessly transmit information. If all items in the supermarket used RFID tags instead of barcodes a customer can load their cart up with food and simply walk out of the store picking up their receipt along the way without having to stop at a register. If an electronic display could be added to the carton of milk, the carton could provide real-time pricing to the consumer. This pricing could change as the carton of milk gets closer to its expiration date, giving an incentive for the customer to purchase it instead of digging through the rack for a newer carton, thus avoiding discarded milk. Further, a sensor could be integrated into the carton which can inform the consumer if the milk has gone bad. No more sour milk surprise in the morning!

Very large area electronics could allow for electronic billboards to be made, but perhaps more interestingly, could allow for rapid deployment of solar cells to help quench our thirst for energy. Flexible electronics would allow for "breakproof" devices. No more broken screens when a laptop is dropped.

Printed electronics means to achieve these goals of low cost, large area, and flexibility by eliminating some of the cost drivers in conventional electronics: vacuum deposition, subtractive processes, and photolithography. Instead, electronics are manufactured using printing processes as in

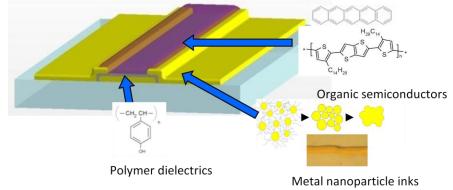

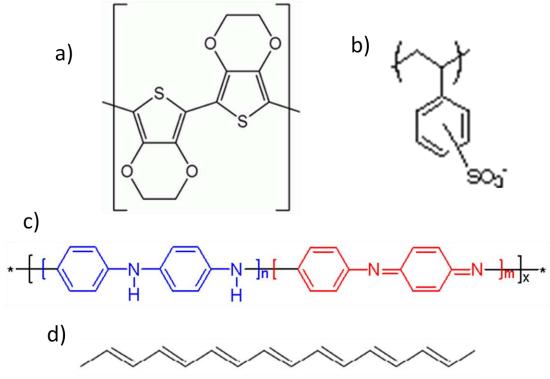

the graphic arts, but with the use of a series of functional materials which can be formulated into inks, and after printing, converted to metals, insulators, and semiconductors. The development of these materials has been a long way in the making, relying on developments in nanoparticle science, conductive polymers, organic semiconductors, and polymer dielectrics, and have allowed for the demonstration of solution processed solar cells, organic light emitting diodes, sensors, and thin film transistors as shown in Figure 1.1. Though these devices are of considerably lower performance than their vacuum deposited or crystalline inorganic counterparts, they offer the potential of being printed, and can thus be integrated into applications where no other technology can be.

Aside from the materials, a key component to making the goals of printed electronics a reality is the ability to deposit these materials, en masse, on inexpensive substrates. However, at this point most of the work in printed electronics has revolved around the use of ink-jet printing as a deposition method, and silicon and glass as substrates. Ink-jet provides a great research tool because it uses very small amounts of ink, is a digital process and thus allows for rapid prototyping of different patterns and structures, and has fairly low capital costs. However, it is a serial printing process which therefore results in a very low throughput. Though attempts to use massively scaled ink-jet printers with 1,000 or even 1,000,000 nozzles at a time could dramatically increase this throughput, those attempts have been met with reliability problems, and high cost.

## **1.2 Conventional Printing Methods**

Perhaps a better approach would be to use printing techniques that are already ubiquitous in large-scale manufacturing. These printing techniques rely on a rotary printing form that deposits an entire pattern of ink on a substrate in a single pass. Printing presses operate at high speeds as the substrate is generally fed from roll-to-roll in a continuous web.

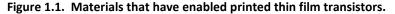

There are four main printing techniques that use a pattern master for image transfer: flexography, lithography, gravure, and screen printing. Of these techniques flexography, lithography, and gravure have been considered for use in printed electronics and are shown in Figure 1.2. Silk-screen, because it is exclusively a thick film process was not considered here, though it enjoys wide adoption in the manufacture of printed circuit boards.

Flexography is essentially a rubber stamp on a roll; of the techniques considered it operates most similarly to Gutenberg's original printing press where the pattern to be printed is raised out of the surface of the printing form. This raised surface then gets inked, and the ink is then transferred to the substrate. Flexography has potential as a laboratory printing technique because the rubber printing forms are relatively easy to manufacture. However, concerns with mechanical deformation of the printing form are of concern for printed electronics where feature sizes must be scaled, and controlled

as much as possible. Further the polymer printing form poses limitations on the type of inks that can be printed, as inks with organic solvents can easily cause swelling or deterioration of the form.

Figure 1.2. Conventional printing processes with inset photographs of a flexography roll (top left) and a gravure roll (bottom middle).

Lithography, specifically offset lithography, is one of the most widely used printing techniques, as it used to print the majority of newspapers and short-run periodicals in the world. It makes use of a printing form that is patterned with hydrophobic and hydrophilic regions. The printing form is dampened with water which adheres only on the hydrophobic regions, and then inked with a hydrophobic ink, which adheres only to the hydrophobic regions of the roll. This pattern of water and ink is then transferred to an intermediary offset roll, and then to the substrate where with paper substrates, the water prevents the ink from spreading as it is absorbed by the paper, providing good quality prints. For electronics, the use of two types of fluids to print one pattern poses unwanted constraints on the design of electronic inks, issues with cross-contamination could be difficult to control, and since most substrates for printed electronics are non-absorbent, the benefits of spreading control are minimal. Further offset litho makes use of two patterns transfers, one from the print master to offset roll, and one from the offset roll to the substrate. This extra transfer can lead to added loss of pattern fidelity which is undesirable.

The last printing technique discussed is gravure. Gravure, also known as rotogravure, is in some sense the inverse process of flexography. Here patterns are etched into the surface of the printing form, creating ink-holding wells which are filled when the entire roll gets coated in ink. A doctor blade then removes excess ink from the non-patterned areas, and the ink from the wells is transferred from to the substrate. Direct gravure provides the highest resolution and pattern fidelity of these techniques because it uses a metallic printing form which does not suffer from deformation or solvent swelling. Further, ink is transferred directly to the substrate, avoiding the need for a secondary transfer process. Because of the materials used in the printing form, gravure can withstand the highest printing speeds allowing for large numbers of prints in a short time. The downside however, is that gravure rolls are very expensive to pattern, and the patterning process is fairly slow making gravure less ideal for print jobs that vary a lot from day to day. Also, direct gravure is not amenable for printing on solid substrates as mating the printing form and the substrate is impractical, to overcome this, offset gravure must be utilized and a two-transfer method is used, reducing overall resolution.

## 1.3 Goals

In this work gravure has been chosen to develop printing processes for electronics. Though gravure is the most expensive of the techniques discussed, it is the highest resolution, fastest, and most compatible with a variety of materials. The goal in developing these printing processes is to bridge the gap between materials and methods used for ink-jet printing in the laboratory and the materials and methods required to print electronics at an industrial scale. There is little known about how conventional printing processes will perform in printed electronics, and there is potentially a large difference in the materials needed for printing with conventional processes versus ink-jet.

As will be shown, there are several technological challenges to enabling printed electronics with conventional printing presses. To begin with, a printing press suitable for new materials development and high resolution printing has not, until now, been developed. Here, such a press is designed, fabricated, and demonstrated. Further, the feature sizes used in graphic arts have not been sufficiently scaled to enable high density, and good performance electronic devices. Here the scalability of gravure for printing metallic lines and dielectrics is shown, giving an indication of the potential to scaling with this technique. Finally, integration issues of multi-level thin film devices have not been well understood, making it difficult to know what printing techniques are best suited for. A printing process for organic thin film transistors has been developed, carefully studying process modules for metals, dielectrics, and insulators separately, and exploring the compatibility between each process to enable high performance devices.

#### 1.4 Background

This is not the first attempt at using gravure for purposes of electronics. One of the earliest reports on this was by Mizuno and Okazaki at Dai Nippon Printing, where they demonstrate the use of gravure offset to print the black matrix for color filters in active matrix displays [1]. Soon after, an offset gravure printed resist process was developed for manufacturing amorphous silicon (a-Si:H) TFTs [2]. Both of these reports used an etched glass intaglio to transfer patterns to the offset roller, and achieved feature sizes as small as  $10 \,\mu$ m.

In 2002 a report on gravure printing functional materials for electronics was made by Gamota where gold nanoparticle inks, polymer dielectrics, and organic semiconductors were combined to fabricate thin film transistors, again using a gravure offset technique [3]. Here minimum feature sizes where 50 µm and due to poor registration capabilities devices used non-overlapping contacts yielding fairly low performance. Soon after, Pudas began studying the ink-transfer process for metallic inks on

ceramic substrates [4] using gravure offset, and continued this work demonstrating printed antennas on ceramic substrates[5] and plastic substrates with feature sizes as small as 20  $\mu$ m [6].

As noted, these early demonstrations used gravure offset instead of direct gravure yet obtained reasonably small patterns on mostly non-flexible substrates as a good indication of the scalability of the gravure printing process.

Direct gravure was demonstrated for the fabrication of organic light emitting diodes in 2005 by Tuomikoski [7] and more recently for the deposition of indium tin oxide nanoparticles for transparent electrodes [8].

During the course of research for this work, two other groups have demonstrated the use of direct gravure printing for electronics: the group of Cho in Korea [9], and the group of Hahn in Germany [10]. In their work, these groups demonstrate thin film transistors on flexible substrates using gravure and a combination of other printing techniques. Though they demonstrate some of the earliest circuits fabricated using mass-printing techniques, their performance is somewhat hindered by large feature sizes.

This work is complementary in the fact that gravure printed organic thin film transistors are also fabricated as part of the goal of demonstrating gravure's feasibility for printed electronics, but adds to that with a thorough discussion on the development of a high-resolution gravure printer, and the careful development of high-quality patterned thin film materials that enable devices with significantly better performance than previously demonstrated.

# 1.5 Organization

Thus this thesis is organized in the following manner: Chapter 2 will discuss the gravure printing technique in detail and describe the design of a high-resolution table-top gravure printer suitable for laboratory scale research on printed electronics, as well as the patterning of fine features on gravure cylinders. Chapter 3 will then discuss the issues in printing metallic traces, describing the needs and requirements for these traces in printed circuit boards, interconnects, and contacts to semiconductor devices. Here gravure printing of nanoparticle and organometallic inks will be described along with an understanding of the mechanics of line formation and the scalability of gravure features. Chapter 4 will then discuss gravure printed dielectrics, and the integration of these technologies to make organic thin film capacitors. Finally, Chapter 5 will describe the integration of these technologies to make structures.

### 1.6 Works Cited

[1] K. Mizuno, J. J.A.P., Vol. 30, No. 11B (1991) 3313-3317.,

[2] Y. Mikami, IEEE Trans. Elec. Dev., 41 (1994) 306-314.,

[3] D. Gamota, Mat. Res. Soc. Symp. Proc. Vol. 725 (2002) P6.3.1-P6.3.6.,

[4] Pudas, Marko, Hagberg, Juha and Leppavüori, Sepo., "The Absorption Ink Transfer Mechanism of Gravure Offset Printing for Electronic Circuitry." s.l.: IEEE Transactions on Electronics Packaging Manufacturing, 2002, Issue 4, Vol. 25, pp. 335-343.

[5] M. Pudas, J. Eur. Cer. Soc., 24 (2004) 2943–2950.,

[6] M. Pudas, Prog. In Org. Coat., 54 (2005) 310-316.,

[7] Tuomikoski, M., et al., "Gravure printed optoelectronic thin films for flexible polymer LEDs and microsystems." s.l. : IEEE/LEOS International Conference on Optical MEMS and their Applications, 1-4 August, 2005. pp. 141-142.

[8] Puetz, Joerg and Aegerter, Michel., "Direct gravure printing of indium tin oxide nanoparticle patterns on polymer foils." s.l. : Thin Solid Films, 2008. pp. 4495-4501. doi:10.1016/j.tsf.2007.05.086.

[9] Cho, Gyoujin., "R2R Printed TFTs and RFID Tags: Demonstration of All Printed 13.56 MHz Operated 1 Bit RFID Tags." Hsinchu, Taiwan : International Symposium on Flexible Electronics and Displays, November 13-14, 2008.

[10] Huelber, A.C., "Ring oscillator fabricated completely by means of mass-printing technologies." s.l. : Organic Electronics, 2007, Vol. 8, pp. 480-486.

# 2 Gravure

# 2.1 Introduction

Printing presses have had an enormous impact on our ability to share and communicate ideas, ever since Gutenberg's first inventions. Today, the vast majority of print material is produced on roll-type printing presses using a variety of techniques including lithography, offset printing, flexography and gravure. Of these techniques, gravure is the least complex, and offers the highest resolution. This has made it an attractive candidate for use in manufacturing printed electronics, where resolution requirements are much higher than those required for publication prints. Using a high throughput process to manufacture integrated circuits has the potential of providing ultra low cost electronics that can have a vast number of new applications, such as electronic paper, smart labels and embedded sensors. All of which aim at providing us with a higher quality of life.

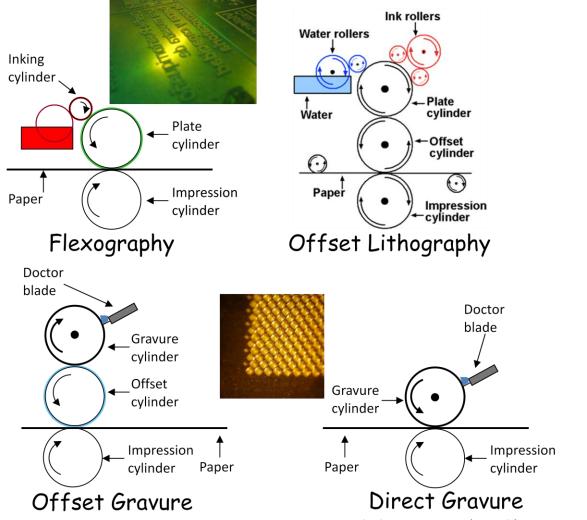

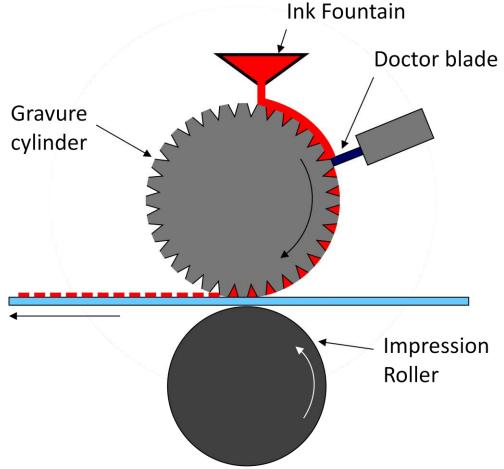

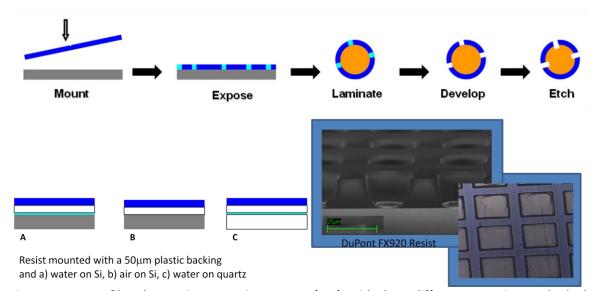

Figure 2.1. The gravure printing process.

## 2.1.1 Gravure printing fundamentals

The gravure printing process uses a metallic roll, also known as the gravure roll, in which the images to be printed have been etched or engraved into its surface. As shown in Figure 2.1, these patterns are filled with ink, and any excess is subsequently wiped off using a blade which is tightly pressed against the roll, the doctor blade. The inked and wiped surface of the roll then comes into

contact with the substrate, which is pressed against the gravure roll with the use of an imprint roll, and the ink is transferred from the rolls' patterns to the substrate, completing the print.

The wiping process is critical to the quality of a print as the doctor blade must remove all ink from the non-patterned areas of the roll. This places a stringent requirement on the quality of the surface of the roll, its hardness, and shape uniformity. It also places hard requirements on the quality of the doctor blade, and the pressure it applies to the surface.

To satisfy these requirements, gravure rolls are made out of hard material such as chrome coated copper, or in special cases an industrial ceramic. The vast majority of rolls are made of a steel or aluminum core, with a layer of electroplated copper, which can be easily machined to provide overall shape uniformity, and patterned to define the printed shapes, then coated with a hard chromium layer which provides good wear resistance against the friction of the doctor blade and substrate.

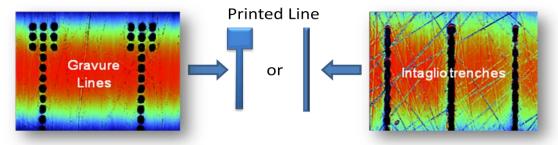

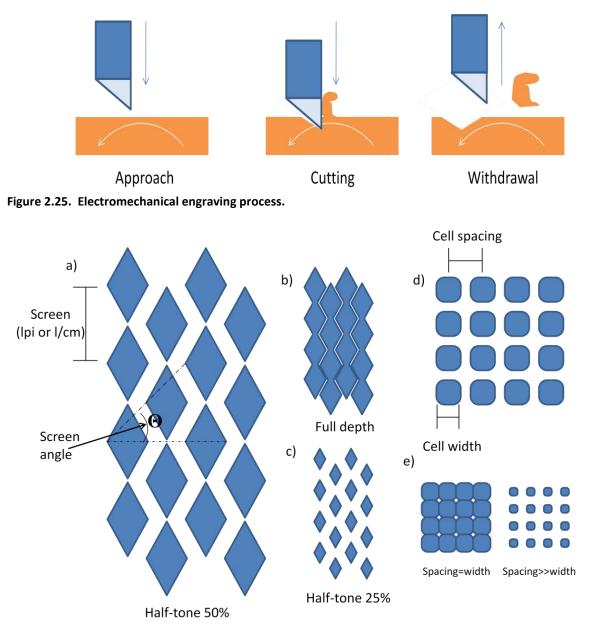

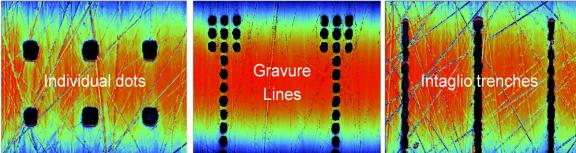

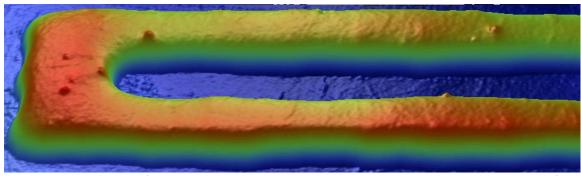

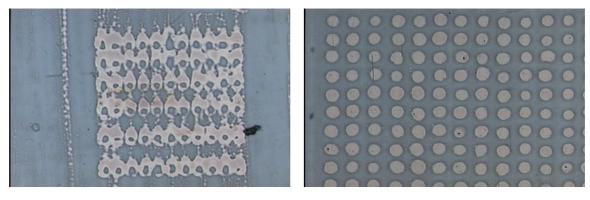

Two approaches can be taken to pattern an image onto a gravure roll, and defines whether the printing technique is considered intaglio or gravure. In intaglio, the image to be printed is etched or engraved directly into the roll. For example, if a line is to be printed, then a thin channel of some depth and width corresponding to the width of the line is patterned into the roll. Likewise, if a solid-filled square is to be printed, then a square of the desired size is etched into the roll. In gravure, images are sampled, or pixilated on a specific grid, and then this grid is etched or engraved into the roll. Each point on the grid corresponds to a single patterned well, or gravure cell, and sufficient space to allow for a cell wall that prevents cells from merging into each other. For images that must have a solid fill, the gravure cell occupies a large portion of the grid. The ink deposited from these wells will spread to make a uniform film. Figure 2.2, shows images of both gravure and intaglio patterns on a roll.

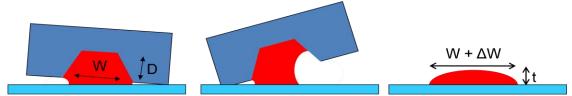

Intaglio can transfer more ink per unit area than gravure, and can make smoother line edges, but it suffers from a variety of drawbacks. Because intaglio patterns are of a single well, controlling the amount of ink deposited is difficult as it scales with the size of the pattern. The lack of a cell wall causes a deflection in the doctor blade when crossing large patterned areas, reducing its ability to wipe the non-image areas. Further, fluid inside intaglio patterns can redistribute itself during the print, causing print inconsistencies. Thus, intaglio has been largely replaced by gravure.

In gravure, the ink is metered by the size of the individual cells. Large area and small area patterns alike can be printed with the same thickness of ink because of this metering. Further tonal differences in an image can be easily implemented by modulating the size of the wells, thus reducing the thickness of ink deposited, or even pixelating the area to provide near-white tones. A drawback, however, is that individual cells tend to print as ragged edges along lines, reducing the quality of fine-line artwork. In printed electronics much of the patterns printed follow under the category of fine-line artwork, and thus we have chosen to study both intaglio and gravure printed patterns. In practice both types of patterns can be made on a single roll taking advantage of each cell type were most appropriate.

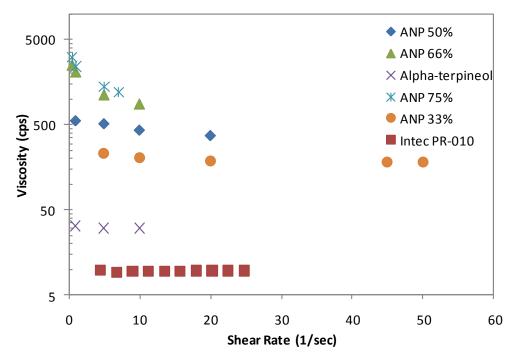

The inks used in gravure can vary quite a bit in formulation and viscosity. Solvent based inks were originally the most popular in the graphic arts, but have fallen out of favor due to environmental concerns. Now most inks for printed media are water based. UV curable inks are also popular because they can be formulated with a small amount of solvents and can provide uniform thick films. Ink viscosities can range from 10 to 500 centiPoise (cP) [1]. Lower viscosity inks are more common in print media such as magazines and books, while higher viscosity inks are found in packaging.

Commercial gravure printing presses are large machines that utilize gravure rolls that can be as small as 20 cm wide and 5 cm in diameter, and as big as 3 meters wide and 1.5 meters in diameter. A complete printing press includes a number of gravure stations, each to print a specific color, ink drying or curing stations between each gravure printing station, mechanics for active registration, and wind and unwind for a continuous substrate, or less commonly, send and receive stations for a sheet fed system. All together these presses can be as long as 70 meters, and require an entire warehouse to operate.

Thanks to the good mechanical and thermal stability of the gravure roll, these presses can operate at speeds as high as 2,000 m/min, which make gravure, by far the fastest printing technique in use. Due to the high cost of patterning gravure rolls, and speed of the printing systems, gravure is only economically feasible for very large print runs in excess of 500,000 copies.

#### 2.1.2 Table-Top Proof Presses and Laboratory Presses

For laboratory use, such as is needed in ink and product development in the graphic arts, two types of presses exist: table-top proof presses and laboratory presses. Because of their smaller size and cost, these presses were considered for use in developing processes for printed electronics.

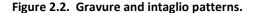

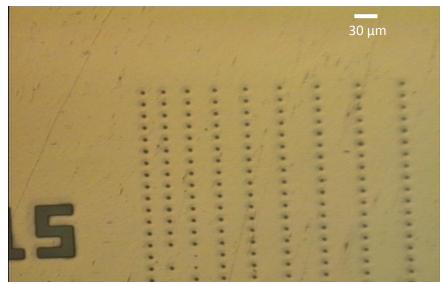

Figure 2.3. Two proof presses. A K printing proofer (left) and a IGT G1-5 (right).

Proof presses are small machines that are ideal for ink development, and rapid print testing. Two notable machines are a K Printing Proofer by RK Print Coat Instruments, and the G1-5 by IGT, both shown in Figure 2.3. The K Printing Proofer uses a flat ballard shell as the printing form. A ballard shell is a product of a common way of patterning gravure rolls and can thus be easily exchanged with custom patterns by the user. The substrate on this system is wrapped around the imprint roller, and placed on a frame that uses micrometer control to adjust the pressure of the imprint roller, and holds the doctor blade just fore of the substrate. The print is made by moving this frame along the ballard shell, such that the doctor blade inks and wipes the shell before the substrate rolls over it. The IGT G1-5, uses small

custom-made gravure rolls, and uses a flat rubber sheet as an imprint roller, with a harder roller behind it that drives the substrate under the roll during the print. Printing pressure is controlled on this printer by a counterweight system.

These proof presses are quite inexpensive, and utilize very small amounts of ink (<1mL) per print, which is ideal for printing high-value experimental materials. However, they suffer a few drawbacks. Because of the small size of the printing forms and substrates, these printers only produce results from the few rotations of the gravure roll. In these early stages, ink may have not fully filled all gravure cells, and the printing process may have not reached a steady state condition. Further, these printers are seriously limited by the speed at which they can print. Finally, there are no provisions for registration and thus these printers are only useful for single-layer prints.

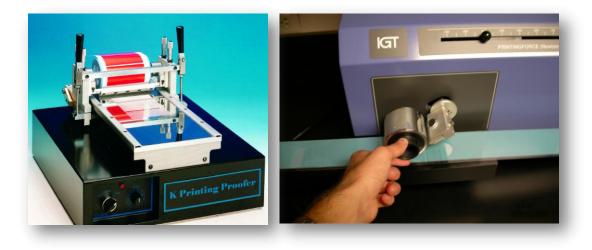

So called laboratory presses, are much larger machines, which much more closely resemble industrial printing presses. These are web-fed systems, which can have multiple printing units, inline drying and automatic registration feedback Figure 2.4. What distinguishes them from their larger counterparts is mainly the size of the printing form and thus the amount of ink required to operate them. Printing forms on laboratory presses can be as narrow as 10 cm and as wide as 50 cm. Because they are web fed systems, they print continuously and thus achieve steady state printing conditions and allow for many printing variables to be changed on the fly. The problem, however, is that these machines are still quite large for laboratory scale printed electronics, and require at minimum hundreds of milliliters of ink per print.

Figure 2.4. A laboratory scale gravure printing press with two print units, and automatic registration capability.

Neither of these types of presses provides all of the features of a full size gravure press, and neither satisfies the requirement of using very small amounts of ink and allowing for high-precision multi-layer printing. Because of this, a custom laboratory press was built.

## 2.2 A Laboratory Scale Gravure Printer for Printed Electronics

The field of printed electronics is still in development, and thus, the majority of printing work is done at a laboratory level, most commonly with ink-jet printers that provide enormous flexibility and small material volume requirements. However, ink-jet is not a technology that can easily provide for high volume manufacturing, and inks developed for ink-jet do not easily transfer to high volume rolltype processes.

In an ideal case, a gravure printing press for printed electronics would combine the small formfactor and low ink usage of a proof press, with the multi-layer registration capability and continuous output of a laboratory press. In terms of resolution and registration, however, such a printer should not be compared to other gravure printers, but to machines currently used for printed electronics and largearea microelectronics, ink-jet printers and photolithography tools, respectively.

Ink-jet printers are by far the most widely used in printed electronics. They benefit from being a digital process, giving a lot of flexibility in creating new printing patterns and allowing for real-time pattern changes which are practical for printing on plastic substrates which suffer from large amounts of strain during thermal processing. Ink-jet printers can also print a wide variety of inks including organic and aqueous solvent based inks, UV curable inks, and even molten solders. State-of-the art ink-jet printers use high-precision air bearing stages which can have sub-micron position repeatability and linearity. Ink can be deposited in volumes which range from 100pL to 1pL using widely available micromachined printing cartridges that can print features that range from 100's of  $\mu$ m to as low as 20  $\mu$ m. Improvements in resolution have been demonstrated by the use of electrohydrodynamic jetting which can deposit femtoliter drop volumes, though these systems are still in early development [2][3]. Despite good machine accuracy and small drop volumes, ink-jet suffers from a large variability in drop directionality, limiting its position accuracy to 5 – 10  $\mu$ m.

For large-area electronics, the main products are a-Si:H TFTs for liquid crystal displays, which are manufactured by photolithography. These photolithography tools are 1:1 projection steppers, which have a registration capability of 0.5  $\mu$ m and a can pattern features as small as 2.5  $\mu$ m over areas as large as 2.5m x 3m.

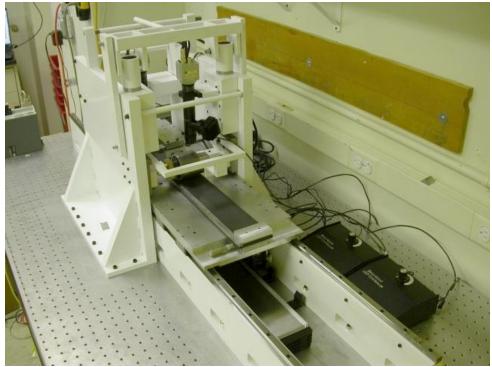

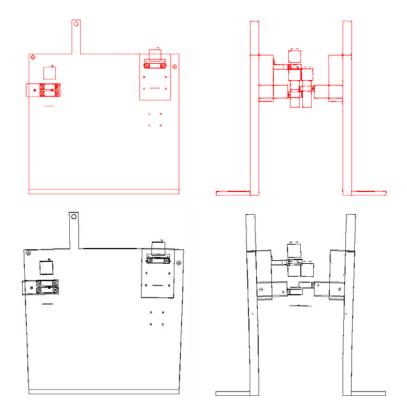

Figure 2.5: A bench top, sheet-fed, high-resolution gravure printing system with a 5cm printing form.

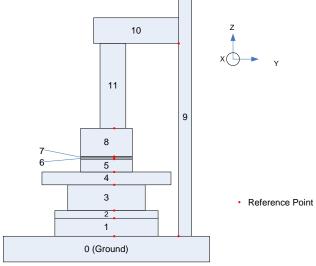

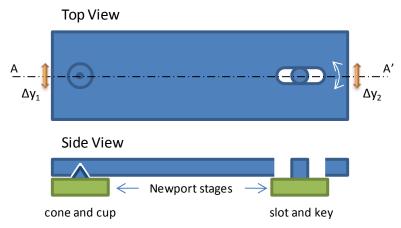

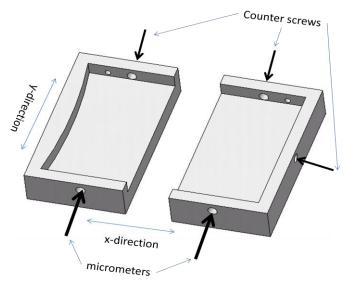

Thus we designed a small bench-top gravure printing system (Figure 2.5) which would hopefully have registration capabilities of 5  $\mu$ m, use less than 1mL of ink per print, and allow for patterns to be printed with better resolution than state-of-the art ink-jet. The machine uses gravure rolls that are 5cm wide and 5-6cm in diameter which are backward compatible with rolls designed for the IGT G1-5, it operates as a sheet fed machine and can print on substrates as long as 70cm and 6cm wide with a 60cmx5cm printing area. Registration is enabled using a 3 camera system and custom software that aids

the user in aligning fiducial marks on the roll with those on the substrate. To improve registration and eliminate errors due to environmental vibrations the system was mounted on an air-cushion table. It was built with a heavy steel frame to avoid any mechanical deflections and minimize the effects of thermal expansion. A Parker-Hafnin 404LXR linear motor provides the driving force to move the substrate through the printing process at speeds up to 2 m/s.

To realize good registration accuracy, principles of precision machine design (error mapping and error budget) were used to describe and analyze the registration capability of this printing machine in order to determine and quantify the major sources of alignment error, and determine possible solutions to these errors.

A description of the alignment process will be given followed by an experimental measurement of its printing errors. With this in mind, we take on the task of building an error map and error budget for the machine [4]. We first determine the thermal errors from a coupled thermal-structural analysis of the machine using finite element simulations, we then build kinematic model of the machine using homogeneous transformation matrices (HTMs). Using these HTMs we combine the thermal errors with errors coming from a variety of other sources such as the motors and stages which move the machine components during a print, and we calculate the total expected alignment error of the machine, using HTMs to quantify the impact of each error source. Finally, we propose and implement series of improvements to the printing system, using the knowledge gleaned from our analysis.

#### 2.2.1 Alignment Process and Sources of Error

The gravure printing system shown in Figure 2.5 is a sheet fed system which operates as follows: A plastic sheet (a.k.a. substrate) is mounted on the black sample holder with a rubber backing using two clamps. The sample holder is then mounted onto a larger base plate (a.k.a. top plate) and two high precision double-row ball bearing Newport stages through a clamp. The substrate is then aligned to the gravure roll using three Navitar microscopes, a small piece of alignment software, the aforementioned Newport stages to provide motion in the y and theta directions, as well as a Parker-Hafnin linear motor which moves the stage in the printing direction x. Once the alignment has been done with the roll sitting slightly above the substrate, it is lowered onto the substrate and loaded with a spring-based compression system to a weight of approximately 10kg and the alignment is re-checked. If the alignment is good, a doctor blade is placed against the roll, the roll is inked, then the substrate is moved under the roll (which rotates) using the Parker linear motor to transfer the ink from the roll to the substrate.

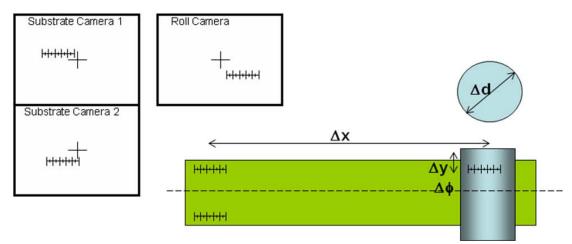

The alignment routine can be described using Figure 2.6. The substrate is placed under the roll such that the alignment marks on the substrate are a distance x away from the axis of the roll. This distance should be 1.5 times the circumference of the roll, or  $3/2\pi d$ , where d is the diameter of the roll. This will ensure that the alignment mark, which is seen at the top of the roll through the roll camera, will roll directly on top of the alignment marks shown in substrate camera 1. A second alignment mark on the roll will print over the mark shown in camera 2, as long as the relative rotation of the substrate is adjusted by properly relating alignment marks on substrate camera 1 to substrate camera 2. Thus, the distance between the substrate cameras and the roll camera must also be 1.5 times the circumference of the roll to ensure the alignment marks are centered exactly in the camera window. However, since the diameter of each roll is slightly different, there is a deviation of roll diameter  $\Delta d$ , which leads to a need to offset the alignment marks by a distance  $\Delta x = 3/2\pi\Delta d$ . The pattern on the roll may also not be aligned exactly in y and theta direction between roll and roll. We thus use a software program to keep calibrated values of  $\Delta d$  and theta, and thus corresponding values of  $\Delta x$  and  $\Delta y$  required to align a variety of different rolls to each other.

Figure 2.6: Diagram of the alignment routine. Three cameras are used to align the substrate to the printing roll. The cameras are spaced such that when the alignment mark is both visible on the roll camera, as well as the substrate cameras, with appropriate spacing. The micrograph shows an example of a printed alignment mark.

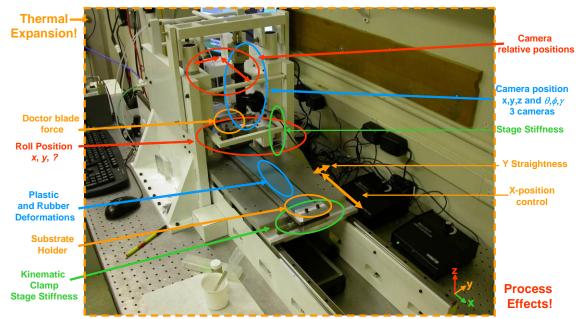

The alignment system is however, susceptible to a wide variety of other errors, including but not limited to the following (Figure 2.7).

- Thermal expansion of the system as the laboratory or local machine temperatures change with time, and use.

- The relative position of the cameras affected by either mechanical disturbances, or thermal expansion.

- The actual position with which the roll is mounted in the machine, since we assume in our alignment routine that the roll is positioned in the same exact position every time, and more specifically that theta errors come only from the theta offset of the patter on the roll, and not the roll position itself.

- The ability of the substrate holder clamp to hold the substrate holder in place, without it moving during the print.

- Deformations of the flexible substrate, and rubber backing during the printing process, which may lead to stretching of the printed pattern and slip between roll and substrate.

- Stiffness and position control of the Newport stages, which are used to move the substrate in y and theta directions, as well as the stiffness and position control of the Newport stages that move the roll up and down into printing position.

- Stiffness and straightness of the Parker linear motor that moves the substrate during the print.

- The movement of the roll caused by the pressure of the doctor blade.

- Effects of the alignment procedure, and printing process, including care of handling components, order in which parts are assembled and particulars of the alignment sequence.

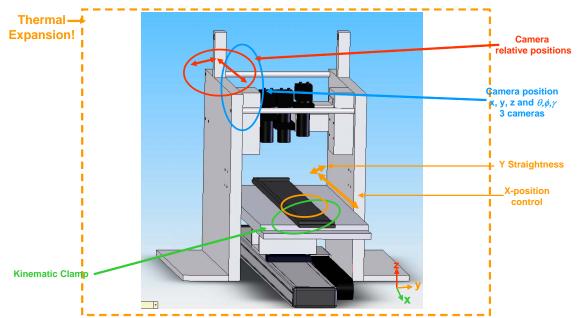

It is clear that modeling every source of error would be a difficult undertaking. Thus in order to reduce the complexity and make our calculations tractable, we selected what we believed to be the prominent sources of error and made a computer model of the printing system that can then be later used with appropriate finite element programs to model the total system error. The main sources of errors and computer generated system model are shown in Figure 2.8. We selected thermal errors, camera positions, repeatability of the substrate holder clamp and position accuracy of the substrate in x and y directions as our preliminary investigations led us to believe these are errors with large possible deviations on the order of microns or more.

Figure 2.7: Gravure printing system and a range of possible sources of error.

Figure 2.8: Computer model of gravure printing system and predicted major sources of error.

### 2.2.2 Experimental Position Repeatability and Alignment Accuracy

As built, this gravure printing system was intended to afford up to  $5\mu$ m alignment accuracy. However, we quickly determined that the practical alignment accuracy of the machine was, in fact, much worse. In order to isolate the major sources of error a few repeatability experiments were carried out on the machine. Using an electronic Mitutoyo indicator with a  $1\mu$ m resolution, we quickly assessed that a major source of error came from positional repeatability of the substrate. This could be due to the repeatability of the substrate holder clamp, which was designed to couple the substrate holder to the Newport stages on the base plate, while still affording movement of the substrate holder in y and theta directions. It could also be due to the repeatability of the parker stage, which should move the substrate straight under the roller and back to the same position after the print.

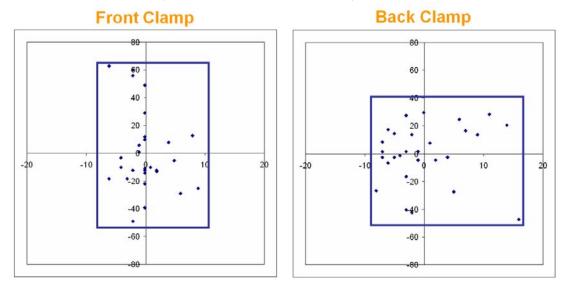

### 2.2.2.1 Substrate holder Clamp Repeatability

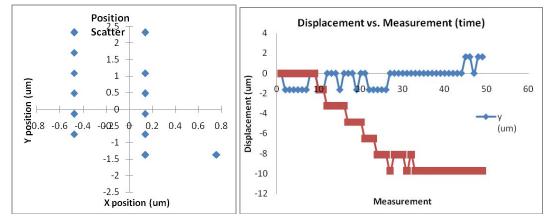

In order to assess the repeatability of the substrate holder clamp, the substrate was placed on the base plate and clamp, and its position in the x and y direction was measured with the electronic indicator. The substrate holder was then removed and the process repeated 50 times, taking measurements in x and y at both extremes of the substrate holder, centered about the contact point of each clamp (one at the front of the substrate holder, and one at the back). The data collected is presented in Figure 2.9. Clearly, repeatability for both clamps is worse than 5 $\mu$ m, especially in the y direction where the error is ±30 $\mu$ m for the front clamp and ±20 $\mu$ m for the back clamp.

Figure 2.9: Position repeatability of substrate holder clamps. For the front clamp  $\Delta x=\pm 5\mu m$ ,  $\Delta y=\pm 30\mu m$ , for the back clamp  $\Delta x=\pm 7\mu m$ ,  $\Delta y=\pm 20\mu m$ .

#### 2.2.2.2 Base Plate Repeatability

We also tested the repeatability of the base plate (onto which the substrate holder is placed) and parker motor using a similar technique. We mounted a small photo-lithographically patterned silicon wafer onto the sample holder using a double sided 3M brand tape, and moved the stage back and forth 500mm 50 times measuring the position of a small alignment mark on the wafer, in the field of view of the camera.

The resolution of the camera was calibrated to be  $0.62\mu$ m/pixel with an 860×640 pixel display. We used an onscreen cursor with a pixel position-tracking program to align a crosshair cursor to the center of a crosshair alignment mark that was patterned onto the wafer with a 5um line width. This allowed for easy centering as the eye can easily catch the symmetry of light shining on the dark cursor crosshair from the shiny gold alignment mark.

Surprisingly, after measuring the position of the crosshair after 500mm back-and-forth movements using a velocity of 20cm/s and an acceleration of 40 m/s<sup>2</sup>, we found that the positional error was only  $\pm 0.36 \mu$ m in the y-direction (perpendicular to the direction of motion) and  $\pm 1.63 \mu$ m along the x-direction, the direction of motion. The two graphs presented below indicate the there is indeed more control in the y direction that in the x (Figure 2.10) but even more importantly, there seems to be a

systematic deviation in x-position as the number of measurements progresses. This is presumably because the encoder on the Parker stage may miss a measurement at some common interval. This systematic deviation was only seen for high-speed motions of 20 cm/s.

Figure 2.10: Scatter plot of x and y repeatability of base plate position (left), and x and y position vs. time (right). It can be seen that the machine shows only a small amount of creep over time.

#### 2.2.2.3 Print Alignment Errors

If errors in the substrate position were the only sources of error, summing the errors from the substrate holder clamp and base plate positions alone would give a total error shown in equation (1) and (2) where  $\varepsilon_v$  and  $\varepsilon_v$  are the standard deviations of the position.

$$\varepsilon_x = \sqrt{\varepsilon_{x-clamp}^2 + \varepsilon_{x-base}^2} = 3.99 \mu m \tag{1}$$

$$\varepsilon_{y} = \sqrt{\varepsilon_{y-clamp}^{2} + \varepsilon_{y-base}^{2}} = 28.63 \mu m$$

(2)

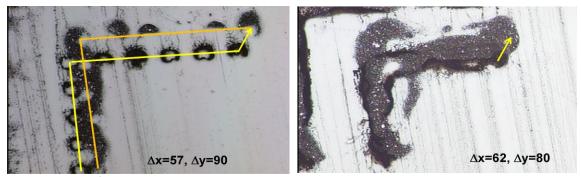

However, in practice the error is still much greater than this. We made a series of eight prints using two types of gravure inks. One conductive carbon ink (DuPont 5069) and one silver flake ink (DuPont 5067). The carbon conductive ink was printed on 8 blank polyester substrates (DuPont Melinex ST505), and left to dry over night. After drying, the substrates were aligned to the same roll used to print the carbon ink using the alignment procedure described above and a silver ink was printed. The use of these two inks provided good contrast between the reflective silver ink and the black carbon ink so that alignment errors can be easily detected in an optical microscope as shown in Figure 2.11. Unfortunately, the alignment were measured on the right alignment mark, which may be a result of the fact that the shape of the alignment mark on the right is different from that on the left, which may provide with a better reference with which to measure the alignment error.

Figure 2.11: Results of a two-layer print with carbon conductive ink as the bottom layer and silver conductive ink as the top layer. The orange and yellow lines on the left image help distinguish the two alignment marks of interest.

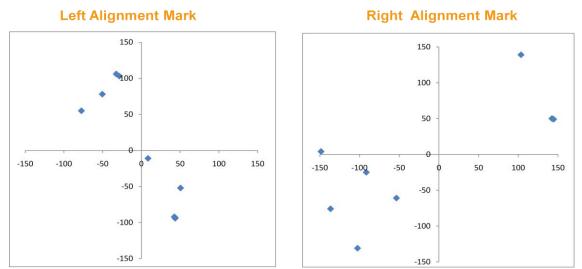

Figure 2.12: Scatter plot of alignment errors for 8 different two-layer prints. The left plot shows alignment errors measured on the left alignment mark and the right plot shows errors measured on the right alignment mark. It should be noted that the shape of the alignment mark itself could lead to measurement errors.

It is thus clear that not only does the stage position contribute a considerable component of misalignment but also there are other components that also contribute to the error. We thus proceed to analyze other sources of error in the machine using finite element modeling and combine them with homogeneous transformation matrices.

#### 2.2.3 Coupled Thermal Structural Analysis

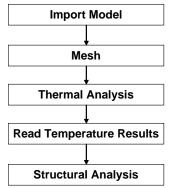

Coupled thermal-structural analysis is a sequentially coupled physics analysis that uses finiteelement methods to model the effects of heat on the shape of a material or object. Using a finite element method for the coupled analysis allows for an accurate representation of how thermal variation will affect the shape of the printer. Of special concern is how this affects the position and orientation of the alignment cameras with respect to the substrate and the gravure roll.

Steps involved in performing such analysis are outlined in Figure 2.13. A 3-D model of the gravure printer was build using SolidWorks. This model was then imported into Ansys where it was meshed, and environments were set up to execute the sequential thermal – structural analysis.

Figure 2.13: Steps in coupled thermal structural analysis

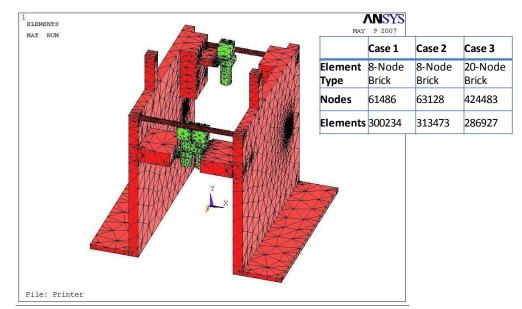

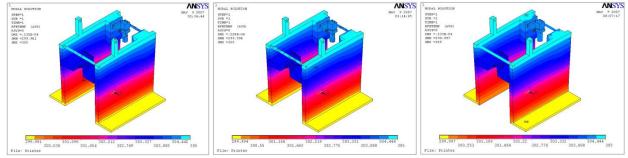

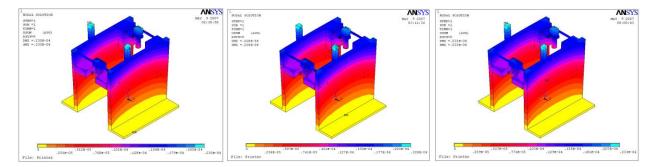

Figure 2.14 shows the 3-D model which was imported into ANSYS. This 3-D model was meshed with 3 different grid resolutions as shown in Figure 2.15. Three mesh grids were used to eliminate the possibility of errors caused by the discretization of the problem. The thermal environment was set up such that the air-cushion table for the printer was considered as a heat sink set at 300° K and the environment temperature was then increased to 305° K (an average temperature difference seen in day to day operation of the machine) to observe how this affects the temperature of the machine, and thus its structure. Output from the thermal analysis is shown in Figure 2.16 for each of the three meshed structured. The top of the machine is affected most by a temperature change as the table provides more thermal stability to the bottom of the structure where heat can be easily conducted out. Results of the thermal analysis were used as parameters for the structural analysis, and the resulting position errors for the alignment cameras were measured. Results for this analysis are shown in Figure 2.17 and Figure 2.18, where a 100x magnification of the distortion effects show how the camera positions move due to the thermal change.

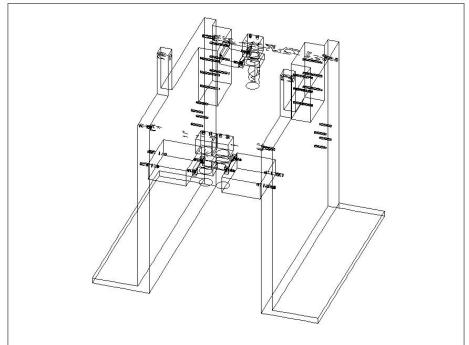

Figure 2.14. Imported 3-D model of the gravure printing system.

Figure 2.15. Meshed 3-D model of gravure printer. 3 Mesh grids (inset) were used to determine the accuracy of the model.

Figure 2.16. Thermal analysis results for each of the three mesh grids described in Figure 2.15.

Figure 2.17. Structural analysis results for the three mesh grids described in Figure 2.15.

Figure 2.18. Lateral and front view of gravure printer after 5° C temperature change (top) and model of same structure with 100x magnification of distortion effects (bottom) to elucidate the nature of the distortion.

#### 2.2.4 HTM Analysis

The output from the coupled thermal-structural finite element analysis was used to perform an HTM analysis of the printing system. The following section gives the details of the different components of the HTM analysis as well as the theoretical error values computed from the analysis.

Homogeneous transformation matrices are used to relate the spatial relationship between two bodies [4]. Using a matrix method allows for the spatial relationship between many bodies to be easily calculated, and changes to any individual objects position to be easily changed and propagated through the system. In order to relate two objects in a three dimensional space a 4x4 matrix is required. A transformation matrix that relates an object with coordinate system N in a reference frame R is written as

${}^{R}T_{N} = \begin{pmatrix} O_{ix} & O_{iy} & O_{iz} & d_{x} \\ O_{jx} & O_{jy} & O_{jz} & d_{y} \\ O_{kx} & O_{ky} & O_{kz} & d_{z} \\ 0 & 0 & 0 & d_{s} \end{pmatrix}.$

Here  $O_{ix}$ ,  $O_{iy}$ ,  $O_{iz}$ , etc., terms are the direction unit vectors i, j, k representing the orientation of the objects coordinate system with respect to the reference frame, and  $d_x$ ,  $d_y$ ,  $d_z$ , and  $d_s$  are the displacements along the x, y, z, direction and the scale factor.

To translate position coordinates in the N frame to the R frame, the transformation matrix is simply multiplied with the coordinate frame N to provide a position in the frame R

$$\begin{pmatrix} x_R \\ y_R \\ z_R \\ 1 \end{pmatrix} = {}^{R}T_N \begin{pmatrix} x_N \\ y_N \\ z_N \\ 1 \end{pmatrix}.$$

Using this method, the transformation matrices can be multiplied to relate the position of one object to another, through any number of intermediary objects or frames

$${}^{n}T_{1} = \prod_{m=1}^{n} {}^{m-1}T_{m}$$

#### 2.2.4.1 Components

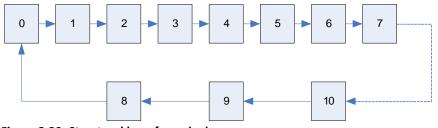

There are a total of three cameras in the printer system, and for each of them we have a HTM system to analyze its alignment error. Camera 1 and 2 are focused on the substrate as shown in Figure 2.6, and camera 3 is used to look at the roll. In the following section, we discuss the details of the HTMs for one camera alone (Camera 1), as the HTMs for the other two cameras are almost the same. However, the HTM for the third camera that looks at the roll has one more component in its structural loop (the roll).

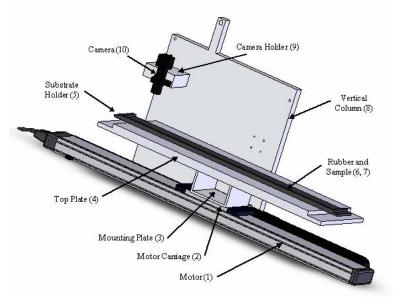

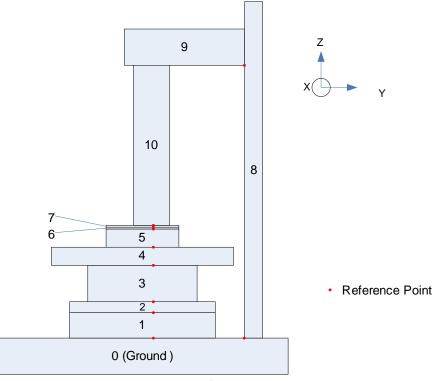

The main components of the analysis as shown in Figure 2.19 are a Parker-Hafnin linear motor with a 1 $\mu$ m encoder resolution (1), which is attached with a mounting place (3) via the motor carriage (2). The mounting plate drives horizontally the 25.4mm aluminum top plate (4), onto which a substrate holder (5) is fixed via a substrate holder clamp. A 1mm thick rubber layer (6) is attached to the top of substrate holder. The sample (7) is then loaded on the rubber layer. The position of the sample is adjusted using the micrometer stage and the linear motor by monitoring the sample position through the camera (10), which is attached to a steel vertical column (8) through a steel camera holder (9).

Figure 2.19: Components of the printer system

The actual system is considerably more complicated, but it is assumed that these components do not interfere with the positional accuracy of the stage and the positional accuracy of the sample in the stage reference and the camera reference. For example, the printer has a second set of bearings that are designed to take the vertical load from a roller, which presses down onto the sample, in the z-

direction. Since we are concerned only with x and y displacements for this analysis these components are orthogonal, and thus do not interfere. The structural loop for this camera is shown in Figure 2.20.

Figure 2.20: Structural loop for a single camera.

Figure 2.21 schematically shows the coordinate system and the origins (reference points) for each component in the structural loop.

Figure 2.21: Coordinate systems and reference points.

### 2.2.4.2 HTMs for Camera 1 The systematic analysis of the alignment errors for camera 1 is listed in

Table 2.1. The values of motion, offset, and positional errors caused by thermal expansion are also specified in the table. The values of other errors are calculated in the next section.

| Component | Motion       | Offset                                                  | Positional error                                                                                                                                                                               | Roll/Pitch/Yaw                                                                                 |

|-----------|--------------|---------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

| 0→1       |              | <i>Z</i> <sub>1</sub> (44.65 <i>mm</i> )                |                                                                                                                                                                                                |                                                                                                |

| 1→2       | x (314.17mm) | Z <sub>2</sub> (15.35 <i>mm</i> )                       | $\delta_{x2}$                                                                                                                                                                                  | Yaw: $\varepsilon_{z2}$                                                                        |

| 2→3       |              | Z <sub>3</sub> (76.2 <i>mm</i> )                        |                                                                                                                                                                                                |                                                                                                |

| 3→4       |              | Z <sub>4</sub> (25.4 <i>mm</i> )                        |                                                                                                                                                                                                |                                                                                                |

| 4→5       |              | Z₅ (6.35 <i>mm</i> )                                    |                                                                                                                                                                                                | Yaw: $\varepsilon_{z5}$                                                                        |

| 5→6       |              | Z <sub>6</sub> (1 <i>mm</i> )                           | $\delta_{z6}$                                                                                                                                                                                  |                                                                                                |

| 6→7       |              | Z <sub>7</sub> (0.5 <i>mm</i> )                         | $\delta_{x7}, \delta_{y7}, \delta_{z7}$                                                                                                                                                        | Yaw: $\varepsilon_{z7}$                                                                        |

| 0→8       |              | Y <sub>8</sub> (106 <i>mm</i> )                         |                                                                                                                                                                                                |                                                                                                |

| 8→9       |              | Z <sub>9</sub> (291.48mm)                               | $δ_{x9}$ (-7.78 μm)<br>$δ_{y9}$ (3.68 μm)<br>$\delta_{z9}$ (5.21 μm)<br>(due to thermal<br>expansions)                                                                                         |                                                                                                |

| 9→10      |              | Y <sub>10</sub> (-106mm)<br>Z <sub>10</sub> (-122.03mm) | $\begin{array}{ll} \delta_{\rm x10}(0.92\;\mu m) \\ \delta_{\rm y10}(-3.71\;\mu m) \\ \delta_{\rm z10}(2.44\;\mu m) \\ ({\rm due} & {\rm to} & {\rm thermal} \\ {\rm expansions}) \end{array}$ | Yaw: $\varepsilon_{x10}$<br>(-89.6 $\mu$ rad)<br>Yaw: $\varepsilon_{y10}$<br>(-20.3 $\mu$ rad) |

Table 2.1: Analysis of alignment errors for camera 1

Based on this table, we can get the HTMs for camera 1 as below.

$${}^{0}T_{1} = \begin{pmatrix} 1 & 0 & 0 & 0 \\ 0 & 1 & 0 & 0 \\ 0 & 0 & 1 & Z_{1} \\ 0 & 0 & 0 & 1 \end{pmatrix} {}^{1}T_{2} = \begin{pmatrix} 1 & -\varepsilon_{z2} & 0 & x + \delta_{x2} \\ \varepsilon_{z2} & 1 & 0 & 0 \\ 0 & 0 & 1 & Z_{2} \\ 0 & 0 & 0 & 1 \end{pmatrix}$$

$${}^{2}T_{3} = \begin{pmatrix} 1 & 0 & 0 & 0 \\ 0 & 1 & 0 & 0 \\ 0 & 0 & 1 & Z_{3} \\ 0 & 0 & 0 & 1 \end{pmatrix} {}^{3}T_{4} = \begin{pmatrix} 1 & 0 & 0 & 0 \\ 0 & 1 & 0 & 0 \\ 0 & 0 & 1 & Z_{4} \\ 0 & 0 & 0 & 1 \end{pmatrix}$$

$${}^{4}T_{5} = \begin{pmatrix} 1 & -\varepsilon_{z5} & 0 & 0 \\ \varepsilon_{z5} & 1 & 0 & 0 \\ 0 & 0 & 1 & Z_{5} \\ 0 & 0 & 0 & 1 \end{pmatrix} {}^{5}T_{6} = \begin{pmatrix} 1 & 0 & 0 & 0 \\ 0 & 1 & 0 & 0 \\ 0 & 0 & 1 & Z_{6} + \delta_{z6} \\ 0 & 0 & 0 & 1 \end{pmatrix}$$

$${}^{6}T_{7} = \begin{pmatrix} 1 & -\varepsilon_{z7} & 0 & \delta_{x7} \\ \varepsilon_{z7} & 1 & 0 & \delta_{y7} \\ 0 & 0 & 1 & Z_{7} + \delta_{z7} \\ 0 & 0 & 0 & 1 \end{pmatrix} {}^{0}T_{8} = \begin{pmatrix} 1 & 0 & 0 & 0 \\ 0 & 1 & 0 & Y_{8} \\ 0 & 0 & 1 & 0 \\ 0 & 0 & 0 & 1 \end{pmatrix}$$

$${}^{8}T_{9} = \begin{pmatrix} 1 & 0 & 0 & \delta_{x9} \\ 0 & 1 & 0 & \delta_{y9} \\ 0 & 0 & 1 & Z_{9} + \delta_{z9} \\ 0 & 0 & 0 & 1 \end{pmatrix} {}^{9}T_{10} = \begin{pmatrix} 1 & 0 & \varepsilon_{y10} & \delta_{x10} \\ 0 & 1 & -\varepsilon_{x10} & Y_{10} + \delta_{y10} \\ -\varepsilon_{y10} & \varepsilon_{x10} & 1 & Z_{10} + \delta_{z10} \\ 0 & 0 & 0 & 1 \end{pmatrix}$$

# 2.2.4.3 HTMs for Camera 2

The HTM analysis for camera 2 is almost the same as that for camera 1, except that the camera height and the thermal expansion are different since the two camera systems are not symmetric. **Table 2.2: Analysis of alignment errors for camera 2**

| Component | Motion       | Offset                               | Positional error                                                 | Roll/Pitch/Yaw           |

|-----------|--------------|--------------------------------------|------------------------------------------------------------------|--------------------------|

| 0→1       |              | Z <sub>1</sub> (44.65 <i>mm</i> )    |                                                                  |                          |

| 1→2       | x (314.17mm) | Z <sub>2</sub> (15.35mm)             | $\delta_{x2}$                                                    | Yaw: $\varepsilon_{z2}$  |

| 2→3       |              | Z <sub>3</sub> (76.2 <i>mm</i> )     |                                                                  |                          |

| 3→4       |              | Z <sub>4</sub> (25.4 <i>mm</i> )     |                                                                  |                          |

| 4→5       |              | $Z_5$ (6.35mm)                       |                                                                  | Yaw: $\varepsilon_{z5}$  |

| 5→6       |              | Z <sub>6</sub> (1mm)                 | $\delta_{z6}$                                                    |                          |

| 6→7       |              | Z <sub>7</sub> (0.5 <i>mm</i> )      | $\delta_{x7}, \delta_{y7}, \delta_{z7}$                          | Yaw: $\varepsilon_{z7}$  |

| 0→8       |              | Y <sub>8</sub> (-106 <i>mm</i> )     |                                                                  |                          |

|           |              |                                      | $\delta_{x9}$ (-6.91 $\mu m$ )<br>$\delta_{y9}$ (-3.80 $\mu m$ ) |                          |

| 8→9       |              | Z <sub>9</sub> (310.53 <i>mm</i> )   | $\delta_{y9}$ (5.74 $\mu$ m)                                     |                          |

|           |              |                                      | (due to thermal expansions)                                      |                          |

|           |              |                                      | δ <sub>x10</sub> (-0.27 μm)                                      | Yaw: $\varepsilon_{x10}$ |

| 9→10      |              | Y <sub>10</sub> (106 <i>mm</i> )     | δ <sub>y10</sub> (3.28 μm)                                       | (-60.6 <i>µ</i> rad)     |

| 3710      |              | Z <sub>10</sub> (-141.08 <i>mm</i> ) | δ <sub>z10</sub> (2.99 μm)                                       | Yaw: $\varepsilon_{y10}$ |

|           |              |                                      | (due to thermal expansions)                                      | (-19.7 <i>µ</i> rad)     |

$${}^{0}T_{1} = \begin{pmatrix} 1 & 0 & 0 & 0 \\ 0 & 1 & 0 & 0 \\ 0 & 0 & 1 & Z_{1} \\ 0 & 0 & 0 & 1 \end{pmatrix} {}^{1}T_{2} = \begin{pmatrix} 1 & -\varepsilon_{z^{2}} & 0 & x + \delta_{x^{2}} \\ \varepsilon_{z^{2}} & 1 & 0 & 0 \\ 0 & 0 & 1 & Z_{2} \\ 0 & 0 & 0 & 1 \end{pmatrix}$$

$${}^{2}T_{3} = \begin{pmatrix} 1 & 0 & 0 & 0 \\ 0 & 1 & 0 & 0 \\ 0 & 0 & 1 & Z_{3} \\ 0 & 0 & 0 & 1 \end{pmatrix} {}^{3}T_{4} = \begin{pmatrix} 1 & 0 & 0 & 0 \\ 0 & 1 & 0 & 0 \\ 0 & 0 & 1 & Z_{4} \\ 0 & 0 & 0 & 1 \end{pmatrix}$$

$${}^{4}T_{5} = \begin{pmatrix} 1 & -\varepsilon_{z^{5}} & 0 & 0 \\ \varepsilon_{z^{5}} & 1 & 0 & 0 \\ \varepsilon_{z^{5}} & 1 & 0 & 0 \\ 0 & 0 & 1 & Z_{5} \\ 0 & 0 & 0 & 1 \end{pmatrix} {}^{5}T_{6} = \begin{pmatrix} 1 & 0 & 0 & 0 \\ 0 & 1 & 0 & 0 \\ 0 & 1 & 0 & 0 \\ 0 & 0 & 1 & Z_{6} + \delta_{z^{6}} \\ 0 & 0 & 0 & 1 \end{pmatrix}$$

$${}^{6}T_{7} = \begin{pmatrix} 1 & -\varepsilon_{z7} & 0 & \delta_{x7} \\ \varepsilon_{z7} & 1 & 0 & \delta_{y7} \\ 0 & 0 & 1 & Z_{7} + \delta_{z7} \\ 0 & 0 & 0 & 1 \end{pmatrix} {}^{0}T_{8} = \begin{pmatrix} 1 & 0 & 0 & 0 \\ 0 & 1 & 0 & Y_{8} \\ 0 & 0 & 1 & 0 \\ 0 & 0 & 0 & 1 \end{pmatrix}$$

$${}^{8}T_{9} = \begin{pmatrix} 1 & 0 & 0 & \delta_{x9} \\ 0 & 1 & 0 & \delta_{y9} \\ 0 & 0 & 1 & Z_{9} + \delta_{z9} \\ 0 & 0 & 0 & 1 \end{pmatrix} {}^{9}T_{10} = \begin{pmatrix} 1 & 0 & \varepsilon_{y10} & \delta_{x10} \\ 0 & 1 & -\varepsilon_{x10} & Y_{10} + \delta_{y10} \\ -\varepsilon_{y10} & \varepsilon_{x10} & 1 & Z_{10} + \delta_{z10} \\ 0 & 0 & 0 & 1 \end{pmatrix}$$

# 2.2.4.4 HTMs for camera 3

Compared to camera 1 and camera 2, the structural loop of camera 3 includes one more component, which is the roll. The structural loop for camera 3 is shown in Figure 2.22 and the corresponding analysis is listed in Table 2.3.

Figure 2.22: Structural loop for camera 3.

| Component | Motion       | Offset                                   | Positional error                        | Roll/Pitch/Yaw          |

|-----------|--------------|------------------------------------------|-----------------------------------------|-------------------------|

| 0→1       |              | <i>Z</i> <sub>1</sub> (44.65 <i>mm</i> ) |                                         |                         |

| 1→2       | x (314.17mm) | Z <sub>2</sub> (15.35 <i>mm</i> )        | $\delta_{x^2}$                          | Yaw: $\varepsilon_{z2}$ |

| 2→3       |              | Z <sub>3</sub> (76.2 <i>mm</i> )         |                                         |                         |

| 3→4       |              | Z <sub>4</sub> (25.4 <i>mm</i> )         |                                         |                         |

| 4→5       |              | Z₅ (6.35 <i>mm</i> )                     |                                         | Yaw: $\varepsilon_{z5}$ |

| 5→6       |              | Z <sub>6</sub> (1mm)                     | $\delta_{z6}$                           |                         |

| 6→7       |              | Z <sub>7</sub> (0.5 <i>mm</i> )          | $\delta_{x7}, \delta_{y7}, \delta_{z7}$ | Yaw: $\varepsilon_{z7}$ |

| 7→8       |              | Z <sub>8</sub> (66.5 <i>mm</i> )         | $\delta_{z8}$                           | Yaw: $\varepsilon_{z8}$ |

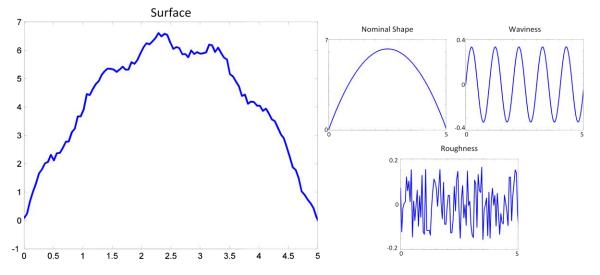

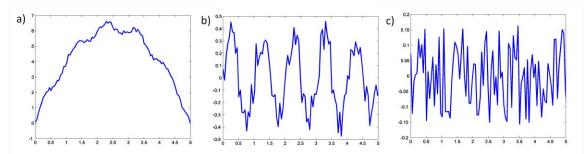

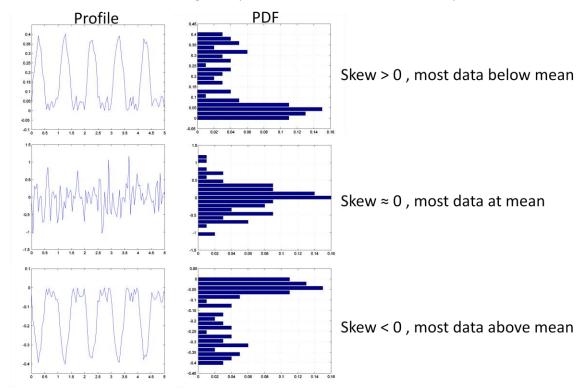

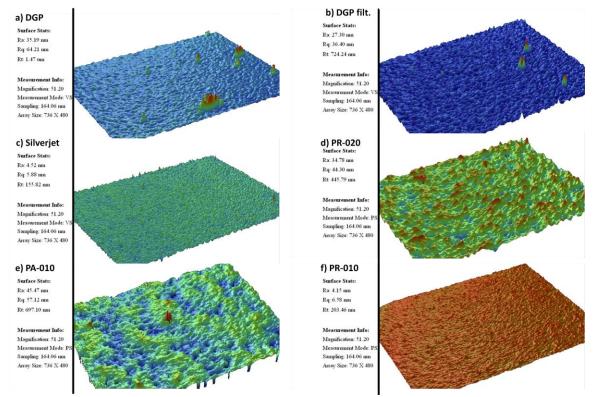

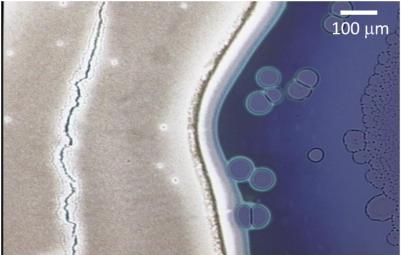

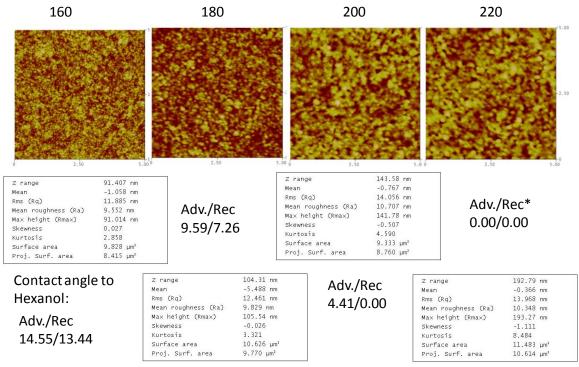

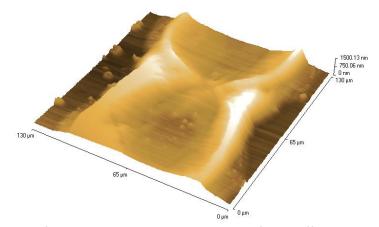

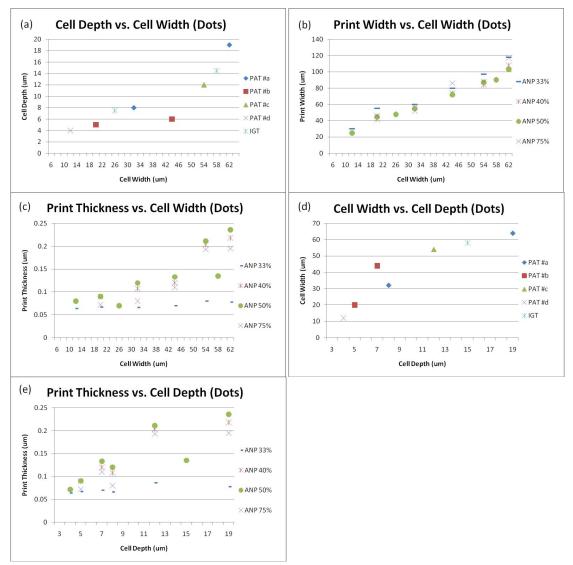

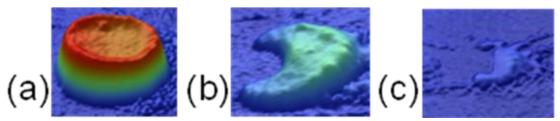

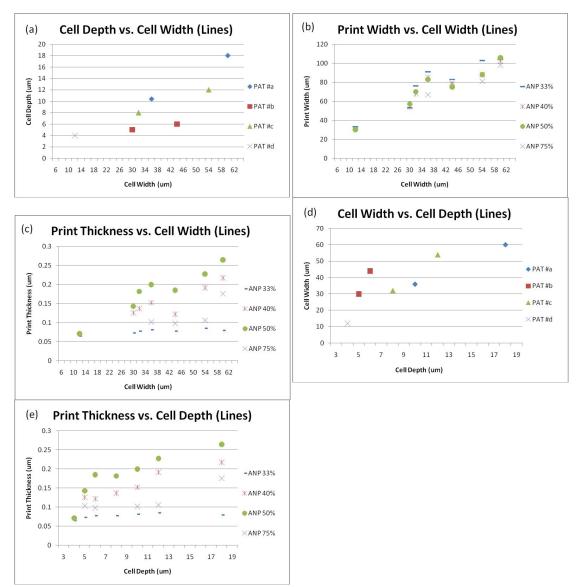

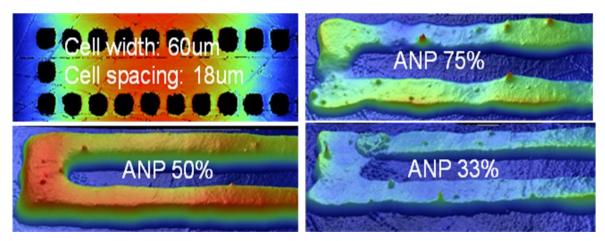

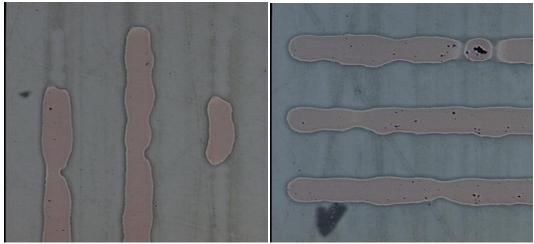

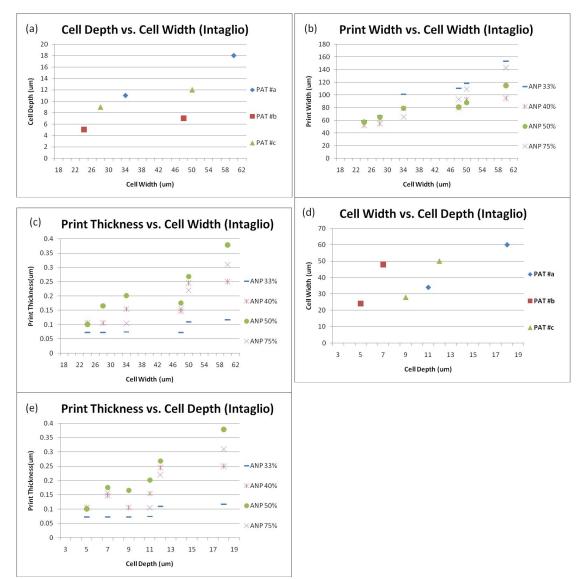

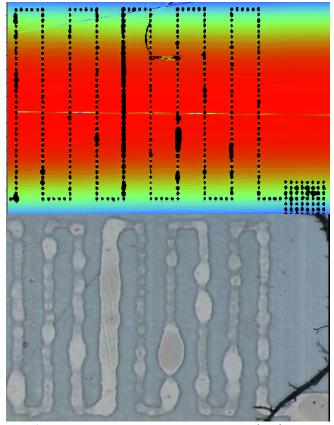

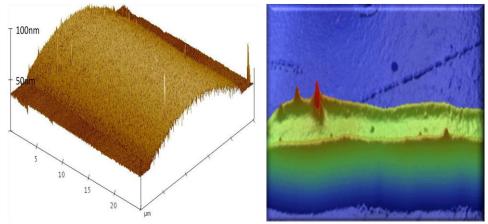

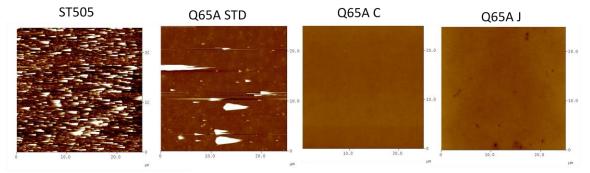

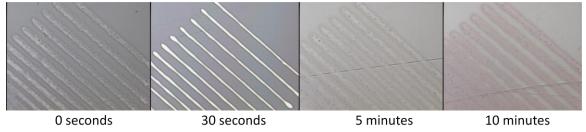

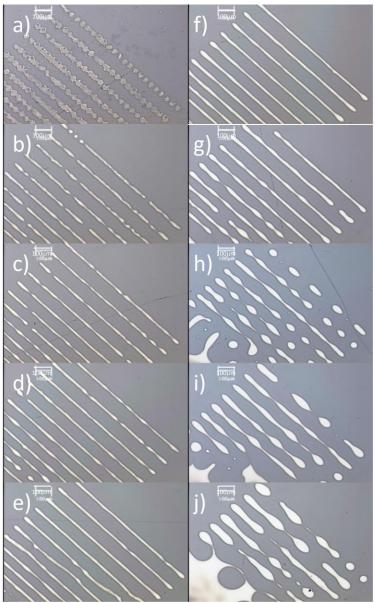

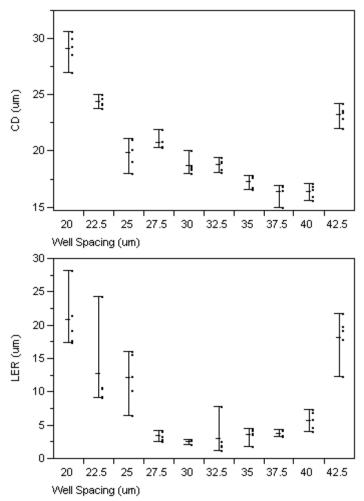

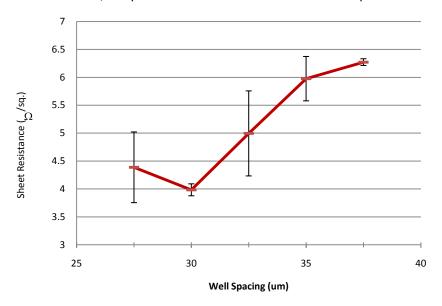

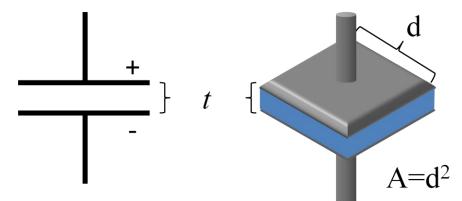

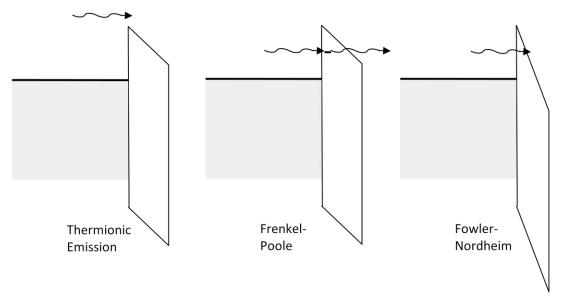

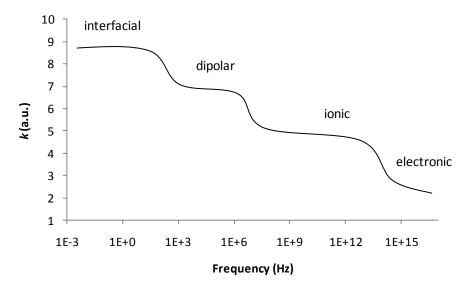

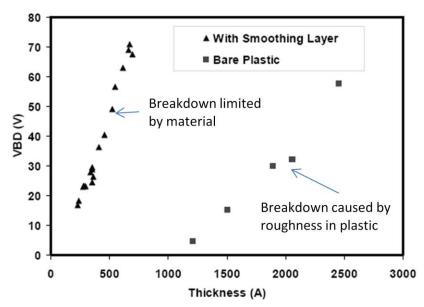

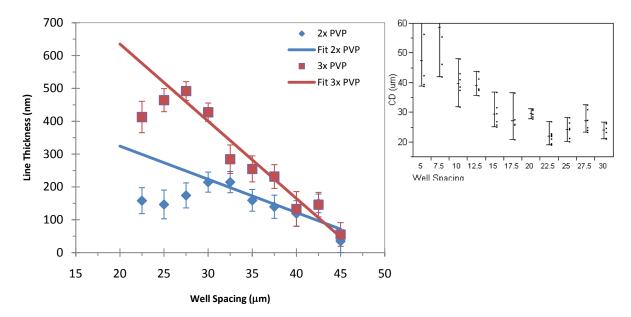

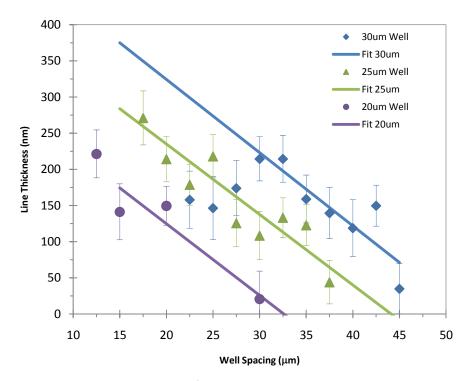

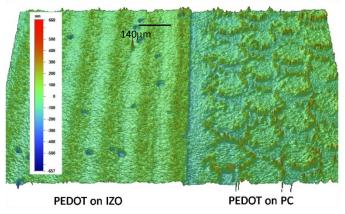

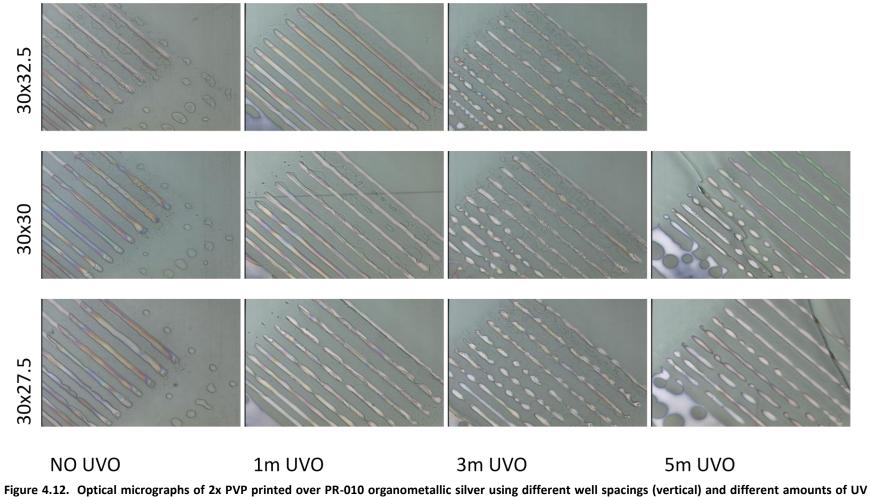

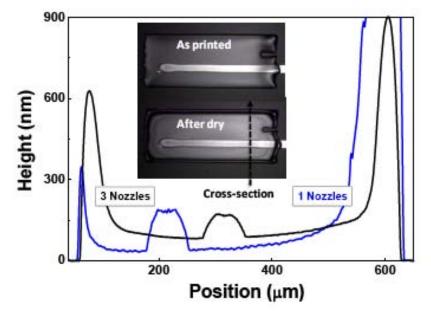

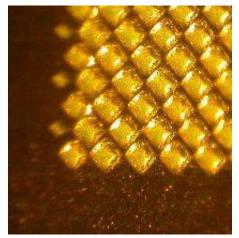

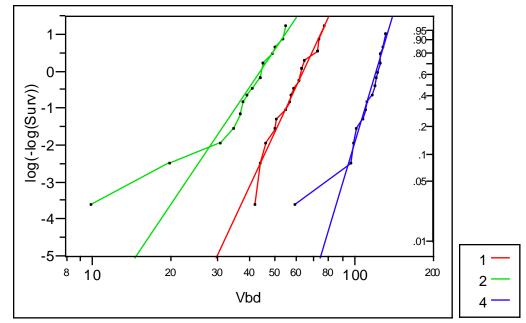

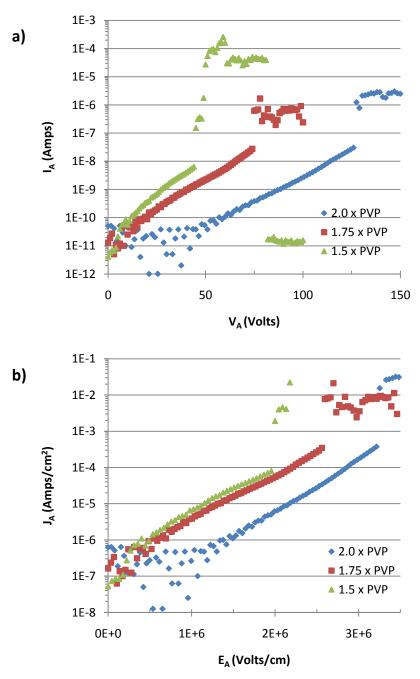

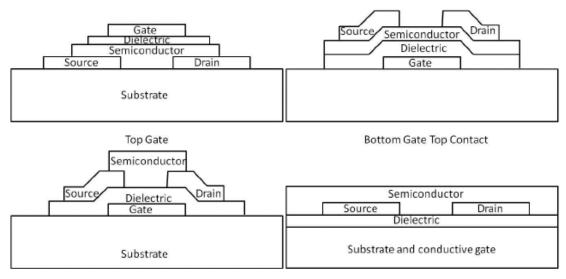

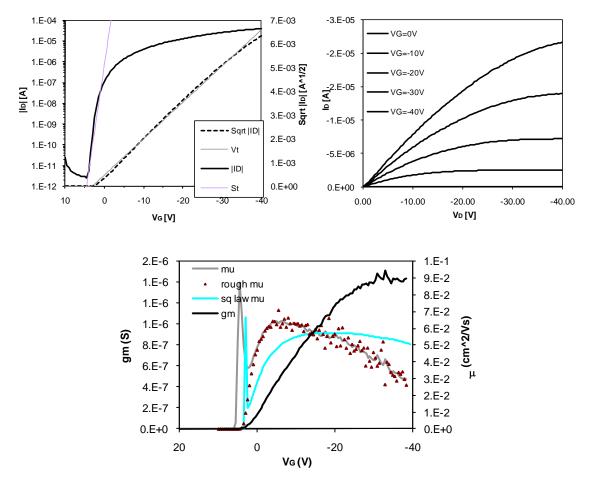

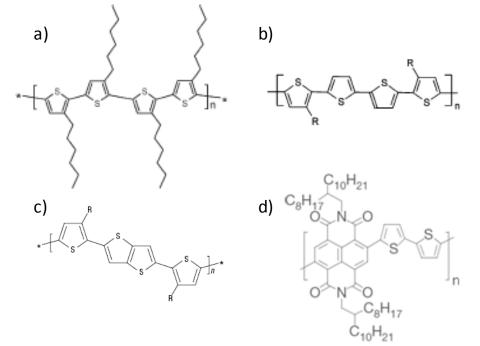

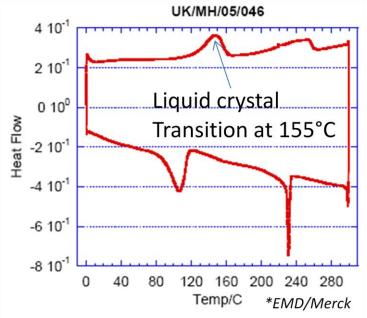

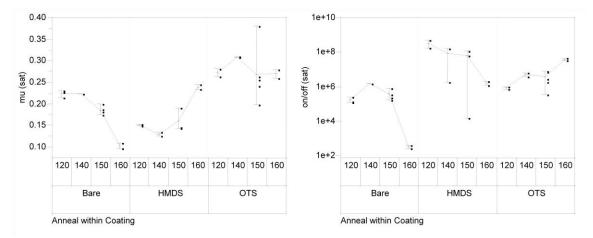

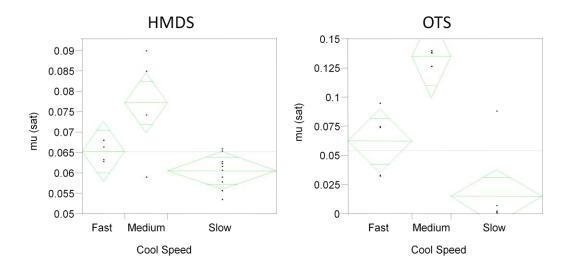

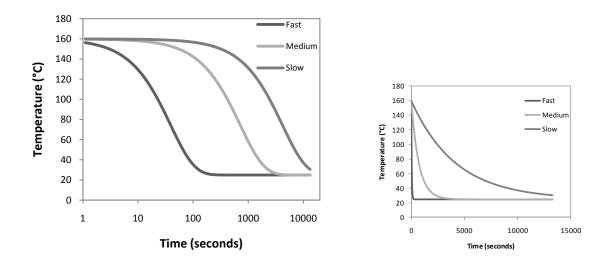

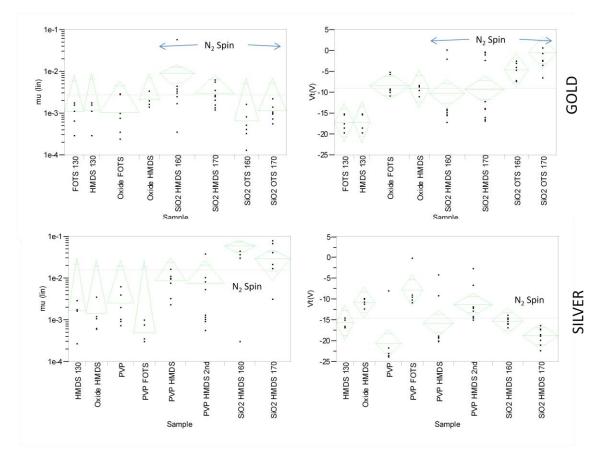

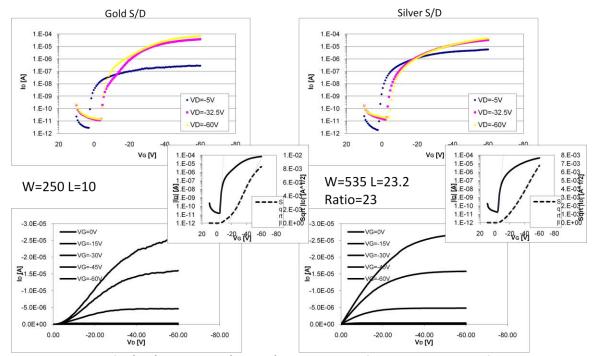

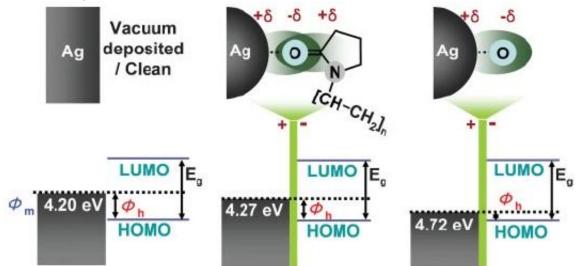

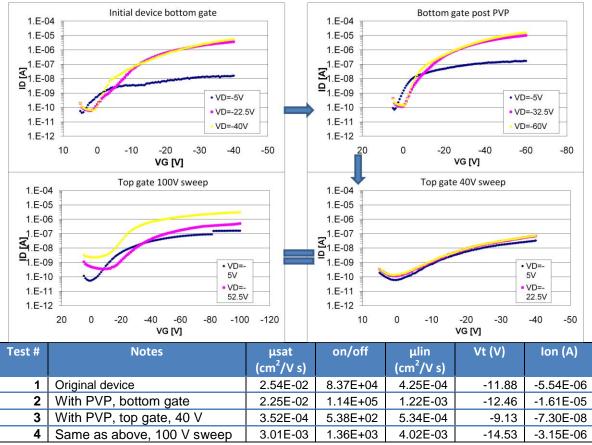

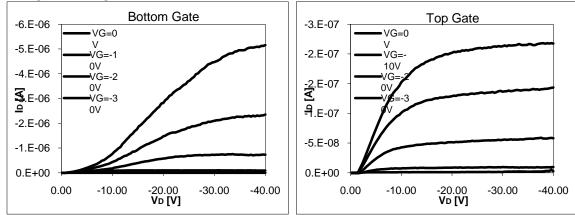

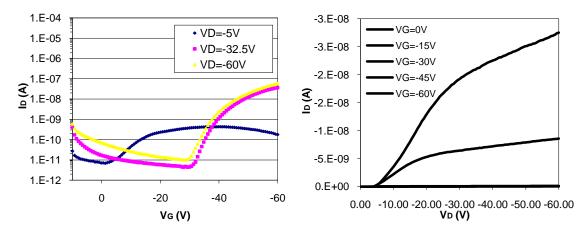

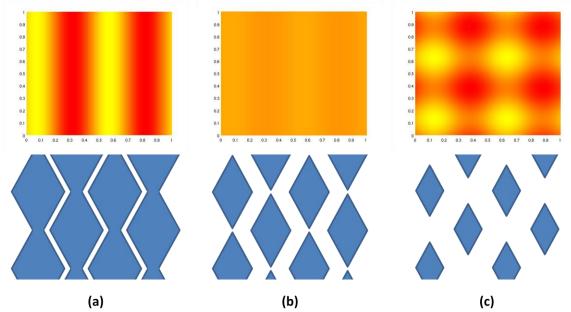

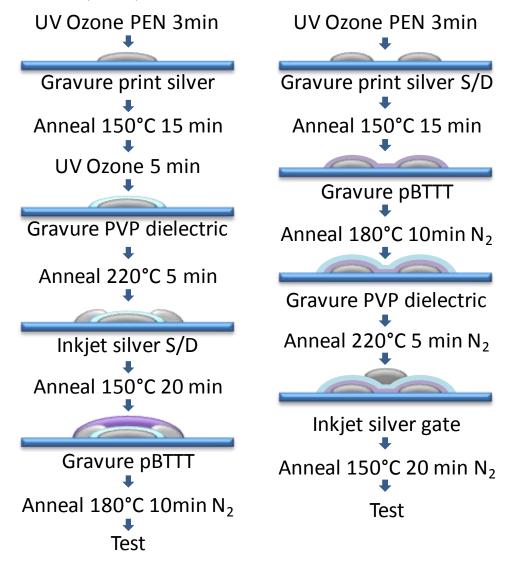

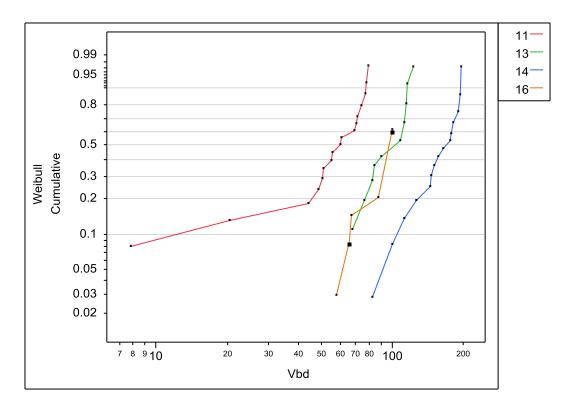

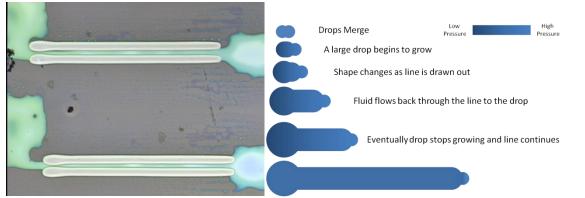

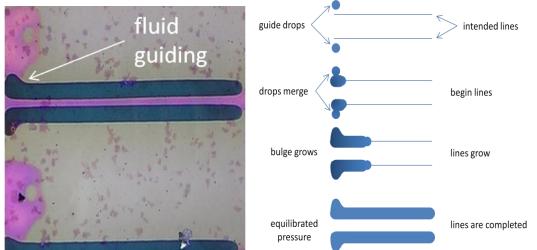

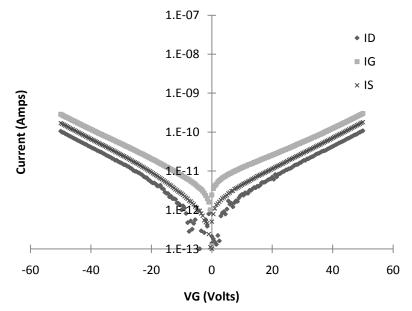

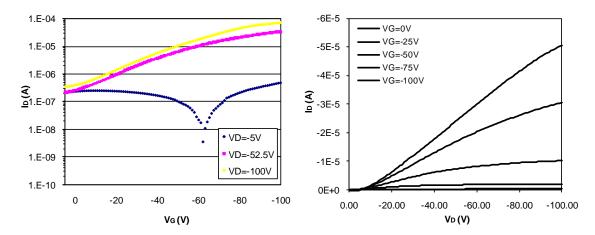

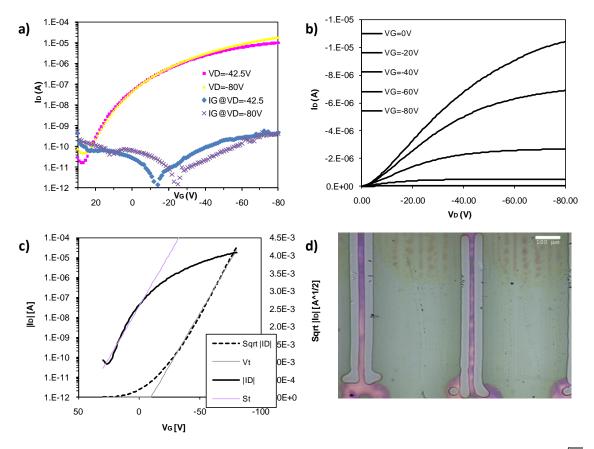

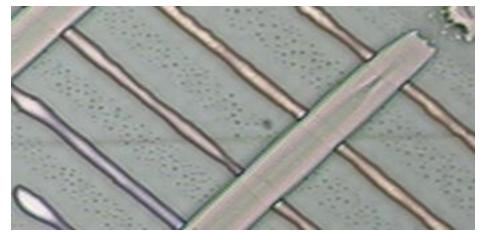

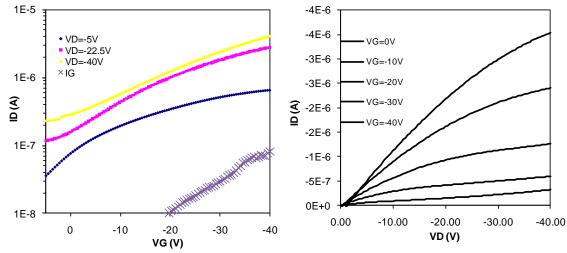

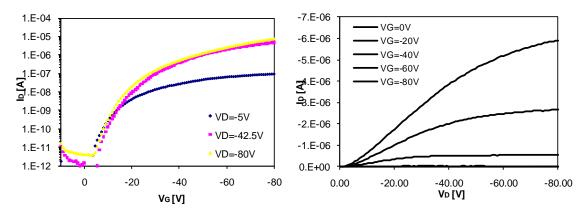

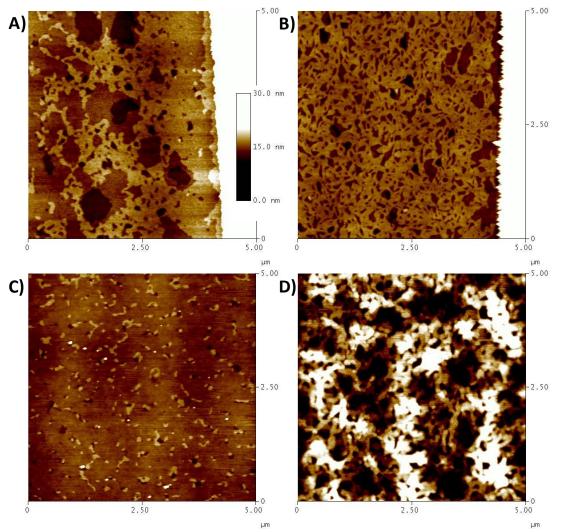

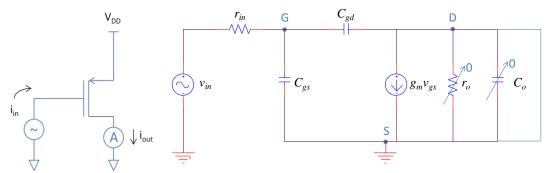

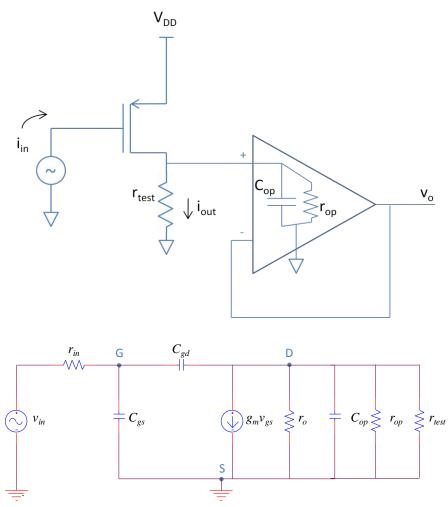

| 0→9       |              | Y <sub>9</sub> (106 <i>mm</i> )          |                                         |                         |