# UCLA UCLA Electronic Theses and Dissertations

### Title

Hardware Design Techniques for Securing and Synthesizing Resource-Constrained IoT Systems

Permalink https://escholarship.org/uc/item/3w66h943

Author Wendt, James Bradley

**Publication Date** 2015

Peer reviewed|Thesis/dissertation

UNIVERSITY OF CALIFORNIA

Los Angeles

# Hardware Design Techniques for Securing and Synthesizing Resource-Constrained IoT Systems

A dissertation submitted in partial satisfaction of the requirements for the degree Doctor of Philosophy in Computer Science

by

### James Bradley Wendt

2015

© Copyright by James Bradley Wendt 2015

#### Abstract of the Dissertation

# Hardware Design Techniques for Securing and Synthesizing Resource-Constrained IoT Systems

by

### James Bradley Wendt

Doctor of Philosophy in Computer Science University of California, Los Angeles, 2015 Professor Miodrag Potkonjak, Chair

The Internet of Things (IoT) paradigm has enabled everyday objects to be instrumented and operated in such a way that they can be queried and controlled over the Internet. While the 1990s saw the connection of nearly 1 billion users to the Internet, and the 2000s saw an increase to 2 billion users through the proliferation of mobile phones, it is estimated that by 2020, IoT will introduce an additional 26 billion units to the Internet ecosystem.

IoT systems have been developed and envisioned for numerous environments and applications and their rapid emergence has introduced a number of unique opportunities and challenges in the space of hardware design. For example, the application of these systems in a variety of environments has lead to an increased need for new low power design solutions, specifically for remote and battery operated devices.

While low energy design is paramount for the successful deployment of resourceconstrained IoT devices, their often remote and physically accessible nature has also contributed to rendering traditional cryptographic techniques insufficient to address all of the security concerns surrounding these systems. Hence, security has become an equally important requirement. These two desiderata, security and low energy, are often conflicting requirements by nature and present a challenging scenario for design. For example, higher levels of security often require larger amounts of energy consumption.

In this dissertation we present energy-aware design methods for the synthesis and security of IoT systems. We present novel energy reduction and delay minimization techniques applied on integrated circuit subsystems of IoT applications in order to enable near-threshold computing operation with maximal energy savings and minimal speed degradation. We also present semantics-based techniques for the organization and coordination of system components in order to both reduce energy consumption as well as increase energy harvester production. Finally, we demonstrate new techniques for securing IoT systems, including intellectual property protection, trusted remote sensing, and trusted chip selection. The dissertation of James Bradley Wendt is approved.

Chih-Kong Ken Yang

Miloš D. Ercegovac

Jens Palsberg

Miodrag Potkonjak, Committee Chair

University of California, Los Angeles 2015

To my parents.

# TABLE OF CONTENTS

| 1        | Intr | roduction                                               | 1  |

|----------|------|---------------------------------------------------------|----|

|          | 1.1  | The Internet of Things                                  | 1  |

|          | 1.2  | Challenges and Motivation                               | 3  |

|          | 1.3  | Contributions and Organization                          | 6  |

| <b>2</b> | Ene  | ergy Reduction through Coordinated Device Aging and NTC | 9  |

|          | 2.1  | Preliminaries                                           | 0  |

|          |      | 2.1.1 Process Variation                                 | 0  |

|          |      | 2.1.2 Near-Threshold Computing                          | 1  |

|          |      | 2.1.3 Device Aging                                      | 3  |

|          |      | 2.1.4 Gate Level Characterization                       | 4  |

|          | 2.2  | Motivation and Problem Formulation                      | 5  |

|          | 2.3  | Energy Reduction                                        | 7  |

|          | 2.4  | Summary                                                 | 22 |

| 3        | Ada  | aptive Body Biasing for Reclaiming Speed in NTC 2       | 3  |

|          | 3.1  | Preliminaries                                           | 24 |

|          |      | 3.1.1 Near-Threshold Computing                          | 24 |

|          |      | 3.1.2 Process Variation                                 | 25 |

|          |      | 3.1.3 Adaptive Body Biasing                             | 25 |

|          |      | 3.1.4 Power and Delay Modeling                          | 26 |

|          | 3.2  | Methodology and Techniques                              | 27 |

|   | 3.3 | ABB     | Group Selection                                             | 30 |

|---|-----|---------|-------------------------------------------------------------|----|

|   |     | 3.3.1   | ABB Group Selection: Single Pass                            | 30 |

|   |     | 3.3.2   | ABB Group Selection: Iterative Refinement                   | 31 |

|   | 3.4 | Summ    | nary                                                        | 35 |

| 4 | Ult | ralow ] | Power Implementations of Linear Systems                     | 36 |

|   | 4.1 | Prelin  | ninaries                                                    | 37 |

|   |     | 4.1.1   | Near-Threshold Computing                                    | 37 |

|   |     | 4.1.2   | Chaining                                                    | 38 |

|   |     | 4.1.3   | Multiple Constant Multiplication                            | 40 |

|   | 4.2 | Iterati | ive Node Replication for Target Delay Yield in NTC $\ldots$ | 41 |

|   |     | 4.2.1   | Algorithm                                                   | 42 |

|   |     | 4.2.2   | Results                                                     | 45 |

|   | 4.3 | Summ    | nary                                                        | 48 |

| 5 | Sen | nantics | -based System Configuration for Energy Reduction .          | 50 |

|   | 5.1 | Relate  | ed Work                                                     | 53 |

|   | 5.2 | Prelin  | ninaries                                                    | 54 |

|   |     | 5.2.1   | Semantics-driven Energy Reduction                           | 54 |

|   |     | 5.2.2   | Medical Shoe                                                | 54 |

|   |     | 5.2.3   | Gait Characteristics                                        | 55 |

|   | 5.3 | Energ   | y Reduction                                                 | 56 |

|   |     | 5.3.1   | Sensor Configuration                                        | 57 |

|   |     | 5.3.2   | Subsampling                                                 | 62 |

|    | 5.4   | Results: Sensor Configuration                              | 65 |

|----|-------|------------------------------------------------------------|----|

|    | 5.5   | Results: Subsampling                                       | 67 |

|    | 5.6   | Summary                                                    | 68 |

| 6  | Ene   | ergy Harvesting                                            | 69 |

|    | 6.1   | Related Work                                               | 70 |

|    | 6.2   | Motivation                                                 | 71 |

|    | 6.3   | Preliminaries                                              | 72 |

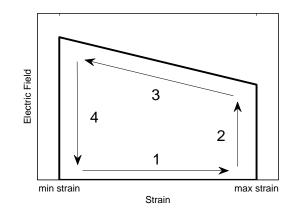

|    |       | 6.3.1 Dielectric Elastomers                                | 72 |

|    |       | 6.3.2 Harvester Simulation                                 | 74 |

|    |       | 6.3.3 Medical Shoe                                         | 74 |

|    | 6.4   | Spatiotemporal Harvester Assignment                        | 75 |

|    | 6.5   | Results                                                    | 77 |

|    | 6.6   | Summary                                                    | 80 |

| 7  | Har   | dware Obfuscation for Intellectual Property Protection and |    |

| Tr | ruste | d Remote Sensing                                           | 81 |

|    | 7.1   | Related Work                                               | 84 |

|    | 7.2   | Standard PUF Overview                                      | 86 |

|    | 7.3   | Arbitrary Logic Replacement                                | 87 |

|    |       | 7.3.1 Programmable Fabric Configuration                    | 88 |

|    |       | 7.3.2 Stabilizing the Standard PUF                         | 91 |

|    | 7.4   | Signal Path Obfuscation                                    | 91 |

|    | 7.5   | Attacks                                                    | 93 |

|   | 7.6 | Techn  | $iques \dots \dots$      |

|---|-----|--------|--------------------------------------------------------------------------------------------------------------------------------|

|   |     | 7.6.1  | Logic Replacement                                                                                                              |

|   |     | 7.6.2  | Signal Path Obfuscation                                                                                                        |

|   | 7.7 | Analy  | sis $\ldots$ $\ldots$ $\ldots$ $$ 97                                                                                           |

|   | 7.8 | Digita | l PUF Overview                                                                                                                 |

|   | 7.9 | Applic | cations of the Digital PUF                                                                                                     |

|   |     | 7.9.1  | Intellectual Property Protection                                                                                               |

|   |     | 7.9.2  | Remote Trust                                                                                                                   |

|   |     |        |                                                                                                                                |

| 8 | Tru | sted C |                                                                                                                                |

|   | 8.1 | Relate | ed Work                                                                                                                        |

|   | 8.2 | Proces | ss Variation $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $121$                                              |

|   | 8.3 | Found  | ry Characterization                                                                                                            |

|   | 8.4 | Extrac | cting IC Parameters                                                                                                            |

|   |     | 8.4.1  | Solving for Threshold Voltage and Effective Channel Length 124                                                                 |

|   |     | 8.4.2  | Solving for Delay                                                                                                              |

|   |     | 8.4.3  | Device Aging 128                                                                                                               |

|   | 8.5 | Identi | fication $\ldots \ldots 128$ |

|   |     | 8.5.1  | Delay Measurement Error                                                                                                        |

|   |     | 8.5.2  | Sample Size                                                                                                                    |

|   |     | 8.5.3  | Gate Delay Characterization                                                                                                    |

|   |     | 8.5.4  | Supply Voltage Range and Magnitude                                                                                             |

|   |     | 8.5.5  | Foundry Identification                                                                                                         |

|   |     |        |                                                                                                                                |

|   | 8.6   | Summary   |         | • |  | • |  |  | • | • |  | • | • | • |  | <br>•   | 135 |

|---|-------|-----------|---------|---|--|---|--|--|---|---|--|---|---|---|--|---------|-----|

| 9 | Con   | cluding R | lemarks |   |  |   |  |  |   |   |  |   |   |   |  |         | 136 |

| R | efere | nces      |         | • |  |   |  |  |   |   |  |   | • | • |  | <br>• • | 138 |

# LIST OF FIGURES

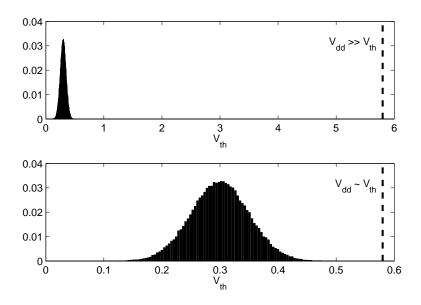

| 2.1 | Example distribution of threshold voltages due to process vari-                |    |

|-----|--------------------------------------------------------------------------------|----|

|     | ation. In the top figure the supply voltage is set in the super-               |    |

|     | threshold region where process variation has very little impact on             |    |

|     | operation. In the bottom figure process variation must be taken                |    |

|     | into account when setting the supply voltage in the near-threshold             |    |

|     | region                                                                         | 13 |

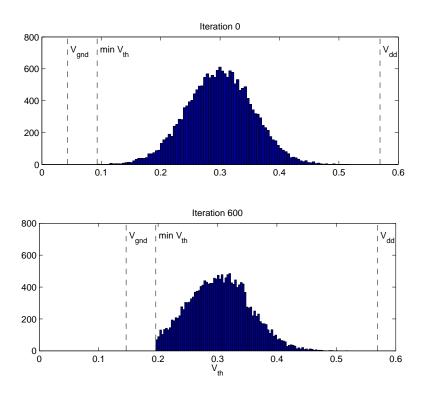

| 2.2 | Gate $V_{th}$ distributions of s38584 from the ISCAS'89 benchmark              |    |

|     | suite [37]. $V_{dd}$ remains at a near-threshold voltage just above the        |    |

|     | highest $V_{th}$ gate while $V_{gnd}$ is set to a near-threshold voltage just  |    |

|     | below the lowest $V_{th}$ gate. After aging the lowest 600 gates we can        |    |

|     | increase $V_{gnd}$ and reduce overall circuit switching energy                 | 18 |

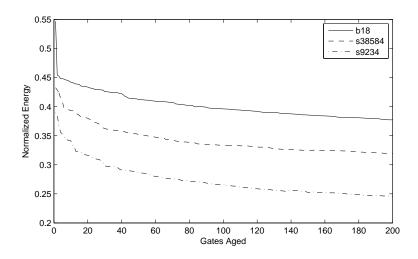

| 2.3 | ASIC energy reduction applied using iterative minimum $V_{th}$ aging           |    |

|     | on circuits from the ISCAS'85 and ISCAS'89 benchmark suites $\left[ 37\right]$ |    |

|     | [38]                                                                           | 19 |

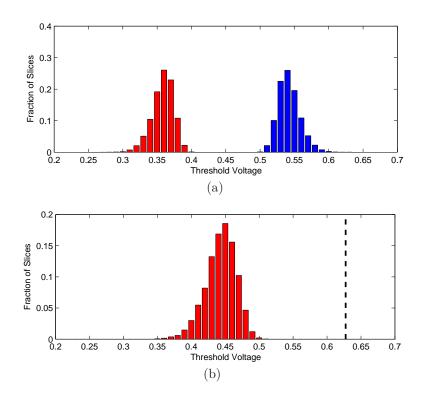

| 2.4 | (a) Distributions of maximum and minimum threshold voltages                    |    |

|     | found in slices of a typical FPGA board. (b) Distribution of mini-             |    |

|     | mum threshold voltages across FPGA slices after aging. The dot-                |    |

|     | ted line represents the maximum threshold voltage of each slice                | 21 |

- 3.1 The red distribution represents gates on the critical path and the blue distribution represents the remaining gates. In this scenario we purposely dope the critical path gates at lower concentrations, thus reducing their nominal threshold voltage values and variance. In order to achieve the same energy savings as NTC, the critical path gates are biased and shifted up from (a) to (b).

29

22

####

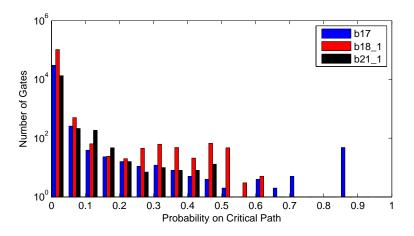

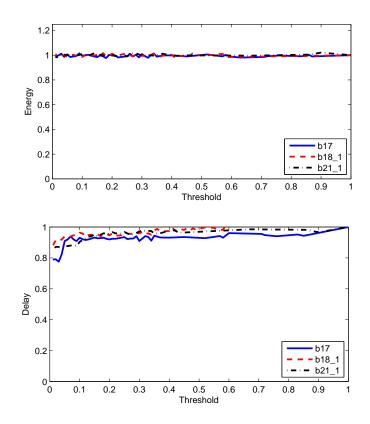

- 3.3 Results from single pass ABB group selection. The energy and delay are averaged values over one thousand instances. The threshold corresponds to the probability of being on the critical path in the generic NTC scenario.

32

- 3.4 Results from iterative refinement ABB group selection. At each iteration we create one thousand instances of the individual circuit and append the k most probable critical path gate candidates from those instances to the ABB group.

33

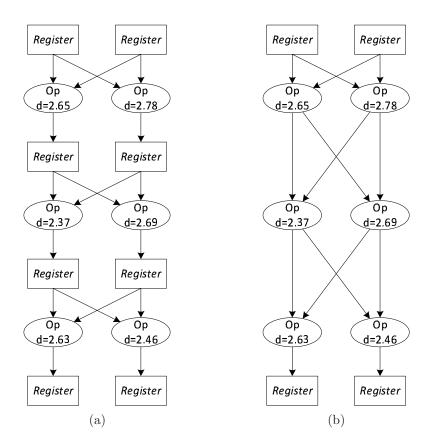

| 4.1 | Motivational example depicting the effect of process variation on       |    |

|-----|-------------------------------------------------------------------------|----|

|     | the delay of (a) multi-cycle and (b) deep chained logic circuits. In    |    |

|     | the multi-cycle case the clock rate is constrained by the maximum       |    |

|     | delay of each pair of operations. Thus, total circuit delay is 8.34.    |    |

|     | In the deep logic case, total delay is 7.93                             | 39 |

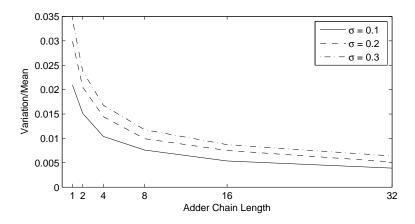

| 4.2 | Effect of deep logic on the impact of process variation at near-        |    |

|     | threshold operation. Sigma $\sigma$ values correspond to the experimen- |    |

|     | tal standard deviation in nominal threshold voltages                    | 40 |

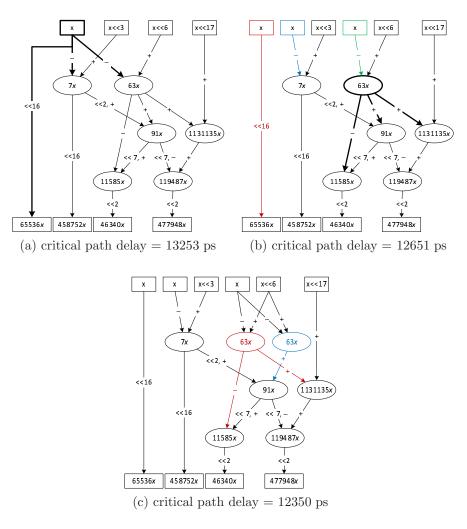

| 4.3 | Functionally equivalent MCM structures for a single variable of an      |    |

|     | 8 point FFT. (a) A minimal depth, minimal operation MCM tree            |    |

|     | created by the Spiral MCM synthesis tool [57]. Bolded nodes are         |    |

|     | those selected to be replicated in the following iteration. (b) A       |    |

|     | reconstructed MCM tree created by replicating inputs for $x$ from       |    |

|     | the previous iteration. (c) The next iteration of the MCM tree cre-     |    |

|     | ated by replicating the $63x$ operation and balancing output load.      |    |

|     | Tables 4.1 and 4.2 specify the values and delays used in this example.  | 43 |

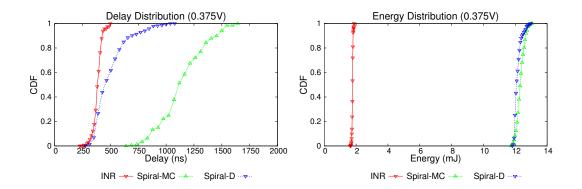

| 4.4 | DCT–16x16 circuit yield with respect to $(top)$ delay and $(bottom)$    |    |

|     | energy in the presence of process variation when operating in near-     |    |

|     | threshold with a nominal $V_{th}$ of 0.33V. We compare our technique    |    |

|     | with the multi-cycle (MC) and deep logic (D) implementations of         |    |

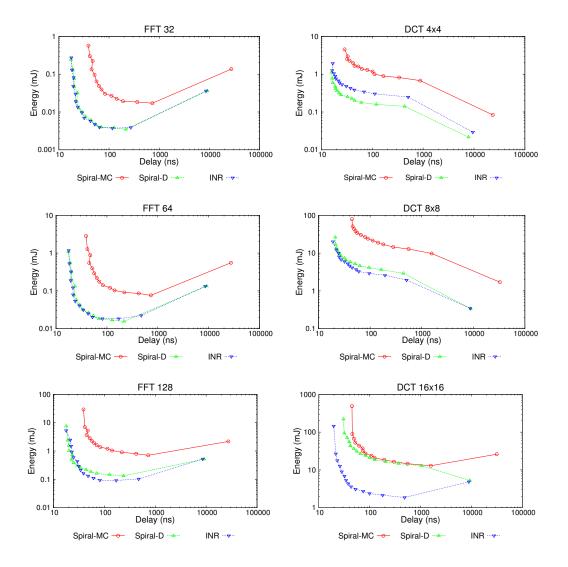

- 4.5 Circuit energy consumption for target delays for FFT and DCT benchmark applications using multi-cycle (MC) and deep logic (D) implementations of Spiral's heuristic solutions and implementations generated using our iterative node replication technique. . . 48

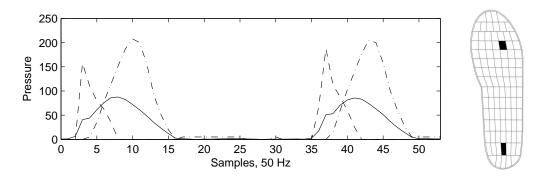

| 5.1 | Pressure measurements of two steps of a single foot measured by           |    |

|-----|---------------------------------------------------------------------------|----|

|     | sensors on the heel (dash), toe (dash-dot), and averaged over all         |    |

|     | ninety-nine sensors (solid). The heel and toe sensors are shaded          |    |

|     | on the Pedar mapping $[60]$                                               | 55 |

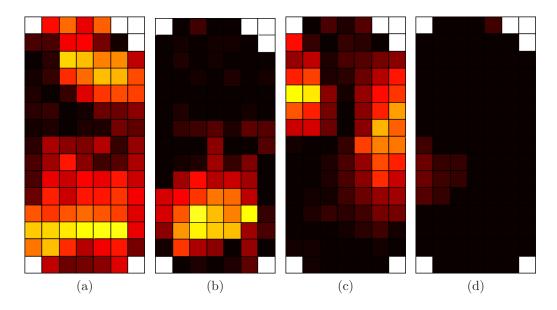

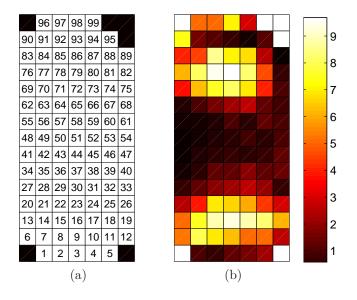

| 5.2 | Individual sensor coefficients of determination for (a) average max-      |    |

|     | imum step amplitude, (b) change in step stride, (c) lateral pressure      |    |

|     | difference, and (d) guardedness. The lighter the sensor, the more         |    |

|     | correlated it is to the metric; darker shadings denote weaker cor-        |    |

|     | relations                                                                 | 58 |

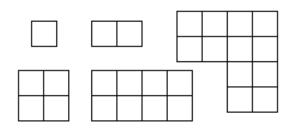

| 5.3 | Shapes used in sensor fusion, pre-computed prior to sensor selection.     | 60 |

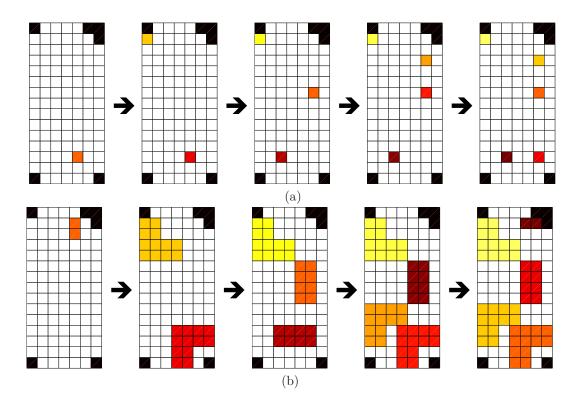

| 5.4 | Top sensor configurations at iterations $1 \leq i \leq 5$ . Solution (a)  |    |

|     | limits sensor selection to individual sensors, (b) includes sensor        |    |

|     | fusion                                                                    | 64 |

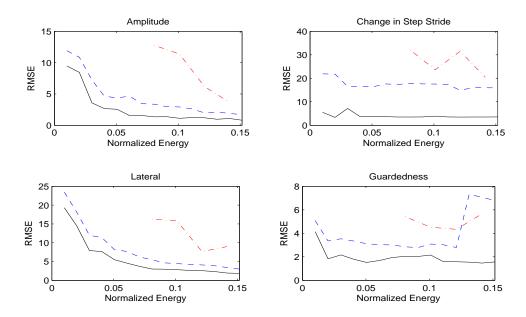

| 5.5 | Coarse grained optimization via sensor configuration. Root mean           |    |

|     | squared testing error in prediction using best selected sensors using     |    |

|     | only single sensors (dash), using sensor fusion (solid), and results      |    |

|     | from Noshadi et al. [61] (dash-dot). Units are <i>pressure</i> for ampli- |    |

|     | tude and lateral, and $samples$ for step stride and guardedness           | 65 |

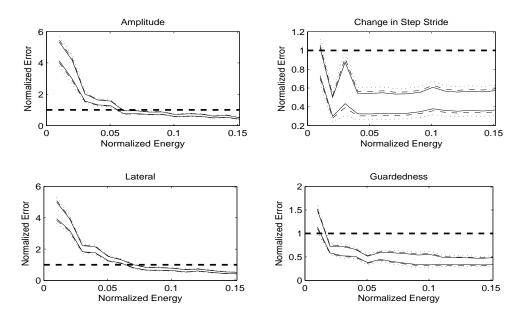

| 5.6 | Coarse grained optimization using sensor fusion. Semantic predic-         |    |

|     | tion error as a percentage of desired error threshold (thick dashed);     |    |

|     | 90% confidence interval (solid), $95%$ (dashed), $99%$ (dotted). When     |    |

|     | the prediction error reduces to the threshold for all semantics, sen-     |    |

|     | sor selection is complete.                                                | 66 |

5.7 Fine grained optimization via subsampling configuration applied to the best configurations found in coarse optimization. Curves are constructed from right to left as sensor-samples are removed iteratively. The four semantic errors are normalized for equal comparison between semantics. Normalized energy is the fraction of energy expended on the new configuration over the original array of ninety-nine sensors sampled at 50 Hz.

67

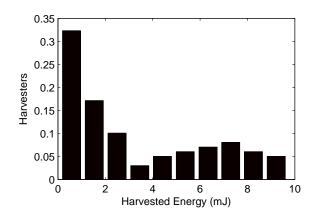

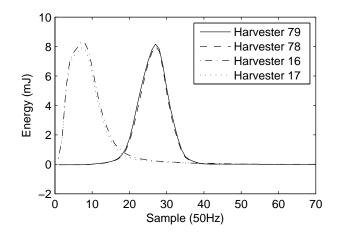

- 6.3 Distribution of average optimal energy output per step across all potential harvester locations on the pedar mapping assuming the load charge is applied at the optimal timing specific to each harvester. 76

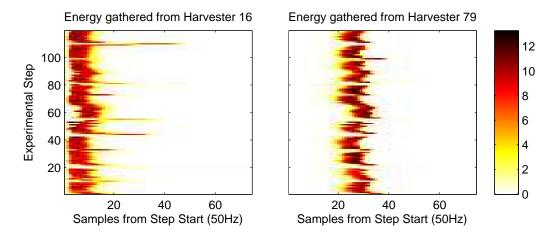

- 6.4 Potential energy harvesting points for harvesters 16 and 79. Assuming the top three harvesters are installed and timed optimally, and the average ambulation frequency is 2Hz, each shoe would produce about 34mW.

78

| 6.5                               | Top harvester average energy distributions given that the charge              |    |

|-----------------------------------|-------------------------------------------------------------------------------|----|

|                                   | is applied to the DE at the specified sample time and the energy              |    |

|                                   | is harvested at the step end                                                  | 78 |

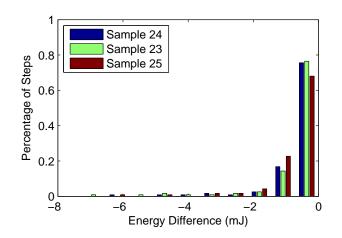

| 6.6                               | Distributions of the difference in harvested energy from the op-              |    |

|                                   | timal potential harvested energy using the labeled global sensor              |    |

|                                   | predictors on harvester 79. For about $90\%$ of all steps, each of the        |    |

|                                   | top three sensor-sample predictors are able to harvest within $1 \mathrm{mJ}$ |    |

|                                   | of optimum                                                                    | 79 |

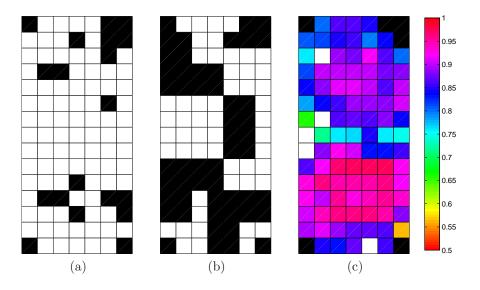

| 6.7                               | (a, b) Minimum subset of sensors capable of measuring gait char-              |    |

|                                   | acteristics necessary for medical diagnosis found in Chapter 5. (c) $$        |    |

|                                   | Average harvested energy as a percentage of the optimal energy in             |    |

|                                   | Figure 6.2b. Energy is harvested when the predicted energy profile            |    |

|                                   | of each harvester (as predicted by the global sensor) is at maximum.          | 79 |

|                                   |                                                                               |    |

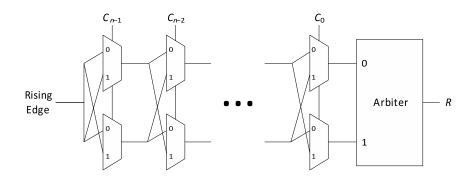

| 7.1                               | Standard delay-based arbiter PUF [93]                                         | 87 |

| 7.1<br>7.2                        |                                                                               |    |

|                                   | Standard delay-based arbiter PUF [93]                                         |    |

|                                   | Standard delay-based arbiter PUF [93]                                         |    |

|                                   | Standard delay-based arbiter PUF [93]                                         | 87 |

| 7.2                               | Standard delay-based arbiter PUF [93]                                         | 87 |

| 7.2                               | Standard delay-based arbiter PUF [93]                                         | 87 |

| 7.2                               | Standard delay-based arbiter PUF [93]                                         | 87 |

| 7.2                               | Standard delay-based arbiter PUF [93]                                         | 87 |

| 7.2                               | Standard delay-based arbiter PUF [93]                                         | 87 |

| <ul><li>7.2</li><li>7.3</li></ul> | Standard delay-based arbiter PUF [93]                                         | 87 |

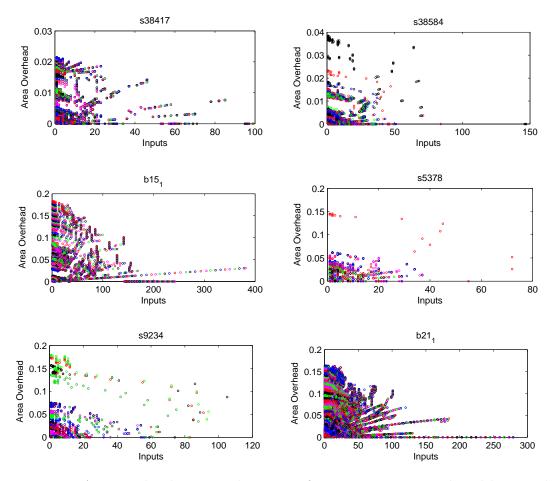

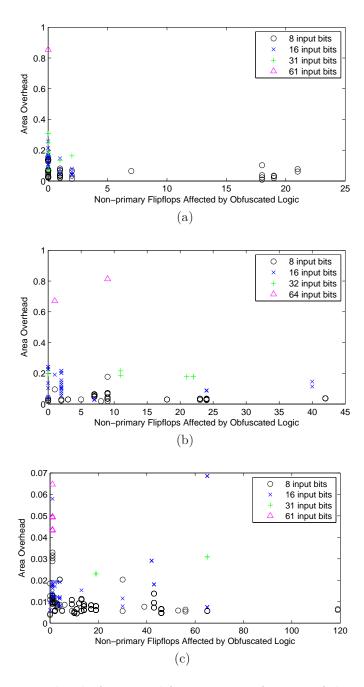

| 7.5  | Total number of flip-flops affected by the labeled number of wire    |     |

|------|----------------------------------------------------------------------|-----|

|      | swapping components.                                                 | 98  |

| 7.6  | Area overhead upon replacement of circuitry using PUF-based          |     |

|      | logic with the labeled number of inputs. The different colors rep-   |     |

|      | resent the flip-flops whose inputs come from the individual PUF-     |     |

|      | based logic component                                                | 99  |

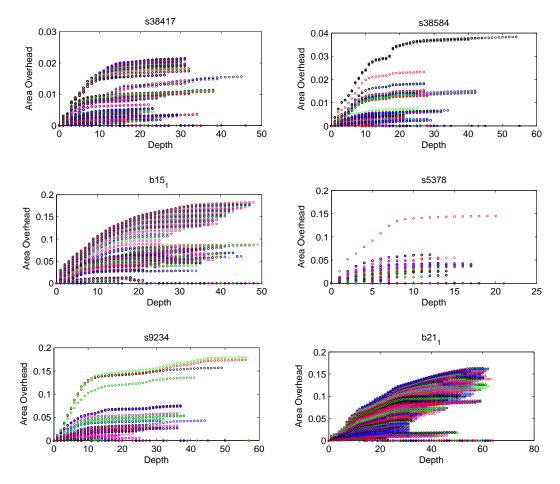

| 7.7  | Area overhead upon replacement of circuitry using PUF-based          |     |

|      | logic with the labeled circuit depth. The different colors represent |     |

|      | the flip-flops whose inputs come from the individual PUF-based       |     |

|      | logic component.                                                     | 100 |

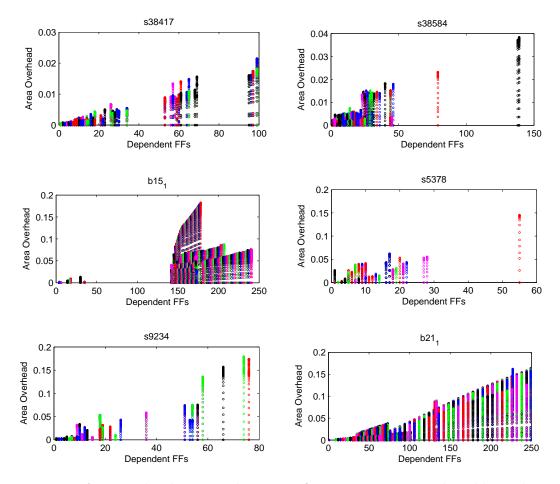

| 7.8  | Area overhead upon replacement of circuitry using PUF-based          |     |

|      | logic that is affected by the labeled number of flip-flops. The dif- |     |

|      | ferent colors represent the flip-flops whose inputs come from the    |     |

|      | individual PUF-based logic component                                 | 101 |

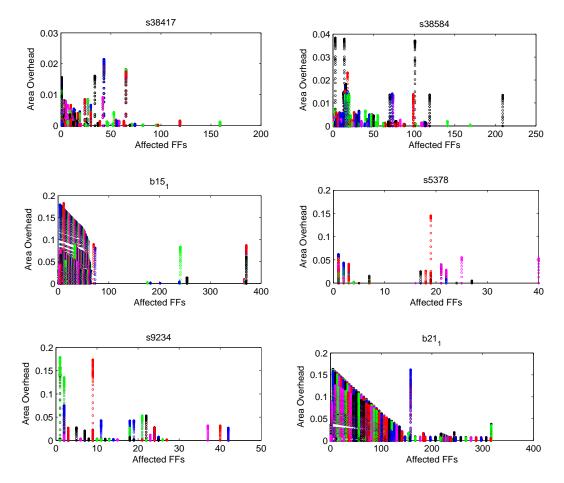

| 7.9  | Area overhead upon replacement of circuitry using PUF-based          |     |

|      | logic that affects the labeled number of flip-flops. The different   |     |

|      | colors represent the flip-flops whose inputs come from the individ-  |     |

|      | ual PUF-based logic component                                        | 102 |

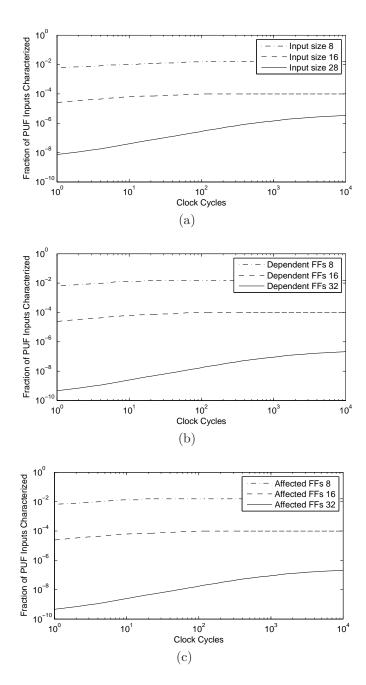

| 7.10 | Fraction of PUF inputs characterized in reverse engineering an       |     |

|      | obfuscated b12 benchmark circuit                                     | 103 |

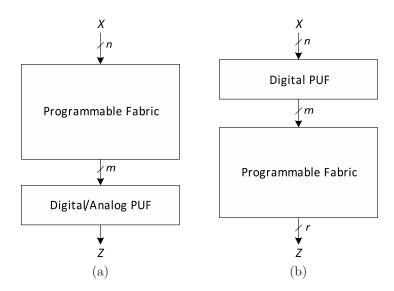

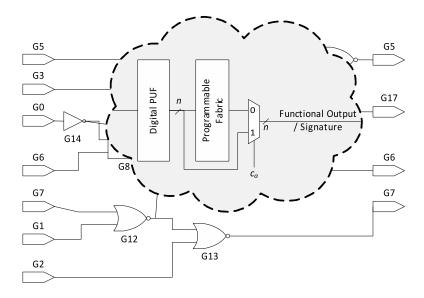

| 7.11 | Hardware logic obfuscation architecture. (b) Pre-logic is required   |     |

|      | for the analog PUF to ensure input-output stability. (c) Post-logic  |     |

|      | is enabled through the use of the digital PUF since it is stable for |     |

|      | all inputs.                                                          | 107 |

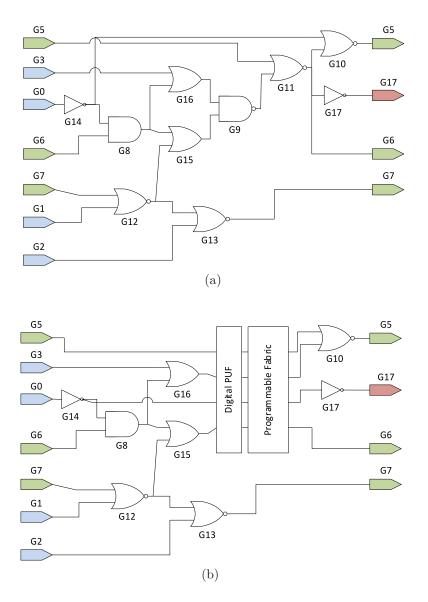

| 7.12 | Motivational example using the (a) s27 circuit from the ISCAS'89 $$         |     |

|------|-----------------------------------------------------------------------------|-----|

|      | benchmark suite. (b) Obfuscated form using the post-logic archi-            |     |

|      | tecture from Figure 7.11b. The blue pins denote primary inputs.             |     |

|      | The red pin denotes a primary output. The green pins represent              |     |

|      | flip-flops                                                                  | 109 |

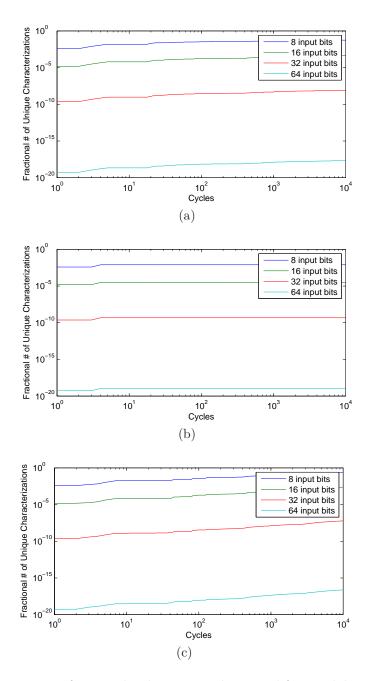

| 7.13 | Fraction of correctly characterized PUF obfuscated logic input-             |     |

|      | output mappings for the (a) s5378, (b) s9234, and (c) s38417 cir-           |     |

|      | cuits from the ISCAS'89 benchmark suite [37]                                | 112 |

| 7.14 | Area overhead of circuit obfuscation as a fraction of the original          |     |

|      | size of a 90nm circuit for the (a) $s5378$ , (b) $s9234$ , and (c) $s38417$ |     |

|      | circuits from the ISCAS'89 benchmark suite [37]                             | 114 |

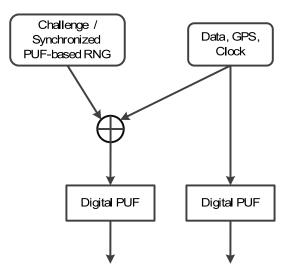

| 7.15 | Trusted remote sensing computation flow at the sensor node. The             |     |

|      | base station provides the challenge                                         | 116 |

| 7.16 | Variant of the hardware obfuscation architecture applied to the $s27$       |     |

|      | benchmark suite enabling hardware attestation. The control signal           |     |

|      | $c_a$ determine whether the circuit operates in normal functional           |     |

|      | mode or in attestation mode.                                                | 118 |

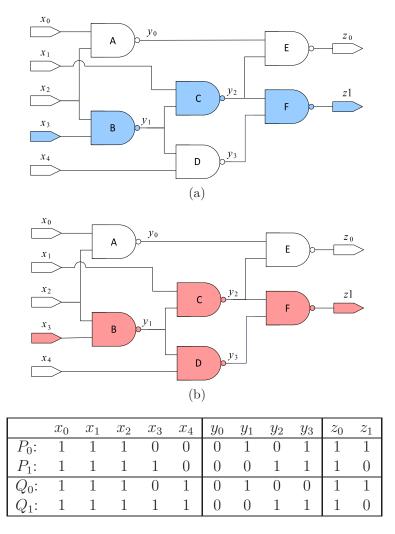

| 8.1  | Circuit c17 from the ISCAS85 benchmark suite [38]. The blue com-            |     |

|      | ponents in (a) correspond to the signal edge path when initialized          |     |

|      | with input $P_0$ followed by applying $P_1$ . The red components in (b)     |     |

|      | correspond to the signal edge path when initialized with input $Q_0$        |     |

|      | followed by applying $Q_1$                                                  | 126 |

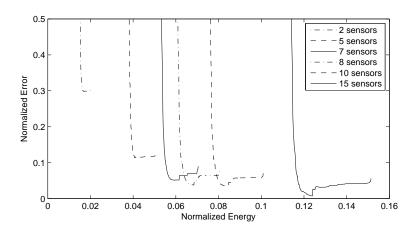

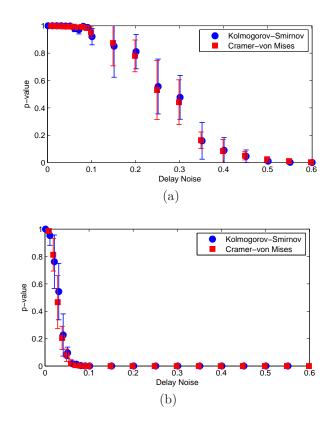

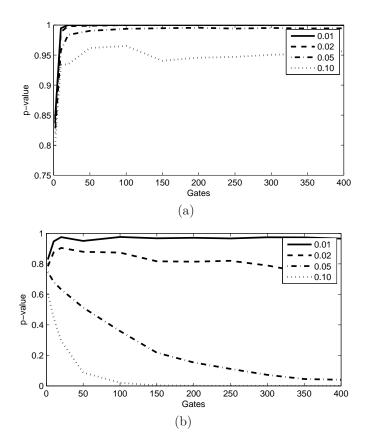

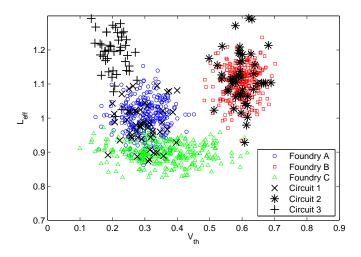

8.2 The effects of delay measurement error on the Kolmogorov-Smirnov and Cramér von-Mises two sample tests for (a)  $V_{th}$  and (b)  $L_{eff}$ . Uncertainty bars represent the standard deviation of *p*-values from 129100 tests. 8.3 The effects of distribution size and delay measurement errors on correct identification using distributions of (a)  $V_{th}$  and (b)  $L_{eff}$ . Legend errors correspond to those described in Figure 8.2. . . . . 130 The effects of supply voltage range on correct identification using 8.4 distributions of (a)  $V_{th}$  and (b)  $L_{eff}$ . The first voltage equals 1V while the second voltage differs by the value along the x-axis. Legend errors correspond to those described in Figure 8.2. . . . . 132 The effects of supply voltage magnitude on correct identification 8.5 using distributions of (a)  $V_{th}$  and (b)  $L_{eff}$ . The first supply voltage corresponds to the value along the x-axis. The second supply voltage is 1V larger. Legend errors correspond to those described 133IC parameters and foundry profiles. Circuit 1 originates from 8.6 foundry A, circuit 2 originates from foundry B, and circuit 3 is a counterfeit that does not originate from any trusted foundry. The circuit parameters are reverse engineered from delay values measured with a 0.05 error rate.  $\ldots$   $\ldots$   $\ldots$   $\ldots$   $\ldots$  134

## LIST OF TABLES

| 1.1 | Major contributions and organization of the dissertation              | 8  |

|-----|-----------------------------------------------------------------------|----|

| 3.1 | Summary of results from applying iterative refinement ABB group       |    |

|     | selection. Normal refers to traditional super-threshold operation.    |    |

|     | NTC refers to basic near-threshold operation without modifica-        |    |

|     | tion. $NTC+ABB$ refers to our iterative refinement ABB group          |    |

|     | selection technique. Energy factor between NTC and NTC+ABB $$         |    |

|     | are near identical. We see a dramatic and expected performance        |    |

|     | degradation from Normal operation near 5×. However, we see a          |    |

|     | factor of improvement in delay between $1.38$ and $1.97$ when utiliz- |    |

|     | ing our NTC+ABB technique over NTC                                    | 34 |

| 4.1 | Multiplier constants for a single input variable used in Figure $4.3$ |    |

|     | in fixed-point representation using 16 fraction bits and 3 integer    |    |

|     | bits                                                                  | 44 |

| 4.2 | Approximate delay values used in Figure 4.3 for a carry-lookahead     |    |

|     | adder (cell size 2) operating at near-threshold                       | 44 |

| 4.3 | Energy and area results for FFT and DCT applications synthe-          |    |

|     | sized using multi-cycle (MC) and deep logic (D) implementations       |    |

|     | of Spiral's heuristic synthesis tool and our iterative node replica-  |    |

|     | tion techniques.                                                      | 47 |

| 7.1 | Average area overhead for obfuscated logic with input sizes of 8,    |     |

|-----|----------------------------------------------------------------------|-----|

|     | 16, 32, and 64 for the pertinent benchmark circuits. The dashed      |     |

|     | placeholders represent input set sizes that could not be found for   |     |

|     | the corresponding circuit.                                           | 113 |

|     |                                                                      |     |

| 8.1 | Gates in benchmark circuits $[37]$ $[45]$ whose IC parameters can be |     |

|     | fully characterized.                                                 | 131 |

| 8.2 | Minimum and maximum $p$ -values for circuit parameter and foundry    |     |

|     | profile comparisons using the Kolmogorov-Smirnov test. Foundry       |     |

|     | distributions correspond to those depicted in Figure 8.6. We test    |     |

|     | 20 instances of each circuit.                                        | 135 |

#### Acknowledgments

First and foremost, I would like to thank my adviser and doctoral committee chair, Professor Miodrag Potkonjak, for his support and guidance through all of my years as a graduate student at UCLA. He not only guided me through the world of academic research but also provided me with numerous opportunities to grow as a scientist, for which I am very grateful.

I would like to thank my doctoral committee members, Professors C. K. Ken Yang, Milos Ercegovac, and Jens Palsberg, for their insightful comments and advice on my prospectus, dissertation, and final defense, and for aiding me in the completion of my graduate studies.

To my professors in the UCLA Computer Science Department and my professors at Pomona College, thank you for not only providing me with a solid scientific foundation, but also for inspiring me with your passion for research and teaching.

To my hosts and colleagues at UC Riverside, JPL, AT&T, and Google, thank you for your patience and mentorship, and for introducing me to the world of engineering and research in industry.

Many thanks to my collaborators and colleagues at UCLA: Sheng Wei, Viswha Goudar, Nathaniel Conos, Jason Zheng, Jong Ahnn, Saro Meguerdichian, Teng Xu, Jia Guo, and Hongxiang Gu. Thank you for participating with me in technical discussions and debate, working late to finish joint papers and proposals, and for sharing in the graduate school experience with me. I would like to extend a special thank you to Nathaniel Conos, Saro Meguerdichian, Vishwa Goudar, and Teng Xu who collaborated with me and provided experimental results and paper writing assistance to support my work in Chapters 4, 5, 6, and 7, respectively.

Special thanks goes to Professor Potkonjak who oversaw and co-authored all of the research work that constituted the chapters in this thesis.

And finally, I would like to thank my family and friends who have supported me throughout my academic journey. A special thank you to my parents for their unconditional love and support, providing me with the means and confidence to dream big. To my sister for her love, friendship, and patience. And to Samantha for her unwavering love and encouragement, especially on the days when I needed it most. Thank you.

#### Vita

| 2005-2009 | B.A. (Physics)                        |

|-----------|---------------------------------------|

|           | Pomona College                        |

| 2009-2011 | M.S. (Computer Science)               |

|           | University of California, Los Angeles |

### PUBLICATIONS

**P1.** J. B. Wendt, "Nanocell-based (public) physical unclonable function," Master's thesis, University of California, Los Angeles, 2011.

P2. J. B. Wendt and M. Potkonjak, "Medical diagnostic-based sensor selection," in *IEEE Sensors*, pp. 1507–1510, 2011.

**P3.** J. B. Wendt and M. Potkonjak, "Nanotechnology-based trusted remote sensing," in *IEEE Sensors*, pp. 1213–1216, 2011.

**P4.** J. B. Wendt, S. Meguerdichian, H. Noshadi, and M. Potkonjak, "Energy and cost reduction in localized multisensory systems through application-driven compression," in *Data Compression Conference (DCC)*, p. 411, 2012.

**P5.** J. B. Wendt, S. Meguerdichian, H. Noshadi, and M. Potkonjak, "Semanticsdriven sensor configuration for energy reduction in medical sensor networks," in International Symposium on Low Power Electronics and Design (ISLPED), pp. 303–308, 2012.

**P6.** J. B. Wendt, V. Goudar, H. Noshadi, and M. Potkonjak, "Spatiotemporal assignment of energy harvesters on a self-sustaining medical shoe," in *IEEE Sensors*, pp. 1312–1315, 2012.

**P7.** S. Meguerdichian, J. B. Wendt, and M. Potkonjak, "Simultaneous trust and privacy in medical systems using public physical unclonable functions," in *Telehealthcare Computing and Engineering: Principles and Design* (F. Hu, ed.), pp. 679–698, CRC Press, 2013.

P8. J. B. Wendt, S. Meguerdichian, and M. Potkonjak, "Small is beautiful and smart," in *Telehealthcare Computing and Engineering: Principles and Design* (F. Hu, ed.), pp. 341–358, CRC Press, 2013.

**P9.** T. Xu, J. B. Wendt, and M. Potkonjak, "Digital bimodal function: An ultra-low energy security primitive," in *International Symposium on Low Power Electronics and Design (ISLPED)*, pp. 292–297, 2013.

**P10.** J. B. Wendt and M. Potkonjak, "Improving energy efficiency in sensing subsystems via near-threshold computing and device aging," in *IEEE Sensors*, pp. 555–558, 2013.

**P11.** J. B. Wendt and M. Potkonjak, "The bidirectional polyomino partitioned PPUF as a hardware security primitive," in *IEEE Global Conference on Signal*

and Information Processing (GlobalSIP), pp. 257–260, 2013.

**P12.** V. Goudar, J. B. Wendt, M. Potkonjak, Z. Ren, P. Brochu, and Q. Pei, "Leveraging human gait characteristics towards self-sustained operation of lowpower mobile devices," in *World Forum on Internet of Things (WF-IoT)*, pp. 468–473, 2014.

P13. M. Rostami, J. B. Wendt, M. Potkonjak, and F. Koushanfar, "Quo vadis, PUF? Trends and challenges of emerging physical-disorder based security," in *Design, Automation & Test in Europe (DATE)*, no. 352, pp. 1–6, 2014.

**P14.** S. Wei, J. B. Wendt, A. Nahapetian, and M. Potkonjak, "Reverse engineering and prevention techniques for physical unclonable functions using side channels," in *Design Automation Conference (DAC)*, no. 90, pp. 1–6, 2014.

**P15.** J. B. Wendt, F. Koushanfar, and M. Potkonjak, "Techniques for foundry identification," in *Design Automation Conference (DAC)*, no. 208, pp. 1–6, 2014.

**P16.** T. Xu, J. B. Wendt, and M. Potkonjak, "Matched digital PUFs for low power security in implantable medical devices," in *International Conference on Healthcare Informatics (ICHI)*, pp. 33-38, 2014.

**P17.** T. Xu, J. B. Wendt, and M. Potkonjak, "Secure remote sensing and communication using digital PUFs," in *Symposium on Architectures for Networking* and Communications Systems (ANCS), pp. 173–184, 2014. **P18.** T. Xu, J. B. Wendt, and M. Potkonjak, "Ultra-lightweight symmetric-key cipher for resource constrained systems," in *IEEE Sensors*, pp. 1252–1255, 2014.

**P19.** J. B. Wendt and M. Potkonjak, "Hardware obfuscation using PUF-based logic," in *International Conference on Computer-Aided Design (ICCAD)*, pp. 270–277, 2014.

P20. T. Xu, J. B. Wendt, and M. Potkonjak, "Security of IoT systems: Design challenges and opportunities," in *International Conference on Computer-Aided Design (ICCAD)*, pp. 417–423, 2014.

**P21.** J. B. Wendt, N. A. Conos, and M. Potkonjak, "Multiple constant multiplication implementations in near-threshold computing systems," to appear in *International Conference on Acoustics, Speech and Signal Processing (ICASSP)*, 2015.

**P22.** J. Rajendran, R. Karri, J. B. Wendt, M. Potkonjak, N. McDonald, G. S. Rose, and B. Wysocki, "Nanoelectronic solutions for hardware security," to appear in *Proceedings of the IEEE*, 2015.

# CHAPTER 1

## Introduction

#### **1.1** The Internet of Things

The Internet of Things is a rapidly emerging paradigm in which the essential concept is that a great variety of Things are equipped in such a way that they can be queried and operated over the Internet. This has enabled both user-to-object applications, in which users can control and sense their environments remotely, and object-to-object applications, enabling opportunities for big data learning, semantic reasoning, and coordinated operation. This paradigm is projected to have a positive impact on many aspects of everyday life, ranging from organizational and operational improvements, to better semantic reasoning and inference in personal, industrial, and global spaces.

Radio-frequency identification (RFID) tags provide a first glimpse into a very rudimentary generation of IoT devices. Companies such as Walmart and Amazon use these devices to automatically identify and track inventory. Over the course of the last half decade a number of new IoT applications and devices have emerged, including wearable medical apparatuses, home automation systems, industrial sensors and actuators, biochip transponders, and wearable accessories such as Internet-connected watches, eye wear, and shoes.

Over the course of the last half decade a number of new IoT applications and devices have emerged, including wearable medical devices, home automation systems, automotive applications, industrial sensors and actuators, biochip transponders, and wearable accessories such as Internet-connected watches, eye wear, and shoes.

By the year 2000 nearly 1 billion users worldwide had connected to the Internet. By 2010 the emergence of mobile connectivity had increased the number of connected devices to 2 billion. In 2008, the National Intelligence Council predicted IoT to be one of the top six disruptive technologies impacting the US economy out to 2025 [1]. Current estimates predict that by 2020 IoT will encompass 26 billion units [2].

In just the last few years many large technology players, including Google, Intel, ARM, and General Electric, have announced and demonstrated significant investments into the IoT space. For example, in 2014 Google acquired Nest Labs, a home automation company, whose flagship device is an Internet connected thermostat that not only allows enables remote querying and control of an individual's home temperature over the Internet, but also aims to learn user behaviors and habits with respect to temperature, power consumption, and scheduling [3]. Google has also expanded its IoT presence with the acquisition of Dropcam, an IoT home security device manufacturer [4].

In January of 2014, Intel announced the production of its Edison computer, a small-form Bluetooth and WiFi enabled development platform created specifically for IoT applications [5]. One year later Intel unveiled Intel Curie, an even smaller form adaptable hardware platform than the Edison, specifically targeted for Internet-connected wearable device development [6].

Companies such as Apple and Samsung have also joined the IoT movement in the hardware space, with devices such as their respective smart watches, and have also produced software development platforms, such as Apple's HomeKit [7] and Samsung's IoT Platform [8] which aim to provide a framework for mobileto-object and object-to-object communications and control.

In addition to the aforementioned consumer facing devices, there also exists a variety of industrial counterparts, such as GE's Industrial Internet project which intends to provide IoT solutions to industries such as aviation, healthcare, manufacturing, mining, oil and gas, and electrical power [9].

#### 1.2 Challenges and Motivation

The practical realization of IoT requires the development of a number of new versions of platforms and technologies. Device identification, process tracking, sensing and actuation, communication, computational sensing, semantic knowledge processing, coordinated and distributed control, and behavioral, traffic, and user modeling are just a few of the processes that the IoT paradigm has enabled or will enable [10].

The realization of IoT systems is subject to numerous constraints including cost, power, energy, and lifetime. One should also consider a great diversity of IoT systems from fully organized to small individual nodes [11] [12] [13]. For example, Things such as cars, airplanes, and industrial equipment allow for much more expensive instrumentation with much high power and energy budgets in comparison to household IoT devices and those that are battery operated, wireless powered, or that even harvest energy from their surrounding environment.Therefore, although for full impact, generic algorithms and protocols that can be applied broadly to all IoT devices are required, different customized solutions for individual environments and applications are also needed.

In this dissertation we present methods for synthesizing and securing resource-

constrained IoT systems. Resource-constrained IoT applications, which are generally wireless, remote, and battery operated systems, have highly constrained design requirements due to their low energy budgets. A significant percentage of these types of IoT devices will also operate in a passive mode without batteries. Energy for these devices will either be harvested or received using a wireless medium. For these devices especially, ultralow energy solutions are required.

A second important design desideratum is security. There is a wide consensus that security will be one of the most challenging of requirements for the successful deployment of IoT. This is especially so since the potential for malicious attacks can and will be greatly spread and actuated from the Internet to the physical world. Already attacks have been carried out on devices such as the Nest thermostat [14].

IoT security encompasses several layers of abstraction and a number of dimensions. These abstraction levels range from physical layers of sensors, to computation and communication, to the semantic layer in which all collected information is interpreted and processed. From a research point of view, most novel attacks are on physical signals and, in particular, semantic attacks during data processing and decision making steps. It is also important to secure hardware since IoT presents the possibility for new physical-based attacks. It is important to observe that the lowest security at any level and at any dimension determines the overall security.

Hardware-based security is ideally suited to answer IoT security requirements. However, in order to realize the full potential of hardware-based security, very significant additional research and engineering issues have to be addressed in novel and creative ways. Hardware-based security provides a natural starting point for the realization of IoT protocols and procedures due to their very low area and energy requirements. They are also naturally more resilient against side-channel and physical attacks. Also very importantly, is that they enable the creation of secure and trusted information flows [15]. Finally, they provide elegant and efficient solutions to several problems that classical cryptography has not been able to solve, such as secure location discovery.

IoT security desiderata can be grouped into two broad classes. The first class consists of required security tasks. As usual, the primary potential difficulties are related but contradictory requirements of different tasks. For instance, the strength of authentication and trust are in direct contradiction with a criterion of privacy. The second class of desiderata is related to design metrics such as cost, size, latency, and, in particular, energy requirements. As usual, the key impact of these requirements is that they greatly constrain acceptable security solutions. The most important security requirements include authentication and tracking, data and information integrity, mutual trust, privacy, and digital forgetting. We expect that a dominant percentage of computational sensing, decision making, communication, and activity organization will be conducted in data centers. Hence, there is a need for ensuring security in data centers as well coordinating security between data centers and distributed IoT devices [16].

Since many IoT systems will require very minimal hardware and constrained energy budgets, they will also require ultra compact security solutions with an ultra small footprint. This is also especially so since many IoT devices will operate in physically accessible, unprotected, and even potentially hostile environments.

#### **1.3** Contributions and Organization

Table 1.1 highlights the major contributions and organization of this dissertation. We present both low energy design methods as well as new security applications. These two aspects of design are not only the premier design requirements for resource-constrained IoT systems, but they also present unique challenges due to their inherent conflicting requirements (e.g. higher security often requires higher power).

We organize our energy reduction techniques into two categories. The first consists of design and operational techniques applied on the integrated circuit. The second set of techniques are applied at a higher level of abstraction which encompasses system-level components, such as individual sensor nodes or harvesters.

We begin by presenting our circuit-level design techniques for energy reduction. Specifically, we advocate for the use of near-threshold computing (NTC). NTC is a technique that provides significant energy savings at the cost of performance degradation and an increase in sensitivity to process variation. It is very well suited for resource-constrained IoT applications both due to its ultralow energy consumption as well as due to the low processing power required by many IoT applications. However, the issues surrounding NTC—most notably, performance degradation and sensitivity to process variation—must be mitigated first in order to ensure its applicability to the IoT domain. In Chapter 2 we present techniques to lessen the impact of NTC's sensitivity to process variation through device aging; a technique that physically alters the threshold voltages of transistors. In Chapter 3 we propose techniques to mitigate the performance degradation effect of NTC through the use of adaptive body biasing; a technique that alters the threshold voltage of a group of gates post-silicon. In Chapter 4 we continue to focus on improving the performance of NTC circuits, but reduce the scope of the relevant applications to those which employ the popular low power and fast multiple constant multiplication hardware architecture commonly used for applications such as image and video processing and radio transmission.

In Chapters 5 and 6 we present system-level design, organizational, and operational techniques for the realization of low power IoT systems. Specifically, we capitalize on the semantic nature of IoT devices in order to reduce the size and number of system components as well as develop subsampling configurations in order to reduce total energy consumption. We also present techniques for energy harvester placement and operation in order to create a self sufficient device. In both of these chapters we apply our techniques to a wearable health device for analysis.

The final chapters of this dissertation present a number of security solutions for IoT. These solutions are categorized under both circuit and system because while they are, for the most part, implemented at the circuit-level, the results are observed and organized in both a circuit-level and system-level context. The techniques we present include hardware obfuscation, which ensures intellectual property protection and trusted remote sensing, as well as techniques for trusted chip selection, which enables anyone to validate that a particular chip was fabricated at a trusted foundry.

|          | Circuit                                                                                                                                                                                                                                    | System                                                                                                                                                                                      |  |  |  |  |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Energy   | <ul> <li>Ultralow power operation using NTC and device aging (ch. 2)</li> <li>Mitigating the adverse delay effects of NTC using adaptive body biasing (ch. 3)</li> <li>Ultralow power implementations of linear systems (ch. 4)</li> </ul> | <ul> <li>Semantic-based component<br/>reduction (ch. 5)</li> <li>Semantic-based subsampling<br/>configuration (ch. 5)</li> <li>Spatiotemporal harvester as-<br/>signment (ch. 6)</li> </ul> |  |  |  |  |

| Security | <ul> <li>Intellectual property protection (ch. 7)</li> <li>Trusted remote sensing (ch. 7)</li> <li>Trusted IC selection (ch. 8)</li> </ul>                                                                                                 |                                                                                                                                                                                             |  |  |  |  |

Table 1.1: Major contributions and organization of the dissertation.

# CHAPTER 2

# Energy Reduction through Coordinated Device Aging and NTC

In this chapter we present circuit-level design techniques for energy reduction in IoT systems. We apply the near-threshold computing paradigm in order to reduce energy consumption dramatically. NTC is a technique applied to integrated circuits in which the supply voltage is set to approximately the threshold voltage of the transistors. Since switching power of a transistor is proportional to the square of the supply voltage, any reduction in supply voltage produces quadratic gains in energy savings. Specifically, NTC has been shown to achieve energy savings comparable to sub-threshold operation while maintaining more favorable performance characteristics [17]. Many IoT systems which interact with the physical world are ideal for NTC because speed is rarely of great benefit while low energy is absolutely paramount. Many systems, for example, do not require high powered processors for data computation, but instead rely on offloading heavily intensive computational tasks to data centers.

The main obstacle to effectively apply NTC is process variation. A single gate in an IC with a low  $V_{th}$  forces operation of the circuit at a low  $V_{gnd}$  and a single gate with a high  $V_{th}$  forces operation of the circuit at a relatively high  $V_{dd}$ . Since the switching energy of the gates in a circuit is a function of  $(V_{dd} - V_{gnd})^2$ , the tails on the low ends and high ends of the threshold voltage distribution are ultimately responsible for superfluous energy consumption.

In order to reduce this effect, we propose the use of device aging to effectively shift the  $V_{th}$  values of the lower gates to higher values [18]. While this slows individual gates, we benefit from an overall energy reduction over the entire circuit by enabling the increase of  $V_{gnd}$ . Furthermore, the majority of gates are often not on the critical path, so aging often has no impact on circuit delay. However, if it is crucial that a gate on the critical path is aged (thus increasing circuit delay), we subsequently increase  $V_{dd}$  to return the circuit to its original delay, before returning to aging minimum  $V_{th}$  gates.

Furthermore, we recognize that application specific integrated circuit (ASIC) solutions are often not always the most cost efficient means in which to realize subsystem designs for IoT applications. Field-programmable gate arrays (FP-GAs), on the other hand, offer much more flexibility and do not require large upfront capital costs and are popular IoT prototyping platforms. Hence, we propose new aging and placement techniques for FPGA energy minimization that capitalizes on the FPGA block architecture.

## 2.1 Preliminaries

#### 2.1.1 Process Variation

Gate delays and effective channel lengths in nanoscale technologies are subject to significant process variation [19] [20]. A variety of manufacturing faults emerge as a result, including but not limited to variations in doping concentrations, imperfect mask alignment, and molecular chemical and physical phenomena. These forms of process variation manifest as the deviation of IC characteristics from nominal values. For example, variations in doping concentrations and line edge roughness alter transistor threshold voltages and effective channel lengths. These manifestations have been thoroughly studied, categorized, and modeled, yet continue to be of paramount concern [21] [22].

#### 2.1.2 Near-Threshold Computing

In modern circuitry, energy consumption and delay is often managed by altering the supply voltage relative to ground. Since the relationship between energy and voltage is quadratic, voltage scaling has become one of the most effective and researched methods for integrated circuit power reduction [23].

Energy consumption is comprised of two components, switching energy and leakage energy, each of which are functions of the supply voltage,  $V_{dd}$ . These energy components are also dependent on other physical characteristics of each transistor, expressed through Equations 2.1 and 2.2 with respective parameters and constants defined by Dreslinksi et al. [17]. What most distinguishes these two components from one another is that switching is a function of  $V_{dd}$  and  $V_{gnd}$ while leakage energy is a function of  $V_{dd}$  and  $V_{th}$ .

$$P_{switching} = \alpha \cdot C_{ox} \cdot W \cdot L \cdot (V_{dd} - V_{gnd})^2$$

(2.1)

$$P_{leakage} = 2 \cdot n \cdot \mu \cdot C_{ox} \cdot \frac{W}{L} \cdot \phi_t^2 \cdot D \cdot V_{dd} \cdot e^{\frac{\sigma \cdot V_{dd} - V_{th}}{n \cdot \phi_t}}$$

(2.2)

Today, the vast majority of circuits operate in the super-threshold region where  $V_{dd} \gg V_{th}$ . Chandrakasan's ultradynamic voltage scaling techniques operate in this region [24]. Here, switching is the dominant component of energy consumption. Traditional techniques for energy reduction apply voltage scaling at the cost of increased delay. In order to increase the speed of the circuit,  $V_{dd}$  is raised, thus increasing the gap between  $V_{dd}$  and  $V_{th}$ , and reducing the delay of the device components as defined by equation 2.3.

$$Delay = \frac{k_{tp} \cdot k_{fit} \cdot L_{eff}^2}{2 \cdot n \cdot \mu \cdot \phi_t^2} \cdot \frac{V_{dd}}{(ln(e^{\frac{(1+\sigma)V_{dd} - V_{th}}{2 \cdot n \cdot \phi_t}} + 1))^2} \cdot \frac{\gamma_i \cdot W_i + W_{i+1}}{W_i}$$

(2.3)

Techniques for sub-threshold operation of circuits in which  $V_{dd} < V_{th}$  have been proposed [25] [26]. Operation in this region returns substantially higher energy savings than operation in the super-threshold region. However, as  $V_{dd}$  extends below  $V_{th}$ , marginal energy savings reduces by an order of magnitude while performance penalties increase substantially (50-100×) [17]. Leakage energy also becomes a dominant component of overall energy usage. Thus, sub-threshold operation has become useful for niche applications due to its degraded performance metrics [27].

The most balanced tradeoffs between energy reduction and performance degradation are found in the near-threshold region where  $V_{dd} \sim V_{th}$  [17]. Here, energy savings are 10× that of super-threshold operation while performance degradation is similar to sub-threshold operation.

Numerous design challenges have emerged as a result of NTC [28]. Most notably, NTC circuits are highly susceptible to variability due to their nearthreshold operation. Inherent variations in manufacturing processes affect threshold voltage distributions, thus imposing design constraints at near-threshold. Take for example Figure 2.1. In the near-threshold case the supply voltage must be carefully set so that it does not accidentally disable any gate on the right tail of the curve. Furthermore, potential voltage fluctuations during operation must also be accounted for. In the super-threshold case, process variation has

Figure 2.1: Example distribution of threshold voltages due to process variation. In the top figure the supply voltage is set in the super-threshold region where process variation has very little impact on operation. In the bottom figure process variation must be taken into account when setting the supply voltage in the near-threshold region.

little to no impact on supply voltage setting and handling of fluctuations. Postsilicon techniques have been proposed to mitigate the effects of process variation on NTC through body-biasing, soft-edge clocking, and employing dual supply voltages [28] [29], while device aging techniques have not yet been proposed.

### 2.1.3 Device Aging

Negative bias temperature instability and hot-carrier injection phenomena can cause significant alterations to the delay characteristics of individual gates [18] [30] [31] [32]. Systematic and constant stressing of gates can irreversibly alter the physical characteristics of the gates, resulting in an increase in their threshold voltages. While device aging is widely considered to be a detrimental effect in the lifetime and operation of general circuitry, we utilize it to our advantage in NTC-operated circuits for overall energy reduction. This is possible because switching energy is a function of the difference between  $V_{dd}$  and  $V_{gnd}$ . By aging individual gates we can alter this distribution post-silicon in such a way that enables a reduction in switching energy.

#### 2.1.4 Gate Level Characterization

Gate level characterization (GLC) techniques can be classified into four major groups: direct measurement approaches, schemes that employ FPGA reconfiguration, approaches that create and observe special IC structures and specialized circuity, and non-destructive techniques that construct global measurements and deduce scaling factors of each gate by solving a system of equations [33] [34] [35].

Direct measurement techniques use atomic force microscopes, electric line measurements, and optical instruments to directly measure critical dimensions (e.g. effective channel length) [33]. They are very accurate and have a wide range of speeds, however their application is often restricted to just dimensions measurements.

FPGA GLC techniques include the iterative creation of clock measurement circuitry that isolate individual blocks [34]. Other techniques include populating chips with structures such as ring oscillators that can be easily characterized through clock sweeping and counting methods [36]. The limitations of these techniques is that they can only be applied to specific types of designs.

Non-destructive GLC techniques include those that do not use any spatial correlation assumptions [35], and those that do. While these techniques are universally applicable with zero overhead and low cost, up until now they were not scalable and not able to characterize significant percentage of gates.

In general, GLC techniques are expensive. Hence, while we present methods

for coordinated device aging and NTC operation on ASIC circuits, which require GLC, in this chapter we focus primarily on methods derived specifically for FPGA platforms, which do not require any expensive GLC techniques.

## 2.2 Motivation and Problem Formulation

In this section we present the first approach for energy and power minimization in FGPA-based systems using device aging. We begin by explaining the motivation and our assumptions, and follow up with a presentation of our problem formulation. We explain the key optimization ideas in the new approach and present a description of our overall approach. And finally, we present a simulation-based study that indicates that energy minimization in FPGAs can be very effective.

There are a number of reasons why studying energy minimization in FPGAbased sensing systems is important. The first is that ASIC-based systems very often have unacceptable preproduction costs that can reach up to tens of millions of dollars. This means that even before the first ASIC-based sensing system is realized, one has to invest around \$30 million dollars just to cover design, testing, and validation.

An alternative to ASIC-based sensing systems is to use more general purpose microprocessors or microcontrollers. However, a serious downfall of these systems is that optimizing general purpose processors for time and energy is often complex and cumbersome.

FPGAs do not impose any non-production costs on the designer and have an unprecedented level of flexibility. Recent developments have put FPGAs at the frontier of integrated systems in terms of both their feature size as well as their potential for integration. For example, FPGA Spartan chips have more than 5.8 million transistors while only Nvidia's graphics processor has a larger number of switching elements. Recently, Xilinx announced that they implemented their newest family of FPGA's at TSMC facilities using 20nm technology. This announcement means that FPGAs now use more advanced and finer technologies than both ASICs and even microprocessors.

Our objective is to develop an approach that minimizes energy spent in FPGA-based subsystems. We employ two generic mechanisms. The first is to use device-based aging for the alternation of FPGA component speeds. Specifically, we consider slices and blocks as basic structures in FPGAs and simultaneously age all transistors in a particular slice. The key observation here is that the FPGA will operate in NTC mode and therefore have a very low energy budget.

The second degree of freedom is that in almost all situations, the size of the actual design is significantly smaller than the capacity of the full FPGA. Therefore, we can move each program component by the same horizontal and vertical shift, thus moving the boundaries of the program design to a number of locations. In such a way, we can place the program in a position to avoid using slices that have transistors with threshold voltages that are not amenable for energy efficiency. Specifically, our goal is to select slices in such a way that the highest threshold voltage in any of them is as low as possible while the lowest is as high as possible. In this type of system, we reduce the voltage swing and hence reduce energy quadratically. These two mechanisms, device aging and selection of slices that only have favorable threshold voltages, are combined in such a way that achieves provably optimum minimum energy.

The key observation is that all slices can be normalized by setting them such that the highest threshold voltages among all of them are equal. This is accomplished using non-uniform device aging as dictated by process variation. An additional and important observation is that transistor-level characterization of slices can be accomplished without using any already proposed and effective but often expensive gate level characterization techniques. We employ a new binary search technique that distinguishes between correctly operating slices and incorrectly operating slices due to either high threshold voltages that prevent low supply voltage or low threshold voltages that prevent high ground voltage. Once we characterize each slice, we search for slices that are adjacent to one another in order not to jeopardize the critical path of the design while excluding slices which have gates with too low of a threshold voltage in their structure.

Our process variation model has two components. In the first we use Asenov's model indicating that threshold voltages are proportional to the number of dopants, and therefore, follow an independent Gaussian distribution [18]. The second component corresponds to the effective channel length of transistors and follows Cline's model that includes information about correlations that are typical for modern integrated circuits [19].

#### 2.3 Energy Reduction

In this section we describe in detail our techniques for energy minimization employing near-threshold computing and utilizing device aging for both ASIC and FPGA systems.

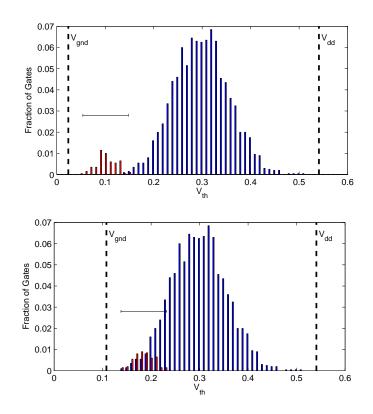

A typical post-fabrication distribution of threshold voltages for the s38584 benchmark circuit is depicted in Iteration 0 of Figure 2.2. Ultimately, the left and right tails of the distribution are most responsible for forcing the relatively high and low setting of  $V_{dd}$  and  $V_{gnd}$ , respectively. In order to minimize this voltage swing and thus reduce circuit switching energy we aim to increase the

Figure 2.2: Gate  $V_{th}$  distributions of s38584 from the ISCAS'89 benchmark suite [37].  $V_{dd}$  remains at a near-threshold voltage just above the highest  $V_{th}$  gate while  $V_{gnd}$  is set to a near-threshold voltage just below the lowest  $V_{th}$  gate. After aging the lowest 600 gates we can increase  $V_{gnd}$  and reduce overall circuit switching energy.

threshold voltages of the gates that comprise the lower tail, thus enabling a higher setting of ground. This is achieved by iteratively aging gates corresponding to the minimum threshold voltage across the circuit to that gate's maximum extent. In the case that a gate on the critical path is selected and subsequently aged, thus increasing the overall circuit delay, we adjust the supply voltage until we return to the original delay before returning to aging.

Figure 2.3 depicts the energy savings relative to normal super-threshold operation. NTC alone provides 45-60% energy savings while our techniques reduce energy consumption by an additional 15%.

In order to apply our aging-based energy minimization methods to the FPGA

Figure 2.3: ASIC energy reduction applied using iterative minimum  $V_{th}$  aging on circuits from the ISCAS'85 and ISCAS'89 benchmark suites [37] [38].

we must first characterize the maximum and minimum threshold voltages of each slice. Existing GLC solutions are expensive and overly detailed for our purposes. Thus, we introduce a new and inexpensive binary search technique for FPGA slice characterization. For the purposes of energy minimization of the FPGA using NTC, we need only to know the minimum and maximum threshold voltages within a single slice. We measure these values by varying the supply and ground voltages until the slice is operational. This technique is described in detail in Algorithm 1.

Herein, we denote the maximum and minimum threshold voltages at a particular slice i as  $V_{th}^{max}(i)$  and  $V_{th}^{min}(i)$ . Once all FPGA slices are characterized we perform coarse grained per slice aging by stressing all gates in a particular slice uniformly. This is performed on each slice individually in order to match  $V_{th}^{max}(i)$  to the FPGA-wide maximum threshold voltage. This will simultaneously increase the values of  $V_{th}^{min}$  across all slices non-uniformly according to each slice's particular  $V_{th}^{max}$ . This change is depicted in Figure 2.4. Now, in order to minimize energy, we find a subset of physically adjacent tiles (as required by the layout of the program) whose minimum  $V_{th}^{min}$  among all covered slices is largest among all possible placements, thus reducing the voltage swing and quadratically reducing energy consumption. This is possible because most programs use a fraction of the total FPGA space. We iteratively disable slices containing the minimum  $V_{th}^{min}$  over all slices, until it is no longer possible to position the program on the FPGA board without covering a disabled slice. The last disabled slice that prevented the program from being positioned is then

#### Algorithm 1 FPGA Slice Characterization

**Require:**  $0 < \epsilon < V_{and} \leq V_{dd}$ 1:  $\delta \leftarrow +1$ 2:  $\Delta \leftarrow V_{dd}$ 3: while  $\epsilon < \Delta$  or  $!circuit.IsOperational(V_{dd}, V_{qnd})$  do  $V_{dd} \leftarrow V_{dd} + \delta \Delta$ 4: if  $\delta = +1$  and *circuit.IsOperational*( $V_{dd}, V_{and}$ ) then 5: $\delta \leftarrow -1$ 6:  $\Delta \leftarrow \Delta/2$ 7: else if  $\delta = -1$  and  $!circuit.IsOperational(V_{dd}, V_{qnd})$  then 8:  $\delta \leftarrow +1$ 9:  $\Delta \leftarrow \Delta/2$ 10: end if 11: 12: end while 13:  $\delta \leftarrow +1$ 14:  $\Delta \leftarrow V_{and}$ 15: while  $\epsilon < \Delta$  or  $!circuit.IsOperational(V_{dd}, V_{qnd})$  do  $V_{qnd} \leftarrow V_{qnd} + \delta \Delta$ 16:if  $\delta = +1$  and  $!circuit.IsOperational(V_{dd}, V_{and})$  then 17: $\delta \leftarrow -1$ 18: $\Delta \leftarrow \Delta/2$ 19:else if  $\delta = -1$  and *circuit.IsOperational*( $V_{dd}, V_{and}$ ) then 20:  $\delta \leftarrow +1$ 21: 22:  $\Delta \leftarrow \Delta/2$ 23: end if 24: end while 25: return  $V_{dd}, V_{and}$

Figure 2.4: (a) Distributions of maximum and minimum threshold voltages found in slices of a typical FPGA board. (b) Distribution of minimum threshold voltages across FPGA slices after aging. The dotted line represents the maximum threshold voltage of each slice.

re-enabled. We subsequently iterate over all possible valid program assignments. The final assignment corresponds to the position in which the slices covered by the program at that location has a minimum  $V_{th}^{min}$  that is largest among all possible positions, thus yielding the smallest operational voltage swing between  $V_{dd}$  and  $V_{gnd}$  and providing the lowest energy utilization.

We compare the energy savings of our techniques for aging and placement against an NTC-operated FPGA with and without aging. We present our results in Figure 2.5. Our technique achieves energy savings of up to 35% against the aged FPGA and 75% to 84% against the traditionally operated non-aged FPGA.

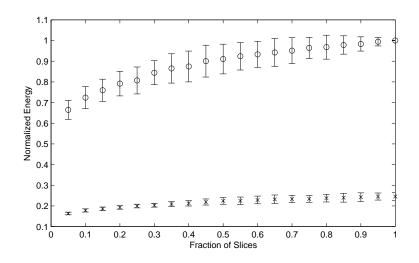

Figure 2.5: FPGA energy consumption of varying sized programs as compared to (o) the case in which the FPGA slices are aged and operated at the maximum  $V_{th}^{max}$  and the minimum  $V_{th}^{min}$  over all slices; and (x) the case in which the FPGA is operated without aging at the maximum  $V_{th}^{max}$  and minimum  $V_{th}^{min}$  over all slices. Error bars correspond to the standard deviation over all simulated FPGA instances.

# 2.4 Summary

Our new approach for the creation of energy efficient subsystems employs the near-threshold computing paradigm on both ASIC—where aging is conducted at the gate-level granularity—as well as on FPGAs—where aging is applied at the slice-level granularity. We have achieved energy reduction of up to  $2.9 \times$  over popular ASIC benchmark circuits and up to  $6 \times$  over traditional operation of FPGAs.

# CHAPTER 3

# Adaptive Body Biasing for Reclaiming Speed in NTC

For some systems, such as a majority of physical remote sensor networks, the increase in delay imposed by near-threshold operation is of no consequence since these systems often rely on sampling frequencies on the order of megahertz which is easily attainable, even using NTC, for current node technologies today. However, for a great majority of applications, NTC is difficult to adopt due to the huge increase in delay it imposes on the application.

In this chapter, we mitigate the effects of NTC on the overall delay of a circuit and reclaim some of that lost speed. This is accomplished while maintaining that the energy savings originally gained through NTC operation are not lost. Our techniques utilize inherent differences in process variations coupled with adaptive body biasing (ABB) in order to speed up the critical path gates, thus reducing overall circuit delay, while not affecting overall switching energy. ABB is a postsilicon technique that enables the temporary tuning of physical characteristics of a selection of gates. Essentially, the effective threshold voltage,  $V_{th}$ , of a biased gate is shifted according to the applied bias voltage. Note that while the effective threshold of these gates can be altered post-silicon, the assignment of gates to a particular ABB group must be done pre-silicon.

Our approach assumes that both the supply voltage and ground voltage are

operated at near-threshold. We select those gates that are most commonly on the critical path during NTC operation and bias them in order to reduce their delay and the overall delay of the circuit.

Furthermore, selection of critical path gates is a non-trivial task since process variation has a chaotic effect on critical path assignment when operating at nearthreshold voltages. We propose both a static solution and an iterative solution for critical path gate selection pre-silicon and compare their results. Our approach is the first of our knowledge to incorporate ABB for circuit speedup in NTC.

## 3.1 Preliminaries

#### 3.1.1 Near-Threshold Computing

Energy consumption in modern CMOS circuits can be minimized quadratically by lowering supply voltage relative to ground. As a consequence, voltage scaling techniques have become one of the most effective methods and widely researched topics in IC power reduction [23].

Operating in the near-threshold region  $(V_{dd} \sim V_{th})$  has been demonstrated to offer balanced trade-offs between energy reduction  $(10\times)$  and performance degradation  $(10\times)$  as compared to super-threshold  $(V_{dd} > V_{th})$  and sub-threshold  $(V_{dd} < V_{th})$  operation [17]. While NTC offers desirable levels of energy efficiency, it has also introduced numerous design challenges [28] [39]. Most notably, due to near-threshold operation and the variability of circuit threshold voltages (due to process variations), NTC circuits are highly susceptible to variability.