## **UC San Diego**

## **UC San Diego Electronic Theses and Dissertations**

#### **Title**

Method and architecture design for motion compensated frame interpolation in highdefinition video processing

#### **Permalink**

https://escholarship.org/uc/item/3xz7x1jf

#### **Author**

Lee, Yen-Lin

#### **Publication Date**

2009

Peer reviewed|Thesis/dissertation

#### UNIVERSITY OF CALIFORNIA, SAN DIEGO

#### Method and Architecture Design for Motion Compensated Frame Interpolation in High-Definition Video Processing

A dissertation submitted in partial satisfaction of the requirements for the degree

Doctor of Philosophy

in

Electrical Engineering (Electronic Circuits and Systems)

by

Yen-Lin Lee

#### Committee in charge:

Professor Truong Nguyen, Chair Professor Yoav Freund Professor Rajesh Gupta

Professor William Hodgkiss

Professor Nuno Vasconcelos

2009

Copyright

Yen-Lin Lee, 2009

All rights reserved.

| The dissertation of Yen-Lin Lee is approved, and     |

|------------------------------------------------------|

| it is acceptable in quality and form for publication |

| on microfilm and electronically:                     |

|                                                      |

|                                                      |

|                                                      |

|                                                      |

|                                                      |

|                                                      |

|                                                      |

|                                                      |

|                                                      |

|                                                      |

| Chair                                                |

University of California, San Diego

## DEDICATION

To my family

## TABLE OF CONTENTS

|   | Signature Page ii                      |

|---|----------------------------------------|

|   | Dedication                             |

|   | Table of Contents                      |

|   | List of Figures                        |

|   | List of Tables xi                      |

|   | Acknowledgements xii                   |

|   | Vita and Publications                  |

|   | Abstract of the Dissertation           |

| 1 | Introduction                           |

| 2 | Motion Compensated Frame Interpolation |

| 3 | The Proposed MCFI Method               |

| 4 | The Proposed MCFI Architecture         |

| 5  | MCH<br>5.1<br>5.2<br>5.3                | Implementation and Experimental Results                                                     | 37<br>39                                                       |

|----|-----------------------------------------|---------------------------------------------------------------------------------------------|----------------------------------------------------------------|

| 6  | MCF<br>6.1<br>6.2                       | FI System Analysis                                                                          | 50<br>50                                                       |

| 7  | High<br>7.1<br>7.2<br>7.3<br>7.4<br>7.5 | Frame Rate Up Conversion Processing                                                         | 53<br>58<br>63<br>65                                           |

| 8  | Cond                                    | elusions                                                                                    | 73                                                             |

| A  | A.1<br>A.2<br>A.3<br>A.4<br>A.5         | ysis and Efficient Architecture Design for VC-1 Overlap Smoothing In-loop Deblocking Filter | 74<br>76<br>76<br>77<br>78<br>81<br>83<br>87<br>89<br>94<br>94 |

|    | A.6                                     | Conclusions                                                                                 | 98                                                             |

| Ri | hliogr                                  | anhy                                                                                        | 100                                                            |

## LIST OF FIGURES

| 0                       | Motion Compensated Frame Interpolation with block-based motion search                                                             | 2        |

|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------|----------|

| _                       | The difference between the eye tracking trajectory and the actual displayed data with zero response time. (a) Original            |          |

| f                       | frame rate. (b) Twice the original frame rate                                                                                     | 6        |

| 1                       | Motion vector processing method                                                                                                   | 6        |

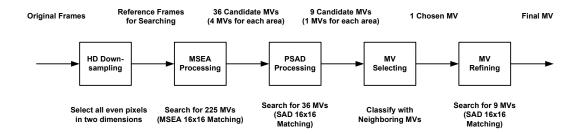

| Figure 3.1: Figure 3.2: | Processing flow of the proposed method                                                                                            | 11       |

| 0                       | (b) Proposed bidirectional search                                                                                                 | 13       |

| Figure 3.3:             | Nine-directional enlarged matching method                                                                                         | 15       |

| Figure 3.4:             | Nine-directional enlarged matching method with type 4                                                                             | 16       |

| _                       | Direct multi-directional enlarged matching method (a) Match-                                                                      |          |

|                         | ing window and interpolated block in a previous frame t. (b)                                                                      |          |

|                         | Matching window and interpolated block in a successive frame                                                                      | 17       |

|                         | t+1                                                                                                                               | 17<br>19 |

| 0                       | Multi-grids Classification in a searching window                                                                                  | 20       |

| _                       | Multi-directional enlarged bidirectional search algorithm with                                                                    | 20       |

| ~                       | temporal information                                                                                                              | 21       |

|                         | Motions on the previous frame and the current block motion                                                                        |          |

| 6                       | are employed on sub-block assignment                                                                                              | 24       |

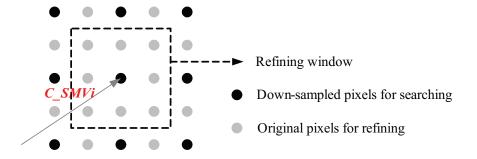

| -                       | Motion vector refining window                                                                                                     | 25       |

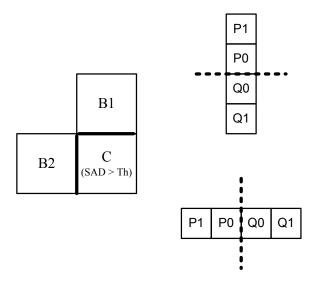

| Figure 3.11:            | Two edges of the current interpolated block C are filtered                                                                        | 26       |

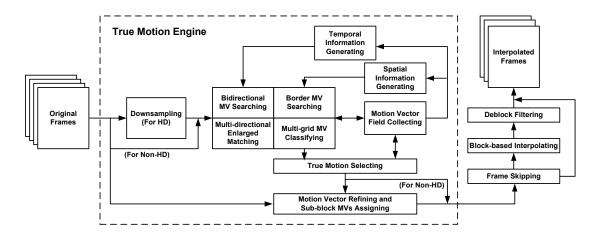

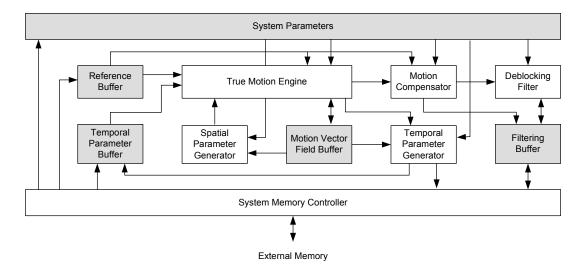

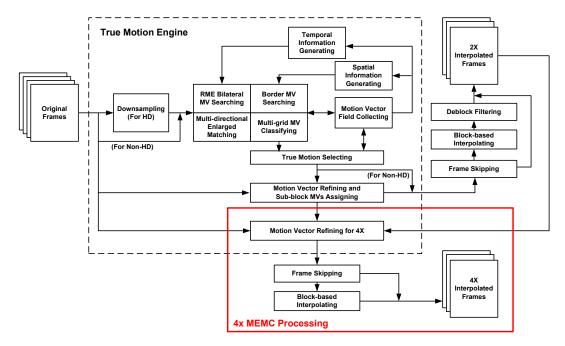

| Figure 4.1:             | System block diagram of the proposed architecture                                                                                 | 29       |

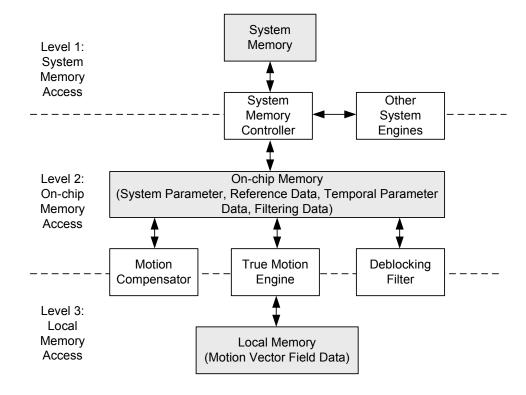

| Figure 4.2:             | Three levels of memory access for the proposed architecture                                                                       | 30       |

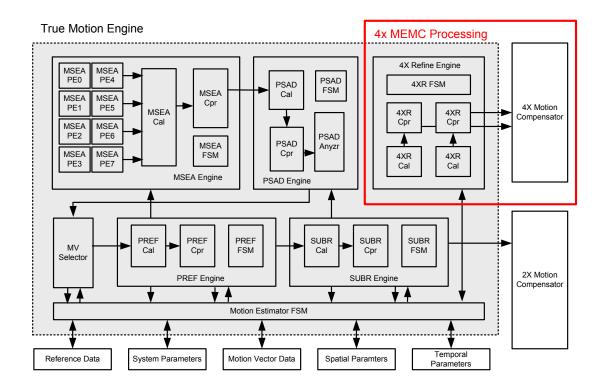

| Figure 4.3:             | Block diagram of the proposed true motion engine                                                                                  | 31       |

| ~                       | Processing flow of the proposed true motion engine                                                                                | 32       |

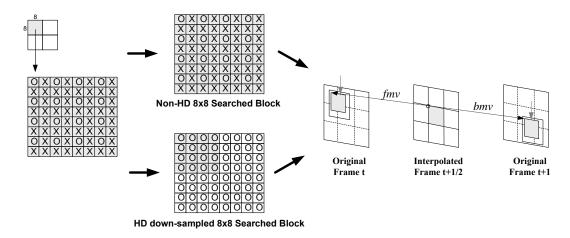

| _                       | HD downsampling - drop all odd pixels in two dimensions                                                                           | 32       |

| _                       | Multi-level Successive Elimination Algorithm (MSEA)                                                                               | 33       |

| 0                       | MSEA searches four true motion candidates for each area                                                                           | 34       |

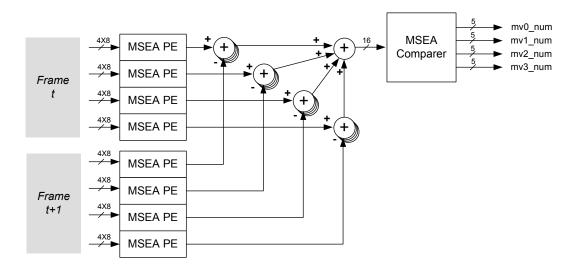

| _                       | Architecture of the proposed MSEA engine                                                                                          | 34       |

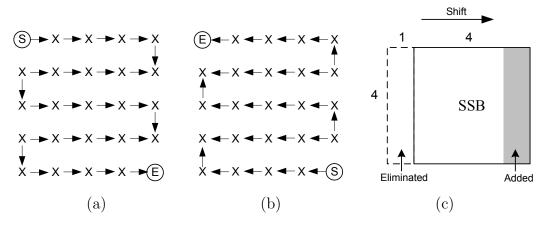

| Figure 4.9:             | (a) Searching order on an area for a previous frame $t$ . (b) Searching order on an area for a successive frame $t+1$ . (c) Added |          |

|                         | and eliminated areas when shifting a MSEA vector position                                                                         | 35       |

|                         | Pipeline scheduling for the proposed architecture                                                                                 | 36       |

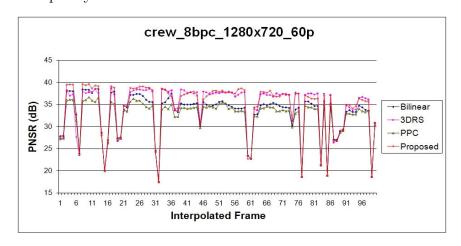

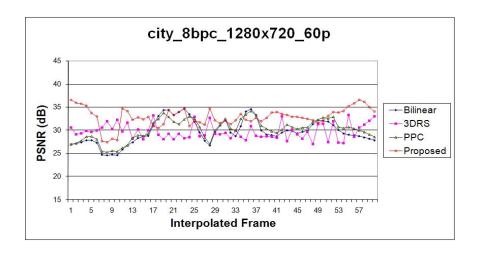

| Figure 5.1:             | PSNR comparison 1 - CREW 1280×720 60fps                                                                                           | 40       |

| Figure 5.2:  | PSNR comparison 2 - CITY $1280 \times 720 60$ fps               | 40 |

|--------------|-----------------------------------------------------------------|----|

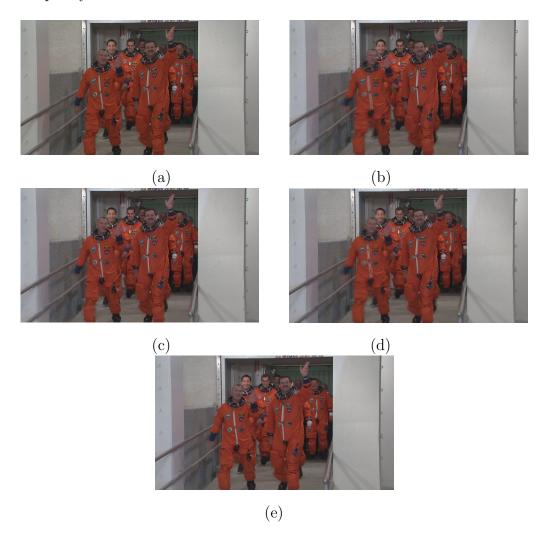

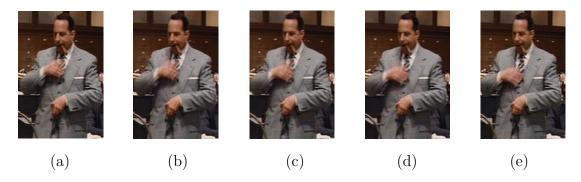

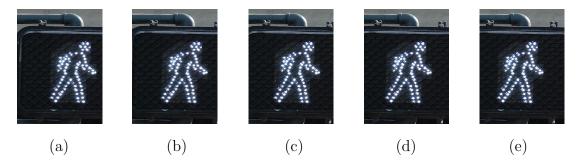

| Figure 5.3:  | Interpolated frame 185 in CREW (a) original frame, (b) bilinear |    |

|              | interpolation (21.2462 dB), (c) 3D Recursive Search (21.3463    |    |

|              | dB), (d) Phase Plane Correlation (21.2293 dB dB), (e) proposed  |    |

|              | method (21.3307 dB)                                             | 42 |

| Figure 5.4:  | Zoom in for interpolated frame 185 in CREW (a) original frame,  |    |

|              | (b) bilinear interpolation, (c) 3D Recursive Search, (d) Phase  |    |

|              | Plane Correlation, (e) proposed method                          | 43 |

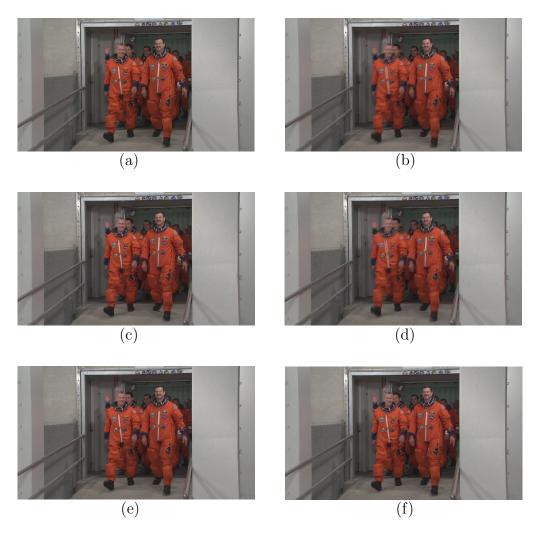

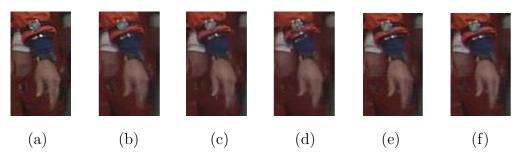

| Figure 5.5:  | Interpolated frame 117 in CREW (a) original frame, (b) bilin-   |    |

|              | ear interpolation, (34.287 dB) (c) 3D Recursive Search (37.756  |    |

|              | dB), (d) Phase Plane Correlation (33.418 dB), (e) proposed      |    |

|              | method (38.237 dB), (f) proposed method with sub_mv assign-     |    |

|              | ment (38.301 dB)                                                | 46 |

| Figure 5.6:  |                                                                 |    |

| O            | (b) bilinear interpolation, (c) 3D Recursive Search, (d) Phase  |    |

|              | Plane Correlation, (e) proposed method, (f) proposed method     |    |

|              | with sub_mv assignment                                          | 46 |

| Figure 5.7:  |                                                                 |    |

| 1 18010 0111 | interpolation (27.1726 dB), (c) 3D Recursive Search (29.0897    |    |

|              | dB), (d) Phase Plane Correlation (27.2179 dB), (e) proposed     |    |

|              | method (35.9651 dB)                                             | 47 |

| Figure 5.8.  | Zoom in for interpolated frame 2 in CITY (a) original frame,    |    |

| 1 1ga10 0.0. | (b) bilinear interpolation, (c) 3D Recursive Search, (d) Phase  |    |

|              | Plane Correlation, (e) proposed method                          | 47 |

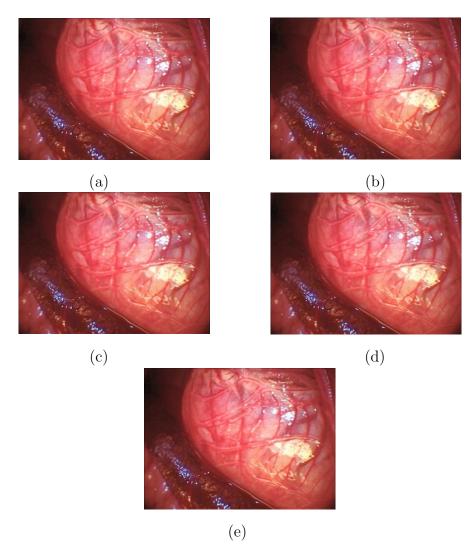

| Figure 5.9:  |                                                                 | 11 |

| rigure 9.9.  | lation, (b) 3D Recursive Search, (c) Phase Plane Correlation,   |    |

|              | (d) proposed method                                             | 48 |

| Figure 5.10  | 2: Zoom in for interpolated frame 267 in PRODUCERS (a) bi-      | 10 |

| 1 1gare 9.10 | linear interpolation, (b) 3D Recursive Search, (c) Phase Plane  |    |

|              | Correlation, (d) proposed method                                | 48 |

| Figure 5.11  | : Interpolated frame 353 in FLIGHT (a) bilinear interpolation,  | 10 |

| rigure 0.11  | (b) 3D Recursive Search, (c) Phase Plane Correlation, (d) pro-  |    |

|              | posed method                                                    | 49 |

| Figure 5.19  | 2: Zoom in for interpolated frame 353 in FLIGHT (a) bilinear    | 10 |

| rigare 5.12  | interpolation, (b) 3D Recursive Search, (c) Phase Plane Corre-  |    |

|              | lation, (d) proposed method                                     | 49 |

|              | iation, (d) proposed method                                     | 43 |

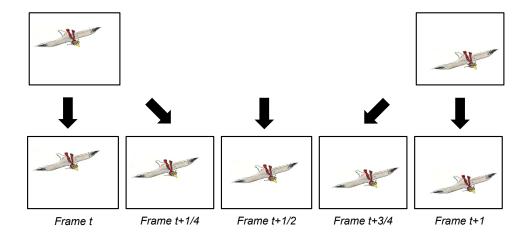

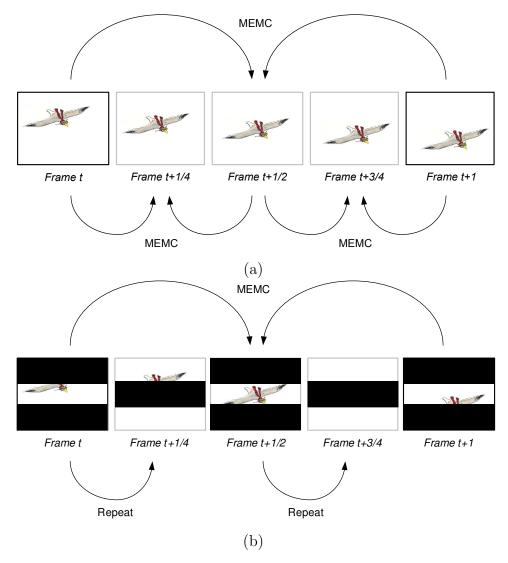

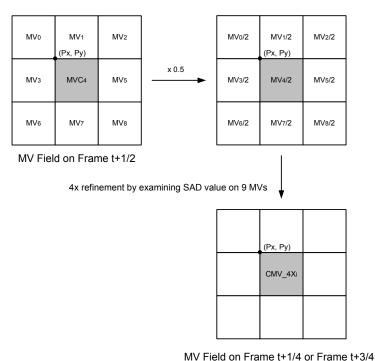

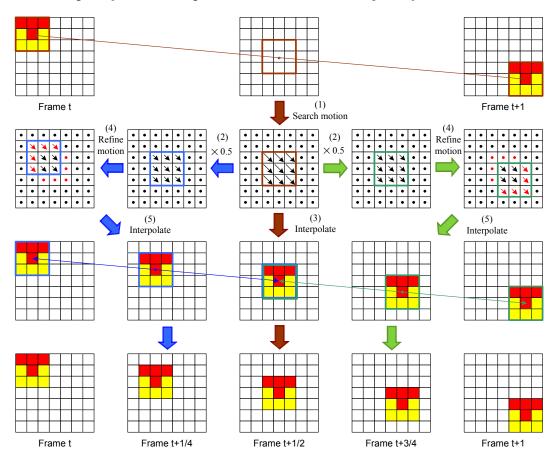

| Figure 7.1:  | An example of 4x Frame Rate Up Conversion                       | 54 |

| Figure 7.2:  | Two methods to achieve 4x Frame Rate Up Conversion. (a)         |    |

| <u> </u>     | Pure MEMC method. (b) MEMC method with backlight scan-          |    |

|              | ning                                                            | 55 |

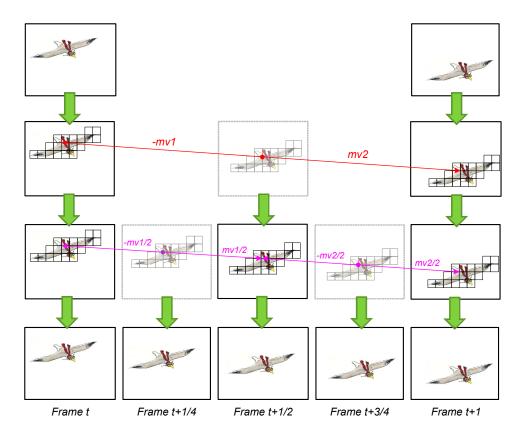

| Figure 7.3: MEMC method with motion trajectory to achieve 4x Frame         |   |

|----------------------------------------------------------------------------|---|

| Rate Up Conversion                                                         | ١ |

| Figure 7.4: MEMC method with motion trajectory to achieve 4x Frame         |   |

| Rate Up Conversion                                                         |   |

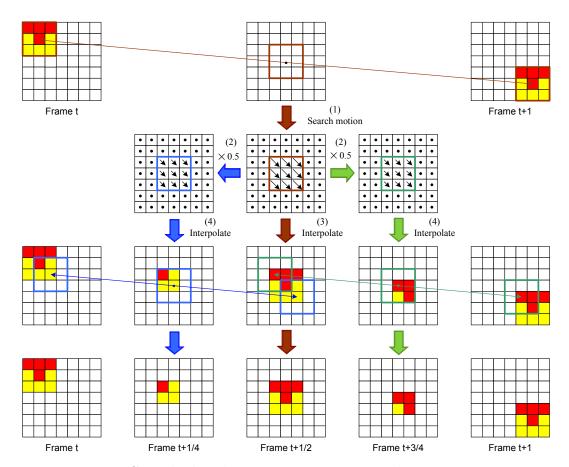

| Figure 7.5: Processing flow of the proposed method on 4x Frame Rate Up     | , |

| Conversion.                                                                | , |

| Figure 7.6: Proposed MEMC method with motion refinement to achieve         |   |

| 4x Frame Rate Up Conversion                                                | ( |

| Figure 7.7: Proposed MEMC method with motion refinement to achieve         |   |

| 4x frame rate up conversion                                                | ( |

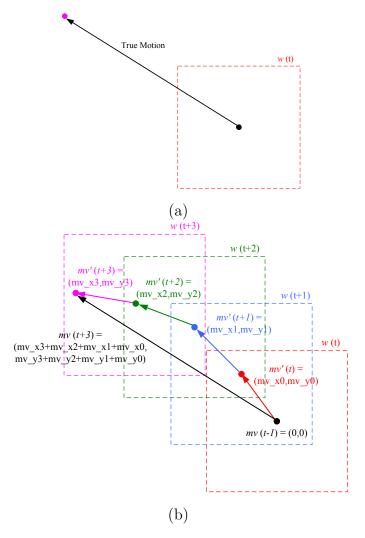

| Figure 7.8: (a) Normal true motion vector search. (b) Relative true motion |   |

| vector search                                                              | ( |

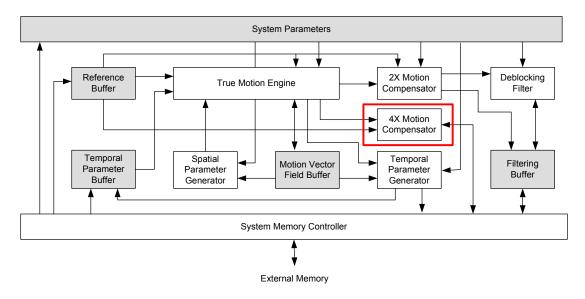

| Figure 7.9: System block diagram of the proposed 4x MCFI architecture.     | ( |

| Figure 7.10: Block diagram of the proposed 4x true motion engine           | ( |

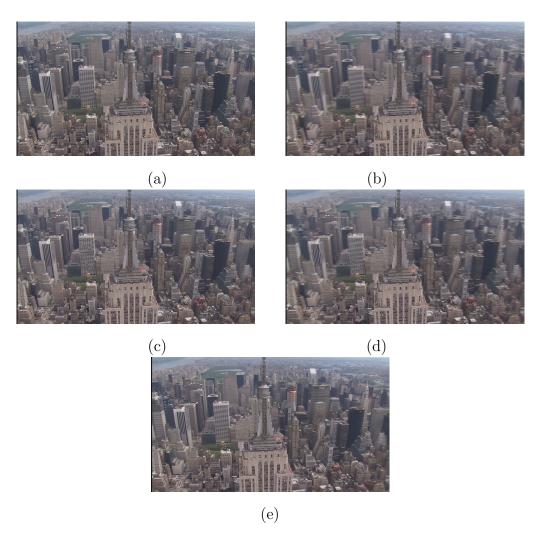

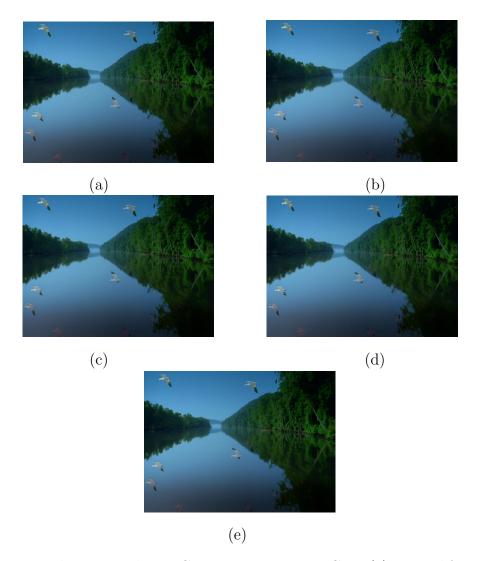

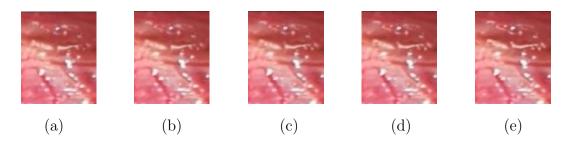

| Figure 7.11: The proposed 4x MCFI Processing in FLIGHT (a) original        |   |

| frame 924, (b) 4x interpolated frame 925, (c) 2x interpolated              |   |

| frame 926, (d) 4x interpolated frame 927, (e) original frame 928.          | ( |

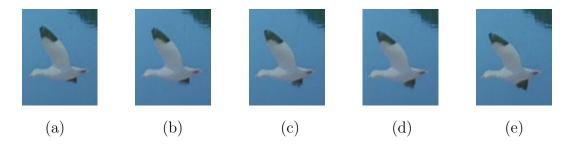

| Figure 7.12: Zoom in on the proposed 4x MCFI Processing in FLIGHT (a)      |   |

| original frame 924, (b) 4x interpolated frame 925, (c) 2x inter-           |   |

| polated frame 926, (d) 4x interpolated frame 927, (e) original             |   |

| frame 928                                                                  | ( |

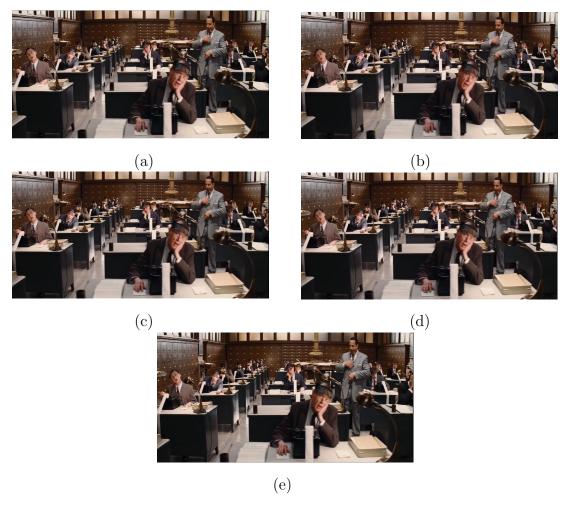

| Figure 7.13: The proposed 4x MCFI Processing in PRODUCERS (a) origi-       |   |

| nal frame 400, (b) 4x interpolated frame 401, (c) 2x interpolated          |   |

| frame 402, (d) 4x interpolated frame 403, (e) original frame 404.          | ( |

| Figure 7.14: Zoom in on the proposed 4x MCFI Processing in PRODUC-         |   |

| ERS (a) original frame 400, (b) 4x interpolated frame 401, (c)             |   |

| 2x interpolated frame 402, (d) 4x interpolated frame 403, (e)              |   |

| original frame 404                                                         | ( |

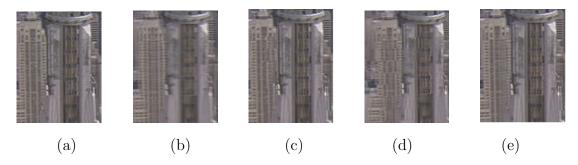

| Figure 7.15: The proposed 4x MCFI Processing in CAMCUT (a) original        |   |

| frame 132, (b) 4x interpolated frame 133, (c) 2x interpolated              | , |

| frame 134, (d) 4x interpolated frame 135, (e) original frame 136.          | , |

| Figure 7.16: Zoom in on the proposed 4x MCFI Processing in CAMCUT          |   |

| (a) original frame 132, (b) 4x interpolated frame 133, (c) 2x in-          |   |

| terpolated frame 134, (d) 4x interpolated frame 135, (e) original          | , |

| frame 136                                                                  | - |

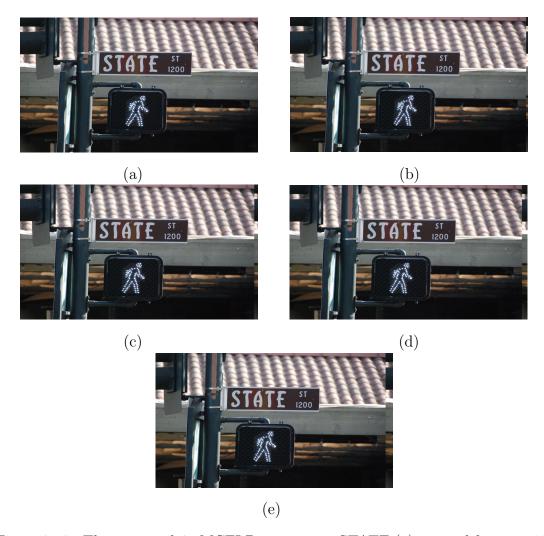

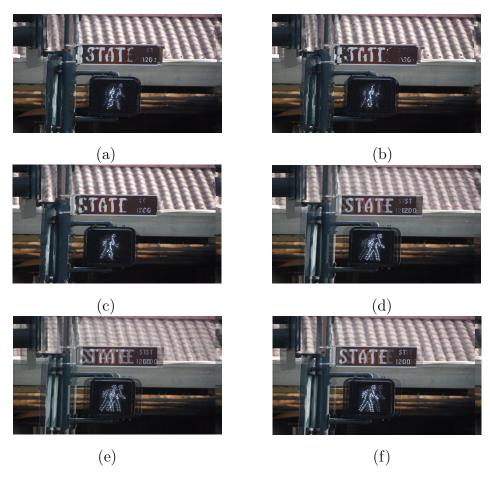

| Figure 7.17: The proposed 4x MCFI Processing in STATE (a) original frame   |   |

| 1580, (b) 4x interpolated frame 1581, (c) 2x interpolated frame            |   |

| 1582, (d) 4x interpolated frame 1583, (e) original frame 1584.             | - |

| Figure 7.18: Zoom in the proposed 4x MCFI Processing in STATE (a) orig-    |   |

| inal frame 1580, (b) 4x interpolated frame 1581, (c) 2x interpo-           |   |

| lated frame 1582, (d) 4x interpolated frame 1583, (e) original             |   |

| frame 1584                                                                 | - |

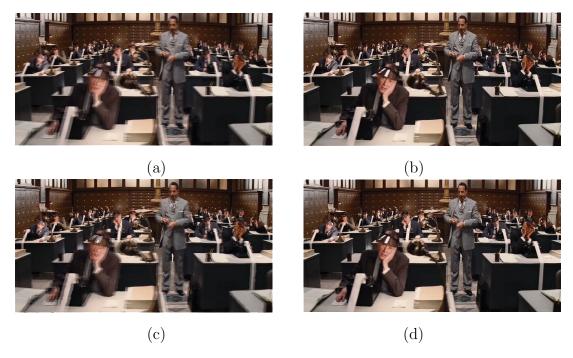

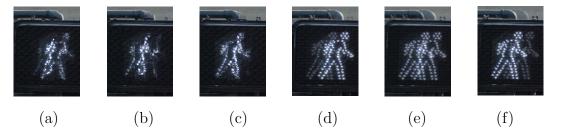

| Figure 7.19: 4x MCFI comparisons with incorrect motions and image averaging in STATE (a) 4x interpolated frame 1581 with incorrect motions, (b) 2x interpolated frame 1582 with incorrect motions, (c) 4x interpolated frame 1583 with incorrect motions, (d) 4x interpolated frame 1581 with averaging, (e) 2x interpolated frame 1582 with averaging, (f) 4x interpolated frame 1583 with averaging | 72       |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| Figure 7.20: Zoom in on the 4x MCFI comparisons in STATE (a) 4x interpolated frame 1581 with incorrect motions, (b) 2x interpolated frame 1582 with incorrect motions, (c) 4x interpolated frame 1583 with incorrect motions, (d) 4x interpolated frame 1581 with averaging, (e) 2x interpolated frame 1582 with averaging, (f) 4x interpolated frame 1583 with averaging                             | 72       |

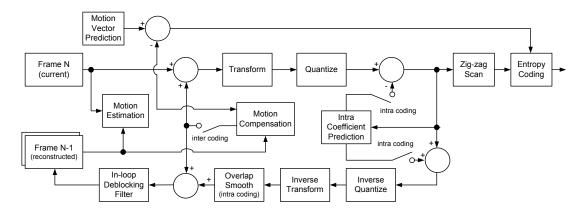

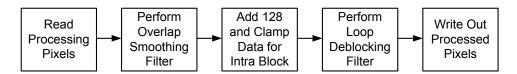

| Figure A.1: Encoding loop of VC-1 codec                                                                                                                                                                                                                                                                                                                                                               | 75       |

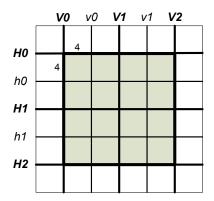

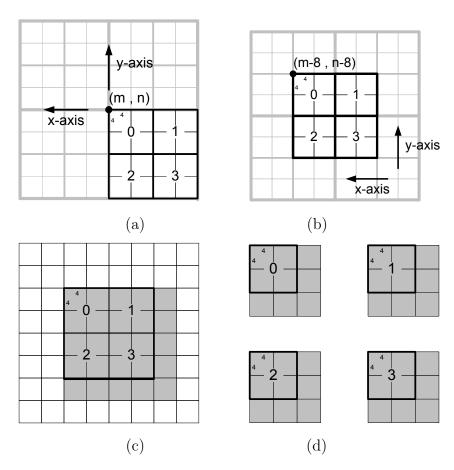

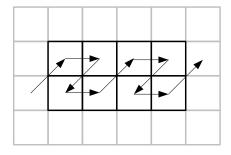

| Figure A.2: All filtered edges relative to the luma data of a macroblock Figure A.3: A 12×12 overlapped block. The bold square defines an 8×8                                                                                                                                                                                                                                                         | 78       |

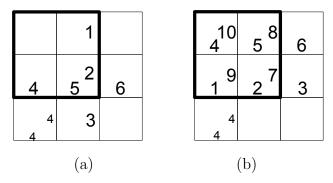

| block (luma or color-difference block) within a macroblock Figure A.4: Fundamental processing order. (a) Overlap smooth processing order applied to an overlapped block. (b) Deblocking filter                                                                                                                                                                                                        | 79       |

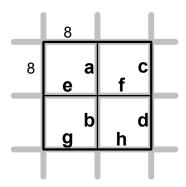

| processing order applied to an overlapped block Figure A.5: Simple processing flow of an overlapped block Figure A.6: 8×8 edges within a reconstructed macroblock. For overlap smoothing, edges a, b, c, and d should be filtered prior to edge                                                                                                                                                       | 80<br>80 |

| f. For in-loop filtering, edges e, f, g, and h should be filtered prior to edge b                                                                                                                                                                                                                                                                                                                     | 81       |

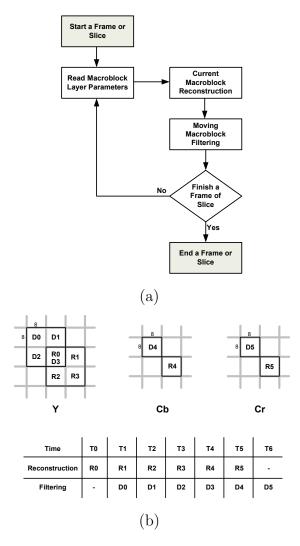

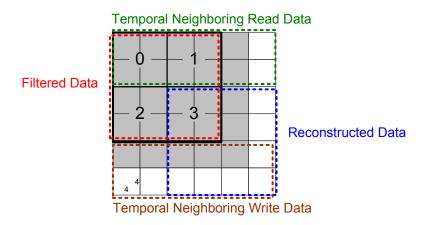

| overlapped blocks from the filtered macroblock Figure A.8: (a) Data processing flow of a frame or slice. (b) Pipeline time                                                                                                                                                                                                                                                                            | 82       |

| schedule of a reconstructed macroblock and a filtering macroblock.                                                                                                                                                                                                                                                                                                                                    | 84       |

| Figure A.9: (a) Single macroblock processing order. (b) Dual macroblock                                                                                                                                                                                                                                                                                                                               |          |

| processing order                                                                                                                                                                                                                                                                                                                                                                                      | 86       |

| Figure A.10: Data processing for a reconstructed macroblock and a filtered                                                                                                                                                                                                                                                                                                                            |          |

| macroblock                                                                                                                                                                                                                                                                                                                                                                                            | 86       |

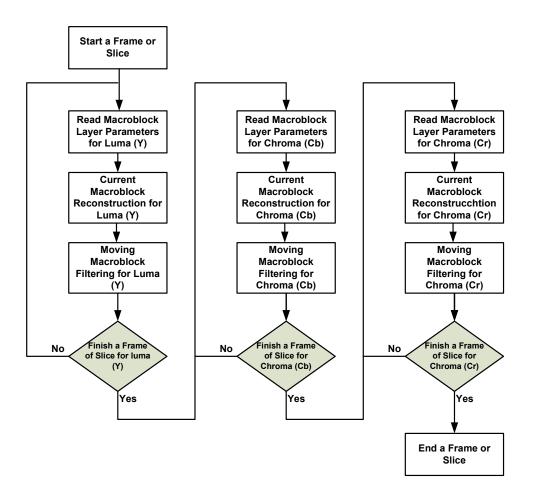

| Figure A.11: Separated data processing flow for a picture or slice                                                                                                                                                                                                                                                                                                                                    | 87       |

| Figure A.12: Y-analogous data procedure for chroma data                                                                                                                                                                                                                                                                                                                                               | 89       |

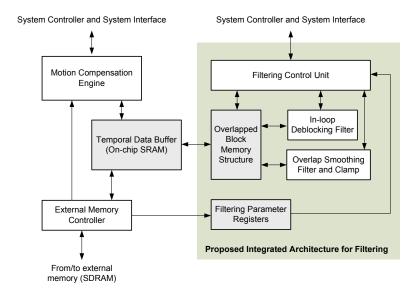

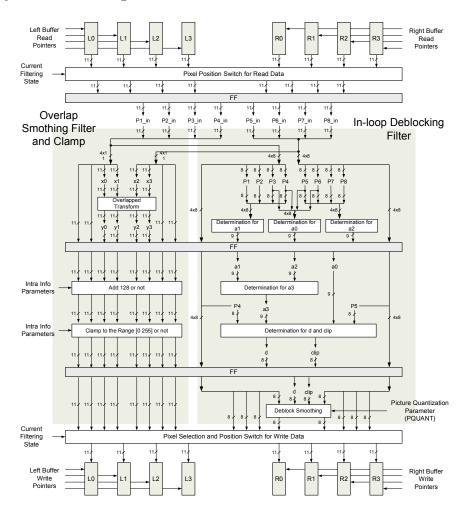

| Figure A.13: Block diagram of the proposed integrated architecture                                                                                                                                                                                                                                                                                                                                    | 90       |

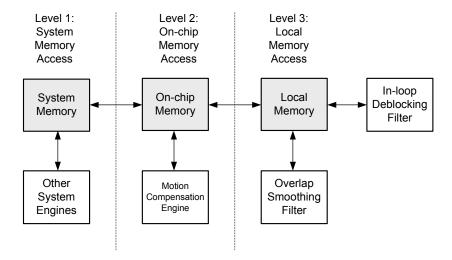

| Figure A.14: Three hierarchical levels of memory access                                                                                                                                                                                                                                                                                                                                               | 91       |

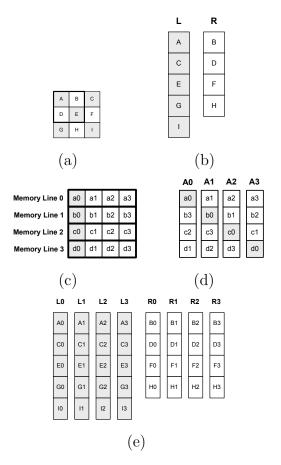

| Figure A.15: (a) Nine $4\times4$ blocks within an overlapped block. Every filtered |    |

|------------------------------------------------------------------------------------|----|

| edge is the boundary between a gray $4\times4$ block and a white                   |    |

| 4×4 block. (b) Two groups of memory structure. Filtering of                        |    |

| an edge must obtain 4-pixels or 2-pixels data from each group.                     |    |

| (c) Normal pixel mapping within a 4×4 block. (d) Rotated                           |    |

| pixel mapping within a $4\times4$ block. (e) Proposed memory struc-                |    |

| ture for an overlapped block including four $20 \times 11$ bits and four           |    |

| $16 \times 11$ bits memory structures                                              | )2 |

| Figure A.16: Data flow of the Proposed Integrated Filter                           | 3  |

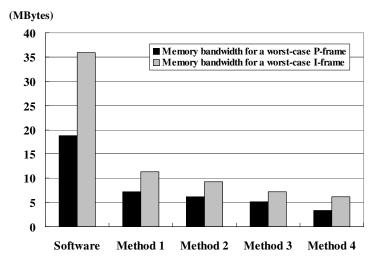

| Figure A.17: Comparison about the requirement of memory bandwidth to               |    |

| the external memory                                                                | 3( |

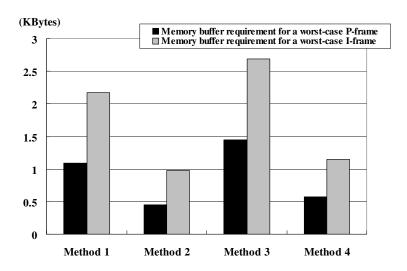

| Figure A.18: Comparison about the SRAM requirement (Temporal Data                  |    |

| Buffer)                                                                            | )Ĉ |

## LIST OF TABLES

| Table 5.1: | Front-end Hardware Cost of the Proposed True Motion Engine       |    |

|------------|------------------------------------------------------------------|----|

|            | with TSMC 90-nm Technology                                       | 38 |

| Table 5.2: | On-chip Memory Buffer Size of the Proposed Architecture for a    |    |

|            | 1080p video                                                      | 38 |

| Table 5.3: | Processing Time of the Proposed Architecture                     | 38 |

| Table 5.4: | External Memory Bandwidth Requirement for the Proposed Ar-       |    |

|            | chitecture                                                       | 39 |

| Table 5.5: | Performance Comparison - PSNR                                    | 39 |

| Table 5.6: | Results of the perceptual experiment                             | 45 |

| Table 6.1: | System Computation                                               | 50 |

| Table 6.2: | Search Strategy Comparison                                       | 51 |

| Table 6.3: | Module Performance Comparison                                    | 52 |

| Table A.1: | Front-end hardware cost of the proposed VC-1 filter architecture |    |

|            | with TSMC 90-nm multi-Vt technology                              | 94 |

|            | Processing time of the proposed VC-1 filter architecture         | 95 |

| Table A.3: | Comparison with Different H.264/AVC Deblocking Architectures     |    |

|            | (The gate count excludes the local memory.)                      | 96 |

| Table A.4: | Analysis of external memory bandwidth for a worst-case 1080p     |    |

|            | 4:2:0 P-frame (without Overlap Smoothing)                        | 97 |

| Table A.5: | Analysis of external memory bandwidth for a worst-case 1080p     |    |

|            | 4:2:0 I-frame (Overlap Smoothing and In-loop Filtering)          | 97 |

#### ACKNOWLEDGEMENTS

The pursuit of a PhD education has been my memorable and challenging stage in my life. Without so much help, advice, and support from many people, I can hardly complete my PhD degree. I would like to acknowledge these important persons in my life.

First and foremost, I offer my sincerest gratitude to my advisor, Prof. Truong Nguyen, for his carefully considered advice, patience and inspirational enthusiasm for this research. I consider myself very fortunate to have studied at the Video Processing Laboratory and work with many brilliant people. I have a great deal of thanks to Prof. Truong Nguyen and his continuing support and encouragement to help me get through my most difficult times in research.

I would also like to thank my committee members, Prof. William Hodgkiss, Prof. Yoav Freund, Prof. Nuno Vasconcelos, and Prof. Rajesh Gupta, for providing me with valuable advice and comments to accomplish this work.

I wish to extend my appreciation to my nice and helpful labmates at the University of California, San Diego, for their companionship during these days spent at the lab, and for contributing to a friendly and motivational working environment. I would like to especially thank Natan Jacobson, Meng-Ping Kao, Wei-Hsin Chang, Shay Har-noy, Dung Vo, Carson Pun, Ai-Mei Huang, Jack Tzeng, Stanely Chan, and Nickolaus Mueller.

I owe a great deal of thanks to my parents, Chien-Erh Lee and Yueh-Chao Lee Hsu, my sisters, Patty Li and Yihsuan Lee, and my brother, Yen-Chi Lee, for encouraging me to set higher career goals and for showing endless love and support. I would also like to take this opportunity to acknowledge all my friends who always give me enormous support and encouragement.

Portions of Chapter 2 appear in "Method and Architecture Design for Motion Compensated Frame Interpolation in High-Definition Video Processing," Yen-Lin Lee and Truong Nguyen, in Proceedings of the *IEEE International Symposium on Circuits and Systems (ISCAS)*, May 2009. The dissertation author was the primary author of these publications, and the listed co-author directed and supervised the research that forms the basis for this chapter.

Portions of Chapter 3 appear in "Method and Architecture Design for Motion Compensated Frame Interpolation in High-Definition Video Processing," Yen-Lin Lee and Truong Nguyen, in Proceedings of the *IEEE International Symposium on Circuits and Systems (ISCAS)*, May 2009; "Fast One-pass Motion Compensated Frame Interpolation in High-Definition Video Processing," Yen-Lin Lee and Truong Nguyen, in Proceedings of the *IEEE International Conference on Image Processing (ICIP)*, Nov. 2009. The dissertation author was the primary author of these publications, and the listed co-author directed and supervised the research that forms the basis for this chapter.

Portions of Chapter 3 appear in "Method and Architecture Design for Motion Compensated Frame Interpolation in High-Definition Video Processing," Yen-Lin Lee and Truong Nguyen, in Proceedings of the *IEEE International Symposium on Circuits and Systems (ISCAS)*, May 2009; "Fast One-pass Motion Compensated Frame Interpolation in High-Definition Video Processing," Yen-Lin Lee and Truong Nguyen, in Proceedings of the *IEEE International Conference on Image Processing (ICIP)*, Nov. 2009. The dissertation author was the primary author of these publications, and the listed co-author directed and supervised the research that forms the basis for this chapter.

Portions of Chapter 4 appear in "Method and Architecture Design for Motion Compensated Frame Interpolation in High-Definition Video Processing," Yen-Lin Lee and Truong Nguyen, in Proceedings of the *IEEE International Symposium on Circuits and Systems (ISCAS)*, May 2009; "Fast One-pass Motion Compensated Frame Interpolation in High-Definition Video Processing," Yen-Lin Lee and Truong Nguyen, in Proceedings of the *IEEE International Conference on Image Processing (ICIP)*, Nov. 2009. The dissertation author was the primary author of these publications, and the listed co-author directed and supervised the research that forms the basis for this chapter.

Portions of Chapter 5 appear in "Method and Architecture Design for Motion Compensated Frame Interpolation in High-Definition Video Processing," Yen-Lin Lee and Truong Nguyen, in Proceedings of the *IEEE International Symposium* on Circuits and Systems (ISCAS), May 2009; "Fast One-pass Motion Compensation"

sated Frame Interpolation in High-Definition Video Processing," Yen-Lin Lee and Truong Nguyen, in Proceedings of the *IEEE International Conference on Image Processing (ICIP)*, Nov. 2009; "Novel Method and Architecture Design for Motion Compensated Frame Interpolation in High-Definition Video Processing," Yen-Lin Lee and Truong Nguyen, revised to *IEEE Trans. on Circuits and Systems for Video Technology*, 2009. The dissertation author was the primary author of these publications, and the listed co-author directed and supervised the research that forms the basis for this chapter.

Portions of Chapter 6 appear in "Novel Method and Architecture Design for Motion Compensated Frame Interpolation in High-Definition Video Processing," Yen-Lin Lee and Truong Nguyen, revised to *IEEE Trans. on Circuits and Systems for Video Technology*, 2009. The dissertation author was the primary author of these publications, and the listed co-author directed and supervised the research that forms the basis for this chapter.

Portions of Chapter 7 appear in "High Frame Rate Motion Compensated Frame Interpolation in High-Definition Video Processing," Yen-Lin Lee and Truong Nguyen, submitted to *IEEE International Conference on Acoustics, Speech and Signal Processing (ICASSP)*, March 2010. The dissertation author was the primary author of these publications, and the listed co-author directed and supervised the research that forms the basis for this chapter.

#### VITA

| 1999 | B. S., Electrical and Control Engineering, National<br>Chiao Tung University, Hsinchu, Taiwan |

|------|-----------------------------------------------------------------------------------------------|

| 2001 | M. S., Electrical and Control Engineering, National Chiao Tung University, Hsinchu, Taiwan    |

| 2009 | Ph. D, Electrical and Computer Engineering, University of California, San Diego               |

#### **PUBLICATIONS**

Yen-Lin Lee and T. Nguyen, "High Frame Rate Motion Compensated Frame Interpolation in High-Definition Video Processing," submitted to *IEEE International Conference on Acoustics, Speech and Signal Processing (ICASSP)*, March 2010.

Yen-Lin Lee and T. Nguyen, "Fast One-pass Motion Compensated Frame Interpolation in High-Definition Video Processing," accepted in *IEEE International Conference on Image Processing (ICIP)*, Nov. 2009.

Yen-Lin Lee and T. Nguyen, "Method and Architecture Design for Motion Compensated Frame Interpolation in High-Definition Video Processing," *IEEE International Symposium on Circuits and Systems (ISCAS)*, pp. 1633-1636, May 2009.

Yen-Lin Lee and T. Nguyen, "Novel Method and Architecture Design for Motion Compensated Frame Interpolation in High-Definition Video Processing," revised to *IEEE Trans. on Circuits and Systems for Video Technology*.

Yen-Lin Lee and T. Nguyen, "Analysis and Efficient Architecture Design for VC-1 Overlap Smoothing and In-loop Deblocking Filter," *IEEE Trans. on Circuits and Systems for Video Technology*, Vol. 18, pp. 1786-1796, Dec. 2008.

Yen-Lin Lee and T. Nguyen, "Analysis and Integrated Architecture Design for Overlap Smooth and In-loop Deblocking Filter in VC-1," *IEEE International Conference on Image Processing (ICIP)*, pp. V161-V172, Sept. 2007.

#### ABSTRACT OF THE DISSERTATION

## Method and Architecture Design for Motion Compensated Frame Interpolation in High-Definition Video Processing

by

#### Yen-Lin Lee

Doctor of Philosophy in Electrical Engineering (Electronic Circuits and Systems)

University of California San Diego, 2009

Professor Truong Nguyen, Chair

Digital displays such as Liquid Crystal Display (LCD) and plasma display televisions have become prevalent in recent years. Sports broadcasting and movies are two prime factors responsible for this popularity. However, motion blur and judder appear as objects move rapidly or color dramatically changes on a wide range of LCD devices because of slow response time and sample-and-hold drive nature. Frame Rate Up Conversion (FRUC) is a well-studied method that is used to minimize these detrimental effects.

A novel, fast, and efficient method with a well-designed architecture is proposed for Motion Compensated Frame Interpolation (MCFI) or Frame Rate Up Conversion. Unlike previous works involving high complexity, time-consuming iterations, and higher complex architecture, the proposed method adopts a one-pass, low-complexity approach without any iteration and is capable of dealing with High Definition (HD) video processing. Rather than a conventional motion estimation in MCFI, our method employs a unique true motion engine that explores at most nine motion candidates with different motion directions and then determines one true motion by referring to neighboring spatial and temporal information.

For the purpose of motion estimation, the proposed method introduces an adaptive overlapped block matching algorithm known as the Multi-Directional Enlarged Matching Algorithm (MDEMA), and considers different overlapped types

based on the direction of the current motion vector in order to enhance searching accuracy and visual quality. For practical issues and real-time HD requirements, the proposed architecture employs a modified Multi-level Successive Eliminate Algorithm (MSEA), which is a Fast Full-Search Block Matching Algorithm (FFS-BMA) and has the ability to reduce the heavy computation of full search while maintaining similar quality. According to analyzed temporal information, our method explores true motion candidates and refines the accuracy of true motions for blocks or sub-blocks. Experimental results show that the proposed algorithm provides better video quality than conventional methods and demonstrates excellent performance for 30fps HD1080p video (1920×1080 resolution) at 180MHz or 30fps 720p video (1280×720) at 83MHz.

## 1 Introduction

Digital displays, such as LCD and plasma, have become widely prevalent in recent years. Sports and movies have been prime factors in the popularity of large screen displays. Unfortunately, artifacts such as motion blur and judder appear due to rapid object motion or dramatic change in color on a wide range of LCD devices. These issues result from slow response time and sample-and-hold drive nature. Frame Rate Up Conversion (FRUC) is a well-studied method that is used to eliminate or reduce a device's physical disadvantages by inserting interpolated frames between any two successive original frames. Another practical application of FRUC is to enhance the reconstructed quality of a low bit rate decoded video as channel bandwidth is limited. Some conventional FRUC methods with low complexity, such as frame repetition and linear frame interpolation [1], yield blurred objects because these methods do not take motion information into account.

Motion Compensated Frame Interpolation (MCFI) [2][3][4] has been widely studied to enhance the quality of reconstructed video. This method explores block motions of the interpolated frames by processing using motion re-estimation or the received motion vectors from an encoded bitstream. MCFI can effectively reduce motion blur and improve visual quality by increasing the frame rate when it acquires true motion information. However, MCFI which directly processes motion vectors from a video encoder may suffer from blocking and ghost artifacts. This is because the encoder seeks to minimize prediction error rather than determining true motion. For this reason, many researchers have started to work on methods to accurately estimate true motion by considering spatial and temporal correlation

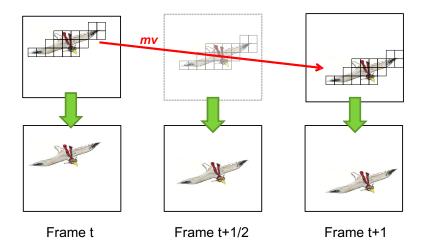

and searching with a Block Matching Algorithm (BMA) [5]. Fig. 1.1 shows an example for block-based MCFI.

Figure 1.1: Motion Compensated Frame Interpolation with block-based motion search.

In the past ten years, numerous methods have been proposed to determine true motion. However, these methods involve complex computation, complicated time-consuming iterations, and are difficult to implement for real-time High-Definition (HD) videos. Considering these drawbacks, the proposed method and architecture adopts a one-pass, low-complexity design without any repeated iteration and is developed with consideration for fast hardware implementation for HD video processing. In addition, the proposed approach has no restriction on video compression format due to a low complexity motion re-estimation. The proposed method is composed of bidirectional estimation, Multi-Directional Enlarge Matching Algorithm, one-pass motion vector selection with multi-grids classification, temporal/spatial object information and localized global motion vectors, Motion Compensated Frame Interpolation, and deblock filtering.

For practical issues and the real-time HD requirement, the proposed architecture is designed with a true motion engine that employs a modified Multi-level Successive Eliminate Algorithm (MSEA) [9], Probable Sum of Absolute Difference (PSAD), true motion selection, and a refinement of motion vector processing. MSEA is a Fast Full-Search Block Matching Algorithm (FFSBMA) [10] for mo-

tion estimation following a Successive Elimination Algorithm (SEA) [11], which has gained popularity for the ability to reduce the heavy computation of Full-Search Block Matching Algorithm (FSBMA) [12] while maintaining similar quality. Although MSEA has initially been developed for video compression, the proposed architecture introduces and modifies this technique to enhance the accuracy of true motion search and reach a balance between complexity and performance.

In order to have a better understanding of Motion Compensated Frame Interpolation and the platform it operates on, we start the dissertation with an introduction to MCFI in Chapter 2. MCFI is a popular approach to generate interpolated frames which considers motion information in an attempt to reduce motion judder and blur effects. Conventional MCFI methods are also discussed in this chapter with illustrations on the techniques that improve visual quality for Frame Rate Up Conversion.

In Chapter 3, a dedicated processing method is proposed, which adopts one-pass and low-complexity design without need for iteration. The proposed techniques are developed based on a motion re-estimation in order to obtain accurate true motion, which has no restriction on specific video compression format. The methods and techniques adopted in our proposed MCFI are presented in this chapter.

In order to reduce the computational complexity, the proposed architecture first introduces a fast full search method, Multi-level Successive Elimination Algorithm (MSEA) in Chapter 4. In this chapter, a practical architecture is proposed to implement all methods proposed in Chapter 3. The proposed architecture has the capability to deal with Frame Rate Up Conversion for a 1080p sequence up to 60fps.

In Chapter 5, the performance of our proposed method and architectural design are examined. To verify the accuracy and the efficiency for the proposed method and architecture, the architecture is designed in VHDL (VHSIC (Very High Speed Integrated Circuits) Hardware Description Language) and implemented with TSMC (Taiwan Semiconductor Manufacturing Company Limited) 90-nm technology. The implemented architecture operates with our VHDL and MATLAB im-

plementation, and the result has been verified with our prototype in MATLAB. In addition to architecture implementation, PSNR tests are used to compare the performance of different MCFI methods including the proposed methods and conventional methods. We test visual quality by conducting subjective tests with human observers. The results demonstrate that the proposed method has better visual quality than conventional methods.

In Chapter 6, each technique of the aforementioned methods will be separately discussed via system analysis and profiling. In this chapter, we will examine each component's contribution and process loading in the proposed MCFI design. Due to the widespread popularity of digital displays, more and more high quality LCD devices with high frame rate have emerged in the market. However, current video sources, media storage, and decoding power are limited to 30- or 60-fps and make it impossible to transmit a 120- or 240-fps High Definition (HD) compressed video bitstream. Hence, the method for high Frame Rate Conversion will be proposed in Chapter 7. Finally, the conclusions will be summarized in Chapter 8.

## 2 Motion Compensated Frame Interpolation

# 2.1 Introduction of Motion Compensated Frame Interpolation

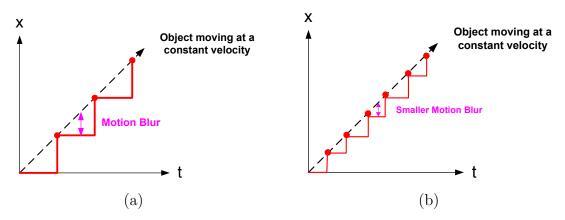

Motion blur occurs because of a disparity between Human eye tracking and the actual displayed data [13]. Fig. 2.1(a) depicts the case of an object moving in a horizontal direction at a constant velocity on an LCD with zero response time. Variable x denotes position and t shows frame time. Eye tracking causes Human observers to form a target trajectory for the object. However, due to the sample-and-hold characteristics of the LCD, the output at each pixel is held constant for the entire frame period. The difference between the eye tracking trajectory and the actual displayed data corresponds to the motion blur perceived by the human observer. Fig. 2.1(b) shows the case of reducing motion blur if data sample rate increases.

In contrast to conventional methods that linearly average [1] or temporally filter two or more successive frames, Motion Compensated Frame Interpolation (MCFI) is a popular approach to generate interpolated frames for a Frame Rate Up Conversion (FRUC) with higher quality and accuracy. MCFI considers motion information to reduce motion judder and blur effects. Although MCFI can enhance visual quality, it may still suffer from blockiness and ghost effects due to a failure of finding true motions. Contemporary proposals and methods in MCFI can be classified into two categories: motion re-estimation method and motion vector

Figure 2.1: The difference between the eye tracking trajectory and the actual displayed data with zero response time. (a) Original frame rate. (b) Twice the original frame rate.

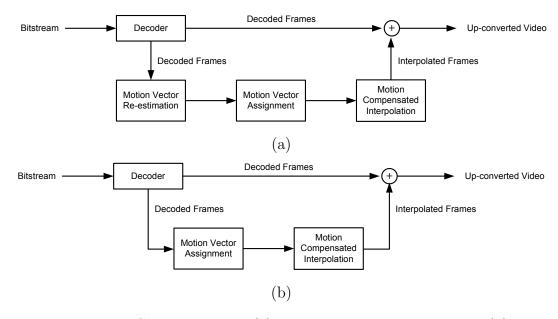

processing method. Fig. 2.2 shows block diagrams for these two approaches.

Figure 2.2: Two MCFI approaches. (a) Motion re-estimation method. (b) Motion vector processing method.

The motion re-estimation method in Fig. 2.2(a) is typically used for applications which demand high quality or multi-standard support. It is because it takes decoded frames from the decoder, and it is independent of the codec used. The disadvantage is the need to implement a motion estimator, which greatly increases computational complexity and memory bandwidth. In addition, lossy compressed

frames also increase the difficulty of true motion search. The concept of the motion vector processing method in Fig. 2.2(b) is to extract the motion vectors from the decoder and process this Motion Vector Field (MVF) so as to assign a true motion for each block. Although this method has lower complexity, the quality strongly depends on performance of an encoder's searching algorithm because block-based motion estimation at the encoder minimizes prediction errors rather than finding true motions. In other words, an unfavorable encoding may ruin the true motion vector field and create challenges in motion vector processing method. Here, we briefly review previous works.

In 1989, Sorvani et al. proposed an approach [6] to coding of moving sequences that combines image segmentation with adaptive thresholding based on a priori knowledge about the scene and motion-adaptive frame interpolation techniques. 3-D Recursive Search (3DRS) [5] enhances video information evaluates candidate vectors of enhancement algorithms utilizing an error function biased towards spatio-temporal consistency with a penalty function. Another temporal frame interpolation technique is presented in [7], based on an object-based algorithm for 3-D motion estimation. This algorithm uses a joint estimationsegmentation scheme to minimize the displaced frame difference between a frame and its motion compensated prediction from the previous frame. The main novelty of the proposed method in [8] is the motion compensation algorithm which has been designed with low computational complexity as an important criterion. In [14], Chen proposed an adaptive temporal interpolation method with both forward and backward estimation conducted with a correction constraint. In [15], the method based on a pyramid structure and the motion compensation process is performed independently at each resolution level. A technique similar to Control Grid Interpolation (CGI) is employed to process hole regions generated at the top level of the pyramid.

Subsequently, a novel method that adopts Overlapped Block-based Motion Estimation (OBME) was proposed by Ha et al. in [16] to obtain higher accuracy motion trajectory. From the approach in [17], the motion vector from Phase Plane Correlarion (PPC) method is used that assigns multiple motion vectors to a block

thus achieving the result of object based approaches with much fewer operation counts. A method that examines the motion vectors by bi-directional motion estimation was proposed in [18] to remove and correct unreliable motion vectors from the bitstream. Kuo et al. proposed two add-on schemes to enhance a Fast Blockbased Motion-Compensated Frame Interpolation (FMCI) [19] in their research. These are the Adaptive Frame Skip (AFS) scheme applied at the H.263 [20] encoder and the Hybrid Frame Interpolation (HFI) scheme which incorporates both frame repetition and FMCI at the decoder. Fujiwara et al. presented a technique [21] based on different block sizes in order to realize the clear interpolation of moving objects regardless of the object's size. Perspective transforms were introduced in [22] to reduce blocking artifacts in boundary blocks. A motion vector processing method was proposed by Dane et al. in [23] when an optimal temporal filter was obtained by minimizing the prediction error variance between original frame and interpolated frame. In [24], Choi et al. partitioned a frame into several object regions by clustering motion vectors and applied the Variable-Size Block Motion Compensation (VS-BMC) and Adaptive Overlapped Block Motion Compensation (AOBMC) to remove the limitations of conventional OBMC.

Yang et al. developed new criteria and coding scheme and adopted adaptive frame skip to guarantee the quality of interpolation [25]. A low complexity Motion Compensated Frame Interpolation method using compressed-domain information based on an H.264 decoder is presented in [26]. In this proposed method, the motion vectors are estimated using the constant acceleration motion model, and the interpolation algorithm is applied based on the macroblock coded types. Huang et al. proposed a motion vector processing algorithm that considers the reliability of motion vectors by analyzing the distribution of residual energies and merging blocks [27]. Yang et al. proposed to select the parameters and thresholds by analysing the statistical characterization of motion vectors and residual energy, thus thresholds can be changed adaptively during the decoding process [28]. The selected moving objects on each decoded frames, are meshed from quadrilateral blocks which are then deformed using specific warping functions in [29]. The meshed objects are reconstructed to the predicted nodes and integrated in

the H.264/AVC video coding standard. [31] addresses the problems of unreliable motion vectors that cause visual artifacts but cannot be detected by high residual energy or bidirectional prediction difference in motion-compensated frame interpolation. Song et al. use three frames to provide an algorithm in [30] to detect the occlusion area and differentiate the covering/uncovering area for Motion Compensated Frame Interpolation. This method aims at reducing artifact in occlusion areas. A correlation-based motion vector processing method is proposed in [31] to detect and correct those unreliable motion vectors by explicitly considering motion vector correlation in the motion vector reliability classification, motion vector correction, and frame interpolation stages.

Although there are many well-developed proposals on MCFI and FRUC, computational complexity is still a serious problem for a real-time processing to cope with the HD requirements due to multi-stage processing and complex searching procedures. Hence, we propose a novel, fast, and hardware-friendly method and its architecture design. The techniques of the proposed method will be discussed in the following chapters.

## 2.2 Acknowledgement

Portions of Chapter 2 appear in "Method and Architecture Design for Motion Compensated Frame Interpolation in High-Definition Video Processing," Yen-Lin Lee and Truong Nguyen, in Proceedings of the *IEEE International Symposium on Circuits and Systems (ISCAS)*, May 2009. The dissertation author was the primary author of these publications, and the listed co-author directed and supervised the research that forms the basis for this chapter.

## 3 The Proposed MCFI Method

As mentioned in Chapter 2, although many methods have been proposed to deal with the processing for temporal frame interpolation, they involve complex computation, time-consuming iterations, and are difficult to implement for real-time high definition systems. In this chapter, one dedicated processing method is proposed, which adopts one-pass and low-complexity design without repeated iteration. The proposed techniques are developed based on motion re-estimation in order to obtain accurate true motion with no restriction to specific video compression format.

## 3.1 Proposed Processing Flow

The proposed scheme adopts a motion-compensated approach to insert one or several interpolated frames between any two contiguous original frames. Accordingly, determining a true motion is the primary and most essential step to generate interpolated frames. Fig. 3.1 shows the entire processing flow of the proposed method including a true motion engine.

The entire processing procedure is composed of three major parts: a true motion engine, a block-based interpolator, and a deblocking filter. The true motion engine takes charge of motion estimation and true motion decision, and it also outputs true motion vectors to the block-based interpolator. The block-based interpolator obtains motion information and performs a motion compensated procedure with weighted values. At last, a deblocking filter smoothes the blocking artifacts where a neighboring or current interpolated block with a large Sum of

Figure 3.1: Processing flow of the proposed method.

Absolute Difference (SAD) shows up.

The purpose of the true motion engine is to assign a true motion vector for each individual block or sub-block, and this engine searches the motion with different processing steps. In our proposed method, a simple down-sampling procedure is performed to reduce computation when input images are of HD resolution, such as HD1080p or HD720p. If this down-sampling procedure is activated, a refinement is executed to increase accuracy for true motion vectors. Other functions include: bidirectional motion vector searching, multi-directional enlarged matching, border motion vector searching, and multi-grids motion vector classification. Most of these techniques refer to spatial and temporal information to acquire motion candidates for the purpose of true motion selection. The true motion selector chooses the best motion vector for compensation according to pre-defined conditions and neighboring and global motion information. After the true motion engine determines the true motions, a block-based interpolator generates each block image for an entire interpolated frame, and then a deblocking filter reduces blocking artifacts with a simple filtering operation before outputting the upconverted frames. Similar to the method in [25], the proposed method also introduces a skipping method to skip some difficult situations when the proposed method cannot generate good quality interpolated frames, especially for large moving motions, scene changes, and dramatic color changes.

## 3.2 Proposed True Motion Search

In this section, a dedicated true motion processing method is proposed, which adopts one-pass and low-complexity design without any repeated iteration. The proposed techniques are developed based on motion re-estimation in order to obtain accurate true motions, which has no restriction on specific video compression formats.

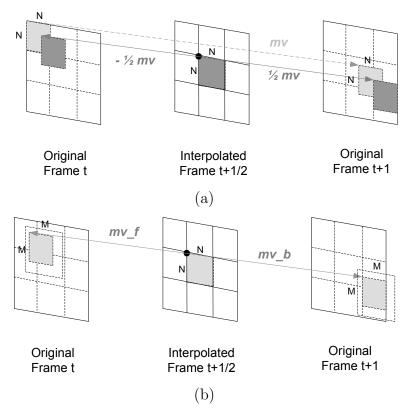

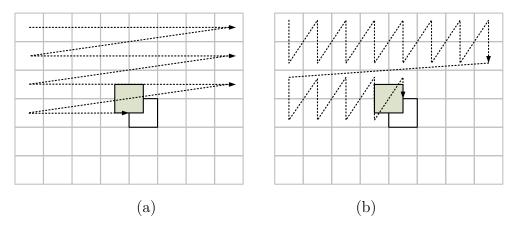

#### 3.2.1 Bidirectional Search

For acquiring an accurate true motion, we employ motion re-estimation with bidirectional search on reconstructed frames from a decoder rather than processing and correcting a motion vector field extracted from a compressed bitstream. Naturally, a method without motion re-estimation should have lower complexity, but it is difficult to find true motions when the motion vector field is inaccurate and irregular. Furthermore, repeated iterations increase computation on highdefinition video with high frame rate, such as 30fps or more. Fig. 3.2(a) shows a unidirectional searching method that is based on a block at the same location on the previous or subsequent frame and moves the motion vector along the trajectory. This is simple and compatible to any conventional encoder, but it might result in an inaccuracy as motions are inconsistent. Fig. 3.2(b) shows the proposed method using a bidirectional search. The proposed bi-directional search directly seeks two similar blocks from a zero distance of the interpolated block.  $mv_{-}f$  and mv\_b represent a forward motion and a backward motion respectively. For upconversion ratios other than 2,  $mv_{-}f$  and  $mv_{-}b$  can be different distances to allow for interpolation of an arbitrary frame rate.

Two adjacent frames are denoted by f(x,t) and f(x,t+1), where x and t are spatial and time domain indices. In the case that the up-conversion rate equals two, a motion vector,  $\overrightarrow{V}$ , of an N×N interpolated block is formulated by

$$\overrightarrow{V} = \arg\min_{\overrightarrow{v} \in S} \sum_{x \in B} |f(x - \overrightarrow{v}, t) - f(x + \overrightarrow{v}, t + 1)|$$

(3.1)

Figure 3.2: MCFI motion estimation method. (a) Unidirectional search. (b) Proposed bidirectional search.

where B denotes a matching M×M block of the current interpolated position; S is a set of motion vectors in our search range;  $\overrightarrow{v}$  is the motion vector examined for the best matching. The interpolated block size of N×N is different than the matching block size of M×M for searching more accurate true motion where M is equal or larger than N. The concept of the proposed method is based on searching for the minimum SAD value using a Block Matching Algorithm. The proposed architecture also applies in adaptive overlapped block motion estimation algorithm, Multi-Directional Enlarged Matching Algorithm (MDEMA), to enhance the accuracy of true motion search and lower the presence of visual blurred artifacts. From our experiments, the engine using bidirectional search achieves better performance and botains a more precise motion vector field than unidirectional search.

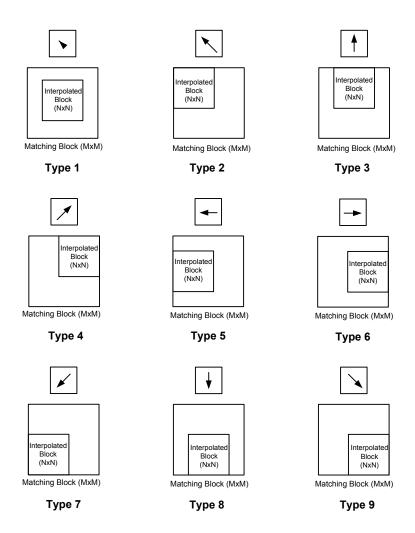

#### 3.2.2 Multi-Directional Enlarged Matching Algorithm

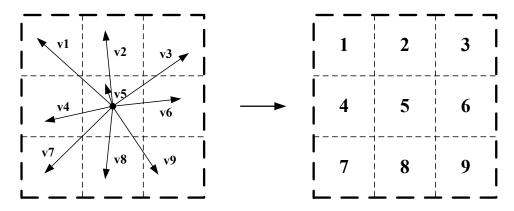

For searching motion candidates and true motion, the proposed method defines different block sizes for the interpolated block and the matching block. The current interpolated block size is defined by N×N pixels, and the matching block size is defined as M×M pixels. Compared to the conventional block matching method, larger matching block size improves the accuracy of true motion search because a larger part of a particular object is considered. However, it might lose some details surrounding the moving object. Based on our experiments, the results reveal that using smaller matching size is worse and often obtains the wrong motion with a smaller pixel difference instead of a true motion, especially for blocks with little texture. Therefore, how to take advantage of a larger block matching size to search a true motion for an interpolated block is a required topic. Although previous works employ an overlapped block searching method as well, the proposed method introduces a novel enlarged matching method, MDEMA. There are two searching modes for the MDEMA: (1) nine-directional enlarged matching and (2) direct multi-directional enlarged matching. The former is used with the MSEA engine to roughly search motion candidates. The MSEA is a fast full-search method, which will be further explained in the next chapter. The latter is used with the PSAD engine to exactly determine a motion vector for each divided search window from the proposed multi-grids classification, which defines nine different partitioned windows for motion candidates. The PSAD will also be explained in the next chapter. Here, we describe the operation of MDEMA.

In accordance with different motion directions, nine types of enlarged matching directions are defined and shown in Fig. 3.3. Small squares in the figure depict  $N \times N$  block size, and this area will be used for interpolation as we find the most suitable true motion vector by matching with a block size of  $M \times M$ . The proposed method determines the type by referring to the current motion vector and the distance from the position with zero motion. For example, consider the case with slow motion. When the current searching motion is small and near the zero motion, the approach chooses type 1 to enlarge the matching block. If the current searching motion goes to the top left side, the proposed approach chooses type

Figure 3.3: Nine-directional enlarged matching method.

2 to enlarge the matching block. If the current searching motion goes to upper side, the proposed approach chooses type 3 to enlarge the matching block, and so on. The reason for using different enlarged directions is to keep the completeness of the front edge of the moving object. From our observation, viewers are more sensitive to the artifacts and fractures of the moving object's front edge. Due to the visual quality, we aim to keep the front edge of the moving object intact by utilizing these enlarged matching types.

When generating and inserting a new frame between original frame t and t+1, the proposed method processes the frame in raster scan order based on an interpolated block size, N×N. For each N×N interpolated block, motion candidates

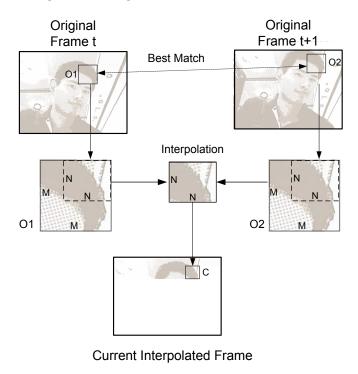

are found by using bidirectional search mentioned above. These motion candidates will be immediately examined with motion information of neighboring blocks without iterations, which is called one-pass processing in the proposed method. In most situations, we choose a motion vector with surrounding consistent motion as true motion rather than with the minimal MSEA or PSAD (these techniques will be discussed in a later chapter). Take type 4 for example, as shown in Fig. 3.4. When processing the N×N interpolated block C, the M×M matching block O1 of frame t and the M×M matching block O2 are our best matching pair. The interpolated block would be a weighted average of these two blocks.

Figure 3.4: Nine-directional enlarged matching method with type 4.

The other multi-directional mode is the direct multi-directional enlarged matching method. Nine-directional enlarged matching method is derived from direct multi-directional enlarged matching method for fast computation and implementation during processing. Direct multi-directional enlarged method, shown in Fig. 3.5, adopts a more precise enlarged range and considers exact direction and magnitude of motion candidates. Because the MSEA engine already performs

a full search and then obtains several motion candidates for the PSAD, direct enlarged matching method is not applied on every motion vector within the entire searching window. There are four motion candidates for each divided searching window and thirty-six motion candidates for an entire searching window in the proposed implementation.

Figure 3.5: Direct multi-directional enlarged matching method (a) Matching window and interpolated block in a previous frame t. (b) Matching window and interpolated block in a successive frame t+1.

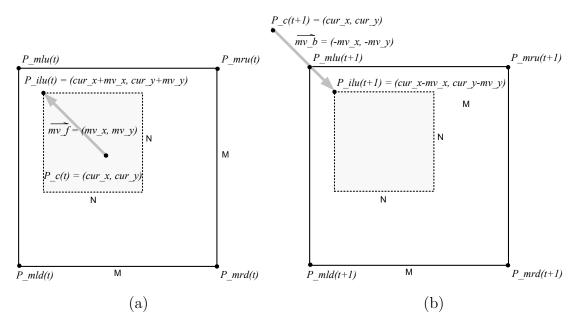

The proposed PSAD method with direct enlarged matching method defines  $M \times M$  matching blocks on previous frame t and successive frame t+1 when searching for a best matching pair. The PSAD is very similar to the SAD in that it finds the minimum sum of the pixel difference, but it only examines motion candidates from the MSEA. The corners of these two blocks in Fig. 3.5 are defined by

$$Corner\_positions(t) = \begin{cases} P\_mlu(t) = (mlu\_x(t), mlu\_y(t)) \\ P\_mru(t) = (mlu\_x(t) + M, mlu\_y(t)) \\ P\_mld(t) = (mlu\_x(t), mlu\_y(t) + M) \\ P\_mrd(t) = (mlu\_x(t) + M, mlu\_y(t) + M) \end{cases}$$

(3.2)

$$where \\ \begin{cases} mlu\_x(t) = cur\_x + mv\_x + \left(\frac{\max\_mv\_x - |mv\_x|}{\max\_mv\_x}\right) \times sign(mv\_x) \times \frac{M}{4} - \frac{M}{4} \\ mlu\_y(t) = cur\_y + mv\_y + \left(\frac{\max\_mv\_y - |mv\_y|}{\max\_mv\_y}\right) \times sign(mv\_y) \times \frac{M}{4} - \frac{M}{4} \end{cases}$$

$$Corner\_positions(t+1) = \begin{cases} P\_mlu(t+1) = (mlu\_x(t+1), mlu\_y(t+1)) \\ P\_mru(t+1) = (mlu\_x(t+1), mlu\_y(t+1) + M) \\ P\_mrd(t+1) = (mlu\_x(t+1), mlu\_y(t+1) + M) \end{cases}$$

$$where \\ \begin{cases} mlu\_x(t+1) = cur\_x - mv\_x + \left(\frac{\max\_mv\_x - |mv\_x|}{\max\_mv\_x}\right) \times sign(mv\_x) \times \frac{M}{4} - \frac{M}{4} \\ mlu\_y(t+1) = cur\_y - mv\_y + \left(\frac{\max\_mv\_x - |mv\_x|}{\max\_mv\_y}\right) \times sign(mv\_y) \times \frac{M}{4} - \frac{M}{4} \end{cases}$$

$$(3.3)$$

#### 3.2.3 One-pass Motion Selection with Multi-grids Classification

The proposed approach adopts a one-pass processing method, which means that no iteration is needed when determining a true motion vector field. This allows faster processing time and reduces memory requirements. From this viewpoint, it does not rely on information of blocks subsequent to the current interpolated block (except searching result for the next block). In other words, this method only counts on information of motion vectors from previous processed blocks, which is similar to advanced techniques in video compression standards, such as H.264 [32] and VC-1 [33].

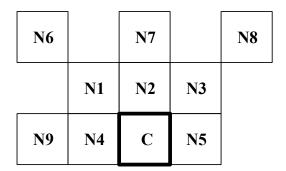

Effective neighboring blocks are shown in Fig. 3.6 and grouped under two levels: N1, N2, N3, N4 and N5 belong to the first level, and N6, N7, N8, and N9 belong to the second level. Blocks in the second level are used to determine how reliable block information is in the first level. C represents the current interpolated block and will be assigned a true motion after the process. The effect of the

neighboring blocks in the first level is more significant than those in the second level, and two levels are considered together: N1 and N6 are regarded as a group; N2 and N7 are regarded as a group; N3 and N8 are regarded as a group; N4 and N9 are regarded as a group. The information of these neighboring blocks or groups is used when determining a true motion.

Block N5 is processed in a unique way during this procedure. As mentioned above, the spatial information comes from the blocks processed prior to the current block. However, N5 does not belong to the processed blocks. According to the experiment, a decision considering motion from N5 greatly increases the correctness when choosing a true motion from nine motion candidates. Hence, the true motion selection for C should be done subsequent to motion search of N5. This searching procedure does not include the decision of the final true motion but obtain true motion candidates for reference. It is acceptable to search one more block in raster scan order because N5 is the subsequent block in this order. Necessary pixels are stored in local memory so as to process the true motion selection and interpolation. However, although the proposed method benefits from one-pass processing and less external memory access by ignoring information from following neighboring blocks, it also loses some advantage from missing information and cannot realize motions from the right or below. To compensate for this shortcoming, the proposed method utilizes temporal information, temporal object information and global motion vectors to enhance the search quality.

Figure 3.6: Effective neighboring blocks for spatial information.

After defining which neighboring block would influence the searching strat-

egy, the proposed method introduces a multi-grids classification to simplify processing and reduce the storage requirement for the motion vector field. It divides a search window into multiple areas shown in Fig. 3.7 (9 grids), and each area has one motion candidate after processing the MSEA and the PSAD. After a motion vector is determined with pre-defined conditions, this motion vector is refined and used for generating an interpolated block of the inserted frame. Then, the procedure will classify this true motion into one of these nine classes and record the classification instead of the motion vector value. This approach simplifies our processing procedure and also lowers memory access bandwidth.

Figure 3.7: Multi-grids Classification in a searching window.

#### 3.2.4 Temporal and Spatial Object Information

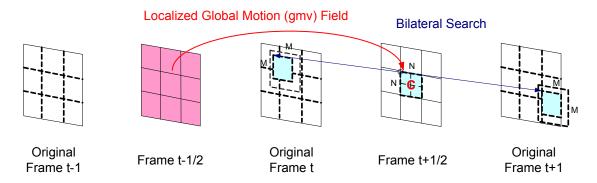

Although one-pass processing does not provide complete neighboring information, such as motion types from the right of or below neighboring blocks relative to the current interpolated frame, it can acquire temporal information from the previous processing result to realize object motion. Here, we assume that an object at a location in the previous frame has high probability of appearing near this location in most cases. Since all motion information is known for previous frames, true motion fields from previous results help us search for current true motion. Fig. 3.8 shows an example for multi-directional enlarged bidirectional search algorithm with temporal information.

Figure 3.8: Multi-directional enlarged bidirectional search algorithm with temporal information.

Temporal information is a method to get an object's motion which has a constant speed, especially for panning scenes. When the camera pans slowly across a scene, most interpolated blocks move consistently except foreground objects. However, not all information from previously interpolated blocks is considered for global motion in our proposed method. Only interpolated blocks with a large pixel variance are considered, which means that the large part of an object will be examined. This method removes inaccurate motion vectors from being taken into account. However, a simple and uniform pattern easily matches a similar block with a false true motion, such as the pattern on a white board, and will provide inaccurate, irregular, and unreliable motion information. These inaccurate motion vectors lower the accuracy of global motion, and therefore are not considered. The Sum of Absolute Variance (SAV), is formulated by

$$SAV(B) = \sum_{k=1}^{N-1} \sum_{l=1}^{N-1} (|p(k,l) - p(k,l+1)| + |p(k,l) - p(k+1,l)|)$$

(3.4)

where the block size of an interpolated block B is N×N. A pixel value within this interpolated block is denoted by p(x,y), where x and y are spatial indices relative to the pixel's position at the top-left corner of a block.

When the SAV of an interpolated block is larger than a threshold, the motion vector of this interpolated block is considered as a global motion vector for the next interpolated frame. In our approach, the global motion,  $\overrightarrow{mv_{global}}$  is processed and we also consider about the localized global motion vector,  $\overrightarrow{mv_{local}}$ ,

because every current interpolated block has its own localized global motion vector. These localized global motion vectors are useful for deciding which motion vectors are accurate, and are therefore considered with higher probability for true motion. Spatial information from the processed blocks is also considered when searching, and motion vectors from neighboring blocks have higher probability of being the true motion. The proposed method combined with the PSAD is formulated by

$$PSAD(\overrightarrow{v}) = \begin{cases} \sum_{x \in B} |f(x - \overrightarrow{v}, t) - f(x + \overrightarrow{v}, t + 1)| - T_{global} & when \overrightarrow{v} = \overrightarrow{mv_{global}} \\ \sum_{x \in B} |f(x - \overrightarrow{v}, t) - f(x + \overrightarrow{v}, t + 1)| - T_{local} & when \overrightarrow{v} = \overrightarrow{mv_{local}} \\ \sum_{x \in B} |f(x - \overrightarrow{v}, t) - f(x + \overrightarrow{v}, t + 1)| & otherwise \end{cases}$$

(3.5)

The proposed method adopts an SAD-like method, PSAD, to address the complexity issue. The PSAD of  $\overrightarrow{mv_{global}}$  or  $\overrightarrow{mv_{local}}$  is subtracted by the threshold value,  $T_{global}$  or  $T_{local}$ , and compared with the PSAD values of other motion vectors. The advantage of this proposed method is prevention of the bidirectional searching method from falling into a background trap. Background trap indicates a situation where an incorrect motion vector is determined from two very similar background blocks. Although unidirectional searching may also find an incorrect motion vector from two similar blocks, the problem in the bidirectional search is more serious. The proposed method introduces these two reference vectors,  $\overrightarrow{mv_{global}}$  and  $\overrightarrow{mv_{local}}$ , and two threshold values,  $T_{global}$  and  $T_{local}$ , to efficiently prevent this trap.

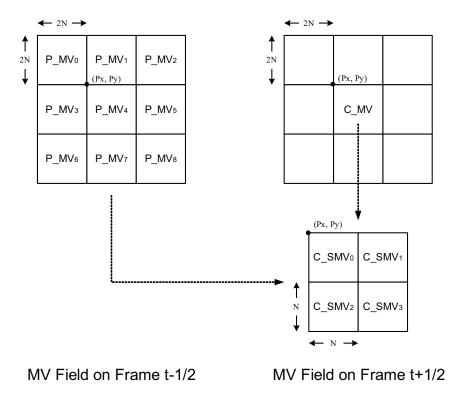

## 3.2.5 Sub-block Motion Assignment and Motion Refinement

According to analyzed temporal information, our method explores true motion candidates and then refines the accuracy of true motions for blocks or subblocks. Not only does this temporal information determine which motion candidate has higher probability, but it also provides criteria to assign true motion for subblocks in order to enhance visual quality and reduce occlusion problems and halo artifacts.

To reduce computation, our proposed method adopts block-based motion

assignment and HD downsampling. Block motion assignment will be used for a  $2N\times2N$  block (by default N=8) after upsampling recovery. However, when a moving objects is smaller than one block or an object boundary crosses a block, occlusion problems and halo artifacts obviously appear. To enhance motion precision and reduce computation, each block is assigned up to four different motions to deal with object boundary issues. Fig. 3.9 shows that the proposed sub-block assignment method examines motions from the surrounding motions of the previous interpolated frame. At first, all sub-block motions,  $\overrightarrow{C\_SMV_i}$  when i=0..3, are assigned the same motion as the original block motion,  $\overrightarrow{C\_MV}$ , for the default motions. These default motions,  $\overrightarrow{P\_MV_i}$  when i equals 0 to 8, are checked with the SAD function by N×N matching blocks. If the SAD of preceding motion is smaller than the SAD of the current assigned motion, a new motion will be assigned to this sub-block as the new true motion. The sub-block motion assignment method is formulated by

$$\overrightarrow{C_{-}SMV_i} = \arg\min_{\overrightarrow{v} \in S'} \sum_{x \in B} |f(x - \overrightarrow{v}, t) - f(x + \overrightarrow{v}, t + 1)|$$

(3.6)

where B denotes a matching N×N block of the current interpolated position; S' is a set of motion candidates, including  $\overrightarrow{C_-MV}$  and  $\overrightarrow{P_-MV_i}$  when i equals 0 to 8;  $\overrightarrow{C_-SMV_i}$  is the sub-block motion vector examined for the best matching. Two adjacent frames are denoted by f(x,t) and f(x,t+1), where x and t are spatial and time domain indices.

After determining the true motion, the proposed method performs the final refinement procedure. This procedure works on the original frames. The refining window is [-1, +1] shown in Fig. 3.10. After refining, this motion vector will be used for the interpolation.

Figure 3.9: Motions on the previous frame and the current block motion are employed on sub-block assignment.

#### 3.3 Frame Interpolation

#### 3.3.1 Frame Motion Skip

Motion Compensated Frame Interpolation is an efficient method to improve the visual quality of video by increasing the frame rate. However, the performance of true motion estimation varies with the image quality, the size of moving objects, and motion velocity. When the true motion engine cannot correctly find the true motion, irregular motions can cause blocking artifacts and provide incorrect spatial and temporal information for the following frame. If the frame interpolator generates an interpolated frame based on these incorrect motions, visual quality might be much worse than the case where MCFI is not applied.

Similar to [25], the proposed method employs an algorithm for the adaptive frame motion skipper. The proposed skipping method considers the level of block matching difference and motion consistency. The frame skip ratio (Skip\_Ratio) is

Figure 3.10: Motion vector refining window

formulated by

$$Skip\_Ratio(t) = \frac{\sum_{i=1}^{BH} \sum_{j=1}^{BW} Skip\_Factor(i, j)}{BH \times BW}$$

(3.7)

where the skip ratio of the current frame t is denoted by  $Skip\_Ratio(t)$ . BH and BW denote the total block number on the height and the width of the current frame t. If  $Skip\_Ratio(t)$  is larger than a threshold value,  $T_{skip}$ , all motion information will be discarded, and the interpolator will repeat the previous frame t or average frame t and frame t+1. The skip factor of each block ( $Skip\_Factor$ ) is formulated by

$$Skip\_Factor(i,j) = \begin{cases} 1 & if \quad SAD(i,j) < SAD_{skip} \\ 1 & if \quad \overrightarrow{MV_{i,j}} \neq any \quad \overrightarrow{MV_{neighboring}} \\ 0 & otherwise \end{cases}$$

(3.8)

#### 3.3.2 Interpolation