# UC Riverside UC Riverside Electronic Theses and Dissertations

#### Title

Accelerating I/O Processing in Server Architectures

### Permalink

https://escholarship.org/uc/item/4dk5k736

#### **Author** Liao, Guangdeng

# Publication Date 2011

Peer reviewed|Thesis/dissertation

#### UNIVERSITY OF CALIFORNIA RIVERSIDE

Accelerating I/O Processing in Server Architectures

A Dissertation submitted in partial satisfaction of the requirements for the degree of

Doctor of Philosophy

in

**Computer Science**

by

Guangdeng Liao

August 2011

Dissertation Committee: Dr. Laxmi N. Bhuyan, Chairperson Dr. Rajiv Gupta Dr. Najjar Walid

Copyright by Guangdeng Liao 2011 The Dissertation of Guangdeng Liao is approved:

Committee Chairperson

University of California, Riverside

#### Acknowledgements

Finishing this dissertation ends one major chapter of my life and triggers the beginning of another. As with any major step in life, I feel lucky and grateful for the endless support from many people. Without their support, I could not have reached this point.

First, I have to thank my advisor, Dr. Laxmi N. Bhuyan, for his guidance and continuous support over the past five years. He gave me the freedom to explore my ideas and was always willing to work through and discuss them with me. He taught me how to choose a research topic, do research and write a high-quality paper. He exemplifies a distinguished scholar, a motivating advisor and a true friend. I also want to thank Dr. Najjar Walid and Dr. Rajiv Gupta for serving on my dissertation committee. Their constructive suggestions helped improve the quality of this dissertation.

In addition to the support from academia, I also earned many helps from my intern mentors at Intel Labs: Steve King, Ram Huggahulli, Xia Zhu. They are patient and are willing to share what they know with me. My internships not only broadened my horizon, but also lay a good foundation for my career.

I would also like to thank former and current members of the architecture lab at UCR, Danhua Guo, Lan Gao, Jia Yu, Jingnan Yao, Satya Mohanty, Jilong Kuang, for their help during my stay at UCR and valuable discussions on my research.

Last but certainly not the least; I dedicate my accomplishment to my wife and parents. Without their endless love and support throughout my life, I will not be what I am today.

#### ABSTRACT OF THE DISSERTATION

Accelerating I/O Processing in Server Architectures

by

Guangdeng Liao

#### Doctor of Philosophy, Graduate Program in Computer Science University of California, Riverside, August 2011 Dr. Laxmi N. Bhuyan, Chairperson

Ethernet continues to be the most widely used network architecture today due to its low cost and backward compatibility with the existing Ethernet infrastructure. Driven by increasing networking demands of cloud workloads such as Internet search, web hosting etc, network speed rapidly migrates from 1Gbps to 10Gbps and beyond. High speed networks require general purpose servers to provide highly efficient network processing. However, traditional architectural designs have been focused on CPUs and often decoupled from I/O considerations, thus being inefficient for network processing.

In this study, we start with fine-grained driver and OS instrumentation to fully understand the network processing overhead over 10GbE on mainstream servers and make several new observations. Motivated by the studies, we propose a new server I/O architecture where DMA descriptor management is shifted from NICs to an on-chip network engine and descriptors are extended to address performance issues while processing packets. In addition, we also conduct extensive experiments on a real integrated NIC platform to understand the benefits of integrating NICs into CPU die. Our studies reveal that simple NIC integration gains little help. We therefore propose an enhanced integrated NIC (EINIC) to address the performance issues of high speed networks. We also find that TCP Control Block (TCB) can pose a challenge in web servers with a large volume of concurrent sessions. Therefore, we also analyze challenges from a large number of concurrent web sessions on managing per-session TCB and propose a new TCB cache architecture to manage TCB data for web servers.

As virtualization has gained resurgent interest and is becoming a key enabling technology in cloud infrastructures, understanding and improving virtualized network processing performance over high speed networks becomes critical. We conduct an experimental study of virtualized network performance on servers with 10GE networking to identify its performance bottlenecks. Then, we develop two VMM scheduler optimizations and design a simplified switch to reduce the network virtualization overhead. We also propose efficient architectural support by extending Direct Cache Access (DCA) to effectively avoid cache misses on packets in virtualized environment.

# Contents

| List of Tables                                                        | xii      |

|-----------------------------------------------------------------------|----------|

| List of Figures                                                       | xiii     |

| Chapter 1 Introduction                                                | 1        |

| 1.1 Challenges in TCP/IP Packet Processing                            | 3        |

| 1.2 Challenges in Network Interface Designs                           | 4        |

| 1.3 Challenges in Network I/O Virtualization                          | 5        |

| 1.4 Overview of the Research                                          | 6        |

| 1.5 Outline and Contributions                                         | 10       |

| Chapter 2 Background and Related Wrok                                 |          |

| 2.1 TCP/IP Packet Processing                                          | 12       |

| 2.2 Research in TCP/IP Packet Processing                              | 14       |

| 2.2.1 Hardware Optimizations                                          | 15       |

| 2.2.2 Software Optimizations                                          | 17       |

| 2.3 Network I/O Virtualization                                        |          |

| 2.4 Research in Network I/O Virtualization                            |          |

| Chapter 3 Understanding TCP/IP Packet Processing Performance Bottlene | eck over |

| 10GbE                                                                 |          |

| 3.1 Experimental Setup                                                |          |

| 3.2 Per-Packet Processing Overhead Breakdown                  |  |

|---------------------------------------------------------------|--|

| 3.3 Fine-Grained Instrumentation                              |  |

| 3.3.1. Driver                                                 |  |

| 3.3.2. Data Copy                                              |  |

| 3.3.3. Buffer Release                                         |  |

| 3.4 Summary                                                   |  |

| Chapter 4 Repartitioning CPU/NIC                              |  |

| 4.1 New Server I/O Architecture                               |  |

| 4.1.1 NEngine                                                 |  |

| 4.1.2 NIC                                                     |  |

| 4.1. 3. Software Support                                      |  |

| 4.2 Performance Evaluation                                    |  |

| 4.2.1 Network Performance                                     |  |

| 4.2.2 Web Server Performance                                  |  |

| 4.2.3 NIC Design Benefits                                     |  |

| 4.3 Summary                                                   |  |

| Chapter 5 Integrating NIC into CPU                            |  |

| 5.1 Performance Measurement of an Integrated NIC Architecture |  |

| 5.1.1 Sun Niagara 2                                           |  |

| 5.1.2 Experiment Methodology                                                                                                                                                                |            |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 5.1.3 Performance Evaluation                                                                                                                                                                | 51         |

| 5.1. 4 Detailed Performance Characterization                                                                                                                                                | 54         |

| 5.1. 5 Summary                                                                                                                                                                              | 62         |

| 5.2 Enhanced Integrated NIC                                                                                                                                                                 | 63         |

| 5.2.1 NIC                                                                                                                                                                                   | 64         |

| 5.2.2 Software LRO                                                                                                                                                                          | 67         |

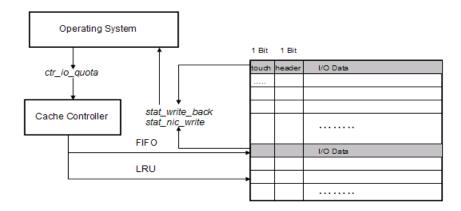

| 5.2.3 I/O-Aware LLC                                                                                                                                                                         | 68         |

| 5.2.4 Performance Evaluation                                                                                                                                                                | 72         |

| 5.2 Summer                                                                                                                                                                                  | 70         |

| 5.3 Summary                                                                                                                                                                                 |            |

| Chapter 6 A TCB Cache to Manage TCP Control Blocks                                                                                                                                          |            |

|                                                                                                                                                                                             | 80         |

| Chapter 6 A TCB Cache to Manage TCP Control Blocks                                                                                                                                          | <b> 80</b> |

| Chapter 6 A TCB Cache to Manage TCP Control Blocks                                                                                                                                          |            |

| Chapter 6 A TCB Cache to Manage TCP Control Blocks<br>6.1 TCB Challenges<br>6.1.1 Challenge in TOEs                                                                                         |            |

| <ul> <li>Chapter 6 A TCB Cache to Manage TCP Control Blocks</li> <li>6.1 TCB Challenges</li> <li>6.1.1 Challenge in TOEs</li> <li>6.1.2 Challenge in protocol processing on CPUs</li> </ul> |            |

| <ul> <li>Chapter 6 A TCB Cache to Manage TCP Control Blocks</li></ul>                                                                                                                       |            |

| <ul> <li>Chapter 6 A TCB Cache to Manage TCP Control Blocks</li></ul>                                                                                                                       |            |

| 6.3.4 Speculative Cache Replacement Policy                |     |

|-----------------------------------------------------------|-----|

| 6.4 Performance Evaluation                                |     |

| 6.4.1 Evaluation Methodology                              |     |

| 6.4.2 TCB Cache Performance                               |     |

| 6.4.3 Impact of Bit Selection                             |     |

| 6.4.4 Exploration of Cache Design Spaces                  |     |

| 6.4.5 Using our TCB cache                                 |     |

| 6.5 Summary                                               |     |

| Chapter 7 Optimizing Virtualized Network Processing       | 106 |

| 7.1 Understanding Virtualized Network Processing Overhead | 107 |

| 7.1.1 Per-packet processing overhead                      | 108 |

| 7.1.2 Architectural Analysis                              |     |

| 7.2 VMM Scheduler Optimizations                           |     |

| 7.2.1 Credit Scheduler in VMM                             |     |

| 7.2.2 Cache-aware Scheduler                               | 117 |

| 7.2.3 Credit-Stealing for I/O VCPU in Dom0                | 119 |

| 7.3 Virtualization-aware DCA                              |     |

| 7.4 Simplified Bridge                                     |     |

| 7.5 Performance Evaluation                                | 123 |

| 7.5.2 Architectural Optimizations through Simulation | 126 |

|------------------------------------------------------|-----|

| 7.6 Summary                                          | 128 |

| Chapter 8 Conclusion and Future Work                 | 130 |

| 8.1 Conclusion                                       | 130 |

|                                                      |     |

| 8.2 Future Work                                      |     |

# List of Tables

| Table 3.1: Instrumentation example   2              | 25 |

|-----------------------------------------------------|----|

| Fable 4.1 System configurations                     | 40 |

| Fable 5.1 INIC vs DNIC   4                          | 49 |

| Table 5.2 Cache read policy                         | 71 |

| Table 5.3. Cache write policy   7                   | 71 |

| Table 5.4 Simulated system parameters               | 73 |

| Fable 6.1 System parameters   9                     | 98 |

| Table 7.1 Component description    10               | 08 |

| Table 7.2 Performance counter example    11         | 11 |

| Table 7.3 Functional overhead in Linux Bridge    11 | 12 |

| Table 7.4 System configurations                     | 24 |

# **List of Figures**

| Figure 1.1: Network speed rates versus Moore's Law  |    |

|-----------------------------------------------------|----|

| Figure 1.2: TCP/IP packet processing performance    |    |

| Figure 2.1 Driver/NIC Interaction                   |    |

| Figure 2.2: Network I/O Virtualization in Xen       | 19 |

| Figure 3.1 Intel Xeon servers                       |    |

| Figure 3.2 Per-packet processing overhead breakdown |    |

| Figure 3.3 Architectural breakdown                  |    |

| Figure 3.4 L2 miss sources in step7                 |    |

| Figure 3.5 Data copy breakdown                      |    |

| Figure 3.6 Buffer release breakdown                 |    |

| Figure 3.7 L2 miss sources.                         |    |

| Figure 4.1 New I/O architecture overview            |    |

| Figure 4.2 Extended DMA descriptors                 |    |

| Figure 4.3 Basic block of NEngine                   |    |

| Figure 4.4 Simplified NIC in the new architecture   |    |

| Figure 4.5 Network throughput                       | 41 |

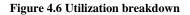

| Figure 4.6 Utilization breakdown                    | 41 |

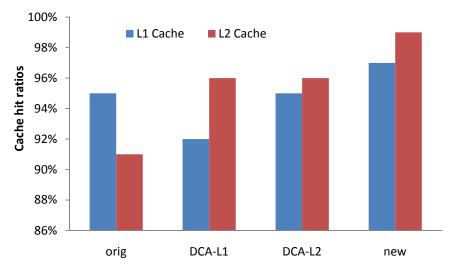

| Figure 4.7 Cache hit ratios                         |    |

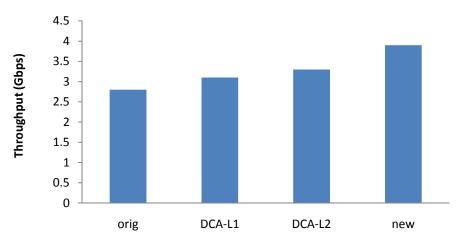

| Figure 4.8 Web server throughput                      | . 44 |

|-------------------------------------------------------|------|

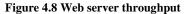

| Figure 4.9 Utilization breakdown                      | . 44 |

| Figure 4.10 Per packet time on DMA Engine             | . 46 |

| Figure 5.1 Niagara 2 Architecture                     | 48   |

| Figure 5.2 Bandwidth & CPU Utilization (RX)           | . 51 |

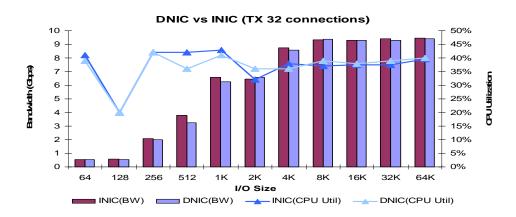

| Figure 5.3 Bandwidth & CPU Utilization (TX)           | . 52 |

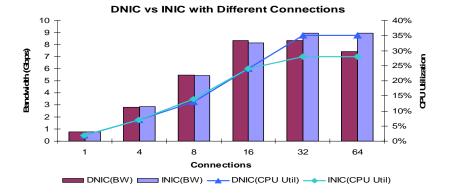

| Figure 5.4 Performance with Various Connections       | . 52 |

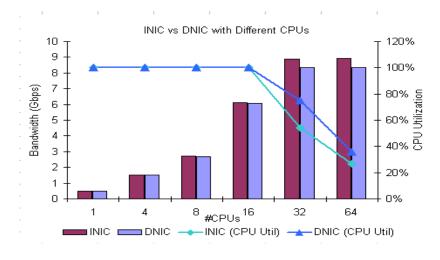

| Figure 5.5 Performance with Various CPUs              | . 53 |

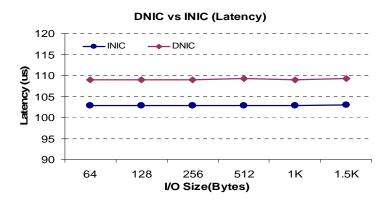

| Figure 5.6 Ping-Pong Latency                          | . 54 |

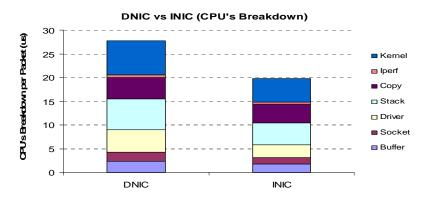

| Figure 5.7 CPU Overhead Breakdown                     | . 55 |

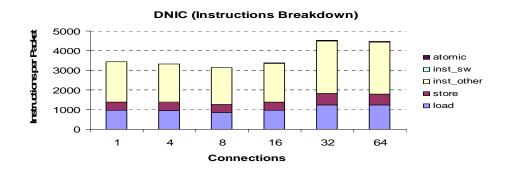

| Figure 5.8 Instruction Breakdown (DNIC)               | . 56 |

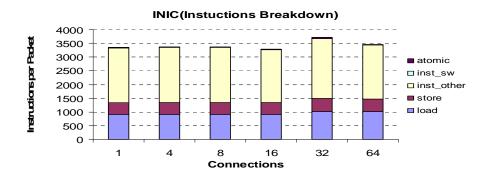

| Figure 5.9 Instruction Breakdown (INIC)               | . 57 |

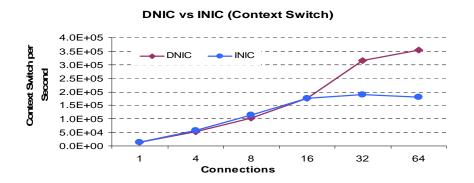

| Figure 5.10 Context Switches with Various Connections | . 57 |

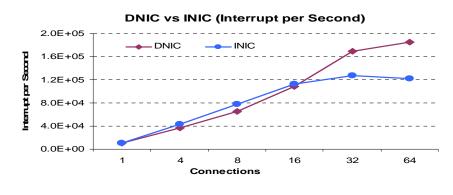

| Figure 5.11 Interrupts per Second                     | . 58 |

| Figure 5.12 System Interrupts Breakdown               | . 58 |

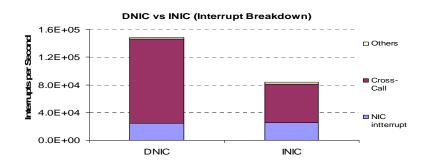

| Figure 5.13 Icache Misses per Packet                  | . 59 |

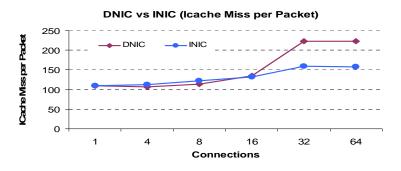

| Figure 5.14 Instruction Misses per Packet in L2       | . 60 |

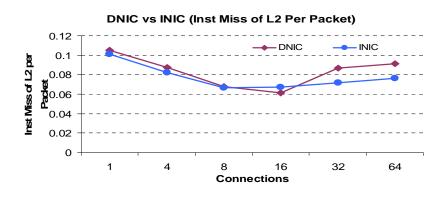

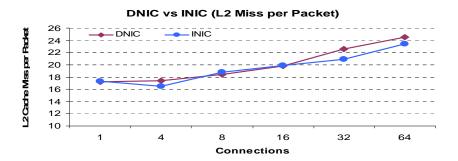

| Figure 5.15 Data Misses per Packet in L2              | . 61 |

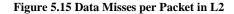

| Figure 5.16 Data Cache Misses per Packet              | . 61 |

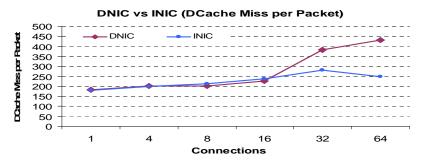

| Figure 5.17 Memory Traffic per Packet                 | 62   |

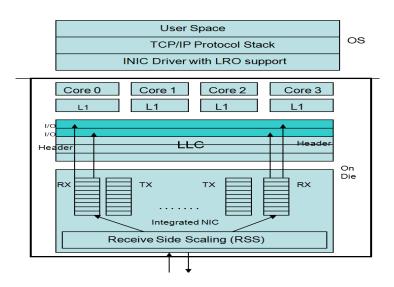

| Figure 5.18 New Architecture Overview                 | . 63 |

| Figure 5.19 Design of the INIC                        | 65   |

| Figure 5.20 I/O-Aware LLC                                      | . 68 |

|----------------------------------------------------------------|------|

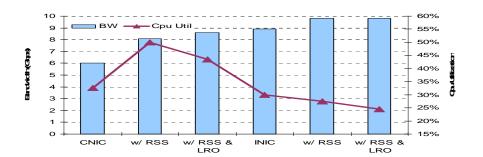

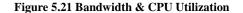

| Figure 5.21 Bandwidth & CPU Utilization                        | . 74 |

| Figure 5.22 Breakdown of CPU Utilization                       | . 74 |

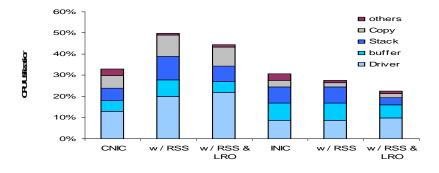

| Figure 5.23 Bandwidth with Memory Intensive Apps               | . 76 |

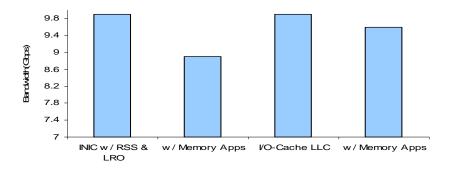

| Figure 5.24 I/O Cache's Way across Timeline                    | . 78 |

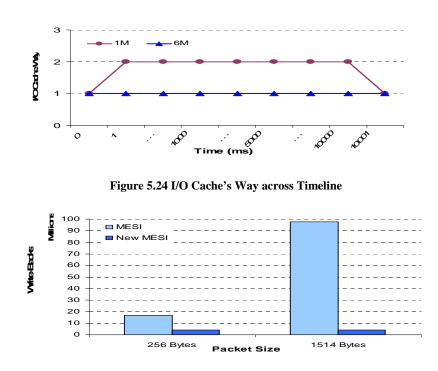

| Figure 5.25 The Number of Write Backs of Network Data          | . 78 |

| Figure 6.1 Function units in TOEs                              | . 82 |

| Figure 6.2 Processing time with a TCB miss                     | . 82 |

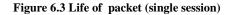

| Figure 6.3 Life of packet (single session)                     | . 84 |

| Figure 6.4 Life of packet (4K sessions)                        | . 84 |

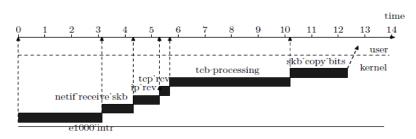

| Figure 6.5 Inter-request time frequency in ON                  | . 86 |

| Figure 6.6 <i>OFF</i> time frequency ( <i>OFF</i> )            | . 86 |

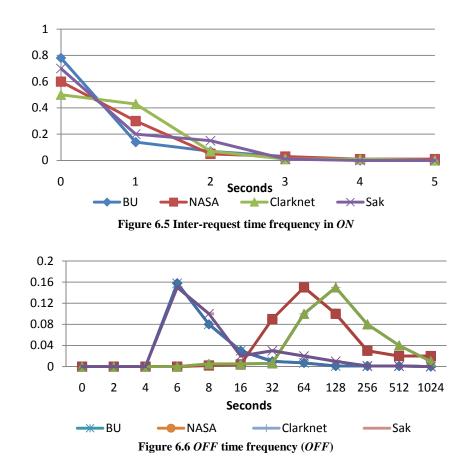

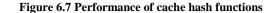

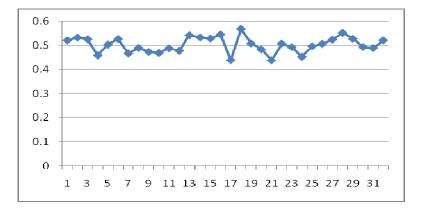

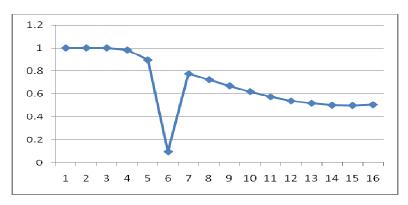

| Figure 6.7 Performance of cache hash functions                 | . 88 |

| Figure 6.8 PDF of absolute deviation of #sessions in cache set | . 88 |

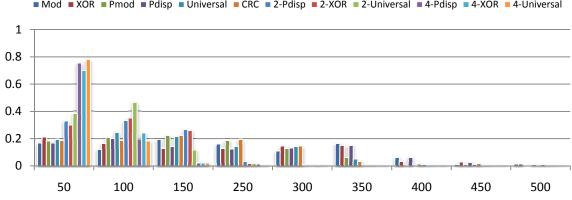

| Figure 6.9 TCB Cache Architecture                              | . 90 |

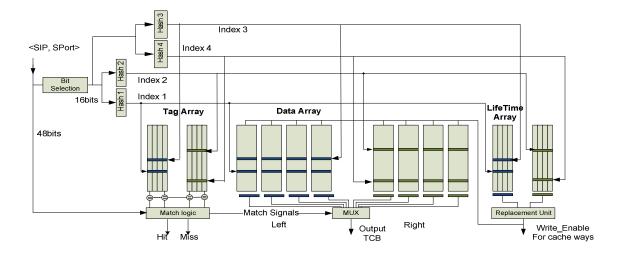

| Figure 6.10 Average bit value of IP address                    | . 91 |

| Figure 6.11 Average bit value of port                          | . 91 |

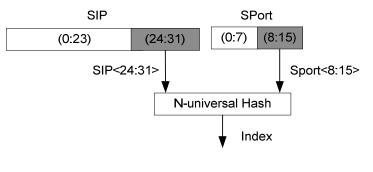

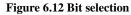

| Figure 6.12 Bit selection                                      | . 92 |

| Figure 6.13 Circuit implementation                             | . 92 |

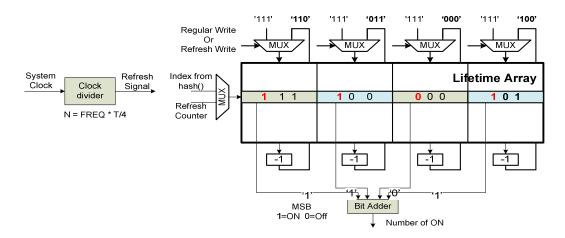

| Figure 6.14 Lifetime array                                     | . 94 |

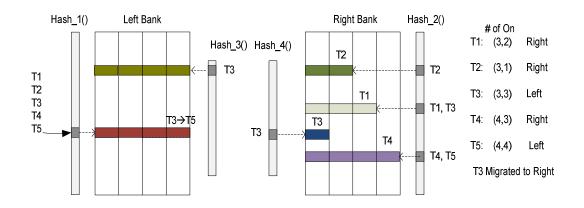

| Figure 6.15 Speculative cache replacement policy               | . 96 |

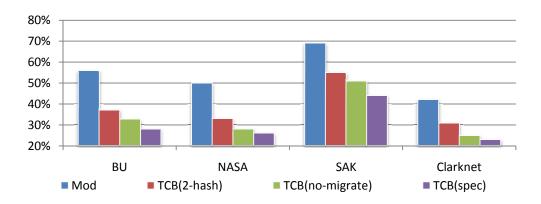

| Figure 6.16 Per packet miss ratio                              | 100  |

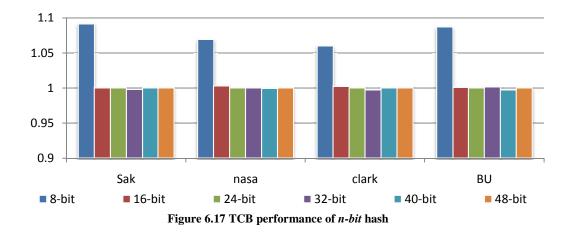

| Figure 6.17 TCB performance of <i>n-bit</i> hash10                   | )0 |

|----------------------------------------------------------------------|----|

| Figure 6.18 Cache replacement policies 10                            | )1 |

| Figure 6.19 Performance impact of cache sizes 10                     | )2 |

| Figure 6.20 Performance impact of set-associativity10                | )2 |

| Figure 6.21 TCP/IP receiving time in TOEs10                          | )3 |

| Figure 6.22 TCP/IP receiving time                                    | )4 |

| Figure 6.23 Web server response time 10                              | )5 |

| Figure 7.1 Intel Xeon Clovertown Machine 10                          | )7 |

| Figure 7.2 Per-packet processing overhead in virtualized environment | )9 |

| Figure 7.3 Linux Bridge overhead breakdown 11                        | 2  |

| Figure 7.4 Domain-copy overhead breakdown11                          | 3  |

| Figure 7.5 Kernel-to-user data copy overhead breakdown               | 4  |

| Figure 7.6 An example of Cache-Aware scheduler 11                    | 8  |

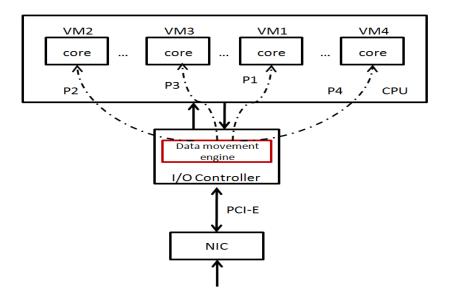

| Figure 7.7 New architecture overview                                 | 20 |

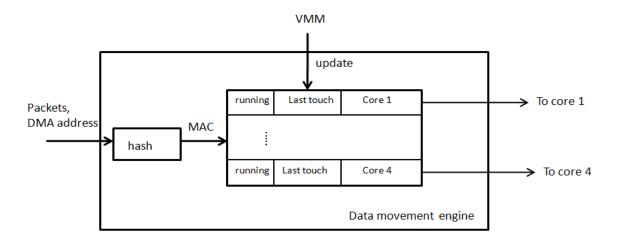

| Figure 7.8 Date movement engine 12                                   | 21 |

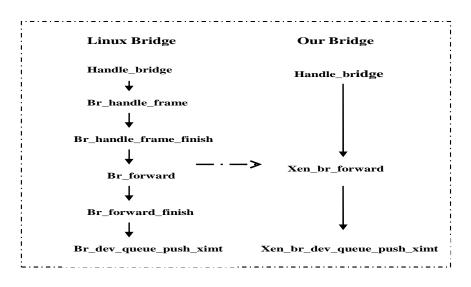

| Figure 7.9 Linux Bridge vs. our bridge 12                            | 23 |

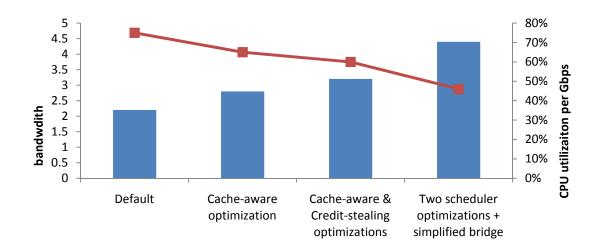

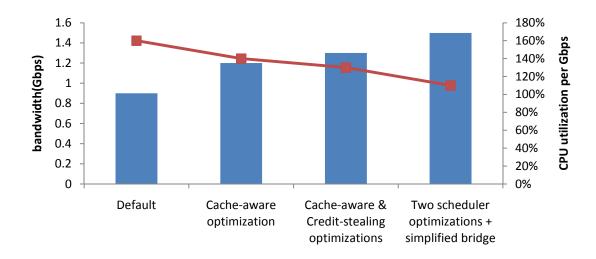

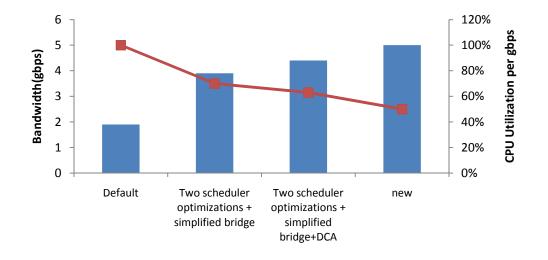

| Figure 7.10 Network performance with system optimizations            | 25 |

| Figure 7.11 Web server performance with system optimizations         | 26 |

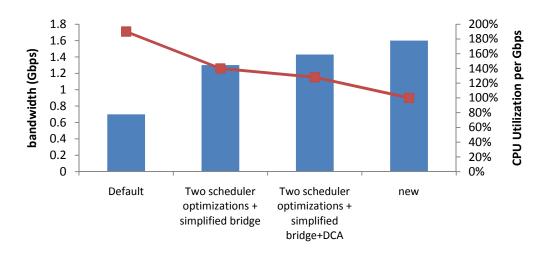

| Figure 7.12 Network performance with architectural optimizations     | 27 |

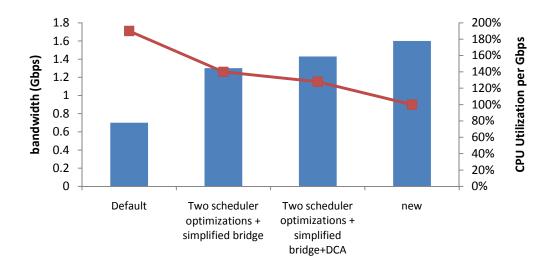

| Figure 7.13 Web server performance with architectural optimizations  | 27 |

| Figure 7.13 Web server performance with architectural optimizations  | 28 |

### Chapter 1

### Introduction

Ethernet continues to be the most widely used network architecture today due to its low cost and backward compatibility with the existing Ethernet infrastructure. It dominates in data centers and is replacing specialized fabrics such as InfiniBand [35], Quadrics [71], Myrinet [9] and Fiber Channel [14] in high performance computers. As of 2011, Gigabit Ethernet-based clusters make up 44.2% of the top-500 supercomputers [87].

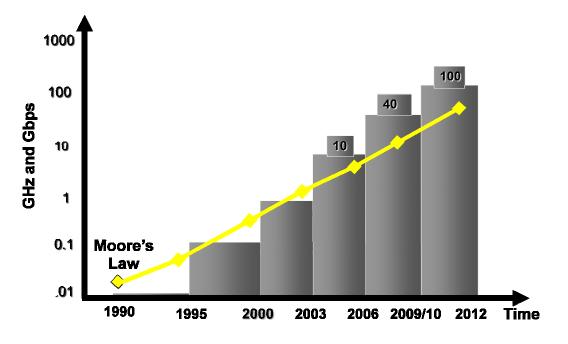

Driven by increasing networking demands of workloads such as Internet search, virtual private network, video servers and web hosting etc, network bandwidth becomes a technology that has outstripped Moore's Law in the past decades. Between 1995 and 2002, the IEEE Ethernet standard quickly migrated from a top speed of 100 Mbps to 10 Gbps, at a hundred-fold rate, while in the same period the 18-month doubling rate of Moore's Law indicates a mere 25x increase in transistor density (Moore's Law). It was reported that IEEE Ethernet standard group has released 40Gbps and 100Gbps specifications and corresponding products will be arriving in the near future [21]. Figure 1 depicts the relative increases of transistor density and network bandwidth. This graph shows that the rate of increase in network bandwidth is much higher than the rate of increase in transistor density.

Figure 1.1: Network speed rates versus Moore's Law

Unfortunately, even as nearly all server platforms completed the transition to 1 Gigabit Ethernet (1GbE), the adoption of 10 Gigabit Ethernet (10GbE) has been limited to a few niche applications [26, 91], not to mention the upcoming higher speed networks like 40GbE and 100GbE. For instance, as of 2011, only 1.2% of the top 500 supercomputers adopt 10GbE as their interconnect, but 44.2% are interconnected with 1GbE networks [87]. Historically, the propagation of 10GbE has been constrained by the cost of network interfaces and processing capability of general purpose platforms. As hardware develops as fast as Moore's Law, the cost of 10GbE connectivity will be reduced to an affordable level for network development in the near future [91]. Therefore the mismatch of host processing capacity with the network bandwidth becomes the biggest challenge. In the following subsections, we will discuss major challenges faced by the deployment of high speed networks on servers.

#### 1.1 Challenges in TCP/IP Packet Processing

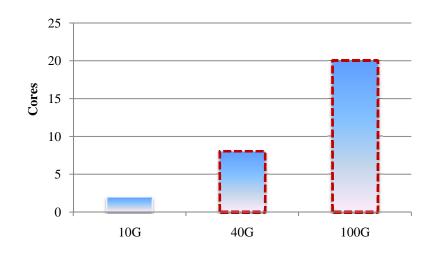

As network speed increases at a very fast rate, the host computer systems at the endpoints of these high-speed Ethernet connections should be designed to efficiently process the packets. The packet processing is accomplished through the TCP/IP protocol stack of the operating system (OS) and NIC device driver, etc that introduce large overheads while receiving the packets from Ethernet network. Unfortunately, traditional architectural designs of processors, cache hierarchies and system interconnects are focused on CPU/memory-intensive applications, and have often been decoupled from I/O considerations being inefficient for TCP/IP packet processing (a.k.a network processing in this study). It was reported that TCP/IP packet processing in the receive side over 10GbE easily saturates two cores of an Intel Xeon Quad-Core processor [46, 49]. Assuming ideal scalability over multiple cores in conventional servers, TCP/IP packet processing over upcoming 40GbE and 100GbE will saturate 8 and 20 cores, respectively (Fig. 1.2).

Figure 1.2: TCP/IP packet processing performance

Although a wide spectrum of research has been trying to improve the efficiency of TCP/IP packet processing on the network server [1, 6, 31, 63, 77, 92, 93, 94, 95], most of them focused on the data copy overhead and did not introduce a comprehensive solution for the problem. Based on extensive experiments and studies in these years, the community gradually realizes that the interactions among platform-wide hardware components, hardware-software interfaces and inter-software interfaces such as those between device drivers, the operating system and applications, render sophisticated multi-dimensional problems that cannot be easily addressed [6, 7, 53]. A comprehensive solution across the hardware platform and software stack rather than exclusive efforts from either side is necessary to satisfy the processing requirement introduced by the 10X or more increase in the upcoming 40Gbps/100Gbps networks.

#### **1.2 Challenges in Network Interface Designs**

Despite the rapid increase in available network bandwidth, NICs in servers are still considered as peripheral devices connected through standard PCI Express (PCI-E) bus [69]. By using DMA engine, NICs read/write network packets from/to main memory over long latency PCI-E interconnect bus.

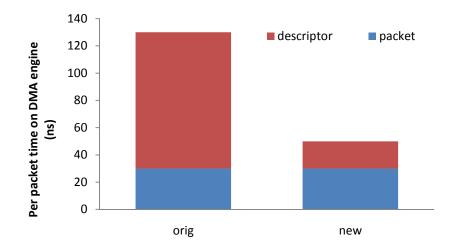

Although PCI-E bus bandwidth continued to improve in the past few years, its latency is degraded by up to 25X over earlier PCI-X incarnations mostly due to complex PCI-E transaction layer protocol implementation [62]. It was reported that up to ~2200 *ns* is needed for a round-trip traversal over PCI-E bus [62]. The long latency traversal substantially increases the processing overhead of DMA engine (although PCI-E pipelined transfers help payload, they do not work for descriptors). As network traffic

becomes intensive, DMA engine is heavily stressed [90]. Long latency descriptor fetches also make the need for large NIC hardware buffers or queues to temporarily keep packets. Moreover, in order to leverage conventional CMPs for packet processing, high speed NICs typically introduce a large number of receive/transmit (RX/TX) queues and allow each core to have a dedicated RX/TX queue. For instance, an Intel 82599 10GbE NIC has 128 RX/TX queues for each port for CMPs, corresponding to 512KB and 160KB buffers [36]. All of these complicate NIC designs and pose a big challenge. Therefore, a new server I/O architecture is required for high speed networks to tackle the TCP/IP packet processing challenge while simplifying NIC hardware designs.

#### **1.3 Challenges in Network I/O Virtualization**

Virtualization has become an integral component of the modern data centers. By introducing hypervisor or virtual machine monitor (VMM), a new thin layer between operating system (OS) and hardware platforms, it provides numerous virtual machine (VM) transparent services [5, 16, 24, 74], such as VM replication, rapid checkpoint, live migration and quality of service to guarantee service level agreement. Although the emergence of virtualization has been a promising solution towards sever consolidation and cloud computing, the virtualized network performance lags significantly behind the performance in native systems operating directly on physical devices. It was reported that virtualized TCP/IP packet processing over 1GbE network consumes up to 4.0x CPU cycles than TCP/IP packet processing on native environment [59, 60, 61]. That is because of high cost of virtualizing network I/O devices in software to allow multiple

guest VMs to share a single NIC device in a secure manner. Thus, more efficient network I/O virtualization is required for high speed networks.

#### **1.4 Overview of the Research**

The goal of this study is to accelerate network processing (or TCP/IP packet processing) in server architectures without introducing high hardware complexity. To achieve this goal, we propose several new I/O solutions to tackle all of the challenges mentioned above.

In the first part of this study, we performed per-packet processing overhead breakdown by running a network benchmark over 10GbE on Intel Xeon Quad-Core processor based servers. We find that besides data copy, the driver and buffer release, unexpectedly take 46% of processing time for large I/O sizes and even 54% for small I/O sizes. To understand the overheads, we manually instrumented the driver and OS kernel using hardware performance counters [34, 38]. Unlike existing profiling tools attributing CPU cost such as retired cycles or cache misses to functions [60, 68], our instrumentation is implemented at the fine-grained level and can pinpoint data incurring the cost. Through the above studies, we obtain several new findings: 1) the major network processing bottlenecks lie in the device driver (>26%), data copy (up to 34% depending on I/O sizes) and buffer release (>20%), rather than the TCP/IP protocol itself; 2) in contrast to the generally accepted notion that long latency NIC register access results in the driver overhead [6, 7], our results show that the overhead comes from memory stalls to network buffer data structures; 3) releasing network buffers in OS results in memory stalls to inkernel page data structures, contributing to the buffer release overhead; 4) besides memory stalls to packets, data copy implemented as a series of load/store instructions,

also has significant time on L1 cache misses and instruction execution. Moreover, keeping packets in caches after data copy, which will not be reused [11, 82], pollutes caches. Prevailing platform optimizations for data copy like Direct Cache Access (DCA) [31] are insufficient for addressing the copy issue.

The second part of our study is to propose new server I/O architecture to tackle the TCP/IP packet processing performance challenge while reducing NIC design hardware complexity. In the proposed server I/O architecture, the responsibility for managing DMA descriptors is moved to an on-chip network engine (NEngine). The on-chip descriptor management exposes plenty of optimization opportunities like extending descriptors to include information about memory stalls during network processing. When the NIC receives a packet, it directly pushes the packet into NEngine without waiting for long latency DMA descriptors fetches. NEngine reads extended descriptors to obtain packet destination location and information about data incurring memory stalls. Then, it moves the packet into the right memory location and checks whether data resides in caches. If not, NEngine sends data address to the hardware prefetching facility for loading data. To address the data copy issue, NEngine moves payload inside last level cache (LLC) and invalidates source cache lines after the movement. The new I/O architecture allows DMA engine to have very fast access to descriptors and leverages CPU caches to keep packets rather than the NIC buffers. This design substantially eliminates burden on the DMA engine and avoids extensive NIC buffers, particularly for high speed networks. The new server I/O architecture ameliorates all major performance bottlenecks of network processing and simplifies NIC designs, making general purpose platforms well suited for high speed networks.

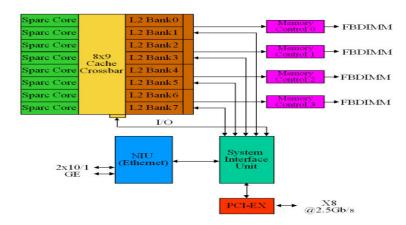

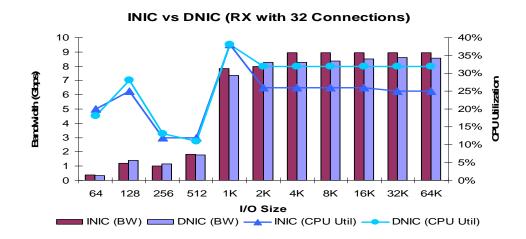

It was extensively reported before that integrating a NIC into CPU die is able to significantly reduce the TCP/IP packet processing overhead, mainly due to the less access latency to NIC registers [6, 7]. In the **third** part of this study, we started with detailed performance evaluation on a real Sun Niagara 2 platform with two integrated 10GbE NICs [83, 84] to fully compare the performance of an integrated NIC (INIC) and a PCI-E based discrete NIC (DNIC). In our experiments, we observe that the INIC only shows its advantage over the DNIC with large I/O sizes. It improves network bandwidth by 7.5% while saving 20% in relative CPU utilization. We characterize system behavior to understand the performance benefits with respect to different number of connections, OS overheads, instruction counts, and cache misses etc. All of our studies reveal that there is only marginal performance benefit of integrating NICs onto CPU die. More aggressive integrated NIC designs are required. We therefore proposed an enhanced integrated NIC (EINIC) for high speed networks. By leveraging fast interactions between CPU and INIC, we redesign CPU/NIC interface from hardware DMA to software program I/O (PIO). Additionally, we deploy several processing optimizations cost-efficiently by first evaluating their software implementations: Receive Side Scaling (RSS) [76] in hardware and Large Receive Offload (LRO) [27] in the driver. In addition, we also develop an I/Oaware LLC to avoid cache interference from other applications, and optimize cache coherence protocol to reduce unnecessary write-backs of network data. Our I/O-aware design splits LLC into I/O cache and general cache at the way level to eliminate cache interference. In order to meet various incoming rates, OS orchestrates the quota of the I/O cache according to the number of replaced cache lines but untouched by network stack.

The **fourth** part of this study is to understand the challenges of per-session data TCP control block (TCB) on TCP/IP packet processing when there are thousands of concurrent sessions like in web servers. Through our analysis, we realized that TCB data poses a great challenge in web servers and should be efficiently managed for fast packet processing. Then, we propose a new TCB cache addressed by session identifiers to address the challenge. We carefully redesign the TCB cache along two important axes: cache indexing and cache replacement policies. First, we propose a new cache indexing scheme for our TCB cache by employing two *Universal* hash functions [12]. Second, by leveraging characteristics of web sessions [4, 15, 19], we design a *speculative* cache replacement policy, which can effectively work on our TCB cache with two cache banks.

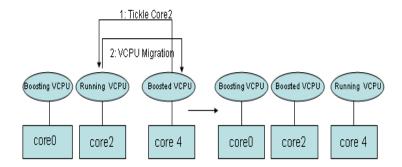

In the **fifth** part of this study, we extended our research to the virtualization domain, which has gained resurgent interests recently. We started with detailed per-packet processing overhead breakdown in virtualized environment. We realized that there are two major bottlenecks introduced by network I/O virtualization: 1) overheads on moving packets while processing packets in virtualized environment (e.g. packet copy among driver domain and guest domain, kernel-to-user packet copy inside guest domain); 2) the overhead of virtual switch in driver domain to de-multiplex packets. Motivated by the studies, we first develop two VMM scheduler optimizations to improve packet movement overheads by co-scheduling the driver domain and guest domain into the same cache domain and stealing credits from idling VCPU to favor I/O VCPUs. We design and implement a simplified virtual switch in an Intel Xeon server to significantly reduce the switching overhead in Xen [60, 61]. Furthermore, in order to eliminate cache misses on

packets along the packet movement path, we extend DCA by considering VMM scheduling information to accurately inject incoming packets into cores where corresponding guest domains are running.

#### **1.5 Outline and Contributions**

This study does detailed performance analysis of network processing over high speed networks and then provides several effective network I/O solutions to address the challenges from network processing. The major contributions of this study can be summarized as follows:

- We conduct NIC driver and OS instrumentation at a very fine-grained level to fully understand the TCP/IP packet processing overhead over 10GbE on mainstream servers. We pinpoint several bottlenecks and make new observations, which have never been reported before. The research is presented in Chapter 3.

- We propose new server I/O architecture to tackle the performance challenge while simplifying NIC hardware designs. In the new architecture, DMA descriptor management is shifted from NICs to an on-chip network engine and descriptors are extended with information about data incurring memory stalls. The new server I/O architecture not only addresses the network processing challenge, but also reduces hardware design complexity. The research is presented in Chapter 4.

- We fairly compare performance of INIC and DNIC on a real Sun Niagara 2 platform with two integrated 10GbE NICs in detail to completely understand the benefits of an integrated NIC. Then, we propose an enhanced integrated NIC

(EINIC) on multi-core processors to provide highly efficient network processing. The research is presented in Chapter 5.

- We analyze the challenges of TCB in web servers with thousands of concurrent sessions, and then design a dedicated TCB cache to efficiently manage TCBs for web servers. The TCB cache is designed along two hardware axes: *two-universal* hash functions based cache indexing and *speculative* cache replacement policy. The research is presented in Chapter 6.

- We do a detailed performance analysis of network I/O virtualization on conventional multi-core systems over 10GbE, and then propose both system optimizations on VMM scheduler and software switch, and efficient hardware support (extending DCA by considering VMM scheduler information to avoid cache misses on packets) to address the network I/O virtualization challenge. The research is presented in Chapter 7.

## **Chapter 2**

### **Background and Related Work**

#### 2.1 TCP/IP Packet Processing

TCP/IP over Ethernet is the most dominant communication protocol in commercial servers such as web server, e-commerce, database, storage over IP, etc. Unlike traditional CPU-intensive applications, TCP/IP packet processing is I/O-intensive. It involves several platform components (e.g. NIC, PCI-E, I/O Controller, main memory, CPU) and system components (e.g. NIC driver, OS). The processing in the receive side has much higher processing overheads than in the transmit side, consuming thousands of CPU cycles for each incoming packet. In this subsection, we revisit the network receiving process.

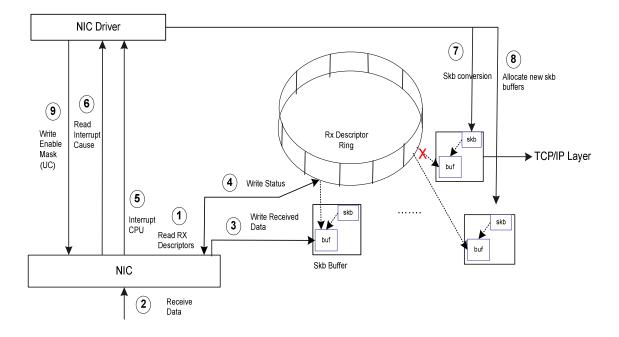

In the receive side, an incoming packet starts with the NIC/driver interaction. The RX descriptors (typically 16 bytes each), organized in circular rings, are used as a communication channel between the NIC driver and the NIC. The driver tells the NIC through these DMA descriptors, where in the memory to copy the incoming packets. To be able to receive a packet, a descriptor should be in "ready" state, which means it has been initialized and pre-allocated with an empty packet buffer (SKB buffer in Linux) accessible by the NIC [11]. The SKB buffer is the in-kernel network buffer to hold any packet up to MTU (1.5 KB). It contains an SKB data structure of 240 bytes carrying

packet metadata used by the TCP/IP protocol and a DMA buffer of 2 KB holding the packet itself.

Figure 2.1 Driver/NIC Interaction

The detailed interaction is illustrated in Figure 2.1. To transfer received packets, the NIC needs to fetch ready DMA descriptors from main memory over PCI-E bus to know the DMA buffer address (step 1). When the NIC receives Ethernet frames from the network (step2), it transfers the received packets into corresponding DMA buffers (denoted as *buf* in Fig.2.1) using DMA engine (step 3). Once the data is placed in memory, the NIC updates descriptors with packet length and marks them as used (step 4). Then, the NIC generates an interrupt to kick off network processing in CPUs (step 5). In the CPU side, the interrupt handler in the driver reads the NIC register to check the interrupt cause (in step 6). If legally, the driver reads descriptors to obtain packet's address and length, and then maps the packet into SKB data structures (step 7). After the driver delivers SKB buffers up to the protocol stack, it reinitializes and refills used

descriptors with new allocated SKB buffers for incoming packets in the near future (in step 8). Finally, the driver re-enables the interrupt by setting the NIC register (step 9). After the driver, SKB buffers are delivered up to the protocol stack. Once the protocol stack finishes processing, applications are scheduled to move packets to user buffers. Finally, the SKB buffers are reclaimed into OS [10, 11].

#### 2.2 Research in TCP/IP Packet Processing

It is well documented that Internet servers spend a significant portion of time processing packets [1, 6, 7, 22, 28-30, 44-46, 48-54, 66, 92-96]. A wide spectrum of research has been done on this topic to understand the overhead [7, 58, 64, 92, 93, 94]. Nahum *et al.* [64] used a cache simulator to study cache behavior of the TCP/IP protocol and showed that instruction cache has the greatest effect on network performance. Similarly, Zhao *et al.* [93, 94] revealed that packets and DMA descriptors exhibit no temporal locality. Xie *et al.* [92] analyzed instructions characteristics of TCP/IP protocol stack and proposed several new instructions for the protocol stack. Binkert *et al.* [7] did performance analysis of system overheads in TCP/IP workloads by using a full system simulator [8]. Makineni *et al.* [58] conducted architectural characterization of TCP/IP processing on the Pentium M microprocessor with 1GbE and concluded that the receive side is much more memory-intensive than the send side. Unfortunately, they built their studies on cache simulators or used low speed networks, and did not conduct a system-wide architectural analysis for high speed network processing on mainstream platforms.

In addition to the above performance analysis, extensive studies have also been conducted to improve TCP/IP packet processing performance. They can be broadly grouped into hardware optimizations and software optimizations.

#### 2.2.1 Hardware Optimizations

Hardware improvement for TCP/IP packet processing performance has been done from different dimensions. Offload support in NIC includes TCP Segmentation Offload (TSO) [36, 37], Interrupt Coalescing [36, 37], Receive Side Scaling (RSS) [76], Large Receive Offload (LRO) [27], TCP/IP Offloading Engine (TOE) [13, 25, 32] etc. TSO in NIC has been proposed long time back to segment a large message from applications into several smaller packets of size up to MTU, saving CPU cycles which are originally dedicated to TCP stack processing. Interrupt coalescing is also used on modern high speed NICs to moderate interrupt frequency by issuing a single interrupt once multiple packets have been received or transmitted. RSS is another hardware technique deployed in hardware NICs to distribute incoming packets across multiple cores based on the connection level. With the support of RSS, multiple cores are be leveraged to parallelize packet processing and cache locality is also considered while processing packets.

Since packet rate in 10GbE is so high, even the slightest improvement in per-packet processing benefits the overall I/O performance. Thus, LRO is proposed in hardware NICs to reduce the overhead by aggregating multiple in-order incoming packets from a single stream into a larger fragmented packet. It is recently implemented in software as an alternative to hardware assistance. Going further, TOE offloads the whole network stack into hardware NIC and would work for high bandwidth, low latency applications, particularly IP storage network with RDMA support. However, the technique itself has

been somewhat controversial because of the overhead in its software interface as well as security and extensibility concerns [25].

In addition to the above hardware offload in NIC, numerous studies have been conducted from the architectural perspective to reduce the data copy overhead [1, 6, 7, 31, 63, 77, 85, 95]. Mukerjee *et al.* [63] put a NIC in coherent memory to improve the performance by facilitating burst transfers of whole cache blocks and reducing control overheads. The Joint Network Interface Controller (JNIC) [77], a collaborative research project between HP and Intel, was designed to explore high performance in I/O operations. They built a system prototype by attaching 1GbE NIC on front side bus. Zhao *et al.* [95] designed an off-chip asynchronous DMA engine close to main memory to move data inside memory. The similar idea has been implemented in Intel platforms with the Intel I/OAT technique [1], but has been widely criticized in industry because memory stalls are still incurred when applications read packets from memory.

To eliminate memory stalls to packets, Intel proposed DCA to route network data into CPU caches [31], and implemented it in Intel 10 GbE adapters and server chipsets. Its performance evaluation on real servers has demonstrated overhead reduction in data copy [45, 46]. Recently, Tang *et al.* [85] claimed that DCA might incur cache pollution on small LLC and introduced two cache designs (a dedicated DMA cache or limited ways of LLC) to keep packets. Binkert *et al.* [6, 7] integrated a redesigned NIC to reduce the processing overhead by implementing zero-copy and reducing access latency to NIC registers.

#### 2.2.2 Software Optimizations

Software optimizations for network processing have also been aggressively explored as an alternative to advanced, more costly hardware.

When concurrent processing units are provided, it is intuitive to run TCP/IP processing on an independent computation resource, which is tightly coupled with the application processor. Instead of using network processor to process network traffic or offload the whole TCP/IP stack onto NIC, one of the cores on a multi-core CPU can be bound to work with network processing, while other cores can run applications such as http requests and/or scientific computations. To distinguish from TOE, the last category is named "TCP Onloading" [26, 28]. Although the idea of TCP onloading sounds intuitive, most of such available designs require a large amount of changes in the operating system level, particularly in the TCP/IP protocol stack. Also, open problems like inter-core communication, mutual influences of processes for different applications still remain unsolved.

With little hardware support from NIC, Shalev *et al.* [80] proposed a loosely coupled TCP acceleration framework to separate out TCP fast path and optimize TCP fast path processing in software. LRO, a technique to coalesce small receiving packets into a large single packet, can also be deployed in the NIC driver to reduce the number of packets delivered up to network stack. Another technique, called zero-copy, eliminates memory copying by directly mapping packet payload in kernel to user buffer and saves memory access penalties [11]. However, it requires that all user buffers should be page aligned for the mapping of kernel to user space, thus limiting its wide deployment.

#### 2.3 Network I/O Virtualization

Virtualization is a broad term that refers to the abstraction of physical computer resources. A typical virtualized platform consists of a software virtual machine monitor that "virtualizes/abstracts" the physical resource of the platform and provides a simulated environment that appears to the operating system as hardware. Network virtualization was invented and implemented in IBM's System/360 and System/370 [74]. Each virtual machine in these initial virtualized architectures was exclusively assigned a particular set of physical devices. Data transfer relied on channel programs executing in the VMM, which ensured resource isolation.

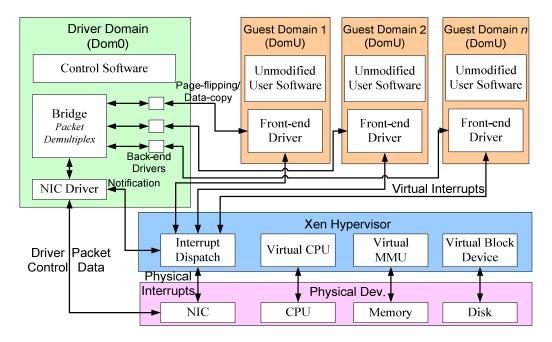

Despite the high performance through private I/O access, the costly replication of physical devices for each virtual machine limited per domain utilization. As a result, research in Xen [5] designed shared access to devices and relied on a dedicated software entity to perform physical device management. This paper focused on the most popular open source virtualized system Xen.

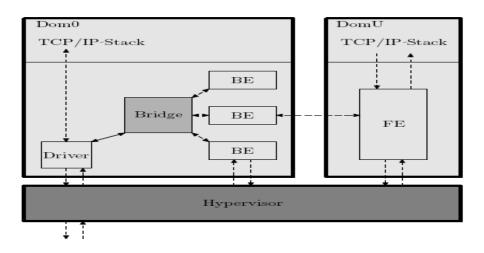

Fig. 2.2 is an illustration of the Xen VMM. The VMM provides an abstraction layer between the VMs and the actual hardware, leaving each guest VM an illusion of running independently on native hardware. A privileged VM (driver domain or Dom0) runs a modified version of Linux that uses native Linux device drivers to manage physical I/O devices. Other VMs (guest domain or DomU) transmit and receive packets by communicating with Dom0 through shared memory I/O channels.

Figure 2.2: Network I/O Virtualization in Xen

Once a packet arrives at the NIC, it generates an interrupt. The VMM then forwards the interrupt to the Dom0. When Dom0 acquires CPU, it DMAs the packet into the reception I/O ring. After de-multiplexing the packet through the nested Ethernet Bridge to an appropriate back-end driver, Dom0 employs a data copy mechanism by default to directly copy data from the back-end driver to the front-end driver in the corresponding DomU. Once the packet reaches the front-end driver in DomU, back-end driver requests the VMM to send a virtual interrupt to notify the target domain of the new packet. Then the packet is processed from the kernel space to the user space of DomU as if it had come directly from the physical NIC.

# 2.4 Research in Network I/O Virtualization

Since the birth of VM, research in improving virtualized I/O performance never faded away. We summarize previous works into two categories: hardware architecture and system optimizations.

Numerous studies have been done in server architectures to efficiently tackle the network I/O virtualization challenge. In industry, Intel [35, 39] offloads virtual switch (or packet de-multiplexing) from the driver domain to hardware NIC and deploys multiple queues to allow guest OS to directly access hardware queues. In order to avoid memory protection and address translation overheads in software, hardware IOMMU [3, 39] was proposed and incorporated into server platforms. Recently, PCI-E standard group proposes single root IO virtualization (SR-IOV) [70] to self-virtualize a physical device into multiple lightweight PCI-E devices, significantly avoiding I/O virtualization overheads.

For system optimizations, Ongaro et al. [67] sorted the domains with the same states in the runqueue based on their remaining credits rather than arbitrarily insert the new domain at the end of each state section. However, they focused on the fairness of I/O performance with 1GE network and did not consider the VMM scheduler on mainstream multi-core systems where behaves significantly different from single core systems. With the same optimizations on our experiment environment under 10 GbE, we find that the blocking of scheduler tickle adversely glooms the I/O performance by a factor of 100 and the runqueue sort does not make any difference for I/O performance. In addition to VMM scheduler optimizations, lots of engineering optimizations have also been implemented to improve network I/O performance in virtualization environment. Menon *et al.* [59, 60, 61] analyzed virtualization performance overhead and then implemented numerous optimizations (e.g. reusing grant table, using large page size, moving data copy to guest etc) to bridge the gap between software and hardware techniques for I/O virtualization. Guo *et al.* [30] designed cache-aware scheduling for virtualization to improve web server performance. Liu et al. [56] adopted virtualization technology for HPC and allowed each domain to directly access the high performance network. However, they targeted to the high performance network InfiniBand rather than Ethernet Network. In Ethernet Network, some researches including Crossbow [18] tried to address the performance issues by taking advantage of the new Ethernet NIC features like multiple TX/RX queues to allow domains to directly access the hardware. They heavily rely on hardware and hence sacrifice the features of portability and live migration, two major incentives for deploying virtualization in high end servers.

# Chapter 3

# Understanding TCP/IP Packet Processing Performance Bottleneck over 10GbE

The performance of the TCP/IP network stack plays a crucial role in network servers. In order to identify the performance problems in network stack, this chapter first profiles the whole running system while processing packets over 10GbE networks to obtain perpacket processing overhead breakdown. Then, we do fine-grained instrumentation in NIC driver and OS kernel to conduct a detailed performance characterization. The performance problems identified in this chapter serve as a motivation for the new I/O architecture in Chapter 4.

# **3.1 Experimental Setup**

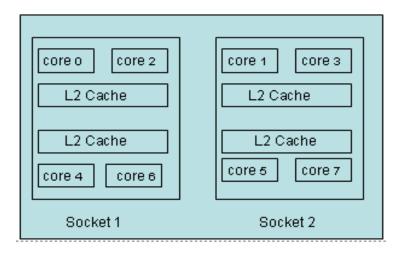

We conduct extensive experiments to understand network processing overheads over 10GbE across a range of I/O sizes. Both SUT (System under Test) and stress machines are Intel servers shown in Figure 3.1. Each server contains two Quad-Core Intel Xeon 5335 processors [38]. Each core is running at 2.66GHz frequency and each processor has 2 LLCs of 4MB each shared by 2 cores. The servers are connected by two PCI-E based Intel 10Gbps XF server adapters [37]. They ran Linux kernel 2.6.21 and Intel 10GbE NIC driver IXGBE version 1.3.31. We retain default settings of the Linux network subsystem

and the driver, unless stated otherwise. Note that LRO, a technique to amortize the perpacket processing overhead by combining multiple in-order packets into a large packet, is enabled in the driver. Stream hardware prefetcher employing a memory access stride based predictive algorithm is configured in the servers [38]. In the experiments, the micro-benchmark Iperf with 8 TCP connections is run to generate network traffic between servers (SUT is a receiver). We find from the experiments that one core with 4MB LLC achieves ~5.6Gbps throughput and two cores with 8MB LLC are saturated to obtain a line rate throughput. The high processing overhead motivates us to breakdown the per-packet processing overhead.

Figure 3.1 Intel Xeon servers

# 3.2 Per-Packet Processing Overhead Breakdown

We use the tool Oprofile [68] to collect system-wide function overheads while Iperf [33] is running over 10GbE. We group all functions into components along the network processing path: the NIC driver, IP, TCP, data copy, buffer release, system call and Iperf. All other supportive kernel functions such as scheduling, context switches etc. are

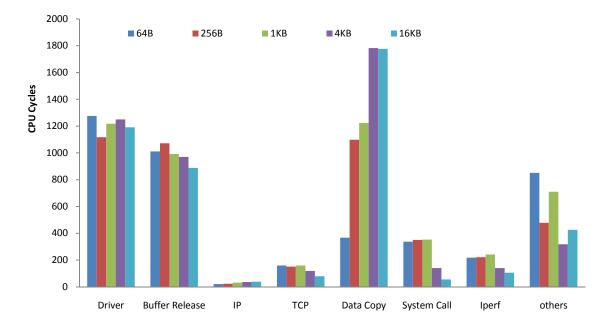

categorized as others. Per-packet processing time breakdown is calculated and illustrated in Figure 3.2. Note that I/O sizes are not packets over Ethernet and large I/Os larger than MTU (1.5KB on Ethernet) are segmented into several packets (<=MTU).

We obtain the following observations from Fig.3.2: 1) the overhead in data copy increases as the I/O size grows and becomes a major bottleneck with large I/Os (>=256 bytes); 2) the driver and buffer release consume ~1200 cycles and ~1100 cycles per packet, respectively, regardless of I/O sizes. They correspond to ~26% and 20% of processing time for large I/Os and even higher for small I/Os; 3) the TCP/IP protocol processing overhead is substantially reduced because LRO coalesces multiple packets into one large packet to amortize the overhead. Fig.3.2 reveals that besides data copy, high speed network processing over mainstream servers has another two unexpected major bottlenecks: the driver and buffer release.

Figure 3.2 Per-packet processing overhead breakdown

# **3.3 Fine-Grained Instrumentation**

The Oprofile in Subsection 3.2 does profiling at the coarsegrained level and attributes CPU cost such as retired cycles and cache misses to functions.

**Table 3.1: Instrumentation example**

| Coarse-grain                                                          | Fine-Grain                                                                                                                                                                                             |  |

|-----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| INSTRUMENT(Counter1)<br>ixgbe_clean_tx_irq()<br>INSUTRUMENT(Counter2) | <pre>ixgbe_clean_tx_irq() {     INSTRUMENT(Counter3)     Code Segment 1     INSTRUMENT(Counter4)     prefetch(skb-&gt;data - NET_IP_ALIGN);     INSTRUMENT(Counter5)      INSTRUMENT(Counter6) }</pre> |  |

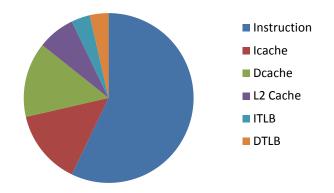

It is unable to identify data or macro incurring the cost. In order to locate the cost, we manually did fine-grained instrumentation inside functions. The environment in Subsection 3.2 is used. Table 3.1 shows one instrumentation example in the driver. We first measure the function's cost and then do fine-grained instrumentation for every code segment if the function has considerable cost. We continue to instrument each code segment with considerable cost until we locate the bottlenecks. Our instrumentation is applied to all functions along the processing path. Most of events are collected including CPU cycles, instruction and data cache misses, LLC misses, ITLB misses and DTLB misses etc. Since large I/Os include all three major overheads, this subsection presents the detailed analysis for the 16KB I/O.

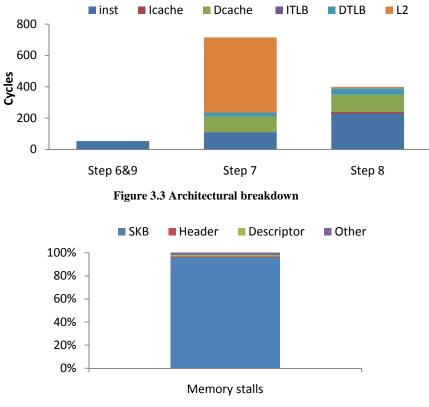

## 3.3.1. Driver

The driver comprises of three main components: NIC register access (step 6 and 9), SKB conversion (step 7) and SKB buffer allocation (step 8), as shown in Fig.2.1. Existing studies [6, 7] claimed that NIC register access contributes to the driver overhead due to

long latency traversal over PCI-E bus, and then proposed NIC integration to reduce the overhead. In this subsection, we architecturally breakdown the driver overhead for each packet and present results in Figure 3.3. In contrast to the general accepted notion that the long latency NIC register access results in the overhead [7], the breakdown reveals that the overhead comes from SKB conversion and buffer allocation. Although NIC register access takes ~2500 CPU cycles on mainstream servers, ~60 packets are processed per interrupt over 10GbE (~7 packets/interrupt over 1GbE) substantially amortizing the overhead. In addition, Fig.3.3 also reveals that L2 cache misses mainly result in the SKB conversion overhead and long instruction path is the largest contributor of the SKB buffer allocation overhead.

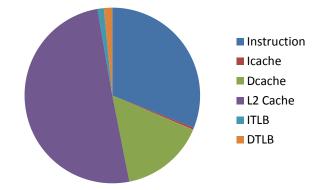

Figure 3.4 L2 miss sources in step7

Since L2 cache misses in SKB conversion constitute ~50% of the driver overhead, we do detailed instrumentation to identify data incurring those misses. We group data in the driver into various data types (SKB, descriptors, packet headers and other local variables) and measure their misses. The result presented in Figure 3.4 reveals that SKB is the major source of the memory stalls (~1.5 L2 misses/packet on SKB). Different from prior studies [6, 7], the memory stalls to packet headers are hidden and overlapped with computation because the recent driver uses software prefetch instructions to preload headers before they are accessed. Unfortunately, SKB access occurs at the very beginning of the driver and software prefetch instructions cannot help. Although DMA invalidates descriptors to maintain cache coherence, the memory stalls to descriptors are negligible  $(\sim 0.04 \text{ L2 misses/packet})$ . That is because each 64 bytes cache line can host 4 descriptors of 16 bytes each and hardware prefetchers preload several consecutive descriptors with a cache miss. To understand the SKB misses, we instrument kernel to study its reuse distance over 10GbE. It is observed that SKB has long reuse distance (~240K L2 access), explaining the misses.

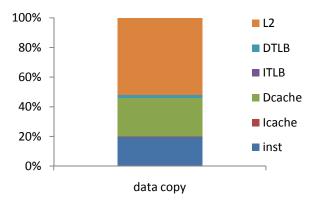

#### 3.3.2. Data Copy

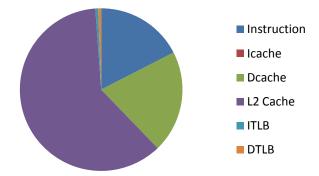

After protocol processing, user applications are scheduled to copy packets from SKB buffers to user buffers. Data copy incurs mandatory cache misses on payload because DMA triggers cache invalidation to maintain cache coherence, and thus consumes a large number of CPU cycles. We study its architectural overhead breakdown as shown in Figure 3.5. 16KB I/O is segmented into small packets of MTU each in the sender and they are sent to the receiver. Fig.3.5 shows that L2 cache misses are the major overhead

(~50%, ~3.5 L2 misses/packet), followed by data cache misses (~27%, ~50 misses/packet) and instruction execution (~20%). Although DCA implemented in Intel recent platforms avoids L2 cache misses, it is unable to reduce overheads in L1 cache misses and a series of load/store instructions execution (total ~47%). Due to the small L1 cache size, routing network data into L1 caches would pollute caches and degrade performance [46, 85]. Moreover, since packets become obsolete after data copy [11], loading them into L1 caches or keeping them in L2 caches may evict other valuable data to incur cache pollution. Hence, more optimizations are needed to fully address the data copy issue.

Figure 3.5 Data copy breakdown

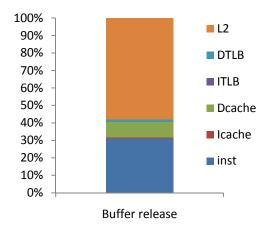

Figure 3.6 Buffer release breakdown

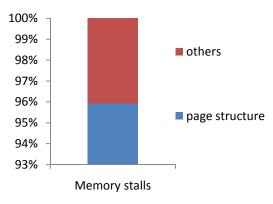

## 3.3.3. Buffer Release

SKB buffers need to be reclaimed after packets are copied to user applications. SKB buffer allocation and release are managed by slab allocator [10]. The basis for this allocator is retaining an allocated memory that used to contain a data object of certain type and reusing that memory for the next allocations for another object of the same type. Buffer release consists of two phases: looking up an object cache controller and releasing the object into the controller. In the implementation of slab allocator, the page data structure is used to keep cache controller information and read during the object cache controller lookup. This technique is widely used by mainstream OS such as FreeBSD, Solaris and Linux etc.

Figure 3.6 shows architectural overhead breakdown for buffer release. We observe from Fig.3.6 that L2 cache misses are the single largest contributor to the overhead (~1.6 L2 cache misses/ packet). Similarly, we analyze data sources of L2 cache misses and present results in Figure 3.7. The figure reveals that L2 cache misses are from the 128 bytes in-kernel page data structures. The structure reuse distance analysis shows that it is reused after ~255K L2 cache access, explaining the cache misses.

Figure 3.7 L2 miss sources.

The above studies reveal that besides memory stalls to itself, each packet incurs several cache misses on corresponding data and has considerable data copy overhead. Some intuitive solutions like having larger LLC (>8MB for 10GbE) or extending the platform optimization DCA might help to some extent, but they have major limitation. Our simulation results show that, without considering application memory footprint, 16MB LLC is needed to avoid those cache misses of packet processing over 10GbE. When network jumps to 40GbE and beyond, increasing LLC becomes an ineffective solution. More importantly, it is unable to address NIC challenges and the data copy issue. Unlike increasing LLC, extending DCA to deliver both packets and those missed data from NICs into caches is more efficient in avoiding memory stalls. Unfortunately, it stresses NICs more heavily and degrades PCI-E efficiency of packet transfers [69, 70], and does not consider the data copy issue as well. In order to attack all challenges from continuously increasing network speed, a holistic and intelligent I/O solution is needed.

#### **3.4 Summary**

In this chapter, we first studied the per-packet processing overhead on mainstream servers with 10GbE and pinpointed three major performance overheads: data copy, the driver and buffer release. Then, we did fine-grained instrumentation in the NIC driver and OS kernel to do a system-wide architectural analysis. Unlike existing tools attributing CPU cost to functions, our instrumentation was done at the data granularity and can pinpoint data with considerable cost. Our studies reveal several new findings: 1) the major network processing bottlenecks lie in the NIC driver, data copy and buffer release; 2) in contrast to the generally accepted notion that long latency NIC register access

results in the driver overhead, our results show that the overhead mainly comes from memory stalls to network buffer data structures; 3) releasing network buffers in OS results in memory stalls to in-kernel page data structures, contributing to the buffer release overhead; 4) besides memory stalls to packets, data copy implemented as a series of load/store instructions, also has significant time on L1 cache misses and instruction execution.

# **Chapter 4**

# **Repartitioning CPU/NIC**

In Chapter 3, we carefully studied the TCP/IP packet processing overhead over high speed networks and pinpointed the bottlenecks. In this chapter, we propose a new server I/O architecture to tackle the performance challenge. In the new I/O architecture, we move DMA descriptor management from the NIC to an on-chip network engine and extend descriptors with information about data incurring memory stalls. The new I/O architecture is not only able to effectively tackle the performance challenge, but also reduce NIC hardware design complexity. Its designs are elaborated in the following subsections.

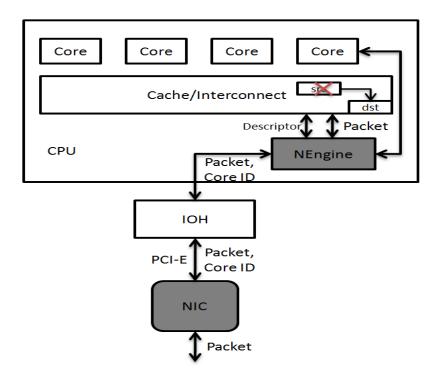

# 4.1 New Server I/O Architecture

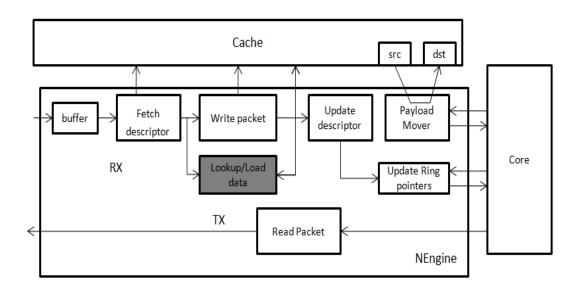

The overview of the new architecture is illustrated in Figure 4.1. In the new architecture, we move DMA descriptor management from NICs to an added on-chip network engine (NEngine) near to LLC. The on-chip descriptor management enables us to easily extend descriptors with information about data incurring memory stalls. Similar to the memory controller, NEngine connects to I/O Hub (IOH) for parsing PCI-E transactions. It communicates with faster cache hierarchy for DMA descriptor fetches/writes and packet movement, alleviating the processing burden on DMA engine. Due to close proximity to LLC, NEngine has low communication cost with LLC.

When NEngine receives a packet, it reads descriptors from cache hierarchy. Then it moves the packet into corresponding cache location and preloads those data incurring memory stalls. The new architecture exploits LLC to keep packets other than multiple RX/TX queues in NICs. Commodity high speed NICs allow each core to have one dedicated RX/TX queue, thus increasing NIC cost and impeding NIC's scalability over cores. The new architecture avoids extensive buffer resources and reduces NIC hardware cost. Moreover, NEngine also implements efficient payload movement inside LLC and proactively purges obsolete packet data after data copy to address the data copy issue. The new architecture fundamentally reduces all three major performance overheads of network processing while effectively simplifying NICs. The detailed designs are elaborated in the following subsections.

Figure 4.1 New I/O architecture overview

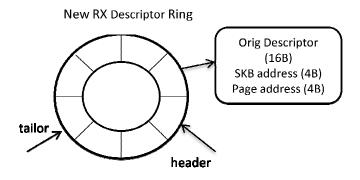

#### 4.1.1 NEngine

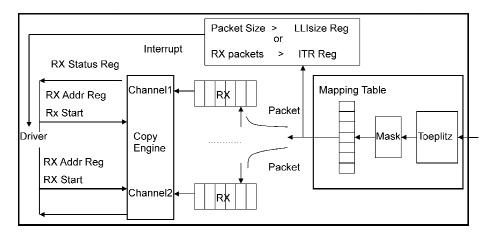

During network processing, CPUs and NICs communicate through DMA descriptors. As the communication channel, DMA descriptors are organized as a circular ring. Each descriptor is 16 bytes and includes packet metadata such as packet length, memory address and status etc. In the contemporary I/O architecture, NICs fetch or write descriptors via PCI-E bus before or after packet movement. The descriptor fetches/writes have long latency stressing DMA engine [90] and also waste a large number of PCI-E transactions degrading PCI-E payload efficiency [69, 70]. The on-chip descriptors management avoids these issues, and more importantly, enables us to easily extend the descriptors because of much faster communication with cache hierarchy. By exploiting this design, we extend RX descriptors with information about data incurring memory stalls: SKB and page data structures, as pinpointed in Section 3. The extended descriptors are illustrated in Figure 4.2. Besides original 16 bytes, the new descriptor includes 4 bytes physical address of SKB and internal page data structures each. Two hardware registers in NEngine are dedicated to storing data structure length in the form of the number of cache lines. In Linux, SKB is 240 bytes and page structure is 128 bytes, corresponding to four and two cache lines of 64 bytes each, respectively. The typical ring buffer size of 10GbE NICs is 1024 entries and thus the new ring buffer size only increases by 8KB.

Figure 4.2 Extended DMA descriptors

With the new descriptors, the block diagram of NEngine is illustrated in Figure 4.3. Besides major components shown in Fig. 4.3, NEngine also offers dedicated registers to keep ring buffer base address and ring pointer information as traditional NICs do. When a packet arrives at the NIC, without fetching DMA descriptors to know memory location for the packet, the NIC calculates core ID for packet processing using RSS hardware unit (RSS distributes packets among cores by hashing packet's 4-tuple) and sends the packetwith core ID into a small buffer in NEngine. Fetch descriptor unit identifies the corresponding descriptor address according to the ring base address of the core ID and ring buffer pointers, and then sends a cache read request to get the descriptor. Chapter 3 shows that mainstream severs exhibit extremely high descriptor cache hit ratios even with DMA invalidation (96%). The on-chip descriptor management avoids DMA invalidation and has a higher descriptor cache hit ratio. Thus, the fetch descriptor unit can access to descriptors very fast and is much simpler than the original DMA engine. With the knowledge of memory location and data incurring memory stalls, the write packet unit moves the packet into caches. Meanwhile, the lookup/load unit lookups those data and loads them if they do not reside in caches. To facilitate the lookup/load unit, we extend the conventional cache architecture with a new cache operation: *lookup*. Unlike normal cache operations such as cache read, write etc, the new operation *lookup* returns whether data is in caches, other than data themselves. The lookup/load unit sends *lookup* operations to lookup those data. If the data is not in caches, it generates prefetch commands to the existing hardware prefetching facility for loading the data. After the packet is moved into cache hierarchy, NEngine updates the descriptor status field and ring buffer pointers for the driver as traditional NICs do.

In addition, NEngine moves payload inside LLC to bypass L1 caches and to avoid a series of load/store instructions. Since the source data becomes obsolete after data copy [10], NEngine invalidates source cache lines to purge the data. To support efficient movement, we extend the cache architecture with a new cache operation: *read\_invalidate*, which reads cache lines and then does cache invalidation. During data copy, TCP/IP protocol breaks discontinuous physical address ranges into a set of consecutive physical ranges and programs NEngine via three hardware registers: *src*, *dst*, *len*. Then, NEngine breaks continuous physical address ranges into a set of chunks at the cache line granularity and generates new *read\_invalidate* operations to read and invalidate cache lines. Finally, it writes those data into destination cache lines. Our payload movement differs from prior copy engines [1, 95] as follows: 1) payload movement is done inside caches and payload in caches is invalidated after movement; 2) the virtual-to-physical address translation overhead is negligible because data copy is done in the OS context. In Linux, less than 10 cycles are needed for the address translation.

Figure 4.3 Basic block of NEngine

When we come to the transmit side, NEngine reads transmitted packets from cache hierarchy and transfers them into the NIC over PCI-E bus. Once the NIC receives the transmitted packets from NEngine, the MAC processing units automatically sends them over Ethernet links. Besides high efficient network processing, our designs simplify NIC designs in terms of buffer resource and DMA engine and also reduce PCI-E traffic used for descriptor fetches/writes.

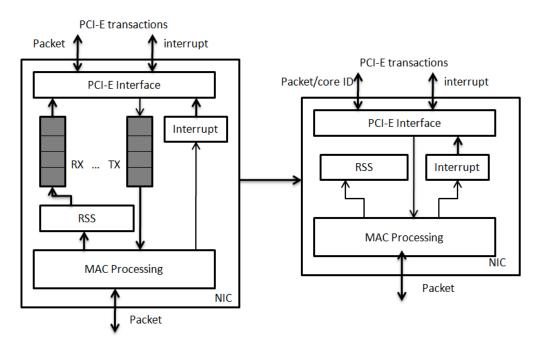

## 4.1.2 NIC

In the new architecture, NICs are simplified with less hardware resource. Figure 4.4 illustrates a traditional NIC in the left box and a new NIC in the right box. In the traditional NIC, the MAC processing unit receives packets from Ethernet links and does RSS to load balance incoming packets among cores/queues at the connection level. The packets are stored in corresponding RX queues. DMA engine uses PCI-E transactions to fetch descriptors from memory and to move data from RX queues to memory. Interrupt

coalescing unit will send interrupts to cores when the number of transferred packets reach up to a threshold set by the driver or a preprogrammed timer expires. Similarly, in order to transmit packets, the NIC fetches TX descriptors to know packet memory location and moves packets into corresponding TX queues. Then, packets are sent over Ethernet links and interrupts are sent to cores. In the new NIC, we remove large multiple hardware queues and DMA engine marked as grey in the left box. When RSS receives a packet from the MAC processing unit, it calculates the core assigned to packet processing. Then, the NIC directly sends the packet with core ID to NEngine. Similar to the receive side, when the NIC receives a transmitted packet, the MAC processing unit directly takes over the packet for transmission. RSS and Interrupt coalescing units behave the same as traditional NICs do.

Figure 4.4 Simplified NIC in the new architecture

#### 4.1. 3. Software Support

The new server I/O architecture inherits the descriptor-based software/hardware interface and only needs some modest support from the device driver and the data copy component. In the driver, when new SKB buffers are allocated to refill RX descriptors, besides DMA buffer address the driver sets starting address of SKB and page data structures to the descriptors. When packets finish protocol processing, the data copy component programs NEngine to move payload and waits until NEngine finishes the movement. There is no need to modify TCP/IP protocol stack, system call and user application.

# **4.2 Performance Evaluation**

We choose the full system simulator Simics [57] to evaluate our designs by enhancing it with detailed cache, I/O timing models and modeling of the effects of network DMA. We extend the Digital Equipment Corporation 21140A Ethernet device with the support of interrupt coalescing using Device Modeling language DML to simulate a 10GbE Ethernet NIC. The device itself is connected to a lossless, full-duplex link of configurable bandwidth. The latency of a packet traversing the link is simply fixed to 1 *us*. Two systems (client and server) running Linux 2.6.16 are simulated and interconnected with 10GbE. Since the stream hardware prefetcher is the most popular prefetcher in mainstream servers, we employ it in the simulator to speed up the memory access of streamed network data.

We implemented the new

I/O architecture and developed a NIC driver in Linux. LRO was implemented in the driver. To understand performance impacts of our designs on network processing, we first

| Processor               | Quad-Core, 3GHz, two issue, in-order                                              |  |

|-------------------------|-----------------------------------------------------------------------------------|--|

| ICache/DCache           | Private per core, 32KB 2-way split, 3-cycle hit<br>latency, 64 bytes cache line   |  |

| L2 Unified Cache        | 8M, 16-way split, 14 cycles hit latency, 64 bytes cache line, shared by all cores |  |

| Main memory             | 400 cycles                                                                        |  |

| Prefetcher              | Stream prefetch, degree: 4                                                        |  |

| I/O Register            | 1600 cycles                                                                       |  |

| Interrupt Coalesce Rate | 64 packets per interrupt                                                          |  |

| NEngine                 | 10 cycles to L2 cache                                                             |  |

| Ring buffer             | 1024 entries/ring                                                                 |  |

**Table 4.1 System configurations**

used the micro-benchmark Iperf in the experiments. Then, we study how much benefit web servers achieve by running the SPECWeb [4] benchmark. In each case, only one system is of interest, while the other merely serves as a stressor. SUT is configured with detailed timing models and the stressor runs with the fast functional mode and is not a bottleneck. The parameters we used in modeling the configuration are listed in Table 4.1. We are more interested in the relative behavior of these systems than their absolute performance, so some of these parameters are approximations.

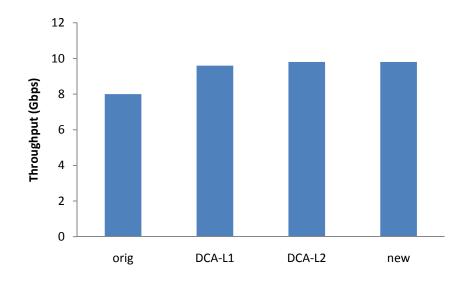

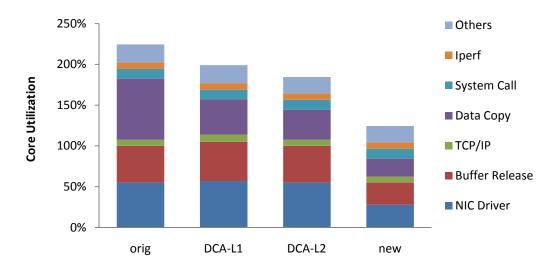

## 4.2.1 Network Performance

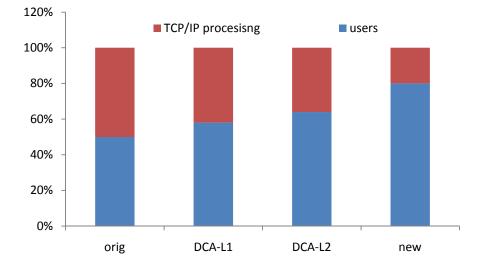

First, we looked at network performance in the receive side by running Iperf under various configurations: the original system (*orig*), DCA routing data to L1 caches (*DCA-L1*), DCA routing data into L2 caches (*DCA-L2*), the new server I/O architecture (*new*). LRO is included in all server configurations. Since large I/Os have all three major overheads, we present large I/O results in this subsection.

Figure 4.5 Network throughput

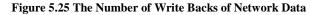

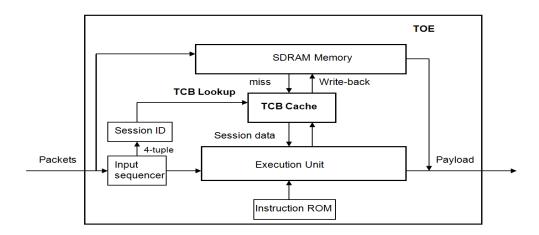

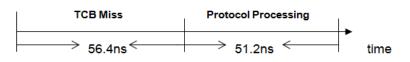

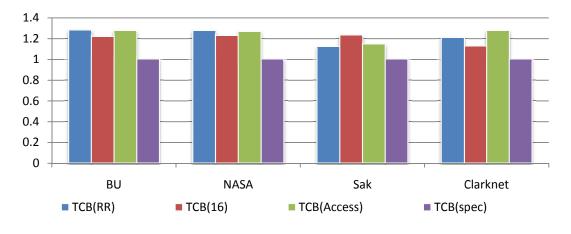

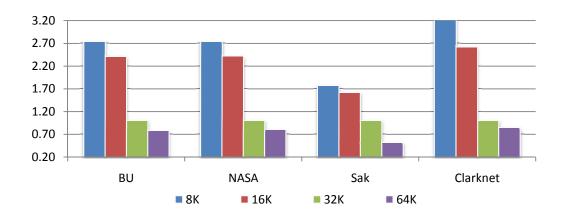

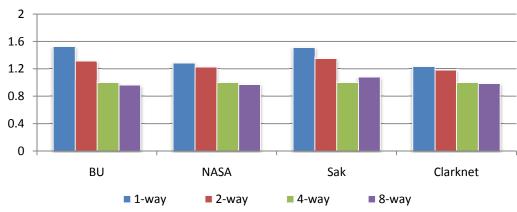

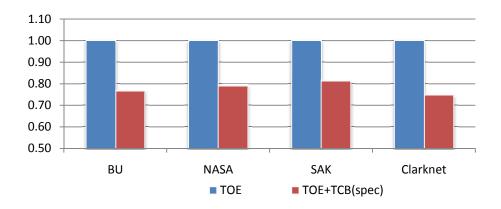

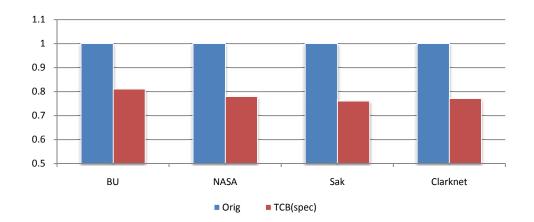

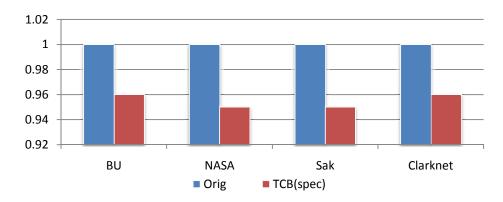

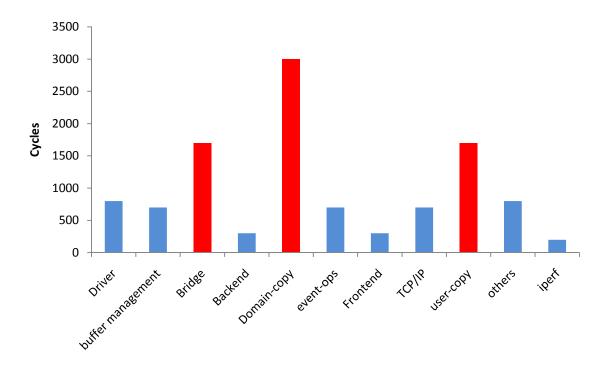

Figure 4.5 illustrates network throughput achieved by various configurations. We also present corresponding core utilization and utilization breakdown in Figure 4.6. As shown in Fig.4.5 and Fig.4.6, *orig* can achieve only ~8 Gbps throughput by consuming ~225% core utilization in the SUT with four cores. Memory subsystem is the potential bottleneck of achieving line rate throughput and an increase in CPU performance could