# UCLA UCLA Electronic Theses and Dissertations

Title

Consistency-based System Security Techniques

**Permalink** https://escholarship.org/uc/item/4fk379ms

**Author** Wei, Sheng

Publication Date 2013

Peer reviewed|Thesis/dissertation

### UNIVERSITY OF CALIFORNIA

Los Angeles

# Consistency-based System Security Techniques

A dissertation submitted in partial satisfaction of the requirements for the degree Doctor of Philosophy in Computer Science

by

Sheng Wei

2013

© Copyright by Sheng Wei 2013

# Abstract of the Dissertation Consistency-based System Security Techniques

by

#### Sheng Wei

Doctor of Philosophy in Computer Science University of California, Los Angeles, 2013 Professor Miodrag Potkonjak, Chair

Gate-level characterization (GLC) is the process of characterizing each gate of an integrated circuit (IC) in terms of its properties, such as power and delay. It is a key step in the IC applications regarding cryptography, security, and digital rights management. However, GLC is challenging due to unpredictable process variations, gate correlations, and difficulties to scale to large designs.

We have developed a new approach for hardware and system security using consistency-based GLC and statistical analysis. In particular, we first conduct input vector control, test point insertion, and thermal conditioning to impose extra variations to the IC properties and break the correlations among gates. Then, we partition the circuit into small segments and characterize the gate-level IC properties in each segment. Finally, we employ statistical methods to analyze the consistency of the gate-level properties, both intra- and inter-segments, to identify and diagnose malicious modifications (e.g., hardware Trojans) or other misconduct (e.g., IC counterfeiting) made by an adversary.

Based on our research findings in the consistency-based GLC, we develop a group of hardware security applications, including (1) hardware Trojan detection and diagnosis; (2) hardware metering and digital rights management; and (3) remote and in-field wireless security. The effectiveness of the consistency-based GLC in varieties of applications indicates that it is the foundation and enabler for reliable hardware and system security techniques.

The dissertation of Sheng Wei is approved.

Hongquan Xu

Majid Sarrafzadeh

Milos Ercegovac

Miodrag Potkonjak, Committee Chair

University of California, Los Angeles 2013

# TABLE OF CONTENTS

| 1        | Intr | $oduction \ldots 1$ | Ĺ |

|----------|------|----------------------------------------------------------------------------------------------------------------|---|

|          | 1.1  | Motivation                                                                                                     | L |

|          | 1.2  | Challenges                                                                                                     | 2 |

|          | 1.3  | Design Principles                                                                                              | 3 |

|          | 1.4  | Contributions and Organizations                                                                                | 1 |

| <b>2</b> | Bac  | kground and Preliminaries                                                                                      | 7 |

|          | 2.1  | Power Models                                                                                                   | 7 |

|          | 2.2  | Delay Model                                                                                                    | 3 |

|          | 2.3  | Process Variation Model                                                                                        | ) |

|          | 2.4  | IC Aging Model                                                                                                 | ) |

| 3        | Gat  | e-level Characterization                                                                                       | L |

|          | 3.1  | GLC Overview                                                                                                   | L |

|          | 3.2  | Gate-level Power Characterization                                                                              | 2 |

|          |      | 3.2.1 Objectives $\ldots$ $12$                                                                                 | 2 |

|          |      | 3.2.2 Power Measurements and Equations                                                                         | 2 |

|          |      | 3.2.3 Technical Issues in Power GLC                                                                            | 1 |

|          |      | 3.2.4 Power Characterization Overall Flow                                                                      | 5 |

|          |      | 3.2.5 Correlation Detection                                                                                    | 3 |

|          |      | 3.2.6 Correlation Elimination                                                                                  | 3 |

|          |      | 3.2.7 Improving the Objective Function                                                                         | L |

|   |     | 3.2.8  | MLE Post-processing                                             | 24 |

|---|-----|--------|-----------------------------------------------------------------|----|

|   | 3.3 | Gate-l | evel Delay Characterization                                     | 25 |

|   |     | 3.3.1  | Delay Characterization Overview                                 | 25 |

|   |     | 3.3.2  | Delay Paths Identification and Selection                        | 27 |

|   |     | 3.3.3  | Delay GLC Using Linear Programming                              | 30 |

|   |     | 3.3.4  | SAT-based Approach for Characterizing All Gates                 | 32 |

|   | 3.4 | Scalab | bility Techniques for GLC                                       | 34 |

|   |     | 3.4.1  | IC Segmentation by Conducting Input Vector Control              | 35 |

|   |     | 3.4.2  | Region-based Circuit Partition for Delay Characterization       | 36 |

|   | 3.5 | GLC ]  | Evaluation Results                                              | 40 |

|   |     | 3.5.1  | Power GLC                                                       | 40 |

|   |     | 3.5.2  | Delay GLC                                                       | 41 |

|   | 3.6 | GLC ]  | Related Work                                                    | 47 |

| 4 | Har | rdware | Trojan Detection and Diagnosis                                  | 49 |

|   | 4.1 | Hardw  | vare Trojan Attack Model                                        | 50 |

|   |     | 4.1.1  | One-gate HT Model and Benchmark                                 | 50 |

|   |     | 4.1.2  | Customizable HT                                                 | 58 |

|   | 4.2 | HT Va  | ariable-based Hardware Trojan Detection and Diagnosis $\ . \ .$ | 62 |

|   |     | 4.2.1  | HT Detection Using HT Variable                                  | 62 |

|   |     | 4.2.2  | HT Diagnosis Using HT Variable                                  | 64 |

|   | 4.3 | Consis | stency-based Hardware Trojan Detection and Diagnosis            | 67 |

|   |     | 4.3.1  | Consistency-based Hardware Trojan Detection                     | 67 |

|          |                   | 4.3.2                                                       | Consistency-based Hardware Trojan Diagnosis                 | 72                                  |

|----------|-------------------|-------------------------------------------------------------|-------------------------------------------------------------|-------------------------------------|

|          |                   | 4.3.3                                                       | Self-consistency Analysis via Optimal Subsegments Creation  | 74                                  |

|          | 4.4               | Hardw                                                       | vare Trojan Evaluation Results                              | 79                                  |

|          |                   | 4.4.1                                                       | Effectiveness of Hardware Trojan Attack Models              | 79                                  |

|          |                   | 4.4.2                                                       | HT variable-based HT Detection and Diagnosis Results        | 85                                  |

|          |                   | 4.4.3                                                       | Consistency-based HT Detection and Diagnosis Results        | 87                                  |

|          | 4.5               | Hardw                                                       | vare Trojan Related Work                                    | 90                                  |

|          | 4.6               | Summ                                                        | ary and Discussions of Hardware Trojans                     | 92                                  |

|          |                   | 4.6.1                                                       | Discussions on HT attacks                                   | 92                                  |

|          |                   | 4.6.2                                                       | Boundaries of the HT Detection Approach $\ . \ . \ . \ .$ . | 93                                  |

|          |                   | 4.6.3                                                       | Target of HT Detection                                      | 94                                  |

|          |                   |                                                             |                                                             |                                     |

| <b>5</b> | Har               | dware                                                       | Metering and Digital Rights Management                      | 96                                  |

| 5        | <b>Har</b><br>5.1 |                                                             | Metering and Digital Rights Management                      | <b>96</b><br>96                     |

| 5        |                   |                                                             |                                                             |                                     |

| 5        |                   | Hardw                                                       | vare Metering Using Physical GLC                            | 96                                  |

| 5        |                   | Hardw<br>5.1.1                                              | vare Metering Using Physical GLC                            | 96<br>96<br>97                      |

| 5        |                   | Hardw<br>5.1.1<br>5.1.2<br>5.1.3                            | vare Metering Using Physical GLC                            | 96<br>96<br>97<br>101               |

| 5        | 5.1               | Hardw<br>5.1.1<br>5.1.2<br>5.1.3                            | vare Metering Using Physical GLC                            | 96<br>96<br>97<br>101<br>104        |

| 5        | 5.1               | Hardw<br>5.1.1<br>5.1.2<br>5.1.3<br>IC Au                   | vare Metering Using Physical GLC                            | 96<br>96<br>97<br>101<br>104        |

| 5        | 5.1               | Hardw<br>5.1.1<br>5.1.2<br>5.1.3<br>IC Au<br>5.2.1          | vare Metering Using Physical GLC                            | 96<br>96<br>97<br>101<br>104        |

| 5        | 5.1               | Hardw<br>5.1.1<br>5.1.2<br>5.1.3<br>IC Au<br>5.2.1<br>5.2.2 | vare Metering Using Physical GLC                            | 96<br>96<br>97<br>101<br>104<br>104 |

|   |     | 5.3.1   | IC Metering                                               | 109 |

|---|-----|---------|-----------------------------------------------------------|-----|

|   |     | 5.3.2   | Coincidence Estimation                                    | 113 |

|   |     | 5.3.3   | IC Auditing                                               | 113 |

|   | 5.4 | Hardw   | vare Metering Related Work                                | 116 |

|   |     | 5.4.1   | Extrinsic IC Metering                                     | 117 |

|   |     | 5.4.2   | Intrinsic IC Metering                                     | 118 |

| 6 | Rer | note Iı | n-field Wireless Security Techniques                      | 119 |

|   | 6.1 | Wirele  | ess Security Challenges                                   | 119 |

|   | 6.2 | Energ   | y Hardware Trojans in Wireless Systems                    | 120 |

|   |     | 6.2.1   | Energy Hardware Trojan Overview                           | 120 |

|   |     | 6.2.2   | Energy Hardware Trojan Attacks                            | 122 |

|   |     | 6.2.3   | Energy Hardware Trojan Detection                          | 126 |

|   | 6.3 | Online  | e Security Attack and Defense                             | 131 |

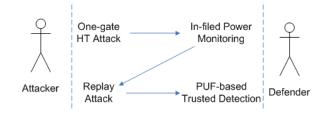

|   |     | 6.3.1   | Attack and Defense Models                                 | 132 |

|   |     | 6.3.2   | Online Detection by In-field Power Measurements           | 134 |

|   |     | 6.3.3   | Online Replay Attack                                      | 134 |

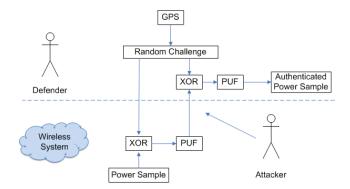

|   |     | 6.3.4   | Trusted Detection Using Physically Unclonable Functions . | 135 |

|   | 6.4 | Wirele  | ess Security Experimental Results                         | 137 |

|   |     | 6.4.1   | Effectiveness of Energy Hardware Trojan Attack            | 137 |

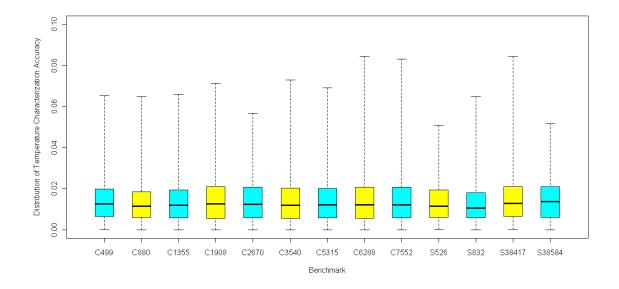

|   |     | 6.4.2   | Effectiveness of Temperature-aware Hardware Trojan De-    |     |

|   |     |         | tection                                                   | 138 |

|   |     | 6.4.3   | Effectiveness of PUF-based Online In-field Detection      | 140 |

| 7  | Concluding Remarks |  | • | • | • | • | • | • | • | • | • | • |  | • | • | • | • | • | • | • | • | • | • | • | 142 |

|----|--------------------|--|---|---|---|---|---|---|---|---|---|---|--|---|---|---|---|---|---|---|---|---|---|---|-----|

|    |                    |  |   |   |   |   |   |   |   |   |   |   |  |   |   |   |   |   |   |   |   |   |   |   |     |

| Re | eferences          |  |   |   |   |   |   |   |   |   |   |   |  |   |   |   |   |   |   |   |   |   |   |   | 144 |

# LIST OF FIGURES

| 1.1  | Major contributions and organizations of the dissertation                                                                                                                     | 6  |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

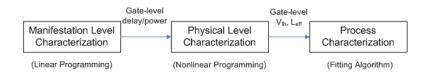

| 3.1  | Overall flow of our GLC scheme. We use a three-phase procedure (pre-processing, GLC, and post-processing).                                                                    | 17 |

| 3.2  | Flow of thermal conditioning for GLC. We increase the tempera-<br>tures of a subset of gates in the circuit to break the correlations in                                      |    |

|      | the system of linear equations.                                                                                                                                               | 19 |

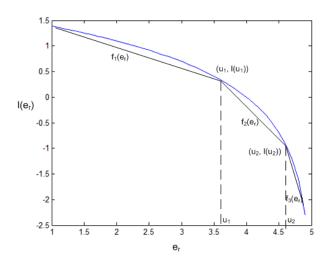

| 3.3  | An example of the likelihood function and the piecewise linear<br>approximation, where $l(e_r) = log(5 - e_r)$ , and two breakpoints $u_1$<br>and $u_2$ are being considered. | 23 |

| 3.4  | Example of uncharacterizable IC components using delay measure-                                                                                                               | 20 |

|      | ments                                                                                                                                                                         | 26 |

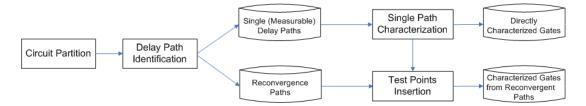

| 3.5  | Overall flow of gate-level delay characterization                                                                                                                             | 27 |

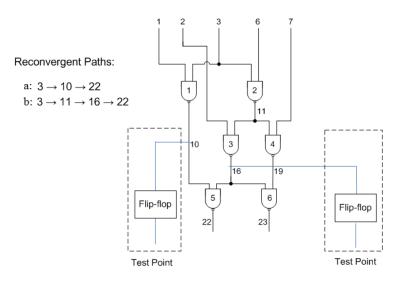

| 3.6  | Example of test points insertion for delay characterization                                                                                                                   | 29 |

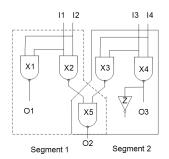

| 3.7  | Example of segmentation using input vector control                                                                                                                            | 35 |

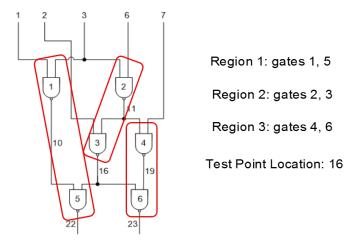

| 3.8  | Example of MFFC-based circuit partition for timing characteriza-                                                                                                              |    |

|      | tion                                                                                                                                                                          | 40 |

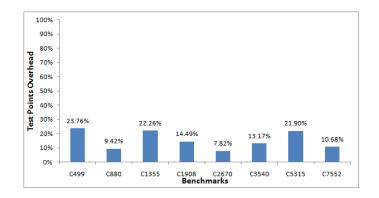

| 3.9  | Area overhead of the inserted test points                                                                                                                                     | 46 |

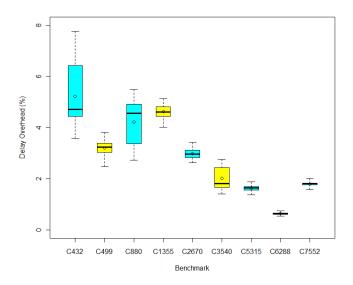

| 3.10 | Delay overhead under process variation                                                                                                                                        | 47 |

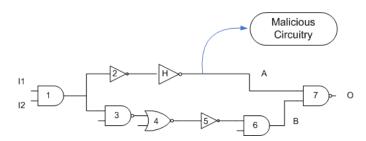

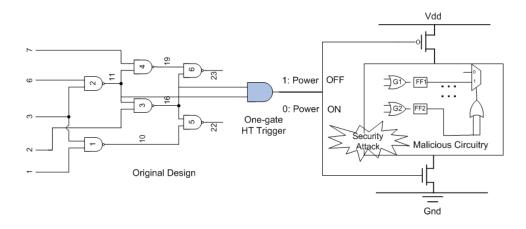

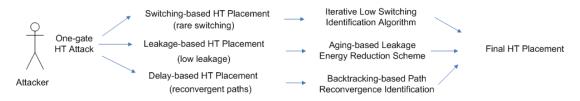

| 4.1  | Overall architecture of the one-gate HT attack model                                                                                                                          | 51 |

| 4.2  | Overall flow for HT creation and placement.                                                                                                                                   | 52 |

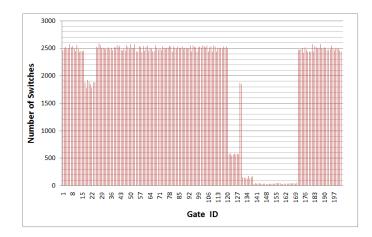

| 4.3 | Switching activities of all gates on ISCAS benchmark C499, under                                              |    |

|-----|---------------------------------------------------------------------------------------------------------------|----|

|     | the application of 5000 pairs of input vectors                                                                | 53 |

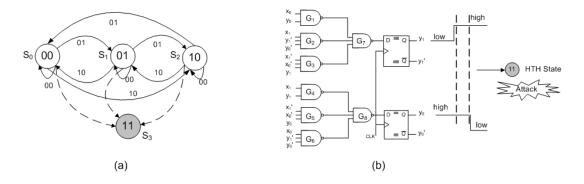

| 4.4 | Motivational example of the undetectable hardware Trojan horses:                                              |    |

|     | (a) finite state machine of a mod-3 up/down counter, which in-                                                |    |

|     | cludes 3 normal states (i.e., $S_0$ , $S_1$ , and $S_2$ ) and 1 redundant state                               |    |

|     | (i.e., $S_3$ ); and (b) demonstration of the HT state transition using                                        |    |

|     | device aging.                                                                                                 | 60 |

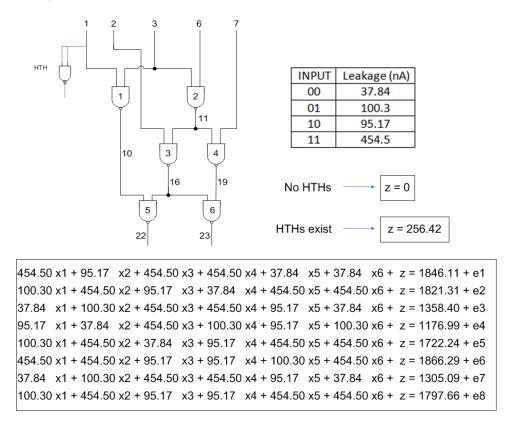

| 4.5 | Example of GLC-based HT detection scheme on benchmark C17.                                                    |    |

|     | The coefficients (nominal leakage power values) $[104]$ are shown in                                          |    |

|     | the lookup table. We add one extra HT variable $z$ to the system of                                           |    |

|     | measurement equations as the indicator of HTs. $e_i$ $(i = 1, 2,, 8)$                                         |    |

|     | represents the leakage power measurement errors. The solution of                                              |    |

|     | z is zero when no HTs are present, and it is a large value (256.4)                                            |    |

|     | in the case where HTs exist                                                                                   | 64 |

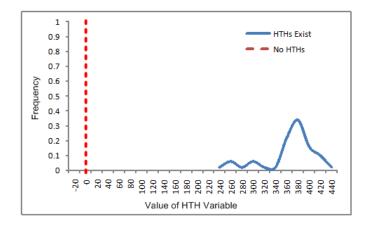

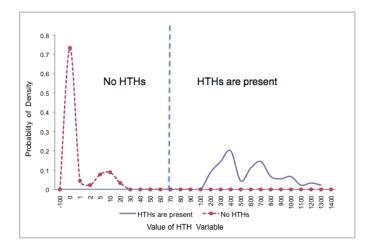

| 4.6 | Probability density function of HT variable for 500 runs of HT $$                                             |    |

|     | detection on benchmark C17. For all the 500 runs, the value of                                                |    |

|     | the HT variable is 0 in the case where there are no HTs , and it is                                           |    |

|     | a large value between 220 and 440 when HTs are present                                                        | 65 |

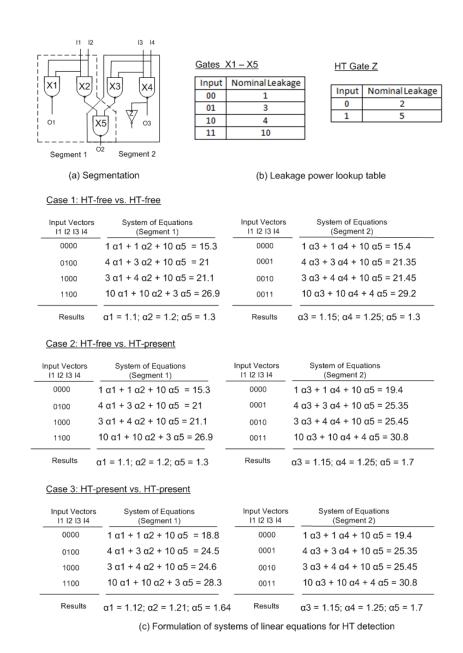

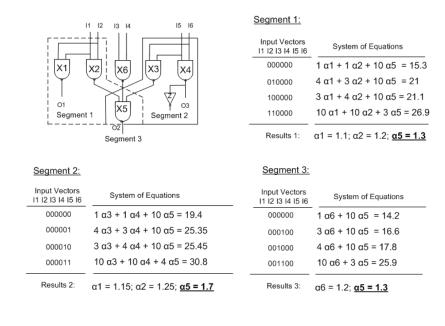

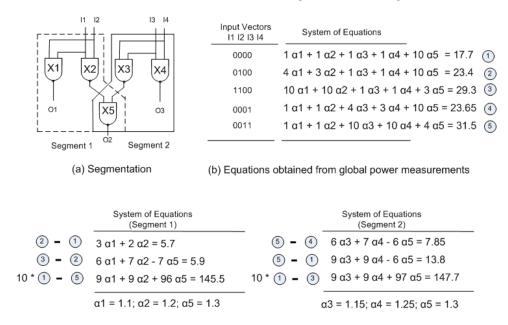

| 4.7 | Example of the segmentation-based HT detection approach: (a)                                                  |    |

|     | shows that a circuit with five gates is segmented into two segments,                                          |    |

|     | and gate $X5$ is the overlapping gate of the two segments; (b) shows                                          |    |

|     | the nominal leakage power values for all the gates in the circuit;                                            |    |

|     | and (c) demonstrates the formulation of systems of linear equations $\left( {\left( {c} \right)_{i}} \right)$ |    |

|     | and their solutions in three cases regarding whether a HT is present                                          |    |

|     | in each segment. The discrepancy in the results of the overlapping                                            |    |

|     |                                                                                                               |    |

| 4.8  | Example of consistency-based HT diagnosis. We demonstrate the                 |     |

|------|-------------------------------------------------------------------------------|-----|

|      | gate characterization in three segments with overlapping gates.               |     |

|      | The consistency in Segment 1 and Segment 3 exposes the possible               |     |

|      | HTs in Segment 2                                                              | 71  |

| 4.9  | Example of the variable elimination technique using linear trans-             |     |

|      | formation.                                                                    | 77  |

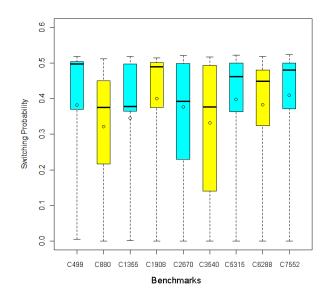

| 4.10 | Simulation results of switching activities of all gates on ISCAS'85           |     |

|      | benchmarks                                                                    | 83  |

| 4.11 | PDF of the HT variable in HT detection, integrated with all the               |     |

|      | ISCAS and ITC benchmarks in Table 4.5. In the case when no HTs                |     |

|      | exist, the HT variable has a small value from 0 to 11.2. When a               |     |

|      | single HT gate is present, the HT variable ranges from $151$ to $1214$ .      |     |

|      | There is a large enough gap between the two cases to enable us to             |     |

|      | draw a decision line at around 70 to distinguish the two cases                | 85  |

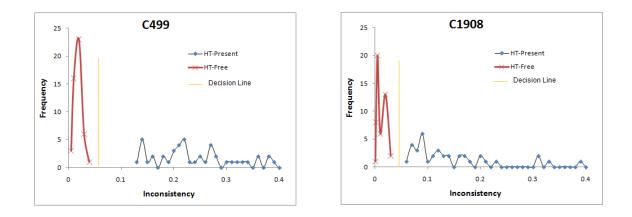

| 4.12 | Distribution of the inconsistency values in the HT-present and HT-            |     |

|      | free cases.                                                                   | 89  |

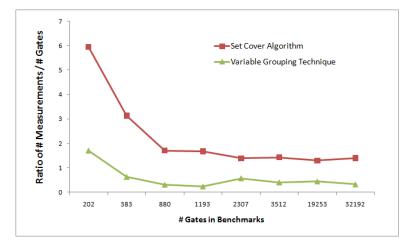

| 4.13 | Comparison of the numbers of measurements in the consistency-                 |     |

|      | based hardware Trojan detection.                                              | 89  |

| 4.14 | Simulation results for the consistency-based HT diagnosis. $\ . \ . \ .$      | 90  |

| 5.1  | Flow of IC metering.                                                          | 98  |

| 5.2  | Probability that a gate has coincidence with other gates in terms             |     |

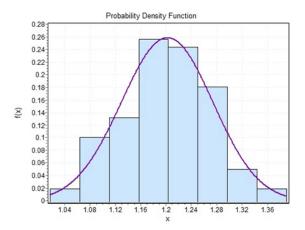

|      | of $L_{eff}$ (benchmark C432 with 160 gates; mean value of $L_{eff}$ is 1.2). | .03 |

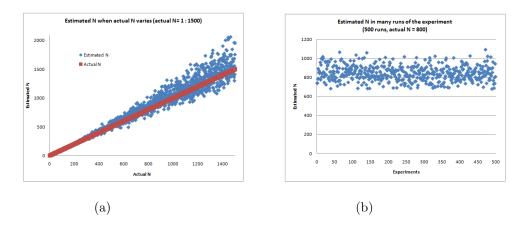

| 5.3  | Validation of our IC auditing scheme: (a) on known sets of chips; ${\cal N}$  |     |

|      | varies from 1 to 1500; (b) on 500 runs of the analytical simulation;          |     |

|      | N is fixed to 800                                                             | .09 |

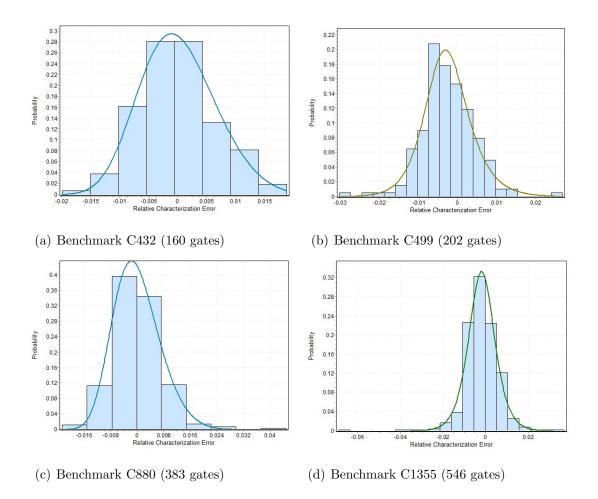

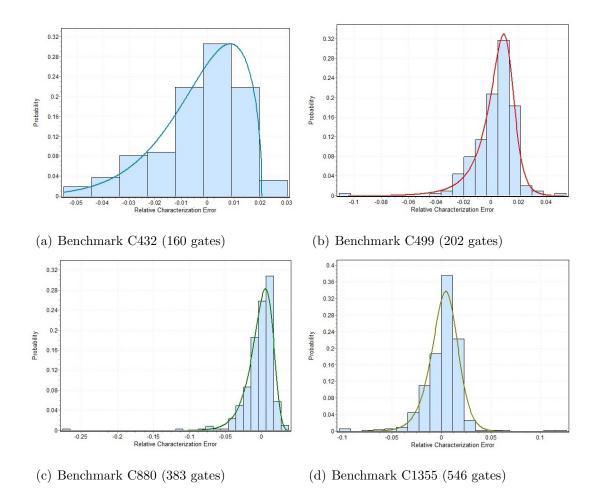

| 5.4 | Accuracy of $L_{eff}$ characterization on a set of ISCAS benchmarks.                                                                                                                                                                                                                                                    | 110 |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 5.5 | Accuracy of $V_{th}$ characterization on a set of ISCAS benchmarks .                                                                                                                                                                                                                                                    | 111 |

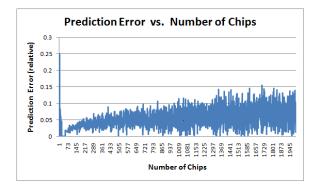

| 5.6 | IC auditing results: prediction error vs. total number of chips<br>(the number of samples is fixed to 20; the sample sizes are fixed<br>to 20; the total number of chips varies from 1 to 2000; and no<br>post-processing of the prediction results is performed).                                                      | 114 |

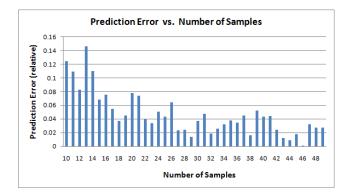

| 5.7 | IC auditing results: prediction error vs. number of samples (the number of chips is 1600; the number of samples varies from 10 to 50; and the sample sizes are fixed to 20 chips.)                                                                                                                                      |     |

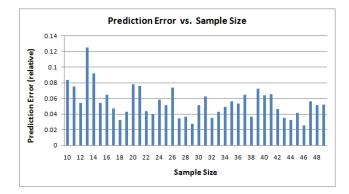

| 5.8 | IC auditing results: prediction error vs. sample sizes (the number of chips is 1600; the number of samples is fixed to 20; and the sample sizes vary from 10 to 50.)                                                                                                                                                    | 117 |

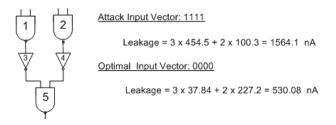

| 6.1 | Leakage current of an inverter and a NAND gate under different input vectors [104].                                                                                                                                                                                                                                     | 123 |

| 6.2 | Example of energy attack via input vector manipulation. The energy consumption caused by the attack input vector is 2.96 times                                                                                                                                                                                          |     |

|     | compared to the optimal input vector.                                                                                                                                                                                                                                                                                   | 123 |

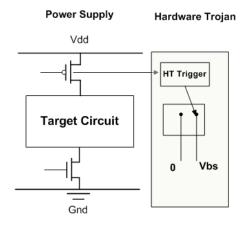

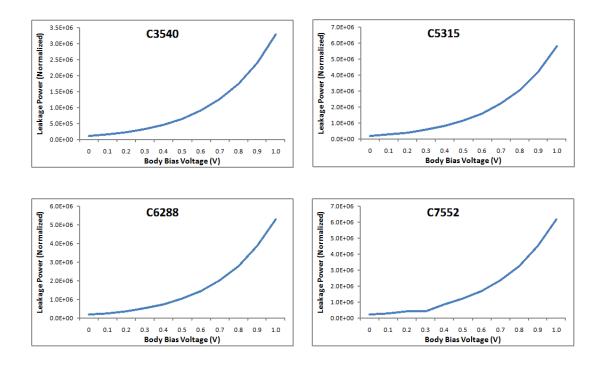

| 6.3 | Example of energy attack using forward body biasing                                                                                                                                                                                                                                                                     | 124 |

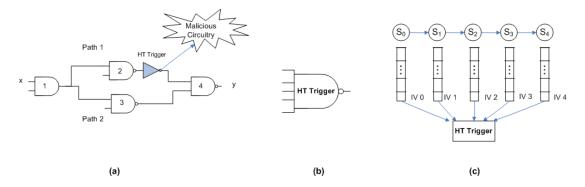

| 6.4 | Example of hiding the HT triggers: (a) a HT trigger embedded<br>in the reconvergent paths where delay is non-observable; (b) a<br>rarely switching HT trigger driven by multiple inputs; and (c)<br>a HT trigger activated by a 5-state finite state machine, which<br>reduces the activation probability exponentially | 125 |

| 6.5 | Principal component analysis (PCA) model to define the hardware                                                                                                                                                                                                                                                         |     |

|     | Trojan indicator.                                                                                                                                                                                                                                                                                                       | 130 |

| 6.6  | Online attack and defense model                                    | 132 |

|------|--------------------------------------------------------------------|-----|

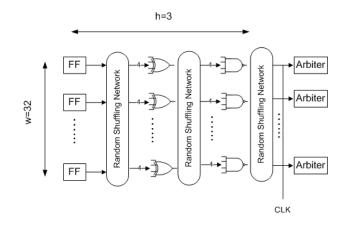

| 6.7  | PUF architecture [61].                                             | 136 |

| 6.8  | PUF-based trusted HT detection                                     | 137 |

| 6.9  | Leakage power increase due to forward ABB attack                   | 138 |

| 6.10 | Accuracy of temperature characterization                           | 139 |

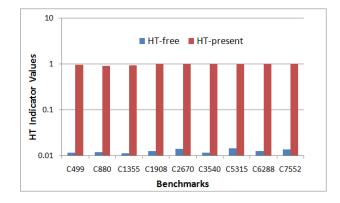

| 6.11 | Energy HT detection results: HT indicator values in HT-free and    |     |

|      | HT-present cases.                                                  | 140 |

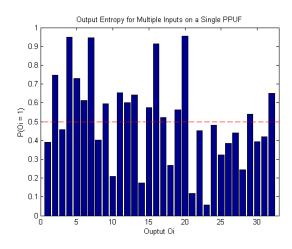

| 6.12 | The probability of output bit $O_i$ being 1 in the PUF (w=32, h=3) |     |

|      | following the architecture in Figure 6.7.                          | 141 |

## LIST OF TABLES

| Accuracy of gate-level power characterization.                                                                                         | 42                                                                                                                                                                                                                                                                                      |

|----------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Results of delay characterization with and without test points. The                                                                    |                                                                                                                                                                                                                                                                                         |

| number of characterizable gates without test points is no more                                                                         |                                                                                                                                                                                                                                                                                         |

| than $60\%$ of all the gates. However, with inserted test points,                                                                      |                                                                                                                                                                                                                                                                                         |

| we can characterize $100\%$ of the gates accurately in all the tested                                                                  |                                                                                                                                                                                                                                                                                         |

| benchmark circuits.                                                                                                                    | 44                                                                                                                                                                                                                                                                                      |

| Overhead of test point insertion in terms of the number of test                                                                        |                                                                                                                                                                                                                                                                                         |

| points (i.e., area overhead) and the number of measured paths                                                                          |                                                                                                                                                                                                                                                                                         |

| (i.e., cost of test) $\ldots \ldots \ldots$ | 46                                                                                                                                                                                                                                                                                      |

|                                                                                                                                        |                                                                                                                                                                                                                                                                                         |

|                                                                                                                                        | 20                                                                                                                                                                                                                                                                                      |

|                                                                                                                                        | 80                                                                                                                                                                                                                                                                                      |

|                                                                                                                                        |                                                                                                                                                                                                                                                                                         |

| (Benchmark C7552). $\ldots$                                                                                                            | 81                                                                                                                                                                                                                                                                                      |

| Switching probability of the HT gate using the maximum indepen-                                                                        |                                                                                                                                                                                                                                                                                         |

| dent set approach. $\ldots$                           | 83                                                                                                                                                                                                                                                                                      |

| Simulation results regarding uncharacterizable gates due to recon-                                                                     |                                                                                                                                                                                                                                                                                         |

| vergences. The high percentage of uncharacterizable gates in each                                                                      |                                                                                                                                                                                                                                                                                         |

| design indicates that there is a large number of candidate locations                                                                   |                                                                                                                                                                                                                                                                                         |

| for embedding the non-detectable one-gate HT trigger. $\ldots$ .                                                                       | 84                                                                                                                                                                                                                                                                                      |

| HT Detection and Diagnosis on ISCAS and ITC Benchmarks                                                                                 | 86                                                                                                                                                                                                                                                                                      |

|                                                                                                                                        | Results of delay characterization with and without test points. The number of characterizable gates without test points is no more than 60% of all the gates. However, with inserted test points, we can characterize 100% of the gates accurately in all the tested benchmark circuits |

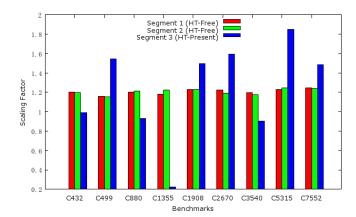

| 4.6 | HT detection results using consistency and self consistency-based   |     |

|-----|---------------------------------------------------------------------|-----|

|     | GLC: the values in the "HT-Free" and "HT-Present" columns rep-      |     |

|     | resent the average discrepancy of the overlapping gates in terms of |     |

|     | their scaling factors.                                              | 88  |

|     |                                                                     |     |

| 5.1 | Accuracy of coincidence estimation. "FP" and "FN" stand for         |     |

|     | "False Positives" and "False Negatives", respectively               | 112 |

| 5.2 | IC auditing on large numbers of ICs.                                | 115 |

#### ACKNOWLEDGMENTS

First and foremost, I would like to thank my advisor and doctoral committee chair Prof. Miodrag Potkonjak for his valuable guidance and continuous help ever since I joined the UCLA computer science PhD program in Fall 2008. He not only guided me through the world of academic research and taught me how to become a good researcher, but also offered me great insights and valuable advices that will benefit my future career and life.

I am very grateful to my doctoral committee members, Prof. Milos Ercegovac, Prof. Majid Sarrafzadeh, and Prof. Hongquan Xu, for their valuable comments on my prospectus, dissertation and the final defense. I benefited a lot from their insights while improving this work.

Many thanks to the professors in the UCLA Computer Science Department: Prof. Jason Cong, Prof. Songwu Lu, and Prof. Y.C. Tay (visiting professor), who taught me not only solid knowledge in computer science, but also how to solve challenging research problems and accomplish successful research projects.

Also, many thanks to the researchers at Adobe Research: Vishy Swaminathan, Saayan Mitra, and Tom Jacobs, who offered me great opportunities to gain valuable industrial research experiences through both the internship and the university collaboration program at Adobe.

Furthermore, I would like to thank my colleagues and collaborators: Saro Meguerdichian, Jason Zheng, James Wendt, Jong Hoon Ahnn, Nathaniel Conos, Vishwa Goudar, Teng Xu, Eun-Sook Sung, Prof. Farinaz Koushanfar, Prof. Ani Nahapetian, and Kai Li, who worked together with me in several research projects and offered me great help in research, experiments, and paper writing. Some chapters of this dissertation are based on my publications co-authored with them and my advisor Prof. Miodrag Potkonjak. For example, a part of Chapter 3 is based on Publications P1-P2, P5, P9, P11, P13, and P16; a part of Chapter 4 is based on Publications P1-P2, P5-P6, P11-P13, and P16-P17; a part of Chapter 5 is based on Publications P3 and P7-P8; and a part of Chapter 6 is based on Publications P4, P10, and P15. In particular, Prof. Farinaz Koushanfar and Kai Li provided experimental platforms, data, and paper writing assistance to support a part of the work in Chapters 3.3, 3.4, 4.1, and 5; Prof. Ani Nahapetian provided experiments and paper writing assistance to support a part of the work in Chapters 3.2, 4.2, and 6.4; and my advisor Prof. Miodrag Potkonjak oversaw all my research projects and provided me with great help in all aspects of this dissertation.

Finally, special thanks to my wife, my son, my parents, and all my other family members who gave me great support, patience, and love during my PhD study. Without their support, I could not have finished this work.

#### Vita

| 2000-2004 | B.E. (Computer Science)                                                             |

|-----------|-------------------------------------------------------------------------------------|

|           | Yanshan University, China                                                           |

| 2004-2008 | Graduate Study / Research Assistant (Computer Science)<br>Beihang University, China |

| 2008–2013 | M.S. (Computer Science)                                                             |

|           | University of California, Los Angeles, USA                                          |

#### PUBLICATIONS

P1. S. Wei, S. Meguerdichian, M. Potkonjak, Gate-level Characterization: Foundations and Hardware Security Applications, Design Automation Conference (DAC), pp. 222-227, 2010.

P2. S. Wei, M. Potkonjak, Scalable Segmentation-based Malicious Circuitry Detection and Diagnosis, International Conference on Computer-Aided Design (IC-CAD), pp. 483-486, 2010.

P3. S. Wei, M. Potkonjak, Integrated Circuit Security Techniques Using Variable Supply Voltage, Design Automation Conference (DAC), 248-253, 2011.

P4. M. Potkonjak, S. Meguerdichian, A. Nahapetian, S. Wei, Differential Pub-

lic Physically Unclonable Functions: Architecture and Applications, Design Automation Conference (DAC), pp. 242-247, 2011.

P5. S. Wei, S. Meguerdichian, M. Potkonjak, Malicious Circuitry Detection Using Thermal Conditioning, IEEE Transactions on Information Forensics and Security, Vol. 6, No. 3, pp. 1136-1145, 2011.

P6. S. Wei, M. Potkonjak, Scalable Consistency-based Hardware Trojan Detection and Diagnosis, International Conference on Network and System Security (NSS), pp. 176-183, 2011.

P7. S. Wei, F. Koushanfar, M. Potkonjak, Integrated Circuit Digital Rights Management Techniques Using Physical Level Characterization, ACM workshop on Digital rights management (DRM), pp. 3-14, 2011.

P8. S. Wei, A. Nahapetian, M. Potkonjak, Robust Passive Hardware Metering, International Conference on Computer-Aided Design (ICCAD), pp. 802-809, 2011.

P9. S. Wei, A. Nahapetian, M. Nelson, F. Koushanfar, M. Potkonjak, Gate Characterization Using Singular Value Decomposition: Foundations and Applications, IEEE Transactions on Information Forensics and Security, Vol. 7, No. 2, pp. 765-773, 2012.

P10. S. Wei, M. Potkonjak, Wireless Security Techniques for Coordinated Manufacturing and On-line Hardware Trojan Detection, ACM conference on Security and Privacy in Wireless and Mobile Networks (WiSec), pp. 161-172, 2012.

P11. S. Wei, M. Potkonjak, Scalable Hardware Trojan Diagnosis, IEEE Transactions on Very Large Scale Integration (VLSI) Systems, Vol. 20, No. 6, pp. 1049-1057, 2012.

P12. S. Wei, K. Li, F. Koushanfar, M. Potkonjak, Hardware Trojan Horse Benchmark via Optimal Creation and Placement of Malicious Circuitry, Design Automation Conference (DAC), pp. 90-95, 2012.

P13. S. Wei, K. Li, F. Koushanfar, M. Potkonjak, Provably Complete Hardware Trojan Detection Using Test Point Insertion, International Conference on Computer-Aided Design (ICCAD), pp. 569-576, 2012.

P14. S. Wei, J. Zheng, M. Potkonjak, Low Power FPGA Design Using Post-Silicon Device Aging (Abstract Only), International Symposium on Field Programmable Gate Arrays (FPGA), pp. 277, 2013.

P15. S. Wei, J. Ahnn, M. Potkonjak, Energy Attacks and Defense Techniques for Wireless Systems, ACM Conference on Security and Privacy in Wireless and Mobile Networks (WiSec), pp. 185-194, 2013.

P16. S. Wei, M. Potkonjak, Malicious Circuitry Detection Using Fast Timing Characterization via Test Points, IEEE International Symposium on Hardware-Oriented Security and Trust (HOST), pp. 113-118, 2013. P17. S. Wei, M. Potkonjak, The Undetectable and Unprovable Hardware Trojan Horse, Design Automation Conference (DAC), Article No. 144, 2013.

# CHAPTER 1

## Introduction

#### 1.1 Motivation

Integrated Circuits (ICs) are fundamental building blocks of virtually all electronic equipments that are widely used today. The cost, performance, and reliability of ICs have become essential design objectives in the modern IC industry. In particular, there are two trends that dominate and play important roles in the IC design and manufacturing.

Firstly, from the perspective of semiconductor technologies, as the scaling of high-performance ICs moves to deep-submicron feature sizes, a higher degree of semiconductor integration provides ever increasing performance. However, the performance gain comes with new challenges such as increased leakage energy, increased substrate noise, profound and intrinsic process variation (PV), and increased susceptibility to environmental (e.g., thermal) and operational (e.g., supply voltage) variations. Among them, PV has emerged as the most limiting factor that essentially redefines the IC synthesis and analysis flow. For example, it has been reported that PV results in up to 20X variations in power consumption and around 30% in timing [14]. Consequently, PV could not only completely compromise the existing IC optimization efforts, it also makes the ICs more vulnerable to even ultra-small variations, due to unintentional defects, unpredictable external factors (e.g., environments), or malicious attacks (e.g., hardware Trojans). As PV has transitioned the domain of IC design and analysis from deterministic to probabilistic, it becomes rather important to bring it back to the deterministic domain, in order to accurately analyze the ICs for design optimization, quality control, and security.

Secondly, from the perspective of business models, IC outsourcing has been widely adopted by most of the IC design companies in order to reduce the manufacturing cost and thus increase their revenue. However, IC outsourcing induces potential security concerns to the manufactured IC, due to the fact that an untrusted foundry has complete access to the hardware during the manufacturing process. In particular, the security concerns include but not limited to the following: (1) The untrusted foundry may embed hardware Trojans (HTs) in the circuit, which are unwanted and malicious components that would make the IC malfunction or extract confidential information from the application system; and (2) IC counterfeiting, in which an untrusted foundry is capable of manufacturing additional unauthorized copies of ICs to obtain extra profits.

In summary, in the modern and pending IC industry, it is essential to be able to accurately characterize and analyze the manufactured IC in a deterministic manner, from which both the design optimization mechanism and security primitives can benefit. In this dissertation, we focus on the security aspect of the problem and develop a set of consistency-based techniques to characterize and analyze the target ICs.

#### 1.2 Challenges

The task of characterizing an IC in an accurate and deterministic manner is challenging due to the following reasons. First, process variation causes the key IC

properties to vary from their nominal design specifications in a random and unpredictable manner. It is difficult for the characterization methods to determine the IC properties after manufacturing based on the specification. Second, even if one can measure the IC properties precisely, the characterized properties, such as delay and power, are subject to change due to environmental factors (e.g., temperatures) or the nature of the silicon (e.g., device aging). The potential variations do not only increase the complexity of the characterization approach by requiring it to execute repeatedly, they also complicate the corresponding procedure of analysis by mixing various sources of variations. Third, with the rapid growth of transistor scaling, modern ICs often contain huge numbers of transistors, in the magnitude of millions or even more. The scale of the circuit size, in terms of the transistor count, challenges the scalability of the characterization and analysis techniques. Finally, from the perspective of attackers, they tend to minimize the exposure of the attacks while maximizing the damage, which adds another layer of difficulty for the characterization approach in addition to the naturally existed variations.

#### **1.3 Design Principles**

In order to address the challenges, we develop a set of consistency-based IC characterization and analysis techniques. Our intuition is that the unexpected component would pose additional variations in the observable IC properties. Even though the variations can be hidden under process variation and become indistinguishable, we observe an important phenomenon that the behavior of the unexpected components would exhibit inconsistent pattern compared to the normal IC components, due to the fact that the controllability over the unexpected components is different from that over the normal gates. In particular, if we partition the IC into several small segments, an unexpected component in any of the segments would cause the shared component of the segments to have inconsistent properties, making it possible to be detected via consistency analysis.

Following this important observation, our design principle is to characterize the gate-level IC properties and conduct consistency-based statistical analysis to identify abnormal IC behavior and patterns. In order to conduct consistency analysis, our initial step is to partition the large IC into a number of small and overlapping segments, where we characterize the gate-level IC properties using global power or delay measurements. Then, we find representative components that are shared by various groups of the segments and analyze their properties in terms of consistency. An inconsistent pattern across segments indicates that there exist either unexpected or malicious components in the target IC.

#### 1.4 Contributions and Organizations

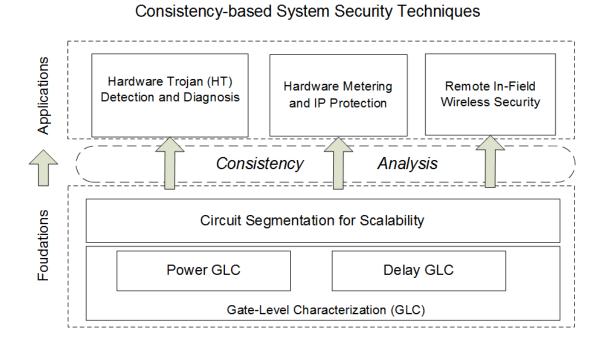

Figure 1.1 summarizes the major contributions of the dissertation. We develop a consistency analysis approach that is based on the accurate characterization of gate-level properties. Based on the characterization results, we demonstrate three system security applications, including hardware Trojan detection, hardware metering and digital rights management, and remote in-field wireless security techniques. In particular, we have the following detailed contributions in each category:

- A systematic consistency analysis approach based on efficient and accurate gate-level characterization using non-intrusive delay and power measurements (Chapter 3):

- Characterization of gate-level power properties using thermal condi-

tioning and linear programming (Chapter 3.2); and

- Characterization of gate-level delay properties using test point insertion (Chapter 3.3);

- A set of circuit partition and cost reduction techniques to ensure that the proposed GLC and consistency analysis approaches are scalable to large industrial designs (Chapters 3.4):

- A circuit segmentation approach by selectively freezing a subset of the inputs and varying the others (Chapter 3.4.1);

- A region-based circuit partition method to further reduce the measurement cost in delay characterization (Chapter 3.4.2).

- The research and demonstration of a group of system security applications that are based on the GLC and the consistency analysis (Chapters 4–6):

- A complete set of hardware Trojan attack, detection, and defense models and methods using consistency-based analysis (Chapter 4);

- An IC metering and auditing approach using physical GLC and statistical analysis (Chapter 5); and

- A set of wireless security techniques that detect and diagnose hardware

Trojans in remote in-field wireless systems (Chapter 6).

Figure 1.1: Major contributions and organizations of the dissertation.

#### 6

# CHAPTER 2

## **Background and Preliminaries**

In this chapter, we introduce the system models that we employ in the discussion of the dissertation, including the power/energy models, delay model, process variation model, and IC aging model. We regard these models as both the principles that lead to our design methodologies and the evaluation criteria that justify our research findings.

#### 2.1 Power Models

There are typically two possible sources of power dissipation on an IC. One is from gate switching (also termed switching power or dynamic power), where the ICs dissipate power by charging the load capacitances of wires and gates. The other source is static power (also termed leakage power), where the gates dissipate power due to the leakage current even if they do not switch.

Equation (2.1) is the gate-level leakage power model [59], where W is width of the transistor in the driving stage, L is the channel length,  $V_{th}$  is the threshold voltage,  $V_{dd}$  is the supply voltage, n is the subthreshold slope,  $\mu$  is the mobility,  $C_{ox}$  is the oxide capacitance, k is the Boltzmann constant, T is the absolute temperature, q is the magnitude of charge on an electron, and  $\sigma$  is the drain induced barrier lowering (DIBL) factor.

$$P_{leakage} = 2 \cdot n \cdot \mu \cdot C_{ox} \cdot \frac{W}{L} \cdot (\frac{kT}{q})^2 \cdot V_{dd} \cdot e^{\frac{\sigma \cdot V_{dd} - V_{th}}{n \cdot (kT/q)}}$$

(2.1)

Also, we note that the leakage power has a non-linear (exponential) relation with the temperature T, which provides us a way to vary the leakage power by changing the temperature of the circuit. In particular, if we apply a set of primary input vectors to the circuit that switch a set of gates, the gates can be heated up, and the heat will be transferred to other gates on the circuit, which causes the temperatures on the circuit to vary over time. In this way, we can condition the temperatures on the circuit and utilize the exponential relation between temperature and leakage power.

The gate-level switching power model [59] is described by Equation (2.2), where the switching power is dependent on the switching probability per unit of time  $\alpha$ , the load capacitance  $C_L$ , the transistor width W, the channel length L, and the supply voltage  $V_{dd}$ :

$$P_{switching} = \alpha \cdot C_L \cdot W \cdot L \cdot V_{dd}^2 \tag{2.2}$$

### 2.2 Delay Model

The delay of a single logic gate can be expressed as

$$d = gh + p \tag{2.3}$$

where g and h are logical effort and electrical effort, respectively; and p is parasitic delay. In particular, We use the delay model in [59] that relates the gate delay to its sizing and operating voltages:

$$Delay = \frac{k_{tp} \cdot k_{fit} \cdot L^2}{2 \cdot n \cdot \mu \cdot \phi_t^2} \cdot \frac{V_{dd}}{(ln(e^{\frac{(1+\sigma)V_{dd}-V_{th}}{2 \cdot n \cdot \phi_t}} + 1))^2} \cdot \frac{\gamma_i \cdot W_i + W_{i+1}}{W_i}, \qquad (2.4)$$

where subscripts i and i+1 represent the driver and load gates, respectively;  $\gamma$  is the ratio of gate parasitic to input capacitance; and  $k_{tp}$  and  $k_{fit}$  are fitting parameters.

#### 2.3 Process Variation Model

Process variation (PV) during IC manufacturing causes IC key parameters to vary from their nominal design specifications. For example, PV may vary leakage power by up to 20X and frequency by 30% on a single wafer [14]. In particular, there are two physical level properties that are major sources of PV: threshold voltage ( $V_{th}$ ) and effective channel length ( $L_{eff}$ ). For example, the effective channel length of a manufactured gate can be expressed by Equation (2.5), where  $L_{nom}$  is the nominal design value of the effective channel length, and  $\Delta L$  is the variation caused by PV.

$$L_{eff} = L_{nom} + \Delta L \tag{2.5}$$

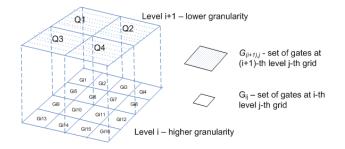

Several models have been proposed to capture the impact of PV [7][23][24], which formulate  $\Delta L$  as a random distribution or a combination of multiple distributions to represent the spatial correlations on a chip, as well as the inter-chip variations. In the discussion of this dissertation, we follow the quad-tree model presented by Cline et al. [24] for the variation of  $L_{eff}$  (i.e.,  $\Delta L$ ). In particular,  $\Delta L$  is distributed into multiple levels where there are different numbers of grids allocated at each level. The grids at each level are assigned variation values that follow a Gaussian distribution. Then, we can calculate the total  $\Delta L$  as the sum of variation values in each level of the grids to which the corresponding gate belongs. Equation (2.6) shows the total variation in the effective channel length of gate j, where  $\Delta L_{ij}$  is the variation in the *i*th level grid to which gate j belongs, and  $\mu_i$  and  $\sigma_i$  are the mean and variance of the Gaussian distribution at level i, respectively.

$$\Delta L_j = \sum_i \Delta L_{ij}, \quad where \quad \Delta L_{ij} \sim N(\mu_i, \sigma_i)$$

(2.6)

For  $V_{th}$ , we use the model presented by Asenov et al. [7], where the distribution of  $V_{th}$  is obtained by the simulation study of random dopants.  $V_{th}$  in this model is fit into a Gaussian distribution, where the parameters are determined by the dopant number and the dopant position.

#### 2.4 IC Aging Model

IC aging causes the threshold voltage of the transistors to increase and, consequently, the speed of the circuit to decrease. In particular, the threshold voltage shift caused by the negative bias temperature instability (NBTI) effect is a function of stress time, temperature, and applied gate voltage, as shown in the following equation [20]:

$$\Delta V_{th} = A \cdot exp(\beta V_G) \cdot exp(-E_{\alpha}/kT) \cdot t^{0.25}$$

(2.7)

where t is the stress time; T is the temperature;  $V_G$  is the applied gate voltage; A,  $\beta$  and k are constants; and  $E_{\alpha}$  is the measured activation energy of the NBTI process. We employ this aging model to quantify the threshold voltage increase of the gates that are in the stress mode.

### CHAPTER 3

### **Gate-level Characterization**

In this chapter, we discuss in details our approach of characterizing each gate of an IC in terms of its manifestational properties, such as delay and power. We show that the proposed characterization approach addresses the concerns caused by process variation and serves as the foundation of conducting consistency-based analysis for system security applications.

#### 3.1 GLC Overview

With the ever increasing trend of transistor scaling, process variation (PV) has emerged as the most limiting factor that essentially redefines IC synthesis and analysis flow. PV is the deviation of IC key parameters from nominal specifications. For example, it has been reported that the frequency of a chip can vary by up to 30% from its nominal design values [14]. For leakage current, the variations are much higher and may reach up to 20 times [14].

Gate-level characterization (GLC) is the process of characterizing each gate of an IC in terms of its properties, such as power and delay. Several research efforts [48][6][70] have proposed conceptually different non-destructive GLC techniques. However, none of them are capable of characterizing all the gates due to insufficient diversity of linear equations that correspond to power or delay measurements. We have developed a group of new GLC approaches for characterizing all the gates in a target circuit [88][89][90][92][96] [93]. To the best of our knowledge, this is the first report of a technique that guarantees a complete gate-level characterization.

#### 3.2 Gate-level Power Characterization

Our goal in gate-level power characterization is to characterize the power scaling factor of each gate, which is the deviation of the gate leakage power or switching power from the nominal specifications due to process variation.

#### 3.2.1 Objectives

We have the following two primary objectives in power GLC:

- Accuracy. The results of characterization must be accurate, i.e., the difference between the characterized scaling factors and their actual values is minimal. Since there exist measurement errors, we must filter out the noises of errors.

- Number of characterized gates. Our goal is to characterize all the gates in the target circuit. In most cases, this objective is challenging due to the fact that there are a large portion of gates in the circuit that are correlated and thus have extremely low individual observabilities.

#### 3.2.2 Power Measurements and Equations

We begin our power GLC approach by applying m different input vectors that are stored in flip-flops to the combinatorial logic and measure the total leakage power of the circuit for each of them. Next, we generate a system of m equations and formulate a linear program (LP). The objective function of the linear program is to minimize the sum of the absolute value (l1-norm) of measurement errors, as shown in Equation (3.1), where m is the number of measurements, and  $e_i$  is the error of the *i*-th measurement.

$$min \qquad \sum_{i=1}^{m} |e_i| \tag{3.1}$$

The system of linear equations (i.e., the constraints in the LP) can be formulated as the following:

$$K \cdot s = \tilde{p} + e \tag{3.2}$$

where  $K \in \mathbb{R}^{m \times n}$  is the nominal design values represented by a matrix of coefficients, which depend on gate types and their input vectors and can be found in a lookup table [104]; *m* is the number of measurements; *n* is the number of gates on the chip; *s*,  $\tilde{p}$ , and *e* are one-dimensional vectors representing the scaling factor of each gate, the measured power, and the unknown measurement error in each measurement, respectively. The format of (3.2) meets that of a linear constraint in a LP. Note that we abstract the impact of PV on leakage power (or switching power) using a scaling factor  $s_i$  for each gate *i* in the circuit. Our goal in GLC is to characterize the scaling factors of all gates by solving the LP. After obtaining the scaling factors, we can recover the manifestational properties due to PV from their nominal design values.

Note that the IC design specification may specify a range of nominal values (i.e., the K values) accounting for the process variation or other possible variations during the manufacturing process. In our GLC formulation, we consider this variation (i.e., the range of nominal values) by employing the scaling factor

s for each gate, which is exactly the set of variables we solve in the LP. However, our GLC formulation does require a constant nominal value for each type of gates under each combination of inputs, which appears as the coefficient matrix K of the linear equations (i.e., Equation (3.2)). In this case, the range of nominal values in the design specification cannot be used directly. Our solution to this problem is to use a representative value (e.g., the average) of the nominal range. Once we solve the GLC equations, the variation of the nominal range will be reflected in the scaling factor values.

## 3.2.3 Technical Issues in Power GLC

The structure of matrix K and thus the formulation of the LP are highly dependent on the selection of input vectors. In order to characterize the scaling factors accurately, one must minimize the dependencies amongst the variables in the system of equations. A simple way of achieving the goal is to create as many equations as possible. However, this technique has two strong negative ramifications:

- Large-Size LP. The number of gates is large in modern IC designs. Hence, the formulated LP may easily exceed the processing power of LP solvers.

- Correlations. Even if we are able to handle a large number of equations, ideally all the possible input vectors, we still cannot characterize the gates that are correlated in the system of linear equations. We define two types of correlations: (1) between gates that have the same ratio of coefficients in all the equations (collinearity correlation); and (2) between gates for which we are not able to obtain a sufficient number of independent equations due to the fact that the number of variables is larger than the number

of equations (insufficient controllability). We observe that the collinearity correlation often occurs when multiple gates are of the same type and have the same input signals. Also, the insufficient controllability correlation is a consequence of the IC structure where a subpart of the circuit has many gates but few intermediate inputs that control them.

The running times and coverage issues in the pertinent set of equations requires us to reduce the size of the LP and to break the correlations. We address the first issue by pre-processing the input vectors in such a way that we maximize the number of unique coefficients in front of each variable. Also, we address the second issue using correlation detection and thermal conditioning.

## 3.2.4 Power Characterization Overall Flow

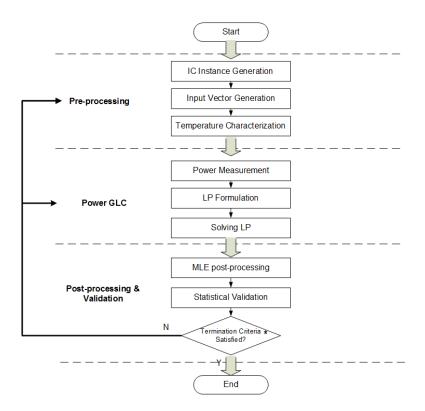

In order to achieve the objectives in GLC and address the technical issues, we develop a power GLC approach that includes three phases, namely pre-processing, GLC, and post-processing, as shown in Figure 3.1. In the pre-processing phase, we first generate the IC instances that take into account the impact of PV. We combine the PV model for individual devices presented by Asenov et al. [7] with the spatial correlation model proposed by Cline et al. [24]. Next, we generate a set of input vectors that can be applied to obtain various leakage voltage values. The goal during input vector generation is to ensure that the maximum number of gates have all their possible input signal combinations, so that the possibility of linear dependencies in the system of linear equations is minimized. Also, we selectively heat up the circuit by switching certain gates on the circuit in such a way that all the remaining linear dependencies among the linear equations can be resolved. After pre-processing, we begin the process of GLC, in which we apply the set of input vectors and measure the total leakage power for each of

them. For each measurement value, we formulate a linear equation by adding the leakage power values of all the gates with the measurement error. Next, we solve the system of linear equations using a LP solver and obtain results for each PV scaling factor.

We repeat the GLC procedure multiple times and conduct post-processing using the obtained results. We apply maximum likelihood estimation (MLE) that selects the most likely scaling factor for each gate as our eventual results of GLC. Finally, we employ statistical methods to validate our prediction results. For this purpose we use resampling, where 60% of the GLC results are used for the training set and 40% for the testing set. The entire GLC procedure terminates when the validated GLC accuracy is within a user predefined threshold value.

## 3.2.5 Correlation Detection

Since the correlated variables in the system of linear equations cannot be solved by the LP solver, we detect them so that we can either break the correlations or, in the worst case, combine those variables to reduce the size of the LP. We have developed two techniques to detect the collinearity correlations. The first one is straightforward: we check the coefficients for all pairs of variables using exhaustive enumeration. If there exists a pair of gates for which the ratio of coefficients are identical over all the equations, the pair of gates is correlated. The second technique employs our LP formulation itself. We add one more constraint in the LP formulation that sets one of the potentially correlated gates to a very large value; if correlations exist, the LP solution would show that several other variables become very small. Therefore, these gates are correlated with the gate whose value has been modified by the extra constraint.

For the insufficient controllability correlations, the detection is not trivial, as

\* The iterative process terminates when the validated GLC accuracy is within a predefined threshold value

Figure 3.1: Overall flow of our GLC scheme. We use a three-phase procedure (pre-processing, GLC, and post-processing).

the number of subparts of the circuit that can possibly have correlations is large. We solve this problem by manipulating the objective function. In particular, we change the objective function to maximizing only one of the variables. If a subset of the gates in the circuit have the insufficient controllability correlation, the other variables would become very small.

## 3.2.6 Correlation Elimination

In this section, we discuss our thermal conditioning approach to GLC that resolves the correlation issues in the system of linear equations.

## 3.2.6.1 Thermal Conditioning Overview

As discussed in Chapter 3.2.3, there are two technical issues that we must resolve in GLC. Firstly, if the target circuit is large, it requires a large number of measurements as well as a very large LP that is difficult to solve. Secondly, we must break the correlations in the system of linear equations in order to characterize all the gates on the circuit. The only way to break these correlations is to find alternatives to supplement input vector variation for changing the coefficients of the scaling factor variables.

We solve both technical issues using thermal conditioning, where we heat up a subset of gates to change their coefficients in the system of linear equations. Our intuition is based on the fact that gate-level leakage power depends on the temperature of the gate (as shown in Equation (2.1)) and that IC heat-up is much faster than the cooling process (as discussed in [62]). Therefore, thermal conditioning provides us with an additional means of controlling a subset of gates in the circuit and thus enables us to change the coefficients of the scaling factors in the system of linear equations. By using thermal conditioning, we can obtain sufficient numbers of equations regardless of the number of input vectors that can be applied. Furthermore, we are able to break the collinearity correlation, since we can obtain different coefficients even without changing the input vectors.

We show our flow of thermal conditioning in Figure 3.2. We first conduct correlation detection using the techniques discussed in Chapter 3.2.5 to determine the subset of gates that are either subject to collinearity correlation or insufficient controllability. Next, we perform thermal conditioning on the set of correlated gates by applying a set of input vectors that cause the gates to switch. The heat generated while switching increases the temperatures of the gates. In order to calculate the new coefficients of the scaling factors in the system of linear equations, we select a subset of gates in the circuit as the representative gates, which can provide us with the temperature profile of the entire circuit (as shown in Algorithm 1). We characterize the new temperatures of the subset of gates by measuring leakage power, switching power, and delay and by solving a system of non-linear equations following the power and delay models discussed in Chapter 2. We utilize the characterized temperatures of the gates as representative temperatures and determine the temperature of each gate in the circuit under the consideration of heat transfer. Finally, we apply the new coefficients to GLC using leakage power measurements and characterize the scaling factor of each gate.

Figure 3.2: Flow of thermal conditioning for GLC. We increase the temperatures of a subset of gates in the circuit to break the correlations in the system of linear equations.

## 3.2.6.2 Thermal Conditioning Using Gate Switching

We conduct input vector control to increase by different amounts the temperatures of the subset of gates that are subject to correlations in the system of linear equations. In particular, we select a set of input vectors in such a way that they can switch the set of correlated gates identified by correlation detection in different ways. The heat generated during switching increases the temperatures of the gates and thus change their coefficients in the system of linear equations. The key observation is that the time needed for gate switching is very fast (on the order of nanoseconds), while the cooling process is much slower (on the order of seconds) [62]. Therefore, we can increase the temperatures of the subset of gates rapidly and assume that the new temperatures we obtain stay constant for seconds until we completely characterize all gates in GLC.

# 3.2.6.3 Temperature Characterization Using Leakage Power, Switching Power and Delay Measurements

In order to calculate the new coefficients in the system of linear equations after thermal conditioning, we must determine the temperature profile of all the gates in the circuit. There are three variables in the gate-level properties, as shown in Equations (2.1), (2.2), and (2.4), temperature (T), effective channel length (L) and threshold voltage ( $V_{th}$ ). From these three equations, we are able to solve for temperature T. The formulation of these three equations requires that we obtain gate-level leakage power, switching power, and delay. Our approach for temperature characterization is nondestructive and does not require complicated thermal models or thermal management tools. We first select a subset of gates for which we can characterize all the three properties using GLC, i.e., the gates that are on critical path, switch often, and do not have correlations in the system of linear equations with other gates in terms of leakage power. Next, we conduct gate-level leakage power, switching power, and delay characterization of the selected gates using the GLC method. After obtaining their gate level leakage power, switching power, and delay, we formulate three non-linear equations according to Equations (2.1), (2.2), and (2.4) for each gate and solve for the variables T, L, and  $V_{th}$ . Finally, we use the temperatures of the selected gates as the representative temperatures and determine the temperature profile of the entire circuit, under the consideration that the gates that are physically close to each other on the circuit have similar temperatures due to heat transfer. Algorithm 1 shows the pseudocode for selecting the representative gates and calculating the temperatures.

## 3.2.6.4 Gate Level Leakage Power Characterization

After obtaining the new temperatures of the gates, we follow Equation (2.1) to set the new coefficients in the system of linear equations. In this way, we are able to create various independent linear equations that break both types of correlations.

## 3.2.7 Improving the Objective Function

So far we have been using the l1-norm of measurement errors as the objective function in the LP. Although the l1-norm helps reducing the large errors, it is not capable of reflecting the actual measurement errors. In order for the optimization process to follow exactly the measurement error distribution, we consider the likelihood function of the measurement error distribution in our objective function. Our goal is to find the solution of maximum likelihood. For example, if we assume the error follows a triangular distribution, the objective function can be formulated as the following: Algorithm 1 Temperature Characterization: We conduct leakage power, switching power, and delay measurements on the pertinent IC and formulate three nonlinear equations with variables T, L, and  $V_{th}$ . We calculate T by solving the three non-linear equations.

Input: Target circuit for characterization.

**Output:** Temperature  $T_i$  of each gate i.

- 1: repeat

- 2: Select a set I of input vectors;

- 3: Determine (via correlation detection)  $S_{leakage}$ , the set of gates that do not have correlations with other gates in the system of linear equations in leakage power GLC;

- 4: Determine (via simulation)  $S_{switching}$ , the set of gates that switch with more than k% probability when I is applied;

- 5: Determine (via simulation)  $S_{delay}$ , the set of gates that are on critical path with more than k% probability when I is applied;

- 6:  $S_{rep} = S_{leakage} \cap S_{switching} \cap S_{delay};$

- 7: **until**  $S_{rep} \neq \emptyset$ ;

- 8: Conduct leakage power, switching power, and delay characterization using GLC;

- 9: for each gate i in  $S_{rep}$  do