# **UCLA**

## **UCLA Electronic Theses and Dissertations**

#### **Title**

Nanoscale contact engineering for Si/Silicide nanowire devices

#### **Permalink**

https://escholarship.org/uc/item/4gh912r9

#### **Author**

Lin, Yung-Chen

## **Publication Date**

2012

Peer reviewed|Thesis/dissertation

## UNIVERSITY OF CALIFORNIA

#### LOS ANGELES

Nanoscale contact engineering for Si/Silicide nanowire devices

A dissertation submitted in partial satisfaction of the requirements for the degree Doctor of Philosophy in Materials Science and Engineering

by

Yung-Chen Lin

© Copyright by

Yung-Chen Lin

#### ABSTRACT OF THE DISSERTATION

Nanoscale contact engineering for Si/Silicide nanowire devices

By

#### Yung-Chen Lin

Doctor of Philosophy in Materials Science and Engineering

University of California, Los Angeles, 2012

Professor Yu Huang, Chair

Metal silicides have been used in silicon technology as contacts to achieve high device performance and desired device functions. The growth and applications of silicide materials have recently attracted increasing interest for nanoscale device applications. Nanoscale silicide materials have been demonstrated with various synthetic approaches. Solid state reaction wherein high quality silicides form through diffusion of metal atoms into silicon nano-templates and the subsequent phase transformation caught significant attention for the fabrication of nanoscale Si devices. Very interestingly, studies on the diffusion and phase transformation processes at nanoscale have indicated possible deviations from the bulk and the thin film system. Here we studied growth kinetics, electronic properties and device applications of nanoscale silicides formed through solid state reaction.

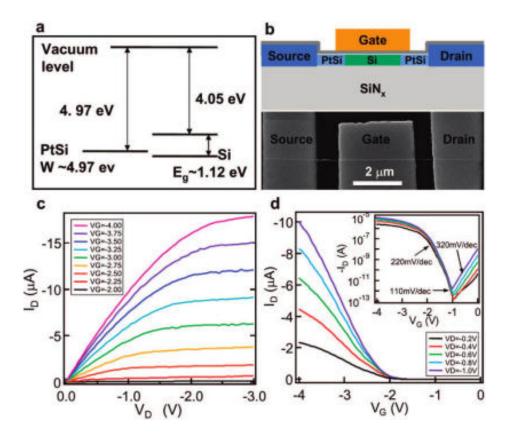

We have grown single crystal PtSi nanowires and PtSi/Si/PtSi nanowire heterostructures through solid state reaction. TEM studies show that the heterostructures have atomically sharp interfaces free of defects. Electrical measurement of PtSi nanowires shows a low resistivity of  $\sim 28.6 \ \mu\Omega$ ·cm and a high breakdown current density beyond  $10^8$  A/cm2. Furthermore, using single-crystal PtSi/Si/PtSi nanowire heterostructures with atomically clean interfaces, we have fabricated p-channel enhancement mode transistors with the best reported performance for intrinsic silicon nanowires to date. In our results, silicide can provide a clean and no Fermi level pinning interface and then silicide can form Ohmic-contact behavior by replacing the source/drain metal with PtSi. It has been proven by our experiment by contacting PtSi with intrinsic Si nanowires (no extrinsic doping) to achieve high performance p-channel device.

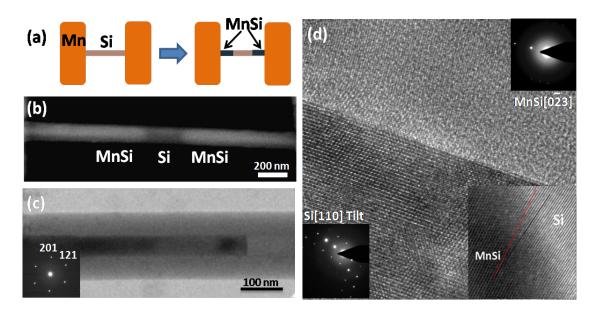

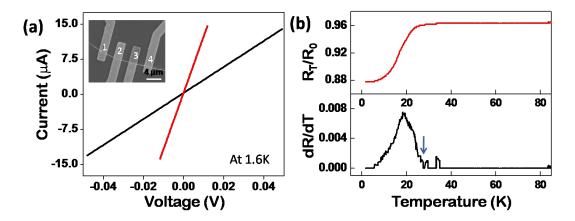

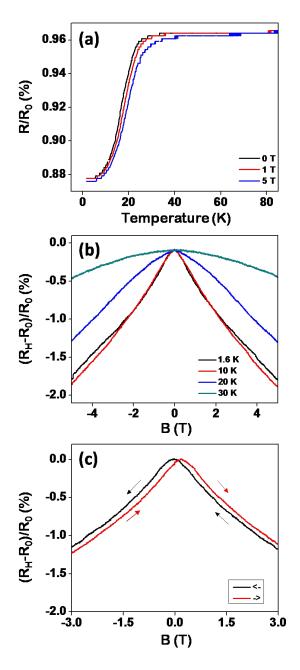

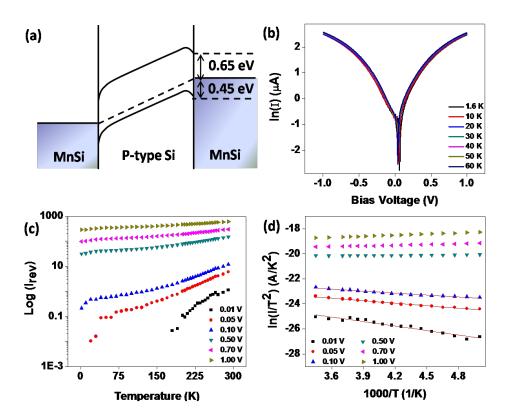

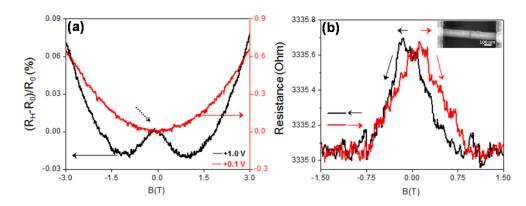

By utilizing the same approach, single crystal MnSi nanowires and MnSi/Si/MnSi nanowire heterojunction with atomically sharp interfaces can also been grown. Electrical transport studies on MnSi nanowire shows an abrupt resistance reduction due to the spin ordering at ~29.7 K. A negative magnetoresistance (MR) ~1.8% under 5 Tesla at 1.6 K is achieved, demonstrating the ferromagnetic behavior of MnSi. Furthermore, using the MnSi/p-Si/MnSi heterostructure, we have studied the charge injection at various temperatures via the Schottky barrier, and the spin scattering was observed through magnetotransport studies of MnSi/p-Si/MnSi heterojunction. Our results represent the first report of magnetic contact fabrication through the formation of single crystal heterojunction nanowires and the first demonstration of spin injection and detection in such Si nanowire devices. The magnetic silicides approach thus opens a new pathway to create ferromagnetic/semiconductor junction with clean and sharp interface, and maysignificantly impact the future of spintronics.

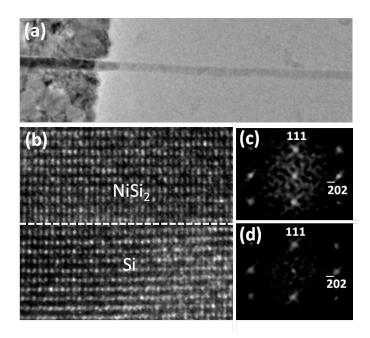

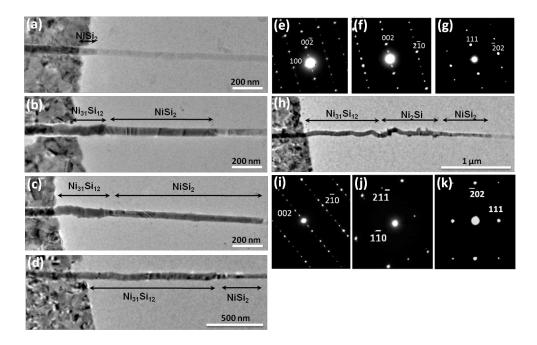

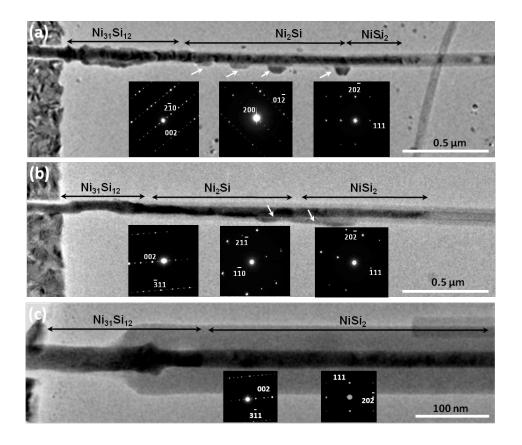

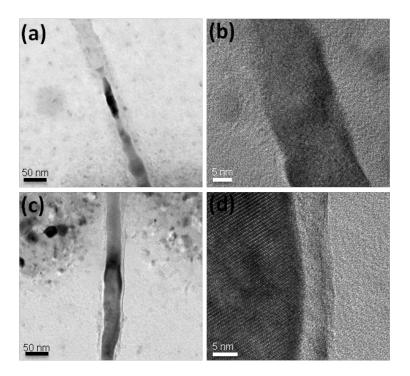

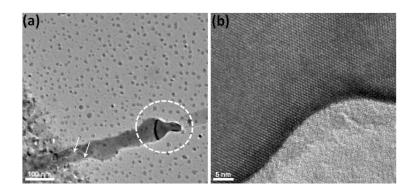

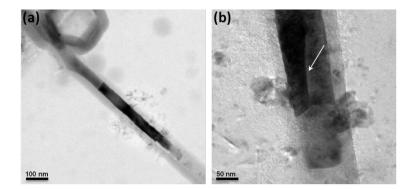

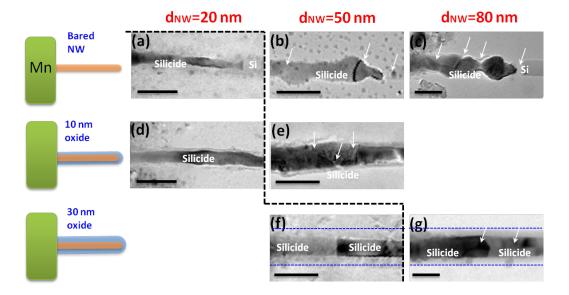

Beyond those applications, silicide phase control at nanoscale is investigated. Three nickel phases, Ni<sub>31</sub>Si<sub>12</sub>, Ni<sub>2</sub>Si and NiSi<sub>2</sub> are observed in one step annealing at 550 °C. NiSi<sub>2</sub> grows initially through the Si NW and then the area close to nickel pad transforms into the nickel-rich phase, Ni<sub>31</sub>Si<sub>12</sub>. With prolonged annealing over 5 minutes, the Ni<sub>2</sub>Si starts to show up in between Ni<sub>31</sub>Si<sub>12</sub> and NiSi<sub>2</sub>. The growth sequence is different from the thin film system where Ni<sub>2</sub>Si usually appears as the initial phase in the beginning as the annealing temperature is higher than 400 °C. Interfacial energy differences and surface free energy are believed to play an important role here at the nanoscale, which lead to the formation of normally unfavorable silicide phases in Si NWs. In addition, Si/SiOx core/shell NW structure is used to explore the phase transformation of silicides in the structure-confined nano environment. Nickel silicides in the structure-confined core/shell Si NW shares the similar phase formation sequences as those appeared in the bared SiNWs, while the growth rate is significantly retarded. This may be attributed to the high compressive stress built-in in the core/shell NW structure that retards the diffusion of the nickel atom as well as limits the volume expansion of the metal-rich phases. As a result, the high stress at this finite scale hinders the continuous growth of Ni<sub>31</sub>Si<sub>12</sub> into the core/shell NWs and totally eliminates the formation of Ni<sub>2</sub>Si in core/shell NWs with thick oxide shells (~ 50 nm). Through these studies, we have demonstrated first time the phase formation sequences of nickel silicides in Si and Si/SiOx NW structures, which is of great importance for reliable contact engineering for Si NW devices. Furthermore, we have provided a clear picture of the hindered nickel silicide growth in confined nanoscale environment and showed the deviated behavior of silicides growth under stress. The information rendered here will be useful for Si NW device applications as well as for the silicon device engineering at nanoscale in general.

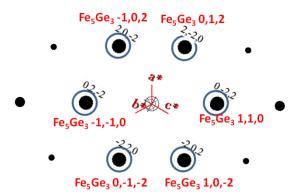

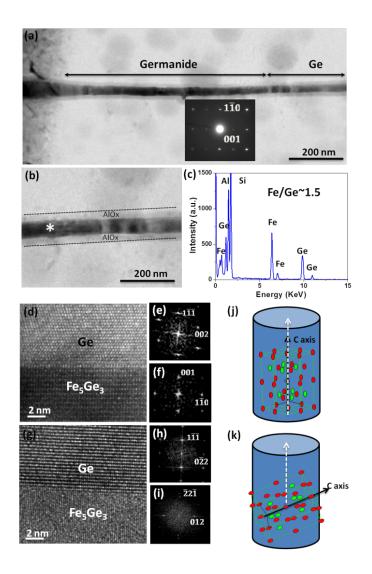

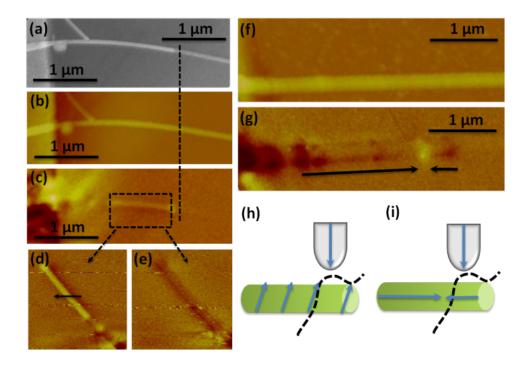

To further investigate the oxide shell effect, Mn<sub>5</sub>Si<sub>3</sub> and Fe<sub>5</sub>Ge<sub>3</sub> NW were grown within various oxide thickness to explore the nucleation and growth in the nanowire structure. A oxide shell exerted a compressive stress on the silicide or germanide materials will make those materials with single-crystal properties. Interestingly, single-crystal growth of contact materials can be also implemented for germanide materials. The iron-rich germanide, Fe<sub>5</sub>Ge<sub>3</sub>, was successfully grown with single-crystal properties. It shows ferromagnetic properties with a Curie temperature above the room temperature verified by magnetic force microscope (MFM). Two different epitaxial relations found at germanide/germanium interface due to the different sizes of the germanium NW templates. These two different crystal structures exhibited magnetic anisotropy in magnetic force microscope (MFM) measurement, showing differently preferred domain orientations. In-plane and out-of-plane magnetization in the Fe<sub>5</sub>Ge<sub>3</sub> NWs are observed in our experiment. The crystal orientation or engineering stress may have influence on the magnetic domain structure. This ferromagnetic contact material may open the way for spintronics to grow the magnetic materials on the semiconducting materials and control the direction of magnetization in the future.

Those silicide studies indicated silicide metal-heterojunction field effect transistor has excellent device performance. In addition, Si channel region can be shrunk to less than 10 nm and also keep semiconducting properties without high leakage current. This approach has the potential for future nanoelectronics. However, silicide phase transformation shows a deviated behavior from the studies in bulk system. It may be associated with stress effect or nucleation behavior at nanosclae, leading the different formation phase or sequence. For those interesting phenomena, it has attracted more and more attention and may gain more insight studies in the near future.

The dissertation of Yung-Chen Lin is approved.

King- Ning Tu

Kang L. Wang

Yang Yang

Yu Huang, Committee Chair

University of California, Los Angeles

2012

Dedicated to my son, Bruce Lin my wife, I-Fang Lee

# TABLE OF CONTENTS

| ABSTRACT OF THE DISSERTATION                                                                 | Page<br>ii |

|----------------------------------------------------------------------------------------------|------------|

| COMMITEE                                                                                     | .vi        |

| LIST OF TABLES                                                                               | xiii       |

| LIST of FIGURES                                                                              | xiv        |

| ACKNOWLEDGEMENTS                                                                             | xvi        |

| VITA                                                                                         |            |

| PUBLICATIONS AND PRESENTATIONS                                                               |            |

| Chapter 1: Introduction                                                                      |            |

| 1.1. The challenges of modern transistor for contact engineering                             | 1-1        |

| 1.2. NW transistor and silicided NW transistor                                               | .1-2       |

| 1.3. The properties and applications of metal silicides                                      | .1-3       |

| 1.4. The growth and applications of silicon NWs                                              | 1-3        |

| 1.5. Synthetic approaches to nanoscale silicides                                             | .1-6       |

| 1.6. Contact formation through solid state reaction                                          |            |

| 1.6.1. Introduction of silicide/Si heterostructure by solid state reaction                   | .1-8       |

| 1.6.2. The growth of silicide NWs by solid state reaction                                    | .1-9       |

| 1.6.3. Forming Silicide/Si NW heterostructure by solid state reaction                        | .1-10      |

| 1.7. New technical approaches or structures for low contact resistance FET and short-channel | el         |

| device                                                                                       |            |

| 1.7.1. The challenging for the low device junction resistance                                | .1-11      |

| 1.7.2. Comparison of junction FET, junctionless FET and                                      |            |

| metal h   | neterojunction FET                                                     | 1-11              |

|-----------|------------------------------------------------------------------------|-------------------|

| 1.8. Ref  | ferences                                                               | 1-14              |

| 1.9. Lis  | t of figures                                                           | 1-16              |

| 1.10. Li  | ist of Tables                                                          | 1-20              |

|           |                                                                        |                   |

|           |                                                                        |                   |

| Chapter   | r 2: Single Crystalline PtSi Nanowires, PtSi/Si/PtSi Nanowire Heteros  | structures, and   |

| Nanode    | evices                                                                 |                   |

| 2.1. Intr | roduction                                                              | 2-1               |

| 2.2. Exp  | perimental                                                             | 2-2               |

| 2.3. Res  | sults and discussions                                                  |                   |

| 2.3.1.    | Epitaxial relationship of PtSi formation within a silicon nanowire     | 2-3               |

| 2.3.2.    | Electrical transport properties of single crystal PtSi nanowires       | 2-4               |

| 2.3.3.    | PtSi/i-Si/PtSi nanowire heterostructures as high performance p-channel | el enhancement    |

|           | mode transistors                                                       | 2-5               |

| 2.4.      |                                                                        |                   |

| Conclus   | sion                                                                   | 2-10              |

| 2.5. Ref  | ferences                                                               | 2-10              |

| 2.6. Lis  | t of figures                                                           | 2-13              |

|           |                                                                        |                   |

| Chapter   | r 3: Detection of Spin Polarized Carrier in Silicon Nanowires with Sir | ngle Crystal MnSi |

| as Mag    | netic Contact                                                          |                   |

| 3.1. Intr | roduction                                                              | 3-1               |

| 3.2. Experimental                                                                | 3-3  |

|----------------------------------------------------------------------------------|------|

| 3.3. Results and Discussions                                                     |      |

| 3.3.1. Manganese silicide nanowire growth and analysis                           | 3-4  |

| 3.3.2. Electrical characterization of MnSi nanowire                              | 3-6  |

| 3.3.3. Magnetoresistance measurement (MR) of MnSi nanowire                       | 3-6  |

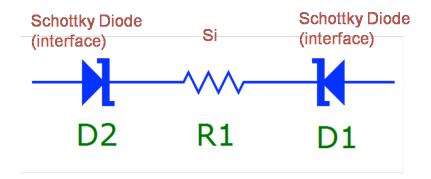

| 3.3.4. Band diagram of MnSi/p-Si/MnSi heterostructure and transport behavior     | 3-8  |

| 3.3.5. Magnetoresistance and resistance change of MnSi/Si/MnSi heterostructure   |      |

| tunneling junction under magnetic field sweeping                                 | 3-9  |

| 3.4. Conclusion                                                                  | 3-12 |

| 3.5. References                                                                  | 3-12 |

| 3.6. Supporting information                                                      | 3-15 |

| 3.7. List of figures                                                             | 3-18 |

|                                                                                  |      |

| Chapter 4: The Growth of Nickel Silicides in Si and Si/SiOx Core/Shell Nanowires |      |

| 4.1 Introduction                                                                 | 4-1  |

| 4.2 Experimental                                                                 | 4-2  |

| 4.3 Results and Discussions                                                      |      |

| 4.3.1. TEM study of nickel silicide growth                                       | 4-3  |

| 4.3.2. Silicide growth in various duration of annealing time                     | 4-4  |

| 4.3.3. Snap-shot TEM images of nickel silicide growth in the Si/SiOx core/shell  |      |

| NW for various annealing durations                                               | 4-5  |

| 4.3.4. Nickel silicide growth in Si/SiOx core/shell NWs with                     |      |

| various oxide shell thickness                                                          | 4-5       |

|----------------------------------------------------------------------------------------|-----------|

| 4.4 Conclusion                                                                         | 4-8       |

| 4.5 References                                                                         | 4-9       |

| 4.6. Supporting information                                                            | 4-12      |

| 4.7. List of Figures                                                                   | 4-14      |

|                                                                                        |           |

| Chapter 5: Control the Pollycrystalline and Single-Crystal Growth of Manganese Silicia | de & Iroi |

| Germanide NWs in the Confined Oxide Shell                                              |           |

| 5.1 Introduction                                                                       | 5-1       |

| 5.2 Experimental                                                                       | 5-2       |

| 5.3 Results and Discussions                                                            | 5-3       |

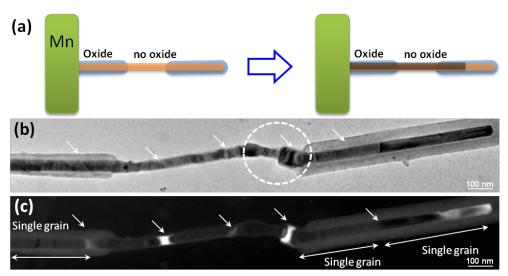

| 5.3.1. Manganese silicide formation in the oxide/Si core-shell NW with                 |           |

| various oxide thickness                                                                | 5-3       |

| 5.3.2. Manganese silicide formation in the oxide/non-oxide region                      | 5-4       |

| 5.3.3. Growth of iron germanide NW and germanide/germanium heterostructure             | 5-6       |

| 5.3.4. The magnetic properties of germanide NW                                         | 5-8       |

| 5.4 Conclusion                                                                         | 5-11      |

| 5.5 References                                                                         | 5-12      |

| 5.6. Supporting information                                                            | 5-14      |

| 5.7. List of figures                                                                   | 5-21      |

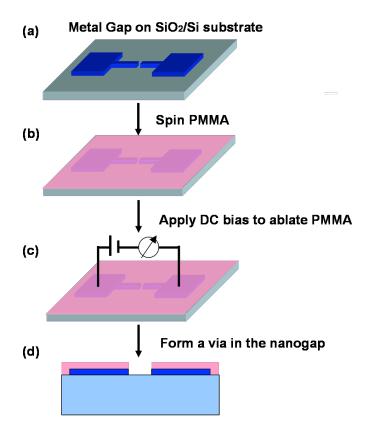

Chapter 6: Self-Aligned Nanolithography in a Nanogap

| 6.1 Int | roduction6-1                                                          |

|---------|-----------------------------------------------------------------------|

| 6.2. Ex | xperimental6-2                                                        |

| 6.3. Re | esults and Discussions                                                |

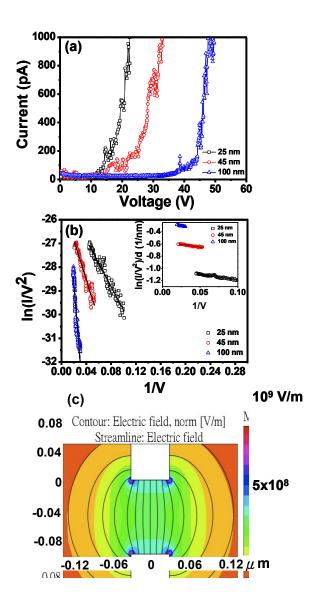

| 6.3.1.  | SEM images of self-aligned nanogap area patterning                    |

| 6.3.2.  | Electrical characteristics and simulation of nanogap structure coated |

|         | with PMMA6-4                                                          |

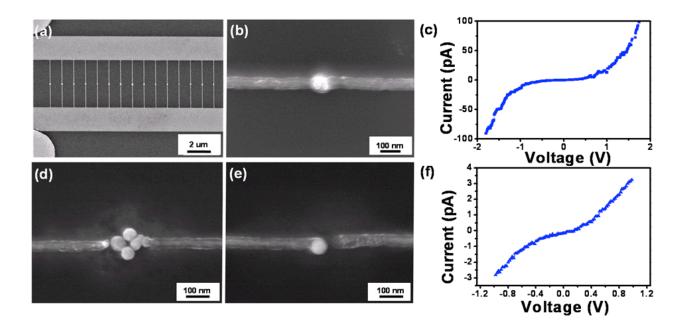

| 6.3.3.  | Self-aligned nanostructure                                            |

| 6.4. Co | onclusion6-6                                                          |

| 6.5. Re | eferences                                                             |

| 6.6. Li | st of figures6-10                                                     |

|         |                                                                       |

| Chapt   | er 7: Summary                                                         |

# LIST OF TABLES

|                                                                      | Page  |

|----------------------------------------------------------------------|-------|

| Table 1-1. Electronic and optical properties of silicide materials   | .1-23 |

| Table 1-2. Work function of silicide materials to the n-type silicon | 1-24  |

# LIST of FIGURES

| Page                                                                                     |

|------------------------------------------------------------------------------------------|

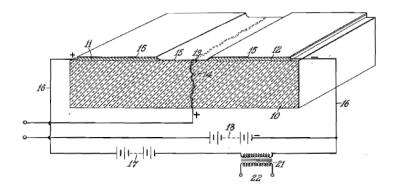

| Figure 1-1. Lilienfeld, J. E. Method and apparatus for controlling electric current1-18  |

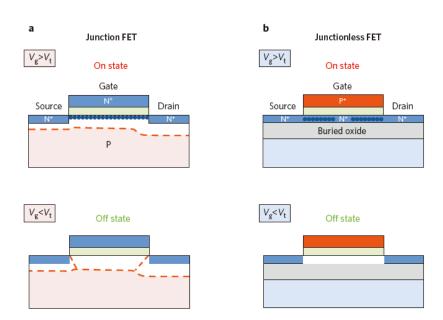

| Figure 1-2. Cross sections and operation principles for an n-type junction FET           |

| and a junctionless FET                                                                   |

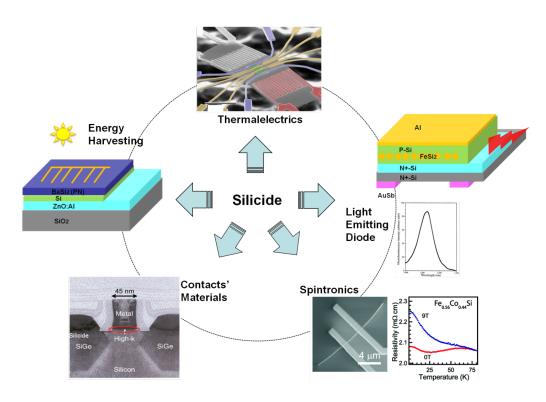

| Figure 1-3. Applications of silicide materials                                           |

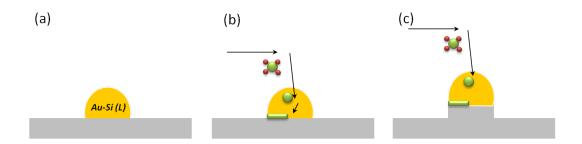

| Figure 1-4. Schematic illustration of the Vapor-Liquid-Solid (VLS) process for Si NWs1-1 |

| Figure 1-5. Growth technologies of silicide materials: Endotaxy                          |

| Figure 1-6. Schematic of Ni silicide NW growth by solid state reaction1-2                |

| Figure 1-7. TEM analysis for silicide/Si/silicide heterostructure                        |

| Figure 1-8. Junctionless FET and metal heterojunction FET based on SOI                   |

| or NW structures1-2                                                                      |

|                                                                                          |

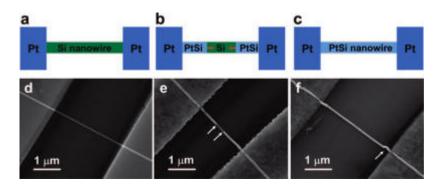

| Figure 2-1. Formation of PtSi nanowire and PtSi/Si/PtSi nanoheterostructures2-14         |

| Figure 2-1. Formation of PtSi nanowire and PtSi/Si/PtSi nanoheterostructures             |

|                                                                                          |

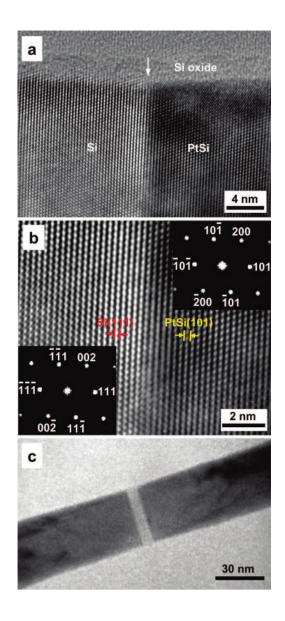

| Figure 2-2. Epitaxial relationship of PtSi formation within a silicon nanowire2-13       |

| Figure 2-2. Epitaxial relationship of PtSi formation within a silicon nanowire           |

| Figure 2-2. Epitaxial relationship of PtSi formation within a silicon nanowire           |

| Figure 2-2. Epitaxial relationship of PtSi formation within a silicon nanowire           |

| Figure 2-2. Epitaxial relationship of PtSi formation within a silicon nanowire           |

| Figure 2-2. Epitaxial relationship of PtSi formation within a silicon nanowire           |

| Figure 3-5. Magnetoresistance and resistance change of MnSi/Si/MnSi              |

|----------------------------------------------------------------------------------|

| heterostructure tunneling junction under magnetic field sweeping                 |

| Figure 4-1. TEM image of nickel silicide growth in bare silicon nanowire after   |

| annealing at 550 °C for 60 seconds & interface                                   |

| Figure 4-2. Silicide growth in various duration of annealing time at 550 °C4-15  |

| Figure 4-3. Snap-shot TEM images of nickel silicide growth in the Si/SiOx        |

| core/shell NW for various annealing durations at 550 °C                          |

| Figure 4-4. Nickel silicide growth in Si/SiOx core/shell NWs with                |

| various oxide shell thickness                                                    |

| Figure 5-1. Manganese silicide formation in the oxide/Si core-shell NW           |

| with various oxide thickness                                                     |

| Figure 5-2. Manganese silicide formation in the oxide/non-oxide region5-21       |

| Figure 5-3. Growth of iron germanide NW and germanide/germanium                  |

| heterostructure                                                                  |

| Figure 5-4. The magnetic properties of germanide NW                              |

| Figure 6-1. Schematic of self-aligned nanolithography in a nanogap6-10           |

| Figure 6-2. SEM images of self-aligned nanogap area patterning6-11               |

| Figure 6-3. Electrical characteristics of nanogap structure coated with PMMA6-12 |

| Figure 6-4. Self-aligned vial holes as template for nanoparticle deposition      |

| obtain electrode-island-electrode tunneling device                               |

#### **ACKNOWLEDGEMNETS**

I would like to thank my advisor, Prof. Yu Huang, for her guidance and encouragement which persuade me to have good research attitude. I would like to thank Prof. King-Ning Tu, Prof. Kang L. Wang and Prof. Yang Yang for serving as my committee members and giving me helpful comments.

Many thanks to all my coworkers and those who ever helped me for my research and my life. I will keep those in mind.

Last, I would like to express my gratitude to my parents for their support. Also, Thank my wife, Yvonne and my cute son, Bruce. I feel happy and lucky to have you.

# VITA

| December 11, 1979 | Born in Taichung, Taiwan                                                                               |

|-------------------|--------------------------------------------------------------------------------------------------------|

| 2002              | B.S., Materials Science and Engineering National Tsing-Hua University Hsin-Chu, Taiwan                 |

| 2004              | M.S., Materials Science and Engineering National Tsing-Hua University Hsin-Chu, Taiwan                 |

| 2012              | Ph.D., Materials Science and Engineering University of California, Los Angeles Los Angeles, California |

#### PUBLICATIONS AND PRESENTATIONS

- 1. <u>Lin, Y. C.</u>, Chen, Y. and Huang Y., The growth and applications of silicides for nanoscale devices., **Nanoscale**, 4 (5), 1412-1421, (2012).

- 2. Wu, W. W., K. C. Lu, Chen, K. N., Yeh, P. H., Wang, C. W., Lin, Y. C., Huang, Y., Controlled large strain of Ni silicide/Si/Ni silicide nanowire heterostructures and their electron transport properties,. **Applied Physics Letters**, 97(20), 203110, (2010).

- 3. <u>Lin, Y. C.</u>, Y. Chen, Di, Xu, Huang, Y. Growth of Nickel Silicides in Si and Si/SiOx Core/Shell Nanowires., **Nano Letters**, 10(11), 4721-4726, (2010).

- 4. <u>Lin, Y. C.</u>, Chen, Y., Shailos, A. and Huang, Y., Detection of spin polarized carrier in silicon nanowire with single crystal MnSi as magnetic contacts, **Nano Letters**, 10 (6), 2281–2287 (2010).

- 5. Lin, Y. C., Bai, J. W., & Huang, Y., Self-aligned nanolithography in a nanogap., Nano Letters, 9 (6), 2234-2238, (2009).

- 6. <u>Lin, Y. C.</u>, Lu, K. C., Wu, W. W., Bai, J. W., Chen, L. J., Tu, K. N., & Huang, Y., Single crystalline PtSi nanowires, PtSi/Si/PtSi nanowire heterostructures, and nanodevices., **Nano** Letters, 8 (3), 913-918, (2008).

#### 1. Introduction

#### 1.1. The challenges of modern transistor for contact engineering

As addressed by the scaling rule, the device dimensions of complementary metal-oxidesemiconductor (CMOS) transistors have been shrunk to improve the performances for ultralarge-scale integrated circuits (ULSI). The shrinkage of the contact feature size or carrier channel size has caused the increase of resistances in both source/drain regions, leading to the degradation of electrical characteristics.<sup>1, 2</sup> This degradation becomes unavoidable in the advanced short-channel devices and thus new design strategies need to be imposed to current nanotechnology. In 1925, a field effect transistor (FET) device structure with only conducting channel (no junctions) was proposed. (Figure 1-1) The FET was only a resistor that could be depleted of charge carriers by gate modulation. To turn the device completely off, the device need to fully deplete its body of carriers. Therefore, it required a very thin nanoscale channel for which the technology did not exist at the time. Recent explorations of NW or thin-film transistor architectures (SOI) have raised practical interest in these simple gated resistors. Especially for the NW transistors, the thin body structure displaying better gate control, allowing researchers to explore diverse device structures and to investigate new operation functions. However, for this type of thin body transistor or NW FET, the contact or sheet resistance is still high. The silicided NW FET utilizes the low resistance properties of silicides in place of the source/drain contacts and has attracted broad research interest. By combining the NW structure and silicide technology, it is possible to solve the short-channel problem and achieve high device performance for ultrashort channel device in the future.

#### 1.2. NW transistor and silicided NW transistor<sup>3</sup>

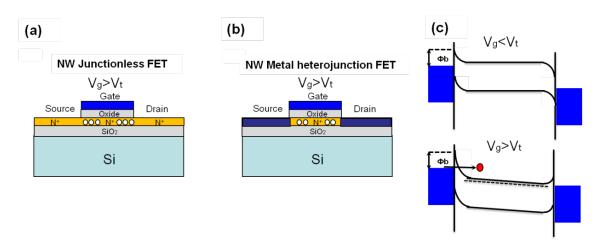

NW FET poses as a potential candidate to resolve the short-channel effect issue since the thin body of NW excludes large depletion region. Hence, degradation of gated control and source/drain leakage can be avoided. The charge carriers in the NW can be fully depleted and thus the NW FET can be operated as junctionless FET (Figure 1-2b) or metal heterojunction FET, having no source/drain implantation compared with conventional junction FET (Figure 1-2a). Moreover, the contact resistance can be effectively reduced when silicides are used as the contact materials, making silicided NW FET promising candidate to achieve high performance transistor operation.

To fabricate the NW FET, silicon NWS are often grown by vapor-liquid-solid (VLS) method. The diameter of NWS can be controlled by the size of the metal catalyst such as gold. In addition, the silicon NW doping can be done by using the in-situ doping which flows the doping elements in gas phase in the growing process. For simplicity, the NW transistor usually functions as junctionless FET (no source/drain implantation). To achieve high performance, the doping concentration of NWS is usually at the level of ~10<sup>17</sup>~10<sup>18</sup> cm<sup>-3</sup>. In these doping ranges, the source/drain contact resistance will not be too large to limit the current. Therefore, in this operation mode, the device is always in the on-state and the accumulation-mode operation is applied to reach higher on-current and lower subthreshold voltage (Vt). The same charge voltage is applied to deplete the NW to reach the off-state. If NWS are doped with even higher doping concentration, the NW device can be operated with body current (carrier flows in the whole NW body) flowing in the on-state and also rely on the reverse voltage to turn the device off. By this design, it is not necessary to attract the carrier to the surface and then is not strongly dependent of the oxide thickness scaling. Therefore, it is better for the ultra-short channel devices.

To reduce the contact resistance further, the metal heterojunction FET can also be fulfilled in the NW structure. With the silicide technology, nickel and platinum silicide has been proposed to grow in the silicon NW and form the silicide/silicon/silicide heterjunction. With various doping concentration of silicon, the device can function in the normal-on or normal-off mode, and in both modes the NW transistor can achieve high performance, due to the better gated control in the NW structure.

#### 1.3. The properties and applications of metal silicides

Silicide materials with diversified properties (Table 1-1) have been widely used in electronics such as device contacts (NiSi, TiSi<sub>2</sub>, CoSi<sub>2</sub>),<sup>4-10</sup> optical light emitting diode (β-FeSi<sub>2</sub>, CrSi<sub>2</sub>),<sup>11, 12</sup> thermoelectrics (MnSi<sub>1.7</sub>),<sup>13</sup> photovoltaic devices (BaSi<sub>2</sub>)<sup>14-16</sup> and spintronics devices (Fe<sub>x</sub>Co<sub>1-x</sub>Si, Fe<sub>3</sub>Si, Co<sub>2</sub>MnSi)<sup>17-19</sup> shown in Fig 1-3.<sup>20-21</sup> Silicides with low contact resistivity, good interface property and better thermal stability are candidates for device contact application. Some metallic silicides are also magnetic which draw considerable interest for its potential application in spintronics due to its compatibility with current Si technology.

#### 1.4. The growth and applications of silicon NWS

Silicon NWS are grown through metal-catalyzed chemical vapor deposition process. The growth is generally to follow the vapor-liquid-solid mechanism. In the beginning, the catalyst, mostly Au, forms a eutectic droplet at low temperature on a heated Si [111] substrate (Fig 1-4a). In the following step, gas precursors containing reactant material (Si) are introduced and then catalytically decomposed to incorporate into the liquid droplet near the eutectic temperature.

This liquid droplet continues to adsorb decomposing Si atoms from the vapor, leading to a supersaturated state (Fig. 1-4b), at which point crystallization of Si occurs at the liquid-solid interface resulting in one-dimensional (1D) NW growth (Fig. 1-4c).

Silicon based devices are wildly used in integrated circuit devices for lots of decades due to its excellent electronic properties, chemical stability, mechanical strength and other solvable process issues such as good insulating oxidation product and etching friendly. Thus, for the nanotechnology, there are lots of efforts, been made, to discover the new functionality of SiNWs. For the capability of transporting electrons and holes, silicon NWS can be function units for nanoscale electronics constructed without complicated and expensive fabrication equipments. Si NWS also have potential applications in chemical sensors, field-emeission devices, spintronics and photonics. Physical properties of Si NWS are addressed as follows: The electronic energy gaps of Si NWs have been investigated by scanning tunneling spectroscopy, found to increase with the decrease of the Si NW diameter from 1.1 eV for 7 nm to 3.5 eV for 1.3 nm. This is coherent with previous theoretical predictions. The Young's Modulus of the VLS-synthesized Si NWS have been characterized by atomic force microscopy to be 186 and 207 GPa, respectively, for single- and double-clamped Si NWS, which are close to the Si (111) bulk value of 169 GPa. The average fracture strength of the Si NWs that are VLS-grown on a [111] Si substrate has been calculated to be around 12 GPa.

The thermal conductivity of individual single-crystal intrinsic Si NWS with diameters of 22-115 nm has been found to be two orders smaller than that of bulk Si in magnitude. The increased phonon-boundary scattering and possible phonon-spectrum modification result in the strong diameter dependence of thermal conductivity in NWS. This is also indicated by molecular dynamics simulation studies based on increased surface-scattering effects/Nevertheless, due to

the phonon-confinement effect, the thermal conductivity was predicted to increase at very small diameter, smaller than 1.5 nm.

For electrical properties, the carrier mobility of single crystalline n-type and p-type Si NWs has been estimated to be coherent with diffusive transport. Also, studies show that Si NWs are expected to be able to be heavily doped and become metallic. Silicon NWS have been demonstrated to be efficient thermoelectric materials that could be applied to waste heat utilization, power generation and refrigeration. The efficiency of the materials is determined by the thermoelectric figure of ZT, which is a function of the Seeback coefficient, electrical resistivity, thermal conductivity and absolute temperature. Since optimizing one parameter of ZT often degrades another, it has been challenging to maximize ZT. However, it is possible to fabricate nanostructures of one or more dimensions, smaller than the mean free path of the phonons but larger than that of electrons and holes. This can greatly reduce thermal conductivity but maintain electrical resistivity, enabling ideal thermoelectric materials. ZT=0.6 at room temperature in rough Si NWS of about 50 nm in diameter has been demonstrated through a wafer-scale processing technique. Additionally, ZT~1 at 200K, has been reported from the single-component system of Si NWS for cross-sectional areas of 10 nm x 20 nm and 20 nm x 20 nm through adjusting impurity doping levels and the nanowire size. The optical properties of and hydrogen-terminated Si NWs have been studied by time-resolved photoluminescence spectroscopy, cathodoluminescence spectroscopy and imaging. Interface states in the Si core and oxygen-based defects at the oxide cladding layer respectively contribute to the red- and the blue-emission bands from these NWs, characterized by homogeneous broadening. Additionally, quantum confinement effects are excluded for being the cause of these emission bands based on the results. The Erbium-doped Si NWs show photoluminescence at room temperature at a wavelength of 1.54  $\mu$ m, which is ideal for optical communication. Additionally, Si NWs have notably larger piezoresistance effect than bulk Si, related to strain-induced carrier mobility change and surface modifications. This may be important for nanowire-based flexible electronics and nano-electromechanical systems.

#### 1.5. Synthetic approaches to nanoscale silicides

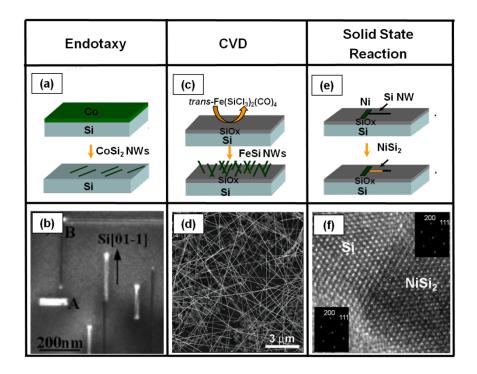

Various approaches have been developed to grow nanoscale silicide structures, which can be summarized to three categories: (1) endotaxy, (2) chemical vapour deposition (CVD) and (3) solid state reaction (Figure 1-5). For the endotaxial growth, transition metals, rare-earth (RE) metals or noble metals were deposited onto a heated Si substrate and subsequently reacted with the substrate to form self-assembled silicide nanostructures. In order to have the lowest strain energy against the substrate, silicide materials adjusted their shape into nanostructures with small anisotropic lattice mismatch (~ 0%) in the larger (longitudinal) direction and larger mismatch (~> 3%) in the smaller (axial) direction. Figure 1-5a, b showed CoSi<sub>2</sub> NW (NWs) islands grown on Si(100) substrate at 750°C. Cobalt was deposited by sublimation onto a heated substrate and reacted with Si to form CoSi<sub>2</sub>. <sup>30</sup> CoSi<sub>2</sub> would self-assemble into two distinct shapes, rectangular and NW (NWS) shape in Fig. 2b. For rectangular shape, CoSi<sub>2</sub> adopts A-type epitaxial relation, Si(111)//CoSi<sub>2</sub>(111), with the Si substrate; for NW shape, B-type epitaxial relation appeared on one side of interface, Si(111)//CoSi<sub>2</sub>(-11-1) and Si(1-51)//CoSi<sub>2</sub>(1-11) epitaxial relation shows on the other side. These interface configurations correspond to the coherent interface relations between CoSi<sub>2</sub> nanostructures and Si(100) substrate with lower interfacial energy. A variety of metals such as Ti, Mn, Fe, Co, Ni and Pt have been reported to form silicide nanostructures on the Si substrate through endotaxy growth.31-34 However, no effective control methods are

available so far over the growth length, growth position of the silicide NWs or NW diameter with this approach.

Chemical vapour deposition (CVD) is a popular synthetic route to form silicide nanostructures which is implemented through the reactions between metal and/or Si precursors. CVD method could be conducted with versatile precursors, reactions between silicon vapour precursor (SiH<sub>4</sub>) and metal thin film (e.g. nickel), metal vapour precursors (e.g. metal halogen precursors such as metal chlorine or metal iodine vaporized at high temperature) with Si substrate, reaction with both Si and metal vapour precursors or reactions from a single source of precursor containing both Si and metal. Fig. 1-5c and d demonstrate the use of a single vapour precursor (trans-Fe(SiCl<sub>3</sub>)<sub>2</sub>(CO)<sub>4</sub>)<sup>35</sup> as the iron and Si source to grow FeSi NWs in a CVD setting. The precursor decomposed at elevated temperatures to form a NW structure on the SiO<sub>2</sub>/Si substrate. In this manner, a wider range of single-crystal silicide NWs can be synthesized and used to explore the properties of various silicide materials. In a CVD setting, vapour precursor can be supplied continuously to synthesize abundant free standing silicide NWs which may be scaled up to mass production. In addition, the silicide growth is not limited to the growth substrates. (e.g. Si, sapphire, SiO<sub>2</sub> substrates) since the metal and Si source can be both supplied through vapour precursors. But as the precursors may under different decomposition routes at different temperature zones and/or growth pressures, mixed product of silicon, silicide thin film, different silicide nanostructures, and sometimes metal film, metal particles can be found in the same reaction chamber.<sup>37-40</sup> Therefore the CVD reaction conditions need to be strictly controlled in order to obtain desired silicide products.

Solid state reaction is another approach to silicide nanostructures and, because of its reaction nature, to form silicide/Si interface which can be explored as contacts for various device

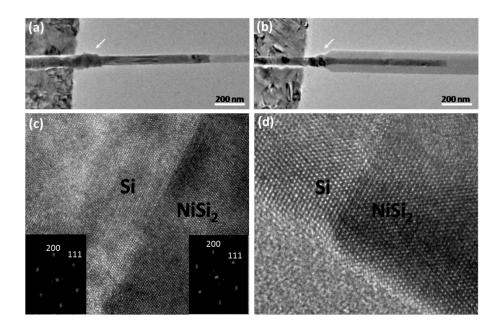

applications based on Si NWs. This approach has been used extensively in microelectronic industry to form metallic silicide contacts to Si through the interface reaction of Si and the metal. In short, metal is deposited as thin film on top of Si NWs and then at elevated temperatures metal atoms diffuse into and react with Si to form silicides, which normally adopt an epitaxial relation with the Si lattice. A variety of silicide contacts with excellent performance by solid state reaction method have been demonstrated such as NiSi<sub>2</sub>/Si, NiSi/Si, Ni<sub>2</sub>Si/Si, CoSi<sub>2</sub>/Si, PtSi/Si and MnSi/Si for nanoelectronics. 36, 41-46 Figure 1-5e shows the schematic of a typical solid state reaction set up. Ni contacts were deposited on top of Si NWs, which were then subject to annealing at elevated temperatures. Ni atoms would diffuse into Si NW template and transform Si into Ni silicides. NiSi<sub>2</sub> was found to form at 550°C, <sup>43</sup> which maintains a sharp clean epitaxial interface with Si lattice (Si[1-10]//NiSi<sub>2</sub>[1-10] and Si(111)//NiSi<sub>2</sub>(111)) as show in the high resolution transmission electronic microscopic (HRTEM) image in Figure 1-5f. The smooth and high quality epitaxial interface between silicides and Si achieved in solid state reactions makes this approach desirable for device fabrication at nanoscale, which is also compatible with current microelectronic processing techniques.

#### 1.6. Contact formation through solid state reaction

#### 1.6.1. Introduction of silicide/Si heterostructure by solid state reaction

While Si NW devices have caught increasing attention for future device applications, it has been difficult to achieve low resistance, high stability or less defective contacts at this scale due to the small contact area, surface traps or non-conformal coverage between electrodes and NW structure. For solid state reactions confined in Si NW structures, the silicides form directly on the silicide/Si interface resulting in a fresh and few-defect metal/Si interface that may

contribute to high device performance. With lithographically patterned metal pads, silicide/Si/silicide structures can be achieved with two silicide regions serving as source and drain electrodes, and the Si as the transistor channel. It has also been demonstrated that silicides can grow up to ~um's length into the Si NW from the metal contacts, which has been explored for device scaling to achieve short channel devices. 44, 45, 49 Studies indicate that the junction leakage is small (~60 nA at the 0.5 V) in the Ni silicide/Si/Ni silicide heterostructure even with an ultrashort Si channel of ~5 nm, which may be attributed to the perfect Ni silicide/Si interface and the low concentration of Ni atoms existing in the Si channel.<sup>50</sup> The current-voltage (I-V) measurement across the ultrashort channel silicide/Si heterostructure device shows a rectified curve which indicates the existence of Schottky barrier in the Ni silicide/Si/Ni silicide heterojunction. This suggests that the semiconducting properties of Si are preserved and the flat interface does not enhance thermal emission or current tunnelling which are normally observed at a rough or spike-like interface, even though the semiconducting channel is less than 10 nm. The impressive results imply that the Ni silicide/Si/Ni silicide heterostructure can be applied for ultrashort channel devices.

#### 1.6.2. The growth of silicide NWs by solid state reaction

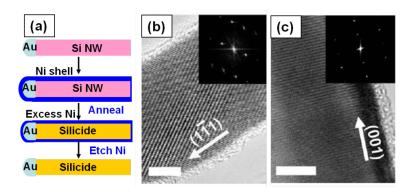

Wu et al.<sup>49</sup> first demonstrated the idea to implement the silicide technology at nanoscale for making silicide NWs by solid state reaction. As illustrated in Figure 6a, Si NWs were grown by vapour liquid solid (VLS) method and then Ni films were deposited with comparable thickness to the average NW diameter. The Ni-coated Si NWs were then annealed at 550°C to form NiSi. The excess Ni was etched away by acid and followed by the post-annealing at 600°C at forming gas (N<sub>2</sub>:H<sub>2</sub>=90:10). This process will render fully silicided NWs that are single crystal in nature

as shown in the figure 3b and c. The different NiSi NW growth directions, NiSi[1-11] (Fig. 1-6b) and NiSi[001] (Fig. 1-6c) may be explained by different growth directions of the starting Si NWs.

#### 1.6.3. Forming Silicide/Si NW heterostructure by solid state reaction

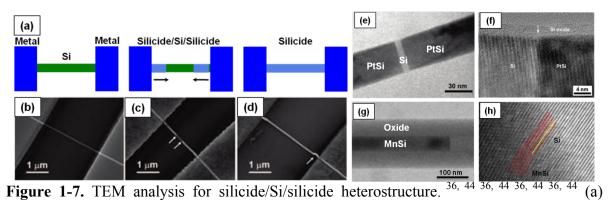

To achieve the growth of silicide/Si heterostructure, it is crucial that metal elements possess higher diffusivity in Si. Due to the fast diffusion of metal atom into the Si NWs, silicides can grow into the NWs, forming silicide/Si heterojunction. Several silicide/Si heterostructures have been investigated with the metallic contacts such as Ni, Pd, Pt, Co and Mn to the Si NWs. 36, 41, 43-<sup>45, 51</sup> The heterostructures are generally formed by patterning the Si NW template with metal pads followed by annealing at elevated temperatures to perform the silicidation (Fig. 1-7a). The silicide/Si/silicide heterostructure or fully silicided NW can be controlled through the annealing time (Fig. 1-7a,b-d). There are various material systems that have demonstrated such heterostructures such as NiSi/Si, CoSi<sub>2</sub>/Si, NiSi<sub>2</sub>/Si, PtSi/Si and MnSi/Si. 36, 44-46, 49 In these systems, epitaxial relations are all observed between silicide and Si with atomically sharp interface and few interface defects, which is desirable for high performance nanoelectronics. Taken PtSi and MnSi as the examples, both silicide systems can form the silicide/Si heterostructure. Surprisingly, although accompanied with large lattice mismatch (~ 8.8% in PtSi/Si, ~24.5% in MnSi/Si), both silicides mange to keep the epitaxial relation and a flat interface with Si when advancing into the Si NWs (Fig. 1-7e-h). 36,44 Even though the Si region is below 10 nm (Fig. 1-7e), the silicide regions will not merge and a clear interface is maintained. The excellent interface properties and junction properties allow silicide heterojunction to potentially work as ultra-short channel devices.

# 1.7. New technical approaches or structures for low contact resistance FET and shortchannel device

#### 1.7.1. The challenging for the low device junction resistance

The conventional FET can be classified as the junction FET. The opposite type of doping for the source/drain and channel is necessary for this device structure. As the device scales down, the main issue is the short-channel effect due to the depletion region across the channel. Other issues such as degradation of sub-threshold slopes, drian-induced-barrier-lowering (DIBL) and source/drain leakage all come from the similar reasons related to the source/drain junction. Industry has several approaches to achieve the shallow junction which relieves the short-channel effect. However, the p-n junction around source and drain still has higher sheet resistance, which may become a current limit for ultra-short channel device. Therefore, major architectural changes have been proposed to facilitate downsizing toward the perceived limit of ~30 nm. Recently, several groups have suggested that short-channel effects can be suppressed by imposing a junctionless structure or a metal heterojunction barrier at the source/drain in place of heavily doped junctions.

# 1.7.2. Comparison of junction FET, junctionless FET and metal heterojunction FET

For the junctionless FET (Fig 1-8a), the conduction in the junctionless gated transistor is based on the transport of majority carriers in the bulk of the device, through a body channel from source to drain. Therefore, drain current in the on-state is proportional to the channel doping and the carrier mobility and not dependant on the gate oxide capacitance (dielectric constant or thickness). Speed (or 'intrinsic delay') is also independent of the gate oxide thickness. The

extreme efforts currently underway to reduce gate oxide thicknesses can therefore be avoided. This junctionless FET needs a thinner body or one-dimensional wire structure to provide the better gated control. The complete depletion is necessary for the junctionless FET to behave as the off-state. Therefore, the junctionless FET can only be fulfilled for the SOI technology or in a NW structure.

Metal heterojunction FET is another new structure to alleviate the short-channel effect (without source/drain doping) and reduce the source/drain sheet resistance. A heterolayer, silicides, grows at the source/drain in place of a heavily doped homojunction (Fig. 1-8b). The Schottky barrier which forms naturally between a metal silicide source/drain and the silicon channel offers a number of advantages such as alleviating shallow source/drain extensions, junction capacitance, parasitic bipolar and latch-up phenomena, and fluctuations due to finite number of randomly placed dopants in the channel. A conventional self-aligned silicide process is employed to create the Schottky barrier MOSFET (SBMOSFET) structure. Gate-induced electric fields then render the source barrier nearly transparent to tunneling in the on-state, Vg>Vt, as in Fig. 1-8c, while carriers remain to be confined by the Schottky barrier in the off state, Vg<Vt as in Fig. 1-8c. A low barrier height of ~0.2-0.3 eV (Table 1-2) is needed at the source in order to induce large tunnel currents in the on-state at practical gate voltage or electric field. Conversely, a relatively high barrier is needed to suppress "reverse" tunneling by opposite type of carriers at the drain. Because the Fowler–Nordheim transmission probability for internal field emission is exponentially dependent upon barrier height as  $\Phi b^{3/2}$ , very large on/off ratio can be achieved at low temperatures in metal heterojunction MOSFETs.

According to the literatures, PtSi and ErSi<sub>2</sub><sup>44, 52</sup> have successfully experimented as the p and n-type metal heterojunction FET on bulk Si substrate. PtSi source/drain p-MOSFETs show excellent scaling to ~25 nm channel length with greatly simplified processing and reduced contact, sheet and parasitic resistance. Junction capacitance is effectively eliminated, and much smaller. Complementary *n*-type devices have also been demonstrated recently based on the low ~0.39 eV n-barrier of ErSi<sub>2</sub>. Due to the high doping concentration in the channel, the off-current is still the limitation for this device structure. However, for the NW structure, the fully depleted characteristic may suppress the strong source/drain leakage. Therefore, it may be more practical for NWs to achieve the metal heterojunciton FET.

#### 1.8. Reference

- 1. J. P. Colinge, I. Ferain, A. Kranti, C. W. Lee, N. D. Akhavan, P. Razavi, R. Yan and R. Yu, *Sci Adv Mater*, 2011, **3**, 477-482.

- 2. J. P. Colinge, C. W. Lee, A. Afzalian, N. D. Akhavan, R. Yan, I. Ferain, P. Razavi, B. O'Neill, A. Blake, M. White, A. M. Kelleher, B. McCarthy and R. Murphy, *Nat Nanotechnol*, 2010, 5, 225-229.

- 3. A. M. Ionescu, *Nat Nanotechnol*, 2010, **5**, 178-179.

- 4. F. Deng, R. A. Johnson, P. M. Asbeck, S. S. Lau, W. B. Dubbelday, T. Hsiao and J. Woo, *J Appl Phys*, 1997, **81**, 8047-8051.

- 5. H. Iwai, T. Ohguro and S.-i. Ohmi, *Microelectron Eng*, 2002, **60**, 157-169.

- 6. H. Jiang, C. M. Osburn, Z. G. Xiao, G. McGuire and G. A. Rozgonyi, *J Electrochem Soc*, 1992, 139, 211-218.

- 7. J. M. Larson and J. P. Snyder, *Ieee T Electron Dev*, 2006, **53**, 1048-1058.

- 8. P. G. McCafferty, A. Sellai, P. Dawson and H. Elabd, *Solid State Electron*, 1996, **39**, 583-592.

- 9. T. Morimoto, *IEEE Trans. Electron Devices*, 1995, 42, 915-922.

- 10. K. N. Tu, W. N. Hammer and J. O. Olowolafe, *J Appl Phys*, 1980, **51**, 1663-1668.

- 11. V. Bellani, G. Guizzetti, F. Marabelli, A. Piaggi, A. Borghesi, F. Nava, V. N. Antonov, O. Jepsen, O. K. Andersen and V. V. Nemoshkalenko, *Phys Rev B*, 1992, **46**, 9380-9389.

- 12. D. Leong, M. Harry, K. J. Reeson and K. P. Homewood, *Nature*, 1997, **387**, 686-688.

- 13. Q. R. Hou, Z. M. Wang and Y. J. He, *Appl Phys a-Mater*, 2005, **80**, 1807-1811.

- 14. Y. Ichikawa, M. Kobayashi, M. Sasase and T. Suemasu, *Appl Surf Sci*, 2008, **254**, 7963-7967.

- 15. T. Saito, Y. Matsumoto, M. Suzuno, M. Takeishi, R. Sasaki, T. Suemasu and N. Usami, *Appl Phys Express*, 2010, **3**.

- 16. T. Suemasu, K. Morita and M. Kobayashi, *J Cryst Growth*, 2007, **301**, 680-683.

- 17. J. Herfort, H. P. Schonherr and K. H. Ploog, *Appl Phys Lett*, 2003, **83**, 3912-3914.

- 18. Y. Sakuraba, M. Hattori, M. Oogane, Y. Ando, H. Kato, A. Sakuma, T. Miyazaki and H. Kubota, *Appl Phys Lett*, 2006, **88**.

- 19. J. P. DeGrave, A. L. Schmitt, R. S. Selinsky, J. M. Higgins, D. J. Keavney and S. Jin, *Nano Lett*, 2011, 11, 4431-4437.

- 20. E. Bucher, S. Schulz, M. C. Luxsteiner, P. Munz, U. Gubler and F. Greuter, *Appl Phys a-Mater*, 1986, 40, 71-77.

- 21. S. P. Murarka, J Vac Sci Technol, 1980, 17, 775-792.

- 22. Q. Huang, A. S. Tan, J. M. Tan, I. S. Goh, Z. Z. Dong, C. K. Ong and T. Osipowicz, *Appl Phys a-Mater*, 2003, **76**, 439-443.

- 23. M. Eizenberg and K. N. Tu, *J Appl Phys*, 1982, **53**, 6885-6890.

- 24. M. Q. Huda and K. Sakamoto, *Mat Sci Eng B-Solid*, 2002, **89**, 378-381.

- 25. S. J. Oh, J. W. Allen and J. M. Lawrence, *Phys Rev B*, 1987, **35**, 2267-2272.

- 26. K. Friemelt, J. F. DiTusa, E. Bucher and G. Aeppli, *Ann Phys-Leipzig*, 1996, 5, 175-183.

- 27. J. Thomas, J. Schumann, H. Vinzelberg, E. Arushanov, R. Engelhard, O. G. Schmidt and T. Gemming, *Nanotechnology*, 2009, **20**.

- 28. Z. A. He, D. J. Smith and P. A. Bennett, *Phys Rev Lett*, 2004, 93.

- 29. P. A. Bennett, Z. He, D. J. Smith and F. M. Ross, *Thin Solid Films*, 2011, **519**, 8434-8440.

- 30. H. C. Hsu, W. W. Wu, H. F. Hsu and L. J. Chen, *Nano Lett*, 2007, 7, 885-889.

- 31. Y. Ohira, T. Tanji, M. Yoshimura and K. Ueda, *Jpn J Appl Phys*, 2008, 47, 6138-6141.

- 32. R. T. Tung, *Mater Chem Phys*, 1992, **32**, 107-133.

- 33. A. L. Schmitt, M. J. Bierman, D. Schmeisser, F. J. Himpsel and S. Jin, *Nano Lett*, 2006, 6, 1617-1621.

- 34. Y. C. Lin, Y. Chen, A. Shaios and Y. Huang, *Nano Lett*, 2010, 10, 2281-2287.

- 35. K. Kang, S. K. Kim, C. J. Kim and M. H. Jo, *Nano Lett*, 2008, **8**, 431-436.

- 36. Y. Q. Qu,J. W. Bai,L. Liao,R. Cheng,Y. C. Lin,Y. Huang,T. Guo and X. F. Duan, *Chem Commun*, 2011, 47, 1255-1257.

- 37. K. Seo, S. Lee, H. Yoon, J. In, K. S. K. Varadwaj, Y. Jo, M. H. Jung, J. Kim and B. Kim, *Acs Nano*, 2009, **3**, 1145-1150.

- 38. K. Seo,H. Yoon,S. W. Ryu,S. Lee,Y. Jo,M. H. Jung,J. Kim,Y. K. Choi and B. Kim, *Acs Nano*, 2010, **4**, 2569-2576.

- 39. Y. C. Chou, W. W. Wu, L. J. Chen and K. N. Tu, *Nano Lett*, 2009, 9, 2337-2342.

- 40. Y. C. Chou, W. W. Wu, S. L. Cheng, B. Y. Yoo, N. Myung, L. J. Chen and K. N. Tu, *Nano Lett*, 2008, **8**, 2194-2199.

- 41. Y. C. Lin, Y. Chen, D. Xu and Y. Huang, *Nano Lett*, 2010, **10**, 4721-4726.

- 42. Y. C. Lin, K. C. Lu, W. W. Wu, J. W. Bai, L. J. Chen, K. N. Tu and Y. Huang, *Nano Lett*, 2008, **8**, 913-918.

- 43. K. C. Lu, K. N. Tu, W. W. Wu, L. J. Chen, B. Y. Yoo and N. V. Myung, *Appl Phys Lett*, 2007, 90.

- 44. W. M. Weber, L. Geelhaar, A. P. Graham, E. Unger, G. S. Duesberg, M. Liebau, W. Pamler, C. Cheze, H. Riechert, P. Lugli and F. Kreupl, *Nano Lett*, 2006, 6, 2660-2666.

- 45. J. Appenzeller, J. Knoch, M. I. Bjork, H. Riel, H. Schmid and W. Riess, *Ieee T Electron Dev*, 2008, **55**, 2827-2845.

- 46. M. Zhang, J. Knoch, J. Appenzeller and S. Mantl, *Ieee Electr Device L*, 2007, 28, 223-225.

- 47. Y. Wu, J. Xiang, C. Yang, W. Lu and C. M. Lieber, *Nature*, 2004, 430, 61-65.

- 48. W. W. Wu, K. C. Lu, K. N. Chen, P. H. Yeh, C. W. Wang, Y. C. Lin and Y. Huang, *Appl Phys Lett*, 2010, 97.

- 49. Y. C. Chou, W. W. Wu, C. Y. Lee, C. Y. Liu, L. J. Chen and K. N. Tu, *J Phys Chem C*, 2011, **115**, 397-401.

- 50. J. Kedzierski, P. Xuan, E. H. Anderson, J. Bokor, K. Tsu-Jae and H. Chenming In *Complementary silicide source/drain thin-body MOSFETs for the 20 nm gate length regime*, Electron Devices Meeting, 2000. IEDM Technical Digest. International, 2000; 2000; pp 57-60.

# 1.9. List of Figures

**Figure 1-1.** Lilienfeld, J. E. Method and apparatus for controlling electric current. US patent 1,745,175 (1925).

**Figure 1-2.** Cross sections and operation principles for an n-type junction FET and a junctionless FET. (a) A junction FET is turned on in the (strong) inversion condition, when a channel of minority carriers is formed just under the gate, and junction barriers to their flow are

reduced. (b) In contrast, the on state of a junctionless FET is obtained in 'flat band' conditions, with majority carriers travelling through a highly doped fi

Figure 1-3. Applications of silicide materials.

**Figure 1-4**. Schematic illustration of the Vapor-Liquid-Solid (VLS) process for Si NWs. (a) The formation of An eutectic molten nanoparticle on a heated Si[111] substrate. (b) Introduction of gas precursors (SiH<sub>4</sub> or SiCl<sub>4</sub>) decompose at the particle surface and Si atoms diffuse into the

nanoparticle which reaches a supersaturated state leading to the onset of ledge nucleation. (c) Continuation of ledge nucleation and propagation at the liquid-solid interface leads the growth of a Si NW with a diameter set by the starting Au nanoparticle diameter.

**Figure 1-5.** Growth technologies of silicide materials: Endotaxy: (a) Formation of NW islandson a heating substrate. (b) Plane-view TEM showing silicide nanostructures with rectangular and NW shapes.<sup>31</sup> (c) Schematic of chemical vapour deposition (CVD) method: FeSi NW was grown from single-source precursor *trans*-Fe(SiCl<sub>3</sub>)<sub>2</sub>(CO)<sub>4</sub> by chemical vapour deposition. (d) Representative SEM images of FeSi NWs.<sup>35</sup> (e) Formation of Ni silicide NWs by Solid state reaction method. (f) HRTEM image of NiSi<sub>2</sub>/Si epitaxial interface. Inset images show the fast Fourier transform (FFT) of Si[0-11] zone axis and NiSi<sub>2</sub>[0-11] zone axis.<sup>36</sup>

**Figure 1-6.** Schematic of Ni silicide NW growth by solid state reaction.<sup>49</sup> (a) Growth of fully-silicided NWs: deposit Ni film to cover the Si NW and then annealing at 550°C to transform Si NW into silicide NW. Then remove the excess Ni metal. (b) TEM image of a 20-nm NiSi NW.Inset, Fourier transform of the image showing the [10-1] zone axis of NiSi. (c) TEM image of a 32-nm NiSi NW.Inset, Fourier transform of the image indicating the [2-10] zone axis of NiSi. The scale bars in (b) and (c) are 5 nm.

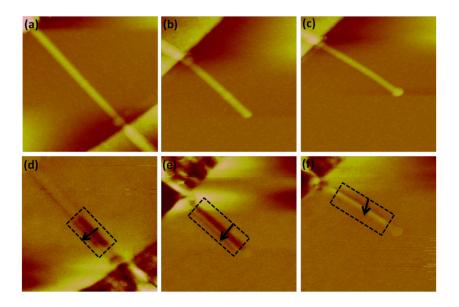

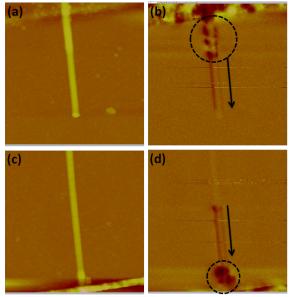

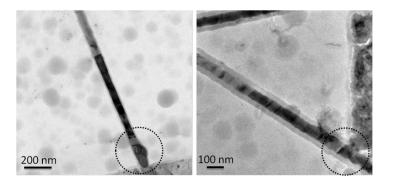

schematic shows to form a silicide/Si heterostructure and silicide NWs. (b)(c)(d) show SEM images of a patterned Si NW, partially silicided NW and fully silicided NW, respectively. (e) A TEM image of a PtSi/Si/PtSi heterostructure with only ~8 nm Si region. (f) A higher

magnification image of a PtSi/Si interface. (g) TEM image of MnSi NW and MnSi/Si interface wrapped in the oxide shell. (h) HRTEM image of MnSi/Si interface.

**Figure 1-8.** Junctionless FET and metal heterojunction FET based on SOI or NW structures. (a) The junctionless FET(b) Metal heterojunction FET: the source and drain regions are replaced by the metal contact (silicides) ErSi2 is used for n-channel contact. (c) Band diagrams of n-channel metal heterojunction device. With low gate bias (Vg < Vt), source barrier width is too wide for tunneling. With high gate bias (Vg>Vt), large electric fields induce tunneling from the source.

# 1.10. List of Tables

| Materials             | Properties                            | Resistivity<br>(μΩ cm) | Bandgap<br>(eV)                        |

|-----------------------|---------------------------------------|------------------------|----------------------------------------|

| δ-Ni <sub>2</sub> Si  | Metallic [22]                         | 22                     |                                        |

| NiSi                  | Metallic [22]                         | 10-18                  |                                        |

| NiSi <sub>2</sub>     | Metallic [23]                         | 50                     |                                        |

| C54-TiSi <sub>2</sub> | Metallic [22]                         | 14                     |                                        |

| Co <sub>2</sub> Si    | Metallic (Ferromagnet) [24]           | 40                     |                                        |

| CoSi                  | Metallic (diamagnetic semimetal) [22] | 120                    |                                        |

| CoSi <sub>2</sub>     | Metallic [22]                         | 24                     |                                        |

| Pd <sub>2</sub> Si    | Metallic [22]                         | 30                     |                                        |

| MoSi <sub>2</sub>     | Metallic [22]                         | 100                    |                                        |

| WSi <sub>2</sub>      | Metallic [22]                         | 70                     |                                        |

| MnSi                  | Metallic (Helicalmagnet) [25]         | 220                    |                                        |

| MnSi <sub>1.7</sub>   | Semiconducting [25]                   | 4100                   | 0.45-0.47 Indirect<br>0.78-0.83 Direct |

| PtSi                  | Metallic [22]                         | 28                     |                                        |

| Pt <sub>2</sub> Si    | Metallic [22]                         | 6.5                    |                                        |

| ErSi <sub>2</sub>     | Metallic [26]                         | 30                     |                                        |

| CrSi <sub>2</sub>     | Semiconducting [22]                   | 600                    | 0.35-0.67 Indirect<br>0.5-0.9 Direct   |

| β-FeSi <sub>2</sub>   | Semiconducting [12]                   | > 1000                 | 0.83-0.89 Indirect<br>0.5-0.9 Direct   |

| FeSi                  | Semiconducting [27,28]                | 300                    | 0.05                                   |

| Fe₃Si                 | Metallic (Ferromagnet) [29]           | 70                     |                                        |

**Table 1-1.** Electronic and optical properties of silicide materials. <sup>22-29</sup>

| Materials                       | Schottky Barrier<br>Height (eV) | Materials           | Schottky Barrier<br>Height (eV) |

|---------------------------------|---------------------------------|---------------------|---------------------------------|

| TiSi <sub>2</sub>               | 0.60                            | HfSi                | 0.53                            |

| VSi <sub>2</sub>                | 0.64                            | TaSi <sub>2</sub>   | 0.59                            |

| CrSi <sub>2</sub>               | 0.57                            | WSi <sub>2</sub>    | 0.65                            |

| MnSi                            | 0.65                            | ReSi <sub>2</sub>   | 0.77                            |

| MnSi <sub>1.7</sub>             | 0.67                            | OsSi <sub>1.8</sub> | 0.85                            |

| FeSi <sub>2</sub>               | 0.68                            | IrSi                | 0.93                            |

| CoSi                            | 0.68                            | Ir2Si 3             | 0.85                            |

| CoSi <sub>2</sub>               | 0.64                            | IrSi₃               | 0.94                            |

| Ni <sub>2</sub> Si              | 0.66                            | Pt₂Si               | 0.85                            |

| NiSi                            | 0.65                            | PtSi                | 0.88                            |

| NiSi 2                          | 0.66                            | SiAu                | 0.80                            |

| YSi <sub>1.7</sub>              | 0.39                            | GdSi <sub>2</sub>   | 0.37                            |

| ZrSi <sub>2</sub>               | 0.55                            | DySi 2              | 0.37                            |

| NbSi <sub>2</sub>               | 0.63                            | HoSi <sub>2</sub>   | 0.37                            |

| MoSi <sub>2</sub>               | 0.65                            | ErSi <sub>2</sub>   | 0.39                            |

| Ru <sub>2</sub> Si <sub>3</sub> | 0.72                            | ErSi <sub>1.7</sub> | 0.40                            |

| RhSi                            | 0.75                            |                     |                                 |

| Pd₂Si                           | 0.71                            |                     |                                 |

**Table 1-2.** Work function of silicide materials to the n-type silicon.<sup>22</sup>

# Chapter 2: Single Crystalline PtSi Nanowires, PtSi/Si/PtSi Nanowire Heterostructures, and Nanodevices

### 2.1. Introduction

One-dimensional nanostructures, such as nanotubes and nanowires, are attractive building blocks for nanoelectronics since their morphology, size, and electronic properties make them suitable for fabricating both active nanodevice elements and device-to-device interconnects. <sup>1-7</sup> In particular, substantial efforts have been made for the development of nanoscale transistors based on silicon nanowires<sup>8,9</sup> due to their potential to replace conventional planar metal-oxidesemiconductor field-effect transistors (MOSFET) in integrated circuits 10,11 or to open new opportunities in flexible macroelectronics<sup>12–14</sup> and highly sensitive biosensors.<sup>15,16</sup> Making reliable electrical contact to individual nanowire devices is one of the key factors that determine the device performance and reliability. Lithographically defined metal contacts are most often used in silicon nanowire transistors, which is, however, limited in at least two respects: (1) the much larger size scale of lithographically defined metal contact limits the scaling potential of the silicon nanowire devices; (2) the interface states between the silicon nanowire and metal contact often lead to Fermi-level pinning and result in a relatively large Schottky barrier for the device. 17 As a result, doped nanowires with a certain doping concentration (e.g., >10<sup>17</sup>/cm3) are typically used in order to make satisfactory source drain contact, which prevent one from making highperformance transistors based on intrinsic silicon nanowires. The formation of metal silicide nanowires and silicide/ silicon heterostructures represents an interesting approach to address the above problems. Nickel silicide has been reported<sup>18-20</sup> and is being used as a contact material for

silicon nanowire transistors. 18,21,22 Being chemically stable in ambient or oxidizing environment, platinum is an interesting interconnecting material for nanoscale electronics where surface to volume ratio is large and the surface chemical stability is important. Additionally, the formation of platinum silicide (PtSi) is of interest because it has a very low barrier height of ~0.2 eV on the valence band of silicon and is an attractive choice for ohmic contacts to p-channel Si nanowire transistors.<sup>23</sup> Platinum silicide nanowires have been reported recently, but without detailed characterization of their properties.<sup>24</sup> Here, we report the formation of single crystal PtSi nanowires, PtSi/Si/PtSi nanowire heterostructures, and nanodevices from such heterostructures. Scanning electron microscopy (SEM) studies show that silicon nanowires can be converted into single crystal PtSi nanowires through controlled reactions between lithographically defined Pt pads and Si nanowires. High-resolution transmission electron microscope (HRTEM) studies show that PtSi/Si/PtSi heteorstructure has clean, atomically sharp interfaces with an epitaxial relationship of Si[1-10]//PtSi[010] and Si(111)// PtSi(101). Electrical measurements show that the pure PtSi nanowires have a low resistivity of ~28.6  $\mu\Omega$ ·cm, and high failure current density >10<sup>8</sup>A/cm<sup>2</sup>. Furthermore, using single crystal PtSi/Si/PtSi nanowire heterostructures with low PtSi/Si energy barrier, we have fabricated high-performance p-channel enhancement mode fieldeffect transistors from intrinsic silicon nanowires, in which the source and drain contacts are defined by the metallic PtSi nanowire regions and the gate length is defined by the Si nanowire region.

# 2.2. Experimental

Silicon nanowires were prepared on a silicon wafer by the vapor–liquid–solid method using Au clusters as the catalyst.<sup>25–27</sup> The silicon nanowires are typically single crystals with diameters

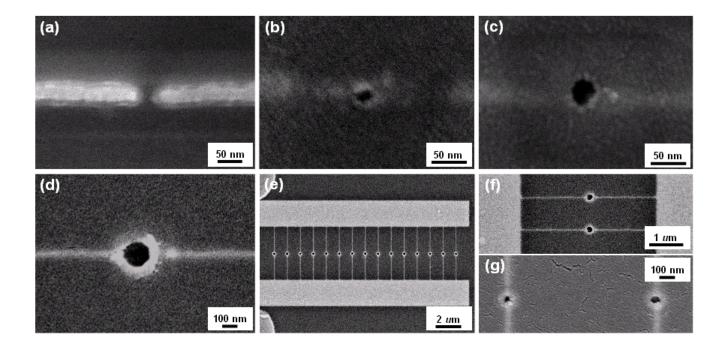

ranging from 30 to 60 nm, lengths greater than 10  $\mu$ m, and growth axes along [111] directions. The Si nanowire device with platinum contacts was fabricated on Si/Si<sub>3</sub>N<sub>4</sub> substrate using ebeam lithography and e-beam evaporation (Figure 2-1a). Prior to platinum deposition, the sample was etched in buffered hydrofluoric acid for 5 s to remove native oxide in the contact region. To allow platinum to diffuse into the silicon nanowire and form partially (Figure 2-1b) or fully silicidized (Figure 2-1c) PtSi nanowire, the device was annealed in forming gas at 520 °C with a rapid thermal processor for various periods of time. Before annealing, a SEM image of the device shows a uniform contrast along the axis of the nanowire (Figure 2-1d). After the device was annealed in forming gas for 30 s, clear contrast developed along the wire axis with two brighter sections emerging from both ends of the nanowire near the platinum pads (Figure 2-1e). A darker section remains between the two brighter sections, corresponding to the unreacted silicon nanowire. These results suggest that a PtSi/Si/PtSi nanowire heterostructure is formed through reaction between the silicon nanowire and two platinum contact pads. This is attributed to the fact that many platinum atoms are able to dissolve into silicon through the contacts between silicon nanowire and platinum pads so that supersaturation can be reached; thereby, nucleation and growth of platinum silicide occur at both platinum pads. Upon further annealing, the two brighter sections (PtSi) converged, and the darker section (Si) disappeared. At this point, all silicon is consumed and a silicon nanowire is fully transformed into a PtSi nanowire (Figure 2-1f). Occasionally, a curved section is seen near the contact pads (Figure 2-1f), which can be attributed to strain resulting from the volume expansion during the silicidation process. Transformation of Si nanowire into PtSi nanowires roughly increases the volume by 50%. However, our studies indicate that no significant diameter increase is observed (<10%). For mass conservation, this means that the silicon atom back diffusion is present in our system, in which

silicon atoms diffuse toward platinum pads and get consumed in or near the pads. Additional studies are required to further understand this phenomenon.

### 2.3. Results & Discussion

# 2.3.1. Epitaxial relationship of PtSi formation within a silicon nanowire

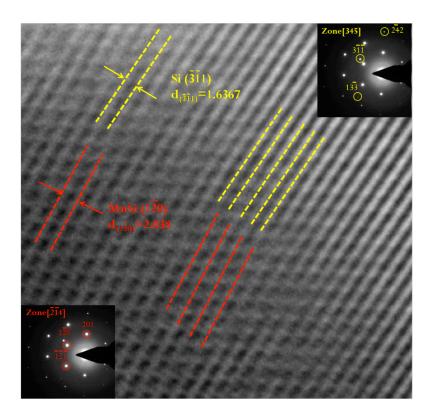

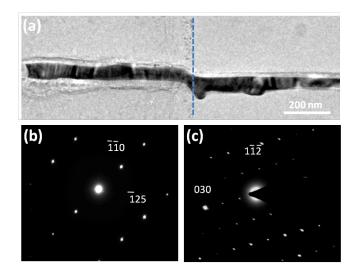

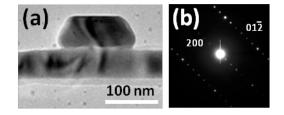

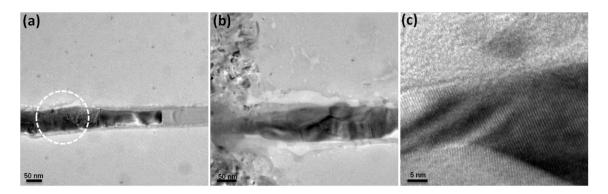

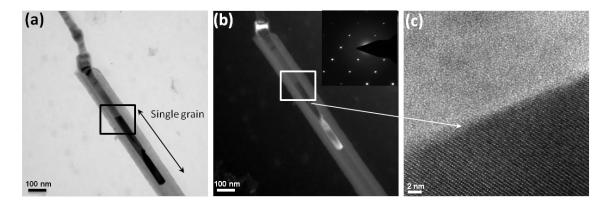

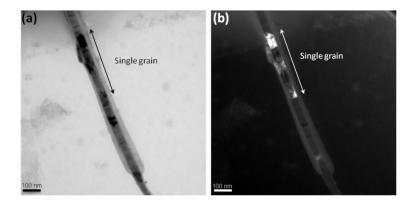

To understand the formation and structure of the PtSi/Si/PtSi nanowire heterostructure, we have used lattice resolved transmission electron microscopy (TEM) images to determine the crystal structure and atomic epitaxial relationships. To prepare TEM samples, silicon nanowires devices were prepared on silicon grids with a square opening covered with a window of a glassy Si<sub>3</sub>N<sub>4</sub> film. The thickness of the Si<sub>3</sub>N<sub>4</sub> film is about 30 nm so that it is transparent to the electron beam and does not interfere with the imaging of the nanowires. Lattice resolved images were taken with a JEOL 3000F high-resolution transmission electron microscope. A high-resolution TEM (HRTEM) image (Figure 2-2a) shows that there are clean interfaces between PtSi/Si with an approximately 2 nm silicon oxide shell surrounding both the silicon and platinum silicide regions, suggesting the growth of platinum silicide nanowire is confined in the preformed native silicon oxide shell. On the basis of the TEM studies, the silicide material is identified to be single crystal PtSi phase with an orthorhombic structure with lattice constants a=0.5939 nm, b=0.5596nm, and c=0.3604 nm. A HRTEM image and its fast Fourier transform (FFT) (Figure 2b and insets) show the Si/PtSi epitaxial interface is parallel to the (111) plane of Si as well as the (101) plane of PtSi. Thus, the growth direction of PtSi is normal to the (101) plane. The crystallographic orientation relationships between Si and PtSi are Si[1-10]//PtSi[010] and Si(111)//PtSi(101). Across the epitaxial interface, the largest lattice mismatch is between the Si(002) plane (d=0.271 nm) and the PtSi(200) plane (d=0.297 nm) with a relative mismatch of about 8.8%. Notably, despite this exceedingly large lattice mismatch, no apparent dislocations or other defects are seen across the interface. These results demonstrate that a sharp and atomically smooth interface is obtained in our Si/PtSi nanowire heterostructure. In stark contrast, atomically uneven interfaces are often seen in previously reported PtSi thin films grown on silicon (111) surfaces due to large lattice mismatch. The clean and sharp interface in nanowire heterostructures might be attributed to increased tolerance of lattice strain and the difficulty to nucleate a dislocation at nano-scale, which is an interesting subject for further investigations. The formation of atomically sharp PtSi/Si/PtSi heterostructures can open many exciting opportunities in nanoscale device engineering. For example, through controlled reactions, the length of the silicon region in nanowire PtSi/Si/PtSi heterostructures can be precisely controlled down to the sub-10-nm regime (Figure 2-2c). This is significant since the sub-10-nm length scale here is defined by controlled chemical reaction rather than by lithography and thereby can open new opportunities for sub-10-nm device engineering when the process is further optimized. To explore single-crystal PtSi nanowires and atomically sharp PtSi/Si/PtSi nanoheterostructures in nanoscale electronics, it is important to understand their electrical transport characteristics.

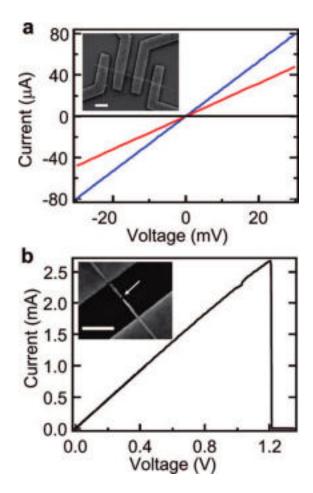

# 2.3.2. Electrical transport properties of single crystal PtSi nanowires

We have carried out the electrical transport studies on individual nanowires before and after PtSi formation. Current–voltage (I-V) measurements show that as-fabricated intrinsic Si nanowire devices with platinum contacts and partly silicidized nanowires exhibit exceedingly high resistance essentially beyond our instrument measurement range (>1 T $\Omega$ ) (black line in Figure 2-

3a). Importantly, the fully silicidized nanowires exhibit perfect linear current-voltage relation, with current typically exceeding 100  $\mu$ A at 100 mV of bias voltage. The two-terminal linear I-Vcurve of a 50 nm PtSi nanowire device gives a linear resistance of 627  $\Omega$  (red line in Figure 2-3a). At this low resistance, contact resistance and electrical lead resistance may start to contribute to a significant fraction of the total resistance. To exclude this extrinsic series resistance and accurately determine the PtSi nanowire resistance, we have carried out four-terminal measurement (inset and blue line in Figure 2-3a), which gives a resistance of 376  $\Omega$  for the device. The high current and low resistance observed in the annealed device clearly suggests the metallic behavior of PtSi nanowires. Indeed, calculation of the PtSi resistivity based on fourterminal measurement gives a value of 28.6  $\mu\Omega$  cm. Significantly, this value compares favorably to the previously reported values in PtSi thin film materials (45–68  $\mu\Omega$ ·cm), which can be attributed to the single crystalline and virtually defect-free structure in our PtSi nanowires as opposed to polycrystalline and defect-prone PtSi films. To explore the PtSi nanowire as metallic interconnects for silicon nanodevices, it is also important to characterize the maximum current density of individual nanowires. Our measurement shows that an individual PtSi nanowire can typically carry more than 1 mA current before electrical breakdown. For example, the currentvoltage curve of a 45 nm PtSi nanowire at large bias shows that the current reaches 2.7 mA before electrical breakdown (Figure 2-3b). This high current through a single nanowire corresponds to a current density  $2 \times 10^8 \text{A/cm}^2$ , comparable to recently reported values in nickel silicide nanowires. 18 SEM observation of the failed device shows the breakdown occurs around the center of the nanowire (inset Figure 2-3b), where one expects the least heat dissipation and highest temperature.

# 2.3.3. PtSi/i-Si/PtSi nanowire heterostructures as high performance p-channel enhancement mode transistors