## UC San Diego UC San Diego Electronic Theses and Dissertations

## Title

Envelope amplifier design for wireless base-station power amplifiers

## Permalink

https://escholarship.org/uc/item/5w4091vx

## **Author** Hsia, Chin

Publication Date 2010

Peer reviewed|Thesis/dissertation

#### UNIVERSITY OF CALIFORNIA, SAN DIEGO

### **Envelope Amplifier Design for Wireless Base-Station Power Amplifiers**

A dissertation submitted in partial satisfaction of the requirements for the degree Doctor of Philosophy

in

Electrical Engineering (Electronic Circuits and Systems)

by

Chin Hsia

Committee in charge:

Professor Peter M. Asbeck, Chair Professor Prabhakar Bandaru Professor William Griswold Professor Lawrence E. Larson Professor Paul Yu

2010

Copyright Chin Hsia, 2010 All rights reserved. The dissertation of Chin Hsia is approved, and it is acceptable in quality and form for publication on microfilm and electronically:

Chair

University of California, San Diego

2010

## DEDICATION

To my parents, my family for their endless love and support

## EPIGRAPH

The Tao can be explained, but not in a normal way

— Laozi

## TABLE OF CONTENTS

| Signature Page  | e       |          |           |        |       | •••    |      | <br>• • | • • |     |     |   | • | <br>iii  |

|-----------------|---------|----------|-----------|--------|-------|--------|------|---------|-----|-----|-----|---|---|----------|

| Dedication      |         |          |           |        |       |        |      | <br>    |     |     |     |   |   | <br>iv   |

| Epigraph        | · · · · |          |           |        | •••   | •••    |      | <br>••  |     |     |     |   | • | <br>v    |

| Table of Conte  | ents .  |          |           |        |       |        |      | <br>••  |     | • • |     |   | • | <br>vi   |

| List of Figures | 8       |          |           |        |       |        |      | <br>    |     |     |     |   | • | <br>ix   |

| List of Tables  |         |          |           |        |       |        |      | <br>    |     |     |     |   |   | <br>xiv  |

| Acknowledge     | ments   |          |           |        |       |        |      | <br>    |     |     |     |   |   | <br>XV   |

| Vita            | ••••    |          |           |        |       |        |      | <br>    |     |     |     |   |   | <br>xvii |

| Abstract of the | e Diss  | ertation |           |        |       |        |      | <br>    |     |     |     |   | • | <br>XX   |

| Chapter 1       | Intro   | duction  |           |        |       |        |      | <br>    |     |     |     |   |   | <br>1    |

|                 | 1.1     | Base S   | tation Po | ower A | Amp   | lifier | s.   | <br>    |     |     |     |   |   | <br>1    |

|                 | 1.2     | •        | fficiency |        | -     |        |      |         |     |     |     | - |   | 5        |

|                 |         | 1.2.1    | Dohert    | y Pow  | ver A | mpli   | fier | <br>    |     |     |     |   |   | <br>5    |

|                 |         | 1.2.2    | LINC F    | ower   | Amj   | plifie | er.  | <br>    |     |     |     |   |   | <br>7    |

|                 |         | 1.2.3    | EER Po    | ower A | Amp   | lifier | •    | <br>    |     |     |     |   | • | <br>7    |

|                 |         | 1.2.4    | ET Pov    | ver Ai | mplif | ier    |      | <br>• • | ••• |     |     |   |   | <br>9    |

|                 | 1.3     | Scope    | of Disse  | rtatio | n     |        |      | <br>••• |     |     | ••• |   | • | <br>10   |

| Chapter 2       | Enve    | lope Tra | acking P  | ower   | Amp   | lifie  | r.   | <br>    |     |     |     |   |   | <br>12   |

|           | 2.1  | Introdu   | uction                                                        | 12 |

|-----------|------|-----------|---------------------------------------------------------------|----|

|           | 2.2  | Envelo    | pe Tracking Techniques                                        | 12 |

|           | 2.3  | ET Pov    | wer Amplifier Efficiency                                      | 15 |

|           | 2.4  | Envelo    | pe Amplifier Architecture                                     | 17 |

|           | 2.5  | Envelo    | pe Amplifier Modeling                                         | 18 |

|           | 2.6  | Envelo    | pe Amplifier Efficiency                                       | 27 |

|           | 2.7  | Summa     | ary                                                           | 38 |

|           | 2.8  | Acknow    | wledgements                                                   | 40 |

| Chapter 3 | Enve | elope An  | nplifier Design for High Voltage Applications                 | 41 |

|           | 3.1  | Introdu   | iction                                                        | 41 |

|           | 3.2  | Design    | Issues for High Voltage Envelope Amplifier                    | 42 |

|           | 3.3  | High V    | Voltage Envelope Amplifier Design                             | 44 |

|           |      | 3.3.1     | Wideband High Voltage Op-Amp Design and Imple-<br>mentation   | 47 |

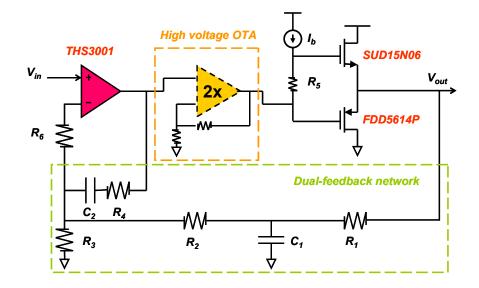

|           |      | 3.3.2     | Wideband High Voltage Linear Stage                            | 64 |

|           |      | 3.3.3     | Wideband High Voltage Sensor Stage                            | 66 |

|           |      | 3.3.4     | High Voltage Switcher Stage                                   | 70 |

|           | 3.4  | High V    | Voltage ET PA Experimental Results                            | 74 |

|           |      | 3.4.1     | High Voltage Envelope Amplifier Measurement                   | 74 |

|           |      | 3.4.2     | High Voltage Envelope Tracking Power Amplifier<br>Measurement | 76 |

|           | 3.5  | Summa     | ary                                                           | 81 |

|           | 3.6  | Acknow    | wledgements                                                   | 84 |

| Chapter 4 | Dua  | l-switche | er Envelope Amplifier                                         | 85 |

|           | 4.1  | Introdu   | uction                                                        | 85 |

|              | 4.2 | 2 DSP Switcher Control |                                                                  |  |

|--------------|-----|------------------------|------------------------------------------------------------------|--|

|              | 4.3 | Dual-s                 | switcher Envelope Amplifier                                      |  |

|              |     | 4.3.1                  | Dual-switcher Envelope Amplifier Architecture 93                 |  |

|              |     | 4.3.2                  | Dual-switcher Design Synthesis                                   |  |

|              |     | 4.3.3                  | Experimental results                                             |  |

|              | 4.4 | Envelo                 | ope Tracking Power Amplifier Measurement 106                     |  |

|              | 4.5 | Summ                   | ary                                                              |  |

|              | 4.6 | Ackno                  | owledgements                                                     |  |

| Chapter 5    | Con | clusion                | and Future work                                                  |  |

|              | 5.1 | Disser                 | tation Summary 117                                               |  |

|              | 5.2 | Future                 | Work                                                             |  |

|              |     | 5.2.1                  | Envelope Tracking System Modeling                                |  |

|              |     | 5.2.2                  | Fully Integrated High Voltage Linear Stage 119                   |  |

|              |     | 5.2.3                  | A Multi-switcher Envelope Amplifier with Closed-<br>loop Control |  |

|              |     | 5.2.4                  | Hybrid Envelope Amplifier Architecture for Other<br>Applications |  |

| References . |     |                        |                                                                  |  |

### LIST OF FIGURES

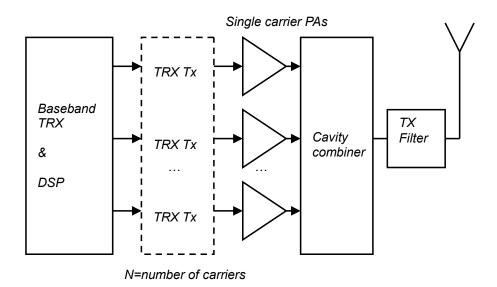

| Figure 1.1:  | Single Carrier Combined Power Amplifier [1]                                                                                                                                                          | 3  |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

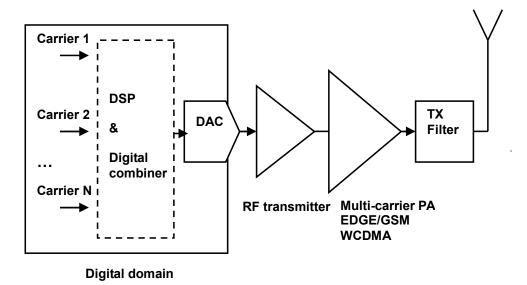

| Figure 1.2:  | Multiple Carrier Power Amplifier Architecture [2]                                                                                                                                                    | 4  |

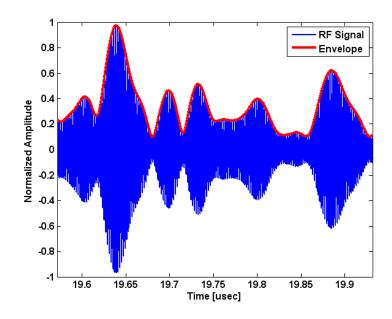

| Figure 1.3:  | Multiple Carrier RF signal                                                                                                                                                                           | 5  |

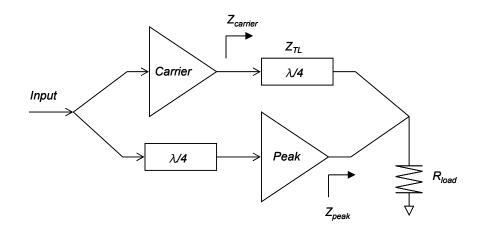

| Figure 1.4:  | Doherty Power Amplifier [3]                                                                                                                                                                          | 6  |

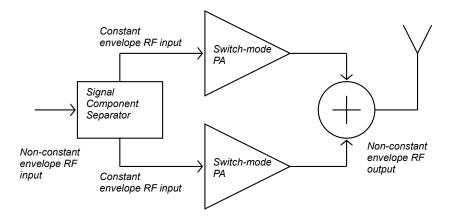

| Figure 1.5:  | LINC Power Amplifier [1]                                                                                                                                                                             | 7  |

| Figure 1.6:  | Envelope Elimination and Restoration (EER) PA [4]                                                                                                                                                    | 8  |

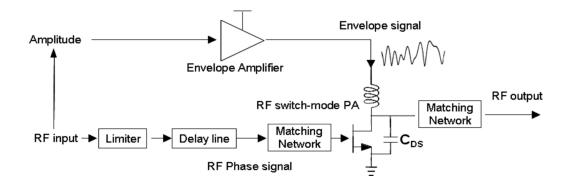

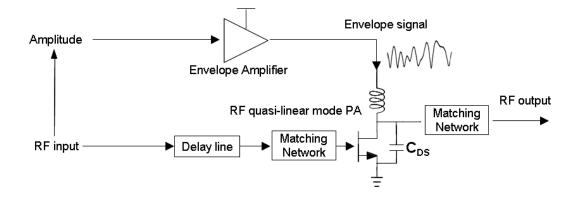

| Figure 1.7:  | Envelope Tracking (ET) PA [5, 6]                                                                                                                                                                     | 9  |

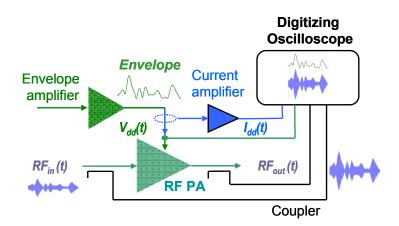

| Figure 2.1:  | Envelope Tracking System [6]                                                                                                                                                                         | 14 |

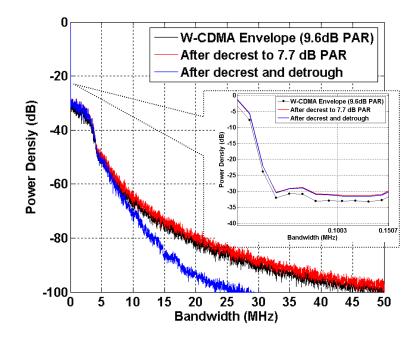

| Figure 2.2:  | W-CDMA Envelope Signal Power Spectrum Before and After De-<br>troughing and Decresting                                                                                                               | 14 |

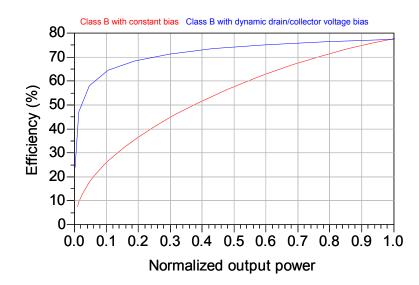

| Figure 2.3:  | Comparison of Simulated Efficiency versus Output Power between<br>Class B Power Amplifier and Class B with Ideal ET Operation                                                                        | 17 |

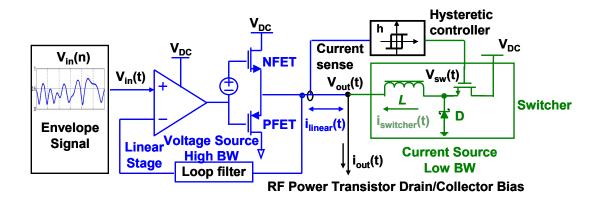

| Figure 2.4:  | Envelope Amplifier Architecture [6]                                                                                                                                                                  | 19 |

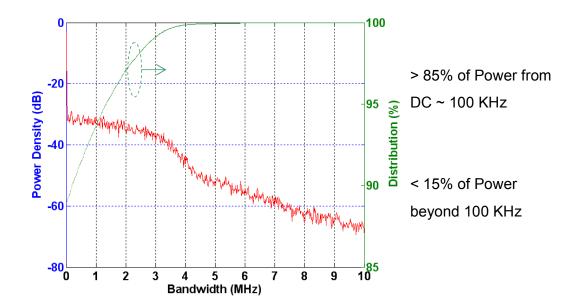

| Figure 2.5:  | W-CDMA Envelope Signal Characteristics                                                                                                                                                               | 19 |

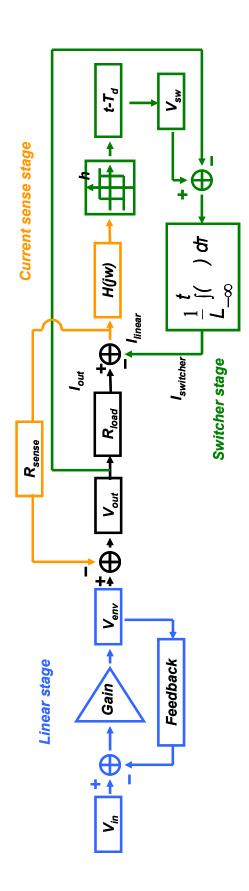

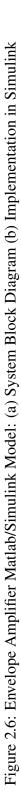

| Figure 2.6:  | Envelope Amplifier Matlab/Simulink Model: (a) System Block Di-<br>agram (b) Implementation in Simulink                                                                                               | 21 |

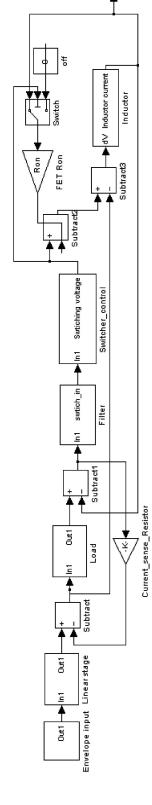

| Figure 2.7:  | EDGE signal: (a) IF signal (b) Envelope signal                                                                                                                                                       | 22 |

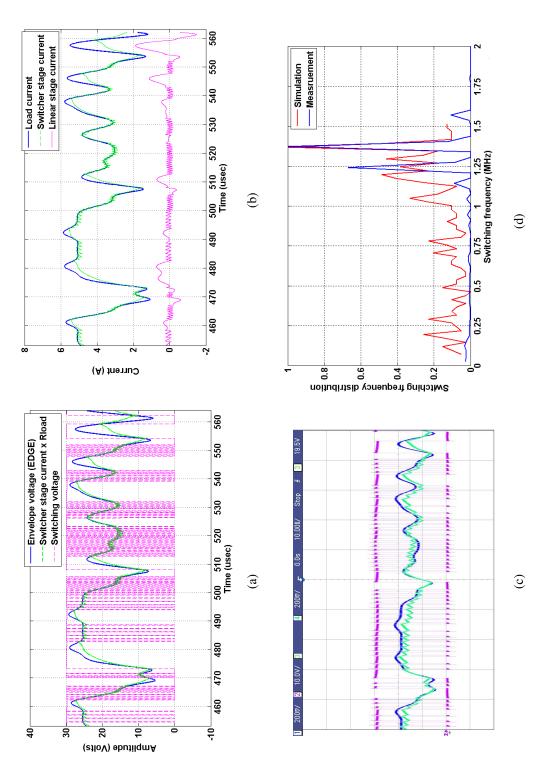

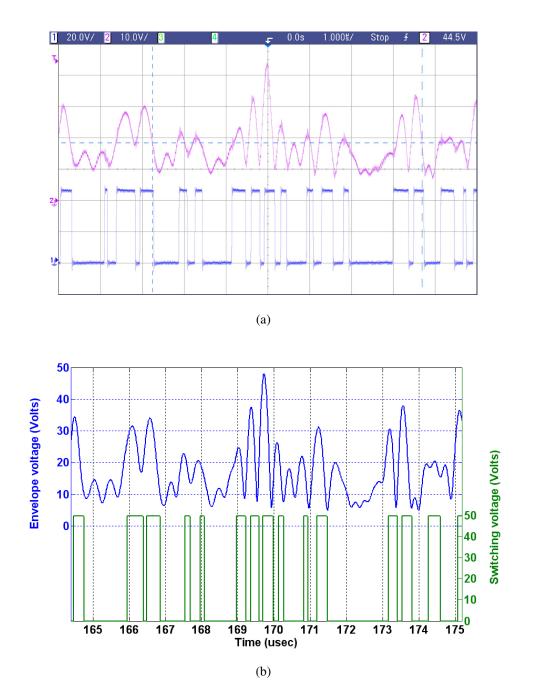

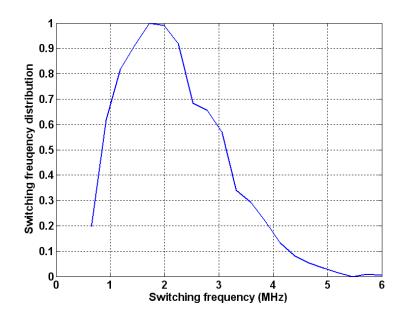

| Figure 2.8:  | Envelope Amplifier Running EDGE Signal: (a) Simulation (b) Simulation (c) Experimental results (Ch1,Ch4: 10 mV = 100 mA) (d) Switching Frequency Distribution comparison.                            | 24 |

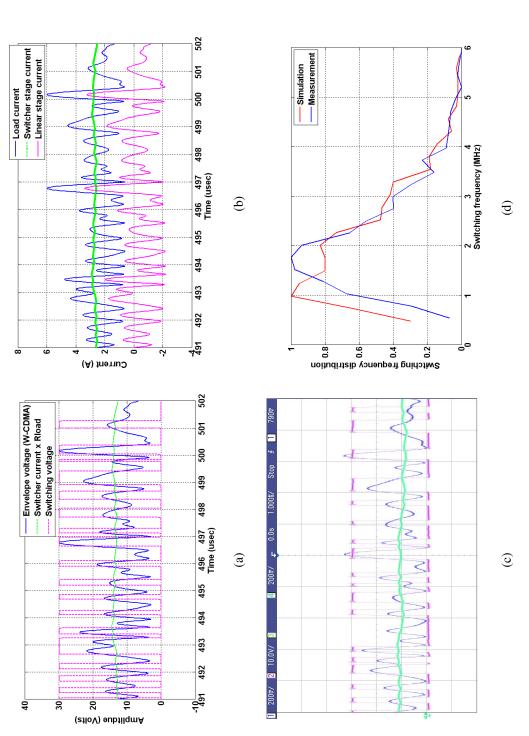

| Figure 2.9:  | Envelope Amplifier Running WCDMA Signal: (a) Simulation (b)<br>Simulation (c) Experimental results (Ch1,Ch4: 10 mV = 100 mA)<br>(d) Switching Frequency Distribution Comparison. $\dots \dots \dots$ | 26 |

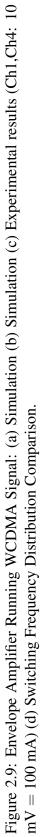

| Figure 2.10: | Envelope Amplifier Start-up Condition: (a) EDGE signal (b) W-CDMA signal.                                                                                                                            | 28 |

| Figure 2.11: | (a) Switcher Stage Schematic; (b) High Side switch-FET Gate Charge Diagram [7]                                                                                                                       | 31 |

| Figure 2.12: | <ul><li>Envelope Amplifier Loss Estimation: (a) EDGE signal (3.2 dB PAR)</li><li>(b) W-CDMA signal (7.7 dB PAR)</li></ul>            | 36 |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 2.13: | Envelope Amplifier Hybrid PCB Design [6, 8, 9]                                                                                       | 38 |

| Figure 2.14: | Simulated and Measured Performance Comparisons of the Enve-<br>lope Amplifier using W-CDMA signals (a) Efficiency; (b) Power<br>loss | 39 |

| Figure 2.15: | Measured Efficiency versus PAR of the Envelope Signals                                                                               | 40 |

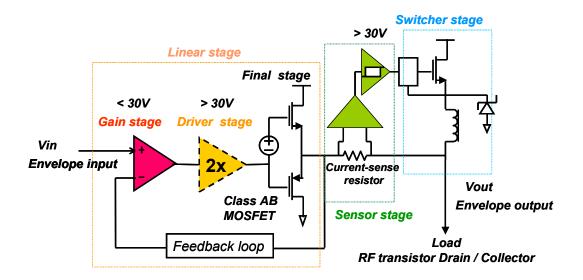

| Figure 3.1:  | High Voltage Envelope Amplifier Schematic                                                                                            | 43 |

| Figure 3.2:  | High Voltage Envelope Amplifier Simulation                                                                                           | 44 |

| Figure 3.3:  | High Voltage OTA Toptology: (a) Folded-cascode Input Stage (b)<br>Source Cross-coupled Differential Pairs.                           | 48 |

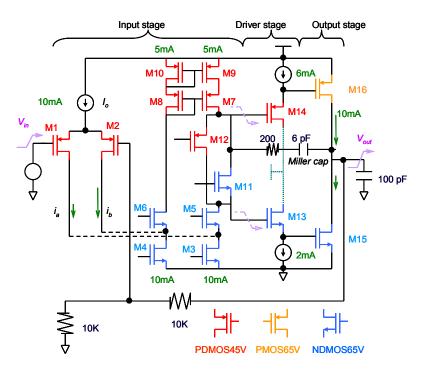

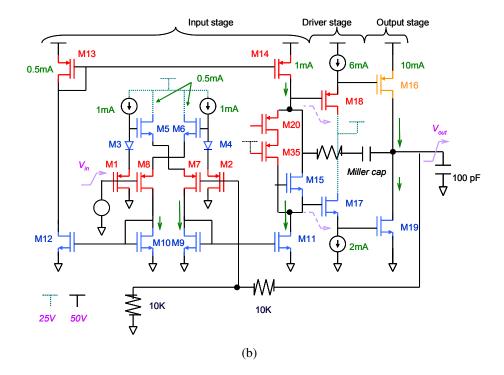

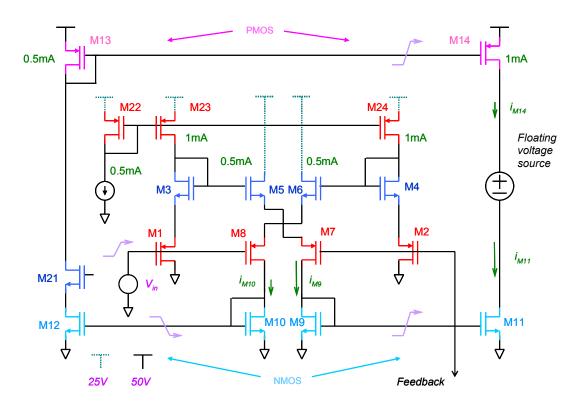

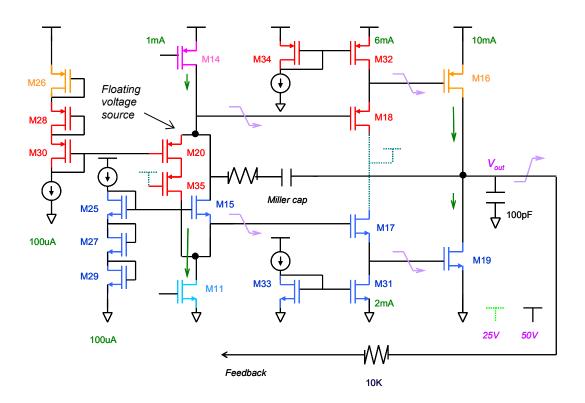

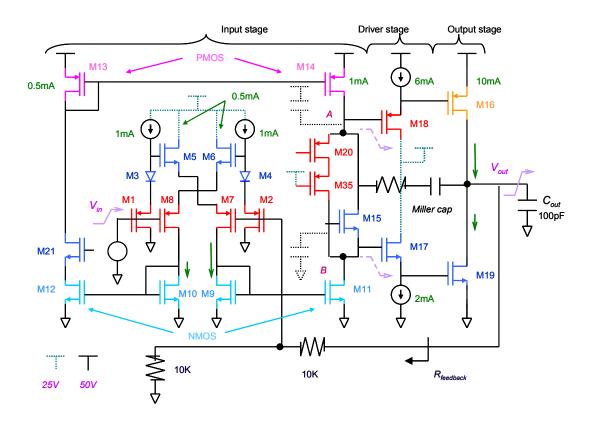

| Figure 3.4:  | High Voltage OTA Cross-couple Input Stage                                                                                            | 52 |

| Figure 3.5:  | High Voltage OTA Driver and Output Stage                                                                                             | 53 |

| Figure 3.6:  | High Voltage OTA Full Schematic                                                                                                      | 54 |

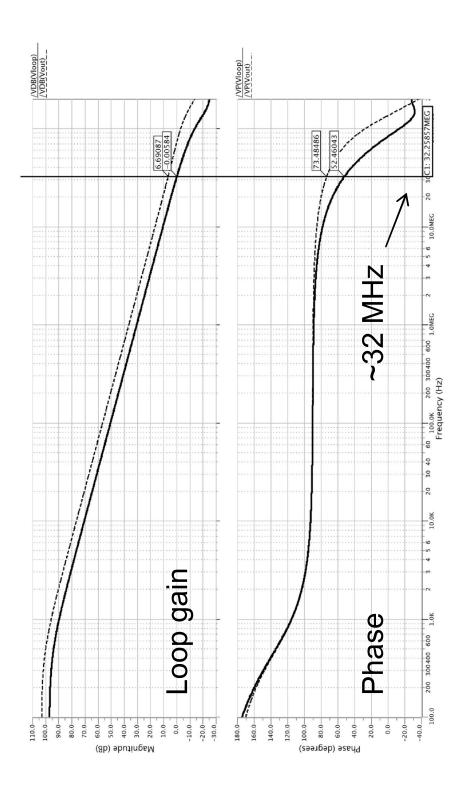

| Figure 3.7:  | High Voltage OTA Loop Gain                                                                                                           | 56 |

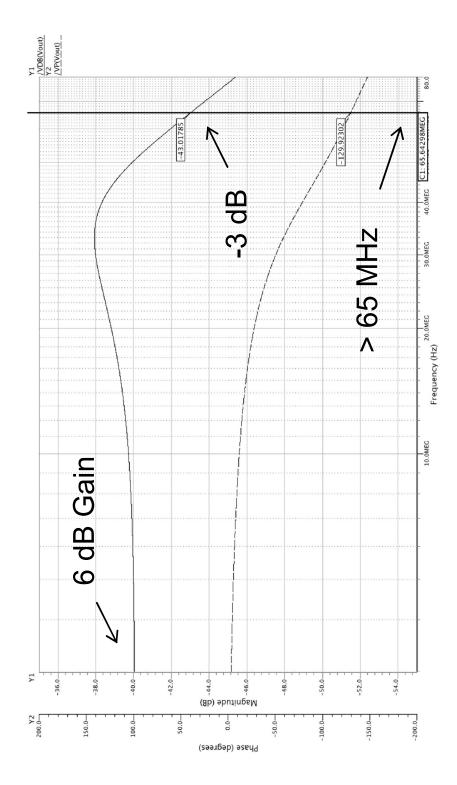

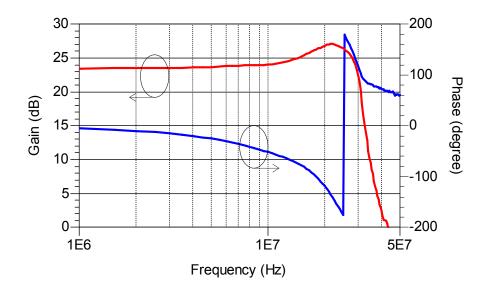

| Figure 3.8:  | High Voltage OTA Frequency Response                                                                                                  | 57 |

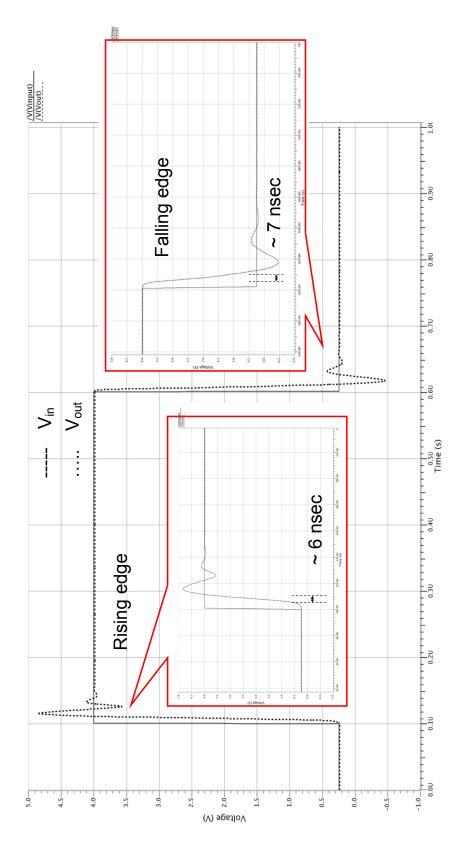

| Figure 3.9:  | High Voltage OTA Transient Step Simulation                                                                                           | 59 |

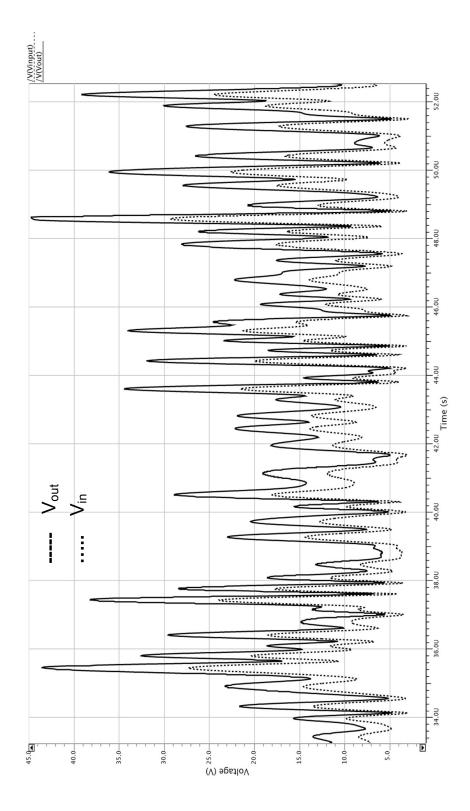

| Figure 3.10: | High Voltage OTA Transient Simulation using a 7.7 dB PAR W-CDMA Signal                                                               | 60 |

| Figure 3.11: | High Voltage OTA Transient Simulation Input/Output Comparisons                                                                       | 61 |

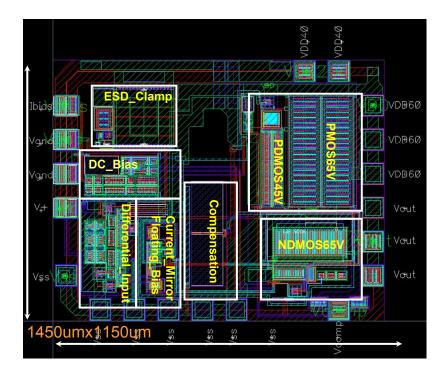

| Figure 3.12: | High Voltage OTA Layout                                                                                                              | 61 |

| Figure 3.13: | High Voltage OTA Package and Test Fixture                                                                                            | 62 |

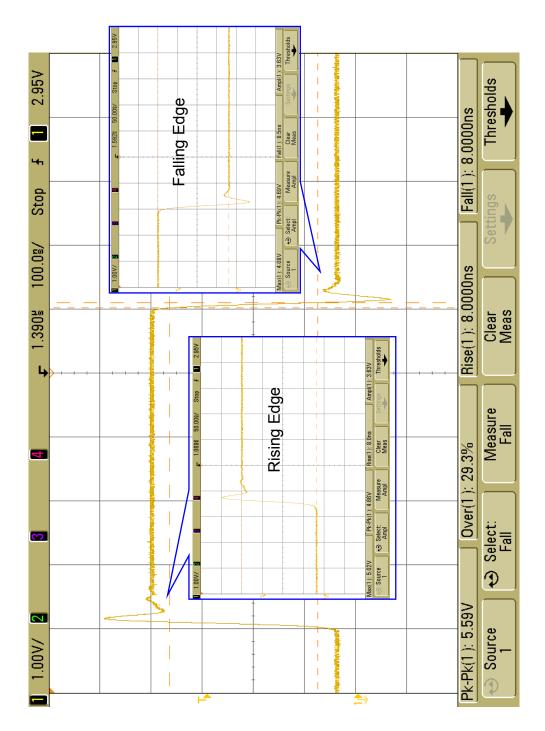

| Figure 3.14: | High Voltage OTA Transient Step Measurement                                                                                          | 63 |

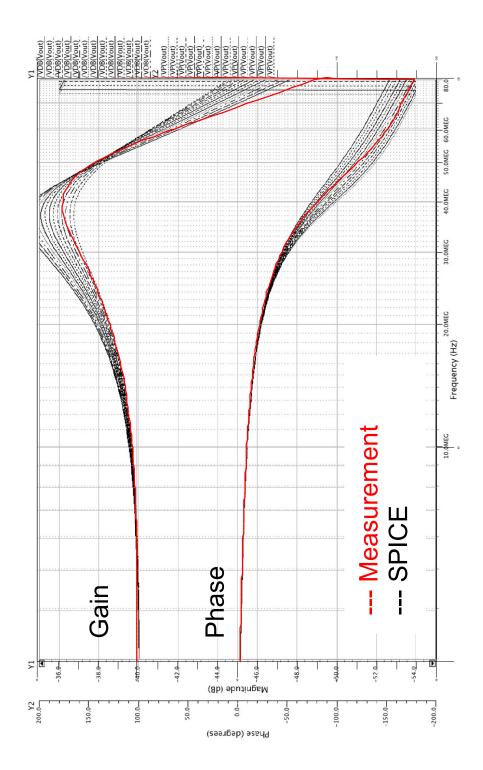

| Figure 3.15: | High Voltage OTA Frequency Response: Measurement versus Sim-<br>ulation                                                              | 65 |

| Figure 3.16: | High Voltage Linear Stage Schematic                                                                                                  | 66 |

| Figure 3.17: | Measured High Voltage Linear Stage Frequency Response                                                                                | 67 |

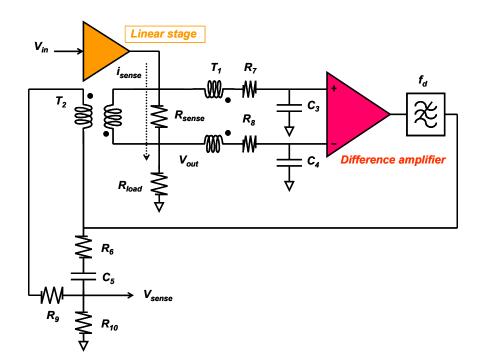

| Figure 3.18: | High Voltage Current-sense Stage Schematic                                                                                           | 68 |

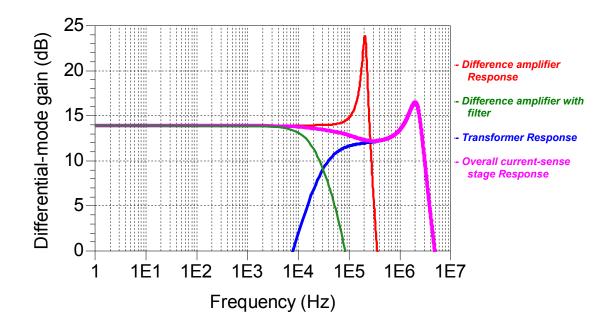

| Figure 3.19: | Simulated High Voltage Current-sense Stage Differential Gain                                                                                                                                                        | 69 |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

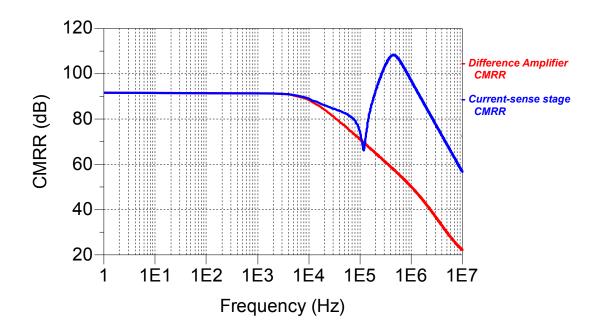

| Figure 3.20: | Simulated High Voltage Current-sense Stage CMRR                                                                                                                                                                     | 69 |

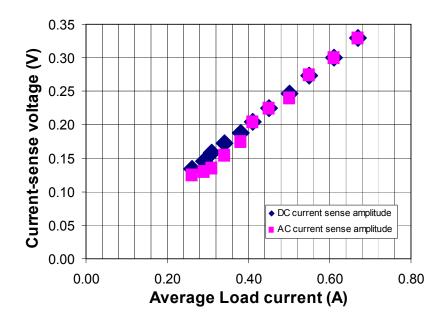

| Figure 3.21: | Measured High Voltage Current-sense Stage Performance                                                                                                                                                               | 70 |

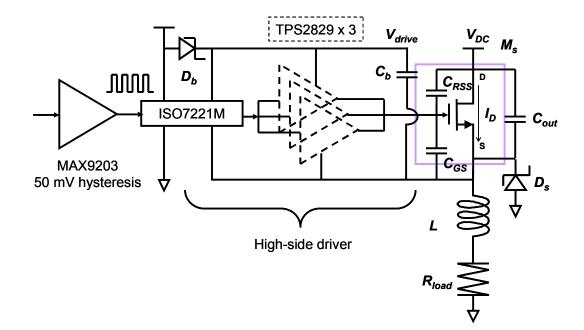

| Figure 3.22: | High Voltage Switcher Full Schematic                                                                                                                                                                                | 73 |

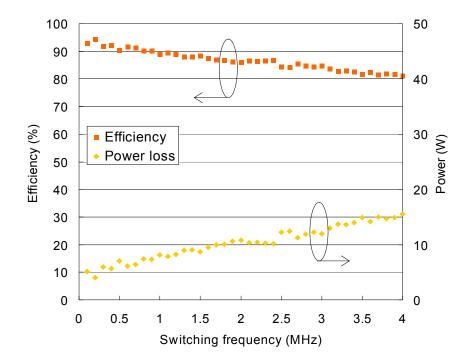

| Figure 3.23: | Measured High Voltage Switcher Efficiency and Power Loss                                                                                                                                                            | 74 |

| Figure 3.24: | High Voltage Envelope Amplifier                                                                                                                                                                                     | 75 |

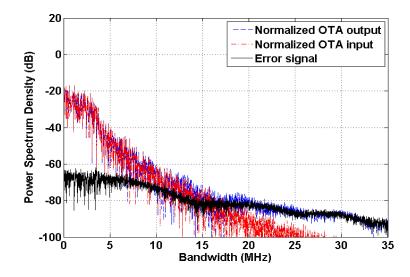

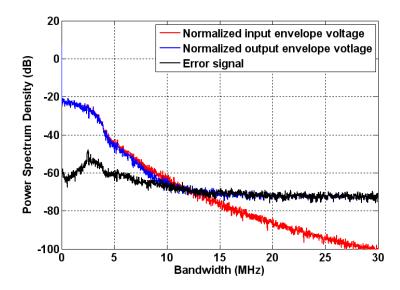

| Figure 3.25: | High Voltage Envelope Amplifier Output versus Input Signal Spec-<br>trum (W-CDMA)                                                                                                                                   | 76 |

| Figure 3.26: | High Voltage Envelope Amplifier with W-CDMA signal: (a) Measurement; (b) Simulation results                                                                                                                         | 77 |

| Figure 3.27: | High Voltage Envelope Amplifier Switching Frequency Distribution                                                                                                                                                    | 78 |

| Figure 3.28: | Eudyna EGN21A090IV-A Power Amplifier Test Fixture [10]                                                                                                                                                              | 79 |

| Figure 3.29: | Envelope Tracking Power Amplifier Instantaneous Efficiency Mea-<br>surement Setup [6]                                                                                                                               | 81 |

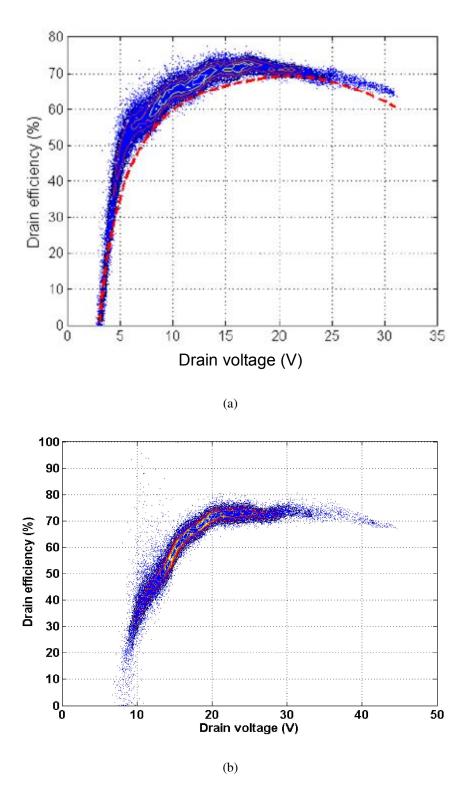

| Figure 3.30: | Envelope Tracking RF Power Amplifier Performance Comparison:<br>(a) 30 V peak Envelope Tracking [10], (b) 45 V peak Envelope<br>Tracking; Test Signal: W-CDMA 7.7 dB PAR                                            | 82 |

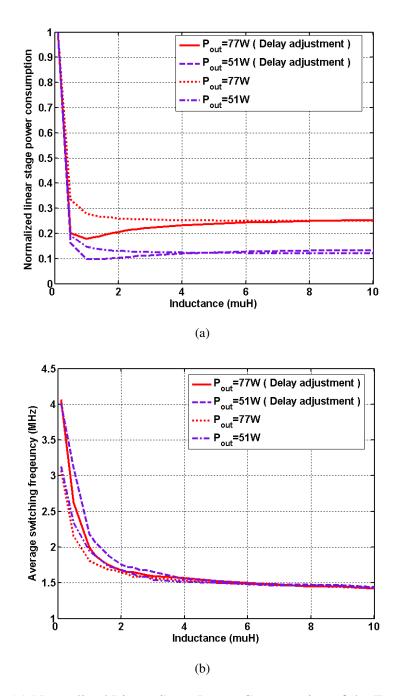

| Figure 4.1:  | Simulated Envelope Amplifier Behaviors with 1.3 $\mu$ H Inductor: (a)<br>Hysteresis: 0.025 V, (b) Hysteresis: 0.5 V; Test Signal: W-CDMA<br>7.7 dB PAR; Peak Envelope: 30 V; Load: 5 ohm                            | 88 |

| Figure 4.2:  | Simulated Envelope Amplifier Behaviors with 1.3 $\mu$ H Inductor and Switcher Control Delay Adjustment                                                                                                              | 90 |

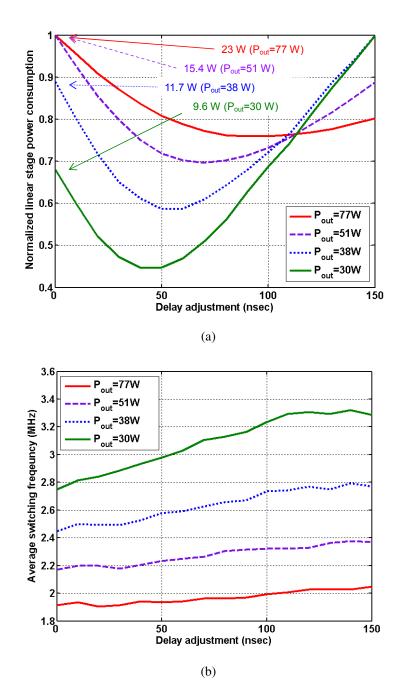

| Figure 4.3:  | (a) Simulated Overall Linear Stage Power Consumption and (b) Average Switching Frequency versus Switcher Control Signal Delay Adjustment for Different Output Power with using 1.3 $\mu$ H Inductor in the Switcher | 91 |

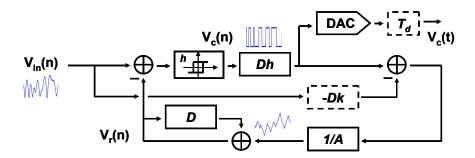

| Figure 4.4:  | Digital Signal Generation for Switcher Control                                                                                                                                                                      | 92 |

| Figure 4.5:  | Simulated DC Current Imbalance at the Output of Envelope Amplifier                                                                                                                                                  | 93 |

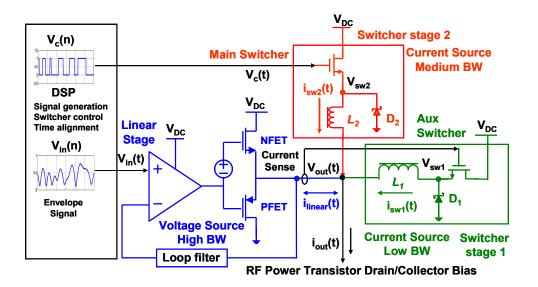

| Figure 4.6:  | Dual-switcher Envelope Amplifier Schematic                                                                                                                                                                          | 94 |

|              |                                                                                                                                                                                                                     |    |

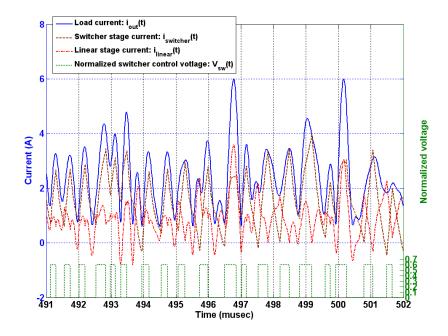

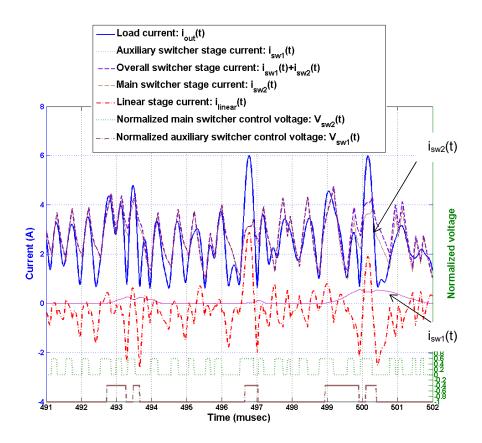

| Figure 4.7:  | Simulated Dual-switcher Envelope Amplifier Behaviors with 1.3 $\mu$ H and 25 $\mu$ H Inductor for the Switchers, respectively                             | 95  |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

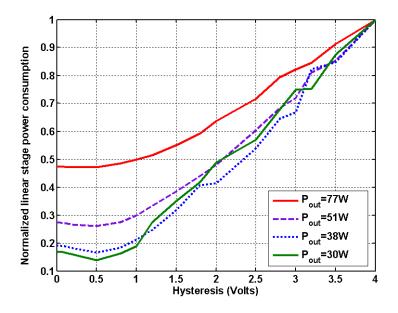

| Figure 4.8:  | Normalized Linear Stage Power Consumption of the Envelope Amplifier versus Hysteresis Value                                                               | 97  |

| Figure 4.9:  | (a) Main Switcher Average Switching Frequency, and (b) Auxiliary<br>Switcher Average Switching Frequency versus Hysteresis Value                          | 98  |

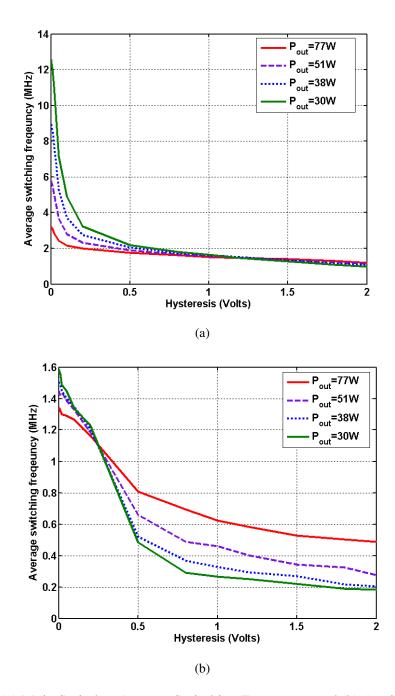

| Figure 4.10: | (a) Normalized Linear Stage Power Consumption of the Envelope<br>Amplifier, (b) The Main Switcher Average Switching Frequency,<br>versus Inductance Value | 100 |

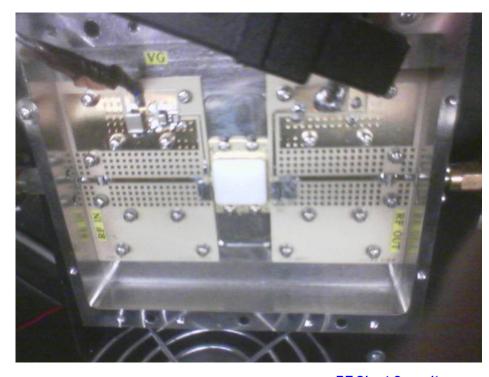

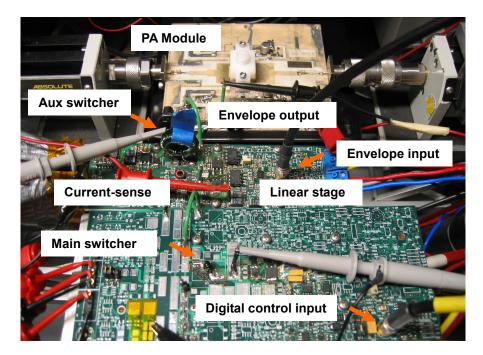

| Figure 4.11: | Dual-switcher Envelope Amplifier Hybrid Integration on PCB                                                                                                | 101 |

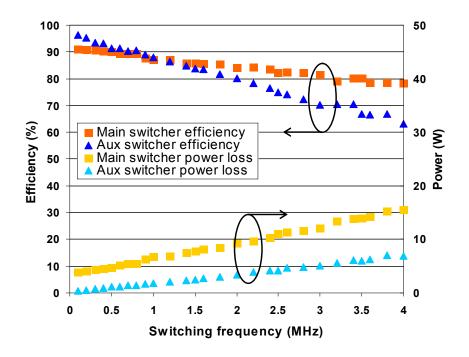

| Figure 4.12: | Measured Switcher Power Loss and Efficiency Performance versus<br>Switching Frequency                                                                     | 102 |

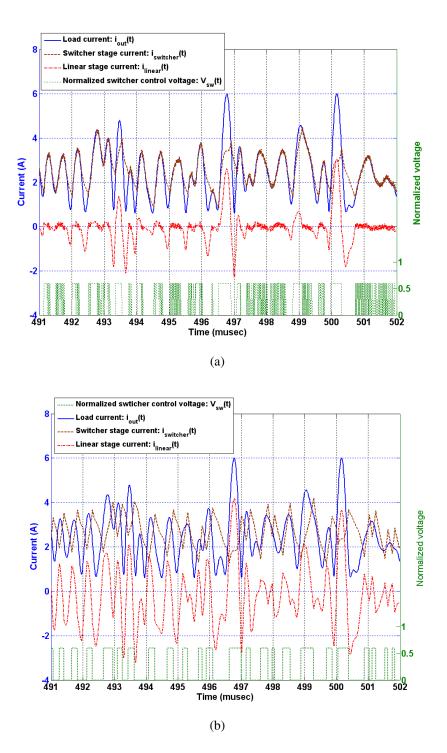

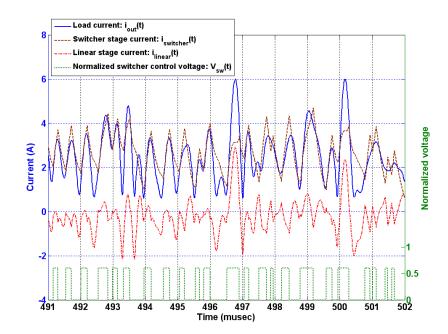

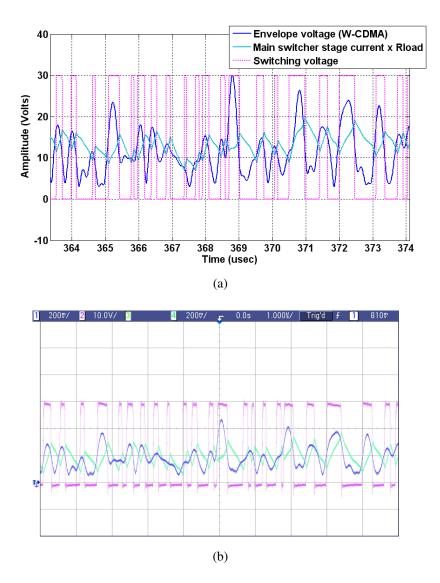

| Figure 4.13: | Recorded Waveform of Dual-switcher Envelope Amplifier Before<br>Delay Adjustment (a) Simulation, (b) Measurement (Ch1,Ch4: 10<br>mV = 100 mA)             | 103 |

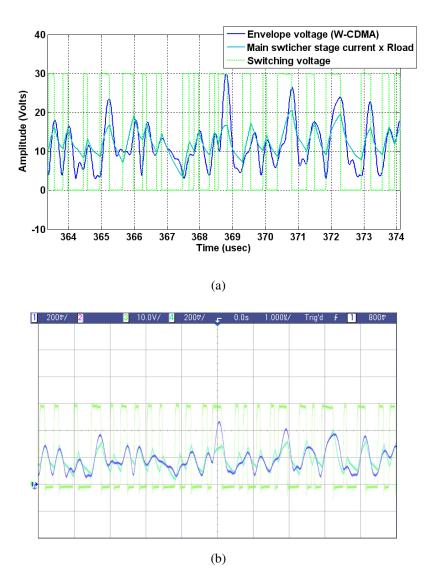

| Figure 4.14: | Recorded Waveform of Dual-switcher Envelope Amplifier After De-<br>lay Adjustment (a) Simulation, (b) Measurement (Ch1,Ch4: 10 mV<br>= $100 \text{ mA}$ ) | 104 |

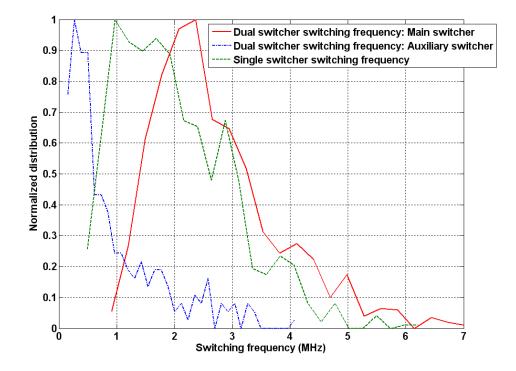

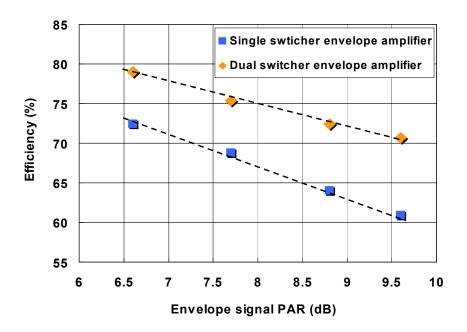

| Figure 4.15: | Measured Switching Frequency Distributions between Different Switch<br>Stages                                                                             |     |

| Figure 4.16: | Efficiency Measurement and Comparisons between Two Envelope Amplifiers                                                                                    | 106 |

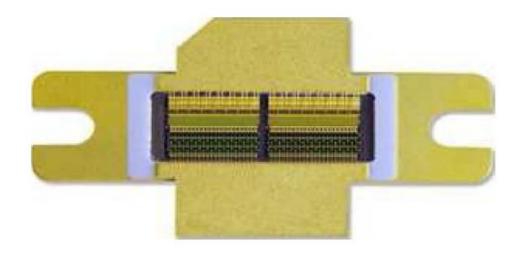

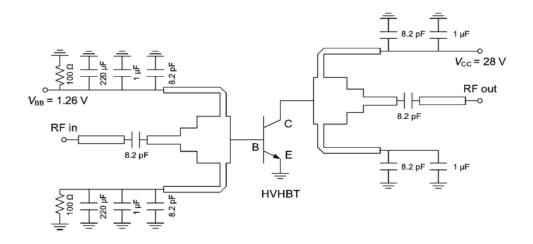

| Figure 4.17: | TriQuint Gen 1 GaAs HVHBT RF Device [9, 11]                                                                                                               | 108 |

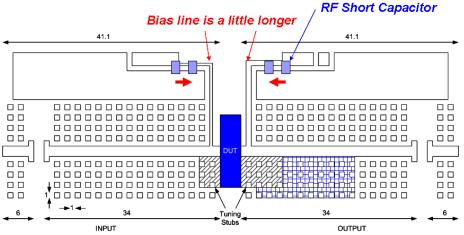

| Figure 4.18: | TrQiuint Gen 1 GaAs HVHBT RF Power Amplifier Test Fixture<br>Schematic [9]                                                                                | 108 |

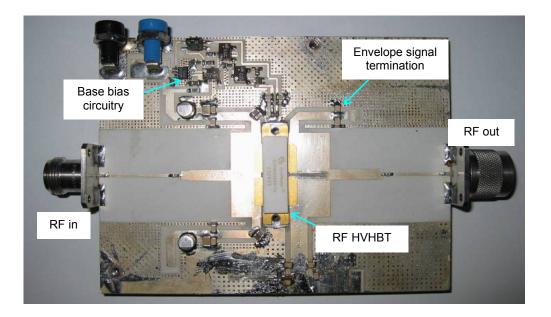

| Figure 4.19: | TriQuint Gen 2 GaAs HVHBT RF Power Amplifier Test Fixture [12]                                                                                            | 109 |

| Figure 4.20: | TriQuint Gen 1 GaAs HVHBT RF Device CW Measurement [9]                                                                                                    | 109 |

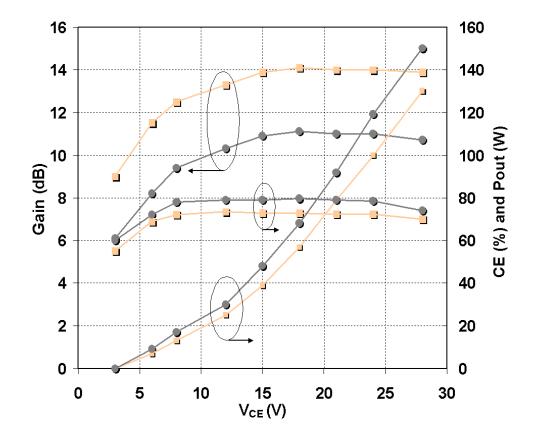

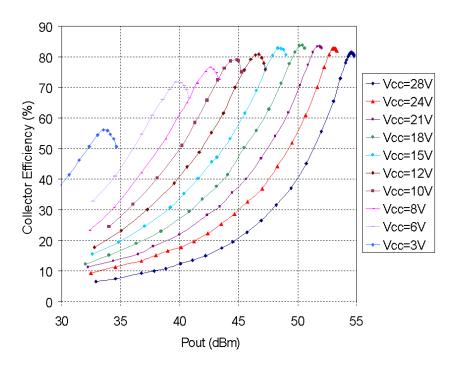

| Figure 4.21: | TriQuint Gen 2 GaAs HVHBT RF Device Pulse CW Measure-<br>ment [13] :(a) Collector Efficiency, (b) Power Gain, versus Collec-<br>tor Voltage               | 110 |

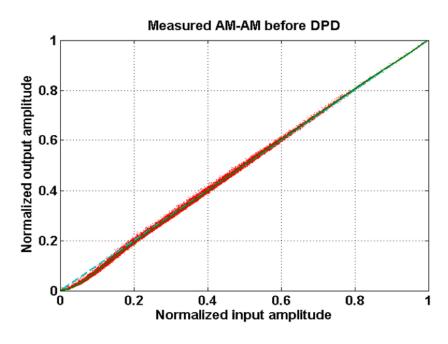

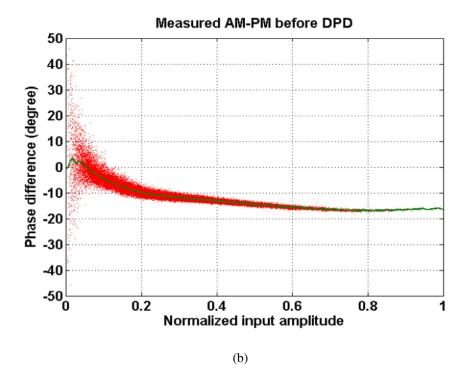

| Figure 4.22: | Measured: (a) AM-AM, (b) AM-PM Performance Before Predistortion [13]                                                                                      | 112 |

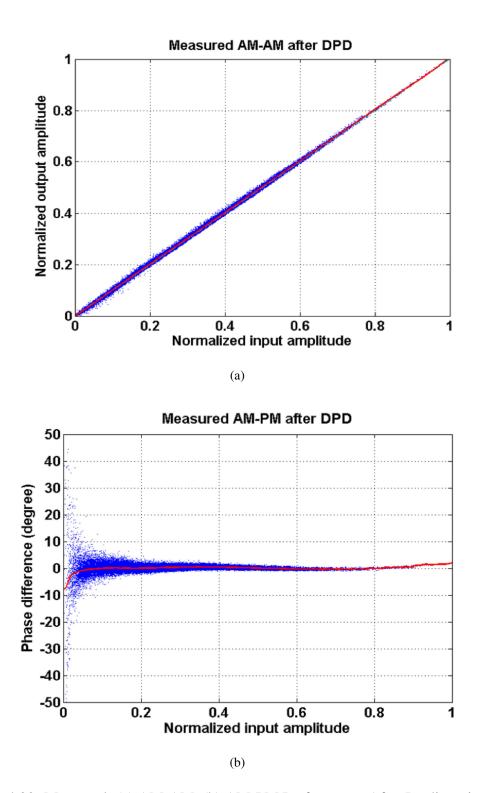

| Figure 4.23: | Measured: (a) AM-AM, (b) AM-PM Performance After Predistor-<br>tion [13]                                        | 113 |

|--------------|-----------------------------------------------------------------------------------------------------------------|-----|

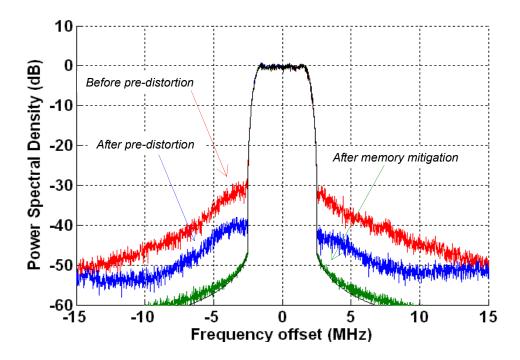

| Figure 4.24: | Normalized Output Spectrum of ET Power Amplifier Before and After DPD using TriQuint Gen 2 GaAs HVHBT RF Device | 114 |

### LIST OF TABLES

| Table 1.1:  | Power Amplifier Power Range and its Applications                                                                                                                         | 2   |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Table 2.1:  | Envelope Amplifier Simulation and Measurement comparisons ( 30 V Envelope Amplifier)                                                                                     | 37  |

| Table 3.1:  | High Voltage Envelope Amplifier Specifications                                                                                                                           | 44  |

| Table 3.2:  | OP-amp and Key Parameters for the Linear Stage                                                                                                                           | 45  |

| Table 3.3:  | Difference Amplifier and Key Parameters for the Current-sense Stage                                                                                                      | 46  |

| Table 3.4:  | High Voltage OTA Specifications                                                                                                                                          | 47  |

| Table 3.5:  | Device Performance in STMicroelectronics BCD Process                                                                                                                     | 49  |

| Table 3.6:  | Summary of High Voltage OTA Simulation Results                                                                                                                           | 50  |

| Table 3.7:  | Summary of high voltage OTA measurement results                                                                                                                          | 58  |

| Table 3.8:  | Tabulated Switch-FET Candidates for High Voltage Switcher Stage .                                                                                                        | 72  |

| Table 3.9:  | Tabulated Schottky Diode Candidates for High Voltage Switcher Stage                                                                                                      | 73  |

| Table 3.10: | Summary of High Voltage Envelope Amplifier Performance                                                                                                                   | 75  |

| Table 3.11: | Summary of EGN21A090IV/-A Constant Drain Measurement Results                                                                                                             | 78  |

| Table 3.12: | Summarized Measurement Results of the Two Envelope Tracking<br>Power Amplifiers with Single Carrier W-CDMA Signal Before and<br>After Memory-less Digital Pre-distortion | 83  |

| Table 4.1:  | Summarized simulated peak current distribution of envelope ampli-<br>fiers with single and dual switcher stages using W-CDMA signal                                      | 96  |

| Table 4.2:  | Summarized Performance of Power Amplifier with Single Carrier<br>W-CDMA and WiMAX Signal Before and After Digital Pre-distortion,<br>MM: Memory mitigation               | 115 |

#### ACKNOWLEDGEMENTS

I would like to express my gratitude to my advisor Prof. Peter Asbeck for his invaluable support and guidance for my research over these past years. His continuous support and suggestions are indispensable in making this research and dissertation possible.

My special thanks goes to Mr. Donald Kimball for his valuable advice and time. Our weekly meetings have provided invaluable insights into various aspects of my research.

I would also like to thank my committee members, Prof. Larry Larson, Prof. Paul Yu, Prof. Prabhakar Bandaru, and Prof. William Griswold for their support and crucial comments during preliminary reviews on my research topics and additionally, to thank Mr. Cuong Vu for his generous help for circuit assembly and measurement.

I, of course, would like to thank my parents as well for doing their best to always provide me with the best education opportunities. It could not be possible for me to finish this work without their constant help, support, and motivation.

It is my pleasure to acknowledge my colleagues at UCSD HSDG group for their knowledge and help in my research, especially Mr. Santaporn Wei Pornmkit, Mr. Paul Draxler, Mr. Paul Theilmann, Mr. Ming-Yuan Li, Ms. Jomei Johana Yan, Mr. Toshi Nataka, Mr. Nick Farcich, and former HSDG group members Dr. Dong-Jang Qiao, Dr. Yu Zhao, Dr. Tsai-Pi Hung, Dr. Adam Conway, Dr. David Keough, Dr. Tomas O'Sullivan, Dr. James Chingwei Li, Dr. Jinho Jeong, Dr. Calogero Presti and Dr. Jinsenog Jeong. Lastly, I would like to acknowledge the support of the Nokia Siemens Network, Center for Wireless Communications at UCSD and its member companies, and the University of California Discovery Grant.

Some of the material in chapter 2 is as it appears in "Effect of Maximum Power Supply Voltage on Envelope Tracking Power Amplifiers Using GaN HEMTs," C. Hsia, D. Kimball and P. M. Asbeck, IEEE Radio Wireless Symposium, 2011 (accepted), and in "Envelope Tracking Power Amplifier Efficiency Performance for Different Supply Voltage Dynamic Ranges," C. Hsia, D. Kimball and P. Asbeck, to be submitted to IEEE Trans. on Microwave Theory Techniques, 2011. The contributions from the co-authors are appreciated. The author of this dissertation was the primary investigator and primary author for these publications.

Some of the material in chapter 3 is as it appears in "Envelope Amplifier Design for Higher Than 50 V Envelope Tracking Power Amplifier Applications," C. Hsia, D. Kimball and P. Asbeck, to be submitted to IEEE Trans. on Microwave Theory Techniques, 2011. The contributions from the co-authors are appreciated. The author of this dissertation was the primary investigator and primary author for these publications.

Some of the material in chapter 4 is as it appears in "Dual-switcher Envelope Amplifier with Digitally-assisted Control for Envelope Tracking Power Amplifiers," C. Hsia, D. Kimball and P. M. Asbeck, IEEE Trans. on Microwave Theory Techniques, 2011 (in review). The contributions from the coauthors are appreciated. The author of this dissertation was the primary investigator and primary author for this publication.

#### VITA

| 1997      | Bachelor of Science, Mechanical Engineering, Chang Gung University, Taiwan                     |

|-----------|------------------------------------------------------------------------------------------------|

| 1999      | Master of Science, Mechanical Engineering, National Taiwan University, Taiwan                  |

| 2000-2002 | Research Engineer, MicroBase Technology, Taoyuan, Taiwan                                       |

| 2002-2004 | Research Engineer, ITRI, Hsinchu, Taiwan                                                       |

| 2005-2010 | Research Assistant, Electrical and Computer Engineering, University of California, San Diego   |

| 2007      | Internship, Freescale Semiconductor., Tempe, Arizona                                           |

| 2009-2010 | Research Intern Engineer, MaXentric LLC, San Diego, Califor-<br>nia                            |

| 2010      | Doctor of Philosophy, Electrical and Computer Engineering, University of California, San Diego |

#### PUBLICATIONS

Chin Hsia, J. J. Yan, P. Draxler, D. Kimball, and P. Asbeck, et. al, "Envelope Tracking Power Amplifier Efficiency Analysis for Different Supply Voltage Dynamic Ranges", *to be submitted to IEEE Transactions of Microwave Theory and Techniques*, 2010.

Chin Hsia, D. Kimball, A. Scuderi, C. Presti, C. Santagati, L. Larson, and P. Asbeck, "Envelope Amplifiers Design for Higher Than 45 V Envelope Tracking Applications", *to be submitted to IEEE Transactions of Microwave Theory and Techniques*, 2010.

Chin Hsia, D. Kimball, and P. Asbeck, "Effect of Maximum Power Supply Voltage on Envelope Tracking Power Amplifiers Using GaN HEMTs", *IEEE Radio Wireless Symposium*, 2011 (accepted).

Chin Hsia, J. J. Yan, P. Draxler, D. Kimball, and P. M. Asbeck, "Wideband High Efficiency Envelope Tracking Power Amplifiers Using High Voltage GaAs HBTs", *IEEE Power Amplifier Symposium*, 2010.

Chin Hsia, A. Zhu, J. J. Yan, P. Draxler, D. Kimball, S. Lanfranco, and P. M. Asbeck, "High Efficiency Envelope Amplifier with Digitally-assisted Switch-Control for Envelope Tracking Base-Station Power Amplifiers", *submitted to IEEE Transactions of Microwave Theory and Techniques*, 2010 (in review).

Chin Hsia, D. Kimball, S. Lanfranco, and P. M. Asbeck, "Wideband High Efficiency Digitally Assisted Envelope Amplifier with Dual Switching Stages for Base-Station Envelope Tracking Power Amplifier", *IEEE MTT-S*, 2010, pp. 672-675.

J. Jeong; D. Kimball, M. Kwak, Chin Hsia, P. Draxler, and P. Asbeck, "Modeling and Design of RF Amplifiers for Envelope Tracking WCDMA Base-Station Applications", *IEEE Transactions of Microwave Theory and Techniques*, Sept. 2009, pp. 2148-2159.

J. Jeong; D. Kimball, M. Kwak, Chin Hsia, P. Draxler, P. Asbeck, "Wideband envelope tracking power amplifier with reduced bandwidth power supply waveform", *IEEE MTT-S*, 2009, pp. 1381-1384.

J. Jeong; D. Kimball, M. Kwak, P. Draxler, Chin Hsia, C. Steinbeiser, T. Landon, O. Krutko, L. Larson, and P. Asbeck, "High-Efficiency WCDMA Envelope Tracking Base-Station Amplifier Implemented With GaAs HVHBTs", *IEEE Journal of Solid-State Circuits*, Oct. 2009, pp. 2629-2639.

Chin Hsia, D. Kimball, P. Draxler, J. Yan, P. M. Asbeck, J. Kinney, E. Toulouse and J. Wood, "High Efficiency LDMOS Power Amplifier for Wireless Base Stations using Envelope Tracking", *Proc. Semiconductor Research Corporation TECHCON, Austin TX*, Nov. 2008.

A. Zhu, P. Draxler, Chin Hsia, T. Brazil, D. Kimball and P. M. Asbeck, "Digital Predistortion for Envelope-Tracking Power Amplifiers Using Decomposed Piecewise Volterra Series", *IEEE Transactions of Microwave Theory and Techniques*, Oct, 2008, pp. 2237 - 2247.

Chin Hsia, D. Kimball, P. Draxler, J. Yan, P. M. Asbeck, J. Kinney, E. Toulouse and J. Wood, "High Efficiency Envelope Tracking Overdriven Class-A LDMOS Power Amplifier for Base Station Applications", *IEEE Power Amplifier Symposium*, 2008.

D. Kimball, M. Kwak, P. Draxler, J. Jeong, Chin Hsia; Steinbeiser, C.; Landon, T.; Krutko, O.; Larson, L.; Asbeck, P, "High Efficiency WCDMA Envelope Tracking Base-Station Amplifier Implemented with GaAs HVHBTs", *IEEE Compound Semiconductor Integrated Circuit Symposium*, 2008, pp. 1-4.

D. Kimball, J. Jeong, Chin Hsia, P. Draxler, S. Lanfranco, W. Nagy, K. Linthicum, L. E. Larson and P M. Asbeck, "High-Efficiency Envelope-Tracking W-CDMA Base-Station Amplifier Using GaN HFETs", *IEEE Transactions of Microwave Theory and Techniques*, Nov, 2006, pp. 3848-3856.

P. Draxler, S. Lanfranco, D. Kimabll, Chin Hsia, J. Jeong, J. van de Sluis and P. M. Asbeck, "High Efficiency Envelope Tracking LDMOS Power Amplifier for W-CDMA", *IEEE MTT-S*, June, 2006, pp. 1534-1537.

D. Kimball, P. Draxler, J. Jeong, Chin Hsia, S. Lanfranco, W. Nagy, K. Linthicum, L. Larson and P. Asbeck, "50% PAE WCDMA basestation amplifier implemented with GaN HFETs", *IEEE Compound Semiconductor Integrated Circuit Symposium*, 2005.

#### ABSTRACT OF THE DISSERTATION

#### **Envelope Amplifier Design for Wireless Base-Station Power Amplifiers**

by

Chin Hsia

Doctor of Philosophy in Electrical Engineering (Electronic Circuits and Systems)

University of California San Diego, 2010

Professor Peter M. Asbeck, Chair

In order to deliver high data rates, modern wireless communication systems transmit complex modulated signals with high peak-to-average ratio, which demands wide bandwidth and stringent linearity performance for power amplifiers. To satisfy spectral mask regulations and achieve adequate error vector magnitude, power amplifiers typically operate at 6 to 10 dB back-off from the maximum output power, leading to low efficiency. To overcome the low efficiency problem, the envelope tracking power amplifier architecture has been proposed for this type of application due to its feature of high efficiency over a wide power range.

The overall efficiency of an envelope tracking system relies not only on performance of the RF power amplifier but also on that of an envelope amplifier that provides a dynamically varying power supply voltage. This dissertation focuses on envelope amplifier design for efficiency enhancement of envelope tracking power amplifiers. First, the envelope tracking power amplifier architecture is analyzed, and the efficiency of a RF transistor in the envelope tracking technique is described. Then envelope amplifier behavior is investigated and a general purpose simulator is developed for analyzing and designing an envelope amplifier. Power loss and efficiency of the envelope amplifier is analyzed and compared with experimental results.

The design of envelope amplifiers for high voltage (> 30 V) envelope tracking applications is described. A high voltage envelope amplifier is designed, implemented and verified. The overall envelope tracking system employing a GaN-HEMT RF transistor is demonstrated.

Finally, a new architecture is developed for the efficiency enhancement of envelope amplifiers, using a digitally assisted controller design. Digital control is utilized to mitigate delay in the control loop inside the envelope amplifier, leading to lower overall power dissipation. A novel envelope amplifier architecture with dual-switcher stages based on the digitally-assisted control strategy is proposed, designed and implemented. The strategy is demonstrated to improve the efficiency of envelope amplifier as well as the system overall efficiency. The resulting performance of envelope tracking system employing a GaAs high voltage HBT with a single carrier W-CDMA input demonstrated state-of-the-art efficiency with good linearity performance.

## Chapter 1

## Introduction

Today's base-station transmitters require highly linear amplifiers to transmit complex modulation signals in order to provide wireless services with high throughput and large capacity. The design of power amplifiers therefore needs special attention to the amplifier output, which usually contains non-ideal spurious signals. In order to provide cost-effective and high performance solutions, a variety of architectures have emerged for the design of power amplifier for base station applications [3, 14]. In the following, a brief review is conducted of base station power amplifier architectures and design considerations for current and future wireless applications.

## **1.1 Base Station Power Amplifiers**

Table 1.1 categorizes power amplifiers and associated applications based on different power ranges. For cellular base station applications, the average output power is between 10 to 100 W. Two different power amplifier architectures are widely used in this power range. One is single-carrier-combined (SCC) architecture shown in Fig. 1.1, which consists of multiple, low or medium power amplifiers [1]. In this architecture, single-carrier modulated signals are generated in baseband separately and combined together at the output of each power amplifier. The advantages of implementing a SCC base station amplifier include ease of manufacture, high yields and suitability for massproduction [2]. However, the outputs of multiple single-carrier power amplifiers are combined passively with frequency-selective combiners of very exacting design, which introduces losses and reduces overall efficiency. Furthermore, each individual amplifier requires linearization to optimize its output power and efficiency, further increasing the system complexity.

| PA average power        | Applications                       |

|-------------------------|------------------------------------|

| $\geq 100 \text{ W}$    | Digital TV broadcast               |

|                         | Radio broadcasting transmitters    |

| $10 \sim 100 \text{ W}$ | Cellular infrastructure (2G/3G/4G) |

|                         | Mobile TV (DVB-T/H)                |

|                         | Military and Public safety         |

| $1 \sim 10 \text{ W}$   | Micro BTS                          |

|                         | Military handset                   |

| $\leq 1 \text{ W}$      | Cellular handset                   |

|                         | Modems                             |

|                         | Wireless backhaul (LOS)            |

Table 1.1: Power Amplifier Power Range and its Applications

A multi-carrier power amplifier (MCPA) is another architecture for cellular base station applications. In a modern MCPA shown in Fig. 1.2, the transmitted signals are combined in the digital domain and permits evolutionary technologies such as predistortion [15, 16, 17] and waveshaping to be employed which further reduce manufacturing costs and eliminate analog design complexity [2]. The output is up conversion by employing a RF transmitter and then drives a high power, high linear final stage power amplifier. The power amplifier output does not require a combiner therefore maximally

Figure 1.1: Single Carrier Combined Power Amplifier [1]

utilizing the amplifier's performance. MCPA becomes more and more popular now-days due to its capability of handling multi-mode, multi-standard and multi-band signals better than SCC architecture [18].

For designing a base-station power amplifier, the Federal Communication Commission (FCC) standards require the linearity performance beyond the capabilities of conventional class A/AB linear amplifiers. The reason is the amplification of multicarrier signals yields inter-modulation distortion (IMD) and results in unacceptable spectral regrowth in the adjacent channels. The FCC imposes, therefore, adjacent channel power ratio (ACPR) specifications on multi-carrier communication systems, on the order of -45 to -55 dBc [19]. To ensure the performance meet the specifications, a linearization technique is generally developed for the overall system. Linearization is a systematic procedure for reducing an amplifier's distortion. Linearity improvement of a power amplifier, however, often leads to a trade-off with efficiency. For example, for amplifying

Figure 1.2: Multiple Carrier Power Amplifier Architecture [2]

a multi-carrier non-constant envelope signal shown in Fig. 1.3 with large crest factor (high peak-to-average ratio), backing off the average power can linearize a power amplifier in order to avoid signal clipping at the peak amplitude, which will significantly impacts the linearity. However, the approach usually results in an unacceptable decrease in DC to RF efficiency because the efficiency of power amplifiers generally decreases from the maximum power the amplifier can provide. (1.1) shows the class B amplifier drain/collector efficiency,  $\eta_{PA}$ , as a function of output power [1].

$$\eta_{PA} = \frac{P_{out}(rf)}{P_{DC}}$$

$$= \sqrt{\frac{P_{out}(rf)}{P_{max}(rf)}} \cdot \frac{V_{max} - V_{min}}{V_{max} + V_{min}} \cdot \frac{\pi}{4}$$

(1.1)

Where  $P_{out}(rf)$  is the average output power,  $P_{DC}$  is the DC input power,  $P_{max}(rf)$  is the maximum output power,  $V_{max}$  is the maximum voltage swing of RF transistor, and  $V_{min}$  is the minimum voltage swing of RF transistor. The efficiency drops from its peak

Figure 1.3: Multiple Carrier RF signal

value in a square root manner with output power. Backing off 6 dB output power, for instance, reduces power amplifier's efficiency from the peak to nearly half, which results in a dramatic performance degradation.

In order to preserve the performance of power amplifier running non-constant envelope signals, efficiency enhancement techniques are proposed to improve the average efficiency of power amplifiers, especially at power back-off [14, 20, 21, 22, 23]. A brief review on different topologies is discussed in the next section.

## 1.2 High Efficiency Techniques for Non-Constant Envelope Signals

### **1.2.1** Doherty Power Amplifier

Doherty amplifier was proposed by William H. Doherty [24] and was originally employed for high power transmitter using vaccum-tubes. Doherty amplifier uses "active load pull" techniques to improve efficiency at power back-off. The simplest configuration of a Doherty amplifier is shown in Fig. 1.4, which consists of two amplifiers, the carrier and peak amplifier. The carrier amplifier generally is biased in Class AB, and the peak amplifier biased in Class C. The amplifiers are connected in parallel with the outputs joined by a quarter-wave transmission line, which performs impedance transformation. At low powers, the carrier amplifier is operated with a relatively high load impedance, which allows it to achieve high efficiency. The peak amplifier delivers current as the carrier amplifier saturates; therefore reduces the impedance seen at the output of the carrier amplifier. This maintains high efficiency without hard saturation of the carrier amplifier. Recently, Doherty amplifiers using high power RF devices gradually emerge for wireless base-station applications, especially replaced for low-efficiency linear amplifiers in Feed-forward architectures [20]. There are various types of Doherty circuits demonstrated to extend the high efficiency over a broad power range [3, 11, 25]; however, modulation bandwidth, linearity and adaptability are challenges for Doherty amplifiers towards wide-band, high efficiency base-station applications.

Figure 1.4: Doherty Power Amplifier [3]

### **1.2.2 LINC Power Amplifier**

LINC (Linear Amplification with Nonlinear Components) is another efficiency improvement technique, which employs a combination of high efficiency switch-mode power amplifiers to produce the linear output. In a LINC amplifier system shown in Fig. 1.5, Signal component separator unit generates signals with constant envelope to encode complex signals such that two switch-mode amplifies can be driven by constant envelope signals to maintain high efficiency. This technique has demonstrated over 48% efficiency with good linearity performance in terminal applications [21]. For basestation power amplifier which requires at least 20 W output power, however, system mismatch, power combiner loss, and high switching loss degrade the overall system performance compared to other techniques [26].

Figure 1.5: LINC Power Amplifier [1]

#### **1.2.3 EER Power Amplifier**

Envelope elimination and restoration (EER) was proposed to linearize a power amplifier in an efficient manner. It was first developed by Leonard R. Kahn in 1952 [27] and later enhanced by others [5, 22]. EER technique, shown in Fig. 1.6, combines a switch-mode amplifier and a highly efficient envelope amplifier. The system typically consists of a limiter to eliminate the envelope. The resulting constant amplitude phase modulated carrier is then amplified by a switch-mode PA like Class E [22] or Class F [28]. A constant envelope signal enables driving the switch-mode amplifiers with high efficiency without performance degradation by high PAR signals. Finally, the envelope is restored by modulating the supply voltage at the amplifier. The efficient combination output inside a RF transistor is linearly dependent on the input signal, and clipping at the peak power is avoided because the bias supply moves with signal's envelope. Therefore, EER technique theoretically can achieve very high efficiency and high linearity [29]. However, it faces several implementation issues for base-station power amplifiers, such as 1.) the linearity is stringently dependent on the time-alignment between RF input and dynamic envelope voltage [4], and 2.) the envelope eliminated input signal will have extreme bandwidth such that a high power input driver is typically required, which lowers the system overall performance.

Figure 1.6: Envelope Elimination and Restoration (EER) PA [4]

#### **1.2.4 ET Power Amplifier**

Envelope Tracking (ET) technique, which is the main focus of this dissertation, is a method to improve the power amplifier efficiency while dealing with high PAR input signals [6, 23, 30]. Similar to EER, the ET technique dynamically varies the drain or collector voltage of the RF transistor to track the RF signal's envelope. However, the difference between ET and EER leads to some advantages of applying it for base-station power amplifier. First, shown in Fig. 1.7, the RF power amplifier is operated in quasi-linear mode with class A/AB gate/base bias [14] such that the power amplifier pre-driver does not have to reach a saturated power level. In other words, ET technique does not limit the amplitude modulation of the RF signal as is in the EER case. The RF input power contains both amplitude and phase information, which eases system implementation and time-alignment [5, 6]. Moreover, the ET technique permits the supply voltage variation to be somewhat less accurate to the RF signal's envelope than EER, which provides flexibility of designing narrow band envelope amplifier for wide band systems [31]. A more detailed description of the ET system will be described in chapter 2.

Figure 1.7: Envelope Tracking (ET) PA [5, 6]

## **1.3 Scope of Dissertation**

The ET amplifier structure has been focus of many research papers [4, 6, 28, 30]. However, more research needs to be done to improve efficiency and linearity performance, both in the area of optimization of RF power amplifier as well as envelope amplifier. This thesis is dedicated to exploring the development of envelope amplifiers used in envelope tracking technique applied for wireless communication systems. The main challenge is to design a high efficiency envelope amplifier to improve the overall efficiency while meeting the system linearity requirements. The objective of this dissertation is to analyze practical design issues for an envelope amplifier and provide solutions for high efficiency and good linearity performance.

First, the envelope tracking power amplifier is analyzed, and envelope amplifier architectures are investigated. Based on the study, design and implementation of envelope amplifiers for different RF transistor technologies is presented and analyzed for maximizing the performance of ET amplifier.

The dissertation is organized as follows:

In chapter 2, the ET technique is reviewed to give a clear picture of ET system architecture and requirements. Design challenges are developed and addressed for the envelope amplifier. A general purpose simulator is presented for analyzing the behavior of the envelope amplifier and modeling the overall performance. Based on the model, an implementation strategy towards high efficiency envelope amplifier is introduced. Experimental results are presented for comparison with the model.

In chapter 3, an envelope amplifier design for high voltage applications is addressed in detail. A hybrid envelope amplifier design based on Bipolar-CMOS-DMOS (BCD) technology is designed and implemented. The demonstration is conducted by using a high voltage envelope amplifier together with a high voltage GaN-HEMT RF transistor. Effect of maximum absolute supply voltage on ET power amplifier performance is analyzed and verified by experiments.

Chapter 4 proposes an efficiency improvement strategy for an envelope amplifier, using a dual-switcher architecture. A digital signal processing (DSP) control switcher is designed, implemented and utilized to improve the efficiency of envelope amplifiers. Efficiency measurement of the ET power amplifier using GaAs high voltage HBT devices together with a dual-switcher envelope amplifier achieves the record-high efficiency with good linearity performance.

Chapter 5 concludes the dissertation and possible future investigation areas are suggested.

# Chapter 2

## **Envelope Tracking Power Amplifier**

## 2.1 Introduction

High power amplifier (HPA) efficiency improvement for W-CDMA base stations is an ongoing area of research. HPA efficiency determines the power consumption, size, cost, and cooling requirements of a base-station. As we discussed in chapter 1, the envelope tracking architecture is designed to improve HPA average efficiency at power back-off. In this chapter, the envelope tracking technique will be first discussed in Section 2.2. Its influence on efficiency of a RF transistor will be reviewed and analyzed in Section 2.3. The envelope amplifier architecture is then studied in Section 2.4, and a general purpose simulator is proposed to provide for guidelines for envelope amplifier design in Section 2.5. Finally, envelope amplifier efficiency measurement together with simulation results are presented for comparison in Section 2.6.

## 2.2 Envelope Tracking Techniques

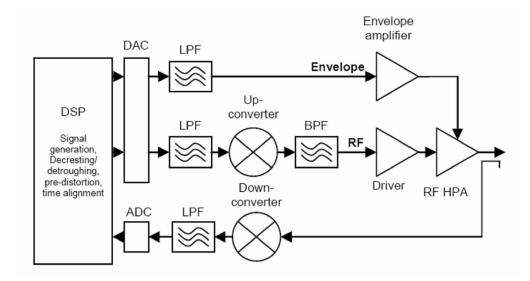

ET power amplifiers share important features with polar transmitter systems which employ phase and amplitude signals instead of I/Q modulation directly. There

are different variations of ET architecture proposed in the literature [4, 6, 30]. Fig. 2.1 shows the envelope tracking system diagram [6]. An analog envelope signal as well as in-phase (I) and quadrature (Q) baseband signals are generated in the digital domain. After up-conversion, the resultant RF signal provides the time varying input signal to the RF amplifier after a suitable driver amplifier. The supply voltage for the RF amplifier is modulated by the amplified envelope signal through an efficient wide-band envelope amplifier such that the RF amplifier keeps operating close to its saturated power region for all envelope amplitudes to improve average efficiency. A detroughing function (2.1) is used to fit the envelope of the RF input signal into a voltage waveform, which avoids RF transistor gain collapse at zero drain/collector voltage.

$$V_{env}(t) = V_{max} \cdot \left(x_{in}(t) + b \cdot e^{\frac{-x_{in}(t)}{b}}\right)$$

(2.1)

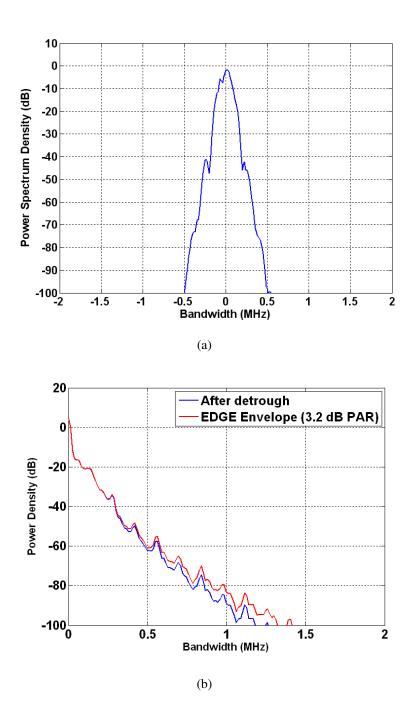

Where  $x_{in}(t)$  is the normalized input IF signal,  $V_{max}$  is the maximum DC power supply, and b is the detroughing factor. The detroughing process also helps reduce high frequency components of the envelope signal [6]. Fig. 2.2 shows the power spectrum of the envelope before and after detroughing. The high frequency component can be manipulated to within certain limited bandwidth.

To reduce the extent of back-off needed for the time varying envelope, a decresting function (an adjustment of the PAR) is performed digitally on the baseband signal to favor improve efficiency by increasing the average output power, as well as to help meet the ACPR and error vector magnitude (EVM) requirements [6]. To minimize distortion caused by the time-delay difference between envelope and RF paths, synchronization is performed by maximizing the amplitude and phase correlation between the input and

Figure 2.1: Envelope Tracking System [6]

Figure 2.2: W-CDMA Envelope Signal Power Spectrum Before and After Detroughing and Decresting

down-converted output signals [4]. In addition to the delay, there are other sources of nonlinearity in the ET amplifier such as RF transistor trans-conductance nonlinearity and output capacitance variations with varying envelope voltage. To minimize the distortion caused by the RF amplifier, pre-distortion is carried out in the digital domain. The pre-distorted input signal is created by the inverse function of the measured AM/AM and AM/PM characteristics of the overall system (including the driver), such that the stringent linearity requirements imposed by the FCC can be fully satisfied [6, 15, 32].

### 2.3 ET Power Amplifier Efficiency

The overall ET power amplifier efficiency  $\eta_{ET}$ , neglecting the DSP unit power consumption, is determined by both RF power amplifier's efficiency,  $\eta_{PA}$ , and the wide-band envelope amplifier's efficiency,  $\eta_{env}$ , as described in (2.2).

$$\eta_{ET} = \eta_{PA} \cdot \eta_{env} \tag{2.2}$$

$\eta_{PA}$  in ET operation, for a class B gate/base bias, can be calculated in (2.3) [1]:

$$\eta_{PA} = \frac{P_{out}(rf)}{P_{DC}}$$

$$= \frac{V_{dd} - V_{min}}{V_{dd}} \cdot \frac{\pi}{4}$$

$$P_{out}(rf) = \frac{1}{2} \cdot V_{fund} \cdot I_{fund}$$

$$P_{DC} = V_{dd} \cdot \frac{I_{rf}}{\pi}$$

$$V_{fund} = R_L \cdot \frac{I_{rf}}{2}$$

$$I_{fund} = \frac{I_{rf}}{2}$$

$$V_{dd} = V_{min} + I_{rf} \cdot \frac{R_L}{2}$$

(2.3)

Where  $P_{out}(rf)$  is the RF fundamental output power,  $V_{fund}$  is the RF fundamental output voltage,  $I_{fund}$  is the RF fundamental output current,  $P_{DC}$  is the DC input power,  $R_L$  is the power amplifier load line,  $I_{rf}$  is the dynamic RF current,  $V_{dd}$  is the dynamic supply voltage, and  $V_{min}$  is the minimum voltage swing of RF transistor. This treatment describes the ideal case for an ET power amplifier with class B gate/base bias in which the envelope amplifier provides the ideal dynamic voltage supply with unlimited bandwidth to the RF transistor. For a constant drain/collector bias class B RF power amplifier, the efficiency varies with output power as described in (1.1). However, from (2.3), the power amplifier's efficiency no longer scales with output power, which is a dramatic improvement for efficiency at power back-off regime. Fig. 2.3 plots the efficiency comparison between a constant drain/collector class B power amplifier and an ideal ET power amplifier efficiency degrades only with the factor,  $V_{min}$ . In other words, the efficiency of RF power amplifier can be maintained within a wide power range (voltage range) in ET operation and rolls off only due to RF transistor's intrinsic knee voltage [10, 33].

From (2.3), it is seen that the larger value of  $V_{dd}/V_{min}$ , the more efficiency RF amplifier can achieve ideally. We can define an efficiency degradation factor,  $\eta_{RF}$  in (2.4) [10, 33].

$$\eta_{RF} = 1 - \frac{V_{min}}{V_{dd}}$$

$$\approx 1 - \frac{R_{on}}{R_{load}}$$

(2.4)

Where  $R_{load}$  can be approximated as the RF amplifier fundamental load line [10] and  $R_{on}$  is the intrinsic "ON" resistance of RF transistor. For the ET operation,  $V_{dd}$  changes continuously with input RF signal and can be generated by a detroughing function in

Figure 2.3: Comparison of Simulated Efficiency versus Output Power between Class B Power Amplifier and Class B with Ideal ET Operation

(2.1). (2.4) illustrates a crucial factor in designing an envelope amplifier for the corresponding RF transistors. While using a RF transistor with higher  $V_{min}$ , the dynamic range of the envelope amplifier has to be extended to preserve the high efficiency of RF amplifier in ET operation [33]. In other words, for a RF transistor with a fixed  $R_{on}$  value, the higher the  $R_{load}$ , the better the efficiency. Increasing the dynamic voltage swing of the RF transistor is helpful in choosing larger  $R_{load}$ . To verify the above analysis, in chapter 3, two different dynamic range envelope amplifiers are employed separately in an ET system with the same RF transistor technology for performance comparison.

### 2.4 Envelope Amplifier Architecture

The envelope amplifier topology we discuss in this section is shown Fig. 2.4 [23]. It was originally proposed for hybrid amplifiers used in various instrument applications [34] and then enhanced by Mara and Kimball, et. al for the ET power amplifier. In Fig. 2.4, the envelope amplifier includes a linear stage in conjunction with a switching buck converter (switcher). The reason for using the hybrid amplifier architecture relies on the characteristics of the signal the amplifier has to handle. The W-CDMA envelope signal power spectrum, shown in Fig. 2.5, has a large portion of power at low frequency, roughly between DC to 100 kHz, and a smaller high frequency component of the signal beyond 100 KHz. The low frequency component contains more than 85% of the signal power. This suggests an architecture where the high efficiency switcher provides a current output and handles the majority of the envelope power. The linear stage provides a voltage output, which is an amplified replica of the input voltage,  $V_{in}$ , to ensure high accuracy of the output signal. The switcher and the linear stage are coordinated by using a current-sense hysteretic controller, which is used to turn on/off the switcher by sensing the current flowing out of the linear stage through a current-sense resistor. The switching noise introduced in the switcher can be attenuated by the loop filter inside the linear stage. The disturbances introduced by the switcher at the output of envelope amplifier are therefore reduced [13, 35]. To better understand the behavior of the envelope amplifier, a general purpose model based on Matlab/Simulink has been developed and is described in the following section.

### 2.5 Envelope Amplifier Modeling

Fig. 2.6(a) shows the systematic block diagram of the envelope amplifier and Fig. 2.6(b) presents the implementation blocks in Matlab/Simulink environment. For simplified analysis without loss of generality, the load line of RF power amplifier is modeled as a constant load impedance,  $R_{load}$ . In Fig. 2.6(a),  $V_{in}$  represents the envelope

Figure 2.4: Envelope Amplifier Architecture [6]

Figure 2.5: W-CDMA Envelope Signal Characteristics

input voltage,  $V_{env}$  represents the linear stage output, Gain represents the linear stage voltage gain with certain bandwidth (set around 50 MHz), V<sub>out</sub> represents the envelope amplifier output voltage, Iout represents the amplifier output current, and Iswitcher represents the switcher output current. The hysteretic comparator is modeled as a relay. The difference current,  $I_{linear}$ , between  $I_{out}$  and  $I_{switcher}$ , which the linear stage has to provide, is directed into the relay, which represents the current-sense feedback path together an comparator used in the hardware implementation.  $I_{linear}$  also feeds back to the linear stage output through a current-sense resistor,  $R_{sense}$ . H(jw) represents a second order low pass filter to limit the bandwidth of the difference signal before going into the comparator. The relay output is the switching waveform,  $V_{sw}$ . For simplicity, the model neglects the actual switcher driver circuits and uses a delay block,  $T_d$  to represent any possible delay in the switcher driver circuits. The switcher current,  $I_{switcher}$ , is generated by the voltage difference between  $V_{sw}$  and a feed-forward envelope output signal,  $V_{out}$ , across an inductor, L. The overall system modeling is similar to a feed-forward delta modulator. Based on the simulation results of  $V_{out}$ ,  $I_{out}$ ,  $I_{linear}$ ,  $V_{sw}$ , and  $I_{switcher}$  generated from the simulator, the envelope amplifier's dynamic behavior is predictable while operating with different signals and at different power levels, which eases the design and analysis.

We use an EDGE signal as the input to begin to illustrate the envelope amplifier modeling results. The 8PSK modulation of an EDGE system uses linear modulation techniques and generates amplitude varying signals with a PAR of 3.2 dB. The spectrum of EDGE signals is shown in Fig. 2.7(a); the signal bandwidth is around 200 KHz. The envelope signal power spectrum is shown in Fig. 2.7(b). Its bandwidth, though

(a)

Scope

Figure 2.7: EDGE signal: (a) IF signal (b) Envelope signal.

broaden than the IF or RF signal, is also within several hundreds KHz. Fig. 2.8(a) and Fig. 2.8(b) present the steady state simulations, including envelope output voltage, the switching waveform (Fig. 2.8(a)), the envelope output current and switcher's output current (Fig. 2.8(b)). In this example, the peak envelope voltage is scaled to 30 V, the load impedance is set at 5 ohm and the inductor value is set at 25  $\mu$ H. The  $V_{rms}$  of the envelope signal is around  $20 \sim 21$  Volts. In Fig. 2.8(b), due to the condition that the switcher's current slew rate is higher than the output current average slew-rate [5], I<sub>switcher</sub> tracks the  $I_{out}$  closely and the linear stage only corrects the switcher output error. For this, it only consumes a small fraction of total input power. The peak current the linear stage has to provide is less than 2 A and this happens only when the instantaneous slew-rate of the switcher is lower than that of the output current. At this moment, the linear stage is required to supply the rest of power. Fig. 2.8(c) shows the experimental results for the same section of EDGE waveform, and the same behavior is observed. Fig. 2.8(d) shows the switching frequency distribution both from the simulation and the measurement results. Here experimental results were obtained by data collections on switching pulses of total 500  $\mu$ sec period with 5 nsec resolution (more than 1 Mega samples) using 4 GS/sec sampling oscilloscope. The switching frequency is around  $1 \sim 2$  MHz, which is higher than EDGE signal's bandwidth.

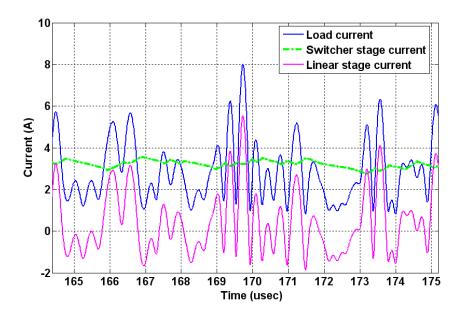

Fig. 2.9 shows the steady state simulation using a W-CDMA signal with 7.7 dB PAR. The peak envelope voltage, the load, and the inductance value are set the same as in Fig. 2.8. The  $V_{rms}$  of envelope signal is around 11~12 Volts. In this example,  $I_{switcher}$  tracks around the moving average of the  $I_{out}$  due to the condition that average slew-rate of envelope current,  $I_{out}$  is larger than that of switcher current [5]. The switching pulses shown in Fig. 2.9(a) shows lower switching frequency than the envelope signal band-

Figure 2.8: Envelope Amplifier Running EDGE Signal: (a) Simulation (b) Simulation (c) Experimental results (Ch1,Ch4: 10 mV = 100 mA) (d) Switching Frequency Distribution comparison.

width shown in Fig. 2.5. In this case, the switcher does not provide the full current to the load but only approximately the average of the signal.  $I_{linear}$  sources and sinks the high frequency current shown in Fig. 2.9(b). The peak current the linear stage has to provide is around 3.5 A. Fig. 2.9(c) shows the experimental results. These exhibit the same behavior (except some rare high frequency switching pulses due to the noise.) Fig. 2.9(d) compares the switching frequency distribution between the simulation and measurement results, illustrating the good accuracy of the model. The switching frequency is around  $1\sim2$  MHz.

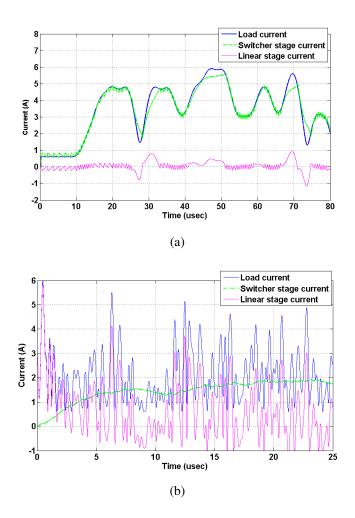

From the simulation results, the envelope amplifier architecture shows different behaviors depending upon the envelope signal's slew rate compared to the switcher's slew rate. In Fig. 2.8(b) with the EDGE signal, the power is mainly produced from the switcher stage. Therefore, even though the peak load current is around 6 A, the peak current provided from the linear stage is small. However, in Fig. 2.9(b) with the W-CDMA case, the peak current the linear stage has to provide is about 3.5 A and therefore, the linear output stage has to be sized large enough to support such high power handling. In order to use the envelope amplifier in different scenarios, the device size and power handling capability of the linear stage should in general follow the case represented by the W-CDMA signals. The magnitude of switcher current shown in Fig. 2.8(b) and Fig. 2.9(b), together with the switching frequency distribution in Fig. 2.8(d) and Fig. 2.9(d), can be used to estimate the switcher's loss, and to design the size of the switch-FETs for implementing a high efficiency switcher. The overall power loss and efficiency performance of the envelope amplifier is described in Section 2.6.

Another important result observed from the simulation is the start-up (or transient) condition. Fig. 2.10(a) and 2.10(b) shows the start-up simulation running EDGE

and W-CDMA signals, respectively. For the case of an EDGE signal, the switcher catches up to the output current quickly such that the linear stage only needs to support a small amount of power. However, in the case of a W-CDMA signal, the linear stage has to provide the majority of current before the switcher moves into its steady-state. The duration of this setting period depends on the time constant of the switcher. In Fig. 2.10(b), the transient time is about 5  $\mu$ sec. During this period, the linear stage is highly stressed, which potentially leads to overheating or damage of the envelope amplifier if the linear stage power handling capability is not enough. In this case, either small time-constant of the switcher or appropriate protection circuits have to be designed.

### 2.6 Envelope Amplifier Efficiency

In this section, we will incorporate an estimator into the simulator to model efficiency of the envelope amplifier. The overall efficiency of the amplifier can be described in (2.5):

$$\eta_{env} = \frac{P_{out}}{P_{out} + P_{loss}} \tag{2.5}$$

Where  $P_{out}$  represents the amplifier average output power while the  $P_{loss}$  represents total power loss inside the amplifier. The power loss can be easily estimated using the simulator by extracting the current and voltage transient information at each stage. There are three main power losses inside the amplifier: 1.) The static power loss, 2.) The linear stage dynamic power loss, and 3.) The switcher stage dynamic power loss.

The static power loss refers to any loss independent of the amplifier's output power. For example, bias current of the linear stage introduces static power loss. The

Figure 2.10: Envelope Amplifier Start-up Condition: (a) EDGE signal (b) W-CDMA signal.

switcher driver also require several mA bias current [36], and the current-sense stage power loss which includes the comparator's static power consumption, etc. By properly selecting low power devices (Section 3.3), the static power loss can be reduced.

Referring to Fig. 2.4, the linear stage dynamic power loss can be estimated by (2.6) [5].

$$P_{losslinear} = P_{lossNFET} + P_{lossPFET}$$

(2.6a)

where  $P_{loss_{NFET}} = (V_{DC} - V_{out}) \cdot (I_{out} - I_{switcher})$  (2.6b)

for Switcher turn-on

$$P_{lossPFET} = (V_{out}) \cdot (I_{switcher} - I_{out})$$

(2.6c)

### for Switcher turn-off

The loss ignores the driver's power consumption and regards it as a static power loss. Using the transient simulation results in Fig. 2.8(b) and Fig. 2.9(b), the linear stage power loss can be easily calculated. The loss is highly related to the envelope signal's amplitude probability distribution and the envelope peak voltage magnitude (headroom). In addition, as we discuss in Section 2.5, the magnitude of linear stage current,  $I_{linear}$  is highly correlated with the switcher's output current,  $I_{switcher}$ . For example, the linear stage using W-CDMA signals has to provide larger current compared to the case with EDGE signals. Therefore the power loss of the linear stage using W-CDMA signals increases. Proper design of the switcher control can reduce the linear stage output current and hence the power loss to help resolve this issue.

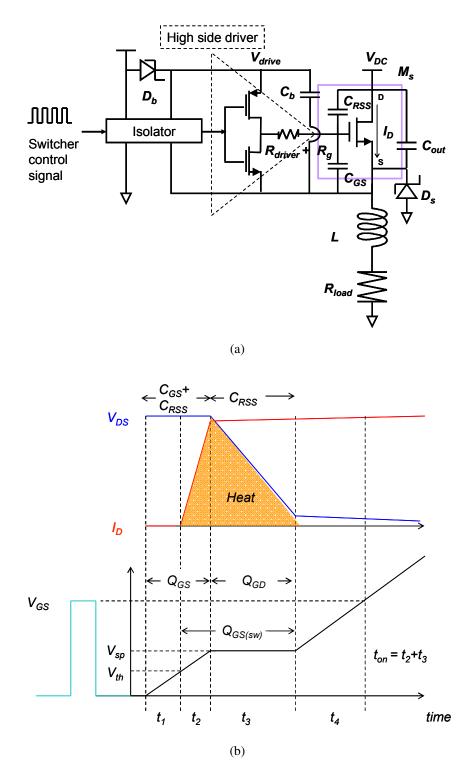

The loss inside the switcher stage is more complicated than the other loss mechanisms of the amplifier. Fig. 2.11(a) shows the schematic of the switcher, which is composed of a switcher high-side driver, a switch-FET,  $M_s$ , a Schottky diode,  $D_s$  and a power inductor, L. The power loss in any switch-FET and Schottky diode is the combination of the switching losses and the conduction losses. Each loss mechanism is presented in (2.7a) [7].

(2.7b) estimates gate charge loss of the switch-FET. The loss is proportional to gate charge of the device and the switching frequency. Generally, the larger size of the device, the larger the gate charge and therefore the loss increases.

(2.7c) estimates commutation loss of the switch-FET during switching.  $t_{on}$  and  $t_{off}$  can be estimated through the gate-charge diagram provided from the the device data-sheet [37, 38, 39]. Fig. 2.11(b) illustrates the gate charge diagram, and associated  $t_{on}$  and  $t_{off}$  can be estimated by (2.8) [7]. The loss consumes a large portion of power in the hard switching, especially with inductance as the load of the switch-FET [40].

(2.7d) estimates the output capacitance switching loss. The loss depends on output capacitance of the switch-FET, diode and associated paralleled parasitics. The loss is proportional to the area of the switch-FET and the diode as well as the switching frequency.

(2.7e) estimates the switch-FET's conduction loss. The magnitude of  $R_{on}$  of the switch-FET is the dominate power loss factor. The conduction loss is generally inverse proportional to the switch-FET size and scales with the switcher's output power.

(2.7f) estimates the conduction loss of Schottky diode,  $D_s$ . The maximum forward voltage drop,  $V_F$ , of the diode dominates the major power consumption. The lower the forward voltage drop, the lower the power loss during the operation.

Figure 2.11: (a) Switcher Stage Schematic; (b) High Side switch-FET Gate Charge Diagram [7]

$P_{loss \, switcher} = P_{loss \, Switching} + P_{loss \, Conduction}$

$$= (P_{lossDriver} + P_{lossCommutation} + P_{lossCout}) + P_{lossRon} + P_{lossDiode}$$

(2.7a)

$$\approx Q_g \cdot V_{gs} \cdot f_{sw} \tag{2.7b}$$

$$+\frac{1}{2} \cdot I_D \cdot V_{DC} \cdot (t_{on} + t_{off}) \cdot f_{sw}$$

(2.7c)

$$+\frac{1}{2} \cdot C_{out} \cdot V_{DC}^2 \cdot f_{sw} \tag{2.7d}$$

$$+ D \cdot I_D^2 \cdot R_{on} \tag{2.7e}$$

$$+ (1 - D) \cdot I_L \cdot V_F \tag{2.7f}$$

where  $Q_g$  is switch-FET total gate charge

- $V_{gs}$  is switch-FET gate-to-source turn-on votlage

- $f_{sw}$  is the average switching frequency

- $I_D$  is the drain current while switch-FET is on

- $t_{on}$  is switch-FET turn-on time

$$t_{off}$$

is switch-FET turn-off time

$C_{out}$  is total output capacitance around source node of switch-FET

- D is average duty ratio of switching pulses

- $R_{on}$  is switch-FET turn-on resistance

- $V_F$  is Schottky diode forward voltage

$$t_{on} = \frac{Q_{G(sw)}}{I_{driver(L \longrightarrow H)}}$$

(2.8a)

$$t_{off} = \frac{Q_{G(sw)}}{I_{driver(H \longrightarrow L)}}$$

(2.8b)

$$Q_{G(sw)} \approx Q_{GD} + \frac{Q_{GS}}{2} \tag{2.8c}$$

$$I_{driver(L\longrightarrow H)} = \frac{V_{drive} - V_{sp}}{R_{driver(L\longrightarrow H)} + R_g}$$

(2.8d)

$$I_{driver(L\longrightarrow H)} = \frac{V_{sp}}{R_{driver(H\longrightarrow L)} + R_g}$$

$$V_{sp} \approx V_{th} + \frac{I_D}{G_M}$$

(2.8e)

where  $Q_{G(sw)}$  is the approximated gate charge for a switch-FET

to move through a switching interval

$Q_{GS}$  is switch-FET gate-to-source charge

$Q_{GD}$  is switch-FET gate-to-drain ("Miller") charge

$I_{driver(L \longrightarrow H)}$  is the switcher driver current in the rising time

$I_{driver(H \longrightarrow L)}$  is the switcher driver current in the falling time

$R_{driver(L \longrightarrow H)}$  is the switcher driver pull-up resistance

$R_{driver(H \longrightarrow L)}$  is the switcher driver pull-down resistance

$R_g$  is the switch-FET gate resistance

$V_{sp}$  is the approximated switching point voltage (Fig. 2.11(b))

$V_{th}$  is the typical gate threshold voltage

$I_D$  is the drain current when switch-FET is on

$G_M$  is the switch-FET trans-conductance

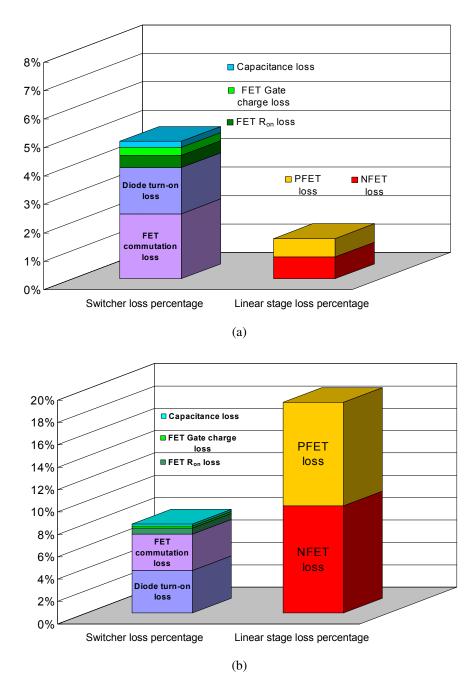

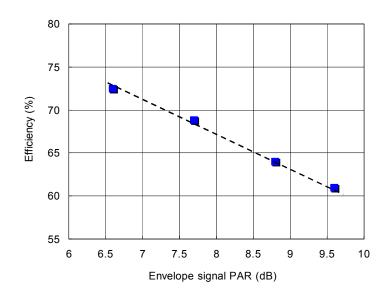

The overall envelope amplifier's power loss can be estimated by using  $(2.6) \sim (2.8)$ . Fig. 2.12(a) shows the simulated percentage of each power loss as a fraction of the overall DC input power of the amplifier using EDGE signal, operating at around 70 W output power. In this example, the linear stage consumes less than 2% of total input power due to the majority power contributed by the switcher. The switcher loss takes about  $5 \sim 6\%$  of the total input power. The results enable high efficiency performance for EDGE signals. Fig. 2.12(b) shows the percentage of each loss as a fraction of the total DC input power using a W-CDMA 7.7 dB PAR signal at similar output power level in Fig. 2.12(a). For this case, the switcher dynamic loss takes about  $7 \sim 8\%$  of the total DC power. The high percentage of Schottky diode turn-on loss can be improved by designing a synchronous switching buck converter [7] for the switcher. The linear stage loss takes about  $18 \sim 19\%$  of the total input power. This accounts for the high frequency power fully provided by the linear stage with this signal. In both examples, the commutation loss of the switch-FET plays an important role due to high switching frequency. A switch-FET chosen for low gate charge and low gate resistance is, therefore, preferable to a low on-resistance device for this application. Reducing the linear stage power loss using W-CDMA signals is discussed in chapter 4.

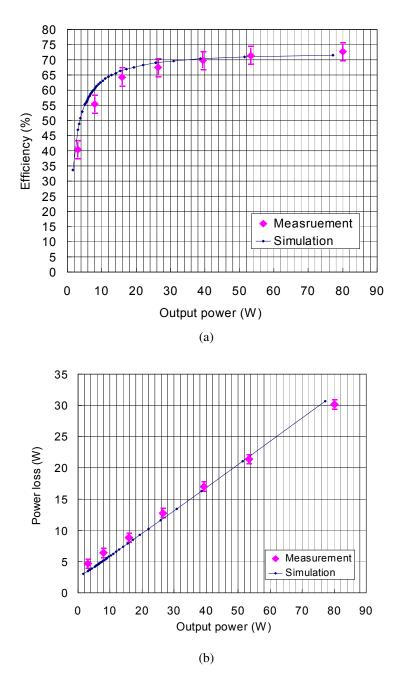

A 30 V peak voltage envelope amplifier, shown in Fig. 2.13, was assembled to verify the efficiency estimation results [6, 8, 9]. The comparison is carried out experimentally with constant resistance as the load of envelope amplifier. Table 2.1 summarizes the comparisons of simulated and measurement performance of the envelope amplifier for EDGE and W-CDMA signals. Good agreements are obtained between the model and the measurement results. The efficiency estimator neglects some small frac-

tion of dynamic power loss, such as switching ringing loss [41], power inductor core loss [42] and Schottky diode reverse recovery power loss.