### **UC Santa Cruz**

### **UC Santa Cruz Electronic Theses and Dissertations**

### **Title**

Design, Fabrication and Characterization of Micro-Electro-Mechanical Fabry-Perot Interferometer for use in Mid-Wave Infrared

### **Permalink**

https://escholarship.org/uc/item/5z13r7mr

#### **Author**

Kozak, Dmitry Alexander

### **Publication Date**

2013

Peer reviewed|Thesis/dissertation

### UNIVERSITY OF CALIFORNIA SANTA CRUZ

### DESIGN, FABRICATION AND CHARACTERIZATION OF MICRO-ELECTRO-MECHANICAL FABRY-PEROT INTERFEROMETER FOR USE IN MID-WAVE INFRARED

A dissertation submitted in partial satisfaction of the requirements for the degree of

DOCTOR OF PHILOSOPHY

In

**ELECTRICAL ENGINEERING**

By

**Dmitry Alexander Kozak**

**JUNE 2013**

| The Dissertation of Dmitry Alexander Kozak is approved: |

|---------------------------------------------------------|

| Professor John Vesecky, chair                           |

| Professor Nobuhiko Kobayashi                            |

| Professor David Koo                                     |

Tyrus Miller

Vice Provost and Dean of Graduate Studies

## **Table of Contents**

| Abstract                                                               | xviii |

|------------------------------------------------------------------------|-------|

| Acknowledgements                                                       | xxi   |

| Chapter 1 : Introduction                                               | 1     |

| 1.1 Introduction                                                       | 1     |

| 1.2 Optical filters                                                    | 2     |

| 1.3 Interferometry in the MWIR                                         | 4     |

| 1.4 Previous work on Fabry-Perot interferometers                       | 4     |

| 1.5 Motivation of dissertation                                         | 6     |

| 1.6 Contributions of the Thesis                                        | 7     |

| Chapter 2 : Fabry-Perot Interferometer Principles and Bragg Reflectors | 9     |

| 2.1 Introduction                                                       | 9     |

| 2.2 Short review of Fabry-Perot interferometer principles              | 9     |

| 2.3 Defects in Fabry-Perot Interferometers                             | 12    |

| 2.4 Bragg Reflectors                                                   | 14    |

| Chapter 3 : Device Design                                              | 18    |

| 3.1 Introduction                                                       | 18    |

| 3.2 Requirements                                                       | 18    |

| 3.3 Optical Design      |                         | 20 |

|-------------------------|-------------------------|----|

| 3.4 Optical Simulat     | tions                   | 22 |

| 3.5 Conclusion          |                         | 28 |

| Chapter 4 Mechanical    | l Design                | 29 |

| 4.1 Introduction        |                         | 29 |

| 4.2 Electrostatic ac    | tuation                 | 30 |

| 4.3 MUMPS Protot        | type                    | 31 |

| 4.3.1 MUMPS p           | rocess                  | 31 |

| 4.3.2 Layout            |                         | 32 |

| 4.3.3 Mechanica         | l modeling and testing  | 34 |

| Chapter 5 : First fabri | cation run              | 37 |

| 5.1 Introduction        |                         | 37 |

| 5.2 Considerations      | for process development | 37 |

| 5.3 Initial process     |                         | 40 |

| 5.4 SNF Process de      | evelopment              | 46 |

| 5.5 Mask design an      | d layout                | 47 |

| 5.6 Fabrication requ    | uirements               | 50 |

| 5.7 Layer depositio     | n                       | 51 |

| 5.8 Stress analysis .   |                         | 57 |

|   | 5.9 Bragg stack etching processes                                           | . 62 |

|---|-----------------------------------------------------------------------------|------|

|   | 5.10 Silicon membrane etching                                               | . 65 |

|   | 5.11 Combined etching                                                       | . 69 |

|   | 5.12 Backside etching                                                       | . 71 |

|   | 5.13 Bonding development                                                    | . 74 |

|   | 5.14 Substrates selection                                                   | . 75 |

|   | 5.15 Final Processing                                                       | . 76 |

|   | 5.16 Resulting chips                                                        | . 83 |

|   | 5.17 Bonded chips                                                           | . 88 |

|   | 5.18 Surface analysis                                                       | . 89 |

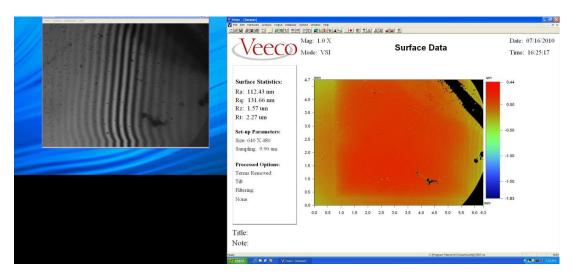

|   | 5.18.1 WE16&WE17: double Bragg stacks                                       | . 90 |

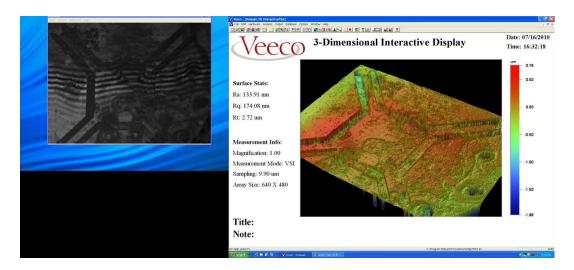

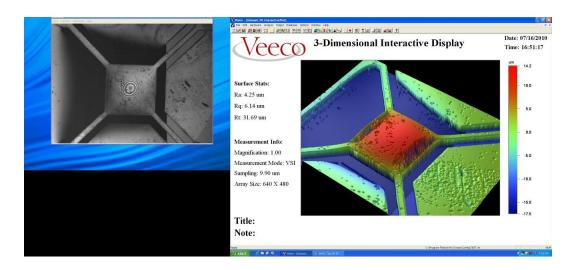

|   | 5.18.2 WE18&WE19: triple Bragg stacks                                       | . 91 |

|   | 5.19 Optical Testing                                                        | . 93 |

|   | 5.20 Bragg reflectors optical testing results and comparison to simulations | . 94 |

|   | 5.21 Bonded pair optical testing                                            | . 99 |

|   | 5.22 Conclusion                                                             | 100  |

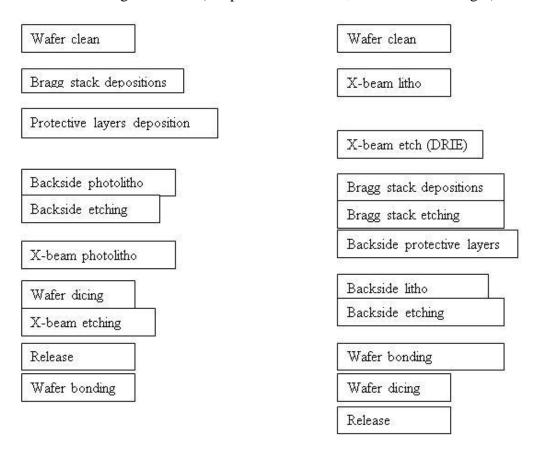

| C | hapter 6 : Second fabrication run                                           | 101  |

|   | 6.1 Introduction                                                            | 101  |

|   | 6.2 Process analysis and modifications                                      | 101  |

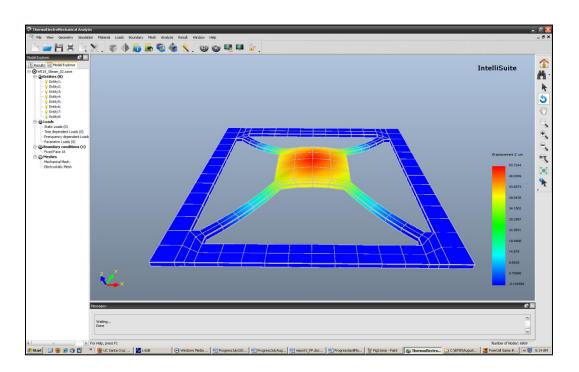

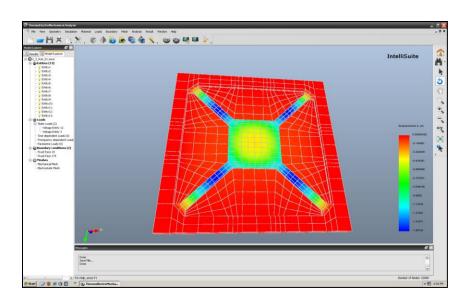

|   | 6.3 Stress simulations with input from fab            | 103 |

|---|-------------------------------------------------------|-----|

|   | 6.4 Modifications to Layout                           | 106 |

|   | 6.5 Modifications to the Process                      | 108 |

|   | 6.5.1 SOI Wafer                                       | 108 |

|   | 6.5.2 Different Silicon Etch                          | 109 |

|   | 6.5.3 Silicon Nitride Compensation                    | 110 |

|   | 6.6 Process flow for second run                       | 110 |

|   | 6.7 Analysis of fabricated chips                      | 111 |

|   | 6.8 Analysis of stress                                | 113 |

|   | 6.9 Attempts to reduce the bow                        | 114 |

|   | 6.9.1 Thermal annealing                               | 114 |

|   | 6.9.2 Compensating layer depositions                  | 116 |

|   | 6.9.3 Using silicon nitride in the Bragg stacks       | 117 |

|   | 6.10 Optical terms                                    | 117 |

|   | 6.11 Conclusion                                       | 118 |

| ( | Chapter 7 : Third fabrication run                     | 119 |

|   | 7.1 Introduction                                      | 119 |

|   | 7.2 Modifications to the previous Fabrication Process | 119 |

|   | 7.3 Layout modifications                              | 120 |

|   | 7.4 Substrate modification                                 | . 125 |

|---|------------------------------------------------------------|-------|

|   | 7.5 Stress Test Structures                                 | . 126 |

|   | 7.6 Fabrication Process                                    | . 128 |

|   | 7.7 Fabrication Cycle Results                              | . 128 |

|   | 7.8 Fabrication Issues                                     | . 129 |

|   | 7.9 Bow Reduction Results                                  | . 131 |

|   | 7.10 Optical terms                                         | . 141 |

|   | 7.11 Chip Bonding                                          | . 141 |

| C | Chapter 8 : Mechanical Actuation                           | . 143 |

|   | 8.1 Introduction                                           | . 143 |

|   | 8.2 Electrostatic Actuation                                | . 143 |

|   | 8.3 Analysis of electrostatic actuation                    | . 144 |

|   | 8.4 Magnetic Actuation                                     | . 146 |

|   | 8.5 Magnetic actuation results                             | . 150 |

|   | 8.6 Modifications to devices needed for magnetic actuation | . 153 |

|   | 8.7 Using permanent ring magnets                           | . 154 |

| C | Chapter 9 : Optical Testing                                | . 156 |

|   | 9.1 Introduction                                           | . 156 |

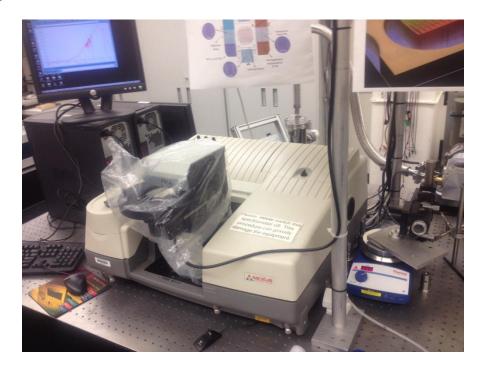

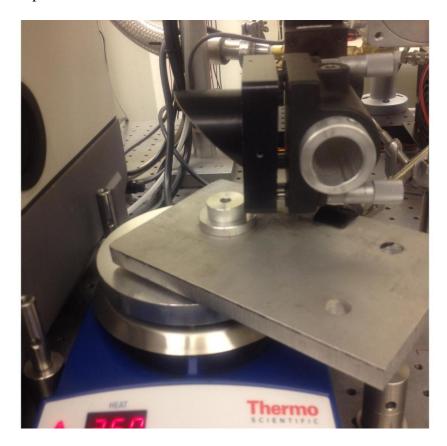

|   | 9.2 Optical setup                                          | . 156 |

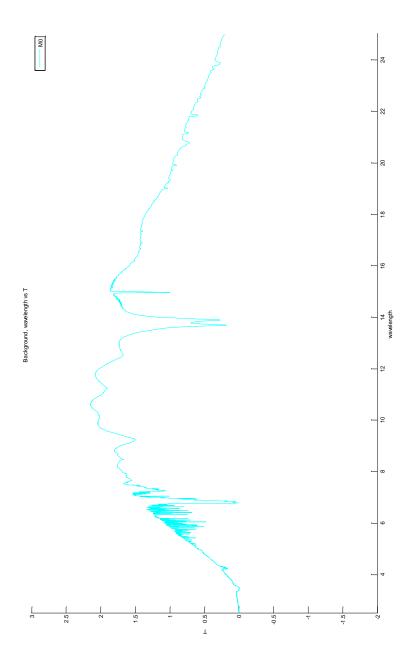

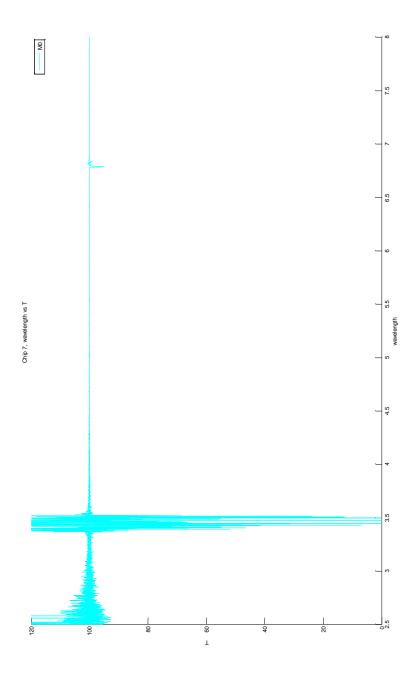

|   | 9.3 Calibration of the FTIR optical set-up          | 158 |

|---|-----------------------------------------------------|-----|

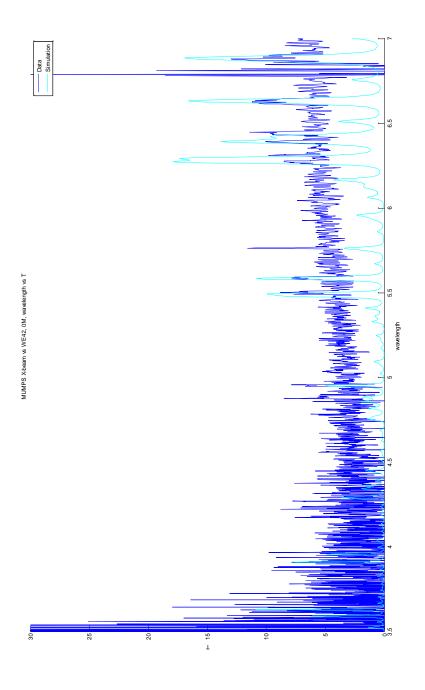

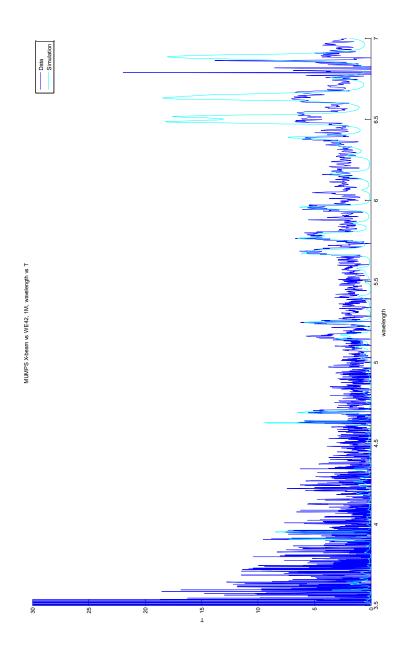

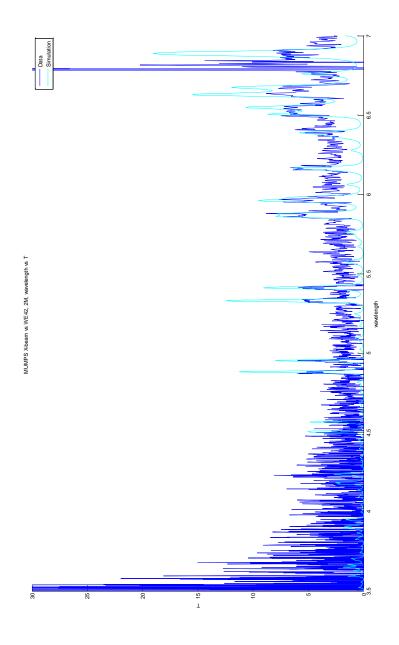

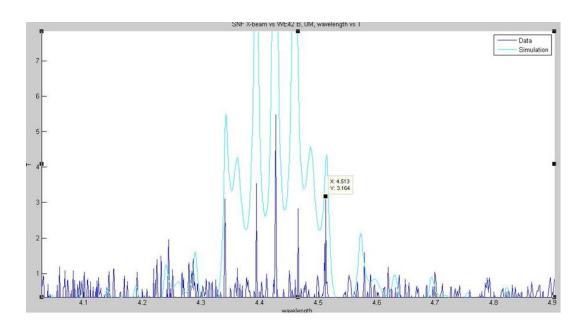

|   | 9.4 Optical testing results for MUMPS X-beam (MX)   | 163 |

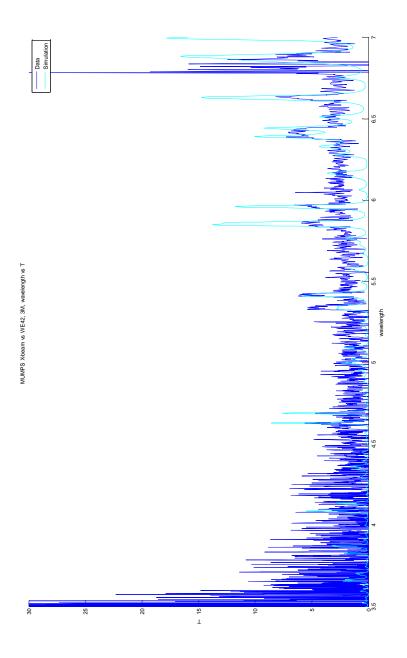

|   | 9.5 Optical Testing Results for Static FPI          | 166 |

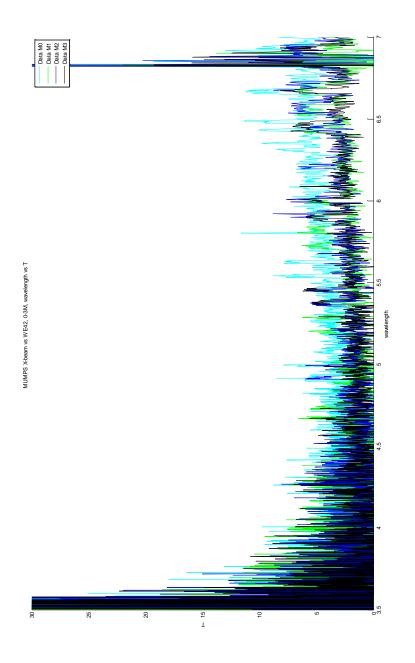

|   | 9.6 Optical Testing Results for Asymmetrical FPI    | 168 |

|   | 9.7 Optical Results for SNF-fabricated chips (SX-B) | 175 |

|   | 9.8 Summary of results                              | 184 |

| C | Chapter 10 : Summary and Conclusion                 | 186 |

| В | Bibliography                                        | 188 |

| Α | Appendix A                                          | 196 |

# **List of Figures**

| Figure 1.1: Basic schematic of an optical filter                                     | 3    |

|--------------------------------------------------------------------------------------|------|

| Figure 1.2: FPI device by Infra Tec                                                  | 5    |

| Figure 1.3: FPI device by UWA                                                        | 6    |

| Figure 1.4 Flow chart of the project                                                 | 8    |

| Figure 2.1: Illustration of a Fabry-Perot interferometer                             | 10   |

| Figure 2.2: Defects in FPIs. Adapted from Atherton [28]                              | 12   |

| Figure 2.3: Indices of refraction of common materials                                | 16   |

| Figure 3.1: Proposed integration mechanism to create a complete device out of filter | er   |

| layers (1 and 2), HgCdTe detector layer (3) and CMOS control and logic layer (4).    | . 19 |

| Figure 3.2: Simulations of Bragg reflectors                                          | 20   |

| Figure 3.3: Bragg reflectors                                                         | 21   |

| Figure 3.4: FPI simulations.                                                         | 23   |

| Figure 3.5: Layers in Double-Triple cavity FPI                                       | 24   |

| Figure 3.6: FPI simulations with addition of silicon layer                           | 25   |

| Figure 3.7: Layers for FPI device                                                    | 26   |

| Figure 3.8: Transmission simulations for FPI device                                  | 27   |

| Figure 4.1 General view of electrostatic actuation                                   | 30   |

| Figure 4.2: MUMPS SOI process [45]                                                   | 32   |

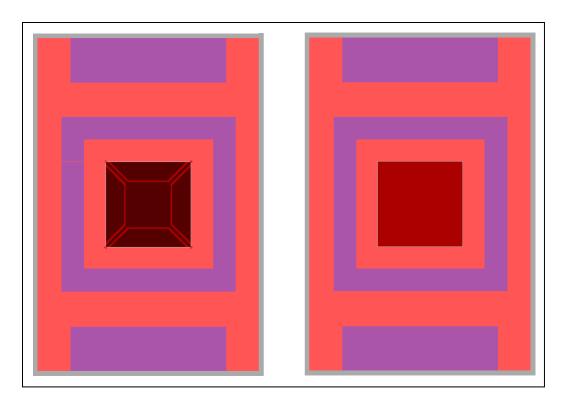

| Figure 4.3: Layout for MUMPS device                                                  | 33   |

| Figure 1.1: FFA model of Y-beam                                                      | 3/1  |

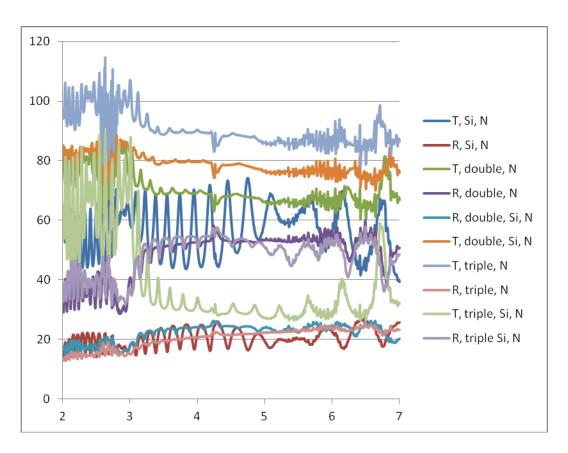

| Figure 4.5: Simulation of optical behavior of MUMPS X-beam                         | 35  |

|------------------------------------------------------------------------------------|-----|

| Figure 5.1: Starting SOI substrate                                                 | 41  |

| Figure 5.2: SOI with Bragg stacks                                                  | 42  |

| Figure 5.3: Substrate with etched Bragg stack                                      | 42  |

| Figure 5.4: Backside etching.                                                      | 43  |

| Figure 5.5: Unreleased X-beam                                                      | 43  |

| Figure 5.6: Released X-beam                                                        | 44  |

| Figure 5.7: Addition of silicon nitride layer                                      | 44  |

| Figure 5.8: Two parts of the Fabry-Perot interferometer                            | 45  |

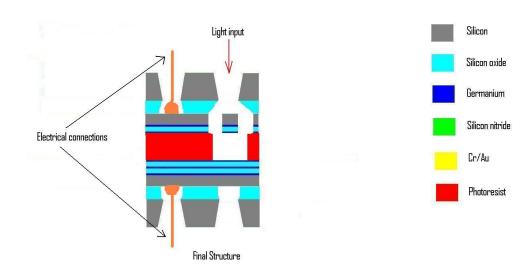

| Figure 5.9: Diagram of two bonded parts with electrical connections                | 47  |

| Figure 5.10: First mask layout with chip detail and actual mask                    | 48  |

| Figure 5.11: Second mask layout with chip detail                                   | 49  |

| Figure 5.12: Actual mask                                                           | 50  |

| Figure 5.13: SEM image of the deposited Bragg stack                                | 53  |

| Figure 5.14: SEM image of the alignment feature after metal etch                   | 54  |

| Figure 5.15: SEM image of the defects in Bragg stack                               | 55  |

| Figure 5.16: SEM image of alignment feature following Bragg stack etch             | 56  |

| Figure 5.17: Silicon wafer with triple Bragg stack                                 | 57  |

| Figure 5.18: Stress in 500 nm silicon nitride layer with different deposition      |     |

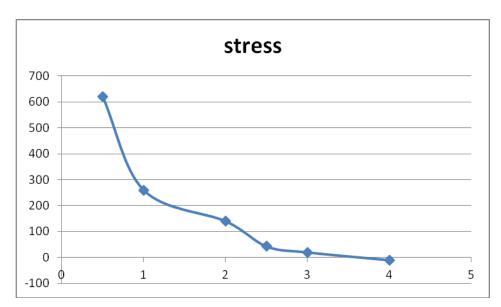

| conditions. Ordinate is stress in MPa and the abscissa is the ratio between high a | and |

| low frequency plasma deposition.                                                   | 60  |

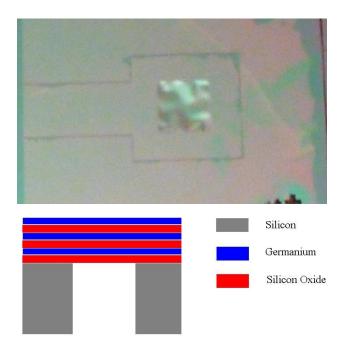

| Figure 5.19 Triple Bragg stack without silicon support                             | 61  |

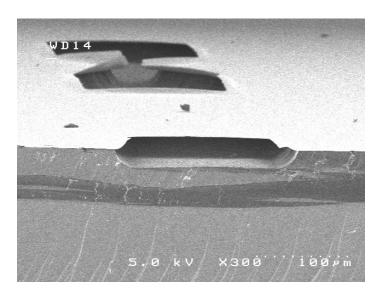

| Figure 5.20: SEM image of Bragg stack etched using consequtive wet etch 64         |

|------------------------------------------------------------------------------------|

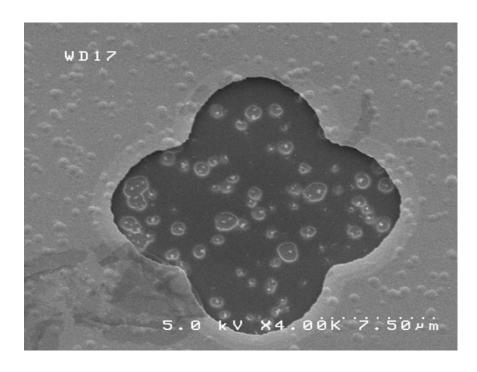

| Figure 5.21: SEM image of alignment mark mask demonstrating widening of features   |

|                                                                                    |

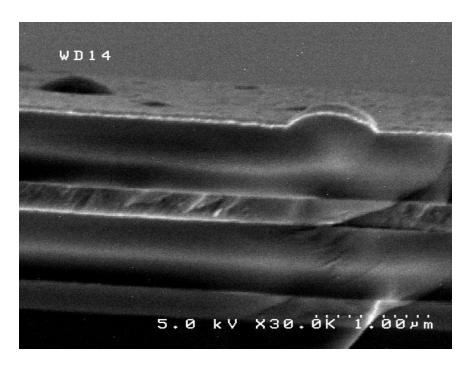

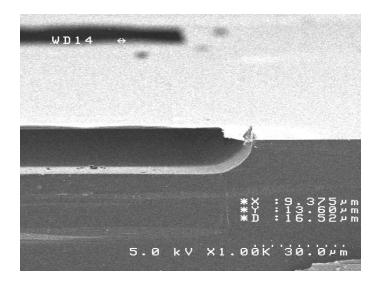

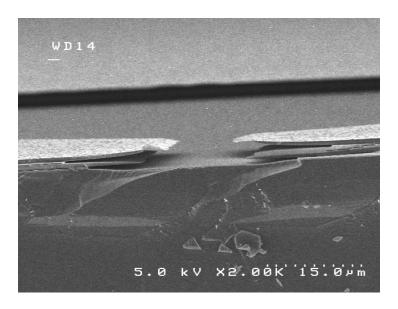

| Figure 5.22: SEM image of silicon etch after 5 minutes using HNA, showing severity |

| of undercut in narrow bridge device                                                |

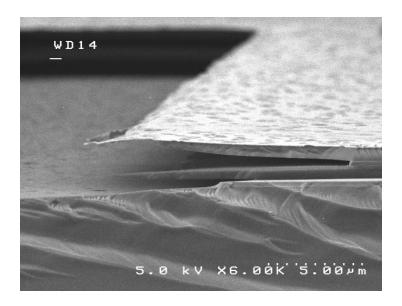

| Figure 5.23: SEM image of silicon etch after 5 minutes using HNA, with details of  |

| the hard mask                                                                      |

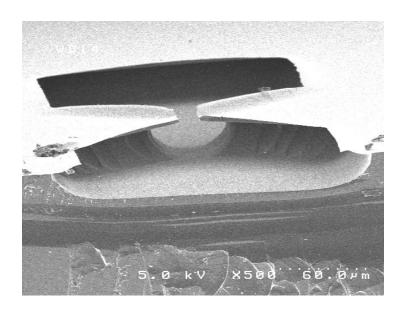

| Figure 5.24: SEM image of silicon etch after 10 minutes using HNA, showing effect  |

| of undercut on narrow feature                                                      |

| Figure 5.25: SEM image of silicon etch after 10 minutes using HNA, with high       |

| magnification showing detail of the hard mask                                      |

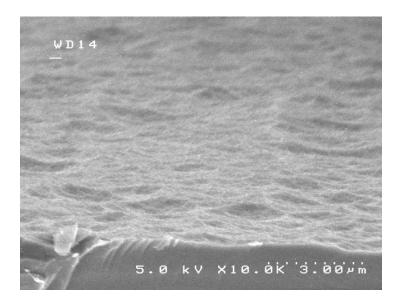

| Figure 5.26: SEM image of silicon surface after HNA etch, resulting in high        |

| roughness of resulting surface                                                     |

| Figure 5.27: SEM image of result of combined Bragg stack and silicon etching 69    |

| Figure 5.28: SEM image of result of combined Bragg stack and silicon etching, with |

| magnified section showing undercut in different layers                             |

| Figure 5.29: SEM image of result of combined Bragg stack and silicon etching 71    |

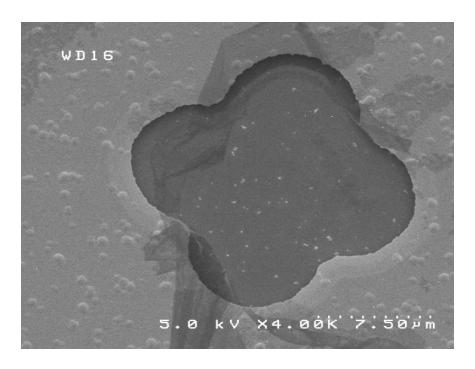

| Figure 5.30: Gold mask over etched silicon, showing the degree of undercutting the |

| hard mask                                                                          |

| Figure 5.31: Gold mask over etched silicon, showing rough mask edges resulting     |

| from undercutting and smooth edge of window underneath                             |

| Figure 5.32: Fabrication flow: step 1: substrate                                   |

| Figure 5.33: Fabrication flow: step 2: Bragg stack deposition                       |

|-------------------------------------------------------------------------------------|

| Figure 5.34: Fabrication flow: step 3: silicon nitride deposition                   |

| Figure 5.35: Fabrication flow: step 4: backside etch mask patterning                |

| Figure 5.36: Fabrication flow: step 5: backside etch mask removal                   |

| Figure 5.37: Fabrication flow: step 6: backside etch                                |

| Figure 5.38: Fabrication flow: step 7: X-beam mask patterning                       |

| Figure 5.39: Fabrication flow: step 8: attachment to handle wafer                   |

| Figure 5.40: Fabrication flow: step 9: X-beam etch and release                      |

| Figure 5.41: Fabrication flow: step 10: protective layer removal                    |

| Figure 5.42: Fabrication flow: step 11: bonding                                     |

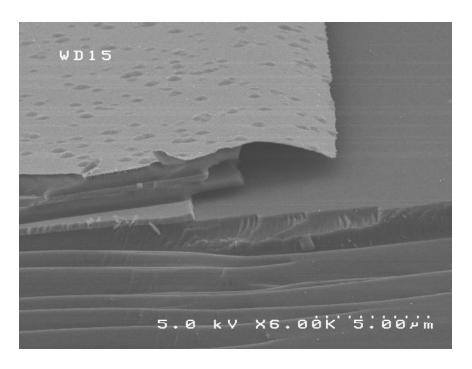

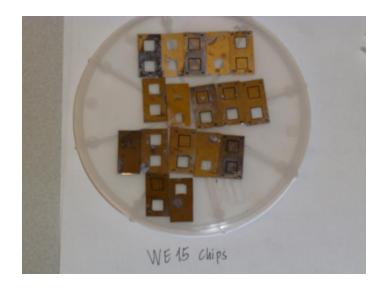

| Figure 5.43: Photograph of WE 15 chips. See-though membranes were destroyed         |

| during processing. 84                                                               |

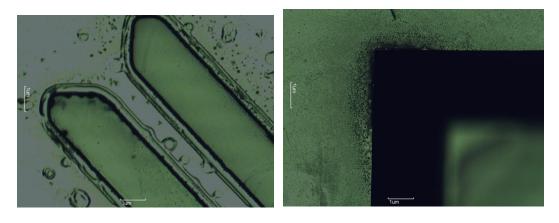

| Figure 5.44: Details of WE 15 chips, showing etching of the X-beam springs and      |

| corner of backside window                                                           |

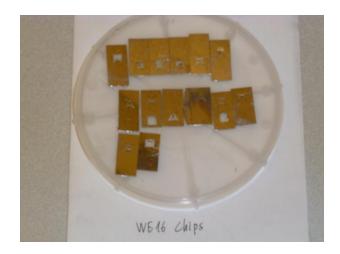

| Figure 5.45: Photograph of WE16 chips. Good chips are chips 1, 2, 3, 5 (from right) |

| in row 1, 1 and 6 in row 2, and 2 in row 3                                          |

| Figure 5.46: Detail of WE16 chips, showing uneven etch of the spring                |

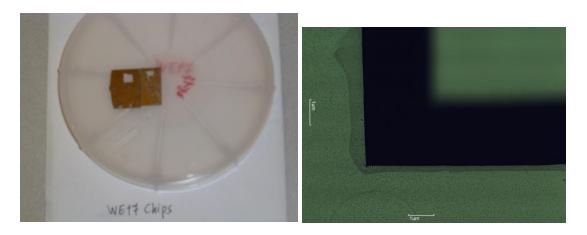

| Figure 5.47: Photograph of WE17 chips with detail of backside window                |

| Figure 5.48: Photograph of WE18 chips, showing defect chips (chip 4 in row 1, chip  |

| 3 in row 2, and chip 1 in row 3)                                                    |

| Figure 5.49:WE18 chip details show misalignment of X-beam to backside etching. 87   |

| Figure 5.50: WE18 chip details show incomplete etch of the spring                   |

| Figure 5.51: WE18 chip details show uneven etch of the spring                        | . 87 |

|--------------------------------------------------------------------------------------|------|

| Figure 5.52: Photograph of WE19 chips. Chips 1-4 and 7 in row 1, chip 2 in row 2     | ·,   |

| and chip in row 3 have both membranes intact                                         | . 88 |

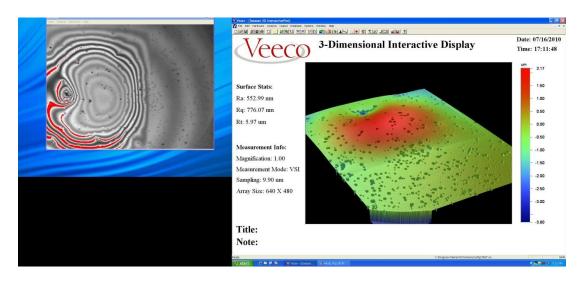

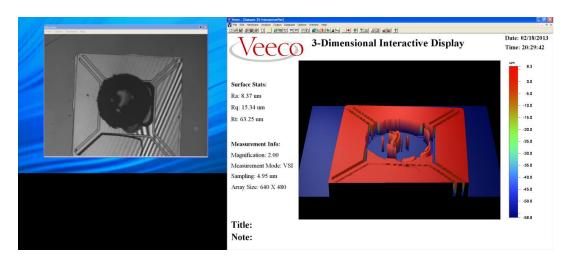

| Figure 5.53: Surface of WE15 chip membrane                                           | . 89 |

| Figure 5.54: Surface of WE15 chip X-beam                                             | . 90 |

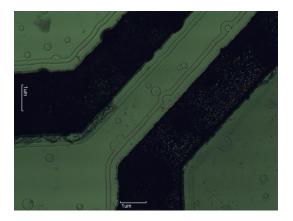

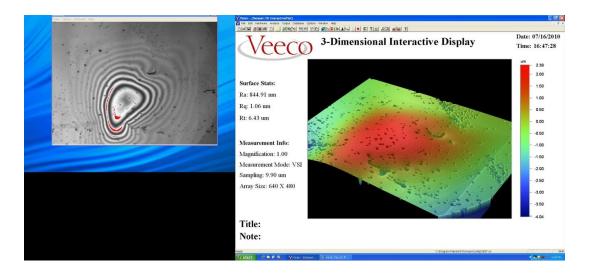

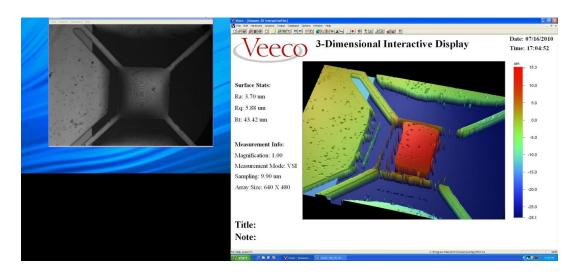

| Figure 5.55: Surface scan of WE17 X-beam                                             | . 91 |

| Figure 5.56: Surface scan of WE17 membrane                                           | . 91 |

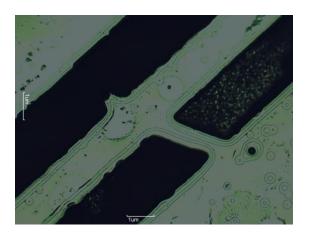

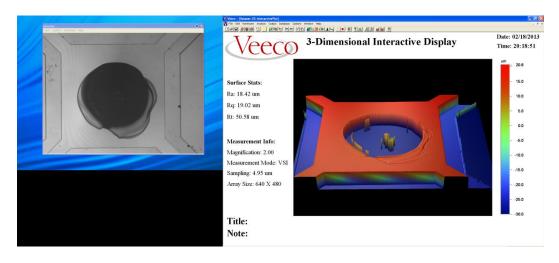

| Figure 5.57: Surface scan of WE18 X-beam                                             | . 92 |

| Figure 5.58: Surface scan of WE18 membrane                                           | . 92 |

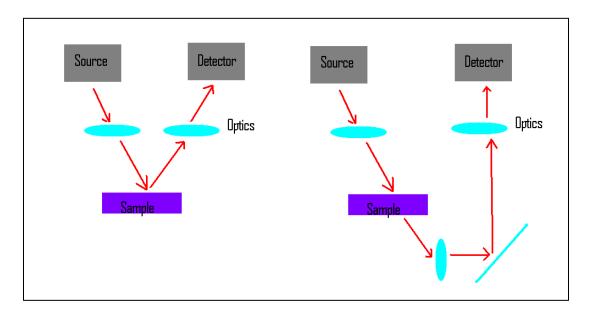

| Figure 5.59: Basic schematic of optical testing setup, reflection and transmission   | . 93 |

| Figure 5.60: Transmission and reflection from fabricated chips (intensity (relative) | vs.  |

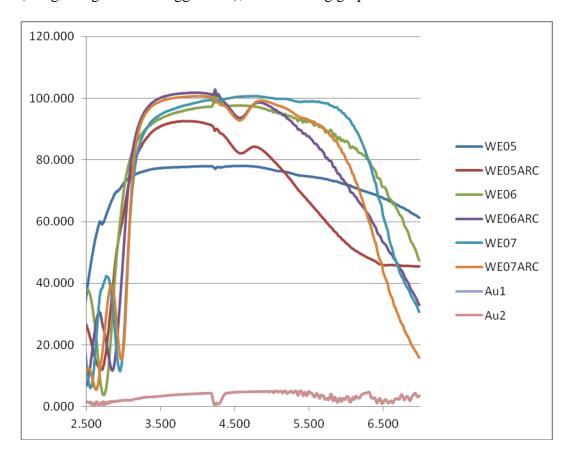

| wavelength in microns)                                                               | . 95 |

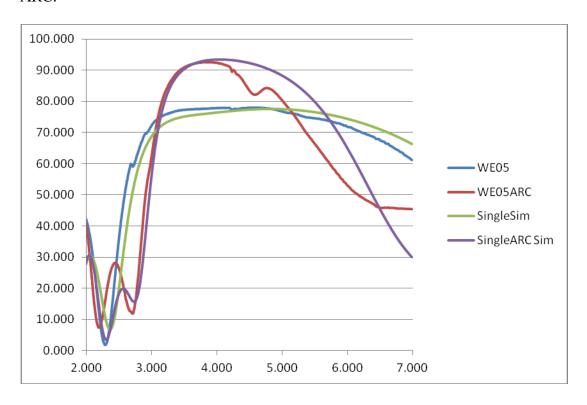

| Figure 5.61: Simulation and test of reflection from fabricated chips, single stack   |      |

| (intensity (relative) vs. wavelength in microns)                                     | . 96 |

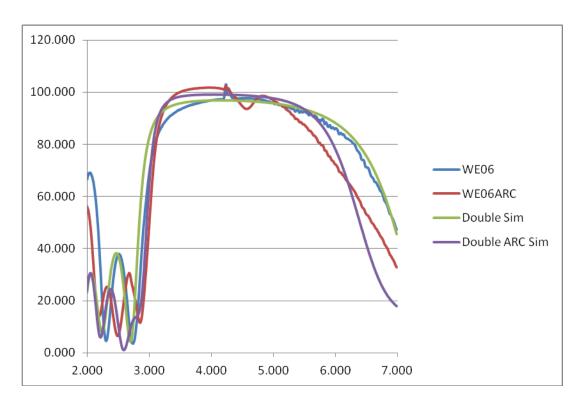

| Figure 5.62: Simulation and test of reflection from fabricated chips, double stack   |      |

| (intensity (relative) vs. wavelength in microns)                                     | . 97 |

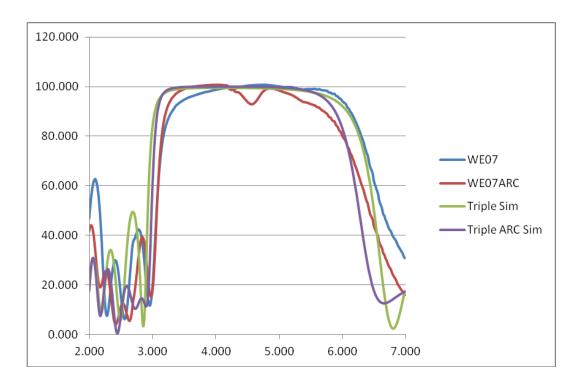

| Figure 5.63: Simulation and test of reflection from fabricated chips, triple stack   |      |

| (intensity (relative) vs. wavelength in microns)                                     | . 98 |

| Figure 5.64: Experimental optical results for silicon, double and triple chips,      |      |

| (intensity (relative) vs. wavelength in microns)                                     | . 99 |

| Figure 6.1 Comparison of fabrication flow                                            | 103  |

| Figure 6.2 Simulation of the deformed X-Beam shape                                   | 104  |

| Figure 6.3 Simulation of the deformed X-Beam shape with silicon nitride        |      |

|--------------------------------------------------------------------------------|------|

| compensating layer                                                             | 106  |

| Figure 6.4: Schematic overlay and bonding                                      | 108  |

| Figure 6.5: Bow in the X-beam component                                        | 112  |

| Figure 6.6: SOI fabrication process with resulting stress                      | 113  |

| Figure 6.7: Wafer-scale stress caused by the Bragg stack                       | 113  |

| Figure 7.1: BOX compensation                                                   | 120  |

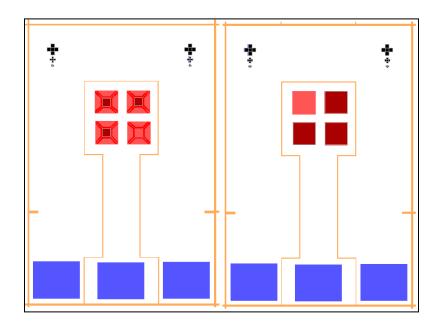

| Figure 7.2: Modified layout of the chips with Bragg stack in white areas       | 121  |

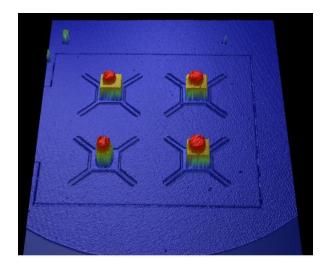

| Figure 7.3: Array of 500 μm by 500 μm devices (4-array)                        | 122  |

| Figure 7.4: Array of 250 μm by 250 μm devices (9-array)                        | 123  |

| Figure 7.5: Four masks used for the fabrication                                | 124  |

| Figure 7.6: Layout of Bow Tie stress test structures                           | 126  |

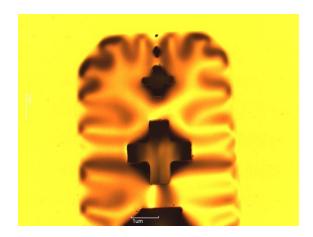

| Figure 7.7: SEM image of V-beam test structures                                | 127  |

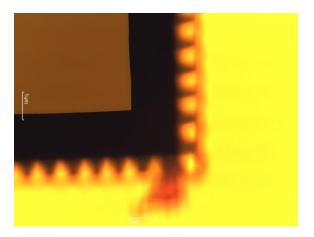

| Figure 7.8: Metallization Remaining on WE54 wafers, 4-array chips              | 130  |

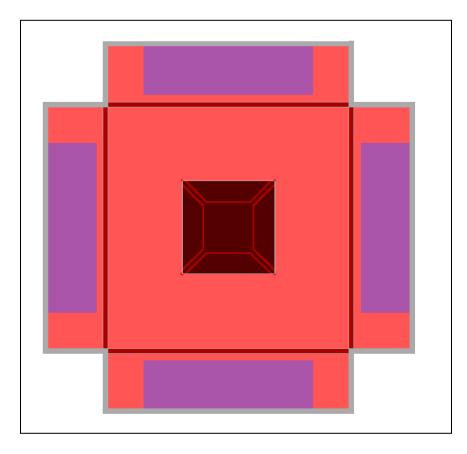

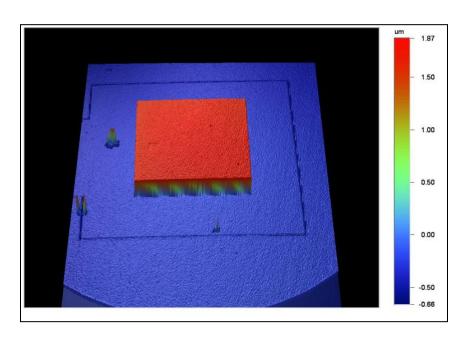

| Figure 7.9: Membrane with Bragg stack, from wafer WE52                         | 131  |

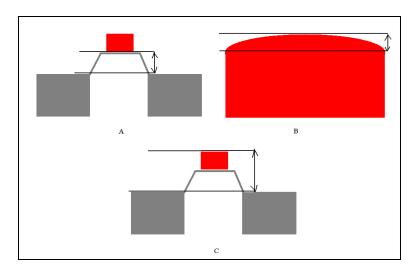

| Figure 7.10: Parameters in the bow discussion                                  | 132  |

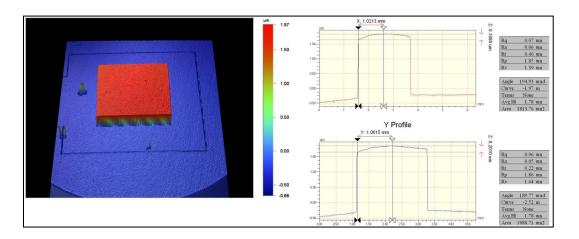

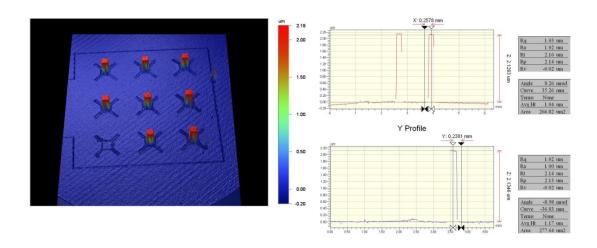

| Figure 7.11: 3-D and 2-D scan of membrane with Bragg stack, single pixel chip, |      |

| WE52                                                                           | 137  |

| Figure 7.12: 3-D and 2-D scan of 9-array X-beams, WE53                         | 138  |

| Figure 7.13: 3-D and 2-D scan of membrane without Bragg stack, single-pixel ch | iip, |

| WE53                                                                           | 138  |

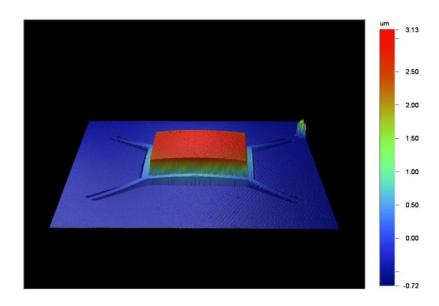

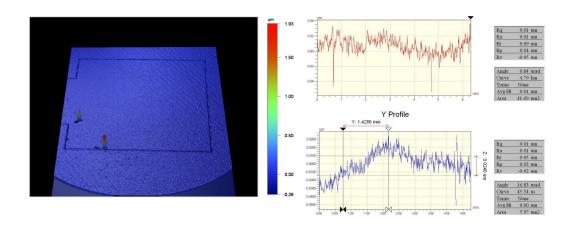

| Figure 8.1: Surface scan of WE42 X-beam with R2 magnet and glue residue        | 148  |

| Figure 8.2: Surface scan of MUMPS X-beam with R1 magnet and glue residue                    | 149 |

|---------------------------------------------------------------------------------------------|-----|

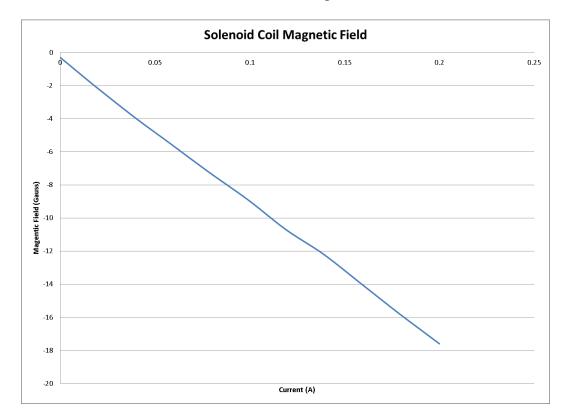

| Figure 8.3: Magnetic Field of Solenoid Coil. The negative sign of the field indicate        | tes |

| that with the polarity of the wires at the time of testing, the field direction is into the | he  |

| solenoid                                                                                    | 150 |

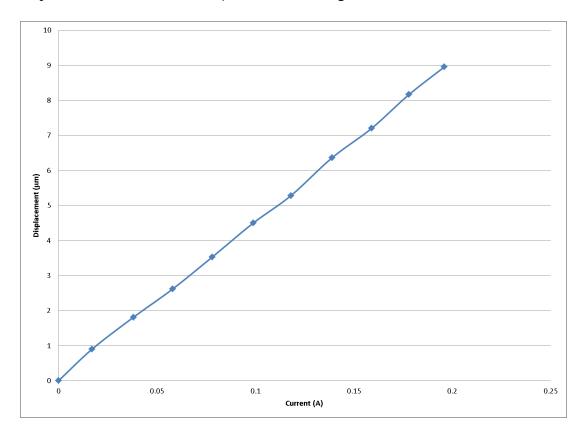

| Figure 8.4: Deflection of MUMPS X-beam with D1 magnet                                       | 151 |

| Figure 8.5: Deflection of MUMPS X-beam with R1 magnet                                       | 152 |

| Figure 8.6: Deflection of WE42 X-beam with R2 magnet                                        | 153 |

| Figure 9.1: NPS FTIR                                                                        | 157 |

| Figure 9.2: NPS FTIR: hot plate and mirror                                                  | 158 |

| Figure 9.3: Background radiation for FTIR                                                   | 160 |

| Figure 9.4: Aperture transmission calibration                                               | 162 |

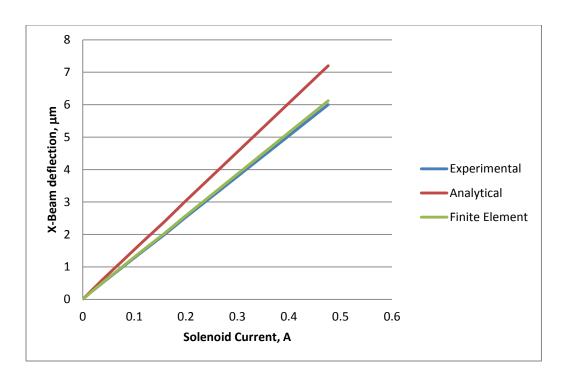

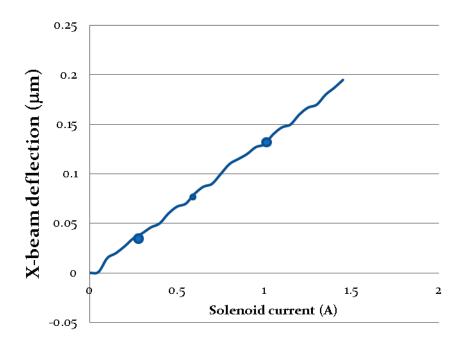

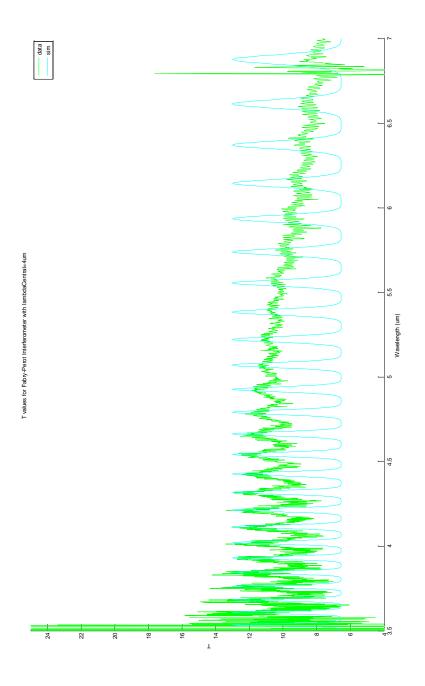

| Figure 9.5: Transmission through MUMPS X-beam with magnet                                   | 164 |

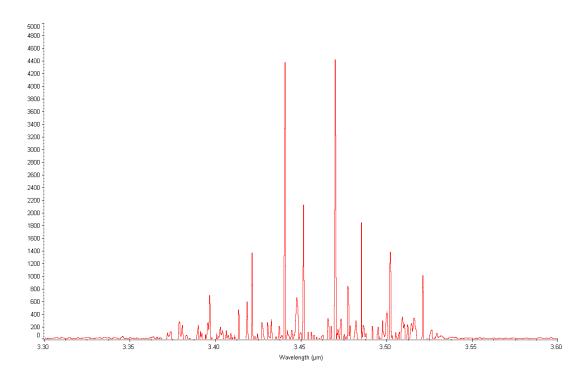

| Figure 9.6 Transmission through static FPI over a 300 nm range centered on 3.45             | μm  |

|                                                                                             | 167 |

| Figure 9.7: Transmission, MX-B device with no magnets                                       | 169 |

| Figure 9.8: Transmission, MX-B device with one magnet (26 Gauss)                            | 170 |

| Figure 9.9: Transmission, MX-B device with 2 magnets (52 Gauss)                             | 171 |

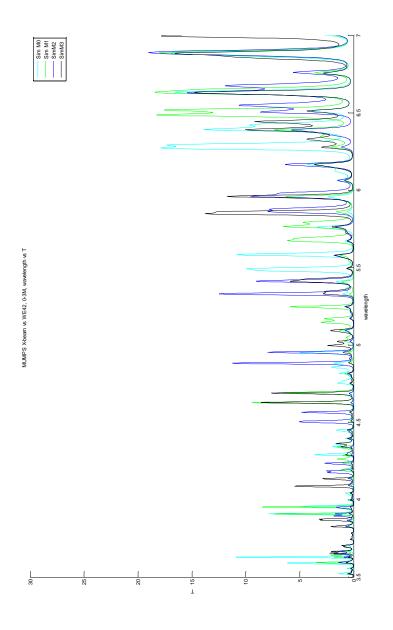

| Figure 9.10: Transmission, MX-B device, 3 magnets (88.6 Gauss)                              | 172 |

| Figure 9.11: Transmission simulation, MX-B device, for 0, 1, 2 and 3 magnets,               |     |

| showing tuning of device                                                                    | 173 |

| Figure 9.12: Transmission, MX-B device, experimental data for 0, 1, 2, and 3                |     |

| magnets                                                                                     | 174 |

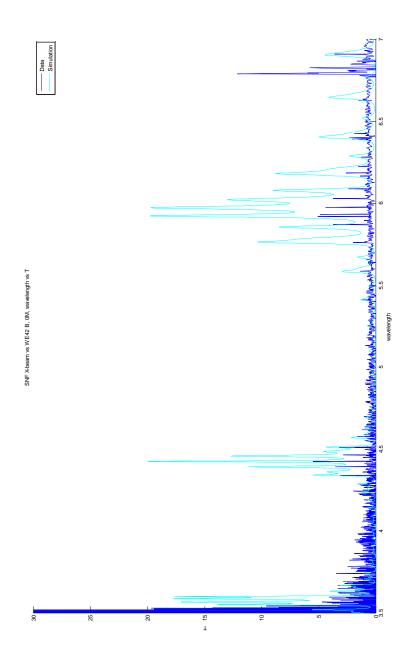

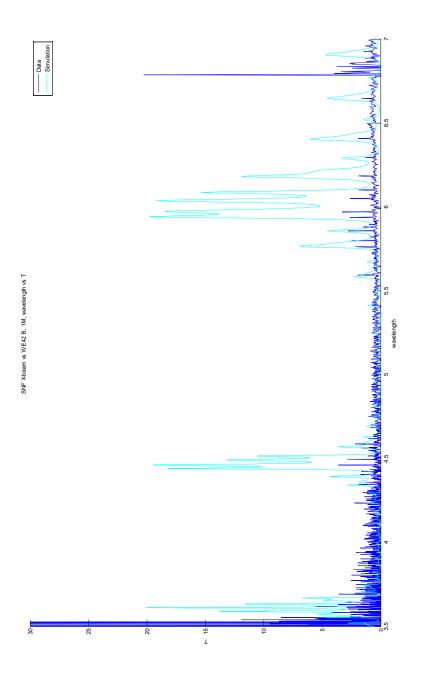

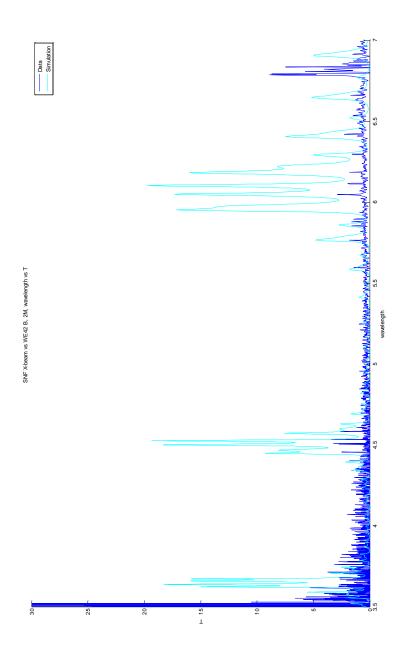

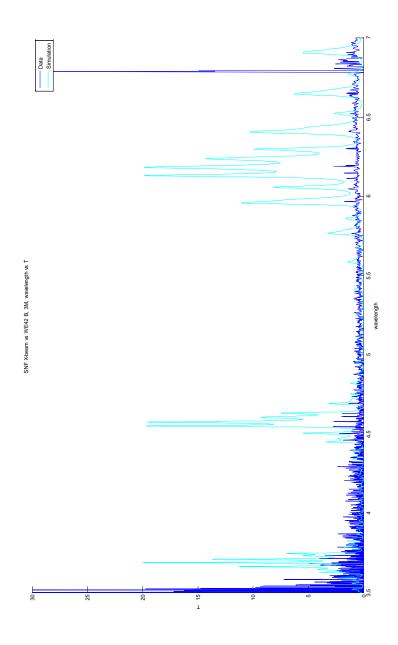

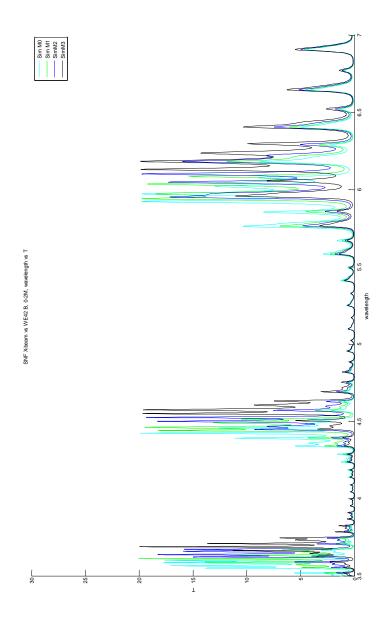

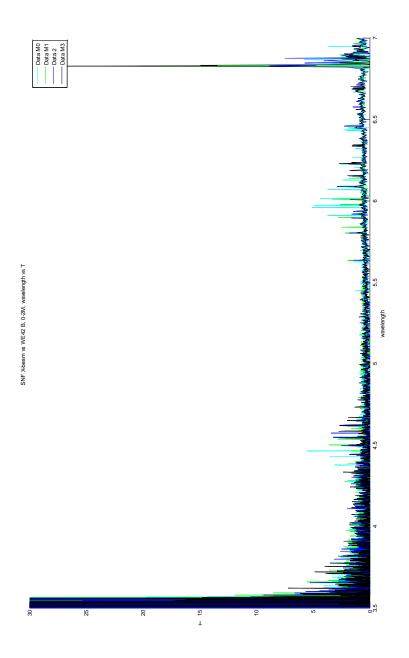

| Figure 9.13: Transmission, SX-B device with no magnets                             |

|------------------------------------------------------------------------------------|

| Figure 9.14:Transmission, SX-B device with one magnet (26 Gauss)                   |

| Figure 9.15: Transmission, SX-B device with two magnets (52 Gauss)                 |

| Figure 9.16:Transmission, SX-B device with three magnets (88.6 Gauss)              |

| Figure 9.17:Transmission simulations, SX-B device with 0, 1, 2, and 3 magnets.     |

| Note change in peak position with number of magnets                                |

| Figure 9.18:Transmission, SX-B device with combined data for 0, 1, 2, and 3 magnet |

|                                                                                    |

| Figure 9.19 Detail of SX-B. 0M transmission                                        |

### **List of Tables**

| Table 5.1 Stress in Materials                                                    |

|----------------------------------------------------------------------------------|

| Table 6.1: Effect of high temperature on bowing                                  |

| Table 7.1: SOI wafers used in several fabrication cycles                         |

| Table 7.2: WE52 component measurements                                           |

| Table 7.3: WE53 component measurements                                           |

| Table 7.4:WE54 component measurements                                            |

| Table 7.5: X-beam with Bragg                                                     |

| Table 7.6: X-beam with Bragg, with post-processing                               |

| Table 8.1: The mechanical spring constants for the X-beam components             |

| Table 8.2: Magnetic field on the surface of three magnets                        |

| Table 8.3: Permanent Ring Magnets B-Field and corresponding solenoid current 155 |

#### **Abstract**

DESIGN, FABRICATION AND CHARACTERIZATION OF MICRO-ELECTRO-MECHANICAL FABRY-PEROT INTERFEROMETER FOR USE IN MID-WAVE INFRARED

### Dmitry Alexander Kozak

Micro-Electro-Mechanical Systems (MEMS) allow scaling down and integration of conventional scientific instrumentation. In particular, advancements in fabrication have made possible the creation of small, precise and inexpensive versions of optical components and systems.

Optical components for the use in mid-wave infrared (MWIR) range, 3-5  $\mu$ m wavelength, are of particular interest for their ability to detect various organic chemical compounds and to determine the temperature of objects based on their radiation emission. High sensitivity, but low spectral resolution of optical detectors in the MWIR region requires addition of optical filters to provide spectral information.

In this thesis we describe the design, fabrication, and testing of a MEMS-based optical filter that combines a Fabry-Perot interferometer with dielectric Bragg reflectors, using magnetic actuation.

The research started with identification of the problem, complete literature search to identify the existing solutions. A novel design for an improved optical filter was proposed. Optical and mechanical models were created, and materials were chosen that correlated to the optical model. Fabrication flow was developed for robust and

wafer-scale process that achieves high yield and improves optical performance.

Three iterations of fabrication cycle resulted in improvement of optical characteristics of the devices by three orders of magnitude.

Mechanical method of magnetic actuation was developed that allows precise movement across the entire range of MWIR. Optical results from the first device were shown to correlate with mechanical and optical models.

To my wife Victoria

### Acknowledgements

This work is dedicated to everyone who has helped me along the way, my family, colleagues and mentors.

Especially I would like to thank the members of the dissertation reading committee: Professor John Vesecky, Professor David Koo, and Professor Nobuhiko Kobayashi for their support and help throughout this work.

Many thanks to my adviser Dr. Kubby for his mentoring along the way.

I would like to thank EPIR Technologies for sponsoring this project and all of their support.

Special thanks to Dr. Grbovic, Dr. Alves, Dr. Kearney and Dr. Karunasiri at Naval Post-graduate School for all the help with optical set-up, testing and analysis.

### **Chapter 1 : Introduction**

### 1.1 Introduction

This thesis is but one part of the research performed over the past seven years at UCSC. Other projects worked on by Dmitry A. Kozak include

- Wafer-scale fabrication of NEMS switch based on carbon nano-fiber, done in collaboration with NASA Ames research center.

- Design and fabrication of MEMS-based electric eel battery, in collaboration with Dr. Kubby and Dr. Fernandez.

- Electric Eel Project in collaboration with Dr. Isaacson and Dr. Pantchenko.

- Design, modeling and fabrication of Lamellar grating optical filter, sponsored by EPIR.

This thesis describes only the most complete and most important project done over the years.

The Mid-wave infrared (MWIR) spectral range from 3-5 µm has recently been of great interest due to its variety of applications in chemical sensing [1,2] and astronomy [3], as numerous gases have distinct absorbance bands in this range [4]. MWIR detectors can have a very high sensitivity, but due to their wide-band response, the spectral resolution is very low [5]. Large mechanically controlled optical filters have been added to the system [6], although these high resolution optical filters are expensive and hard to adapt for all the desired applications. Availability of individually controlled pixel detectors allows for high-density focal

plane arrays, but requires a device that can provide individually controlled filtering for each pixel for fast narrow waveband scanning. It is our goal to create technology that would combine the highest quality detector and filter components to create low-cost, easy to manufacture optical devices that have high sensitivity and spectral resolution for in a wide variety of applications.

### 1.2 Optical filters

The first optical filter that broke down the incoming light into its spectral components is, arguably, a prism. Science has come a long way from using these devices as mere toys to realizing that there is great amount of information that could be obtained from the observation of different spectral lines. Amount of emission or absorption at specific wavelength can provide information about the relative composition of a gas [7] or can be used to determine the temperature of an object [8].

For many applications the detectors can be made to respond to a very narrow wavelength range [9]; therefore reading from an array of detectors, each centered on a specific region of absorption, can give the required spectral information. This approach, however, is very expensive.

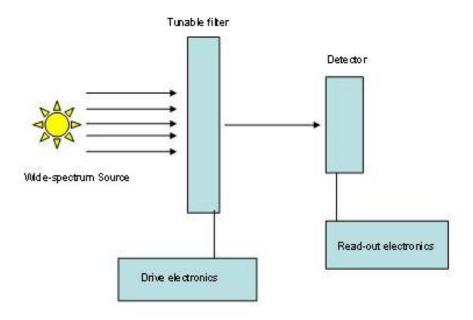

Another approach would be to have a wide-band, sensitive detector and a tunable filter that allows only certain wavelength of input light to reach it. The basic diagram of such a device is shown below in Fig. 1.1. A wide-band emitter source, which can be either a black body or an LED, is used to provide the input light across all the wavelengths of interest. A tunable filter, controlled by electronics, selectively passes

only a narrow band of incoming light. A detector that is designed for a specific region is placed immediately after the filter, and provides read-out of the signal strength.

Figure 1.1: Basic schematic of an optical filter

Filters can be either static or dynamic. Static filters, such as Bragg reflectors, are designed to pass or reflect only a narrow bandwidth of light [10]. This approach suffers from the same problems as having arrays of narrowly tuned detectors: they are expensive, can take up large areas and require multiple redundant elements.

Dynamic filters overcome these problems by having just one filter and one detector.

With the ability to tune the filter, spectral information can be obtained. An example of the most commercially popular optical filter is a motor driven diffraction grating, which is an integral part of such scientific instruments as monochromators [11].

### 1.3 Interferometry in the MWIR

The region of 3-5 µm, known as mid-wave infrared, has been of interest, in particular to chemists, for several decades [12]. In this region most organic compounds have very distinct absorption lines, and interferometry allows for easy identification of components and their relative composition [2]. The most common instrument used in chemistry labs for this purpose is the Fourier Transform Infrared Spectroscope (FTIR) [13]. This device uses a mirror moved by a mechanical motor to obtain spectra. While very precise, these devices are very large, expensive and consume large amounts of power.

The usefulness of these devices for chemists has driven extensive work to find an alternative that would be smaller and cheaper, while still providing the same accuracy and spectral range [14].

With the emergence of micro-electro-mechanical systems (MEMS), it was realized that the combination of mechanical movement, low cost, small size, and precision afforded by MEMS would be a good fit for making MWIR spectroscopes more efficient. Most of the projects involve scaling down existing spectroscopic instruments, such as Michelson interferometer, Lamellar grating interferometer, and Fabry-Perot interferometer [9, 15].

### 1.4 Previous work on Fabry-Perot interferometers

Large Fabry-Perot interferometers have been used in astronomy since the 1950s [16]. Lately there has been work on creating small, light and inexpensive filter/detector devices, starting with NIR and moving into MWIR and LWIR [17].

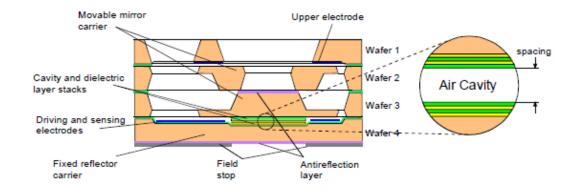

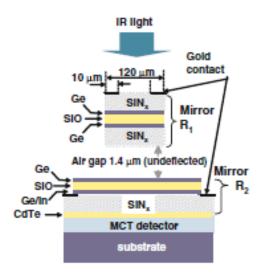

Scaling down infrared detectors allows them to be coupled with MEMS-based optical filters in several ways. Integration in a package has been done by the InfraTec Corporation, which has created a commercial product based on a Fabry-Perot filter made out of several layers of bonded silicon wafers, with Bragg stack mirrors made out of silicon and silicon dioxide layers [18]. Schuler et al. gives an excellent summary of the theory and an extensive overview of several technologies [19].

Figure 1.2: FPI device by Infra Tec

Monolithic integration has been done by Martyniuk, Antoszewski, Musca, Dell, and Faraone at the University of Western Australia, who have worked on the monolithic integration of a HgCdTe detector with a MEMS filter, that uses a Bragg stack composed of germanium and silicon oxide layers on a silicon nitride structural layer [20-22].

Figure 1.3: FPI device by UWA

### 1.5 Motivation of dissertation

While the work done by the InfraTec and the UWA group has been extensive and has also resulted in a commercial device by InfraTec, there is room for improvement. The InfraTec devices have low travel distance, requiring two separate devices to cover the 3-5 mm range [23]. Also, their integration with the detector in a package makes assembly cost high and reduces the yield. Such devices cannot be cheaply integrated into large multi-channel arrays to provide fast and efficient finger-printing of chemical agents or FPGA arrays for vision.

By partnering with the manufacturer of HgCdTe detectors, EPIR Technologies, we were able to create a device that is highly selective in optical filtering and allows integration into large arrays.

This dissertation describes the development of an optical filter that has a narrow bandwidth, can be controlled over large spectrum, and can be integrated into single-pixel devices for chemistry applications and large arrays for vision applications.

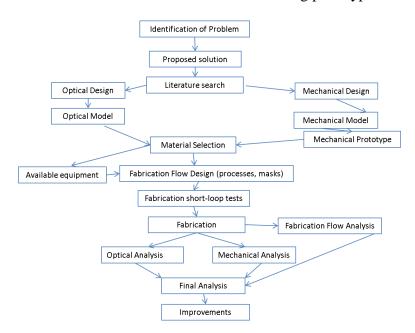

The overall flow of the project follows the cycle shown in Fig. 1.4, with multiple iterations of the cycle described in this work. Starting from the identification of the problem and existing solutions, requirements from optical and mechanical design have to be brought together. Materials have to be analyzed that would accomplish the goals of optical and mechanical behavior and also fit the fabrication requirements.

Fabrication flow has to be designed, executed and analyzed, with consequent testing of the devices. Following the identification of problems, the process has to be repeated again.

#### 1.6 Contributions of the Thesis

This dissertation describes in detail three iterations of the cycle described above.

- The problem of tunable optical filters in MWIR that can be integrated into arrays has been identified.

- Solution of tunable MEMS filter based on the principle of Fabry-Perot interferometer has been proposed.

- Optical and mechanical theoretical analysis has been performed, resulting in optical and mechanical models of the proposed devices.

- Materials that can be used to fabricate the tunable filter have been identified.

- Fabrication flow that uses equipment available at Stanford Nanofabrication

Facility has been designed.

- A series of short-loop tests to verify the possibility of the proposed fabrication flow have been performed.

- Three iterations of the project have been performed, resulting in at least one order of magnitude improvement in optical characteristics with each iteration.

- Novel method of mechanical actuation of the devices has been proposed and executed, resulting in devices that can provide filtering over the entire region of MWIR.

- Optical testing of the devices has confirmed the correlation between models of the devices and observations with the first working prototypes.

Figure 1.4 Flow chart of the project

# Chapter 2 : Fabry-Perot Interferometer Principles and Bragg Reflectors

#### 2.1 Introduction

In this chapter, a short overview of an optical filter known as a Fabry-Perot interferometer is given. Figures of merit and filtering behavior is discussed for ideal devices, as well as changes in filtering behavior due to defects. Theory and design of dielectric Bragg reflectors is presented.

### 2.2 Short review of Fabry-Perot interferometer principles

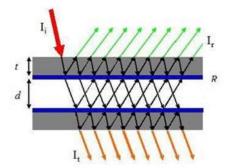

A typical Fabry-Perot device, consisting of two partially transmitting and partially reflecting parallel mirrors separated by an air gap, is illustrated in Fig. 2.1 [24-26]. Light with intensity  $I_i$  is incident on a thin film of thickness t, with angle of incidence  $\theta$ . Some of the light is reflected,  $I_r$ , and some of the light is transmitted,  $I_t$ . The two mirrors have reflectivity R, and are separated by an air gap of distance d. Constructive and destructive interference of light as it passes through multiple interfaces and is refracted within each layer produces a filtering effect, allowing light of wavelength md/2 (m is an integer) to pass through, while reflecting all other wavelengths.

Figure 2.1: Illustration of a Fabry-Perot interferometer

The principle of this device is the change in phase of the incoming beam based on the transmission and reflection from each surface. In the same medium, upon reflection from a boundary, parallel lines have phase difference of  $\delta$ , given by

$$\delta = \frac{2\pi}{\lambda} 2nd \cos\theta \tag{2.1}$$

Where n is the refractive index of the medium and  $\lambda$  is the wavelength of the light. Multiple reflections produce beams that interfere constructively, if they are in phase, or destructively, if they are out of phase.

In order to achieve the maximum constructive interference, the following condition has to be satisfied, where m and n are integers:

$$nd \cos\theta = \frac{m\lambda}{2} \tag{2.2}$$

If the medium of cavity is air, and the incident angle is zero, this condition is met when the wavelength is equal to m multiples of 2d.

Summing up the intensities of all the reflected and transmitted beams yields the intensity of the transmitted light,  $I_t$ , as follows:

$$I_T = \frac{T^2}{(1-R)^2} \times \frac{1}{1 + \left[\frac{4R}{(1-R)^2}\right] \sin^2\frac{1}{2}\delta}$$

(2.3)

Where R is the reflectivity of the mirrors in Fig. 2.1, T is the transmissivity of the mirrors, and  $\delta$  is defined in Eq. 2.1. The main figure of merit of a Fabry-Perot interferometer is reflective finesse,  $N_R$ , given by

$$N_R = \frac{\pi\sqrt{R}}{1-R} \tag{2.4}$$

The bandwidth, or full width at half maximum (FWHM), of the Fabry-Perot interferometer is

$$FWHM = \frac{\lambda_c}{mN_R}$$

(2.5)

where  $\lambda_c$  is the central wavelength of interest. For the majority of applications, it is of particular interest to decrease the bandwidth, as this would allow for higher spectral resolution, and for that one needs to increase the finesse.

### 2.3 Defects in Fabry-Perot Interferometers

Compared to the ideal FPI, with perfectly parallel, infinite plates with zero roughness, fabricated interferometers have several common defects that make their behavior deviate from theory.

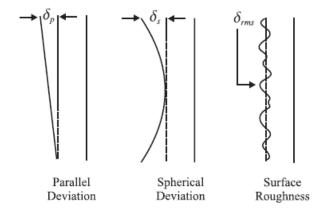

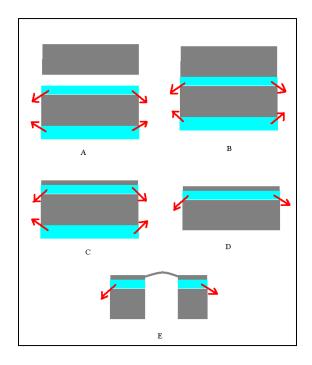

Hernandez [24] in his fundamental book introduced analysis of these defects and their treatment, and others [27-31] have simplified this treatment for use by engineers developing and characterizing the devices. In this treatment, one of the plates is assumed to be perfect, and all the defects are transferred to the second plate. Three types of defects are shown in Figure 2.2.

Figure 2.2: Defects in FPIs. Adapted from Atherton [28]

The parallel deviation results from non-parallelism due to difference in plate separation, the spherical deviation results from bowing of the plate, and the surface roughness deviation results from a non-ideal surface.

The treatment of both parallel and spherical deviations can be understood by first breaking up the non-ideal surface into infinitesimal areal elements of width  $d_x$  and  $d_y$ .

Each of these elements can then be considered to be perfectly parallel to the opposite perfect surface, creating a separate Fabry-Perot interferometer, with its own gap  $d_{\rm g}$ . Bandwidth of each of these elements is calculated and then summed up.

The method for calculating the effects of defects for non-ideal devices is to use contributions to modify the finesse of the ideal device  $(F_R)$ , which is dependent only on the reflectivity of the surfaces for the ideal case, by introducing the term defect finesse,

$$\frac{1}{F_E^2} = \frac{1}{F_R^2} + \frac{1}{F_D^2} \tag{2.6}$$

where  $F_E$  is the effective finesse of the imperfect device. The defect finesse term is composed of three terms associated with each type of defect,

$$\frac{1}{F_D^2} = \frac{1}{F_P^2} + \frac{1}{F_S^2} + \frac{1}{F_{rms}^2} \tag{2.7}$$

Each term is defined as

$$F_p = \frac{\lambda}{3^2 l_2 \delta_p} \tag{2.8}$$

$$F_{\mathcal{S}} = \frac{\lambda}{2 \, \delta_{\mathcal{S}}} \tag{2.9}$$

$$F_{rms} = \frac{\lambda}{4.7 \ \delta_{rms}} \tag{2.10}$$

As can be seen from the equations 2.6 and 2.7, just as in the case of resistors in parallel the smallest resistor dominates, the smallest finesse term dominates the effective finesse of the device. In order to predict the filtering behavior of non-ideal

devices, the effective finesse is substituted for reflective finesse in equation 2.5 to produce

$$FWHM = \frac{\lambda(1 - R_E)}{n \pi \sqrt{R_E}} = \frac{\lambda}{n F_E}$$

(2.11)

Therefore, in design and fabrication of Fabry-Perot interferometers, it is necessary to increase the effective finesse by increasing the reflectivity of the plates and reducing the defects. This would produce the smallest bandpass filtering necessary for accurate detection of absorption peaks and emissions.

Unlike other types of optical filters, the Fabry-Perot interferometer can be designed not to be polarization dependent. As described in the literature [32], the polarization dependence of FPI depends on the incidence angle. If the device and the whole system is designed to have normal incidence on the reflective surface of the interferometer, then the filter is completely polarization independent. This feature is extremely useful when using the non-polarized emission from thermal sources such as black bodies for spectroscopy.

### 2.4 Bragg Reflectors

Reflectors usable in the MWIR have to be composed of dielectric Bragg reflectors, which consist of pairs of alternating materials with high and low index of refraction, thickness of each layer equal to a quarter of central wavelength [33].

The basic principle of the Bragg reflectors is the same as the Fabry-Perot interferometer, the destructive and constructive interference of beams within each

stack based on the change of phase with each boundary [34]. Traditional dielectric Bragg reflectors are designed so that the thickness of each layer is equal to multiples of the quarter wavelength of the central wavelength of interest [35].

The reflectivity, R, of such a stack is given by Eq. 2.12 [35],

$$\mathbf{R} = \left[ \frac{\mathbf{n_0}(\mathbf{n_2})^{2N} - \mathbf{n_s}(\mathbf{n_1})^{2N}}{\mathbf{n_0}(\mathbf{n_2})^{2N} + \mathbf{n_s}(\mathbf{n_1})^{2N}} \right]^2$$

(2.12)

where  $n_0$  is the index of refraction of the incident media,  $n_1$  and  $n_2$  are indices of refraction of the two materials that make up the stack, and  $n_s$  is the index of refraction of the substrate. The reflectivity is increased with a higher number (N) of high-low refraction pairs and an increase in the difference in the index of refraction of the two materials.

As was stated in the previous section, the optical filter part would have to consist of a tunable Fabry-Perot interferometer. Such a device includes two mirrors separated by distance  $d_{cav}$ , and primarily wavelengths of  $\lambda = 2*d_{cav}$  are transmitted.

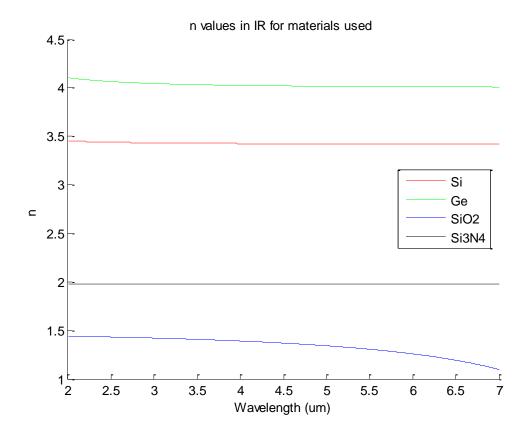

To make the fabrication of the devices less complex, standard MEMS materials (silicon, silicon dioxide, silicon nitride) as well as germanium have to be used. Refractive indices of these materials in MWIR range, 2-7  $\mu$ m, are shown in the Figure 2.3 below:

Figure 2.3: Indices of refraction of common materials

For the Fabry-Perot interferometer to have the best characteristics (such as selectivity, width of operational range, and maximum transmittance at the desired wavelength) it is best to have the reflectivity of mirrors shown in Figure 2.1 as high as possible. Although some groups have tried to use thin metal coatings for the mirrors of a Fabry-Perot Interferometer (FPI), they have found that performance is greatly non-linear and absorption is quite high [36]. For the materials above, index of refraction does not change that greatly in the wavelength region of interest, and absorption for all materials (with exception of Ge) is quite negligible.

So, if metal coatings are not to be used as reflective surfaces, then Bragg stacks have to be used. Bragg stacks are stacks of alternating high and low index materials. For the highest reflectivity, several conditions have to be met. One is that difference in index between successive layers is as high as possible. Second, layers have to be of quarter-wavelength thick – this means  $d=\lambda/(4*n)$  (here, one has to take index of refraction into account – geometric thickness of  $\lambda/4$  is different from optical thickness  $\lambda/(4*n)$ ).

Utilizing the requirements above, Bragg stack has to be made with layers of lowest n material – in this range, silicon dioxide – and highest n material, germanium. Thicknesses used for trial design around 4  $\mu$ m wavelength are  $d_{SiO2}$ =0.720  $\mu$ m and  $d_{Ge}$ =0.248  $\mu$ m, thicknesses that are easy to deposit using standard IC processing

equipment.

Insertion losses can be quite high for Bragg stacks, mainly due to reflectance resulting from difference in n of incident medium (air) and first layer of Bragg stack. To counteract this effect, an anti-reflection coating (ARC) is utilized. Such coatings should have n of geometric mean of two indices, and be of  $\lambda/2$  thickness. For the Bragg stack in our design, insertion from air (n=1) into Ge (n=4.0249 @  $\lambda$ =4 µm) would require ARC with n=2 @  $\lambda$ =4 µm, and this is almost precisely the index of refraction of silicon nitride (n=1.974 @ $\lambda$ =4 µm).

# **Chapter 3: Device Design**

#### 3.1 Introduction

This chapter will transition from general overview of optical filters, and particularly filters for the use in the mid-wave infrared region, 3-5 µm, to the considerations of the particular device that was developed. It will describe the choice of components and overall design of the device, especially integration of optical and mechanical requirements. Optical simulations are presented, as well as fabrication and modeling of the first prototype using commercial foundry.

## 3.2 Requirements

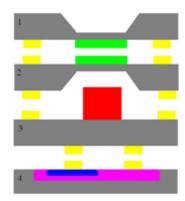

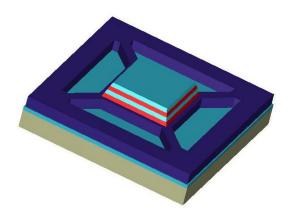

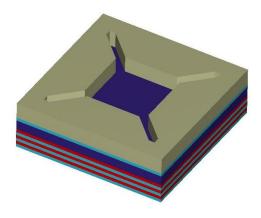

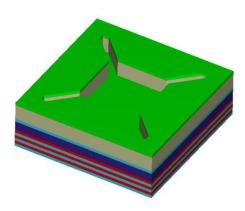

The overall goal of this project is the fabrication of the Fabry-Perot filter integrated with HgCdTe detector and CMOS circuitry, as shown in the Fig.3.1. The device that was fabricated as filter is a MEMS interferometer based on mechanical parts consisting of one movable membrane, supported by springs at the corners (X-beam) and one stationary membrane [37].

Figure 3.1: Proposed integration mechanism to create a complete device out of filter layers (1 and 2), HgCdTe detector layer (3) and CMOS control and logic layer (4).

The cavity length is changed by electrostatically moving the suspended membrane with respect to the stationary one. In electrostatic actuation, the maximum usable voltage of actuation, pull-in voltage, is defined in Eq. 3.1 [38, 39], where t is the thickness of the membrane and springs.

$$V_{pI} = \sqrt{\frac{4 x_o^2 Ewt^3}{9 C l^3}} \propto t^{\frac{3}{2}}$$

The actuation voltage increases with increased thickness of the springs. It is the goal of this project to create devices that can be actuated with the lowest possible voltages, preferably under the range of CMOS circuitry. Therefore, the thickness of the springs has to be minimal.

The absorption losses in the FPI devices depend on the absorption coefficients of materials used and the thickness of layers. The optical design dictates that the

thickness of the silicon layer, which serves only as a mechanical and stress-absorption layer, should be kept to a minimum.

# 3.3 Optical Design

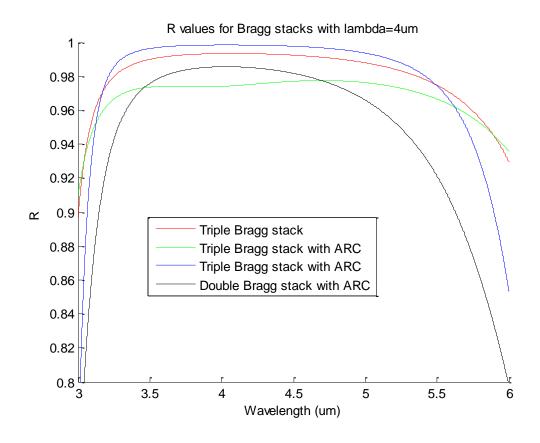

Following the design steps described above, reflectivities of several configurations have been calculated using  $\lambda$ =4  $\mu$ m as a design parameter. These spectra are presented in the figure 3.2 below. The spectra were computed using a matrix method for dielectric Bragg reflectors [40], and the MATLAB code is presented in Appendix A.

Figure 3.2: Simulations of Bragg reflectors

The first curve (red) is triple stack of Ge-SiO<sub>2</sub> quarter-wave layers, with germanium thickness of 250 nm and silicon oxide thickness of 720 nm. Second curve (green) shows effect of adding ARC next to Ge layer—the curve is slightly widened. Third curve, blue, represents effect of adding ARC next to SiO<sub>2</sub> layer—the curve is significantly widened and is more uniform in the range. If it is impossible to utilize triple stack (fabrication constraints), double stack was modeled as the final curve, black.

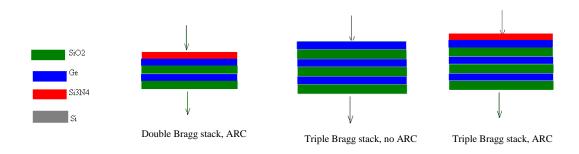

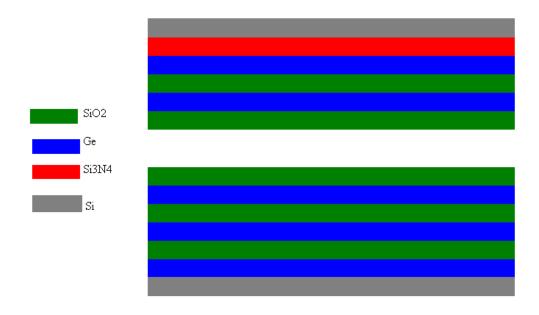

Figure 3.3 below provides cross-sections of these stacks:

Figure 3.3: Bragg reflectors

Using this data and Bragg stacks designed around  $\lambda$ =4  $\mu$ m, the entire Fabry-Perot device was modeled.

## 3.4 Optical Simulations

The perfect Fabry-Perot interferometer can be approximated as a dielectric Bragg reflector, with one of the layers (the gap) being air. Therefore, to study the optical behavior of Fabry-Perot interferometers, the code used to compute reflectivities of the Bragg stacks was modified. While modeling the Airy function as a separate program with input of calculated reflectivities based on Bragg stack simulations is possible, the best effect is achieved by putting all the system in a single simulation. This requires addition of the silicon layers to the Bragg stack calculations, and treating the air gap as just another layer with index of refraction of air. The code is included in Appendix A.

From the reflectivity data obtained in the simulations, R=98% over 3-5  $\mu$ m region, the finesse is calculated to be 155, with the FWHM at  $\lambda$ =4  $\mu$ m, calculated using Eq. 2.11 to be 27 nm.

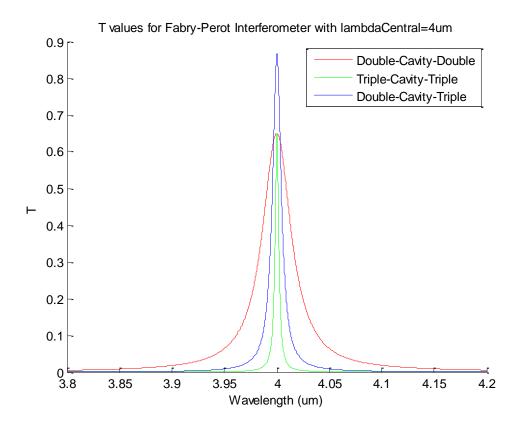

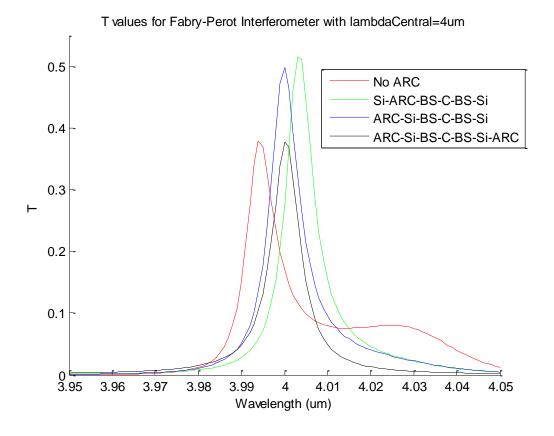

If the device consists of nothing more than two Bragg stacks (with appropriate ARCs) and a mechanically tuned cavity, performance is quite good, as expected from literature [24]. Simulations of this device with cavity length  $d_{Cav}$ =2  $\mu$ m is in the figure 3.4 below:

Figure 3.4: FPI simulations

The red line represents FPI using double Bragg stacks as reflectors. Green line represents same device, but Bragg stacks are triple. Blue line represents FPI using asymmetrical, double-triple Bragg stacks. As can be seen from these curves, selectivity improves greatly when using triple stacks over double stacks. The most interesting figure is asymmetrical FPI, as literature states that best transmissions are achievable when mirrors are perfectly equal. In this case, transmission and selectivity were improved by using an asymmetrical stack.

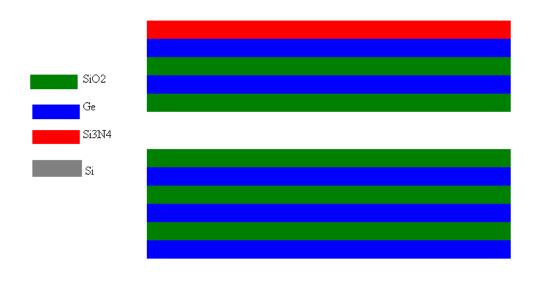

Cross-section of Double-Cavity-Triple FPI used to generate blue line of the Figure 3.4 is below in figure 3.5.

Double-Cavity-Triple FBI

Figure 3.5: Layers in Double-Triple cavity FPI

Utilizing design inputs described below, in the mechanical section, it was determined that silicon is to be utilized as the structural material. Addition of this layer might degrade performance of the FPI. As described below, SOI wafers with structural layer thickness of  $d_{struct}$ =10  $\mu$ m are to be used (at this stage of design). From initial analysis, introduction of this element might be tolerable, as this thickness is a multiple of half design wavelength,  $\lambda$ =4  $\mu$ m: d=(4/(2n))\*m=(4/(2\*3.425))\*17. Curves below are simulation of device performance, with cavity width = 2  $\mu$ m:

Figure 3.6: FPI simulations with addition of silicon layer

The red curve is 2-3 stack without  $Si_3N_4$  ARC added between diaphragm and Bragg stack; green curve is 2-3 stack with ARC added after the diaphragm; blue curve is 2-3 stack with ARC added before the diaphragm; black curve shows addition of ARC to the back side of the FPI.

Analysis of the simulations above demonstrates that although silicon structural layers do degrade peak transmittance of FPI (FWHM of  $0.5\mu m$  vs  $0.89\mu m$  without silicon), ARC coating prevents further degradation.

Cross-section of Si-ARC-BS-C-BS-Si is below in Fig. 3.7:

Si-ARC-BS-C-BS-Si FPI

Figure 3.7: Layers for FPI device

The results from the optical simulations above that include the effect of the silicon layer don't correspond to the finesse-based calculations of FWHM because the finesse based calculation does not include the filtering effect provided by the silicon layer. The silicon layer acts as its own Fabry-Perot etalon, and its effect can be seen only by the comprehensive optical simulation developed here.

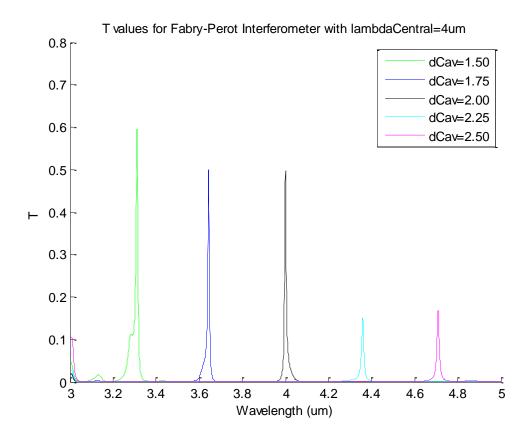

The final simulation run for this design is the simulation of changing cavity length (done mechanically) for the FPI designed with central wavelength of  $\lambda$ =4  $\mu$ m. Results are presented in Fig. 3.8:

Figure 3.8: Transmission simulations for FPI device

These curves represent changing the cavity width from 1.50  $\mu$ m (green) to 2.5  $\mu$ m (magenta) in steps of 0.25  $\mu$ m. This would effectively cover the range from 3  $\mu$ m to 5  $\mu$ m. As expected, wavelength selectivity is demonstrated in transmission. For this design, at d=2  $\mu$ m, FWHM is 0.007  $\mu$ m, comparable to 0.1  $\mu$ m claimed by InfraTec [23].

## 3.5 Conclusion

In conclusion, software has been written that allows simulation of FPI and Bragg stacks, separately and then as an integrated device. This allows fast design checks and optimization of the optical part of the device. This project design of a FPI with central wavelength of 4  $\mu$ m, and performance of this device has been shown to be acceptable as a narrow-band tunable filter for the MWIR, to be utilized as a chemical sensor or thermal imaging.

# **Chapter 4 Mechanical Design**

#### 4.1 Introduction

While there are multiple ways of supporting a membrane by springs, traditionally in MEMS, cantilever beams are used [38]. The deformation of these beams is widely studied [39], and allows useful design, given mechanical constants. While folded spring designs would provide a low mechanical constant and therefore low actuation forces, in order to increase defect finesse of the Fabry-Perot interferometer the surfaces have to be kept as parallel as possible [41], which folded spring design fails to do [42]. In previous work in our group [43], it has been determined that the Xbeam arrangement of springs provides the best uniformity of movement, at the expense of high actuation forces. Therefore, for this project, the mechanical design was chosen as a square plate suspended by four cantilever beams at the corners. By varying the length and width of the beams different mechanical stiffness can be achieved, as described in Eq. 4.1. For best optical performance, it is necessary to keep the plate as flat as possible. The plate acts as a spring by itself, and can be deformed upon actuation; therefore it was necessary to find a design that provides for the most mechanical deformation of the springs while keeping the plate sufficiently stiff, balanced with minimizing actuation voltage given by Eq. 3.1.

$$k = \frac{E w t^2}{l^2} \tag{4.1}$$

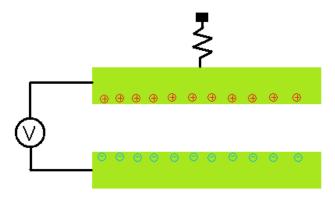

#### 4.2 Electrostatic actuation

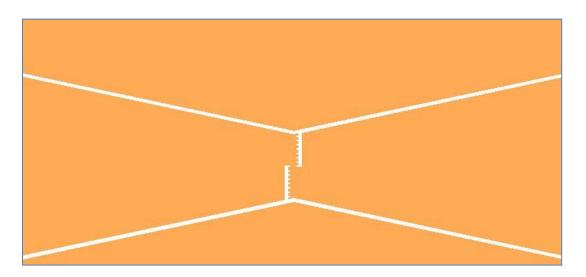

One of the most common means of actuating MEMS devices composed of large parallel plates is the electrostatic actuation [39]. This method is based on charge accumulation on two electrically separated plates that compose a capacitor. When a voltage source is connected to the plates, charges of opposite polarity accumulate on two separated surfaces, as shown in Fig. 4.1.

Figure 4.1 General view of electrostatic actuation

The attraction of opposite charges, described by the Coulomb equation [44], creates mechanical force from electrical input. When one of the plates is fixed, and the other is suspended by linear springs, the electrostatic force creates attractive force that pushes the plates together, while the mechanical force of the springs creates mechanical restoring force that opposes the movement. When the two forces are equal, equilibrium is reached and the system is stable. The mechanical restoring force is based on deformation of the spring and follows linear Hooke's law, while the attractive electrostatic force follows Coulomb's equation. Up until the distance of a third of the gap, in any configuration, the mechanical linear force dominates, and the

movement is linear. Past the distance of a third of the gap electrostatic force dominates over the restoring force, producing effect of "pull-in", or uncontrollable collision of the two plates. Therefore, electrostatic actuation is limited to only one third of the original gap. For the design of FPI device with starting gap of 2.5  $\mu$ m, this translates into controllable movement over 0.833  $\mu$ m, to final gap of 1.67  $\mu$ m.

# 4.3 MUMPS Prototype

#### 4.3.1 MUMPS process

In order to study the mechanical behavior of the proposed device and develop realistic mechanical models, a high-level mechanical prototype is used. Also, the fabrication process used for the prototype would be a good starting point for development of custom fabrication process for complete devices.

The process for the fabrication of the prototype is the commercial MUMPS (Multi-User MEMS Processes) SOI (Silicon-on-Insulator) process, developed by MEMSCAP, that uses silicon-on-insulator wafers as the substrate [45]. The fabrication process was developed to address as many needs of designers as possible by allowing them to change only the geometry of devices, but not the layer thicknesses. The diagram that indicates all the layers of devices produced by this process is shown in Fig. 4.2.

Figure 4.2: MUMPS SOI process [45]

# **4.3.2 Layout**

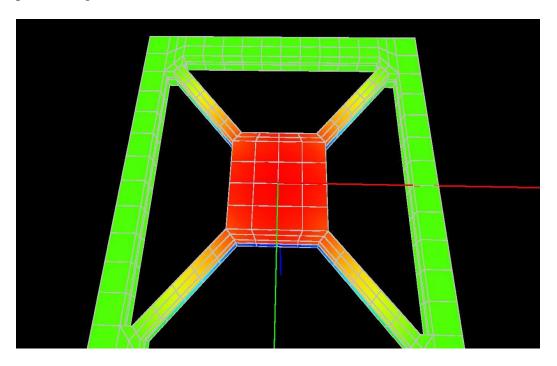

Taking into consideration the requirements of the project and the limitations of the MUMPS process, the initial device was designed to act as a high-level mechanical prototype.

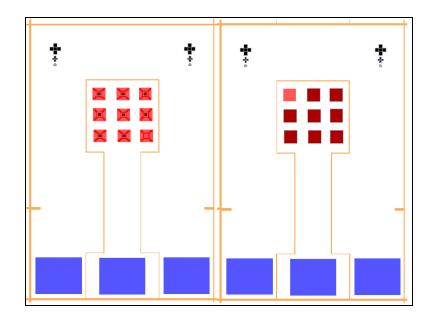

Figure 4.3: Layout for MUMPS device

The method of making these parts into a mechanical prototype of the device involves bonding two identical chips. This is made possible by the metal pads (purple color in the figure above) that are 1.6  $\mu$ m thick. Therefore, if the chips are aligned with each other, the separation between them would be 3.2  $\mu$ m, allowing a test in the MWIR range.

# 4.3.3 Mechanical modeling and testing

Although this prototype would not be a perfect optical filter, it would provide us with information about the realistic deformation of the plate. In our simulations, the best variation that could be achieved was 600 nm from center to edge in the 2 mm square plate. A figure of this simulation is below.

Figure 4.4: FEA model of X-beam

Although the plate curvature does not seem significant, it could introduce unwanted optical effects into the filter. From the curvature of the plates, the reflective finesse is 3.3, the finesse term due to curvature is 0.181, and the effective finesse is 0.18, resulting in FWHM=  $22 \mu m$ .

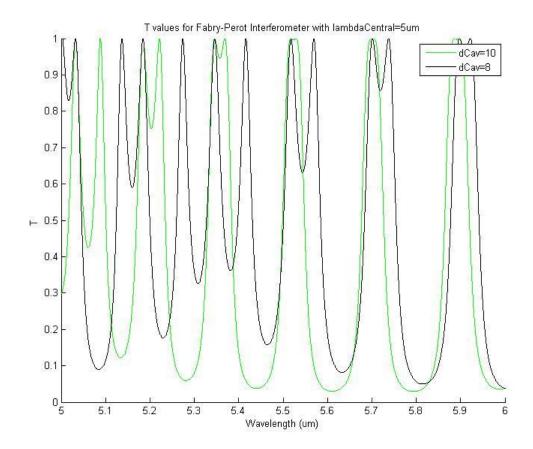

The optical behavior of the prototype has been simulated using Matlab software, and the behavior is shown in the figure below:

Figure 4.5: Simulation of optical behavior of MUMPS X-beam

This figure represents behavior of the filter as the wavelength is scanned from 5  $\mu m$  to 6  $\mu m$ , with the undeformed cavity length being 10  $\mu m$  (green line) and 8  $\mu m$  (black line).

The design, analysis and simulation of the first mechanical prototype has given valuable insight into the mechanical behavior of plates suspended by springs fabricated on SOI wafers. Low reflectivity of silicon surfaces and high curvature of

the membrane makes this an unacceptable optical prototype. To create a device that would have good optical performance, a custom process needs to be developed that addresses these issues, by incorporating highly reflective surfaces and minimizing the curvature of the membrane.

# **Chapter 5: First fabrication run**

#### 5.1 Introduction

In the previous chapters, it was determined that the best materials for the Bragg reflectors are to be germanium and silicon oxide. This chapter will describe how by using several different methods of deposition, it was determined that the lowest stress per dielectric pair is 100 MPa of compressive stress. With a thin supporting membrane, this leads to bowing of the mirrors and decreases resolution of the device. The thickness of the silicon layer has to be thick enough to reduce the stress bowing to a minimum.

The experiments were performed at Stanford Nanofabrication Facility (SNF). The main point of this part of the project was finding the fabrication flow that combines the least expensive methods (i.e. wet etching instead of dry etching) and the substrate thickness that will be just thick enough to reduce the stress bowing, but will not increase significantly the actuation voltages and absorption losses of the device.

## 5.2 Considerations for process development

Although silicon nitride has been used as structural material in UWA group [46-48], other materials have to be used, as silicon nitride has good optical properties, but has too much stress for use as structural layer. Instead of spending time and funds developing low-stress silicon nitride deposition process (UWA), we decided to use a

more well-known and more widely available (equals less expensive) materials, such as silicon layer in SOI wafers. Also, as X-Beams have been finalized as springs for the mechanical design, this requires material that is more inelastically deformable, and silicon is a better candidate.

As was stated in the previous chapter, the optimal Bragg stack would be double-triple Bragg stack with germanium and silicon oxide alternating layers, with silicon membrane and silicon nitride anti-reflective coating.

Research has been conducted into determining what methods of deposition of these materials would be best for optical device.

In general, there are several tools available for deposition of dielectric layers [49]: CVD (chemical vapor deposition), PECVD (plasma-enhanced CVD), epitaxial (slow growth of single-crystal layer), sputtering, and other more exotic methods. Almost all of these methods are available to us through SNF [50].

Although UWA group has deposited all of the layers by PECVD [51], personal experience with PECVD (used extensively in previous project [52]) and literature shows that this method is not acceptable for optical-quality films. PECVD produces thick films in relatively short time, but these films are usually extremely prone to having bubbles and gradients in film quality. Such film would cause scattering and reflections, and introduce unpredictable behavior.

Epitaxial growth produces extremely uniform films, but might introduce large stress into the stack, if subsequent layers are mismatched.

There are two tools that allow deposition of germanium at the SNF. One of them, "tylansige", is a low-pressure chemical vapor deposition (LPCVD) tool that allows deposition of germanium and silicon films [53]).

Another tool that is capable of depositing germanium films is epitaxial tool, "epi" [54]. This tool is an epitaxial chamber.

Apart from the method of deposition, the main difference between these two machines is the temperature range of the processes. LPCVD tool deposits in the range of 400-650C, while epi tool uses 600-1200C range. While epitaxial tool might give superior quality film, it might not be usable for our process. High temperatures are not significant if only one film is grown, and even then substrate and deposited film have to be very carefully thermally matched. In case of our process, we are depositing consequent layers of several materials, and coefficients of thermal expansion of these films are sufficiently different as to almost guarantee problems at high temperatures (such as lamination, cracking, etc.)

After some consideration, it has been determined that the optimal deposition method is LPCVD, which is a standard IC fabrication method and therefore would have more standard recipes.

Silicon oxide could be deposited on several tools, but considerations of contamination between machines, as established by SNF guidelines, guide towards use of the "teos" tool [55]. This is a standard tool, and used a low-temperature recipe.

Silicon nitride can be deposited on "tylannitride" [56]. This is a standard tool, and numerous recipes have been developed by SNF staff, including low-stress nitride film.

Patterning of various films used in the process can be done in one tool, "p5000etch" [57], which is a versatile tool used for deep reactive ion etching of various materials. Photolithography was done on the standard track at SNF, utilizing the KarlSuss aligner for exposure (resolution and alignment precision down to 0.5 microns). Contamination rules at SNF are as follows [58]: all tools are split into three groups, "clean", "semiclean" and "contaminated". Wafers usually start off as "clean", and move down the rating depending on the processing. Once a wafer is processed on "semiclean" tool, it cannot be processed on "clean", and so on. The process flow that has been designed follows these contamination rules.

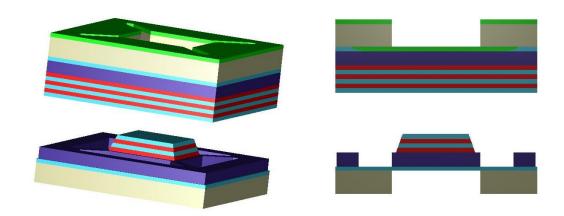

#### **5.3 Initial process**

Process flow has been designed that would allow one to fabricate a Fabry-Perot interferometer that would replicate the device designed previously. In the process of design, several things were taken into effect: capability of tools at SNF, quality of films produced, and simplicity of the process. The simpler the process, the more robust it is. The more standard processes are used, that much easier to transfer fabrication from research facility to commercial fab, and therefore lower costs. As many common steps as possible have been used, and number of masks has been minimized.

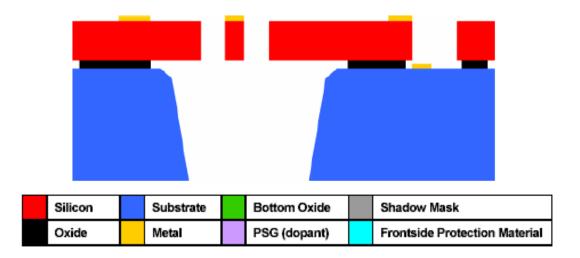

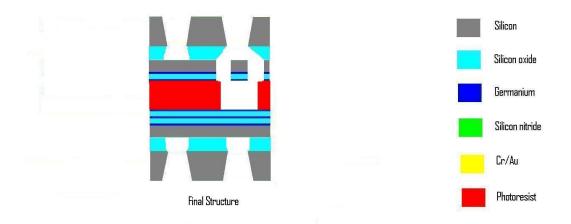

Figures 4.1-4.8 below have been generated using SoftMems, commercial add-on to LEdit.

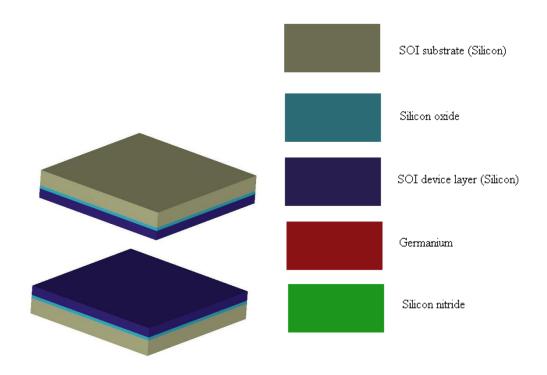

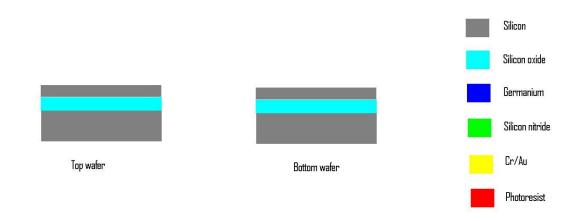

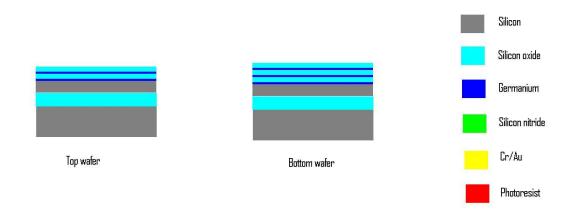

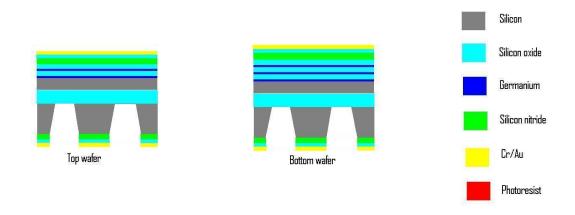

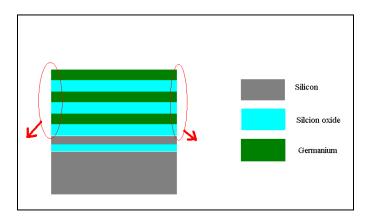

**Step 1:** we are starting off with two SOI wafers, with substrate thickness of 400 microns, 1 micron of silicon oxide as the isolation layer, and 25 microns of "device" layer. (Layer thicknesses are intentionally not to scale, as 400 microns of substrate layer would make 0.4 microns of germanium invisible). Legend for material colors is included.

Figure 5.1: Starting SOI substrate

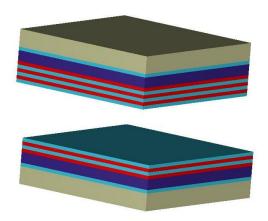

**Step 2:** (Next series of steps are combined into Step 2) deposits consequent germanium and silicon oxide layers on appropriate sides of the wafers:

Figure 5.2: SOI with Bragg stacks

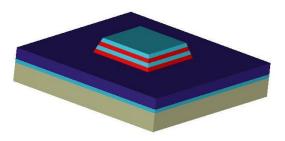

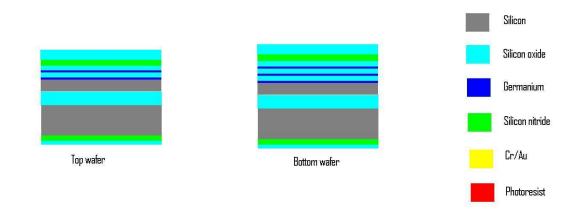

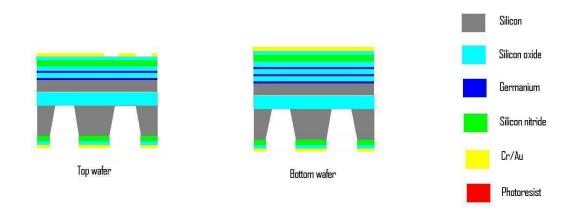

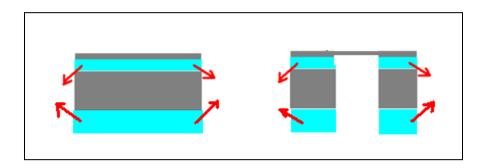

**Step 3:** uses Mask1 to etch the Bragg stack on lower wafer, leaving the layers only in the area of the active device:

Figure 5.3: Substrate with etched Bragg stack

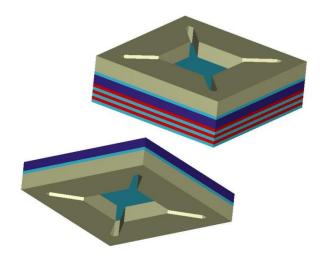

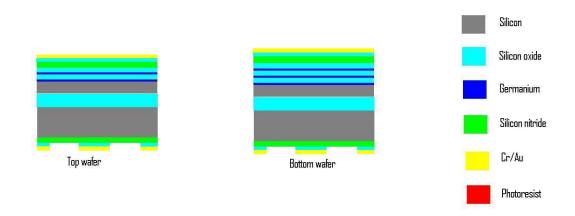

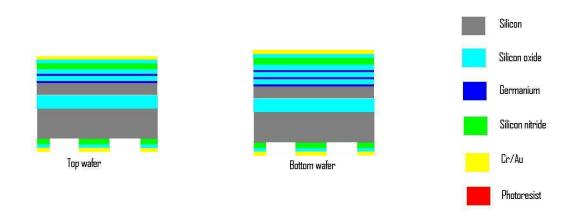

**Step 4:** uses Mask2 to etch the backsides of both wafers. Here, same mask and same etching process are utilized.

Figure 5.4: Backside etching

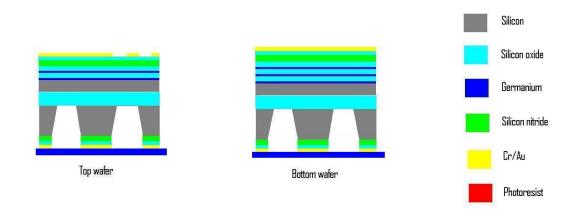

**Step 5:** uses Mask3 to etch the top of lower wafer to produce the device:

Figure 5.5: Unreleased X-beam

**Step 6:** uses wet etch on top wafer to etch away the exposed silicon oxide:

Figure 5.6: Released X-beam

**Step 7:** deposits silicon nitride on top wafer, creating anti-reflective coating:

Figure 5.7: Addition of silicon nitride layer

## **Step 8:** bonding of the wafers:

Figure 5.8: Two parts of the Fabry-Perot interferometer

**Step 9:** following dicing of the wafer, the membrane is released using HF bath.

In Step 8, the method of bonding was omitted. It was our plan to use simple dryresist bonding for the first batch of devices, and move on to metal-to-metal or anodic bonding in the final fabrication process, requiring one additional mask. Also, for bonding to detector, additional metal layers would have to be deposited and patterned on the back side of the wafer.

Although this process sounds simplistic, it would require a series of short-loop tests that verify correctness and compatibility of each step. It has been my experience in the past that even such simple process as deposition of a layer might go wrong, and serious verification is needed.

#### These short-loop tests are:

- Layer deposition stress in the deposited layers, adhesion, quality

- Layer compatibility deposition of the entire Bragg stack and verification that no peeling, cracking or other defects are present

- Proper process for back-side etching that would not damage deposited Bragg stack

- Process for membrane etching that would not damage any other layers

- Bonding

- Membrane release usually the hardest part of any MEMS process

This process has been submitted to SNF staff and determined to be realistic and to follow SNF guidelines.

## **5.4 SNF Process development**

After consultation with several employees at SNF, it was determined that the proposed process does not violate their procedures and use of equipment. There have been several changes, as some of the steps had to be done on other tools than originally projected. The germanium layer, as part of the Bragg stack, would not be mono-crystalline, it would be poly-crystalline or amorphous, due to its deposition on top of mis-matched silicon oxide layer. This might introduce some slight changes to the optical response of the filter.

The goals for the initial round of fabrication were primarily fabrication of Bragg stacks of single, double and triple thickness for optical testing, development of key

processes for the fabrication, and testing of commercially available SOI wafers. For the region of MWIR, the original design was centered around wavelength of 4 microns. This required germanium layers to be 250 nm thick, and silicon oxide layers to be 720 nm thick.

The final device would have this configuration:

Figure 5.9: Diagram of two bonded parts with electrical connections

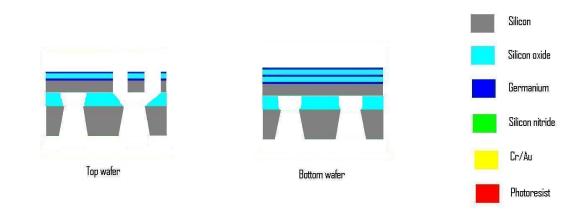

## 5.5 Mask design and layout

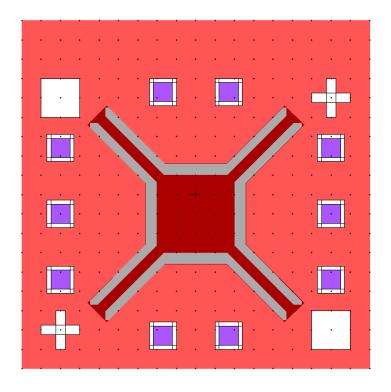

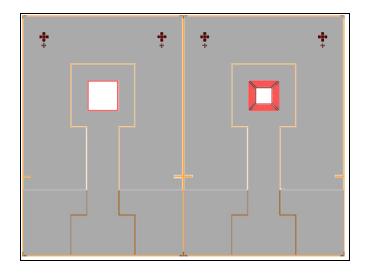

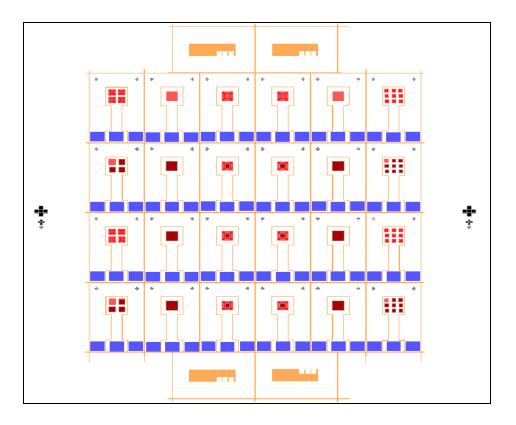

For the start of this process, two major masks are needed: one mask for the etching of optical windows into the backside of the wafers, and second mask for the definition of X-beam to be released.

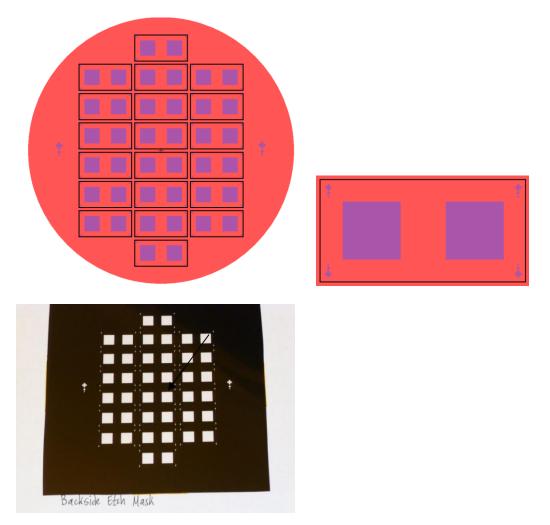

The first mask, "Backside etch" (Fig. 5.10), consists of 20 chips, each 2 cm by 1 cm, with the following pattern: two squares, each 5.6 mm on the side. The reason for this

size is that when through-wafer etching is done on the backside, the entire device area should be open. Also, this mask could be re-used for defining thick resist used for bonding. This mask defines openings in the backside of the wafer and is used for through-wafer etching to the device layer. One of the openings is used for optical testing, and another to provide electrical contact to the device layer, as shown in the picture above. Global alignment marks are on the edges of the wafer, and each chip has four sets of local alignment marks.

Figure 5.10: First mask layout with chip detail and actual mask

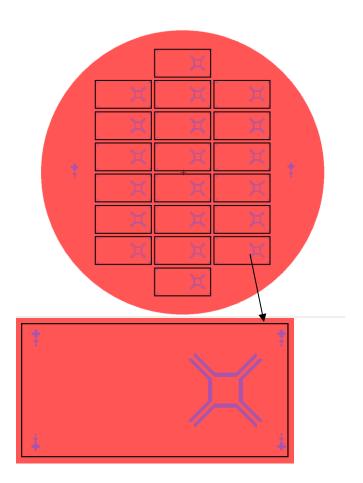

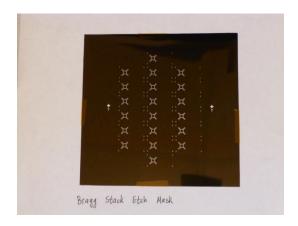

Second mask, "X-beam etch" (Fig. 5.11), follows the layout of the backside mask, and defines X-beam mechanical element to be etched through Bragg stack and device layer.

Figure 5.11: Second mask layout with chip detail

Figure 5.12: Actual mask

These two masks have been laid out using L-Edit software, and fabricated on Mylar transparent film. This provides for a quick and inexpensive trial for masks.

## **5.6 Fabrication requirements**

The main goal was to start process development and verify separate steps, which will be used to fabricate the final device. Although at this point the focus is on obtaining samples to verify optical and mechanical designs, the eventual goal of developing a technology that can be used for multiple applications at a commercial foundry should be kept in mind. Therefore, process should be robust, wafer-scale, and able to transfer from current scale of devices (somewhat large, detector side being 2 mm square) to much smaller scale, with scale reduction by at least a factor of ten. Standard IC and MEMS fabrication steps should be used throughout, with keeping special processes to a minimum. Robustness means allowing for slight variations in

wafer thickness and uniformity, as well as chemical concentrations and etch rates. Photolithography, layer depositions, and etching should be consistent from wafer to wafer and across each wafer. Such process should be transferable to a commercial large-scale foundry for future production, so all the steps would become a standard process.

The work has two main approaches, the optical design part and the mechanical design part. The optical design involves deposition of optical component, the Bragg stack. The mechanical part is the fabrication of the carrier, the X-Beam parallel plate actuator.

#### 5.7 Layer deposition

The Bragg stack requires alternating layers of germanium and silicon oxide. For the design of filter in MWIR (3-5  $\mu$ m), the filter was designed with center wavelength of 4  $\mu$ m, and that required the following layer thicknesses: germanium 250 nm, silicon oxide 720 nm, silicon nitride 500 nm. For optical purposes, such films should be as uniform and defect-free as possible. All optical design was done for monocryistalline germanium.

There are several methods for depositions of these materials, as was described above. From my previous project, the CNF-based NEMS switch, I was already trained on the metal evaporator, that allowed deposition of germanium, and the PECVD system that allowed depositions of silicon oxide and silicon nitride. Although the UWA group deposited all their dielectric layers by PECVD [51], films produced by this method have high defect density (pinholes, globules, cavities) and CVD furnaces produce

higher quality films. Advantages of PECVD systems is that they are quick (single deposition lasts 30 min to 90 min) and allow quick changing of parameters. CVD furnace systems deposit films on both sides, requiring extra steps of etching undesired films.

At SNF, there are several furnace systems for deposition of high-quality dielectric systems and epitaxial germanium films with controllable doping. Another benefit of using a CVD furnace to deposit germanium was its ability to deposit single-crystalline layers on substrates with appropriate lattice size, resulting in high-quality film. After consultation, it was determined that germanium deposited over silicon oxide would never be monocrystalline after the first layer, therefore introducing variations into the optical performance.

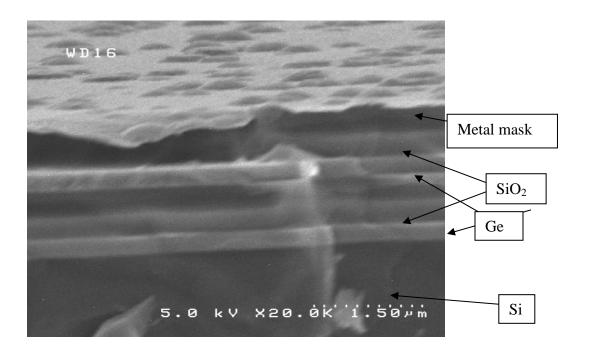

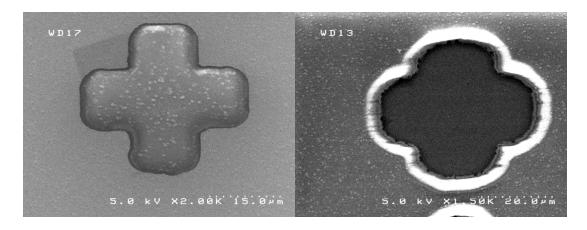

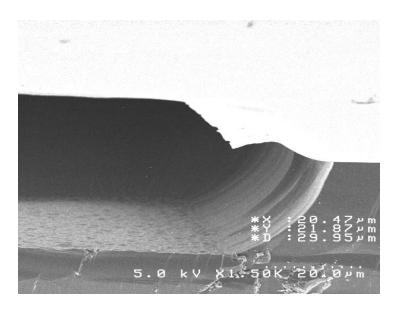

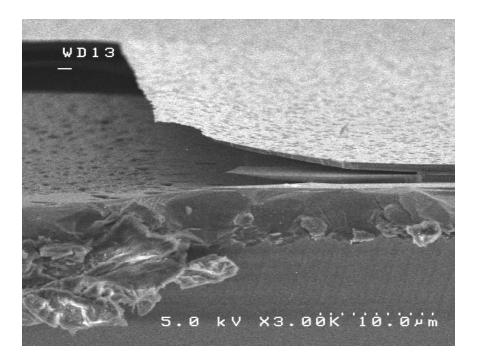

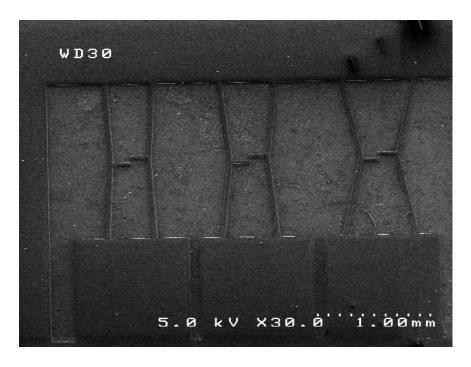

Figure 5.13 is the SEM image of a double Bragg stack with gold-chromium mask on top (this sample was used for etch tests).

Figure 5.13: SEM image of the deposited Bragg stack