# **UC San Diego**

# **UC San Diego Electronic Theses and Dissertations**

#### **Title**

Dynamic workload characterization for energy efficient computing

#### **Permalink**

https://escholarship.org/uc/item/69x5h7ps

#### **Author**

Dhiman, Gaurav

### **Publication Date**

2011

Peer reviewed|Thesis/dissertation

#### UNIVERSITY OF CALIFORNIA, SAN DIEGO

## Dynamic Workload Characterization for Energy Efficient Computing

A dissertation submitted in partial satisfaction of the requirements for the degree

Doctor of Philosophy

in

Computer Science

by

Gaurav Dhiman

#### Committee in charge:

Professor Tajana Rosing, Chair Professor Rajesh Gupta Professor Tara Javidi Professor Dean Tullsen Professor Amin Vahdat

Copyright

Gaurav Dhiman, 2011

All rights reserved.

| The dissertation of Gaurav Dhiman is approved, and it    |

|----------------------------------------------------------|

| is acceptable in quality and form for publication on mi- |

| crofilm and electronically:                              |

|                                                          |

|                                                          |

|                                                          |

|                                                          |

|                                                          |

|                                                          |

|                                                          |

|                                                          |

|                                                          |

|                                                          |

| Chair                                                    |

University of California, San Diego

2011

# DEDICATION

To my parents.

## EPIGRAPH

karmany evadhikaras te

ma phalesu kadachana

ma karma-phala-hetur bhur

ma te sango stv akarmani.

-Lord Krishna

(Bhagavad Gita)

## TABLE OF CONTENTS

| Signature P   | age .            |                                                                                                    |                                                                 |                                            |                                                                        |                                               |                                    |                                 |                         |                        |               |     |                                       |   |    |    |      |      | iii                                                        |

|---------------|------------------|----------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|--------------------------------------------|------------------------------------------------------------------------|-----------------------------------------------|------------------------------------|---------------------------------|-------------------------|------------------------|---------------|-----|---------------------------------------|---|----|----|------|------|------------------------------------------------------------|

| Dedication .  |                  |                                                                                                    |                                                                 |                                            |                                                                        |                                               |                                    |                                 |                         |                        |               |     |                                       |   |    |    |      |      | iv                                                         |

| Epigraph .    |                  |                                                                                                    |                                                                 |                                            |                                                                        |                                               |                                    |                                 |                         |                        |               |     |                                       |   |    |    |      |      | V                                                          |

| Table of Co   | ntents           |                                                                                                    |                                                                 |                                            |                                                                        |                                               |                                    |                                 |                         |                        |               |     |                                       |   |    |    |      |      | vi                                                         |

| List of Figur | res .            |                                                                                                    |                                                                 |                                            |                                                                        |                                               |                                    |                                 |                         |                        |               |     |                                       |   |    |    |      |      | ix                                                         |

| List of Table | es               |                                                                                                    |                                                                 |                                            |                                                                        |                                               |                                    |                                 |                         |                        |               |     |                                       |   |    |    |      |      | xi                                                         |

| Acknowledg    | ement            | s                                                                                                  |                                                                 |                                            |                                                                        |                                               |                                    |                                 |                         |                        |               |     |                                       |   |    |    |      |      | xii                                                        |

| Vita          |                  |                                                                                                    |                                                                 |                                            |                                                                        |                                               |                                    |                                 |                         |                        |               |     |                                       |   |    |    |      |      | XV                                                         |

| Abstract of   | the D            | issertati                                                                                          | on                                                              |                                            |                                                                        |                                               |                                    |                                 |                         |                        |               |     |                                       |   |    |    |      |      | xvi                                                        |

| Chapter 1     | Intr<br>1.1      | 1.1.1<br>1.1.2<br>1.1.3<br>1.1.4                                                                   | n  nic Ene Dynan Dynan Applic Energy Contri                     | rgy 1<br>nic P<br>nic V<br>abili<br>y Effi | Man<br>Powe<br>Volta<br>ty o<br>icien                                  | age<br>r M<br>ge :<br>f A                     | mer<br>Iana<br>Frec<br>ctiv<br>for | nt<br>ager<br>que<br>e F<br>Ser | me<br>ency<br>ow<br>rve | nt<br>7 S<br>er<br>: S | <br>cal<br>Ma | ing | ge<br>s                               | m | en | .t | <br> | <br> | 1<br>2<br>3<br>4<br>6<br>8                                 |

| Chapter 2     | Acti 2.1 2.2 2.3 | Design<br>2.2.1<br>2.2.2<br>2.2.3<br>Impler<br>2.3.1<br>2.3.2<br>Experi<br>2.4.1<br>2.4.2<br>2.4.3 | System Contro Performentation Devices Iments of CPU ( Overhous) | on Modeller mand on Des with and I (DPM)   | odel ce B etail th of th C Resu M) ——————————————————————————————————— | ounder our our our our our our our our our ou |                                    |                                 |                         |                        |               |     | · · · · · · · · · · · · · · · · · · · |   |    |    |      |      | 133<br>155<br>177<br>199<br>200<br>211<br>300<br>377<br>45 |

|               | 2.5              | Conclu                                                                                             | usion .                                                         |                                            |                                                                        |                                               |                                    |                                 |                         |                        |               |     |                                       |   |    |    |      |      | 46                                                         |

| Chapter 3 | Analysis of Energy Efficiency in Server Systems                   |

|-----------|-------------------------------------------------------------------|

|           | 3.1 Introduction                                                  |

|           | 3.2 DVFS for System Level Energy Savings                          |

|           | 3.3 Evaluation Setup and Results                                  |

|           | 3.4 Conclusion                                                    |

| Chapter 4 | Energy Efficient Memory Hierarchy                                 |

|           | 4.1 Introduction                                                  |

|           | 4.2 Design                                                        |

|           | 4.2.1 PRAM/DRAM Background 60                                     |

|           | 4.2.2 Architecture                                                |

|           | 4.2.3 Endurance Analysis                                          |

|           | 4.3 Evaluation                                                    |

|           | 4.3.1 Methodology                                                 |

|           | 4.3.2 Results                                                     |

|           | 4.4 Conclusion                                                    |

| Chapter 5 | Energy Efficiency using Workload Consolidation                    |

| - · · ·   | 5.1 Introduction                                                  |

|           | 5.2 Data Center Workloads                                         |

|           | 5.2.1 Services                                                    |

|           | 5.2.2 Batch                                                       |

|           | 5.2.3 Workload Management                                         |

|           | 5.3 Related Work                                                  |

|           | 5.4 Motivation for Workload Characterization 81                   |

|           | 5.4.1 Performance and Power Profile of VMs 82                     |

|           | 5.5 vGreen Design                                                 |

|           | 5.6 vGreen Implementation                                         |

|           | 5.7 Evaluation Methodology                                        |

|           | 5.8 Results                                                       |

|           | 5.8.1 Heterogeneous Workloads                                     |

|           | 5.8.2 Homogeneous Workloads                                       |

|           | 5.8.3 Different Machine Architecture and Configurations 104       |

|           | 5.8.4 Overhead                                                    |

|           |                                                                   |

|           | 5.9 Conclusion                                                    |

| Chapter 6 | Energy Efficient Consolidation of Batch and Service Workloads 110 |

|           | 6.1 Introduction                                                  |

|           | 6.2 Batch and Service Workload Comparison                         |

|           | 6.2.1 Workload Performance and QoS requirements 112               |

|           | 6.3 Energy Efficiency of Diverse Workloads                        |

|           | 6.3.1 Why consolidate batch and services VMs? 116                 |

|           | 6.3.2 Diverse Workload Challenges                                 |

|              | 6.4 | System Design                                                                                                                | 122 |

|--------------|-----|------------------------------------------------------------------------------------------------------------------------------|-----|

|              |     | 6.4.1 Energy efficiency metric                                                                                               | 122 |

|              |     | 6.4.2 Themis Design                                                                                                          |     |

|              | 6.5 | Evaluation Methodology                                                                                                       |     |

|              | 6.6 | Results                                                                                                                      | 133 |

|              |     | 6.6.1 Controller Adaptability                                                                                                | 137 |

|              | 6.7 | Conclusions                                                                                                                  | 140 |

| Chapter 7    | Con | clusion and Future Work                                                                                                      | 142 |

|              | 7.1 | Thesis Summary                                                                                                               | 143 |

|              |     | 7.1.1 Active Power Management                                                                                                | 143 |

|              |     | 7.1.2 Energy Proportional Design                                                                                             | 144 |

|              |     | 7.1.3 Workload Consolidation                                                                                                 | 144 |

|              | 7.2 | Future Research Directions                                                                                                   | 145 |

|              |     | 7.2.1 I/O Resource Management in Virtualized Envi-                                                                           |     |

|              |     | $ronments \dots \dots$ | 145 |

|              |     | 7.2.2 Energy Proportionality for Storage                                                                                     | 146 |

| Ribliography |     |                                                                                                                              | 147 |

## LIST OF FIGURES

| Figure 1.1:                               | Average CPU utilization, power and energy efficiency of 5000 servers during six-month period                                                                                                                                                       | 8        |

|-------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| Figure 2.1:<br>Figure 2.2:                | Overall System Model                                                                                                                                                                                                                               | 16       |

|                                           | consumption or energy loss                                                                                                                                                                                                                         | 23       |

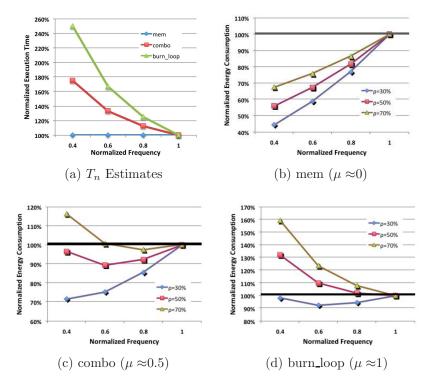

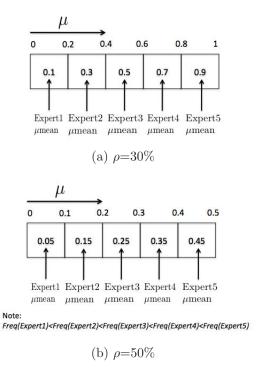

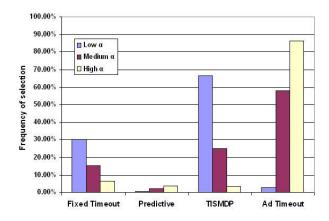

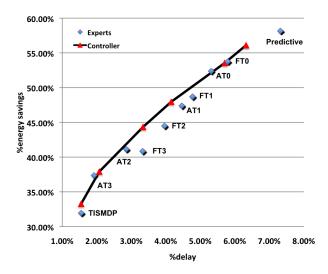

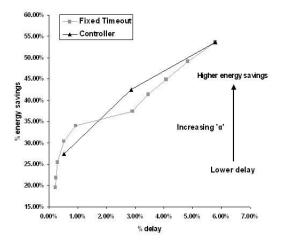

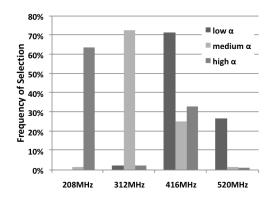

| Figure 2.3:<br>Figure 2.4:<br>Figure 2.5: | Example of $\mu$ -mappers for CPUs with different $\rho$ values Frequency of selection of experts for HP-3 trace Comparison of e/p tradeoff of controller with multiple experts for HP-1 trace. The black line connects the different e/p tradeoff | 29<br>34 |

| Figure 2.6:                               | points of the controller                                                                                                                                                                                                                           | 35       |

| F: 0.7                                    | experts respectively.                                                                                                                                                                                                                              | 36       |

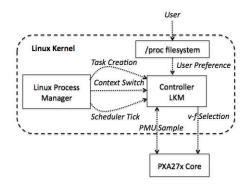

| Figure 2.7:                               | System Level Implementation of Controller for CPU                                                                                                                                                                                                  | 37<br>42 |

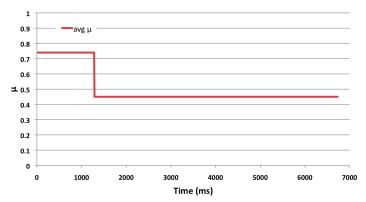

| Figure 2.8: Figure 2.9:                   | Frequency of selection of experts for qsort benchmark Plot of average $\mu$ of qsort benchmark across its execution timeline.                                                                                                                      | 43       |

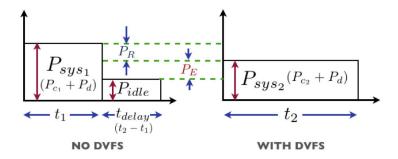

| Figure 3.1:                               | Comparison of Power Consumption and Execution Times of a workload with and without DVFS                                                                                                                                                            | 49       |

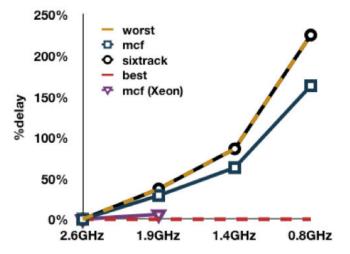

| Figure 3.2:                               | Analysis of Performance Delay (%delay) for <i>mcf</i> and <i>sixtrack</i> workloads at lower frequency settings                                                                                                                                    | 51       |

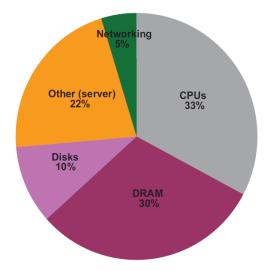

| Figure 3.3:                               | Power Consumption breakdown for a typical modern server [42].                                                                                                                                                                                      | 56       |

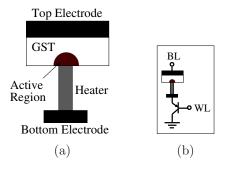

| Figure 4.1:                               | Illustration of PRAM cell (a) and transistor (b)                                                                                                                                                                                                   | 60       |

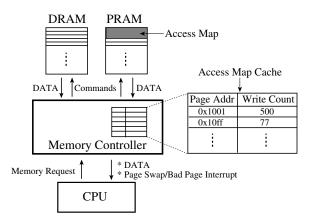

| Figure 4.2:                               | PDRAM Memory Controller                                                                                                                                                                                                                            | 63       |

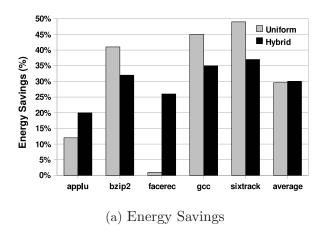

| Figure 4.3:                               | Energy Savings and Performance Overhead Results for Uniform and Hybrid Policies                                                                                                                                                                    | 70       |

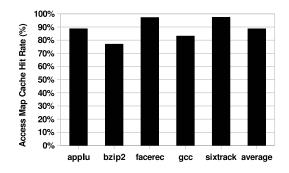

| Figure 4.4:                               | Access Map Cache Hit Rate (%) (the values were similar from both Uniform and Hybrid Policies)                                                                                                                                                      | 72       |

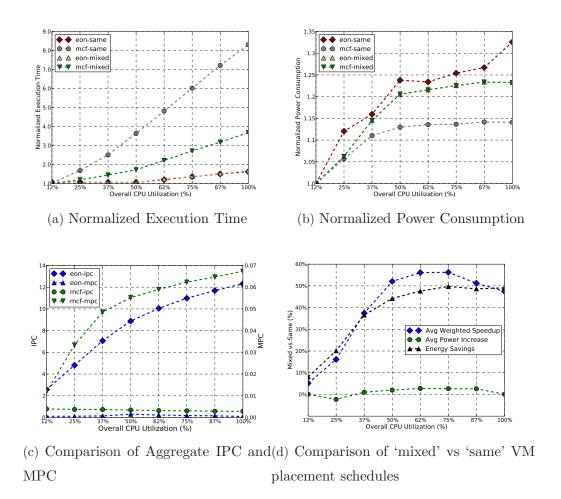

| Figure 5.1:                               | Comparison of various metrics of <i>eon</i> and <i>mcf</i> across 'mixed' and 'same' schedules                                                                                                                                                     | 83       |

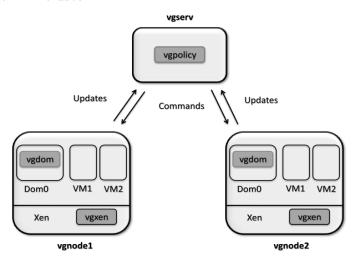

| Figure 5.2:                               | Overall Architecutre of vGreen system                                                                                                                                                                                                              | 87       |

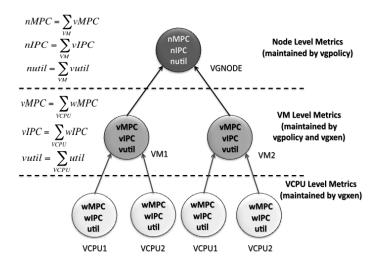

| Figure 5.3:                               | An example of Hierarchical Workload Characterization in vGreen.                                                                                                                                                                                    | 88       |

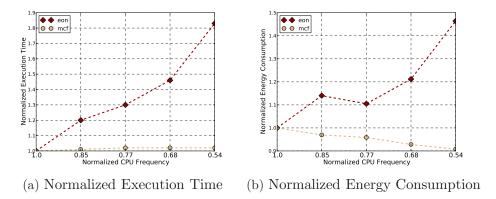

| Figure 5.4:                               | Comparison of execution time and energy consumption of <i>mcf</i>                                                                                                                                                                                  |          |

|                                           | and <i>eon</i> at different frequency levels                                                                                                                                                                                                       | 93       |

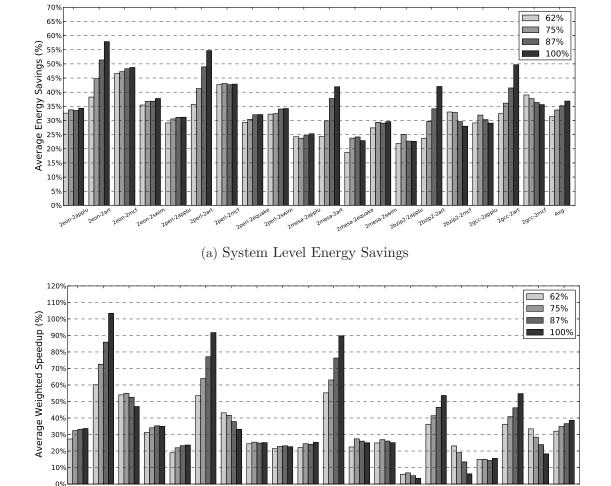

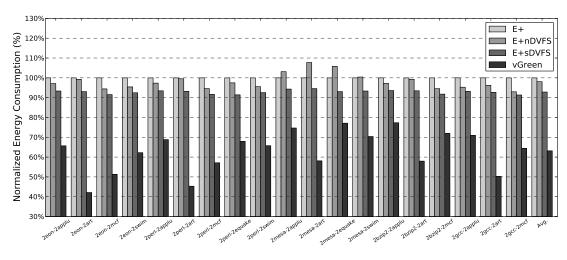

| Figure 5.5               | : Comparison of E+ and vGreen. The results are normalized against E+ system        | 99  |

|--------------------------|------------------------------------------------------------------------------------|-----|

| Figure 5.6               |                                                                                    |     |

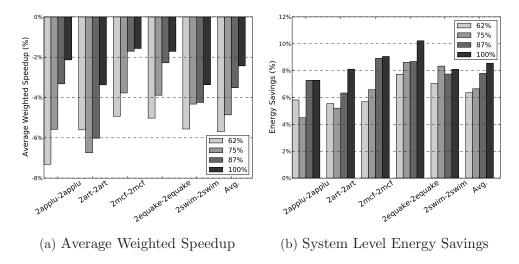

|                          | algorithm                                                                          | 101 |

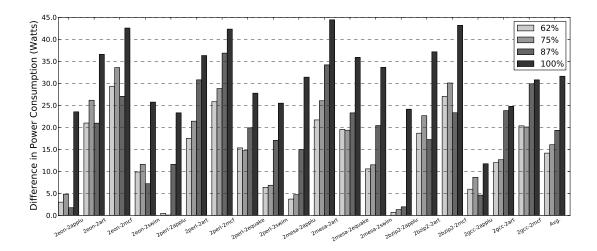

| Figure 5.7               |                                                                                    | 101 |

| 1 100110 011             | results are baselined against the E+ system                                        | 102 |

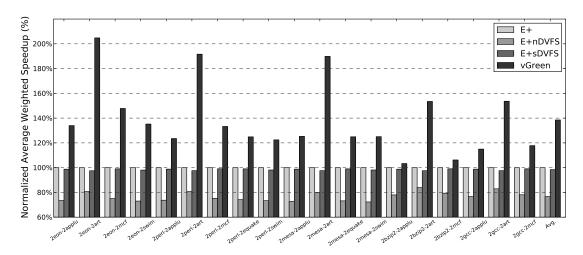

| Figure 5.8               | · · · · · · · · · · · · · · · · · · ·                                              |     |

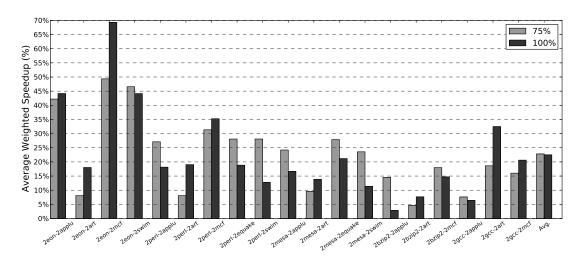

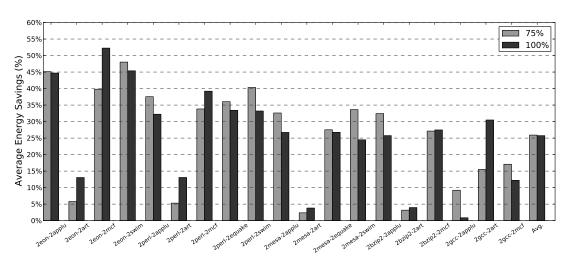

| 0                        | The results are baselined against the E+ system                                    | 104 |

| Figure 5.9               | e v                                                                                |     |

| 0                        | The results are baselined against E+ system                                        | 106 |

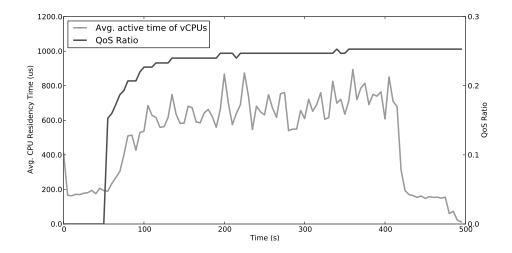

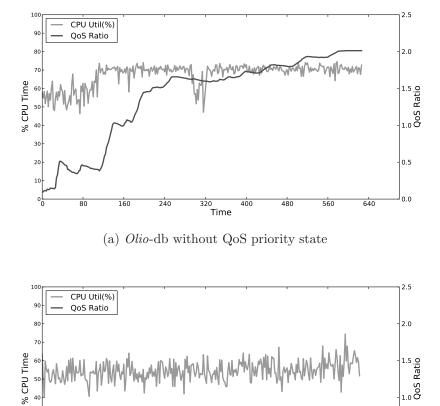

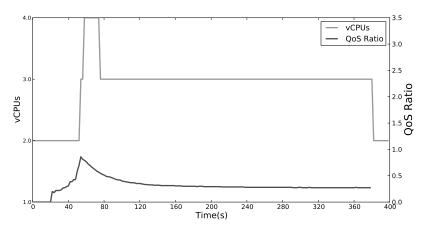

| Figure 6.1               | · · · · · · · · · · · · · · · · · · ·                                              |     |

|                          | configured with 2 vCPUs                                                            | 113 |

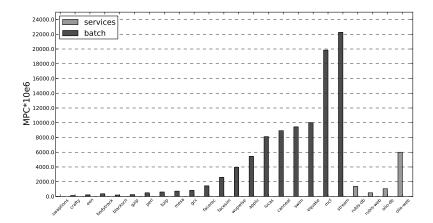

| Figure 6.2               |                                                                                    |     |

|                          | applications.                                                                      | 114 |

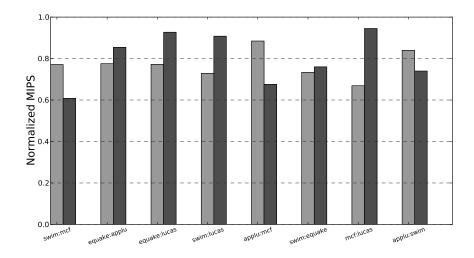

| Figure 6.3               | 1                                                                                  |     |

|                          | the MIPS of each workload in a consolidated combination nor-                       |     |

|                          | malized against the MIPS it had when running alone. For each                       |     |

|                          | combination b1:b2, the gray bar shows the normalized MIPS of                       | 110 |

| D:                       | b1 and the black bar shows the normalized MIPS of b2                               |     |

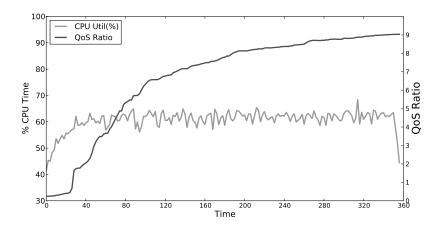

| Figure 6.4               | ± /                                                                                |     |

| Figure 6.5               | • • • • • • • • • • • • • • • • • • • •                                            | 119 |

| Figure 6.6               | : Impact of interference effects on the QoS ratio of service VM (RUBiS web server) | 191 |

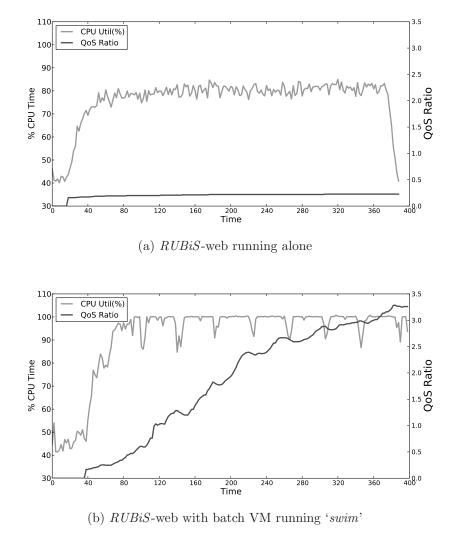

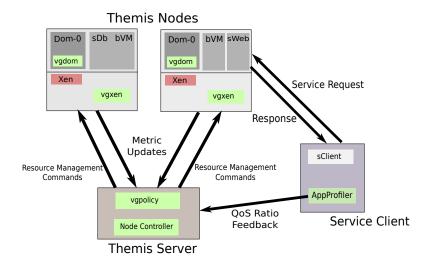

| Figure 6.7               | ,                                                                                  | 124 |

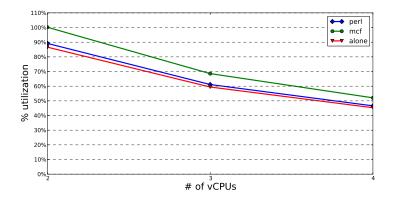

| Figure 6.7<br>Figure 6.8 |                                                                                    | 124 |

| rigure 0.8               | RUBiS web server                                                                   | 127 |

| Figure 6.9               |                                                                                    | 141 |

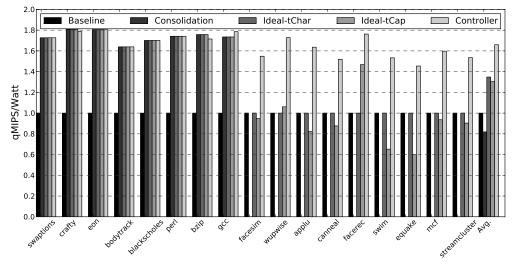

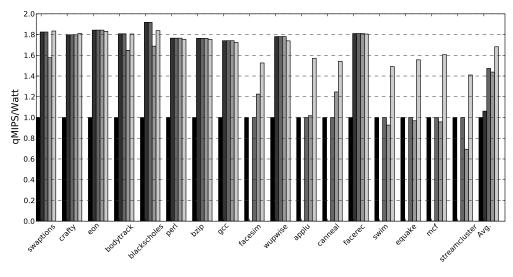

| riguic 0.5               | results are normalized against the Baseline policy                                 | 132 |

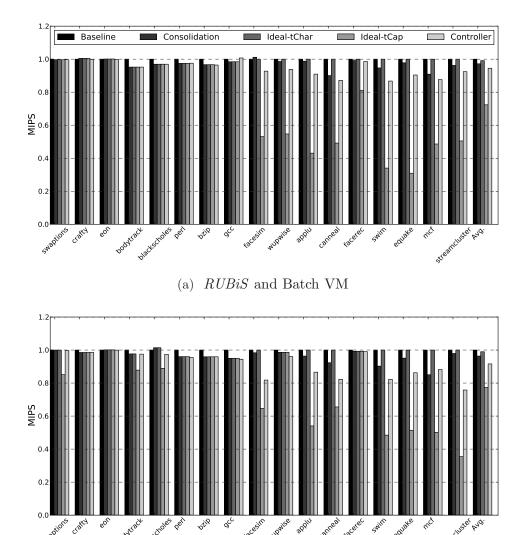

| Figure 6.1               | 0: Comparison of all the policies for Batch VM MIPS. The results                   | 102 |

| 1 18410 0.1              | are normalized against the Baseline policy                                         | 133 |

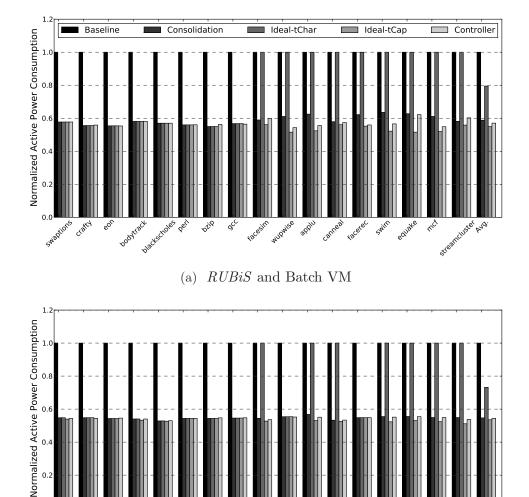

| Figure 6.1               | 1: Comparison of all the policies for active power consumption.                    | 100 |

| 1 180110 0.1             | The results are normalized against the Baseline policy                             | 134 |

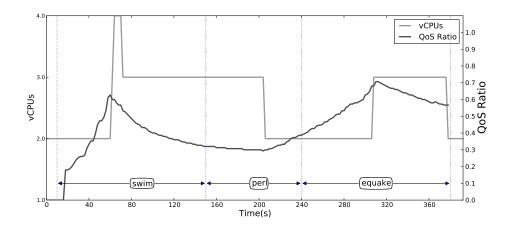

| Figure 6.1               | 2: vCPU selection timeline of Controller for the <i>RUBiS</i> web server           | 101 |

| 0                        | with streamcluster as the consolidated batch VM                                    | 138 |

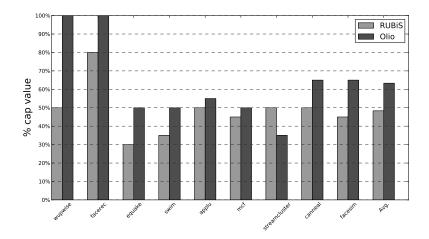

| Figure 6.1               | 3: % cap applied by the Capping policy on the different batch VMs                  |     |

| O                        | with both $RUBiS$ and $Olio.$                                                      | 138 |

| Figure 6.1               | 4: Adaptability with changing batch VM workloads ( <i>RUBiS</i> web                |     |

| Ü                        | server in the service VM)                                                          | 139 |

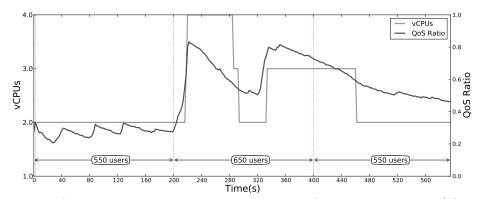

| Figure 6.1               | 5: Adaptability with changing number of service VM users (Olio                     |     |

| -                        | is the service VM and perl is the batch VM)                                        | 140 |

|                          |                                                                                    |     |

# LIST OF TABLES

| Table 2.1:               | Algorithm Controller                                                         | 18       |

|--------------------------|------------------------------------------------------------------------------|----------|

| Table 2.2:               | Loss Evaluation Methodology                                                  | 29       |

| Table 2.3:               | Device and Workload Characteristics for HDD                                  | 30       |

| Table 2.4:               | Working set characteristics for HDD                                          | 31       |

| Table 2.5:               | Energy Savings/Performance Delay Results for HDD with Indi-                  | 33       |

| Table 2.6:               | vidual Experts                                                               |          |

| Table 2.7:               | troller                                                                      | 34<br>38 |

| Table 2.8:               | Energy Savings/Performance Delay Results for CPU on Idle Dominated Workloads | 40       |

| Table 2.9:               | Frequency of selection of experts (%)                                        | 41       |

|                          | Energy Savings/Performance Delay Results for CPU on Compu-                   |          |

|                          | tationally Intensive Workloads                                               | 42       |

| Table 2.11:              | Energy Savings/Performance Delay at 208MHz/1.2V                              | 44       |

| Table 3.1:<br>Table 3.2: | Power Management Policies                                                    | 53<br>55 |

|                          |                                                                              |          |

| Table 4.1:               | DRAM and PRAM Characteristics (1Gb memory chip)                              | 68       |

| Table 4.2:               | Benchmark Characteristics                                                    | 69       |

| Table 4.3:               | Page Swap Interrupts                                                         | 73       |

| Table 5.1:               | MPC Balance Algorithm                                                        | 91       |

| Table 5.2:               | Benchmarks Used                                                              | 97       |

| Table 5.3:               | Comparison of Machines                                                       | L05      |

| Table 6.1:               | Performance Model ( $n_{ref}$ Estimation)                                    | 126      |

#### ACKNOWLEDGEMENTS

It is my pleasure to take this opportunity to thank a number of people who contributed directly or indirectly in my research and this thesis.

Foremost, I would like to express my deep and sincere gratitude to my advisor Prof. Tajana Rosing for imbibing in me the understanding for the nuances of research and for her valuable advice, constant encouragement and able guidance in the pursuit of my research work. I am extremely grateful to her for giving me an opportunity to be her student. I must also thank my doctoral committee, Prof. Dean Tullsen, Prof. Rajesh Gupta, Prof. Tara Javidi and Prof. Amin Vahdat for their valuable feedback and contributions.

My internships at Sun Microsystems (now Oracle) during my PhD were an invaluable experience, and I thank Darrin Johnson for providing me with the opportunities. I sincerely thank Jonathan Chew and Eric Saxe for their prolific discussions, ideas and suggestions that helped me immensely. Collaboration with Google, especially Chris Sadler, in the latter half of my PhD was extremely fruitful and beneficial. I thank Chris for his patience and time in answering my questions, resolving my doubts and helping me establish a clear research direction. My research work was made possible by funding from NSF Project GreenLight Grant 0821155, NSF Grants 0916127 and 1029783, NSF CIAN EEC-0812072, MuSyC, DARPA, UC Micro, Oracle, Google and UCSD Center for Networked Systems. I thank them for their generous support.

I delightfully thank all my lab mates and colleagues for their immense contribution through comments, discussions and guidance. I owe special thanks to Raid Ayoub, Vasileios Kontorinis, Ayse Coskun, Shervin Sharifi, Giacomo Marchetti, Edoardo Regini, Bryan Kim, Nima Nikzad, Arup De and Priti Aghera for their friendship and contributions to my research.

I will also fondly remember the time that I have spent with Mayank Kabra, Vikram Mavalankar, Nikhil Rasiwasia, Nikhil Karamchandani, Sashikant Madduri, Anshuman Gupta, Vijay Mahadevan, Ankit Srivastava and Himanshu Khatri. They prodigiously contributed in making life outside work enjoyable and memorable.

I am indebted to my parents for their unconditional love and selfless support – they have been my pillars of strength. Their unfaltering trust and absolute confidence in my abilities always kept me inspired, focused and optimistic. I thank my younger brother Saurabh for being a perfect buddy. It has been wonderful to see him grow into a mature and responsible person he has become. His relaxed and calm demeanor under all circumstances has amazed and inspired me in equal measure. I thank my wife Kirti for her unflinching support, love and encouragement, which made the tough and relentless phases of my PhD seem a lot easier. I feel extremely privileged to have such a wonderful and loving family.

Chapters 1 and 2, in part, are reprints of the material as it appears in Proceedings of the IEEE/ACM International Conference on Computer-Aided Design, 2006. Dhiman, G. and Rosing, T.S. The dissertation author was the primary investigator and author of this paper.

Chapters 1 and 2, in part, are reprints of the material as it appears in Proceedings of the 12th ACM/IEEE International Symposium on Low Power Electronics and Design, 2007. Dhiman, G. and Rosing, T.S. The dissertation author was the primary investigator and author of this paper.

Chapters 1 and 2, in part, are reprints of the material as it appears in IEEE Transactions in Computer Aided Design of Integrated Circuits and Systems, 2009. Dhiman, G. and Rosing, T.S. The dissertation author was the primary investigator and author of this paper.

Chapters 1 and 3, in part, are reprints of the material as it appears in Proceedings of the Workshop on Power Aware Computing and Systems, 2008. Dhiman, G.; Pusukuri, K.K. and Rosing, T. S. The dissertation author was the primary investigator and author of this paper.

Chapters 1 and 4, in part, are reprints of the material as it appears in Proceedings of the 46th ACM/IEEE Design Automation Conference, 2009. Dhiman, G.; Ayoub, R. and Rosing, T.S. The dissertation author was the primary investigator and author of this paper.

Chapters 1 and 5, in part, are reprints of the material as it appears in Proceedings of the 14th ACM/IEEE International Symposium on Low Power Electron-

ics and Design, 2009. Dhiman, G.; Marchetti, G. and Rosing, T.S. The dissertation author was the primary investigator and author of this paper.

Chapters 1 and 5, in part, are reprints of the material as it appears in ACM Transactions on Design Automation of Electronic Systems, 2010. Dhiman, G.; Marchetti, G. and Rosing, T.S. The dissertation author was the primary investigator and author of this paper.

Chapters 1 and 6, in part, are reprints of the material under submission at International Conference for High Performance Computing, Networking, Storage and Analysis, 2011. Dhiman, G.; Kontorinis, V.; Ayoub, R.; Sadler, C.; Tullsen, D. and Rosing, T.S. The dissertation author is the primary investigator and author of this paper.

#### VITA

| 2002 | B. Tech. in Computer Science and Engineering,<br>Indian Institute of Technology, Roorkee, INDIA |

|------|-------------------------------------------------------------------------------------------------|

| 2007 | M. S. in Computer Science,<br>University of California, San Diego, La Jolla, CA                 |

| 2011 | Ph. D. in Computer Science,<br>University of California, San Diego, La Jolla, CA                |

#### **PUBLICATIONS**

Dhiman, G.; Marchetti, G. and Rosing, T.S., vGreen: A System for Energy Efficient Management of Virtual Machines. In ACM Transactions on Design Automation of Electronic Systems, November 2010.

Dhiman, G.; Kontorinis, V.; Tullsen, D.; Rosing, T.S.; Saxe, E. and Chew, J., Dynamic Workload Characterization for Power Efficient Computing in CMP Systems. In Proceedings of the 15th ACM/IEEE International Symposium on Low Power Electronics and Design, 2010.

Dhiman, G.; Mihic, K. and Rosing, T.S., A System for Online Power Prediction in Virtualized Environments Using Gaussian Mixture Models. In Proceedings of the 47th ACM/IEEE Design Automation Conference, 2010.

Dhiman, G. and Rosing, T.S., System Level Power Management Using Online Learning. In IEEE Transactions in Computer Aided Design of Integrated Circuits and Systems, May 2009.

Dhiman, G.; Marchetti, G. and Rosing, T.S., vGreen: A System for Energy Efficient Computing in Virtualized Environments. In Proceedings of the 14th ACM/IEEE International Symposium on Low Power Electronics and Design, 2009.

Dhiman, G.; Ayoub, R. and Rosing, T.S., PDRAM: A Hybrid PRAM and DRAM Main Memory System. In Proceedings of the 46th ACM/IEEE Design Automation Conference, 2009.

Dhiman, G., Pusukuri, K.K. and Rosing, T. S., Analysis of Dynamic Voltage Scaling for System Level Energy Management. In Proceedings of the Workshop on Power Aware Computing and Systems, 2008.

Dhiman, G. and Rosing, T. S., Dynamic voltage frequency scaling for multi-tasking systems using online learning. In Proceedings of the 12th ACM/IEEE International Symposium on Low Power Electronics and Design, 2007.

Dhiman, G. and Rosing, T. S., Dynamic power management using machine learning. In Proceedings of the IEEE/ACM International Conference on Computer-Aided Design, 2006.

#### ABSTRACT OF THE DISSERTATION

#### Dynamic Workload Characterization for Energy Efficient Computing

by

#### Gaurav Dhiman

Doctor of Philosophy in Computer Science

University of California, San Diego, 2011

Professor Tajana Rosing, Chair

Energy management has become a key issue in the design of computing systems in both mobile as well as enterprise space. For mobile systems it is important from the perspective of battery life, while for large scale systems it directly impacts operational costs, making dynamic energy management methods a critical system component. An effective and conventional mechanism to achieve runtime energy savings is to dynamically reduce the power consumption of the system by transitioning to sleep. This thesis introduces a novel online learning based meta-policy for dynamic power management, where based on characteristics of the device and workload, the system converges to the best suited power management policy for it. We show, that this approach provides superior adaptability across diverse work-

loads compared to state of the art single policy solutions achieving energy savings of up to 61%.

The thesis next provides analysis of effectiveness of power management based approach for energy management on mobile and server class systems. The study reveals that while the effectiveness is high for mobile systems, it is on a decline for server systems due to their *non energy proportional* design. This motivates energy management through two alternative means – energy proportional design and workload consolidation.

For energy proportional design, the thesis focuses on memory subsystem as an example and proposes a memory hierarchy using phase change memory (PRAM) and conventional DRAM. The proposed system exploits the characteristics of workloads (in terms of their read and write intensity) to intelligently place pages across both the memories, thus reducing overall energy consumption of the memory subsystem by 40% on average compared to conventional DRAM. For workload consolidation, the thesis devises cluster level virtual machine (VM) scheduling and resource management algorithms. We show that fine grained information on how the VMs utilize share the system resources like the CPU pipeline, memory bandwidth etc. can be exploited to perform more intelligent VM consolidation and resource management to maximize the overall energy efficiency. Real-life implementation of such VM management policies out-perform state of the art techniques that primarily use just CPU utilization for VM management by 35% on average.

# Chapter 1

# Introduction

Energy management has become a key issue in the design of computing systems today. On one end, the increasing popularity of small scale battery driven portable systems necessitates a design that offers longer battery life without compromising the performance of increasingly complex applications (eg. multimedia, web etc.). On the other end, for large scale systems that populate modern data center and enterprise environments, energy efficient design is key to reduction of all energy-related costs, including capital, operating expenses, and environmental impacts. These reasons have made energy efficient design an active area of research for both small and large scale systems.

Modern system designers and architects have designed system components with efficient support for energy management. For instance, modern CPUs and hard drives support sleep states, which consume dramatically lower power than active states. Modern multi-core architectures provide much higher performance per watt through inherent hardware parallelism. Technologies like virtualization enable higher resource utilization through consolidation, which reduces operational costs and increases the energy efficiency of individual systems.

Effectively utilizing these architectures and designs is key to achieving runtime energy efficiency. This thesis shows that in order to do so, it is extremely important to understand and exploit the characteristics of the workloads running on the system. The characteristics here refer to the way the workloads utilize different resources and components of the system such as CPU, caches, memory etc. Most of the existing state of the art dynamic energy management techniques currently treat CPU utilization as the primary workload characteristic to drive their management decisions, which as we show in this thesis, is sub-optimal. More fine grained information on how intensively workloads use the whole architecture hierarchy – CPU pipeline, shared caches, memory bandwidth etc. can provide opportunities for aggressive energy management even at same CPU utilization levels. This idea forms the over-arching theme of this thesis – developing mechanisms and policies to perform dynamic runtime energy management of the system by leveraging the way workloads use the system resources.

# 1.1 Dynamic Energy Management

A workload that uses a given system component can be represented by a two state finite state machine in terms of how it uses the component: busy and idle. Busy state corresponds to the times during which the workload uses the component to actively perform some processing. For instance, when an application thread in running on the CPU or the hard disk is spinning to serve a block request. Conversely, the idle state corresponds to the instances when the workload is not generating any requests for the component, as a consequence of which, it is inactive or not being utilized. Energy consumption for any workload on an operational system is the product of the power consumption of the system components and the runtime of the workload:

$$E = \int_{t_0}^{t_1} P(t) \ dt \tag{1.1}$$

Based on this equation, an intuitive way of dynamically achieving energy savings is to reduce the power consumption of the system with minimal impact on the execution time of the workload. This will result in reduction in energy consumption proportional to the decrease in power consumption. This approach towards energy management is referred to as 'active power management', since it is based on actively managing the power consumption of the system to achieve

energy savings. The power consumption can be managed during both the busy as well as the idle states of the workload. Based on the state of the workloads (and hence the component), i.e. busy or idle, during which power management is performed, the active power management techniques can be divided into two categories:

- Dynamic Power Management (DPM): When the workload is in the idle state, the system component is inactive and its ability to actively execute workloads or serve user requests is not required. Consequently, modern system components like CPUs, hard drives, network cards etc. support sleep states, which consume lower power but compromise the ability of the component to actively serve workload requests. Dynamically utilizing such sleep states during the idle state to achieve energy savings is referred to as Dynamic Power Management or DPM.

- Dynamic Voltage Frequency Scaling (DVFS): In addition to the sleep states, modern CPUs also support low power states (in terms of lower voltage frequency settings) that can be used when it is actively executing the workload. This form of active power management is referred to as Dynamic Voltage Frequency Scaling or DVFS.

The goal of both the active power management techniques – DPM and DVFS, is to maximize the reduction in power consumption with minimal impact on performance, so that the energy consumption (based on equation 1.1) can be minimized. The following discussion will provide details on the existing state of the art approaches for active power management and their applicability and limitations in terms of their effectiveness for energy management.

# 1.1.1 Dynamic Power Management

Dynamic Power Management (DPM) refers to the mechanism of dynamically exploiting the sleep or low power states of system components during the idle states to reduce their power consumption. The control procedure that performs

the DPM decision is referred to as the DPM policy. DPM has been an active area of research and several system level DPM policies have been proposed in the past. The existing DPM policies can be broadly classified into timeout, predictive and stochastic policies. In a timeout policy, the device is put to sleep if it is idle for more than a specified timeout period [59, 37]. For instance, in [59], the device is put to sleep if it is idle for more than  $T_{be}$  (break-even time).  $T_{be}$  of a low power state is the minimum length of the idle period, which compensates for the cost associated with entering it. In contrast, predictive policies [92, 53, 21] predict the duration of upcoming idle period and make the shutdown decision as soon as the device goes idle. Such heuristic policies tend to be easy to implement, but do not offer any guarantee on energy and performance delay, since they do not model the statistical properties of the workload.

Stochastic policies model the workload and device power state changes as stochastic processes. Minimizing power consumption and performance delay then becomes a stochastic optimization problem. For instance, in [80], Paleologo et al assume the arrival of requests as a geometric distribution and model power management as a Discrete-Time Markov Decision Process (DTMDP). This model is subsequently improved in [84, 90] using more complex MDP models (for instance the Time Indexed Semi Markov Decision Process or TISMDP model in [90]) to characterize real life workloads. Stochastic policies offer optimality only for stationary workloads. The work in [20] and [88] extends the stochastic model to handle non stationary workloads by switching between a set of pre-calculated optimal stochastic policies. However, these approaches compromise optimality by switching heuristically and are also quite complex to implement.

# 1.1.2 Dynamic Voltage Frequency Scaling

For components like CPU, power consumption can be also managed while actively executing workload by reducing its operational voltage and frequency setting (v-f setting). This technique is known as Dynamic Voltage Frequency Scaling (DVFS). To see why this is beneficial, the following equation shows the breakdown of power consumption of a typical CPU:

$$P = D + L, D = C_L V^2 f, L = I_L V$$

(1.2)

where  $C_L$  is the load capacitance, V is the supply voltage,  $I_L$  is the leakage current, and f is the operational frequency. The first term corresponds to the dynamic power consumption component of the total power consumption (referred to as D), while the second term corresponds to the leakage power consumption (referred to as L). We can clearly see that the dynamic power has a cubic dependence on the product of voltage and frequency while the leakage power a linear dependence on voltage. Thus, the dynamic component of power consumption clearly benefits (gets reduced) more than the leakage component through reduction in v-f setting. This implies that DVFS is more effective for energy savings on CPUs with lower leakage power component ( $\frac{L}{P}$ ), which makes CPU leakage a very important characteristic to be taken into account while designing DVFS policies.

The existing DVFS techniques may be broadly divided into three categories. The first category of techniques target systems, where the task arrival times, workload and deadlines are known in advance [85, 106]. DVFS is performed at task level in order to reduce energy consumption while meeting hard timing constraints. The second category of techniques require either application or compiler support for performing DVFS [7, 104, 22]. The third category comprises of system level DVFS techniques that target general purpose systems that have no hard task deadlines, and expect no support from application/compiler level. The work done in [101, 38, 96] monitor the system workload in terms of CPU utilization at regular intervals and perform DVFS based on their estimate of CPU utilization for the next interval. These approaches, however, do not take the characteristics of the running tasks into account, which as we show in section 2.3.2, determine the potential benefits of performing DVFS. In contrast, the work done in [102, 19, 56] characterize the running tasks at runtime, and accordingly make the voltage scaling decisions. They use dynamic runtime statistics such as cache hit/miss ratio, memory access counts etc. obtained from the hardware performance counters to perform task characterization. However, the policy in [102] is not flexible since it operates for a static performance loss (10%), while [19] and [56] present results only in a single task environment. Besides, none of these techniques give strategies on how to adapt DVFS policies to different CPU leakage characteristics, which as we discussed above is extremely important for energy savings. The prior algorithms that take leakage into account [58, 24], are targeted towards real time systems, and assume precise knowledge of task deadlines and characteristics in advance.

The existing work on DPM and DVFS policies falls short on three major fronts: (1) Most of the DPM policies are not designed to adapt to diverse device and workload characteristics. As we show in this thesis, some policies can perform very well for certain workloads, but can be easily outperformed by other policies across diverse workloads. (2) Most of the DVFS policies do not take into account both the leakage and workload characteristics for general purpose systems, which, as this thesis shows, is key to performing effective DVFS across diverse workloads. More fine grained information on how intensively the workload uses the CPU pipeline (as opposed to just CPU utilization) and CPU leakage provides additional opportunities for DVFS policies to achieve higher energy savings. (3) None of the DVFS policies are designed to take into account the impact of their decisions on possible energy savings due to DPM. This is extremely important since both of them can be used to save energy for CPUs, and it is critical to devise an approach that can symbiotically perform DVFS and DPM during busy and idle times to save energy.

These observations and limitations serve as our motivation for developing novel DPM and DVFS policies taking into account the workload characteristics to address these concerns.

## 1.1.3 Applicability of Active Power Management

Active power management is an effective approach to achieve energy savings only in systems where majority of power consumed is contributed by components that are 'energy proportional' [42]. Energy proportionality refers to the property of components where their power consumption is proportional to their utilization. This property is extremely important for active power management since it relies on moving components into lower power states when their utilization is low.

For instance, CPUs are highly energy proportional since their power consumption can be reduced in proportion to their utilization through DPM and DVFS states commonly supported by commercial vendors like Intel and AMD. In contrast, components like fans, power supply and memory are not energy proportional since their utilization and power consumption curve is non linear.

The usage pattern of mobile systems is bimodal in nature, high levels of activity interspersed with long periods of inactivity [90, 42]. The majority of power consumption for these systems comes from devices like CPU, screen and radio interface, which can be easily turned off during idle periods. These reasons make mobile systems attractive candidates for aggressive active power management.

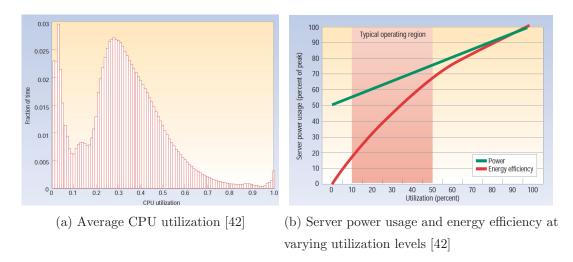

However, the same is not true for the server class systems that populate modern data centers. The usage model for servers has very different characteristics. Figure 1.1a shows the distribution of CPU utilization levels for thousands of servers during a six-month interval at Google [42]. The key observation that can be made from the figure is that servers are rarely completely idle and seldom operate near their maximum utilization. Instead, servers operate most of the time at between 10 and 50% of their maximum utilization levels. As they have few windows of complete idleness, it implies that the servers cannot take advantage of system level DPM policies that mobile devices otherwise find so effective for dynamic energy management. Furthermore, we show in section 3 that the effectiveness of DVFS for energy management on server systems has significantly diminished.

In terms of power consumption, close to 50% power consumed by such systems is contributed by non energy proportional components like fans, power supplies, memory etc. [42]. Figure 1.1b plots the power consumption and the energy efficiency (\frac{utilization}{power}) for a server with active power management enabled. We can clearly see that even an energy efficient server still consumes about half its full power when doing virtually no work. Moreover, the peak energy efficiency occurs at peak utilization and drops quickly as utilization decreases. Notably, energy efficiency in the 20 to 30% utilization range – the point at which servers spend most of their time – has dropped to less than half the energy efficiency at peak performance. Thus, the applicability of active power management for energy

Figure 1.1: Average CPU utilization, power and energy efficiency of 5000 servers during six-month period.

management on such systems is pretty low.

### 1.1.4 Energy Efficiency for Server Systems

For server class systems which, as shown in the previous discussion are not energy proportional, there are two ways of achieving energy efficiency: (1) Design systems to be more energy proportional. (2) Push the existing systems towards more energy efficient zone of operation by increasing their utilization (see Figure 1.1b).

The first approach requires changes at hardware as well as software level. For instance, new non-volatile memory technologies like phase change memory, flash memory etc., that are more energy efficient than conventional DRAM can be used. This may require modifications to both the hardware and software stack of the system to incorporate them. We refer to this approach towards energy management as 'energy proportional design'.

The second approach is to leverage technologies like virtualization that enable consolidation of workloads on fewer physical machines to increase the overall utilization of the system. This is beneficial from three angles: (1) It can generate idle systems, which may be either turned off or be used for doing additional work

thereby increasing the overall energy efficiency; (2) The consolidated machines run at higher utilization, which is inherently more energy efficient (see Figure 1.1b); (3) The energy efficiency of the consolidated machines can be enhanced by optimizing the runtime or throughput of the workloads (refer equation 1.1) under the same power budget. We refer to this mechanism for energy efficiency as 'workload consolidation'.

Role of Workload Characteristics: Due to the flexibility and benefits offered by the virtualization and consolidation approach, it has achieved a lot of traction in recent years in both the open source community (Xen, KVM etc.) as well as industry (VMware, Hyper-V etc.). Policies for power aware virtual machine (VM) consolidation and management using these solutions have been proposed in previous research [86, 74, 103] and are available as commercial products as well (eg. VMware DRS [99]). These policies require understanding of the power consumption and resource utilization of the physical machine, as well as its breakdown among the constituent VMs for optimal decision making. Currently, they treat the overall CPU utilization as the primary workload characteristic of VMs to estimate their respective power consumption and resource utilization, and use it for guiding the VM management policy decisions (VM migration, DVFS etc.). However, this thesis shows that based on more fine grained characteristics of the workloads in these different co-located VMs (like the CPU pipeline, shared cache and memory bandwidth usage), the overall power consumption, resource utilization and performance of the VMs can vary a lot even at similar CPU utilization levels, which can mislead the VM management policies into making decisions that create hotspots of activity, violate performance requirements of diverse workloads and degrade the overall energy efficiency.

### 1.2 Thesis Contributions

This thesis presents research for energy management using all the techniques described above: active power management, energy proportional design and workload consolidation. The following discussion highlights the primary contributions and the outline of the rest of the thesis:

- It presents an online learning based approach towards active power management (both DPM and DVFS). We apply an online learning algorithm [34] to select among a set of possible policies and v-f settings instead of developing a new policy. The algorithm (referred to as controller) has a set of experts (DPM policies/v-f settings) to choose from and selects an expert that has the best chance to perform well based on the controller's characterization of the current workload. The selection takes into account energy savings, performance delay as well as the user specified energy-performance tradeoff (referred to as e/p tradeoff). The algorithm is guaranteed to converge to best performing expert in the set, thus delivering performance atleast as good as the best expert in the set, across different workloads. Evaluation across devices with varying characteristics and workloads shows that the controller is able to achieve energy savings of up to 61%. The controller is described in Chapter 2.

- It shows that the applicability of active power management techniques for server class systems has severely diminished for achieving energy savings, and identifies the reasons for such a trend (non energy proportionality being one of them, as identified in the discussion above). Memory hierarchy is then used an example to illustrate the potential of energy savings through a redesign in both hardware and software stack to achieve much better energy proportionality and system level energy efficiency. The proposed novel memory hierarchy comprises of both conventional DRAM and phase change memory (PRAM), and the system exploits the characteristics of the workloads (in terms of memory reads and writes) to optimize page allocation across both the memories to achieve energy savings of up to 40%. This discussion is included in Chapters 3 and 4.

- It introduces vGreen, a multi-tiered software system to manage virtual machine scheduling and consolidation across a cluster of physical machines with the objective of maximizing the overall energy efficiency and performance

in terms of instruction throughput. The basic premise behind vGreen is to understand and exploit the relationship between the architectural characteristics of the VM workload (eg. instructions per cycle, memory accesses etc.) and its performance and power consumption, which has been not taken into account by the previous state of the art VM management systems. vGreen is implemented and validated on a real life testbed of server systems, and improves the overall performance up to 100% and energy efficiency up to 55% compared to state of the art VM scheduling and power management policies at negligible runtime overhead. The details of vGreen are presented in Chapter 5.

• The vGreen system is extended to include resource management for managing diverse workloads (both latency sensitive and batch applications) in the data center. The enhanced system (referred to as Themis) is responsible for managing the performance and QoS of these diverse workloads while maximizing the overall energy efficiency by facilitating aggressive workload consolidation. The key idea behind Themis is to exploit the inherent heterogeneity in the characteristics of the latency sensitive services and batch applications in the way they use system resources, which allows it to maximize energy-efficient throughput of the latter without sacrificing the service guarantees of the former. Themis implements a resource management policy that outperforms ideal implementations of prior state of the art policies by up to 35% on average in terms of energy efficiency. We present the details of Themis in Chapter 6.

Chapter 1, in part, is a reprint of the material as it appears in IEEE Transactions in Computer Aided Design of Integrated Circuits and Systems, 2009. Dhiman, G. and Rosing, T.S. The dissertation author was the primary investigator and author of this paper.

Chapter 1, in part, is a reprint of the material as it appears in Proceedings of the Workshop on Power Aware Computing and Systems, 2008. Dhiman, G.; Pusukuri, K.K. and Rosing, T. S. The dissertation author was the primary investigator and author of this paper.

Chapter 1, in part, is a reprint of the material as it appears in Proceedings of the 46th ACM/IEEE Design Automation Conference, 2009. Dhiman, G.; Ayoub, R. and Rosing, T.S. . The dissertation author was the primary investigator and author of this paper.

Chapter 1, in part, is a reprint of the material as it appears in ACM Transactions on Design Automation of Electronic Systems, 2010. Dhiman, G.; Marchetti, G. and Rosing, T.S. . The dissertation author was the primary investigator and author of this paper.

Chapter 1, in part, is a reprint of the material under submission at International Conference for High Performance Computing, Networking, Storage and Analysis, 2011. Dhiman, G.; Kontorinis, V.; Ayoub, R.; Sadler, C.; Tullsen, D. and Rosing, T.S. . The dissertation author is the primary investigator and author of this paper.

# Chapter 2

# Active Power Management

# 2.1 Introduction

Dynamic Power Management (DPM) and Dynamic Voltage Frequency Scaling (DVFS) are the two most popular techniques for dynamically reducing system power dissipation. DPM achieves this by selective shutdown of system components that are idle, while the key idea behind DVFS techniques is to dynamically scale the supply voltage/frequency level of the device. Reduction in voltage/frequency level is beneficial, since it reduces the overall power consumption [17]. While DPM can be employed for any system component with multiple power states, while DVFS is useful only for components that support multiple speed and voltage levels (like CPU). A number of modern processors such as Intel XScale [36], AMD Opteron [1] etc. are equipped with DVFS capability. In existing literature however, the design of DPM and DVFS policies for general purpose systems has been treated as separate problems. In this thesis, we target both the problems with the objective of achieving system wide energy efficiency.

A number of heuristic and stochastic policies have been proposed in the past with their design varying in terms of how they take the decision to perform shutdown for DPM. While simpler DPM policies like timeout and predictive policies do it heuristically with no performance guarantees, more sophisticated stochastic policies guarantee optimality for stationary workloads. There is no single policy solution which guarantees optimality under varying workload conditions. We propose a novel setup for DPM, where we maintain a set of DPM policies (suited for different workloads) and design a control algorithm that selects the best suited one for the current workload. In such a setup, the DPM problem reduces to one of accurate *characterization* and *selection*, where the best suited policy is selected based on the characterization of the current workload.

For devices like CPU that support both DPM and DVFS, it is essential to understand the interplay between the two, since the energy savings based on DVFS come at the cost of increased execution time, which implies greater leakage energy consumption and shortened idle periods for applying DPM. This impact, as we show later on, depends on the nature of the executing workload in terms of its CPU and memory intensiveness and the leakage power characteristics. Therefore, the problem of performing DPM aware DVFS can be also viewed as one of accurate *characterization* and *selection*, where the best suited voltage-frequency setting (hereon referred to as *v-f setting*) is selected based on the characterization of CPU leakage and the executing workload.

Instead of proposing a new policy for DPM and DVFS, we apply online learning [34] to select among a set of possible policies and v-f settings. The online learning algorithm (referred to as controller) has a set of experts (DPM policies/v-f settings) to choose from and selects an expert that has the best chance to perform well based on the controller's characterization of the current workload. The selection takes into account energy savings, performance delay as well as the user specified energy-performance tradeoff (referred to as e/p tradeoff). The algorithm is guaranteed to converge to best performing expert in the set, thus delivering performance atleast as good as the best expert in the set, across different workloads.

We implement the controller for a server and laptop hard disk drive (HDD), and Intel PXA27x CPU. The controller chooses among a set of policies representing state-of-the-art in DPM, and v-f settings available on the Intel PXA27x CPU. In our experiments, the controller achieved as high as 61% and 49% reduction for HDD and CPU respectively at negligible overhead.

# 2.2 Design

In this section we first describe how both DPM and DVFS can be formulated as a problem of accurate workload characterization and selection. The selection is done among a set of DPM policies (eg. Fixed Timeout, TISMDP etc.) or allowable v-f settings available on the processor or both depending upon the problem we are targeting. Without the loss of generality, we refer to these policies/v-f settings as experts. We then elaborate on our algorithm, which we employ to perform this control activity of workload characterization and expert selection.

### 2.2.1 System Model

DPM problem is fundamentally a decision problem in which the policy has to decide whether or not to perform a shutdown for a given idle period. As described in section 1.1.1, different DPM policies use different mechanisms to decide this. However, as we show in section 2.4, DPM policies outperform each other under different workloads, devices and user e/p tradeoff preferences. This observation motivates the use of multiple DPM policy experts, where the best suited expert is selected as a function of the current workload characteristics and e/p tradeoff.

DVFS problem is intuitively a problem of selection among the given v-f setting experts of the device (eg. CPU). A lower v-f setting can prolong the execution time of a task, hence shortening the upcoming idle period durations, which has a direct impact on the energy savings possible due to DPM. Longer execution times also cause extra leakage energy consumption, which can offset power savings due to DVFS (explained in detail in section 2.3.2). An ideal DVFS policy must understand this impact and hence perform v-f setting selection with the objective of reducing the overall energy consumption. The primary elements which govern the choice of v-f settings are the characteristics of the executing workload in terms of its CPU/memory intensiveness and the device leakage power characteristics. This observation transforms the DVFS problem into one of accurate modeling of the characteristics of the executing task and device leakage, which in turn drives the

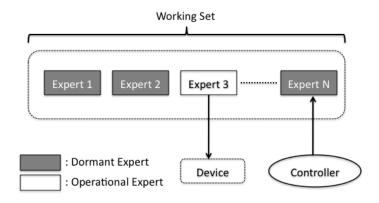

Figure 2.1: Overall System Model.

expert selection.

To summarize, both DPM and DVFS problems can be solved by selection of appropriate expert based on the current workload characterization. For DPM, the characterization is in terms of the distribution of idle period durations, while for DVFS it is in terms of the CPU/memory intensiveness of the executing task. With this background, we now present our system model, which consists of 3 primary entities as shown in Figure 2.1: (1) Controller: The core algorithm we employ to perform the workload characterization and expert selection activity for both DPM and DVFS. (2) Working Set: It is the set of experts, the controller selects from. An expert can be any DPM policy (for DPM) or any allowable v-f setting (for DVFS). (3) Device: Device is the entity whose power is being managed by the controller.

We invoke the controller on an *event*, which we refer to as the *controller event*. For DPM this event is the idle period, i.e. we run the controller whenever an idle period occurs. For DVFS, it is the scheduler tick of the operating system. Scheduler tick is a periodic timer interrupt, which is used by the OS scheduler to make scheduling decisions. Hence, it is the finest granularity at which system updates are performed.

As shown in Figure 2.1, the experts can be in one of the 2 possible states: dormant or operational. By default all the experts are in the dormant state, and are referred to as the dormant experts. When a controller event occurs, the controller on the basis of its model of the current workload selects an expert that has the

highest probability to perform well. This selected expert is referred to as the operational expert, which can either be a DPM policy or a v-f setting depending upon the event (idle period or scheduler tick). The amount of time for which the expert stays in the operational state is referred to as the operative period, after which it returns to its default dormant state. The operative period for an operational expert in case of DPM is the length of the idle period, while in case of DVFS is the length of the scheduler quantum. In Figure 2.1, this implies that Expert3 has been selected by the controller as the operational expert for the current operative period.

#### 2.2.2 Controller

We adapt Freund et al's on-line allocation algorithm [34] to the problem of DPM/DVFS. A big advantage of the algorithm is that it provides a theoretical guarantee on convergence to the best suited expert in the working set. We present an analysis of the theoretical bound in section 2.2.3.

Table 2.1 contains the pseudo-code for the algorithm. The controller has N experts to choose from; we number these i=1,2...N. The experts can be any DPM policy (for DPM) or any valid v-f setting (for DVFS). The algorithm associates and maintains a weight vector  $\mathbf{w}^t = \langle w_1^t, w_2^t \dots w_N^t \rangle$ , where  $w_i^t$  is a weight factor corresponding to expert i for operative period t. The value of weight factor, at any point in time, reflects the performance of the expert, with a higher value indicating a better performance. All of the weights of the initial vector  $\mathbf{w}^1$  sum to one, as seen in Table 2.1. In our implementation, we assign equal weights to all the experts at initialization.

To perform expert selection, the controller maintains a probability vector  $\mathbf{r}^t = \langle r_1^t, r_2^t \dots r_N^t \rangle$  where  $0 \leq r_i^t \leq 1$ , consists of probability factors associated with each expert for operative period t. It is obtained by normalizing the weight vector as shown below:

$$\mathbf{r}^t = \frac{\mathbf{w}^t}{\sum_{i=1}^N w_i^t} \tag{2.1}$$

At any point in time the best performing expert, in accordance with the current workload, has the highest probability factor among all the experts. Thus the

Table 2.1: Algorithm Controller.

Parameters:  $\beta \in [0,1]$

#### Initialization:

- -Initial weight vector  $\mathbf{w}^1 \in [0,1]^N$ , such that  $\sum_{i=1}^N w_i^1 = 1$

- -DPM/DVFS specific initialization

For operative periods  $t = 1, 2 \dots$

- 1: Choose expert with highest probability factor in  $r^t$

- 2: Operative period starts  $\rightarrow$  operational expert takes control of the device

- 3: Operative period ends  $\rightarrow$  DPM/DVFS specific evaluation of experts

- 4: Set the new weights vector to be:  $w_i^{t+1} = w_i^t \cdot \beta^{l_i^t}$

controller simply selects the expert with the highest probability factor as the operational expert for the upcoming operative period. If the probability factor of multiple experts is equal, then it randomly selects one of them with a uniform probability (step 1 in Table 2.1).

When the operative period starts, the operational expert takes control of the device (step 2 in Table 2.1). For DPM, the operational DPM expert takes the shutdown decision. For DVFS, the v-f setting corresponding to the operational DVFS expert is applied to the CPU. When, the operative period ends, the controller does an evaluation of all the experts in the working set (step 3 in Table 2.1). The key objective of performing evaluation is to figure out how suitable each expert was for the just concluded operative period. The details on how the controller actually estimates this suitability are DPM/DVFS specific and are provided in the next section. The end result of this evaluation is a loss factor ( $l_i^t$ ) corresponding to each expert i, which indicates how unsuitable it was for the previous operative period. A higher value indicates higher unsuitability and vice versa.

The final step in the algorithm involves updating the weight factors for each expert on the basis of the loss they have incurred:

$$w_i^{t+1} = w_i^t \cdot \beta^{l_i^t} \tag{2.2}$$

Thus, the weight factors corresponding to experts with higher loss are penalized

more by this simple multiplicative rule. The value of constant  $\beta$  can be set between 0 and 1. The criterion for selecting its appropriate value is explained in [34]. This rule gives higher probability of selecting the better performing experts in the next operative period. Once the weights are updated we are again ready to select the operational expert for next operative period by calculating the new probability vector  $\mathbf{r}^t$  using step 1 in Table 2.1.

#### 2.2.3 Performance Bound of Controller

From the previous discussions we know that  $l_i^t$  is the loss incurred by each expert for the operative period t. Hence, the average loss incurred by our scheme for a given operative period t in a system with N experts is:

$$\sum_{i=1}^{N} r_i^t l_i^t = \mathbf{r}^t \cdot \mathbf{l}^t \tag{2.3}$$

The goal of the algorithm is to minimize its cumulative loss relative to the loss incurred by the best expert. That is, the controller attempts to minimize the net loss

$$L_G - min_iL_i$$

where,  $L_G = \sum_{t=1}^T \mathbf{r}^t \cdot \mathbf{l}^t$  is the total loss incurred by controller, and  $L_i = \sum_{t=1}^T l_i^t$  is individual expert i's cumulative loss over T operative periods. It can be shown [34], that net loss of the algorithm is bounded by  $O(\sqrt{T \ln N})$  or that the average net loss per period decreases at the rate  $O(\sqrt{\ln N/T})$ . Thus, as T increases, the difference decreases to zero. This guarantees that the performance of the controller is close to that of the best performing expert for any workload.

# 2.3 Implementation Details

The previous section gave an overview of how DPM and DVFS can be modeled as workload characterization and expert selection problems that can be solved using the controller algorithm. In this section, we provide implementation details required for accomplishing this solution. We break this section into two parts, with the first part discussing details pertaining devices that support only DPM and the second part considering devices that support both DPM and DVFS (specifically CPU). Finally, we show how controller can explicitly be adapted to different leakage regimes.

# 2.3.1 Devices with only DPM

In this section, we discuss controller implementation with respect to devices that support only DPM such as HDD, memory, network card etc.