# UC Berkeley UC Berkeley Electronic Theses and Dissertations

## Title

Fully Integrated Silicon Terahertz Transceivers for Sensing and Communication Applications

Permalink https://escholarship.org/uc/item/6d6311w8

Author Park, Jungdong

Publication Date 2012

Peer reviewed|Thesis/dissertation

Fully Integrated Silicon Terahertz Transceivers for Sensing and Communication Applications

By

Jung-Dong Park

A dissertation submitted in partial satisfaction of the

requirements for the degree of

Doctor of Philosophy

in

Engineering - Electrical Engineering and Computer Sciences

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge: Professor Ali M. Niknejad, Chair Professor Jan M. Rabaey Professor Paul K. Wright

Spring 2012

Fully Integrated Silicon Terahertz Transceivers for Sensing and Communication Applications

Copyright © 2012

by

Jung-Dong Park

#### Abstract

Fully Integrated Silicon Terahertz Transceivers for Sensing and Communication Applications

by

Jung-Dong Park

Doctor of Philosophy in Engineering – Electrical Engineering and Computer Sciences

University of California, Berkeley

Professor Ali M. Niknejad, Chair

With advancement of the silicon device, we have witnessed revolutionary achievements in RF and millimeter-wave integrated circuit (IC) technology during last decade. Reflecting the impact of the RFICs in its compactness, low-cost, and mass production, the Terahertz Silicon Integrated Circuit (THz-IC) will open a new era in imaging, sensing, spectroscopy, and ultrafast wireless communication. This thesis mainly explores two fully integrated terahertz transceivers for sensing and communication applications in well matured 0.13 µm BiCMOS and 65 nm digital CMOS technology. Since antenna size shrinks quadratically as radiation frequency increases for a given gain, on-chip antennas have great potential in terahertz range by eliminating packaging issues for cost-effective, compact terahertz transceivers. To achieve high radiation efficiency, we investigate the loss mechanisms of several on-chip antennas implemented in conventional (Bi) CMOS technologies. By introducing a compact N-push clamping harmonic generator utilizing the transformer-coupled push-push structure with Coplanar Stripline (CPS), the fundamental signal filtering is effectively achieved by highly rejecting the common-mode input. The designed *N*-push harmonic generator with proposed architecture is robust to the phase mismatch in driving signals. A 0.38 THz Frequency Modulated Continuous Wave (FMCW) radar transceiver is presented with the ranging and detection of a target in 10 cm. A 0.26 THz fully integrated CMOS transceiver is demonstrated for wireless chip to chip communication. The non-coherent On-Off Keying (OOK) transceiver with dual antenna chains is implemented to overcome the limited device performance in 65 nm CMOS which achieves +5 dBm of the Equivalent Isotropically Radiated Power (EIRP).

To my wife for her devoted love, to my son and daughters for their endless love, and to my parents for their unbounded love and support.

# Contents

| List of Figures |  |  |

|-----------------|--|--|

| List of Tables  |  |  |

| 1 | Introduction                                                     | 1  |

|---|------------------------------------------------------------------|----|

|   | 1.1 Terahertz Overview                                           | 2  |

|   | 1.1.1 Terahertz Regime                                           | 2  |

|   | 1.1.2 Terahertz Gap                                              | 2  |

|   | 1.1.3 Terahertz Source in Photonics                              | 3  |

|   | 1.1.4 Terahertz Source in Electronics                            | 4  |

|   | 1.2 Terahertz Applications                                       | 10 |

|   | 1.2.1 Terahertz Sensing                                          | 10 |

|   | 1.2.2 Terahertz Short Range Communication                        | 11 |

|   | 1.3 Atmospheric Attenuation in Terahertz                         | 12 |

|   | 1.4 Thesis Outline                                               | 13 |

| 2 | On-chip Antennas in (Bi) CMOS Technology                         | 14 |

|   | 2.1 Introduction                                                 | 14 |

|   | 2.2 Loss Mechanism in On-chip Antenna in Silicon                 | 15 |

|   | 2.2.1 Loss from Low Resistive Silicon Substrate                  | 15 |

|   | 2.2.2 Surface-wave Mode Excitation on Silicon Substrate          | 16 |

|   | 2.3 Wafer-thinning Approach for Dipole and Slot Antennas         | 18 |

|   | 2.3.1 Antenna Radiation Efficiency                               | 18 |

|   | 2.3.2 On-chip Folded Slot Antenna with Thinned Silicon Substrate | 19 |

|   | 2.3.3 100 GHz Folded Slot Antenna Design with Wafer-thinning     | 20 |

|   | 2.4 On-chip Antenna with Microstrip Structure                    |    |

|   | 2.4.1 Microstrip Rectangular Patch Antenna                       | 22 |

|   | 2.4.2 Microstrip Half-width Leaky-wave Antenna                   | 31 |

|   | 2.5 Conclusion                                                   | 37 |

| 3 | A 0.38 THz Fully Integrated FMCW Radar Transceiver in BiCMOS     | 38 |

|   | 3.1 Introduction                                                 |    |

|   | 3.2 Harmonic Generation with <i>N</i> -Push Circuitry            |    |

|   | 3.2.1 Generalized <i>N</i> -push Harmonic generator              |    |

|   | 3.2.2 BJT Clamping Circuit Analysis                              | 40 |

|   | 3.3 Terahertz FMCW Transceiver Design                            |    |

|   | 3.3.1 Terahertz FMCW Transceiver Architecture                    |    |

iv

vii

|   | 3.3.2 Fundamental Signal Generation                             | 50  |

|---|-----------------------------------------------------------------|-----|

|   | 3.3.3 Transmitter Circuit Design                                | 53  |

|   | 3.3.4 Receiver Circuit Design                                   |     |

|   | 3.4 Passive Elements                                            | 59  |

|   | 3.4.1 Coplanar Stripline (CPS) Characterization                 | 59  |

|   | 3.4.2 On-chip Patch Antenna Design                              | 63  |

|   | 3.5 Measurement                                                 | 65  |

|   | 3.6 Conclusion                                                  | 68  |

| 4 | A 0.26 THz Fully Integrated Wireless Transceiver in CMOS        | 73  |

|   | 4.1 Introduction.                                               | 73  |

|   | 4.2 Short Range Communication System                            | 74  |

|   | 4.2.1 Required Signal to Noise Ratio                            | 74  |

|   | 4.2.2 Multiple Antenna Transceiver with Spatial Diversity       | 75  |

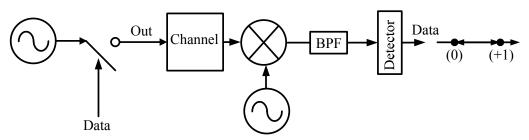

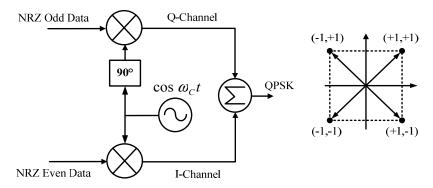

|   | 4.2.3 Modulation Scheme for Terahertz Short Range Communication | 77  |

|   | 4.2.4 Link Budget Analysis                                      | 80  |

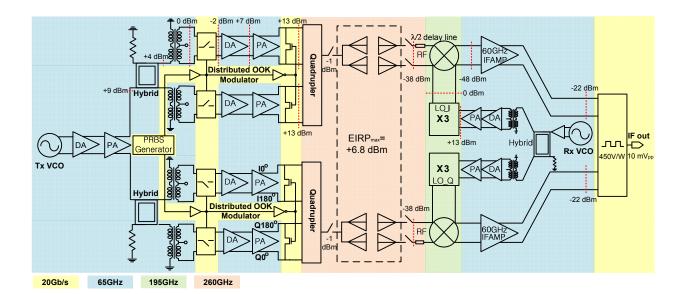

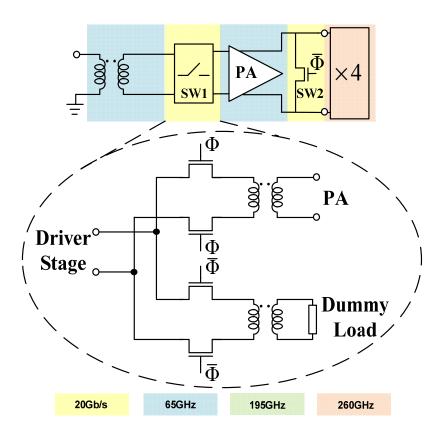

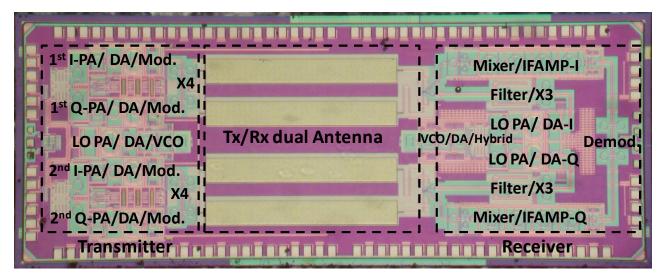

|   | 4.3 CMOS Terahertz Wireless Transceiver Architecture            |     |

|   | 4.4 Transmitter Circuits                                        |     |

|   | 4.4.1 260 GHz Quadrupler                                        | 84  |

|   | 4.4.2 V-band Hybrid                                             | 86  |

|   | 4.4.3 Distributed Non-coherent OOK Modulator in V-band          |     |

|   | 4.4.4 V-band D <sup>-1</sup> Power Amplifier                    | 90  |

|   | 4.4.5 PRBS Generator.                                           |     |

|   | 4.5 Receiver Circuits                                           | 94  |

|   | 4.5.1 195 GHz Tripler                                           | 94  |

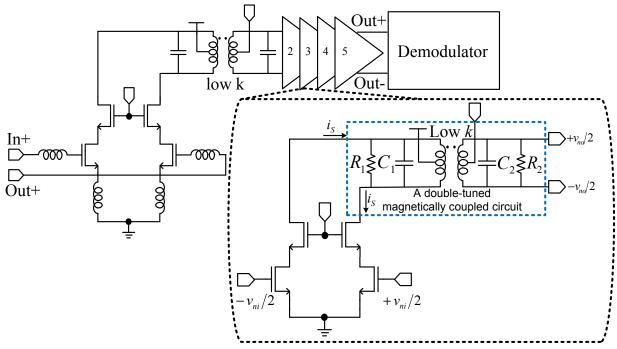

|   | 4.5.2 Demodulator                                               | 97  |

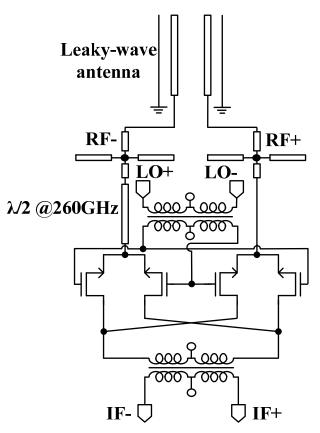

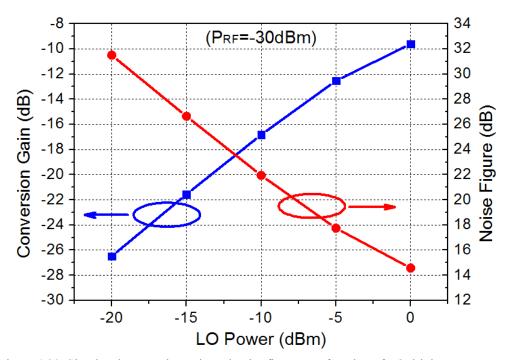

|   | 4.5.3 260 GHz Double Balanced Mixer                             | 99  |

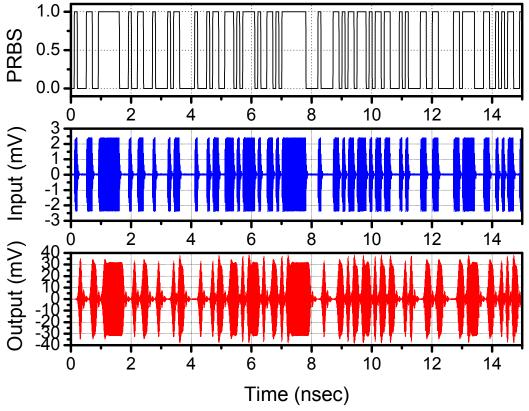

|   | 4.5.4 V-band Wideband IF Amplifier                              | 101 |

|   | 4.5.5 V-band Voltage Controlled Oscillator                      |     |

|   | 4.6 Tx/Rx Dual On-chip Antenna Design                           | 104 |

|   | 4.6.1 Half-width Microstrip Leaky-wave Antenna                  | 104 |

|   | 4.6.2 Tx/Rx Dual Half-width MLWA                                | 104 |

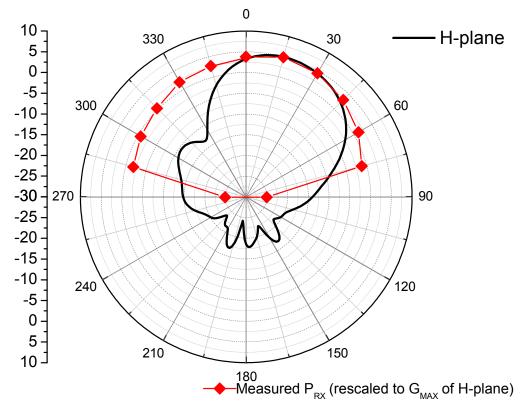

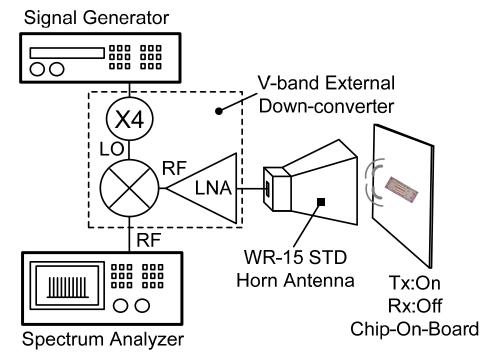

|   | 4.7 Measurement                                                 | 107 |

|   | 4.8 Conclusion                                                  | 110 |

| 5 | Conclusion                                                      | 111 |

|   | 5.1 Thesis Summary                                              | 111 |

|   | 5.2 Future Directions                                           | 112 |

| B | ibliography                                                     | 114 |

|   |                                                                 |     |

# **List of Figures**

| 1.1 Unique terahertz region placed in the transition region                                        | 2  |

|----------------------------------------------------------------------------------------------------|----|

| 1.2. Reported THz-emission power output as a function of frequency                                 | 3  |

| 1.3. Current gain cut-off frequency $(f_T)$ of NMOS, SiGe HBT, and InP HEMT                        | 6  |

| 1.4. Maximum oscillation frequency $(f_{max})$ of NMOS, SiGe HBT, and InP HEMT                     | 6  |

| 1.5. SEM microphotographs of the device cross-section                                              | 7  |

| 1.6. Flow chart of the terahertz circuit design in CAD case                                        | 9  |

| 1.7. Application examples of terahertz sensing                                                     | 10 |

| 1.8. Application examples of terahertz communication                                               | 11 |

| 1.9. Specific attenuation of the earth's atmosphere                                                | 12 |

| 2.1. The two main loss mechanisms of the on-chip antenna                                           | 15 |

| 2.2. Reported on-chip antennas by reducing resistive loss                                          | 16 |

| 2.3. Critical substrate thickness $(h_c)$ as a function of frequency permittivity                  | 17 |

| 2.4. Reported on-chip antennas by suppressing surface-wave excitation mode                         | 18 |

| 2.5. Structural dimension of the designed folded slot antenna with a meandered stub                | 20 |

| 2.6. Input impedance of the designed folded slot with a meandered stub                             | 21 |

| 2.7. Simulated radiation patterns of the folded slot antenna                                       | 22 |

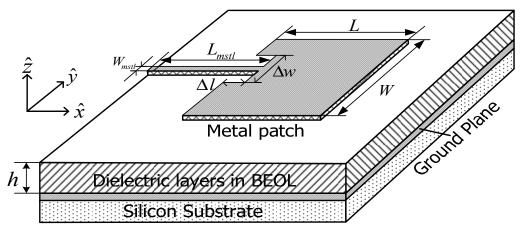

| 2.8. Geometry of the edge-fed microstrip rectangular patch antenna with inset                      | 23 |

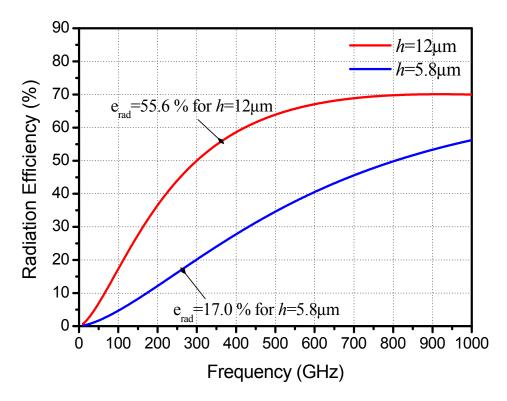

| 2.9. Calculated radiation efficiency of the rectangular patch antenna                              | 28 |

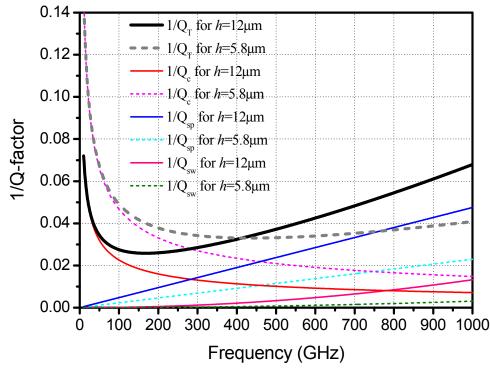

| 2.10. Calculated $1/Q$ factor of the rectangular patch antenna                                     | 28 |

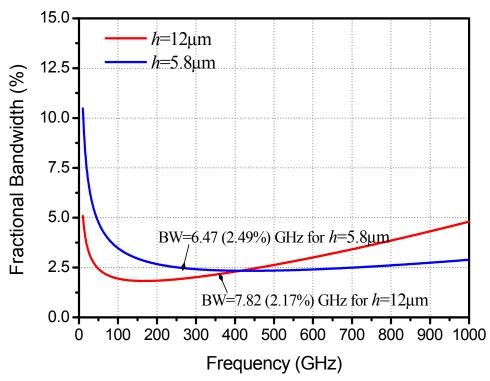

| 2.11. Calculated fractional bandwidth of the rectangular patch antenna                             | 29 |

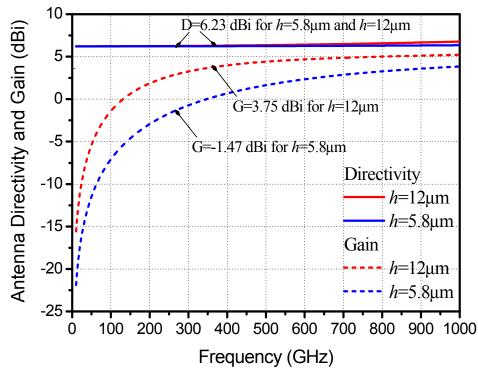

| 2.12. Calculated antenna directivity and gain of the rectangular patch antenna                     | 29 |

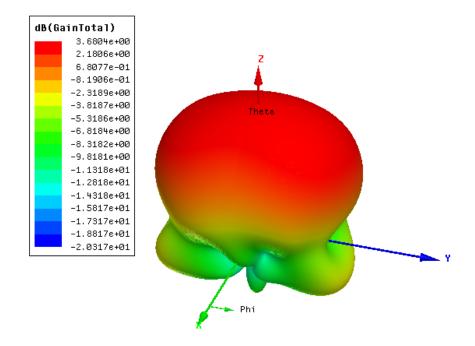

| 2.13. Simulated radiation pattern of the designed microstrip edge-fed patch antenna                | 30 |

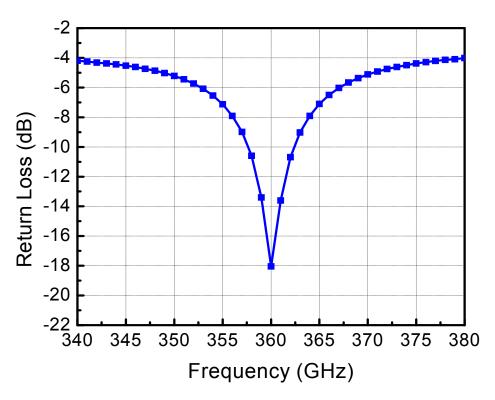

| 2.14. Simulated return loss of the single rectangular patch antenna in 50 $\Omega$ input impedance | 31 |

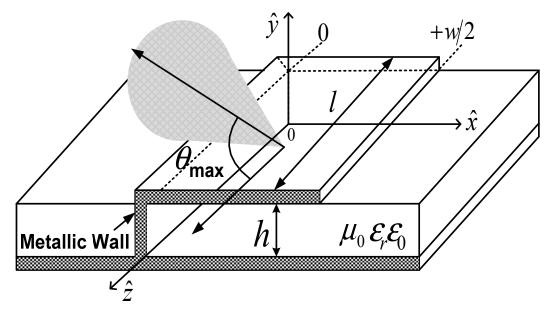

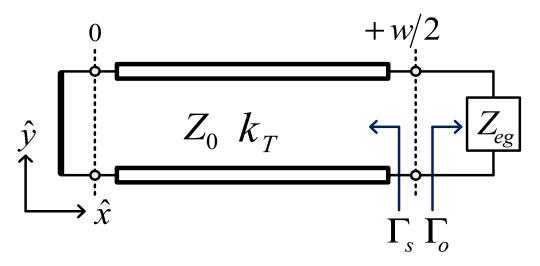

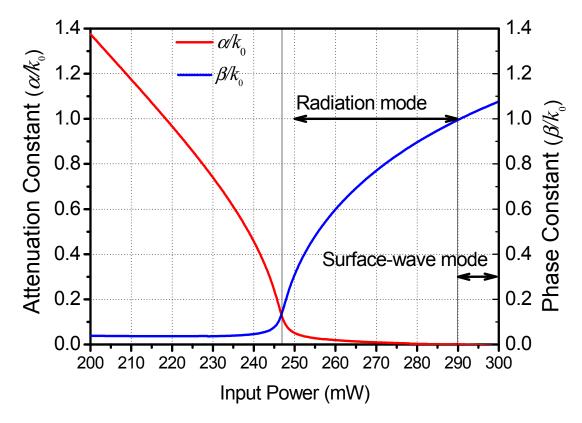

| 2.15. Geometry of the half-width microstrip leaky-wave antenna (MLWA)                              | 34 |

| 2.16. Equivalent circuit for transmission resonance method (TRM)                                   | 34 |

| 2.17. Calculated phase and attenuation constant as a function of the radiation frequency           | 36 |

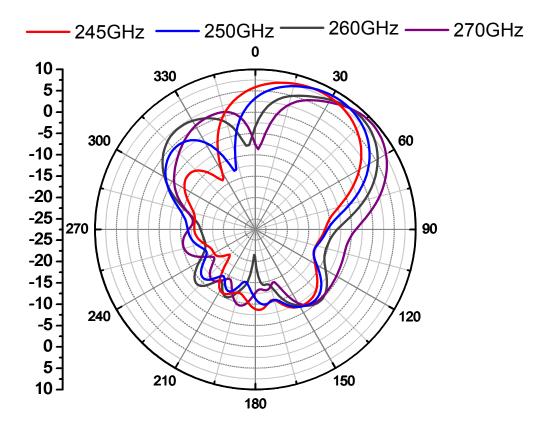

| 2.18. Simulated radiation pattern of the single half-width MLWA vs. frequency                      | 37 |

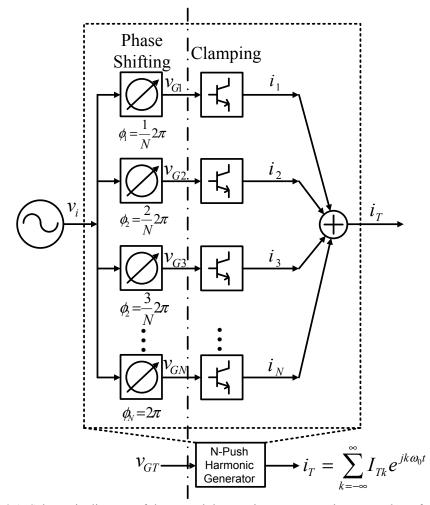

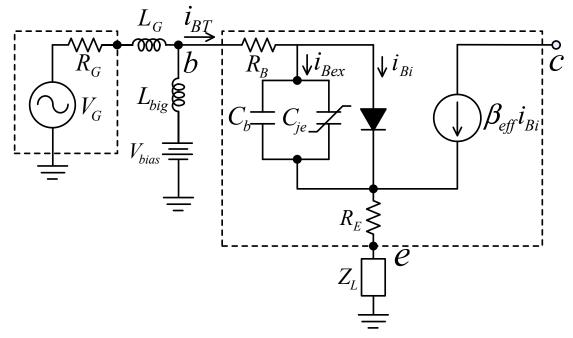

| 3.1. Schematic diagram of the <i>N</i> -push harmonic generator                                    | 39 |

| 3.2. Simplified equivalent BJT clamping circuit for an analytical expression                       | 41 |

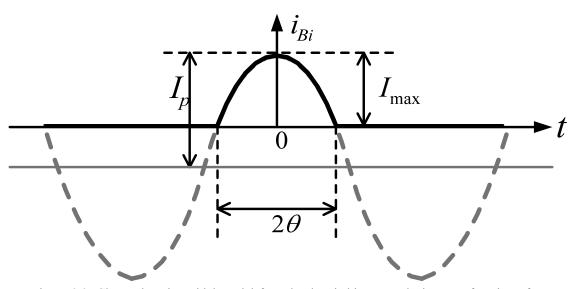

| 3.3. Clamped cosinusoidal model for a hard switching BJT                                           | 41 |

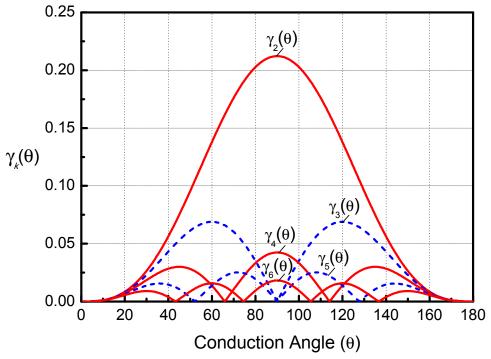

| 3.4. Coefficient of expansion ( $\gamma_k(\theta)$ ) of the clamped cosinusoidal output current    | 43 |

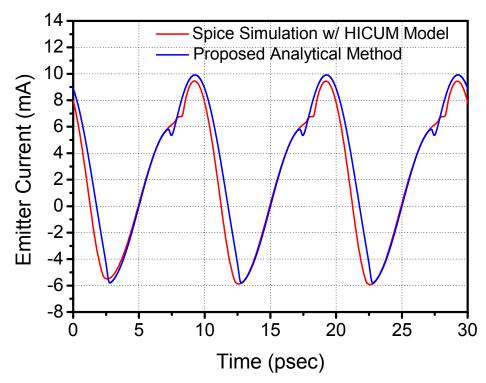

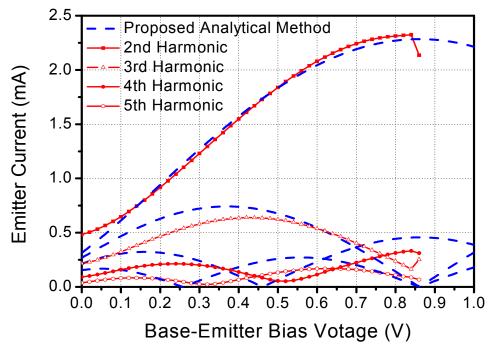

| 3.5. Comparison of transit emitter current between SPICE and proposed model                        | 46 |

| 3.6. Comparison of harmonic components between SPICE and proposed model                            | 46 |

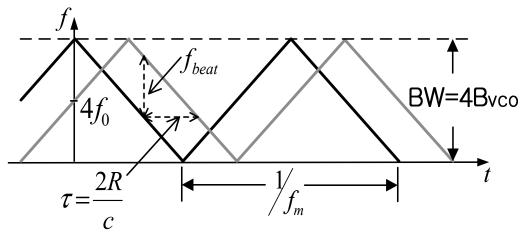

| 3.7. Principle the homodyne FMCW radar                                                             | 49 |

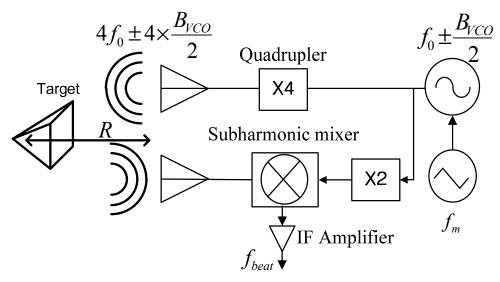

| 3.8. Block diagram of the designed homodyne FMCW transceiver                               | 49 |

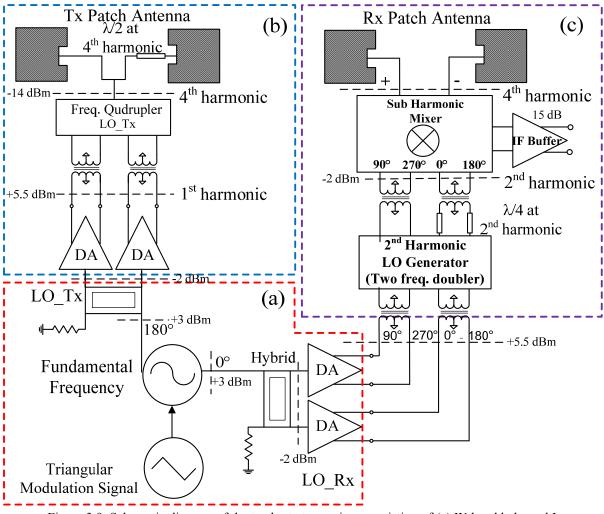

|--------------------------------------------------------------------------------------------|----|

| 3.9. Schematic diagram of the THz transceiver                                              | 50 |

| 3.10. Circuit diagram of (a) Colpitts VCO and (b) driving amplifier                        | 51 |

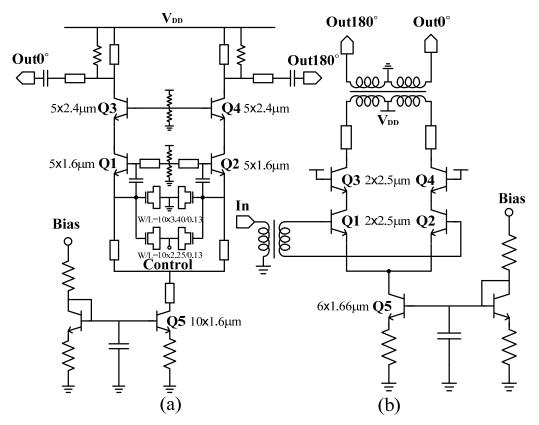

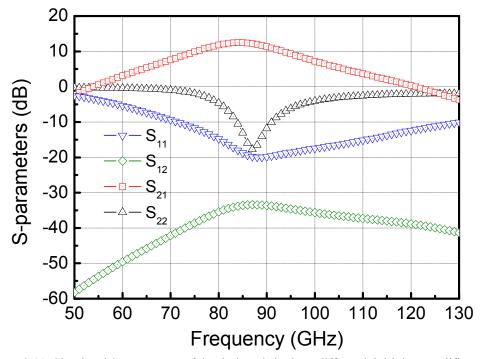

| 3.11. Simulated S-parameters of the designed single to differential driving amplifier      | 51 |

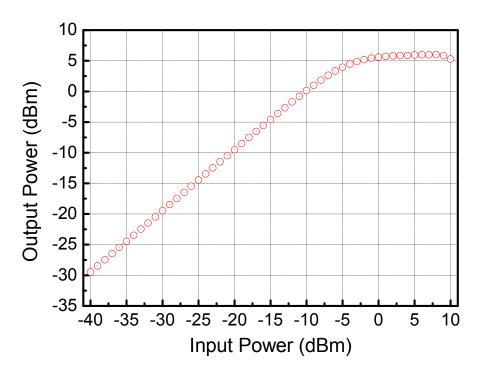

| 3.12. Simulated output power for the designed single to differential driving amplifier     | 52 |

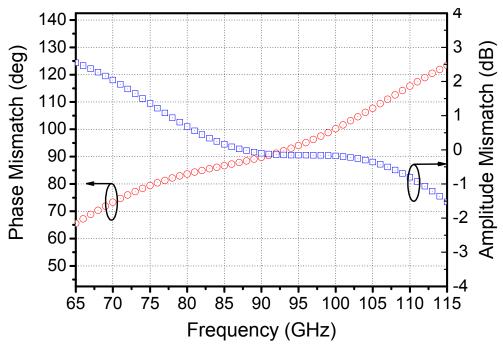

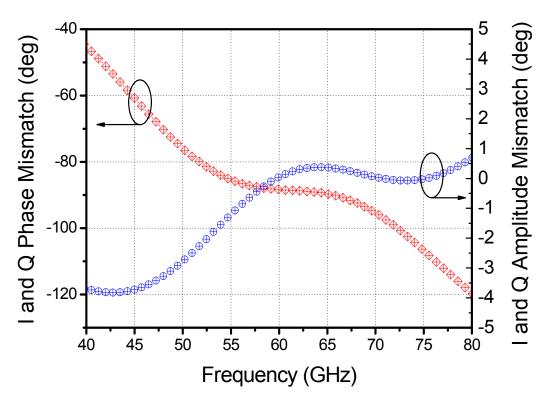

| 3.13. Simulated phase and amplitude mismatch of the designed size reduced hybrid           | 52 |

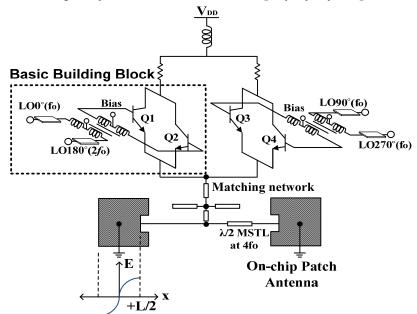

| 3.14. Circuit diagram of the Tx quadrupler                                                 | 53 |

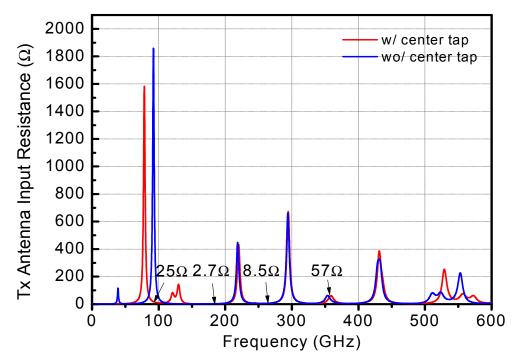

| 3.15. Comparison of the Tx antenna input impedance w/ and w/o ground center tap            | 54 |

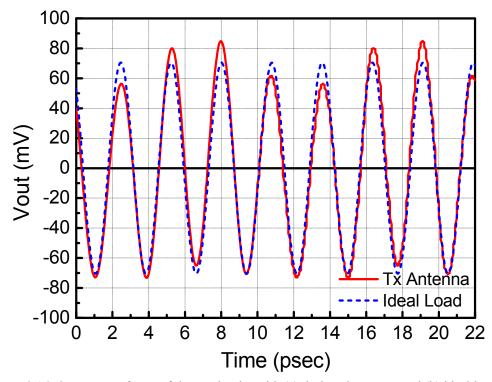

| 3.16. Output waveforms of the quadrupler with (a) designed antenna (b) ideal load          | 54 |

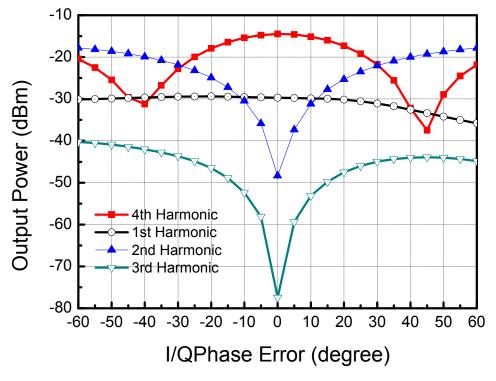

| 3.17. Output harmonics of the transmitter as a function of I/Q phase mismatch              | 55 |

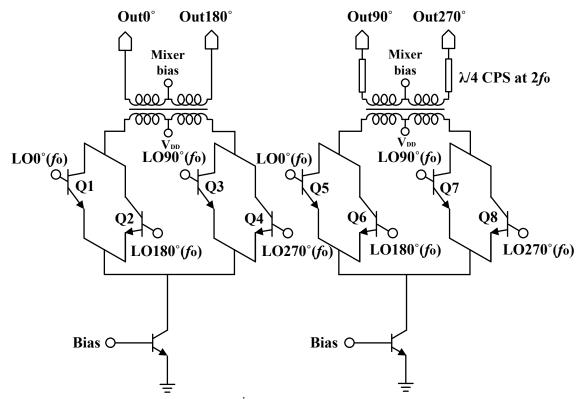

| 3.18. Circuit diagram of the 2 <sup>nd</sup> harmonic quadrature LO generator              | 56 |

| 3.19. Output harmonics of the 2 <sup>nd</sup> harmonic LO generator for I/Q phase mismatch | 57 |

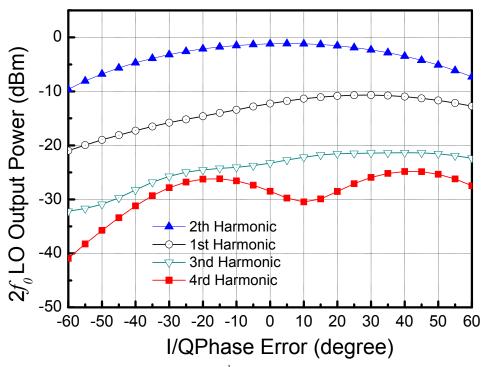

| 3.20. Circuit diagram of the Rx subharmonic double-balanced mixer                          | 58 |

| 3.21. Power conversion loss and NF of the receiver as a function of $2f_0$ LO input power  | 58 |

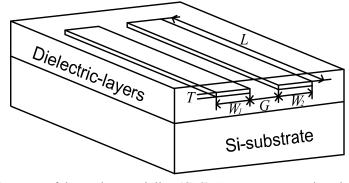

| 3.22. Structure of the Coplanar Stripline (CPS)                                            | 59 |

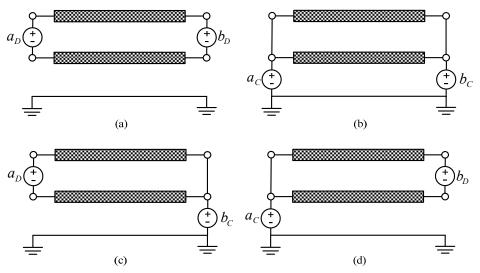

| 3.23. Definition of mixed mode Scattering parameters                                       | 60 |

| 3.24. (a) Port assignment for S-parameter extraction (b) Equivalent model for CPS          |    |

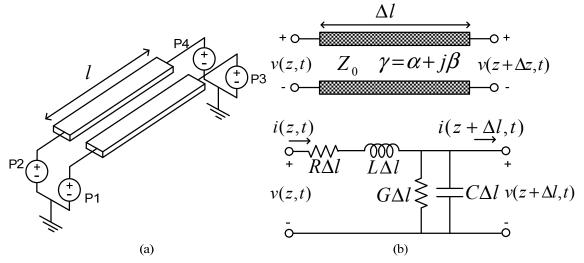

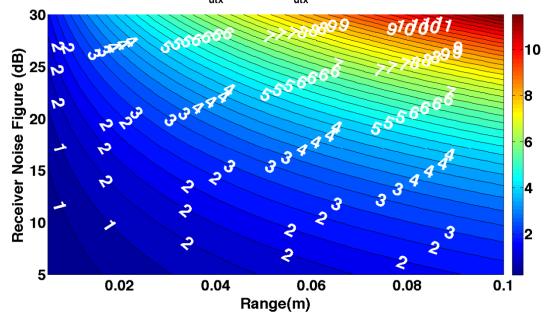

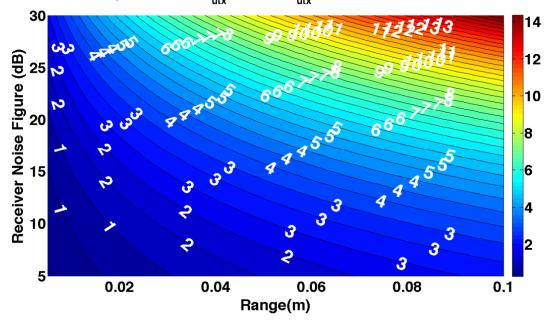

| 3.25. Differential-mode $Z_0$ contour of the CPS depending on the width and gap            |    |

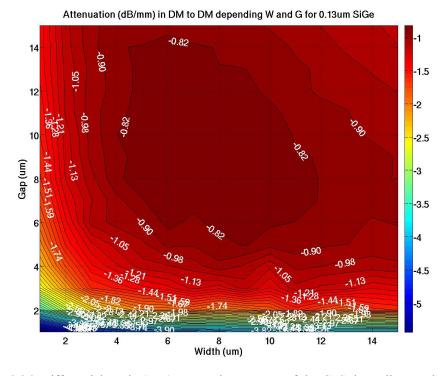

| 3.26. Differential-mode $\alpha$ (dB/mm) contour of the CPS depending on the width and gap |    |

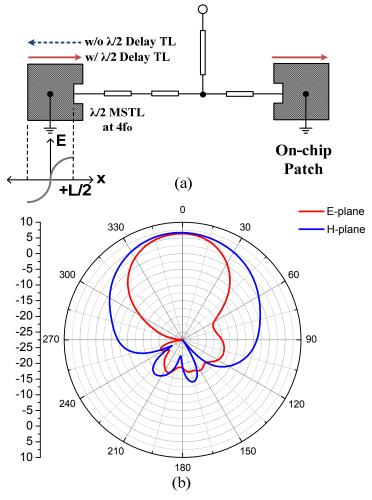

| 3.27. (a) The structure of the Tx on-chip patch antenna and (b) The radiation pattern      |    |

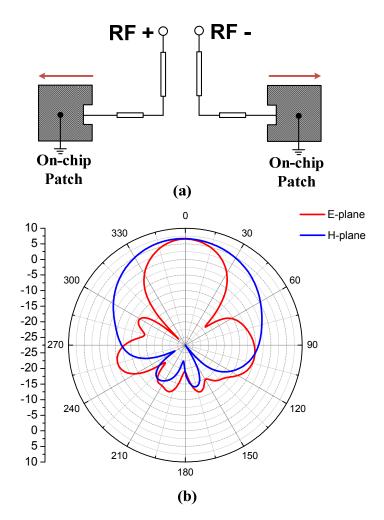

| 3.28. (a) The structure of the Rx on-chip patch antenna and (b) The radiation pattern      |    |

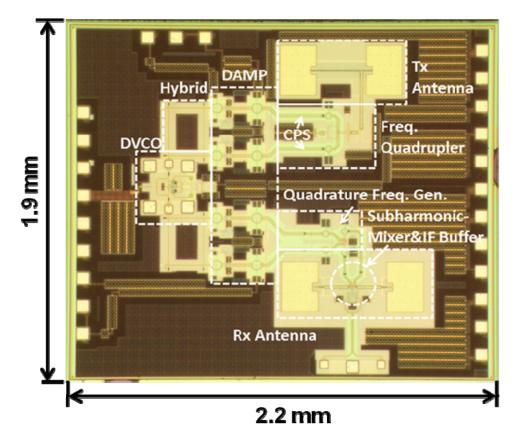

| 3.29. Microphotograph of the fabricated 0.38 THz FMCW radar transceiver                    |    |

| 3.30. Measured phase noise of the stand alone VCO                                          |    |

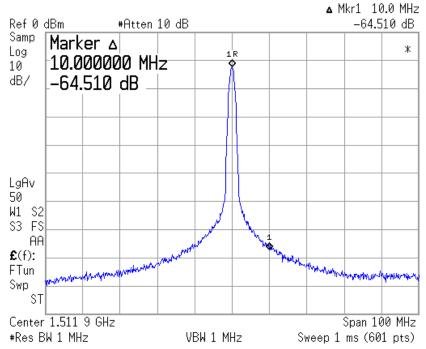

| 3.31. Measurement setup for VCO characterization of the <i>in-situ</i> VCO                 |    |

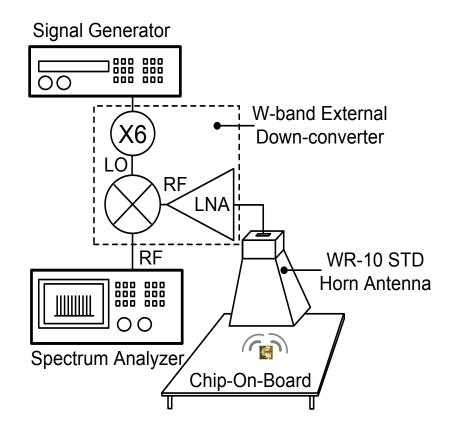

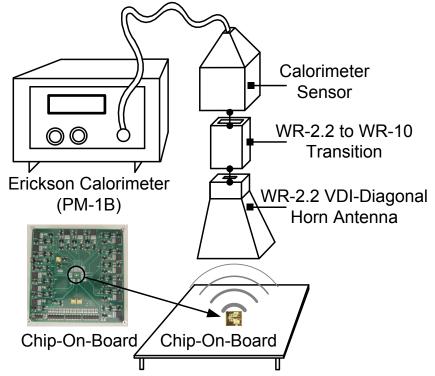

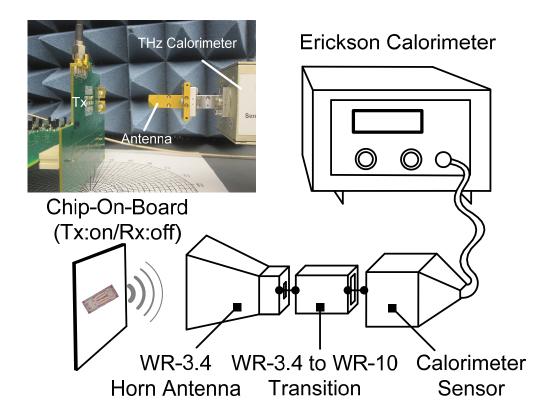

| 3.32. Measurement setup for the EIRP of the transmitter                                    |    |

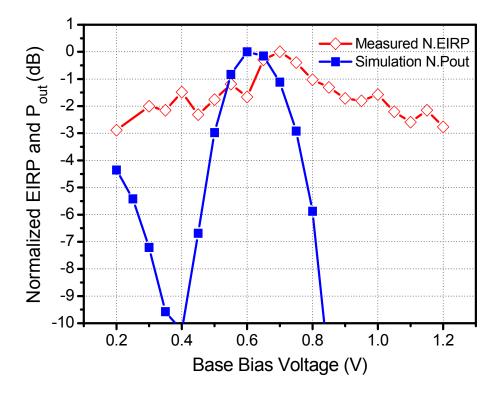

| 3.33. Comparison between measured EIRP and simulated output power vs. the base bias        |    |

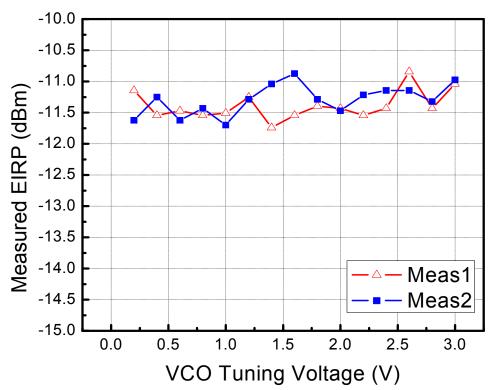

| 3.34. Measured EIRP with calorimeter as a function of the VCO control voltage              |    |

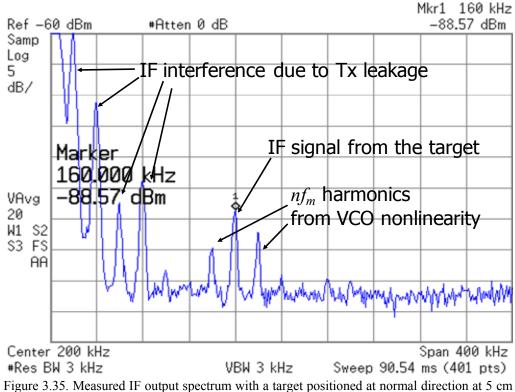

| 3.35 Measured IF output spectrum w/ a target positioned 5 cm distance from TRx             |    |

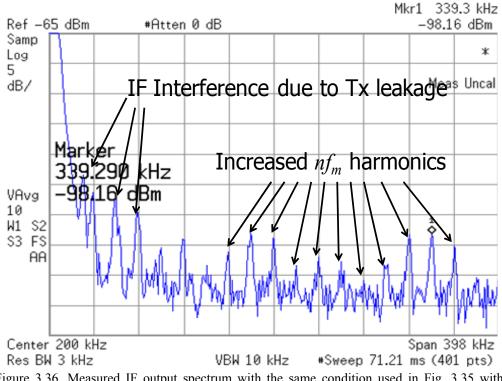

| 3.36. Measured IF output spectrum with maximum frequency chirp in VCO                      |    |

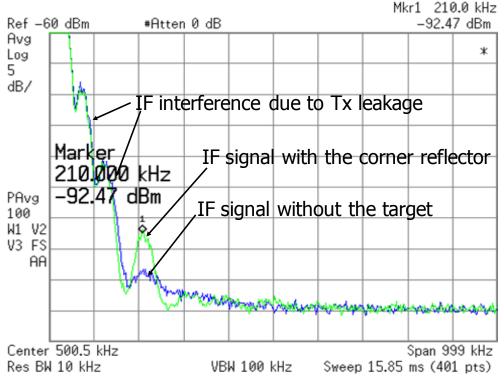

| 3.37. Measured IF output spectrum w/ and w/o a target 10 cm distance from TRx              |    |

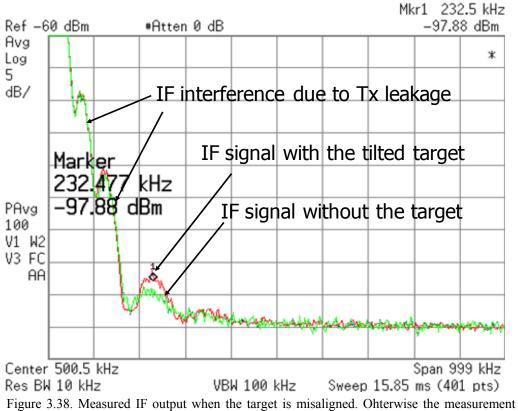

| 3.38. Measured IF output when the target is misaligned                                     |    |

| 4.1. Terahertz short range communication for wireless chip to chip interconnection         |    |

| 4.2. Multiple antenna (a) transmitter (b) receiver for the terahertz wireless link         |    |

| 4.3. Schematic diagram of OOK modulation scheme, and its constellation diagram             | 79 |

| 4.4. Schematic diagram of QPSK modulation scheme, and its constellation diagram            |    |

| 4.5. Required number of array for a TRx with QPSK modulation scheme                        |    |

| 4.6. Required number of array for a TRx with coherent OOK modulation scheme                |    |

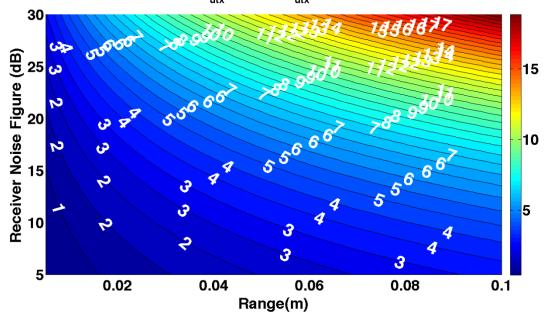

| 4.7. Required number of array for a TRx with non-coherent OOK modulation scheme            | 82 |

|                                                                                            |    |

| 4.8. Block diagram of designed THz wireless transceiver                                  | .83 |

|------------------------------------------------------------------------------------------|-----|

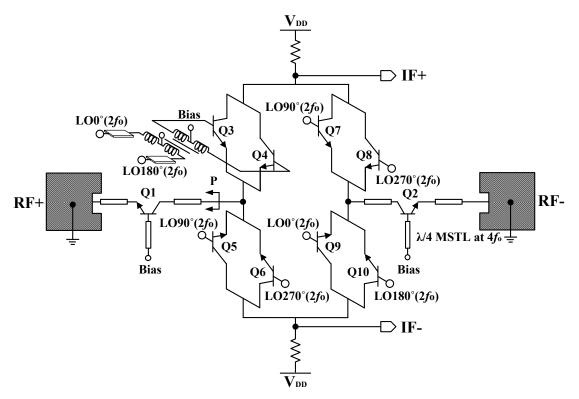

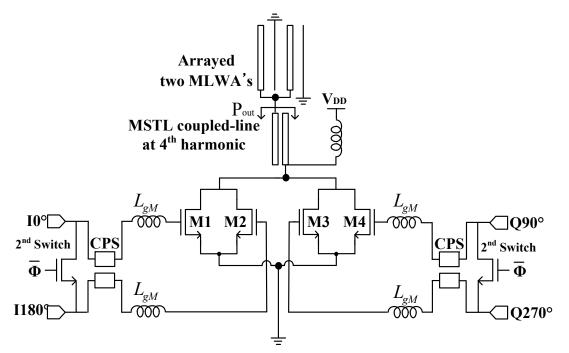

| 4.9. Circuit diagram of the Tx quadrupler with the quadruple-push harmonic structure     | .85 |

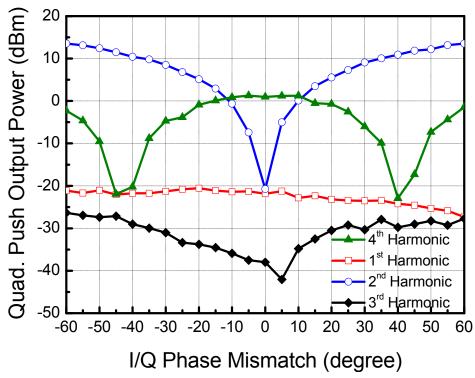

| 4.10. Output harmonics of the Tx quadrupler as a function of I/Q phase mismatch          | .85 |

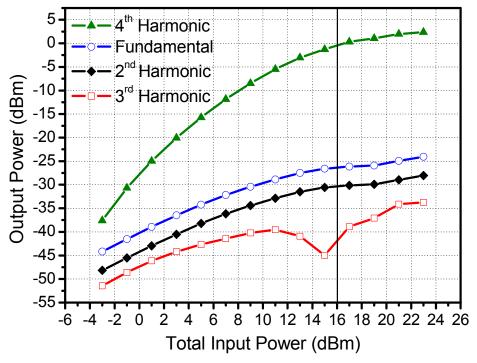

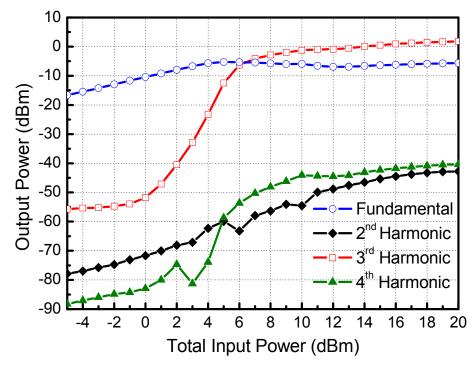

| 4.11. Simulated quadrupler Pout of harmonic components vs. total Pin                     | .86 |

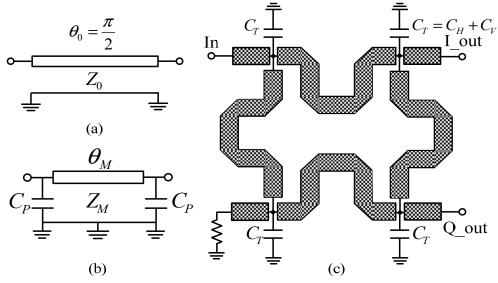

| 4.12. Structure of the meandered hybrid with capacitive load $C_T$                       | .87 |

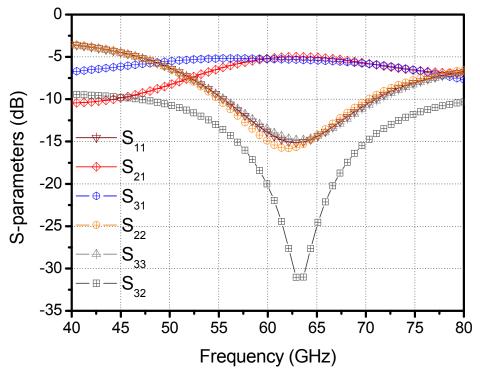

| 4.13. Simulated S-parameters in dB for the designed size reduced hybrid                  | .87 |

| 4.14. Simulated phases of $S_{21}$ and $S_{31}$ for the designed size reduced hybrid     | .88 |

| 4.15. Circuit diagram of the Transmitter distributed non-coherent OOK modulator          | .89 |

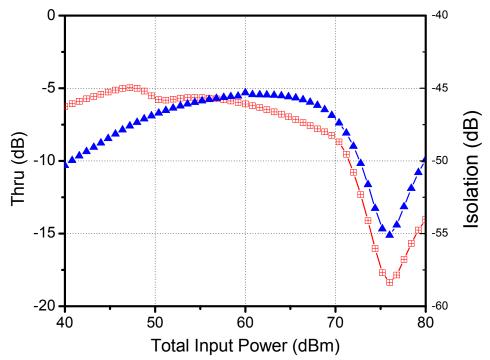

| 4.16. Simulated isolation and thru in dB for the distributed non-coherent OOK modulator  | .89 |

| 4.17. Simulated non-coherent OOK modulated output signal of the power amplifier          | .90 |

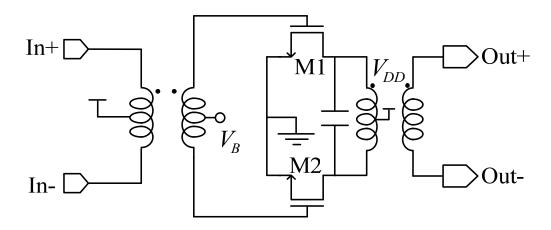

| 4.18. Schematic diagram of Class D <sup>-1</sup> power amplifier                         | .91 |

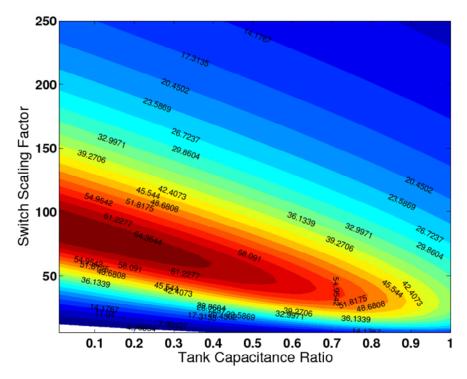

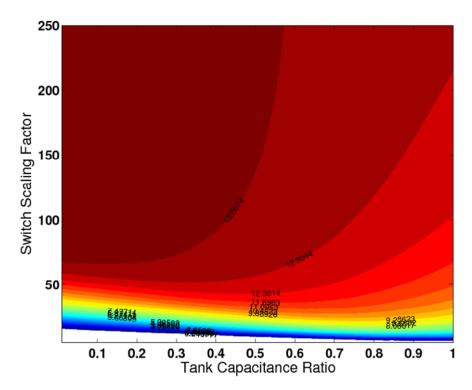

| 4.19. Drain efficiency as a function of tank capacitance ratio and switch scaling factor | .92 |

| 4.20. Output power as a function of tank capacitance ratio and switch scaling factor     | .92 |

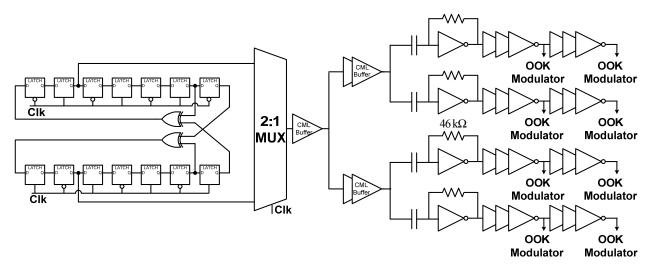

| 4.21. Schematic diagram of the PRBS generator with interleaved architecture              | .93 |

| 4.22 Circuit diagrams of the CML components used in the PRBS generator                   | .94 |

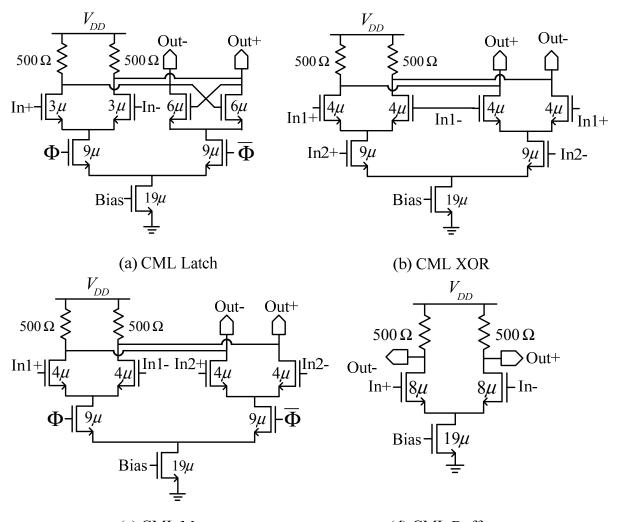

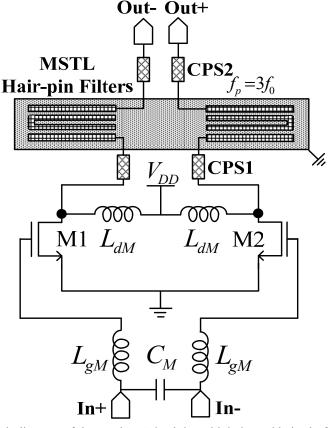

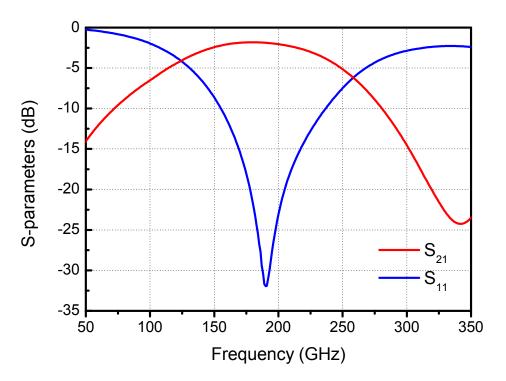

| 4.23. Circuit diagram of the receiver LO tripler with balanced hair pin filters          | .95 |

| 4.24. Simulated differential $S_{21}$ and $S_{11}$ in dB for the balanced hairpin filter | .96 |

| 4.25. Simulated tripler $P_{out}$ of harmonic components depending on the input $P_{in}$ | .96 |

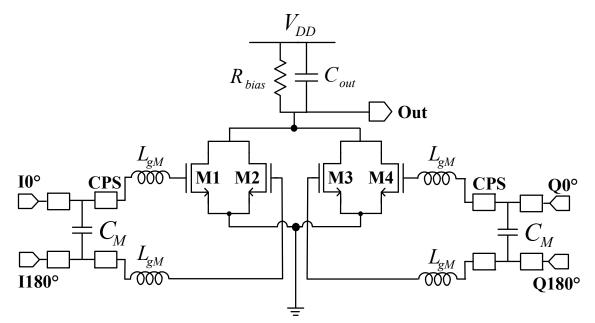

| 4.26. Circuit diagram of the receiver demodulator with two push-push structures          | .97 |

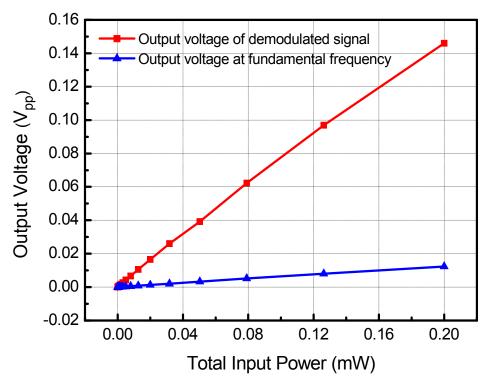

| 4.27. Output voltage of the demodulated signals as a function of the total input power   | .98 |

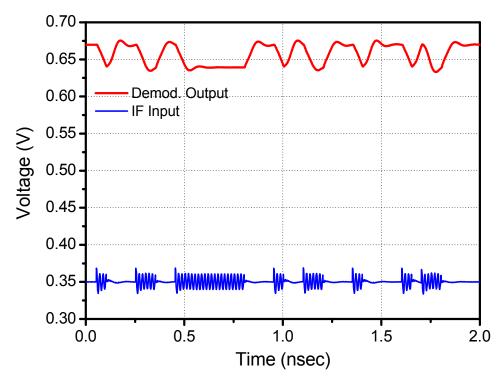

| 4.28. Demodulated output voltage waveform with 20 Gb/s OOK modulated input signal        | .98 |

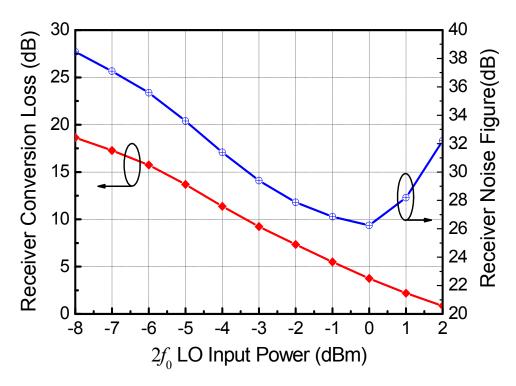

| 4.29. Circuit diagram of the down converting mixer with two push-push structures1        | 00  |

| 4.30. Simulated conversion gain and noise figure as a function of LO driving power1      | 00  |

| 4.31. Schematic diagram of the wideband IF amplifier1                                    | 02  |

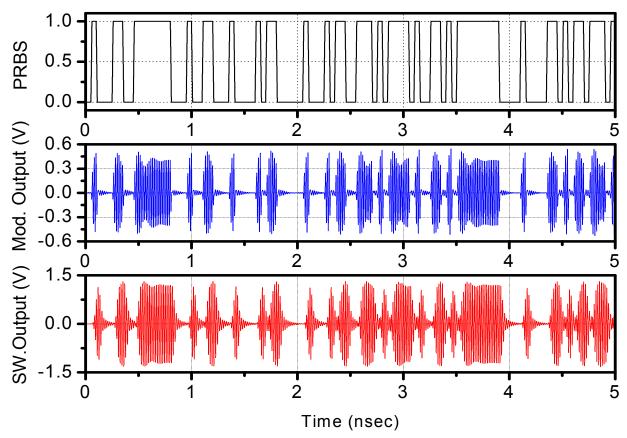

| 4.32. Simulated output with N-OOK modulated 60 GHz signal with 10 Gb/s data rate1        | .02 |

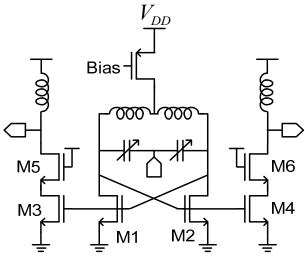

| 4.33. Circuit diagram of the VCO with a cascade buffer1                                  | 03  |

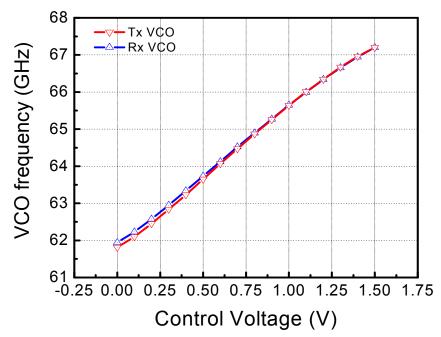

| 4.34. Measured Sweep frequency of Tx and Rx VCO as a function of the control voltage1    | 03  |

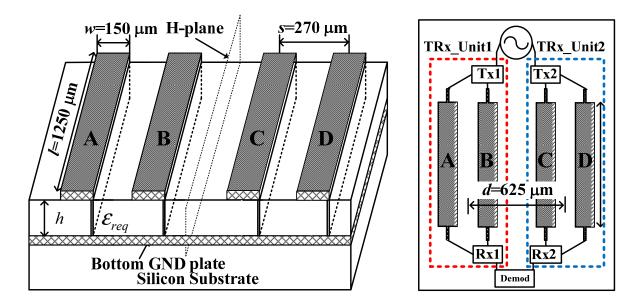

| 4.35. Structure of the four-elements arrayed Tx/Rx dual leaky-wave antenna1              | 05  |

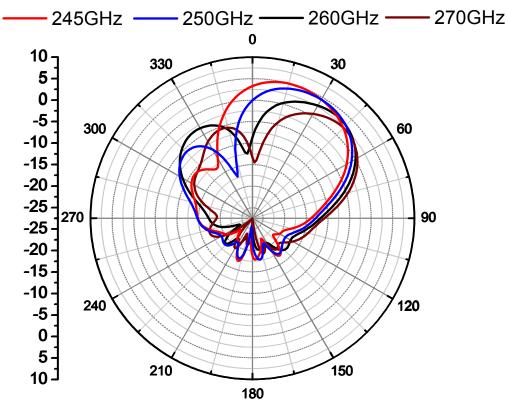

| 4.36. Simulated radiation pattern (Gain) of the designed half-width MLWA vs. frequency1  | 05  |

| 4.37. Simulated return loss of the designed half-width MLWA vs. frequency1               | 06  |

| 4.38. Microphotograph of the 0.26 THz CMOS wireless transceiver1                         | 06  |

| 4.39. Measurement setup for the EIRP of the transmitter1                                 | 07  |

| 4.40. Measured radiation pattern in H-plane at 0.246 THz1                                | 08  |

| 4.41. Measurement setup for the spectrum of the transmitter at fundamental frequency1    | 08  |

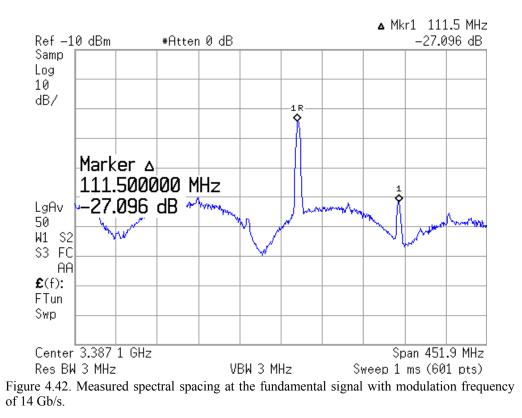

| 4.42. Measured spectral spacing for the fundamental signal with 14 Gb/s of modulation1   | 09  |

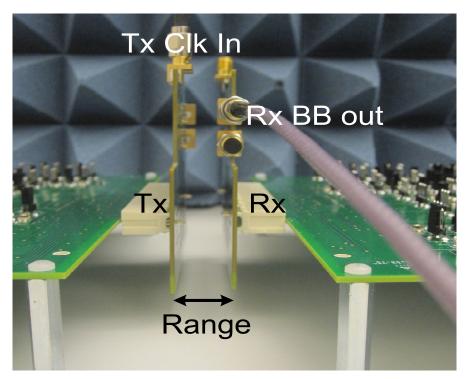

| 4.43. Test setup for the short range wireless communication link1                        | 09  |

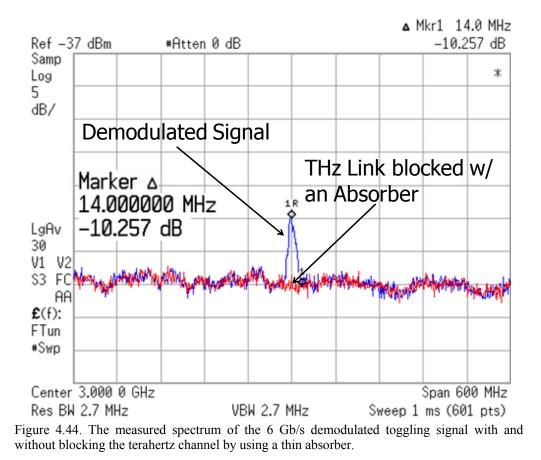

| 4.44. The measured spectrum of the 6 Gb/s demodulated toggling signal1                   | 10  |

# **List of Tables**

| 2.1. | Reported | on-chip | antennas | in | silicon | substrate. | <br> | <br> | 1 | 9 |

|------|----------|---------|----------|----|---------|------------|------|------|---|---|

|      |          |         |          |    |         |            |      |      |   |   |

#### Acknowledgements

This work would not have been possible without the help and influence of many wonderful and talented people. I would first like to express my sincerest gratitude to my advisor Prof. Ali M. Niknejad for his countless help and support. He has always been generous, attentive, available and supportive throughout all the peaks and valleys of my Ph.D. journey. My work in Berkeley has been constructed mainly inspired by his shining perspective, tireless enthusiasm, amazing engineering-intuition, and firm and solid knowledge. I would like to express my sincere thanks to Prof. Jan M. Rabaey and Prof. Paul K. Wright for serving on both my qualifying examination committee. I also thank to Prof. Ahmad Bahai for being a part of my qualifying examination committee. I am grateful for all the support and advice of Prof. Elad Alon throughout my research works during Ph.D. course.

My collaboration with Shinwon Kang and Siva V Thyagarajan in designing transceivers was particularly fruitful and enjoyable. Without their contribution, my journey might be more tough and lonely. Especially I am grateful for valuable technical discussions among us. I also give special thanks to Dr. Dick Plambeck for his encouragement and generous support of the terahertz instruments. I thank to seniors at BWRC who have provided so much insight and technical advice: Zhiming Deng, Amin Arbabian, Debopriyo Chowdhury, and Cristian Marcu, and thank to visiting researchers: Jay Wang, Dr. Vason Srini, Stefano Dal Toso, and Gyungtae Moon. I would like to give many thanks to my peer students: Lu Ye, Jiashu Chen, Jun-Chau Chien, Ashkan Borna, Mariam Tabesh, Lingkai Kong, Chintan Thakkar, Yue Lu, Ping-Chen Hwang, Paul Liu, Yida Duan, Han-Phuc Lee, and many BWRC colleagues for their help and technical discussion. I would like to express sincere thanks to Mrs. Ruth Gjerde in Cory Hall for her kindness, and encouragement to me. I am grateful to BWRC staff: Tom, Kevin, Brian, Bira, and Olivia for their kindness and consistency in assisting students.

Many Korean students helped me to keep going forward. I would like to give a special thanks to all the Korean circuit nerds: Ji-Hoon Park, Kyuhyun Noh, Namseog Kim, Kwangmo Jung, and Jaehwa Kwak. The Korean seniors Changhwan Shin, Kanghoon Jeon, Jemin Park gave me invaluable information and encouragement for me to adapt a new life in Berkeley. Many thanks to Min Hee Cho, Se Young Park, Jaeseok Jeon, Seonghwan Kim, Young-Ki Yoon, and Prof. Hyuck Choo for their help. I also give special thanks to Byeong-Gyu Nam and Dan An.

My journey became possible by encouragement, support, and recommendation of Prof. Jin-Koo Rhee who introduced me electronics, Prof. Jong-In Song who taught me research skills and attitudes, Prof. Hyun-Chang Park, Prof. Sam-Dong Kim, Prof. Chee Sun Won, Dr. Wan-Joo Kim, and the Late Prof. Un-Chul Paek who has been a role model as a great researcher and educator in his whole life.

Finally, I would like to express deepest gratitude to my parents for their love and endless support. Without their devotion and sacrifice, I could not be where I am today. I also express my sincere gratitude to my mother-in-law. I would like to special thanks to my truthful siblings, Young-Sun, Bong-Jin, and Ju-Ha for always being there for me. My academic journey must be something like walking though the dessert without my lovely sweeties: Juhyun who has always tried to find four leaf clovers in the village courtyard hoping for my graduation, Hyunjoong who has always shown happiest smile to me, and Seohyun who made our family live together here in Berkeley. Most special thanks have to go to my loving wife, Sunsook Moon who has sacrificed and devoted everything that she had for my academic journey in Berkeley.

# Chapter 1

# Introduction

Terahertz (THz) technology has gained high interests in various applications owing to its unique characteristics. Generally, the terahertz range is widely conceived as 0.3 THz to 3 THz whose wavelength ( $\lambda$ ) is between 1 mm to 0.1 mm, a transition region between electronics and photonics [Siegel02]. It has great potential in sensing and communication applications. Terahertz radiation can penetrate dielectric materials without causing any destructive ionization of the material. In the category of sensing applications, the terahertz imager can achieve much higher imaging resolution than millimeter-wave counterpart. Terahertz radiation has been widely used in spectroscopy by using the vibration of molecules for a given terahertz radiation frequency which can produce a unique fingerprint depending on type of dielectric materials. Biomedical spectroscopy [Wallace04] [Pickwell06] [Ajito09], and remote gas sensing [Oh09] are the promising examples of the application. Owing to extremely short wavelength, the terahertz compact range is useful for indoor millimeter-wave radar cross section (RCS) characterization of tanks and aircrafts [Danylov10]. The terahertz spectrum has great potential in ultrafast wireless communication by providing wide bandwidth in the new spectrum regime [Piesiewicz07] [Federici10]. In order to expand the use of the electromagnetic spectrum as such, designing highly efficient compact sources and detectors are essential. However there exist many challenges in achieving compact, reliable sources and detectors in this transition spectrum regime. Enormous research efforts have been directed to bridge this gap with different approaches from high-frequency electronics and photonics [Siegel02] [Tonouchi07] [Williams07].

Until recently fully integrated THz transceiver in silicon has not been considered a promising solution due to the limited device performance and the large propagation losses coupled through a resistive silicon substrate in terahertz range. However, we have witnessed revolutionary achievements in RF and millimeter-wave integrated circuit (IC) technology during last decade with advancement of the nano-scale silicon technology. Considering the impact of the RFICs in its compactness, low-cost, and mass production, the "THz-IC" will open a new era in imaging, sensing, spectroscopy, and ultrafast wireless communication. This thesis explores the realization of the fully integrated terahertz transceivers for sensing and communication applications in BiCMOS and digital CMOS technologies.

### **1.1 Terahertz Overview**

#### **1.1.1 Terahertz Regime**

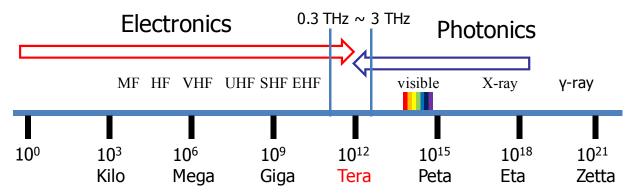

The terahertz range generally implies the unique frequency range which lies between the microwaves and infrared in the electromagnetic spectrum as presented in Fig. 1.1. Owing to this loosely defined range, slightly different frequency ranges are considered as terahertz regime in the literatures. Roughly, it ranges between 0.1 THz to 30 THz [Tonouchi07]. In some literatures of photonics society, it is conceived as 0.3 THz to 10 THz [Williams07] while microwave electronics society typically considers the terahertz range as 0.3 THz to 3 THz [Siegel02] which is synonymously termed submillimeter-wave range. In this thesis we mainly explore the lower frequency range of terahertz regime around 0.3 THz.

#### 1.1.2 Terahertz Gap

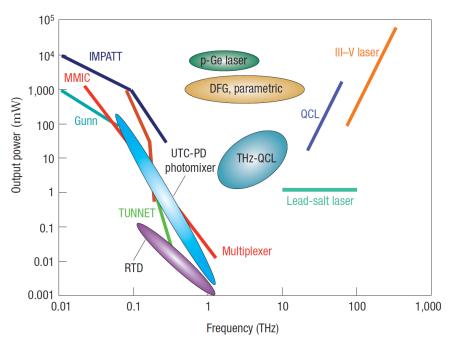

Placed in a unique position in the electromagnetic spectrum— a transition region between the realm of microwave electronics and photonics, terahertz-wave has unique characteristics in sensing and communication applications. However the technology has not been matured as much as microwave or optical technology. The terahertz radiation is limited to milliwatt range around 2 THz in photonics approach and it is around 0.1 milliwatt range around 0.5 THz in highfrequency electronics approach. While the wavelength of terahertz source limits a high photon energy generation (E=hv) from the photonics, the performance of the electronic THz source and detector is severely limited by active device performance from the approach of high-frequency electronics. Moreover, the measurement instrumentation at terahertz regime is scarce and expensive. When we approach the realization of terahertz source in electronics, the output power is limited by the active device performance  $(f_T / f_{max})$ . Owing to this reason, current status of THz technology for generating, detecting, and analyzing terahertz radiation is not as advanced as high-frequency electronics or infrared photonics. This technological barrier is generally conceived as the 'Terahertz gap' [Sigel02] [Huang08]. Fig. 1.2 shows the output power of the reported signal sources depending on operating frequency which clearly shows the lack of sources in submillimeter-wave range [Tonouchi07].

Figure 1.1. Unique terahertz region placed in a transition region between microwaves and infrared in the electromagnetic spectrum.

Figure 1.2. Reported THz-emission power output as a function of frequency: the terahertz-gap, the lack of strong and reliable THz sources, is evident in submillimeter-wave range [Tonouchi07] © Nature Photonics.

#### **1.1.3 Terahertz Source in Photonics**

Many research efforts have been directed to close this terahertz gap in photonics. Quantum cascade laser (QCL) has been considered one of the promising solid-state terahertz source with average optical power levels of much greater than a milliwatt since it was first developed in 1994 [Faist94]. Researchers have demonstrated THz-QCL below 2 THz. Monolithic integration of a terahertz QCL and diode mixer has been also demonstrated to form a terahertz photonic integrated circuit [Wanke10]. However, THz-QCLs are required to be cryogenically cooled whose operating temperature is proportional to operating frequency  $\omega$ .

$$T_{\max} = k \frac{\hbar \omega}{k_B} (\circ K) \tag{1.1}$$

where the proportionality constant  $k = 1 \sim 1.9$  for low frequency QCLs, and 2 mW of output power at 1.8 THz was achieved in  $T_{max}=155 \ ^{\circ}K$  [Kumar11]. From (1.1), the operating temperature of QCL at 1 THz scales only to 86  $^{\circ}K$ .

Uni-traveling carrier photodiode (UTC-PD) with low wavelength laser diode (LD) is another popular approach to generate terahertz signal around 0.3 THz. High quality terahertz waves can be generated by the photo-mixing of two different wavelength laser diodes which produces the optical beat frequency of the two LDs. The beat frequency is typically tunable upto 1.5 THz [Tounouchi07], and the reported output power of the UTC-PD module in 0.35 THz is around 0.5 mW [Wakatsuki08]. Using high-gain lens antennas, discrete PD, LD, and UTC-PD, a 0.3 THz wireless transceiver module has been reported with 12.5 Gb/s in ASK modulation scheme over 0.5 m link range [Song10].

#### **1.1.4 Terahertz Source in Electronics**

In microwave and solid-state circuit technology, there are many ways available to generate lower frequency range of the terahertz sources. With advancement of extremely high speed III-V compound semiconductor, a fundamental frequency oscillator is feasible in the lower terahertz range. Owing to the limited device performance of silicon devices, harmonics generated from nonlinear characteristics are used widely in (Bi) CMOS technology. Fundamentally the harmonic output power is limited to  $1/k^2$  for  $k^{th}$  harmonic component from a nonlinear resistive device [Page56]. Hence most of the harmonic oscillators and multiplier chains driven by mm-wave oscillator severely suffer from the lack of output power. To generate higher output power, the order of desired harmonic should be minimized which naturally requires high performance device.

#### **1.1.4.1 Active Device Performance**

For an electronic active device, the high-frequency performance is evaluated with two important figures of merit (FOMs), one is the current gain cut-off frequency ( $f_T$ ), and the other is the maximum oscillation frequency ( $f_{max}$ ) which is the highest frequency that an active device is capable of providing power gain. Therefore  $f_{max}$  represents a critical limitation of amplifier and fundamental-frequency oscillator designs for a given device.

As technology node scales down, the gate length of FET and base width of BJT shrink and these two FOMs improve. While  $f_T$  is mainly determined by intrinsic parameters of the device,  $f_{max}$  is a strong function of device layout as well as device  $f_T$ . Hence a careful layout is important to minimize external parasitics associated with routings and interconnections to achieve higher device  $f_{max}$ . The ratio  $f_{max}/f_T$  can be used to evaluate optimality of the layout [Heydari08]. The device FOMs,  $f_T$  and  $f_{max}$  for FET are given by [Gray04] [Lee05]

$$f_T^{FET} = \frac{g_m}{2\pi (C_{gs} + C_{gd})} \approx \frac{3}{2} \frac{\mu_n}{2\pi L_g^2} V_{ov}, \text{ or } \approx \frac{1}{L_g^a}$$

(1.2)

$$f_{\max}^{FET} \approx \frac{f_T^{FET}}{2} \sqrt{\frac{C_{gs} + C_{gd}}{r_g(g_{ds}(C_{gs} + C_{gd}) + g_m C_{gd})}}$$

(1.3)

The quantitative expressions for  $f_T$  and  $f_{max}$  of BJT are similar to those of FET as follows [Herkx97]

$$f_T^{BJT} = \frac{1}{2\pi} \left( \frac{g_m}{C_{je} + C_{\mu}} + \frac{1}{\tau_F} \right) = \frac{g_m}{2\pi (C_{\pi} + C_{\mu})} \approx \frac{\mu_n}{\pi W_B^2} V_T, \text{ or } \propto \frac{1}{W_B^b}$$

(1.4)

$$f_{\max}^{BJT} \approx \sqrt{\frac{f_T^{BJT}}{8\pi r_b C_{\mu}}}$$

(1.5)

where a, and b denote scaling factors of gate length and emitter width, respectively.

5

With crude estimations using the quadratic equation of FET and the diffusion equation of HBT for  $\tau_F$ , we see the  $f_T$  improves quadratically with device scale-down. In advanced silicon technology, the performance improves almost linearly with the scale-down due to secondary effects like carrier velocity saturation. From (1.3) and (1.5), the Miller parasitics between gate-drain or base-collector ( $C_{gd}$ ,  $C_{\mu}$ ) and the loss at gate or base ( $r_g$ ,  $r_b$ ) mainly affect on the available power gain as well as noise factor of the device.

While  $f_{max}$  is the FOM for the power gain of an amplifier and fundamental oscillation,  $f_T$  is directly related to the minimum noise factor  $F_{min}$  given by [Fukui79]

$$F_{\min} \approx 1 + k_f \frac{f}{f_T} \sqrt{g_m (r_g + r_s)}$$

(1.6)

where  $k_f$  is Fukui's empirical noise factor coefficient which is close to 2 [Fukui79], and can be physically described as  $k_f = 2\sqrt{\gamma_{gm}}$  with  $\gamma_{gm}$  is the  $g_m$  referenced excess noise factor [Cui07]. As technology node move forward,  $F_{\min}$  improves with increased  $g_m$  from the scaling-down of gate length ( $L_g$ ) and oxide thickness ( $t_{ox}$ ), but it is negatively impacted by increased parasitic components (*i.e.*  $C_{gs}$ ,  $r_g$ ) from the higher fringe capacitances and resistances due to the tighter pitch size.

The FOMs,  $f_T$  and  $f_{max}$  of a device are estimated by measuring 2-port S-parameters of common source (emitter) device using the vector network analyzer. The magnitude of current gain  $|h_{21}|$  is extracted given by

$$\left|h_{21}\right| = \frac{-2S_{21}}{(1-S_{11})(1+S_{22}) + S_{12}S_{21}}$$

(1.7)

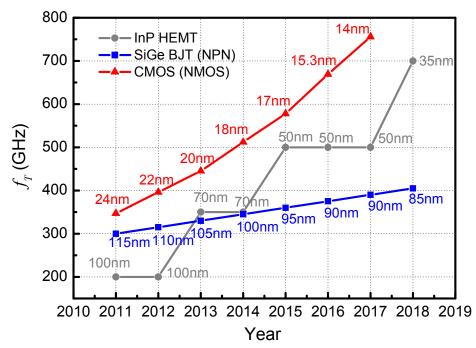

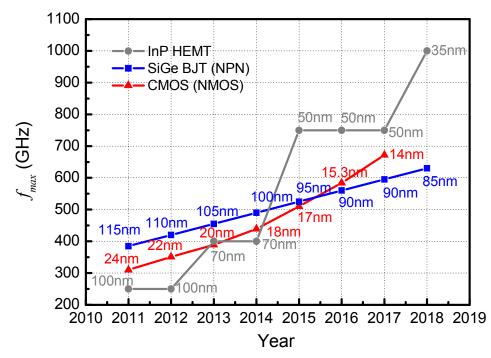

Fig. 1.3 and Fig. 1.4 present  $f_T$  and  $f_{max}$  of NMOS, SiGe HBT, and InP HEMT devices in the 2011 International Technology Roadmap for Semiconductors (ITRS) [ITRS2011]. Here  $f_T$  and  $f_{max}$  were determined by peak  $f_T$  measured from  $|h_{21}|$ , and unilateral gain U extrapolated from 40 GHz with a 20 dB/dec slope, respectively. The scaling factor a of NMOS is close to 1.5, and b of SiGe BJT is about 1 from the trend reported in the roadmap as shown in the figure.

In terms of manufacturability, the required  $f_T$  and  $f_{max}$  of the CMOS technology of the roadmap look quite challenging. In the 2011 ITRS report, CMOS with 24 nm of the gate-length  $(L_g)$  has been reported to have optimized manufacturable solutions yet. Up until 18 nm CMOS, manufacturable solutions are known which has  $f_T$ =512 GHz, and  $f_{max}$ =439 GHz.

Another challenge in using CMOS in extremely high-frequency applications is that the intrinsic gain  $g_m/g_{ds}$  of the CMOS decreases with scale-down. From the 250 nm to the 45 nm node, the intrinsic voltage gain  $g_m/g_{ds}$  has decreased from 15 to 5 due to an increased  $g_{ds}$ . If this trend continues, extrapolation for 10 nm technology leads to an intrinsic gain close to unity. In this case, it would not be possible to design any useful RF amplifier. Another difficulty arises from a fabrication of thin oxide layer. In order to obtain channel control over the gate, an oxide thickness  $t_{ox}$  of around 1 nm is required for the 10 nm node. Further reduction of  $t_{ox}$  less than 1 nm is difficult considering gate leakage, flicker noise, and process variation. As process node moves forward, total height of the inter-metal dielectric (IMD) layers also scales down which increases the influence of the substrate losses on the propagation for thinner IMD layers. Hence the attenuation the transmission-line increases and the radiation efficiency of the on-chip antennas are severely degraded which is briefly discussed in Chapter 2.

Figure 1.3. Current gain cut-off frequency ( $f_T$ ) of NMOS, SiGe HBT, and InP HEMT in ITRS 2011 [ITRS2011].

Figure 1.4. Maximum oscillation frequency ( $f_{max}$ ) of NMOS, SiGe HBT, and InP HEMT in ITRS 2011 [ITRS2011].

Contrary to CMOS technology which approaches the physical limitation of the technology, SiGe BJT and InP HEMT processes still have a room for better performance in the lower terahertz range owing to the superior material characteristics. For SiGe BiCMOS technology interim solutions are already known by 85 nm SiGe NPN BJT, and its  $f_T$  is equal to 405 GHz, and  $f_{max}$  is 630 GHz in the 2011 ITRS report. Regarding InP HEMT, one of the promising III-V compound semiconductor, the optimized manufacturable solution already exists up until  $L_g$ =50 nm of gate-length which achieves  $f_T$ =465 GHz, and  $f_{max}$ =1060 GHz [Kim10]. Recently a 30 nm InP HEMT having  $f_T$ =600 GHz and  $f_{max}$ =1200 GHz has been used to demonstrate amplifiers, mixers, and multipliers operating at 670 GHz [Deal11].

However, the advantage of using silicon technology is clear when we consider the fully integrated system with analog and logic circuits for base band and Digital Signal Processor (DSP) even though high frequency performance of the CMOS and SiGe device is distinctively inferior to the III-V compound devices. Fig. 1.5 shows Scanning Electron Microscope (SEM) microphotographs of the crosssections of 45 nm NMOS [Auth08], 0.13 µm SiGe BJT [Chevalier05], and 30 nm InP HEMT [Deal11]. As can be shown, silicon processes have multiple metal layers for complex interconnection which requires 40 to 50 mask layers which make it possible to integrate analog circuits as well as logic blocks. Moreover cost–effective mass production with high yield is possible owing to massive infrastructure in silicon industry as well as reliable material properties of silicon compared with III-V compound semiconductors. Hence THz-SOC in silicon is very promising in the applications for sensing and communication which requires intensive analog interface and digital logic for signal processing on chip for the cost-effective massive production.

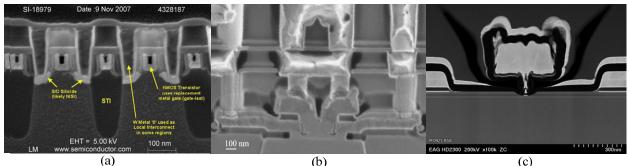

Figure 1.5. SEM microphotographs of the cross-sections of (a) 45 nm CMOS [Auth08] ©Intel 2008, (b) 0.13 $\mu$ m SiGe [Chevalier06], © IEEE 2005, and 30 nm InP HEMT [Deal11] © IEEE 2011.

## **1.1.4.2** Terahertz Circuits beyond $f_T$ and $f_{max}$

In order to achieve an amplifier with moderate gain and noise performance,  $f_T$  and  $f_{max}$  of the used device should be roughly 2~3 times higher than the operating frequency. This is same for an oscillator design to achieve moderate output power and phase noise. Contrary to designing amplifiers and oscillators, mixer and multipliers are not limited by device  $f_{max}$ . Mixers and multipliers can be implementable with any devices exhibiting nonlinear performance. Hence the active device with lower  $f_T$  and  $f_{max}$  can be still used as a nonlinear passive device which provides rectification with junction diodes in the device though we can not achieve conversion gain with that device. Using a schottky diode in designing mixer and multiplier is also possible

choice in THz range, and possible to implement sub-millimeter-wave diodes in CMOS without any extra processes [Sankaran05].

Among many ways of generating terahertz signal in high frequency electronics, the *N*-push  $N^{th}$  harmonic generator has been widely used in harmonic oscillators [Tang01] [Baeyens03] [Cao06] [Sinnesbichler06] [Cao06] [Seok08], multipliers, and mixers [Huang08] [Park11]. Basically the *N*-push harmonic generator utilizes *N* number of coupled clamping devices in parallel driven by 0 to  $2\pi \cdot (N-I)/N$  phase-shifted fundamental signals. The advantage of this structure is that it can generate the combined output power at  $N^{th}$  even harmonic frequency without any bulky and lossy fundamental signal rejection filter as odd harmonics cancel out owing to the push-push structure. The detailed analysis of *N*-push harmonic generator is covered in Chapter 3.

Theoretically it has been reported that a short FET has resonance response to electromagnetic radiation at the plasma oscillation frequencies of the two dimensional electrons in the device. This response can be used for detectors, mixers, and multipliers. These devices should operate at much higher frequencies than conventional, transit-time limited devices (FET) since the plasma waves propagate much faster than drift velocities [Dyakonov96M]. In order for this plasma wave mixing happen, the critical frequency of oscillation is extremely high; 7.7 THz for silicon and 3.5 THz for GaAs in 300 °K [Dyakonov96O]. In non-resonant limit where  $\omega_0 \tau < 1$ , it can be considered as the distributed RC network from the nature of the channel of FET [Lisauskas09], a small portion of the channel serves in rectification, and rest of the channel merely serves as a gate-drain capacitance which provides coupling path for self-mixing [Ojefors09]. Owing to the distributed nature of the NMOS channel, 0.3 THz and 1 THz imager in 130 nm CMOS [Schuster11] and, 0.9 THz imager in 65nm digital CMOS technology has been reported with [Sherry12].

#### 1.1.4.3 Terahertz Circuit Design Methodology

In designing circuits at terahertz region, the inductor size should be controlled in pH scale, and the device size is limited by the matching network accuracy and the modeling of the complex interconnection structures with several vias. Distributed matching network with open and short stubs are appealing as values are relatively precisely controllable with transmission-line length.

Dealing with active devices is quite complicated. Even a simple on-wafer s-parameter measurement is not easy due to measurement inaccuracy from extremely small size RF pad, and on-tip calibration errors from "Reflection" reference. Detailed on-wafer measurement procedure and at terahertz region are elsewhere [Samoska11] [Fung12]. Hence the modeling of active device is quite challenging as its measurement error is larger than required accuracy. With advancement of the full-wave 3-D electromagnetic (EM) simulation, we can rely highly on 3-D EM simulation based modeling for the extrinsic parasitic [Liang09]. Considering the total thickness of the inter-metal layers (IMDs) are close to 10  $\mu$ m, all distributed inductances and capacitances from the interconnection via structures should be considered precisely as well. Two transceivers presented in this thesis utilize harmonic components in generating and down-converting the terahertz signals. All the terahertz circuits are designed with intensive 3-D EM simulations for all structures including vias from top metal to M1.

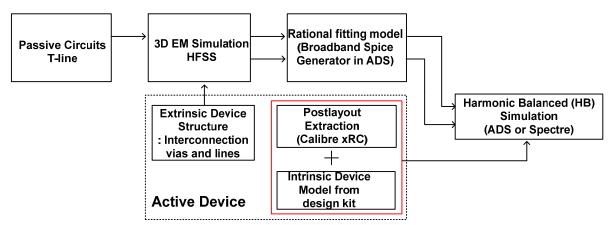

Figure 1.6. Flow chart of the terahertz circuit design in CAD case.

By using Broadband Spice Model Generator in ADS<sup>TM</sup>, rational fitting models are generated from the extracted S-parameters. Only for small size core active devices without including any metal interconnections, we rely on the post-layout extraction using Calibre xRC<sup>TM</sup> with intrinsic transistor models provided by design kit. For millimeter-wave amplifiers for driving LO, and amplifying IF signals, the simulation based active device modeling is more relied on the post-layout extraction with a reasonable size of inter-metal connections. However, still all the thick metal layers and related vias are simulated in HFSS<sup>TM</sup>. In order to achieve robust design from process variation and modeling inaccuracy, wide-band matching networks are designed by using transformer coupled architecture [Simburger99] [Aoki02] [Galbraith07].

#### 1.1.4.4 Silicon Passive Elements in Terahertz

At the terahertz regime the reactive elements for matching networks and resonators become extremely small, and the required inductance is only around 5 to 50 pH even in the lower range of the terahertz region. Considering such a small inductance required for the matching networks, distributed matching network with open and shunt stubs in transmission-line is ideal as transmission lines are inherently scalable in length and are capable of realizing precise values of small reactance. Like millimeter-wave silicon integrated circuits, the coplanar waveguide (CPW) [Wen69], and the microstrip-line (MSTL) [Wheeler65] can be used as the transmission-line in the lower frequency range of the terahertz. For the propagation of the balanced signals which are widely required for push-push architecture, the coplanar strip-line (CPS) can be used providing better signal integrity with a comparable propagation loss compared to CPW and MSTL [Gevorgian01]. A T-line with the quasi-transverse electromagnetic (Quai-TEM) mode can be characterized with the characteristic impedance  $Z_0$  and the propagation constant  $\gamma = \alpha + j\beta$ . The quality factor  $Q = \beta/(2\alpha)$  can be used as a figure-of-merit (FOM) for a given transmission line. As wavelength of the propagating terahertz signal is smaller than 1 mm in air and less than 0.5 mm in the transmission-line of the silicon IC, three dimensional structure of the T-line should be thoroughly considered with 3-D electromagnetic simulation as the dispersion effect and fringing fields from the thick metal layer affect on the transmission-line characteristics ( $Z_0$  and  $\gamma$ ). Analysis and design of CPW, MSTL, and CPS is elsewhere in the literatures [Gupta96] [Simons01]. A design example of the CPS in 0.13 µm SiGe BiCMOS is given in Chapter 3.

# **1.2 Terahertz Applications**

#### 1.2.1 Terahertz Sensing

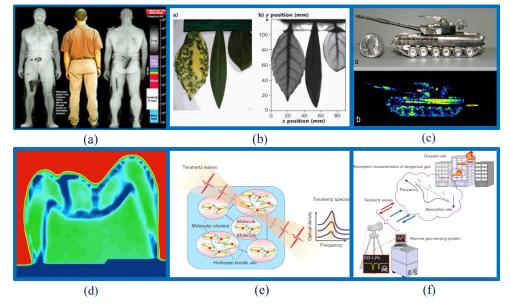

Historically terahertz imaging and spectroscopy have been attractive applications. Because of their shorter wavelength compared with imaging in the gigahertz band, terahertz wave offers better spatial resolution in imaging. Owing to the spectral absorption features, terahertz spectroscopy [Wallace04] [Pickwell06] can be used in agriculture and food products, security in detecting concealed objects and dangerous substances, cancer detection, DNA binding state for label-free analysis, and space instrumentation. Imaging mechanism in terahertz waves have fundamental differences from X-ray imaging in that they are nondestructive as photon energy is low enough that it does not ionize the material under the illumination. In spectroscopy, terahertz radiation can be used to identify specific materials by using the vibration of molecules. In particular, the 1–3 THz band corresponds to the oscillations of hydrogen bonds and other forces between molecules [Ajito09]. This is promising for identifying toxic or explosive substances and also has applications in the spectral analysis of macromolecules such as proteins. Similar to molecular spectroscopy, terahertz remote gas sensing is another spectroscopy application as many gases have characteristic absorption lines in this frequency range [Oh09]. Terahertz compact range is also appealing area in radar engineering. The radar cross section (RCS) of the huge structure at millimeter-wave range can be scaled to small structural model and can be illuminated under the terahertz radiation to estimate the RCS of the large structure at millimeterwave range [Coulombe99] [Danylov10]. Hence cost effective indoor measurement is possible to characterize aircrafts or ships using the terahertz compact range. While terahertz sensing applications require relatively high terahertz frequency range from 0.5 THz to 2 THz, the required bandwidth of the intermediate frequency (IF) is guite narrow less than several MHz.

Figure 1.7. Application examples of terahertz sensing: (a) Security imaging, (b) Agricultural imaging for water content measurement [Schuster11] © IEEE 2011, (c) Compact range [Danylov10] ©SPIE 2010, (d) Medical diagnostic, (e) Molecular spectroscopy [Ajito09] © NTT, (f) Remote gas sensing [Oh09] © IEEE 2009.

#### **1.2.2 Terahertz Short Range Communication**

During past four decades of advancement of integrated circuits, we have witnessed that the computing power doubles every eighteen months. This trend exactly applies to wireless communication power which increases two folds every eighteen months. It can be predicted that data rates of around 5–10 Gb/s will be required in ten years according to the "Edholm's law of Bandwidth" [Cherry04]. Because the spectrum bandwidth of the signal is mostly limited by the carrier frequency, we need to expand the use of the electromagnetic spectrum to terahertz range.

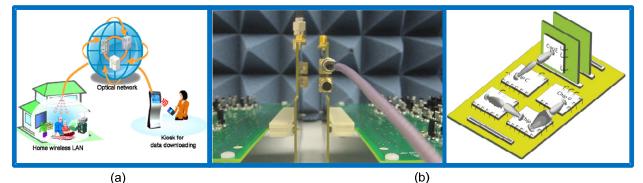

Various applications with ultra-fast wireless THz communication are possible in similar ways to current WLNA and WPAN: wireless extensions of broadband access fiber optical networks, ultrafast uploading and downloading of large files to and from a server, campus/auditorium deployments, indoor wireless transmission for the ultra-high definition television, and security communication with virtue of high propagation loss are some of the typical application of terahertz communication [Federici10]. Recently many research groups are exploring the terahertz communication using photonics approach. Using high-gain lens antennas, discrete laser diode (LD), and UTC-PD, more than 10 Gb/s data-link with ASK modulation over 0.5 m link range have been reported at 0.3 THz [Song10].

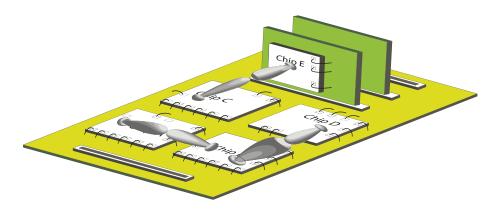

Different from the sensing application, the terahertz communication transceiver has to achieve broadband modulation and demodulation. Moreover the silicon based active device has extremely limited high frequency performance compared with III-V compound semiconductor. Hence the silicon terahertz wireless transceiver should be approached from system level design. Considering limited device performance in silicon technology, a feasible data-link range must be very limited to several centimeters. We propose terahertz wireless chip to chip communication which requires low latency, high data rate, and reasonable power consumption. The first prototype is demonstrated with spatially combined multiple chain transceiver in a 65 nm digital CMOS technology in Chapter 4. Compared with the inductive-coupling inter-chip link which requires the link range less than 0.1 mm with a precision alignment of chips over the dielectric layers, the ultrafast terahertz wireless link is very attractive in wireless chip to chip inter-connection.

Figure 1.8. Application examples of terahertz communication: (a) Indoor wirless LAN connecting with fiber optical network [Song10]  $\bigcirc$  IEEE 2010, (b) Wireless communication for chip to chip communication.

### **1.3 Atmospheric Attenuation in Terahertz**

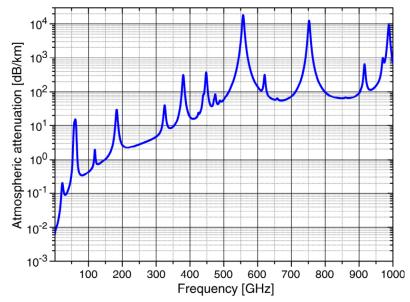

The attenuation of the THz signals in atmosphere is very high compared with lower frequency range owing to the oscillations of atmospheric gas and water molecules initiated by the electromagnetic waves. Therefore the amount of the attenuation strongly depends on the resonance frequency of the atmospheric molecules. It is clear that the terahertz transceiver for sensors and communication needs to operate at a frequency near an atmospheric window where absorption to due to water vapor is a minimum. These windows are nominally centered near 94, 140, 250, 350, 410, 500, 650, 850, 1035, 1350, and 1500 GHz. With the ITU-R [ITU09] and *am* models [Scott12] the specific attenuation of the atmosphere at frequency up to 1000 GHz due to dry air and water vapor can be quantitatively estimated depending on specific pressure, humidity, and temperature. Fig. 1.8 presents the attenuation of atmosphere at sea level for typical values of temperature and water vapor density. As shown, there exists two attenuation peaks at 557 GHz and 752 GHz which has atmospheric attenuation larger than 10<sup>4</sup> dB/km which must be avoided for sensing and communication applications. The atmospheric attenuation is around 2 dB/km at 260 GHz, and 10 dB/km at 360 GHz.

Rain and fog also cause additional attenuation in THz range. Attenuation due to fog increases with density of fog and the propagation frequency. Regarding the attenuation caused by fog additional attenuation is about 7~9 dB/km between 260 GHz and 360 GHz for the vision range 50 m (0.5 g/m<sup>3</sup>). In rainy atmosphere, terahertz wave experiences a Mie-scattering which results in high attenuation as the size of the rain droplets are similar to the wavelength of the terahertz wave. Additional attenuation caused by 50 mm/h of rain is around 19 dB/km between 260 GHz and 360 GHz. However the atmospheric attenuation in frequency window is negligible for indoor short range sensing and communication applications as the atmospheric attenuation is expected to be less than 0.1 dB in 10 m range.

Figure 1.9. Specific attenuation of the earth's atmosphere at sea level in the frequency range between 1 and 1000 GHz for an air pressure of 1013 hPa, a temperature of 15 °C and a water vapor density of 7.5 g/m [Schneider12], © IEEE 2012.

### **1.4 Thesis Outline**

Under the limited  $f_T$  and  $f_{max}$  of the silicon device which are even lower than THz transceiver operating frequency, it is unavoidable to utilize harmonics from the device nonlinearity which impinges on several issues such as low output power, low conversion efficiency, filtering, and modeling accuracy in the circuit design and integration. Therefore it becomes critical to research on high gain on-chip antennas with improved radiation efficiency, the harmonic generator with better conversion efficiency and filtering structure, and the optimal terahertz transceiver architectures for silicon technology to achieve desirable system requirement. This thesis explores two innovative THz transceivers for sensing and communication applications. As a terahertz transceiver for sensing application, a fully integrated 0.38 THz FMCW radar sensor has been designed and implemented in 0.13 µm BiCMOS having  $f_T$ =0.23 THz [Park11]. As the second design example, a 0.26 THz wireless transceiver for wireless chip-to-chip communication is presented in 65 nm digital CMOS having  $f_T$ =0.16 THz [Park12]. In order to realize the terahertz transceiver for sensing and communication, this thesis covers on-chip antennas, harmonic generators, frequency multipliers, mixers, and millimeter-wave fundamental signal generation circuits, and front-end architectures.

In Chapter 2, we explore various types of on-chip antennas in BiCMOS and CMOS technology. Radiation efficiency and loss mechanisms of the on-chip dipole/slot antennas and microstrip structure antennas are studied for the advanced silicon technologies which have thin IMD multi-layers and lossy silicon substrate. Design and analysis of 100 GHz folded slot antenna with meandered stub, 0.36 THz microstrip rectangular patch antenna, and 0.26 THz half-width microstrip leaky-wave antenna are briefly discussed.

In Chapter 3, we present a 0.38 THz fully integrated FMCW radar transceiver. The coplanarstripline (CPS) and the transformer coupled architecture have been widely used with *N*-push clamping harmonic generators to achieve efficient fundamental signal rejection. The clamping circuit is analyzed with a simplified BJT model for an optimal efficiency. Designs of terahertz and millimeter-wave circuits are briefly presented, followed by measurement results of the ranging and detection of the target.

In Chapter 4, a 0.26 THz non-coherent On-Off Keying (OOK) transceiver is presented to explore the feasibility of the terahertz wireless chip to chip communication. In order to overcome the inferior performance of the 65 nm CMOS in THz regime, the transceiver consists of spatially combined two unit-transmitters and unit-receivers which make it robust to the possible Rician fading channel in the size constrained box. System level design is presented with budget analysis for different types of modulation schemes for different range and receiver noise figure conditions. Tx/Rx dual on-chip antennas are implemented with half-width microstrip leaky-wave antenna (MLWA) while obviating the need for an explicit TR switch. Detailed designs of terahertz and millimeter-wave circuits are discussed with measurement results of Tx chip to Rx chip signal transfer.

Finally, a summary of this thesis and future directions are presented in Chapter 5.

# Chapter 2

# **On-chip Antennas in (Bi) CMOS Technology**

### 2.1 Introduction

On-chip integrated antenna in silicon technology is promising as radiating frequency approaches the terahertz range. On-chip antenna could be even more cost-effective than a conventional packaging of an external antenna with transceivers considering packaging cost and its compactness at terahertz range. The area consumption of an on-chip antenna with moderate antenna gain can be comparable to an RF pad size when appropriate type of antenna is chosen depending on the radiation frequency. Moreover, fully integrated on-chip antenna in a single chip provides extra design flexibilities by co-designing antenna with transceivers which can achieve broader space coverage, wide-band, and better beam shaping characteristics. The main issue of on-chip antenna in silicon is that the radiation efficiency is severely low [Shamim05] [O05].

Up until 60 GHz range, the size of the on-chip antenna is bulky, and the packaging technology is well matured. Therefore the transceiver with an external antenna having high radiation efficiency is more reasonable choice. Since antenna size is quadratic function of the wavelength of the radiation signal for a given antenna gain, the on-chip antenna has great potential as frequency increases. As radiation frequency approaches terahertz range, the insertion loss and cost from the packaging overwhelms disadvantage of on-chip silicon antenna such as low radiation efficiency, low antenna gain, and bulky size.

In this chapter we investigate several types of on-chip antennas suitable for advanced (Bi) CMOS technology in 100 GHz to 360 GHz range. Firstly we study on the effects of the lossy silicon as an antenna substrate, and secondly we investigate the effects of the thin dielectric layers in BEOL as the antenna substrate in microstrip structure antennas. We design a 100 GHz folded slot antenna with CPW feed and a 360 GHz microstrip rectangular patch antenna with inset. Finally, a 260 GHz half-width microstrip leaky-wave antenna design is discussed, followed by conclusion.

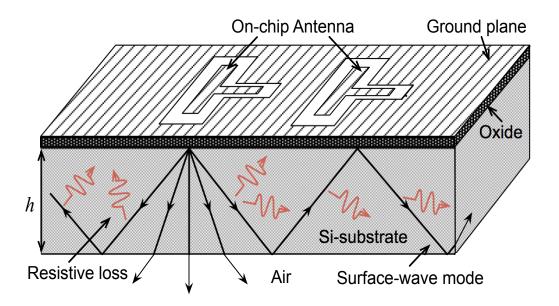

Figure 2.1. Two main loss mechanisms of the on-chip antenna in a lossy silicon substrate.

## 2.2 Loss Mechanism in On-chip Antenna in Silicon

Low radiation efficiency of the on-chip antenna in silicon technology is mainly from the silicon substrate with low resistivity, and high permittivity ( $\varepsilon_r$ =11.8), which are undesirable characteristics used for antenna substrate. When we use the silicon substrate of a conventional digital CMOS technology as an antenna substrate, there exists two main loss mechanisms as presented in Fig. 2.1. One is the conduction loss owing to the low resistivity of the silicon substrate, and another is the surface-wave mode excitation caused by the thick silicon substrate with a high permittivity [Pozar83]. Those two loss mechanism can be avoided if we can isolate the radiation signal from the lossy silicon substrate. However, there exists another loss mechanism. When we use the dielectric layers of the back end of line (BEOL) process as an antenna substrate, *e.g.* microstrip patch or microstrip leaky-wave antenna, the very thin dielectric layer compared with  $\lambda_0$  results in larger conduction loss in the metal trace. Moreover, the thin dielectric substrate makes it difficult to radiate energy to the space.

#### 2.2.1 Loss from Low Resistive Silicon Substrate

A digital CMOS process uses a low resistive silicon substrate (~ 10  $\Omega$ -cm) to prevent the latchup of the circuits [Gray04]. In order to mitigate the effect of low resistivity, high resistive (HR) substrate has been investigated [Montusclat06] [Barakat07]. SOI substrate is a good example of the HR substrate which makes it possible to achieve a fully integrated transceiver with on-chip antenna having relatively high radiation efficiency. However the SOI substrate is not a cost effective choice for an on-chip antenna. One interesting way to get a HR substrate using a low resistive silicon substrate is proton implantation method using cyclotron ion source [Chan03].

Figure 2.2. Reported on-chip antennas by reducing resistive loss with (a) Proton Implantation Method [Chan03] © IEEE 2003, (b) MEMS antenna with dielectric membrane [Aziz03] © IEEE 2003, (c) MEMS antenna with 'air' substrate [Pan06] © IEEE 2006.

However, this method could cause damage to the semiconductor active layers. Another approach to achieve high radiation efficiency is to use MEMS technology. Using MEMS technology, a lossy silicon substrate is substituted with a dielectric membrane to mitigate both conductive loss and surface-wave mode excitation [Aziz03]. One exotic example using MEMS technology is a patch antenna with air substrate which achieves radiation efficiency of 94 percent [Pan06]. However, MEMS technology requires various extra processes other than a conventional CMOS technology which prohibits full integration on chip with CMOS ICs. Moreover, the structural robustness is usually sacrificed with the improved radiation efficiency. Fig. 2.2 shows the reported on-chip antennas in silicon aiming at mitigating the substrate conduction loss.

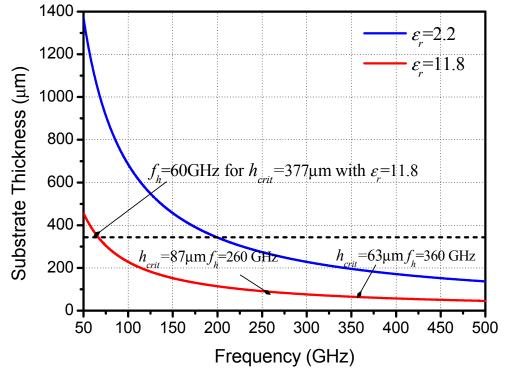

#### 2.2.2 Surface-wave Mode Excitation on Silicon Substrate

As an active antenna have a wide ground plate with active circuits, the silicon substrate with high permittivity ( $\varepsilon_r$ =11.8) can be considered as a dielectric slab waveguide mirrored with ground plane at one side (Fig. 2.1). Because of the bouncing of the E-field between the edge of the slab and metal plate, the dominant mode that can be excited in this slab is TM<sub>0</sub> which has zero cut-off frequency. Therefore, resistive loss caused by the highly conductive substrate is unavoidable. To reduce the resistive loss in a digital CMOS process, the lossy silicon substrate must be thin enough to tolerate the loss. When the substrate is thick enough to excite higher order mode, the surface-wave mode becomes another loss mechanism. From the cut-off frequency of higher modes of the dielectric slab waveguide with metal plate, the critical thickness ( $h_c$ ) that starts to excite the first higher order mode (TE<sub>1</sub>) is given by [Balanis89]

$$h_c = \frac{c}{4f_h \sqrt{\varepsilon_r - 1}} \tag{2.1}$$

where *c* is the speed of light,  $f_h$  is the highest operating frequency of the antenna, and  $\varepsilon_r=11.8$  for silicon substrate. Parts of the excited surface-wave mode energy are dissipated as a heat, and rest radiates through the edge of the substrate that increases side-lobes. As the silicon substrate gets thicker, the E-field is confined to the high dielectric substrate which produces asymmetric antenna radiation pattern and it worsen radiation efficiency. Fig. 2.3 shows critical substrate thickness as a function of operating frequency. Considering the general thickness of the substrate

is around 380  $\mu$ m without special die-thinning, an extra wafer-thinning process is necessary to achieve reasonable radiation efficiency for whole terahertz frequency range. Comparing with one of the most commonly used antenna substrate RT/duroid 5880 ( $\varepsilon_r$ =2.2), the critical thickness of the silicon substrate should be 1/3 of that for RT/duroid 5880.

In order to mitigate the surface-wave excitation, substrate dielectric lens is widely used in millimeter-wave applications where the substrate is thick enough to cause multimode surface-wave excitation [Raman96] [Babakhani06] [Shireen07]. The dielectric lens confines the electric field which prohibits surface-wave excitation. Moreover it can achieve much higher gain of antenna by confining field to a certain direction. The main disadvantage of using a dielectric lens is large lens size as well as process difficulty in its fabrication. In order to improve the fabrication difficulty for the substrate lens, a superstrate dielectric layer over the on-chip antenna has been reported [Bahl82] [Ahamdi07]. Another type of antenna which avoids the surface-wave excitation is a dielectric resonator antenna [Bijumon07]. For this type of antenna, most of the electric fields are confined within a high dielectric resonator that the conduction loss is mitigated. However, this type of antenna has critical limitation in fabrication as it requires an extra-post process and a precise alignment of the dielectric resonator. Moreover those reported methods require bulky structure which contradicts with aim of using an integrated on-chip antenna. Fig. 2.4 shows the reported on-chip antennas in silicon aiming at mitigating the surface-wave mode excitation.

Figure 2.3. Critical substrate thickness  $(h_c)$  as a function of the radiation frequency depending on substrate permittivity.

Figure 2.4. Reported on-chip antennas by suppressing surface-wave excitation mode with (a) Dielectric (Si) lens on top of the silicon on-chip antenna [Shireen07] © IEEE 2007, (b) On-chip antenna with superstrate dielectric layer [Ahamdi07] © IEEE 2007, (c) Dielectric resonator antenna [Bijumon07] © IEEE 2007.

# 2.3 Wafer-thinning Approach for Dipole and Slot Antennas

#### 2.3.1 Antenna Radiation Efficiency

The input impedance of an antenna is computed from  $Z_{in}=V/I(0)=R_A+jX_A$ , where I(0) is the current value at the input terminals. In terms of resistances, antenna radiation efficiency can be expressed as [Lee97]

$$e_{rad} = \frac{P_{sp}}{P_{in}} = \frac{P_{sp}}{P_{sp} + P_{sw} + P_c + P_d} = \frac{1/Q_{sp}}{1/Q_{sp} + 1/Q_{sw} + 1/Q_c + 1/Q_d}$$

(2.2)

where  $P_{in}$  is the antenna input power,  $P_{sp}$  is the space-wave radiated power,  $Q_{sp}$  is the quality factor for  $P_{sp}$ ,  $P_{sw}$  is the excited surface-wave power, and  $Q_{sw}$  is the quality factor for that,  $P_c$  is the conduction loss in metal trace and  $Q_c$  is its quality factor, and  $P_d$  is power dissipation from dielectric loss tangent, and  $Q_d$  is the quality factor for that. We substitute the power dissipation in terms of equivalent resistance ratio.

$$e_{rad} = \frac{R_{rr}}{R_A} \approx \frac{R_{rr}}{R_{rs} + R_{rr} + R_{ohm}}$$

(2.3)

where  $R_A = R_{rs} + R_{rr} + R_{ohm}$  is real part of antenna input impedance, and  $R_{rr}$  is radiation resonant resistance since  $R_{rs}$ , and  $R_{rr}$  are directly proportional to the power coupled into the substrate as guided modes and to the power radiated in space, respectively [Alexopoulos83]. In order to improve radiation efficiency, both  $R_{ohm}$  and  $R_{rs}$  have to be minimized. Based on this expression, high resistive (HR) silicon substrate technology is categorized to the group of reducing  $R_{ohm}$ , and substrate/superstrate dielectric lens technology belongs to the group of reducing  $R_{rs}$ . The MEMS technology and wafer-thinning technology reduces both  $R_{ohm}$  and  $R_{rs}$ . Therefore wafer-thinning approach could be a good candidate for the on-chip antenna on a lossy silicon substrate without modifying antenna structures. Table 2.1 summarizes several different approaches to improve the radiation efficiency. It should be noticed that the radiation frequency is the design criteria in making decision for the feasibility of on-chip antenna.

|                 |                                 |                                                                                 | Advantages                                                                                                                                               | Disadvantages                                                                                                   |

|-----------------|---------------------------------|---------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|

| Native Antennas |                                 | - Low cost / Easy fabrication<br>- Best for full integration<br>-Wafer-thinning | <ul> <li>Low radiation efficiency</li> <li>Limited antenna gain</li> <li>Main-lobe distortion due to<br/>surface-wave modes</li> </ul>                   |                                                                                                                 |

| 5               | HR substrate                    | (a)                                                                             | <ul> <li>Very good for full integration</li> <li>Moderate radiation efficiency</li> </ul>                                                                | - SOI substrate<br>- Mainlobe distortion                                                                        |

| Antennas        | MEMS                            | (a), (b)                                                                        | - High radiation efficiency                                                                                                                              | - Bad structural robustness<br>- Bad for full integration                                                       |

| Modified An     | Substrate<br>Dielectric Lens    | (b)                                                                             | <ul> <li>Widely used in mmW</li> <li>Applicable to various types<br/>of antennas</li> <li>High directivity</li> <li>High radiation efficiency</li> </ul> | <ul> <li>High cost</li> <li>Large lens size</li> <li>Difficult in fabrication</li> <li>Extra process</li> </ul> |

|                 | Super-strate<br>Dielectric Lens | (b)                                                                             | - Moderate radiation efficiency<br>- Good for full integration                                                                                           | - Extra process<br>- Not yet widely used                                                                        |

Table 2.1. Reported on-chip antennas in silicon substrate.

(a) : Reducing high conductive substrate loss

(b) : Reducing surface-wave mode excitation

It shows that the two main factors causing low radiation efficiency could be mitigated by applying the wafer-thinning technology which has been widely studied for demanding requests in RFID, and advanced multichip packaging (MCP) [Sandireddy07]. This approach takes advantage of the native antenna design which is cost effective and easy for integration with transceivers in a single chip. Moreover, wafer-thinning is required for an advanced packaging technology to improve the insertion loss due to bond-wires even for the transceiver with external antenna. It should be noted that less than 50  $\mu$ m of substrate thickness is required for even the lower frequency range of the terahertz dipole or slot antenna. Hence the wafer-thinning is more effective for the frequency range less than 200 GHz whose critical thickness is thicker than 100  $\mu$ m considering yield and cost.

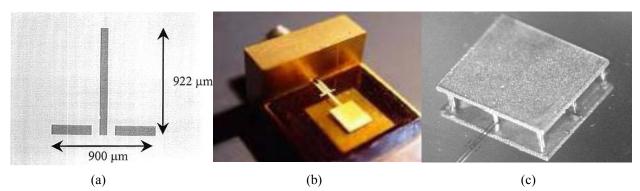

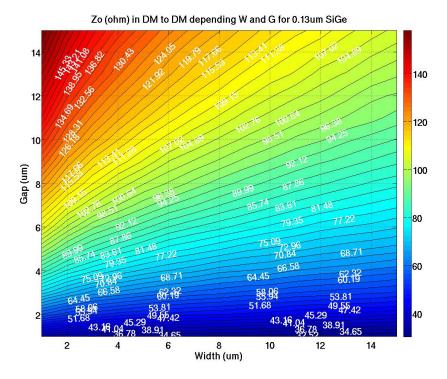

#### 2.3.2 On-chip Folded Slot Antenna with Thinned Silicon Substrate

In on-chip antenna arrays, slot antenna is more practical than printed dipole antenna because slots couple to the dominant  $TM_0$  mode along the perpendicular direction to their axis (broadside), which can alleviate the complexity of the required feed network. Moreover, many slots can be integrated in the same ground plane, which can be easily integrated with planar structure amplifiers with CPW transmission-line.

The folded slot antenna is one of the popular types of on-chip antennas which can be easily fed by CPW [Ding98] [Eldek02] [Chen03]. Usually, the circumference of the folded-slot is designed to be approximately equal to one guided wavelength ( $\lambda_g$ ) [Weller95]. It can be fed with a CPW allowing for easy integration of three-terminal devices or MMIC's for microwave amplification and reception. Basically, folded antenna has the characteristic of a broad bandwidth of frequency and a radiation pattern with maximum radiation at the broadside. From Babinet's principle [Kraus], the input impedance of complementary antennas can be calculated by

$$Z_{slot} = \frac{\eta^2}{4Z_{dipole}} \approx 500\,\Omega \tag{2.4}$$

Where  $\eta$  is the free space intrinsic impedance (~376.7  $\Omega$ ) In order to reduce the  $Z_{slot}$  to realize an appropriate matching network, the multiple stubs can be included inside of the slot which is a complementary of the *N*-element dipole antenna ( $Z_{in,N} = N^2 Z_{dipole}$ ). Therefore, the input impedance of the *N*-element slot antenna is reduced by,

$$Z_{in,N} = \frac{Z_{slot}}{N^2}$$

(2.5)

Therefore when N=2, around 100  $\Omega$  of the input impedance could be realized. Further reduction of the antenna impedance is performed by controlling the stub size.

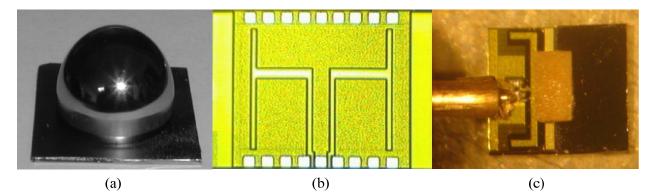

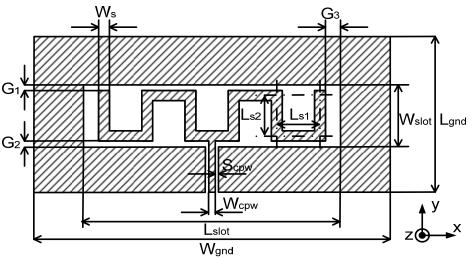

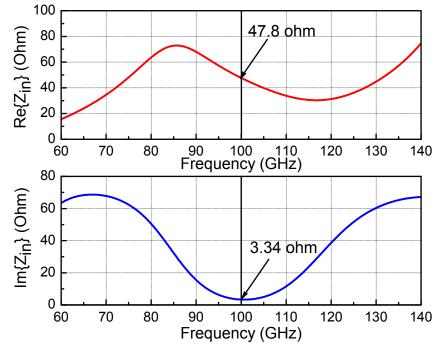

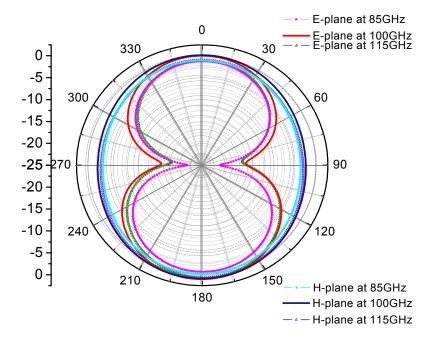

#### 2.3.3 100 GHz Folded Slot Antenna Design with Wafer-thinning

As a design example, a folded slot antenna with wafer thinned silicon substrate is presented for a wideband radiometry application. To apply on-chip antenna element for an antenna array, a compact unit element is essential to avoid grating lobes while scanning the main beam. Moreover the antenna must provide wide bandwidth for the passive imaging application. Considering the radiation pattern whose main-lobe direction must be broadside to the planar on-chip antenna, we design a CPW-fed folded slot antenna that is easy to integrate with active circuits which forms active antenna element.

Different from dipole type antennas, slot antenna utilizes the peripheral ground plates from the planar active circuits, which is ideal for active antenna array. We start from a folded slot antenna whose single stub reduces antenna input impedance and provides wider bandwidth [Chen03].

Figure 2.5. Structural dimension of the designed folded slot antenna with a meandered stub ( $W_s$ =30 µm,  $L_{s1}$ = $L_{s2}$ =85 µm,  $G_1$ = $G_2$ =9 µm,  $G_3$ =26 µm,  $W_{slot}$ =612 µm,  $L_{slot}$ =108 µm,  $W_{gnd}$ =1000 µm,  $L_{gnd}$ =1000 µm, and  $W_{cpw}$ =10 µm,  $S_{cpw}$ =5 µm). (E-plane: *z*-*y*, H-plane: *z*-*x*)