# UC San Diego UC San Diego Electronic Theses and Dissertations

## Title

Multi-band high efficiency power amplifier

**Permalink** https://escholarship.org/uc/item/6gb284v2

Author Besprozvanny, Randy-Alexander Randolph

Publication Date 2011

Peer reviewed|Thesis/dissertation

## UNIVERSITY OF CALIFORNIA, SAN DIEGO

### Multi-Band High Efficiency Power Amplifier

## A Thesis submitted in partial satisfaction of the requirements for the degree of Master of Science

in

## Electrical Engineering (Electronic Circuits and Systems)

by

Randy-Alexander Randolph Besprozvanny

Committee in charge:

Professor James Buckwalter, Chair Professor Gabriel Rebeiz Professor Daniel Sievenpiper

2011

The Thesis of Randy-Alexander Randolph Besprozvanny is approved, and it is acceptable in quality and form for publication on microfilm and electronically:

Chair

University of California, San Diego

2011

## DEDICATION

I would like to first dedicate this work to my mother, Penny Besprozvanny, for without her, I would not be here.

Secondly, I would like to dedicate this work to Todd Thornton, a mentor and a friend that has not wavered in his commitment, guidance and friendship throughout the years.

## TABLE OF CONTENTS

| Signatu   | re P    | Page                                                            | iii                  |

|-----------|---------|-----------------------------------------------------------------|----------------------|

| Dedicat   | ion     |                                                                 | iv                   |

| Table of  | f Co    | ontents                                                         | V                    |

| List of S | Syn     | nbols                                                           | vii                  |

| List of I | Figu    | ures                                                            | viii                 |

| List of ] | [ab]    | les                                                             | xi                   |

| Abstrac   | t of    | f the Thesis                                                    | xii                  |

| Chapter   |         | Introduction                                                    | 1                    |

| Chapter   |         | Amplifier Operating Class                                       | 2                    |

| Chapter   |         | Power Transistor Technologies<br>3.1 Power Transistor Selection |                      |

| Chapter   |         | <ul> <li>Power Transistor Model</li></ul>                       | 12                   |

| Chapter   |         | Microwave Integrated Circuit Manufacturing Process              |                      |

| Chapter   |         | <ul> <li>High Efficiency Power Amplifier Design</li></ul>       | 20<br>22<br>26<br>27 |

| Chapter   | 7<br>7. | Multi-Band Series Switching Networks                            |                      |

| Chapter 8  |       |                                   |    |

|------------|-------|-----------------------------------|----|

| 8.         | Mul   | lti-Band Shunt Switching Networks |    |

|            |       | PIN Diode Switching               |    |

|            |       | Transistor Switching              |    |

| Chapter 9  |       |                                   |    |

| 9.         | Mea   | asurements                        | 60 |

|            | 9.1   | Test Environment                  | 61 |

|            | 9.2   | Physical Model                    |    |

|            |       | Prototype Results                 |    |

| Chapter 10 |       |                                   |    |

| 10.        | . Con | nclusion                          | 70 |

| References |       |                                   | 72 |

## LIST OF SYMBOLS

- [ $\mu$ ] Scaling Factor of  $1 \times 10^{-6}$

- [∫] Integral

- $[\sum]$  Summation

- [ $\omega$ ] Angular Frequency

- [\overline] Conduction Angle

- [π] Pi

- $[\theta]$  Phase Variable

- $[\zeta]$  Phase Variable

- [φ] Phase Variable

- $[\lambda]$  Wavelength

- [δ] Partial Derivative

- $[\sqrt{}]$  Square Root

- $[\Omega]$  Ohms

- [ɛ] Dielectric Constant

## LIST OF FIGURES

| FIGURE 2-1: Reactance-Compensated Class E Output Network Reactance             |

|--------------------------------------------------------------------------------|

| FIGURE 4-1: I-V Characteristics for the CGH60030D13                            |

| FIGURE 4-2: Drain Current vs. Gate Voltage Characteristics for the CGH60030D13 |

| FIGURE 4-3: Equivalent RF Transistor Model                                     |

| FIGURE 4-4: Transistor Input Impedance                                         |

| FIGURE 4-5: Transistor Output Impedance17                                      |

| FIGURE 6-1: Multi-Band Class E Design Schematic                                |

| FIGURE 6-2: Input Bias Network                                                 |

| FIGURE 6-3: Output Bias Network                                                |

| FIGURE 6-4: Input Impedance (Un-Matched)25                                     |

| FIGURE 6-5: Input Impedance (Matched)                                          |

| FIGURE 6-6: Input Impedance (Optimized)                                        |

| FIGURE 6-7: Input Impedance (Micro-Strip)25                                    |

| FIGURE 6-8: Small Signal (Lumped Tuning)25                                     |

| FIGURE 6-9: Small Signal (Micro-strip Tuning)                                  |

| FIGURE 6-10: Multi-Band Class E Amplifier Performance                          |

| FIGURE 6-11: Multi-Band Class E Amplifier Power Gain and PAE28                 |

| FIGURE 6-12: Voltage and Currents (Band 1)                                     |

| FIGURE 6-13: Voltage and Currents (Band 2)                                     |

| FIGURE 6-14: Voltage and Currents (Band 3)                                     |

| FIGURE 6-15: Voltage and Currents (Band 4)                                     |

| FIGURE 6-16: Micro-strip Transformer Performance Characteristics               |

| FIGURE 6-17: Multi-Band Class E Amplifier Performance with Output Transformer  |

## LIST OF FIGURES

| FIGURE 7-1: Series-Shunt Switch Network                                          |

|----------------------------------------------------------------------------------|

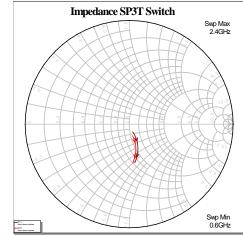

| FIGURE 7-2: Diode Switch Impedance                                               |

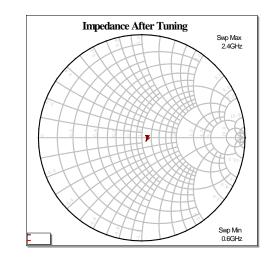

| FIGURE 7-3: Diode Switch Impedance (Tuned)                                       |

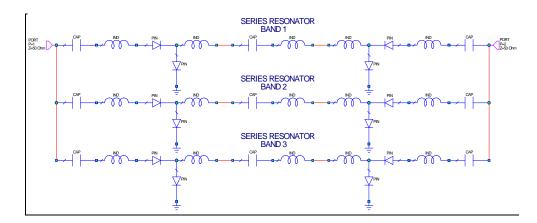

| FIGURE 7-4: SP3T Schematic                                                       |

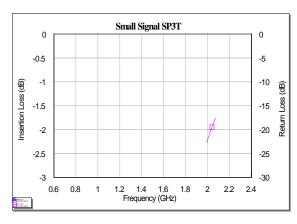

| FIGURE 7-5: Diode Switch Response                                                |

| FIGURE 7-6: Diode Switch Impedance (Tuned)                                       |

| FIGURE 7-7: Class E Amplifier Performance with Switched Series Resonator40       |

| FIGURE 7-8: Output Impedance (Band 1)40                                          |

| FIGURE 7-9: Output Impedance (Band 2)                                            |

| FIGURE 7-10: Output Impedance (Band 3)41                                         |

| FIGURE 7-11: Multi-Band Power Amplifier Output Power and Drain Efficiency42      |

| FIGURE 7-12: Multi-Band Power Amplifier Power Gain and PAE42                     |

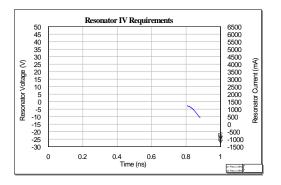

| FIGURE 8-1: Voltage and Currents (Band 1)                                        |

| FIGURE 8-2: Voltage and Currents (Band 2)                                        |

| FIGURE 8-3: Voltage and Currents (Band 3)                                        |

| FIGURE 8-4: Voltage and Currents (Band 4)                                        |

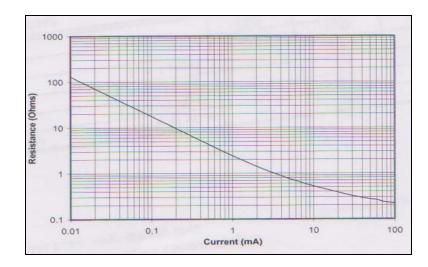

| FIGURE 8-5: Aeroflex Metelics PIN Diode Resistance Bias Curve [9]46              |

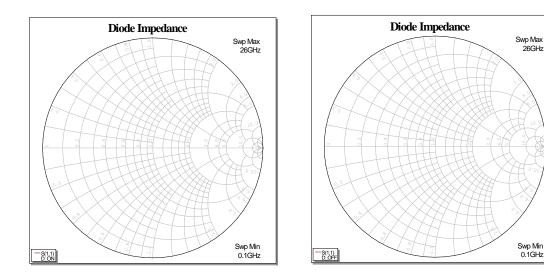

| FIGURE 8-6: PIN Diode Impedance (100mA)                                          |

| FIGURE 8-7: PIN Diode Impedance (-40V)47                                         |

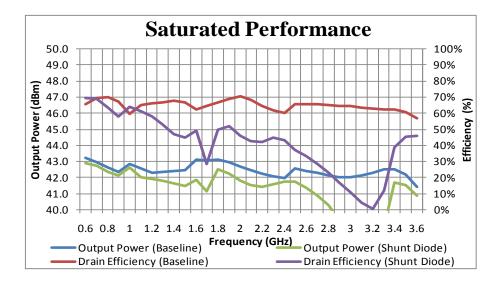

| FIGURE 8-8: Power Amplifier Performance with Shunt Diode Switching               |

| FIGURE 8-9: Power Amplifier Performance with Shunt Diode Switching (Optimized)51 |

| FIGURE 8-10: Power Amplifier Performance with Shunt Diode Switching (Optimized)  |

## LIST OF FIGURES

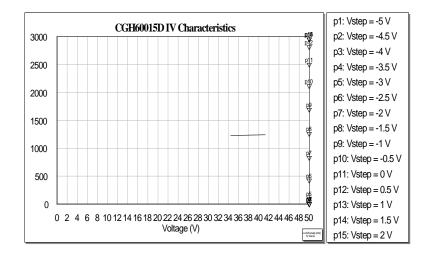

| FIGURE 8-11: CGH60015D I-V Characteristics                                      |

|---------------------------------------------------------------------------------|

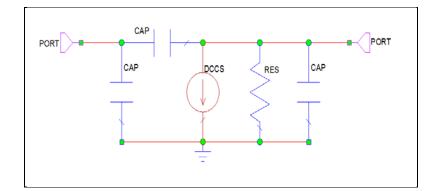

| FIGURE 8-12: Simplified FET Model54                                             |

| FIGURE 8-13: Power Amplifier Performance with Shunt Transistor Switching55      |

| FIGURE 8-14: Power Amplifier Performance with Shunt Diode Switching (Optimized) |

| FIGURE 8-15: Power Amplifier Performance with Shunt Diode Switching (Optimized) |

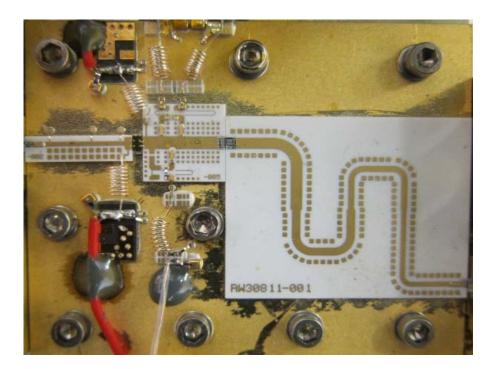

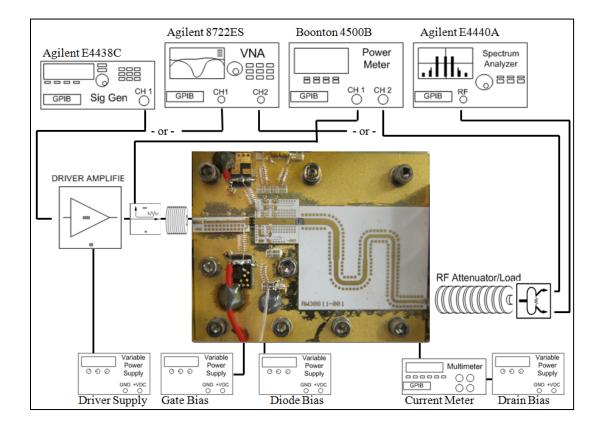

| FIGURE 9-1: MIC Prototype Fixture                                               |

| FIGURE 9-2: Prototype Test Setup                                                |

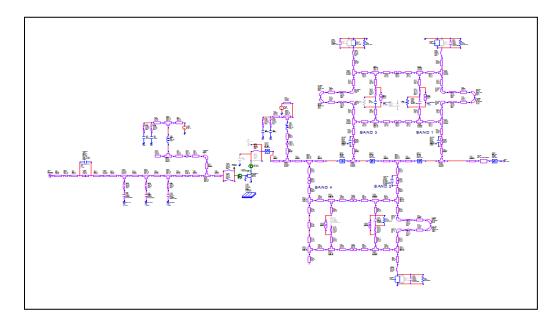

| FIGURE 9-3: Physical Model63                                                    |

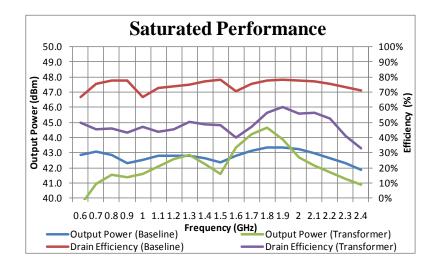

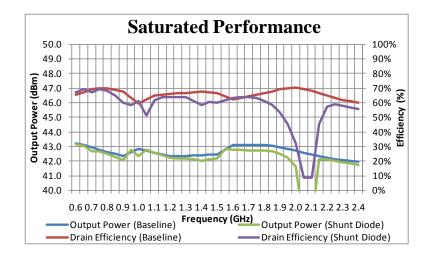

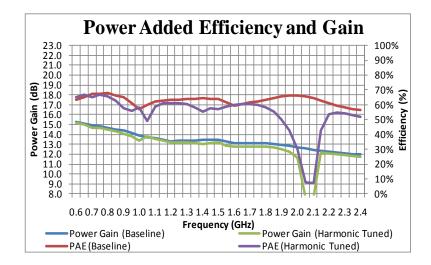

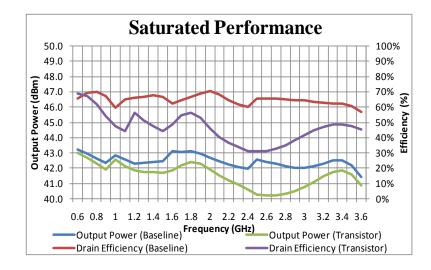

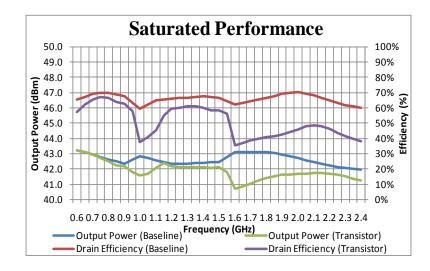

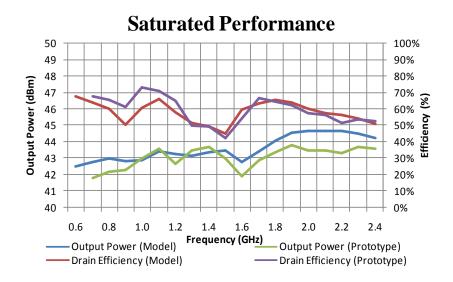

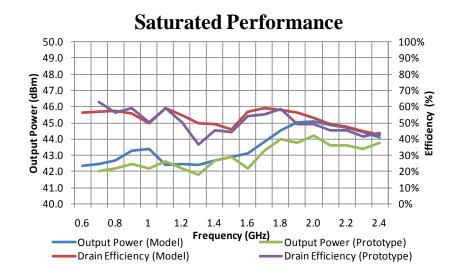

| FIGURE 9-4: Prototype Saturated Performance                                     |

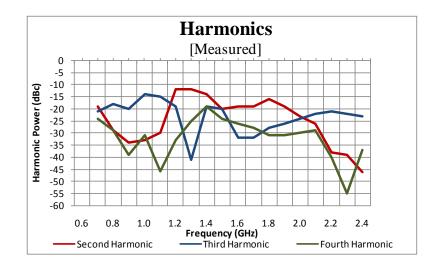

| FIGURE 9-5: Prototype Harmonic Performance                                      |

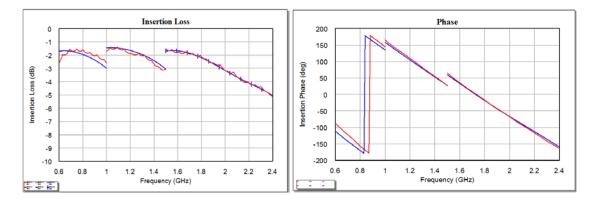

| FIGURE 9-6: Insertion Loss                                                      |

| FIGURE 9-7: Insertion Phase                                                     |

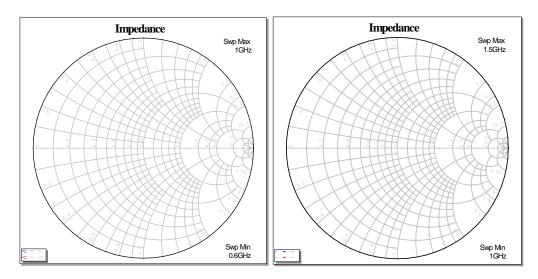

| FIGURE 9-8: Impedance (Band 1)                                                  |

| FIGURE 9-9: Impedance (Band 2)                                                  |

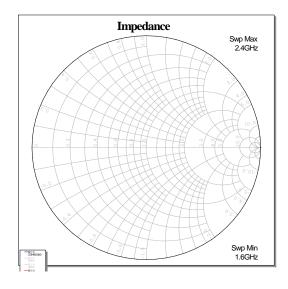

| FIGURE 9-10: Impedance (Band 3)67                                               |

| FIGURE 9-11: Prototype Saturated Performance                                    |

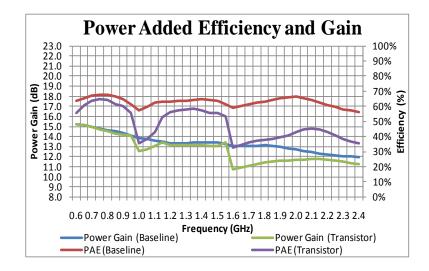

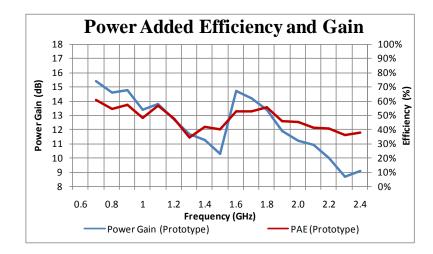

| FIGURE 9-12: Prototype Power Gain and PAE                                       |

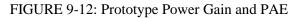

| FIGURE 9-12: Prototype Harmonic Performance                                     |

### LIST OF TABLES

| TABLE 3-1: Various Semiconductor Properties Contrasted                         | 9  |

|--------------------------------------------------------------------------------|----|

| TABLE 3-2: Commercially Available RF Power Transistor Properties               | 10 |

| TABLE 3-3: Commercially Available GaN DIE Transistors                          | 11 |

| TABLE 4-1: Active Characteristics for the CGH60030D                            | 14 |

| TABLE 4-2: Transistor Small Signal Equivalent Model Parameters                 | 16 |

| TABLE 6-1: Initial Input Impedance Values                                      | 24 |

| TABLE 6-2: Design Operating Conditions for Reactance Compensation Class E      | 27 |

| TABLE 6-3: Ideal Component Values for Reactance Compensation Class E Operation | 27 |

| TABLE 6-4: Multi-Band Class E Output Network Characteristics                   | 29 |

| TABLE 6-5: Binomial Transformer Design Parameters                              | 33 |

| TABLE 8-1: Output Network Impedances                                           | 49 |

| TABLE 8-2: Tuned Parallel Resonator Components                                 | 50 |

| TABLE 8-3: Tuned Parallel Resonator Components                                 | 57 |

#### ABSTRACT OF THE THESIS

Multi-Band High Efficiency Power Amplifier

by

Randy-Alexander Randolph Besprozvanny

Master of Science in Electrical Engineering (Electronic Circuits and Systems)

University of California, San Diego, 2011

Professor James Buckwalter, Chair

Achieving high efficiency power amplification over multi-octave RF bandwidths pose many design challenges. Conventional design techniques do not support high efficiency operation since use of distributed matching circuits and/or multiplexing several power amplifiers incur nonoptimal matching environments or high output losses. A new design approach is discussed whereby using the latest Gallium Nitride transistor technology and leveraging a Class E circuit environment, multiple electronically switched output networks are provided to the RF transistor providing high efficiency operation over multi-octave RF bandwidths. Two electronic switching elements are considered including PIN diodes and RF transistors. Using commercially available components, measurements are conducted on a physical prototype using PIN diode switch elements demonstrating typical efficiencies of 50% over two octaves bandwidth and at frequencies up to 2.4GHz.

# **CHAPTER 1**

## 1. Introduction

As wireless communication evolves in the highly competitive technology market, the need for high efficiency power amplifiers is more critical than ever. The latest commercially available RF transistor technologies are able to offer power amplifier systems with high efficiency, high power densities and high frequency capabilities. To achieve enhanced efficiency operation, specialized tuning techniques are necessary that minimize the dissipated power and control the harmonic content from the device. These design techniques define specific high efficiency operating classes, but offer very narrow RF bandwidths.

Extended bandwidths can be offered in conjunction with these high efficiency design techniques by multiplexing multiple narrow-band power amplifiers together yielding a larger composite RF bandwidth. This method is not ideal since its implementation can be very large, expensive and incur high output losses. Another design approach is to use a distributed matching circuit environment. This method is also not ideal because high transformation ratios are required when matching to high power transistors. As a result, a non-optimal matching environment is provided without the ability to effectively control the dissipated power or harmonics from the device.

A new design approach shall be discussed by which multiple narrow-band, high efficiency circuits shall be electronically switched into the RF transistor matching network. This method shall provide enhanced efficiency operation over a demonstrated composite bandwidth in excess of two octaves. Utilizing Microwave Integrated Circuit (MIC) manufacturing processes, a prototype shall be constructed to demonstrate up to three bands with output power levels of 30W using commercially available components.

# **CHAPTER 2**

## 2. Amplifier Operating Class

A power amplifier design requires a matching circuit on the input and output of an RF transistor in order for the device to provide signal amplification. These matching circuits are tailored for specific operating classes and are defined by the circuit environment and bias condition at the device. Conventional designs include Class A, Class AB and Class B operating conditions, while high efficiency designs include Class E, Class F and harmonically tuned circuits. Each presents inherent trade-offs in bandwidth, linearity and efficiency.

A Class A design is implemented by biasing the RF transistor such that the quiescent DC current draw is half of the maximum channel current capability, denoted as " $I_{dss}$ ". The bias current defines the conduction angle of the device. When the device is excited with a sufficiently large sinusoidal input signal, the peak to peak output current waveform conducts between " $I_{dss}$ " and 0 Amps. The circuit implementation provides wide bandwidth capabilities by matching to the device load-line impedance and providing a conjugate match to the device reactance. The output circuit impedance allows the device to operate between its maximum current and voltage limitations, whereby achieving maximum output power capability and efficiency.

Efficiency is degraded by an intrinsic parasitic property of the transistor defined as the device knee voltage " $V_{min}$ ". At this operating point, the transistor transitions between the saturation and triode operating points and results in current collapse for any further decrease in drain voltage. Effectively, efficiency is reduced since the transistor is unable to produce RF power at drain voltages below " $V_{min}$ " while DC supply power is dissipated within this region between common potential and the knee voltage.

With the exception of the current magnitudes near " $I_{dss}$ " and 0, the device yields minimal distortion of which is predominantly controlled by the current saturation and non-linear device transconductance near threshold voltages. Therefore, Class A provides one of the most linear operating classes. Consequently, since the bias point operates the device at half " $I_{dss}$ ", Class A operation is one of the least efficient designs. Assuming an ideal RF transistor, the maximum efficiency of a Class A design is 50%. The corresponding operating characteristics are described by Colantonio [1] as:

$$\begin{array}{ll} P_{out} & = 1/4 \; [I_{dss} \, * \, (V_{ds} - V_{min})] \\ R_L & = 2(V_{ds} - V_{min}) \, / \, I_{dss} \\ N_d & = \frac{1}{2} \, (1 - V_{min} / \, V_{ds}) \end{array}$$

A Class AB or Class B design is implemented by biasing the RF transistor such that the quiescent DC current draw is reduced from half " $I_{dss}$ " to 0 Amps. When the device is excited with a sufficiently large sinusoidal input signal, the peak to peak output current waveform conducts between " $I_{dss}$ " and 0 Amps as in the Class A case. Since part of the input voltage waveform operates the transistor below threshold voltage, part of the output current waveform is effectively clipped below 0 Amps, requiring more input drive power to achieve " $I_{dss}$ ", thereby reducing gain.

Since part of the current waveform is clipped, a non-sinusoidal signal is created as governed by the device conduction angle. This non-sinusoidal waveform adds distortion to the output power signal and can be represented by the Fourier series of the current waveform. Consequently, higher efficiency is achieved since the static DC power requirements are reduced without a peak power reduction from the transistor. When considering an ideal device, the maximum efficiency of a Class AB or Class B design ranges from 50% to 78.5% depending on the conduction angle. The corresponding design equations are detailed by Colantonio [1] as: Conduction Angle:

$$\phi = \cos^{-1}(I_{dc}/I_{dss})$$

1

Fourier Series Waveforms:

$$\begin{split} i_{\rm D}(t) &= I_{\rm D} + \sum I_{\rm n} \cos(n \varpi t + \zeta_{\rm n}) \\ v_{\rm DS}(t) &= V_{\rm dc} - \sum I_{\rm n} |Z_{\rm n}| \cos(n \varpi t + \varphi_{\rm n}) \end{split}$$

Fourier Series Coefficients:

$$\begin{split} I_0 &= (I_{dss}/2\pi) * \left[ (2\sin(\phi/2) - (\phi * \cos(\phi/2)) / [1 - \cos(\phi/2)] \right] \\ I_1 &= (I_{dss}/2\pi) * \left[ \phi - \sin(\phi) \right] / [1 - \cos(\phi/2)] \\ I_n &= (2I_{dss}/\pi) * \left[ \sin(n * \phi/2)\cos(\phi/2) - n * \sin(\phi/2)\cos(n * \phi/2) \right] / \left[ n * (n^2 - 1) * (1 - \cos(\phi/2)) \right] \end{split}$$

**Operating Characteristics:**

$$\begin{aligned} P_{out} &= [I_{dss} * (V_{ds} - V_{min})] * [\phi - \sin(\phi)] / [4\pi (1 - \cos(\phi/2))] \\ R_L &= [2\pi (V_{ds} - V_{min}) (1 - \cos(\phi/2))] / I_{dss} (\phi - \sin(\phi)) \\ N_d &= [(\phi - \sin(\phi)) * (V_{max} - V_{min})] / [(2\sin(\phi/2) - \phi\cos(\phi/2)) * (V_{max} + V_{min})] \end{aligned}$$

The Class AB and Class B power amplifier circuit design can achieve yet higher efficiencies by providing a harmonically tuned output impedance environment to the RF transistor. This harmonically tuned circuit design presents specific impedances to the device at the fundamental and harmonic frequencies, whereby minimizing the dissipated power within the transistor and reducing harmonic power delivered to the load. These are defined as the power balance conditions as discussed by Colantonio [1] and require the following relationships be satisfied simultaneously in order to achieve maximum efficiency:

Harmonic Power:

$$P_{dissipated} + \sum_{n=2}^{\infty} P_{out,n} = 0$$

**Dissipated Power:**

$$P_{\text{dissipated}} \qquad = 1/T \int_0^T v_{\text{DS}}(t) \, \ast \, i_{\text{D}}(t) \; \text{d}t = 0$$

A Class F design is a type of harmonically tuned amplifier which presents high odd-order harmonic impedances and low even-order harmonic impedances to the RF transistor drain. This harmonically tuned approach presents a square drain voltage to the device whereby the overlap between drain current and drain voltage is minimized. Reducing the time-domain overlap of the two drain signals ideally results in no dissipated power within the device satisfying part of the power balance condition and ideally resulting in up to 100% efficiency. Limited bandwidth in excess of 20% is achieved by controlling each of the harmonic impedances in this operating class.

A Class E design is another high efficiency operating class by which dissipated power and harmonic content delivered to the load are simultaneously reduced. These conditions are satisfied by ideally operating the device as a switch and ensuring that when the transistor is enabled, the drain voltage is zero. Simultaneously, it is necessary to ensure that any change in voltage across the transistors parasitic drain capacitance is zero so that no switching losses occur in the device. As discussed by Colantonio [1], these two conditions are defined as the Zero Voltage Switching (ZVS) and Zero Voltage Derivative Switching (ZVDS) and thus satisfy part of the power balance condition.

The circuit design requires a purely sinusoidal load current setup, an inductive load impedance with a phase angle of 32.5 degrees to the transistor and a specific amount of shunt capacitance on the output network as detailed by Asbeck [3]. The sinusoidal load current is facilitated by implementing a series resonator in-line with the load. As such, no power is lost to harmonics satisfying the remaining part of the power balance condition to ideally achieve 100% efficiency. The resonator is mis-tuned from the fundamental frequency by increasing the series inductance providing the required load phase angle. This results in limited bandwidth due to the reactive load variation over frequency.

For the time period that the transistor is enabled, a sinusoidal load current is constrained by the series resonator. During the period that the transistor is disabled, the remaining part of the sinusoidal load current is sustained through the output networks shunt capacitance. The required capacitance is determined by the operating frequency and can ideally absorb the device drain capacitance.

Increased RF bandwidths can be achieved by implementing reactance compensation on the output impedance network as discussed by Grebennikov [4] by which a consistent load phase angle is provided over much wider frequency ranges. It has been demonstrated that high efficiency operation can be provided for bandwidths in excess of 40% as discussed by Asbeck [3].

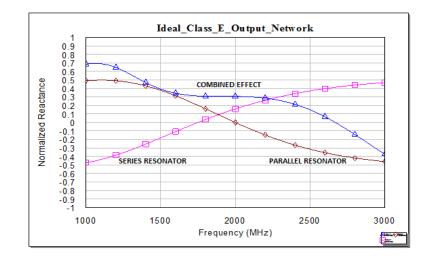

This circuit design approach is implemented by including a shunt resonator in conjunction with the series resonator on the output impedance network. The series resonator is tuned at the fundamental operating frequency while the shunt resonator is mis-tuned to present an inductive load phase angle of 34.244 degrees. The combination of the two resonators allows the shunt resonant circuit to compensate the frequency sensitive reactance variation of the series resonant circuit as is illustrated in FIGURE 2-1.

By offering extended bandwidth potential and higher frequency capabilities over the other operating class discussed, the reactance compensation Class E design is the best suited circuit configuration for the Multi-Band High Efficiency Power Amplifier and will serve as the baseline circuit design approach.

FIGURE 2-1: Reactance-Compensated Class E Output Network Reactance

# **CHAPTER 3**

# 3. Power Transistor Technologies

There are four commercially available transistor technologies that can be considered for the Multi-Band High Efficiency Power Amplifier. These technologies include Gallium Arsenide (GaAs), Gallium Nitride (GaN), Silicon Carbide (SiC) and Silicon (Si) Laterally Diffused Metal Oxide Semiconductor (LDMOS) devices. Selection of the appropriate device is determined by the circuit requirements and can be evaluated based on the device properties detailed by Colantonio [1] and subsequently shown for the key parameters in TABLE 3-1.

Achieving high system efficiency not only requires a high efficiency circuit design, but selection of a transistor that can provide high power gain. Since a power amplifier achieves its highest efficiency when operated in saturation, high power gain reduces the input drive requirements to achieve saturation thereby resulting in high power added efficiency (PAE).

A particular transistors transit frequency " $F_t$ " and maximum power gain frequency " $F_{max}$ " limits are metrics used to determine the associated power gain. The transit frequency is the point where the device current gain goes to unity while the maximum power gain frequency is the point where the output power of a device is equivalent to the input power. Each frequency limit decays at a rate of 20dB per decade whereby the maximum expected device gain can be extrapolated based on the desired operating frequency. The corresponding maximum operating frequency should be selected in order to achieve a minimum 10dB. The relationship for the two frequency limits are detailed by Asbeck [3] as:

$$\begin{split} F_{t} &= g_{m} / 2\pi \; (C_{gs} + C_{gd}) \\ F_{max} &= F_{t} / \; \sqrt{\; [2(R_{g}/R_{o}) + (8\pi \; F_{t}R_{g}C_{gd})]} \end{split}$$

| PROPERTY                    | UNITS                | TRANSISTOR TECHNOLOGY |       |       |        |  |

|-----------------------------|----------------------|-----------------------|-------|-------|--------|--|

| PROPERTY                    | UNITS                | Si                    | GaAs  | GaN   | 4H-SiC |  |

| Electron Mobility           | cm <sup>2</sup> /V*S | 1500                  | 8500  | 1000  | 900    |  |

| Hole Mobility               | cm <sup>2</sup> /V*S | 450                   | 400   | 350   | 120    |  |

| Bandgap                     | eV                   | 1.12                  | 1.42  | 3.2   | 3.23   |  |

| Avalanche Field             | 10 <sup>5</sup> V/cm | 3.8                   | 4.2   | 50    | 35     |  |

| Saturated Drift Velocity    | 10 <sup>7</sup> cm/s | 0.7                   | 2     | 1.8   | 0.8    |  |

| Saturation Field            | $10^3$ V/cm          | 8                     | 3     | 15    | 25     |  |

| Thermal Conductivity at 25C | W/cm*C               | 1.4                   | 0.45  | 1.7   | 4.9    |  |

| Dielectric Constant         | -                    | 11.9                  | 12.9  | 14    | 10     |  |

| Substrate Resistance        | Ω*cm                 | -                     | >1000 | >1000 | 1-20   |  |

TABLE 3-1: Various Semiconductor Properties Contrasted

High " $F_t$ " and " $F_{max}$ " frequencies are dependent on high device transconductance " $g_m$ ." There are many factors involved in achieving high transconductances from an RF transistor including transistor design, but the primary mechanism is attributed to high device electron mobility. GaAs transistors exhibit the highest electron mobility and consequently yield the highest power gain of the considered technologies. Among the wide bandgap devices considered, GaN yields the highest transconductance and associated power gain capabilities.

Another device characteristic needed to further enhance efficiency capability from an RF transistor are associated with the intrinsic parasitic elements. For the device technologies considered, various commercially available devices with a representative output power of 30W were evaluated as shown in TABLE 3-2.

Selection of a high efficiency device should include a low knee voltage " $V_{min}$ " since it sets the upper limit on the device efficiency. For a particular current conduction capability, a low " $V_{min}$ " is associated with a low on-state resistance " $R_{on}$ " which is described as the ratio of " $V_{min}$ " and " $I_{dss}$ ". By comparing the commercially available transistor technologies, GaAs transistors offer the lowest on-state resistance, while GaN offers the lowest among the wide bandgap devices.

| Manufacturer | Part Number | Technology | Rated Power | Voltage | Breakdown<br>Votlage | Drain<br>Capacitance | On-State<br>Resistance | Trans-<br>conductance | Ref. |

|--------------|-------------|------------|-------------|---------|----------------------|----------------------|------------------------|-----------------------|------|

|              |             |            | W           | V       | V                    | pF                   | Ω                      | mS                    |      |

| Eudyna       | FLL300IL-3  | GaAs       | 30          | 10      | 15                   | -                    | 0.1                    | 6000                  | [14] |

| NXP          | BLF3G21-30  | LDMOS      | 30          | 28      | 65                   | 48                   | 0.3                    | 3000                  | [15] |

| Cree         | CRF24060    | SiC        | 60          | 48      | 120                  | 5                    | -                      | 800                   | [16] |

| Cree         | CGH60030    | GaN        | 30          | 28      | 100                  | 1.3                  | 1.1                    | 1800                  | [5]  |

TABLE 3-2: Commercially Available RF Power Transistor Properties

Lastly, by operating an RF transistor in a Class E circuit environment, a device that can withstand high breakdown voltages is required. As detailed by Cripps [2], the Class E output circuit can present drain voltages in excess of 3.6 times the nominal DC bias voltage. Evaluating the key device properties show that only GaN presents the highest breakdown voltage margin relative to the nominal bias voltage. This is attributed to avalanche field strengths an order of magnitude higher than all other considered technologies.

### 3.1 Power Transistor Selection

Since the Multi-Band High Efficiency Power Amplifier is to be based on a Class E circuit design, high design voltages require wide bandgap devices to be considered exclusively. GaN transistors are able to offer the best balance of intrinsic properties and operational characteristics, making them the best technology choice.

Most commercially available GaN transistors are available in a packaged configuration. However, achieving maximum efficiency and frequency potential requires specific control of the impedances at the transistor drain, making it difficult to compensating package parasitic contributions. Therefore, device selection must consider an un-packaged transistor in "DIE" form. Consideration of the various commercially available devices has been restricted to transistors that can deliver output power levels of approximately 30W. Use of higher power device is possible depending on manufacturer product offerings. The various un-packaged, commercially available GaN transistors and their associated properties are summarized in TABLE 3-3.

| Manufacturer | Part Number | Process | Rated Power | Vds | Vds,max | Cds | Fmax | Reference |

|--------------|-------------|---------|-------------|-----|---------|-----|------|-----------|

| Wanulacturer | Part Number | um      | W           | V   | V       | рF  | GHz  | Reference |

| RFMD         | RF3931D     | 0.5     | 30          | 50  | 150     | 12  | 0.08 | [17]      |

| Triquint     | TGF2023-05  | 0.25    | 25          | 28  | 40      | 1.2 | 2.07 | [12]      |

| Cree         | CGH60030D   | 0.4     | 30          | 28  | 100     | 1.3 | 2.35 | [5]       |

TABLE 3-3: Commercially Available GaN DIE Transistors

Selection of the best commercially available DIE GaN transistor is predicated on the device maximum frequency capability when used in the reactance compensation Class E amplifier design. This limit is set by the device drain capacitance since the desired value becomes progressively small as the operating frequency increases. Operation beyond this limit is possible, however reduced efficiency will occur since the ZVDS operating constraint can no longer be satisfied. This upper frequency limit for Class E operation is described by Grebennikov [4] as:

$F_{max,Class-E} = 0.0798 * [P_{out} * (C_{ds} * V_{dc}^2)^{-1}]$

Use of larger power devices is possible without ideally influencing the frequency limit capabilities of the device in Class E operation. This is a result of the inverse proportionality between output power and drain capacitance. Thus, the limit can only be influenced by the DC bias voltage for a particular device.

By comparing the commercially available GaN device properties shown in TABLE 3-3, the best transistor choice is the Cree CGH60030D which offers the highest output power capabilities and frequency limit capabilities.

# **CHAPTER 4**

## 4. Power Transistor Device Model

The power amplifier design requires a non-linear transistor model that is representative of the physical device when operated under large signal conditions. When supplemented with external circuit elements, the model can reveal the fundament and harmonic behavior of the circuit by which a high efficiency, high frequency power amplifier design can be characterized and optimized. Evaluation of the transistor active and passive characteristics is necessary in the design of the external circuit elements.

A non-linear model is available from Cree Inc. for the CGH60030D transistor and is used in the Applied Wave Research (AWR) Microwave Office harmonic balance simulator. After consulting with Cree Inc., the transistor model is based on a modified Kondoh model [10] with inputs from Fager-Statz [19]. By using Cree Inc. proprietary modifications and additions, the nonlinear model was constructed.

### 4.1 Transistor Active Characteristics

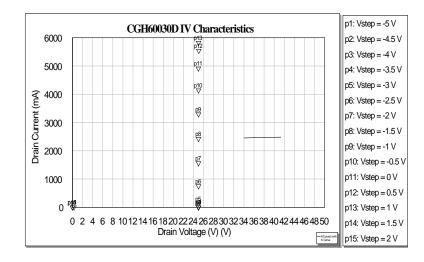

The active "on-state" characteristics of the CGH60030D can be evaluated by simulating the transistor drain voltage and current "I-V" characteristics. Since the selected transistor is a depletion mode device, the I-V characteristics can be evaluated by stepping the gate voltage between [-5.0V to +2.0V] and measuring the associated drain current as the drain voltage is swept between [0.0V to +50.0V]. The corresponding I-V characteristics are shown in FIGURE 4-1.

FIGURE 4-1: I-V Characteristics for the CGH60030D

FIGURE 4-2: Drain Current vs. Gate Voltage Characteristics for the CGH60030D

| Description          | Symbol              | Units      | Value   | Equation                                          |

|----------------------|---------------------|------------|---------|---------------------------------------------------|

| Minimum Voltage      | V <sub>min</sub>    | V          | 5.75    | Figure                                            |

| Threshold Voltage    | V <sub>t</sub>      | V          | -3.4    | Ids = 1mA                                         |

| Saturation Voltage   | V <sub>gs,sat</sub> | V          | 0.8     | Ids = 5.8A                                        |

| Saturated Current    | I <sub>dss</sub>    | А          | 5.8     | Figure                                            |

| Transconductance     | g <sub>m</sub>      | S          | 1.8     | Figure : $\delta I_D / \delta V_{gs}$             |

| On-State Resistiance | R <sub>on</sub>     | Ω          | 1       | $V_{min}$ / $I_{dss}$                             |

| Channel Modulation   | λ                   | $1/\Omega$ | 0.00027 | Figure 2: $\delta I_{ds,sat} / \delta V_{ds,sat}$ |

TABLE 4-1: Active Characteristics for the CGH60030D

Additional active device characteristics can be obtained by evaluating the transistor " $I_{ds} - V_{gs}$ " characteristics. With the drain biased at +28V, the transistor gate voltage was swept between [-5.0V to +2.0V] and the associated drain current recorded. The corresponding  $I_{ds} - V_{gs}$  characteristics are shown in FIGURE 4-2. The device active characteristics are summarized in TABLE 4-1.

#### 4.2 Transistor Passive Characteristics

The device model provided by Cree Inc. is a locked circuit element with four ports and does not permit visibility of any internal device characteristics. The only accessible attributes are the transistor gate, drain, source device terminals along with a port to monitor the device junction temperature.

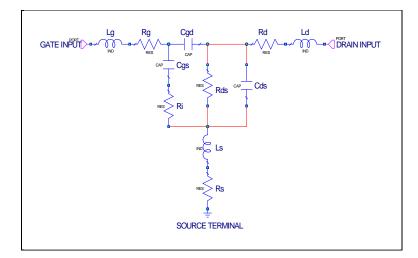

Since the intrinsic properties of the transistor are critical to the design of the Class E output network, a representative model is constructed based on the equivalent transistor model detailed by Kondoh [10]. The corresponding equivalent transistor model is shown in FIGURE 4-3. Leveraging the model design considerations outlined by Pengelly [18], the model shall be representative of the transistors passive components. The current generator shall be ignored in the equivalent model and it shall be compared to the CGH60030D with ideal bias components, +28V drain bias and operated at pinch-off [ $V_{gs} = -6V$ ].

FIGURE 4-3: Equivalent RF Transistor Model

Baseline component values shall be leveraged from published values for a similar GaN DIE transistor, the Triquint TGF2023-05. Within the product datasheet [12], Triquint lists the device component for their 1.25mm GaN unit cell which is representative of the 6W transistor transistor. Since the CGH60030D is a 30W device, the device is approximated as five 1.25mm unit cells arranged in parallel, except for the parasitic elements " $C_{gs}$ ", " $C_{ds}$ " and " $C_{gd}$ " which are published in the Cree product datasheet [5]. The corresponding initial values are detailed in TABLE 4-2. The " $R_{ds}$ " value was selected based on the leakage current through the drain terminal of the locked model. The corresponding leakage current was simulated as 13.9 µA and was approximated in the equivalent linear model as a 2MΩ resistance.

Since the Triquint GaN transistor is based on the 0.25  $\mu$ m fabrication process and the Cree GaN transistor is based on the 0.40  $\mu$ m fabrication process, a small error between the two models were observed. To bring the corresponding impedance environment in closer agreement, each component was iteratively tuned. The corresponding final values were then determined as shown in TABLE 4-2 for the CGH60030D device.

| PARAMETER | UNITS | DEVICE     |           |  |

|-----------|-------|------------|-----------|--|

| PARAMETER | UNITS | TGF2023-05 | CGH60030D |  |

| Cgs       | pF    | 8.95       | 8.6       |  |

| Cgd       | pF    | 0.32       | 0.86      |  |

| Cds       | pF    | 1.54       | 1.3       |  |

| Lg        | nH    | -0.0026    | -0.023    |  |

| Ld        | nH    | 0.0036     | 0.04      |  |

| Ls        | nH    | 0.00116    | 0.00116   |  |

| Rg        | Ω     | 0.156      | 0.26      |  |

| Rd        | Ω     | 0.256      | 0         |  |

| Rs        | Ω     | 0.026      | 0.026     |  |

| Ri        | Ω     | 0.052      | 0.052     |  |

| Rds       | Ω     | 24.72      | 2000000   |  |

TABLE 4-2: Transistor Small Signal Equivalent Model Parameters

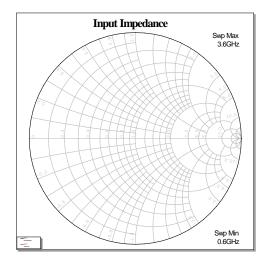

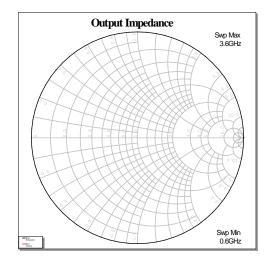

After fine tuning the equivalent transistor model, the equivalent impedance environment was evaluated with respect to the gate and drain terminals while the source was terminated to ground. The corresponding impedance environment was then compared to the locked CGH60030D transistor model.

The corresponding input impedance and output impedance for both models are simultaneously detailed in FIGURE 4-4 and FIGURE 4-5, respectively. Correlating the two models together yields a typical error of less than 1 $\Omega$  in magnitude. This close correlation validates the equivalent transistor model behavior of the CGH60030D. Under idealized circumstances, only "C<sub>ds</sub>", "C<sub>gs</sub>" and "C<sub>gd</sub>" present the most significant parasitic loading effects in the off-state as these parameters are the largest for the selected device, however the contribution of the additional parasitic elements becomes more pronounced at higher operating frequencies.

FIGURE 4-4: Transistor Input Impedance

FIGURE 4-5: Transistor Output Impedance

# **CHAPTER 5**

# 5. Microwave Integrated Circuit Manufacturing Process

Physical realization of the power amplifier will require Microwave Integrated Circuit manufacturing processes. MIC assemblies provide integration of DIE RF transistors, substrates, associated passive components and specific metal features needed to fully realize a power amplifier design on a common assembly.

The substrate to be used for MIC assembly is Asfired Alumina Oxide (Al<sub>2</sub>O<sub>3</sub>). This substrate presents a dielectric constant " $\varepsilon_r$ " of 9.8 while exhibiting excellent thermal conductivities in excess of 18 W/m\*K. The thickness and dielectric constant influence the characteristic impedance of the transmission line and is arbitrarily selected as 20 mils. The conductor metallization will provide a solid ground plane on one surface while the other side shall have features facilitating the power amplifier design. The conductor material composition shall consist of 0.15 mils Gold (Au) over 0.006 mils Palladium (Pd) over 0.003 mils Tin-Tungsten (TiW).

The entire assembly shall be constructed on a Copper-Molyblyum-Copper (CuMoCu) base material. The assembly begins by applying Gold-Germanium (AuGe) pre-forms between the CuMoCu carrier, the substrate and under a transistor shim. The transistor shim is made of gold plated Molyblyum (Mo) and is used to account for the height differences between the transistor thickness and the substrate height so that the final assembly sets the top of the transistor at the same level as the substrate. The assembly is heated to 400C at which point the AuGe reflows and joins the substrates and shim to the CuMoCu. After the substrates and shim are soldered in place with the pre-forms, Gold-Tin (AuSn) solder is placed between the RF transistor and the transistor shim. The assembly is heated up to 300C at which point the AuSn reflows and bonds the transistor to the assembly.

The RF transistor is connected to the substrates using three mil thick silver ribbons. Each ribbon is gap welded to the gate or drain land pad using DIE attach manufacturing processes.

Inductors shall be hand wound AWG-30 silver wire and shall be gap-welded to the substrates where appropriate. All tuning capacitors shall be the DiCAP series single layer capacitors from DiLABS with values and voltage breakdown limits required by the design. Each capacitor shall be installed on the substrates or CuMoCu carrier using conductive epoxy.

# **CHAPTER 6**

# 6. High Efficiency Power Amplifier Design

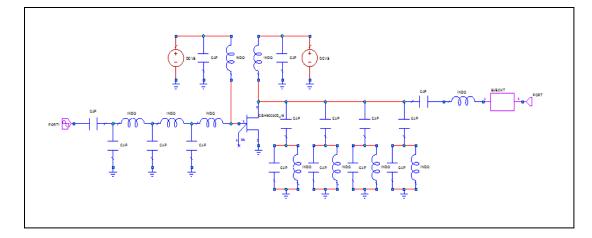

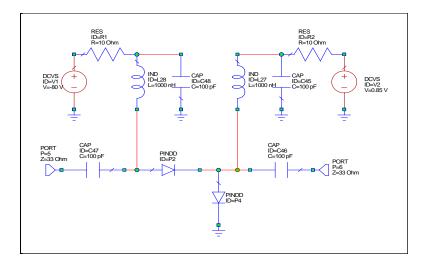

The Multi-Band High Efficiency Power Amplifier design process shall implement an input matching circuit, an output matching circuit, bias networks and switch elements. The input matching circuit is responsible for matching the transistor input impedance to the system characteristic impedance, thereby maximizing the device gain and optimizing PAE. The output impedance network shall facilitate a high efficiency circuit environment. The bias networks shall provide DC voltage to the gate, drain and switch elements as necessary. The switch elements shall facilitate multi-band functionality of the output matching circuit. The general circuit schematic is shown in FIGURE 6-1.

### 6.1 Bias Circuit

Each bias circuit shall provide a high impedance RF path to the DC supply providing the appropriate DC bias voltage. The circuit implementation is achieved using an inductor between the supply and the RF path. After the inductor, a capacitor is used to provide a low impedance path to ground whereby increasing isolation between the two points.

The inductor shall be implemented by gap welding a silver AWG-30 wire to the substrates. Each wire shall by hand wound around a 60-mil diameter core with a total of 8-turns. The total inductor length shall be 120-mils yielding a net inductance of 48nH. The substrates shall provide a 25-mil square land pad attachment point which will be connected to the main RF path through 5-mil wide feed lines.

FIGURE 6-1: Multi-Band Class E Design Schematic

The bias network is completed by placing DC bypass capacitors after the inductor on the supply side. The DC bypass capacitor selected is the D20BU101F1EX, 100pF single layer capacitor from DLI Dielectric Laboratories. Isolation is further increased by placing the D20BU101F1EX adjacent to the American Technical Ceramics ATC200A102KCA100X, 1000pF gold terminated capacitor. Each capacitor is connected to the inductor using silver ribbons which are attached using thermosonic ribbon bonding.

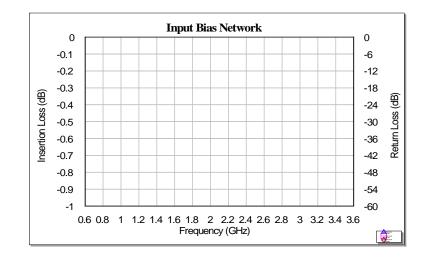

To ensure that the bias network is properly isolating the DC supply from the RF path, the bias network discussed was modeled. The corresponding pass-band performance was evaluated for the bias networks connected in the center of two 100-mil long,  $50\Omega$  lengths of line. The isolation through the bias network was also modeled by placing an RF port after the inductor and recording the insertion loss between the main path and the third port. The results are detailed for the input bias network and output bias network in FIGURE 6-2 and FIGURE 6-3, respectively. The results show good isolation characteristics of at-least -30dB and insertion losses up to - 0.08dB demonstrating the physical design provides a high impedance path between the DC supply and the RF network.

FIGURE 6-2: Input Bias Network

FIGURE 6-3: Output Bias Network

#### 6.2 Input Matching Circuit

Implementing the ideal Class E amplifier design requires that the transistor is operated as a switch whereby the device is either enabled by conducting current, or disabled. Since the RF transistor is effectively a voltage controlled current source, this switch functionality can be provided by presenting a square voltage waveform to the device input. This input voltage characteristic can be provided by cascading a Class F driver amplifier with the Class E amplifier. Unfortunately, such a harmonically tuned amplifier design does not yield multi-octave RF bandwidth capabilities necessary for the design. Therefore, a distributed input match is necessary to provide the wide bandwidth capabilities.

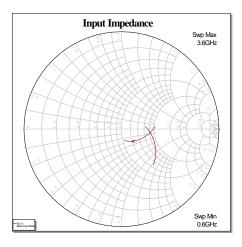

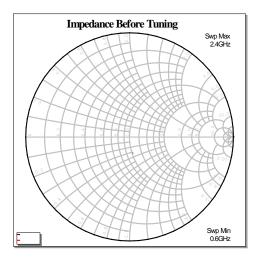

The input match design begins by determining the input impedance of the transistor when properly biased and terminated to the system impedance on both input and output. The bias condition was arbitrarily selected at  $[I_{ds} = 0.25A]$  which corresponds to a gate voltage of  $[V_{gs} = -2.7V]$  for the CGH60030D. The corresponding active input impedance is shown in FIGURE 6-4 and shows the device input impedance at center band  $[F_c = 2.1GHz]$  is  $[1.2 - j2.2]\Omega$ .

To establish a broadband match, a low quality factor transformation ratio is necessary. This is achieved by cascading multiple transformer sections together yielding intermediate impedances between the transistor and the system characteristic impedance. The transformer used shall be a low-pass filter configuration consisting of a series inductor followed by a shunt capacitor. The actual component values are dependent on the operating frequency and the impedance step. The corresponding transformation ratio and component values are detailed by Asbeck [3] as:

$$\begin{split} Q_{trans} &= \sqrt{R_{Load}/R_{source}-1}\\ L_{inductor} &= Q_{trans}*R_{source} \ / \ \varpi \\ C_{capacitor} &= Q_{trans} \ / \ R_{Load} * \ \varpi \end{split}$$

To achieve a low transformation ratio, the upper limit was arbitrarily set at a factor of about 1.5 which can be realized in the form of a 6 element low-pass filter. This reduces the transformation ratio from a high value of 6.3 which would be necessary if realized by a single low-pass section. The resulting tuning values are determined and shown in TABLE 6-1 with the matched input impedance shown in FIGURE 6-5.

| DESCRIPTION | DESCRIPTION SYMBOL    |      | INITIAL VALUE<br>(Lumped Element) | FINAL VALUE<br>(Lumped Element) | FINAL VALUE<br>(Micro-Strip) |

|-------------|-----------------------|------|-----------------------------------|---------------------------------|------------------------------|

|             |                       | nH   | 0.32                              | 0.3                             | -                            |

| SECTION 1   | L                     | mils | -                                 | -                               | 43                           |

|             | <b>C</b> <sub>1</sub> | pF   | 27.3                              | 17.8                            | 3.3                          |

|             | L <sub>2</sub>        | nH   | 0.6                               | 0.7                             | -                            |

| SECTION 2   |                       | mils | -                                 | -                               | 117                          |

|             | C2                    | pF   | 7.6                               | 8.0                             | 2.2                          |

|             |                       | nH   | 1.8                               | 1.6                             | -                            |

| SECTION 3   | L3                    | mils | -                                 | -                               | 167                          |

|             | C₃                    | pF   | 2.2                               | 2.3                             | 1.0                          |

**TABLE 6-1: Initial Input Impedance Values**

The matching conditions outlined thus far have provided a conjugate match at one discrete frequency. To extend the frequency capabilities, each input matching component is iteratively tuned until a more even impedance distribution is provided over the entire frequency range. The corresponding final lumped element component values are also detailed in TABLE 6-1 with the matched input impedance shown in FIGURE 6-6.

With the transistor output impedance terminated to  $50\Omega$ , the corresponding input impedance and associated small signal gain is modeled as shown FIGURE 6-8. Results show typical return losses of -6dB above 1.7GHz and small signal gain of 17dB across the evaluated frequency range. Due to bandwidth limitations, it proved extremely difficult to improve the return loss match at frequencies below 1.7GHz without significantly degrading the response above 3.5GHz.

The last step in the final input match design is to implement the lumped element components in a physical circuit environment. The final input match will consist of the matching components, bias networks and micro-strip to RF transistor transitions.

25

Input Impedance 3.6GHz

FIGURE 6-4: Input Impedance (Un-Matched)

FIGURE 6-6: Input Impedance (Optimized)

FIGURE 6-8: Small Signal (Lumped Tuning)

FIGURE 6-5: Input Impedance (Matched)

FIGURE 6-7: Input Impedance (Micro-Strip)

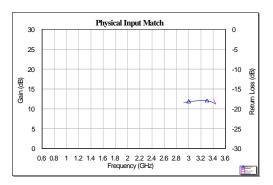

FIGURE 6-9: Small Signal (Micro-strip Tuning)

The input matching network inductors are to be approximated by micro-strip transmission lines with a particular line length printed on the substrates. Realizing the inductors on the substrates is preferred to implementing wire inductors to increase component quality factors and reduce manufacturing variation control. The shunt capacitors can be realized using single layer capacitors from DLI Dielectric Laboratories. Since the final design shall be used for demonstration of a physical prototype, the inductors will be realized by 50Ω micro-strip lines of specific length between shunt capacitors with the final tuning values summarized in TABLE 6-1 yielding modeled input impedances shown in FIGURE 6-7 and performances shown in FIGURE 6-9. The corresponding input impedance and associated small signal gain shows typical return losses of -2.2dB above 1.5GHz and typical small signal gain of 14dB.

### 6.3 Output Matching Circuit

The output impedance network shall be designed to support a reactance compensated Class E amplifier as outlined by Grebennikov [4] and [13] with the equations summarized in TABLE 6-2 and TABLE 6-3. Leveraging the peak output power capability from the transistor as indicated by the active component parameters summarized in TABLE 4-1, the output impedance network circuit component values are determined based on the formulas shown in TABLE 6-3.

With the operating characteristics determined, the circuit component values are derived based on the desired center-band operating frequency. The intended frequency range for the design shall extend between 600MHz through 2400MHz. Since the reactance compensation Class E design can support bandwidths in excess of 40%, a total of three individual bands will be necessary. A fourth band shall be considered in the analysis where possible to show the expected performance beyond which the ZVDS condition can be satisfied. The corresponding bands are divided as follows:

Band 1: [0.6 to 0.9] GHz→ $F_{center} = 0.75$ GHz Band 2: [1.0 to 1.5] GHz→ $F_{center} = 1.25$ GHz

| DESCRIPTION     | SYMBOL           | UNITS | VALUE | FORMULA                                           |

|-----------------|------------------|-------|-------|---------------------------------------------------|

| Maximum Power   | P <sub>out</sub> | W     | 32    | $1/4 [I_{dss} * (V_{ds} - V_{min})]$              |

| Load Impedance  | R <sub>L</sub>   | Ω     | 33    | $1.365 * (V_{dc}^2 / P_{out})$                    |

| Peak Voltage    | V <sub>pk</sub>  | V     | 102   | 3.647 * V <sub>dc</sub>                           |

| Peak Current    | I <sub>pk</sub>  | А     | -     | 2.647 * I <sub>dc</sub>                           |

| Frequency Limit | F <sub>max</sub> | GHz   | 2.5   | $0.0798 * [P_{out} * (C_{ds} * V_{dc}^{2})^{-1}]$ |

TABLE 6-2: Design Operating Conditions for Reactance Compensation Class E

TABLE 6-3: Ideal Component Values for Reactance Compensation Class E Operation

| DESCRIPTION      | SYMBOL         | UNITS | BAND 1 | BAND 2 | BAND 3 | BAND 4 | FORMULA                      |

|------------------|----------------|-------|--------|--------|--------|--------|------------------------------|

| Series Inductor  | L <sub>s</sub> | nH    | 7.2    | 4.3    | 2.7    | 1.8    | 1.026 * (RL / @)             |

| Series Capacitor | Cs             | pF    | 6.3    | 3.8    | 2.4    | 1.6    | $(\varpi^2 L_s)^{-1}$        |

| Shunt Inductor   | L <sub>p</sub> | nH    | 5.1    | 3.1    | 1.9    | 1.3    | 0.732 * (R <sub>L</sub> , o) |

| Shunt Capacitor  | Cp             | pF    | 4.4    | 1.8    | 0.4    | 0.0    | $0.685 * (0.8 R_L)^{-1}$     |

Band 3: [1.6 to 2.4] GHz $\rightarrow$ F<sub>center</sub> = 2.00GHz

Band 4: [2.5 to 3.6] GHz $\rightarrow$ F<sub>center</sub> = 3.00GHz

Utilizing each the center frequency of each band, the corresponding output network component values are determined and summarized in TABLE 6-3. The parallel resonant circuit capacitance " $C_p$ " is compensated to absorb the transistor drain capacitance after reactive loading.

### 6.4 Ideal Amplifier Performance

The idealized Class E power amplifier design for the CGH60030D transistor was evaluated with the input and output impedance network circuits. For the output impedance network, each of the series and shunt resonator circuit elements were exclusively applied into the network for the evaluated frequency band. The output network is highly idealized because no transmission lines are implemented, selected components have infinite quality factors and the load impedance is purely resistive over all frequencies. The model serves as a baseline by which the maximum achievable efficiency can be established for the implemented Class E design.

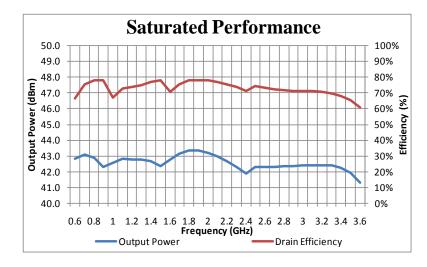

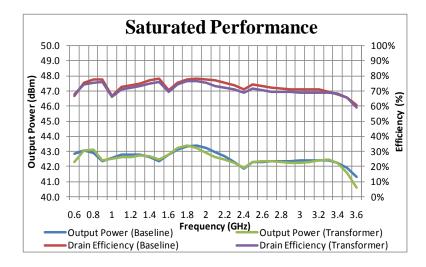

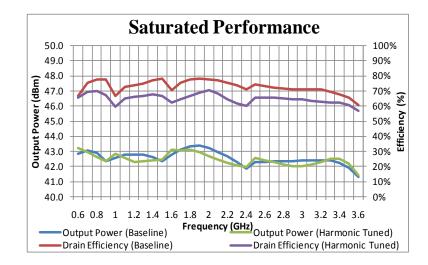

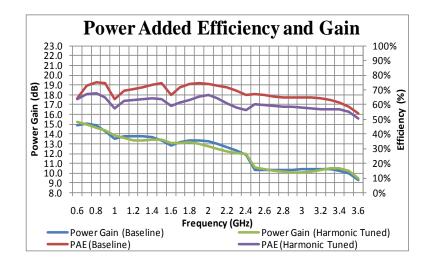

FIGURE 6-10: Multi-Band Class E Amplifier Performance

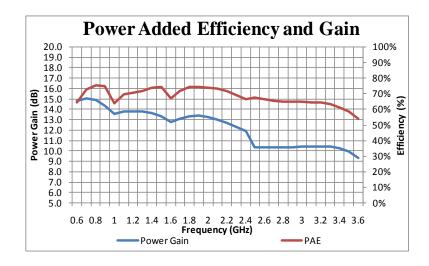

The corresponding simulation results show a composite performance response from all four bands in FIGURE 6-10. The average efficiency from the power amplifier is 75% over the target bandwidth with an average output power of +42.8dBm (19W). The corresponding power gain and power added efficiency is illustrated in FIGURE 6-11 with an average gain of 13.5dB and an average power added efficiency of 71%.

FIGURE 6-11: Multi-Band Class E Amplifier Power Gain and PAE

Based on the ideal Class E amplifier, the impedance environment presented to the RF transistor from the output impedance network was evaluated and summarized in TABLE 6-4. The output impedance environment up to the fourth harmonic was considered with the equivalent transistor model detailed in FIGURE 4-3 to show the impedances seen at the transistor drain. The transistor is presented an inductive load impedance which is sustained through each bands frequency range. Additionally, the transistor is presented capacitive impedances at harmonic frequencies which help facilitate a harmonically tuned impedance environment and meeting the design objectives for a reactively compensated Class E amplifier.

| FREQUENCY |       | HARMONIC IMPEDANCE |         |         |         |         |         |         |         |  |

|-----------|-------|--------------------|---------|---------|---------|---------|---------|---------|---------|--|

|           |       | FUNDA              | MENTAL  | SEC     | OND     | TH      | IRD     | FOURTH  |         |  |

| GHz       |       | Re{Zin}            | lm{Zin} | Re{Zin} | lm{Zin} | Re{Zin} | Im{Zin} | Re{Zin} | Im{Zin} |  |

|           | 0.6   | 28                 | 18      | 52      | -27     | 3       | -22     | 0.6     | -13     |  |

| D 1       | 0.7   | 29                 | 12      | 20      | -38     | 1       | -16     | 0.3     | -10     |  |

| BAND      | 0.8   | 30                 | 10      | 7       | -29     | 1       | -13     | 0.1     | -9      |  |

|           | 0.9   | 34                 | 10      | 3       | -22     | 0.3     | -11     | 0.1     | -7      |  |

|           | 1.0   | 29                 | 18      | 50      | -27     | 3       | -22     | 0.5     | -13     |  |

| 2         | 1.125 | 29                 | 12      | 26      | -39     | 1       | -17     | 0.3     | -11     |  |

| BAND      | 1.25  | 29                 | 10      | 11      | -33     | 1       | -14     | 0.2     | -9      |  |

| B₽        | 1.375 | 31                 | 10      | 5       | -26     | 0.5     | -12     | 0.1     | -8      |  |

|           | 1.5   | 35                 | 10      | 3       | -22     | 0.3     | -11     | 0.1     | -7      |  |

|           | 1.6   | 28                 | 18      | 46      | -30     | 2       | -19     | 0.4     | -11     |  |

| 3         | 1.8   | 29                 | 12      | 21      | -37     | 1       | -15     | 0.2     | -9      |  |

| BAND      | 2     | 29                 | 11      | 9       | -30     | 1       | -12     | 0.1     | -7      |  |

| B∕        | 2.2   | 31                 | 10      | 4       | -24     | 0.4     | -10     | 0.1     | -6      |  |

|           | 2.4   | 35                 | 10      | 2       | -19     | 0.2     | -9      | 0.1     | -5      |  |

|           | 2.6   | 34                 | 6       | 9       | -24     | 1       | -10     | 0.0     | -1      |  |

| 4         | 2.8   | 33                 | 3       | 5       | -21     | 0.4     | -8      | 0.1     | -4      |  |

|           | 3     | 33                 | 1       | 3       | -18     | 0.2     | -7      | 0.1     | -3      |  |

| BAND      | 3.2   | 34                 | -1      | 2       | -15     | 0.2     | -6      | 0.1     | -3      |  |

|           | 3.4   | 35                 | -3      | 1       | -13     | 0.1     | -5      | 0.0     | -2      |  |

|           | 3.6   | 37                 | -7      | 1       | -12     | 0.1     | -5      | 0.0     | -2      |  |

TABLE 6-4: Multi-Band Class E Output Network Characteristics

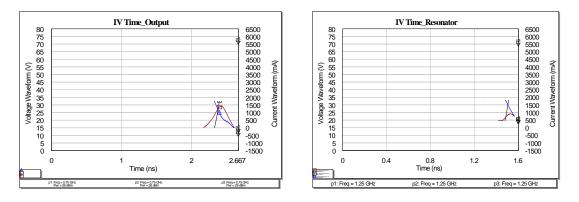

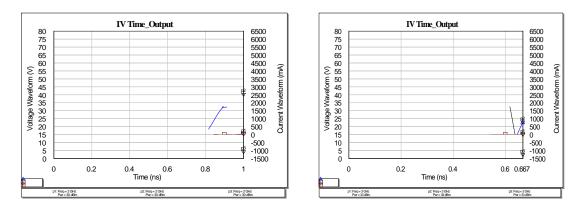

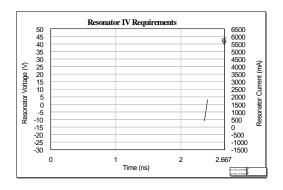

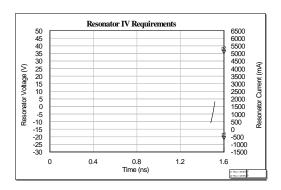

FIGURE 6-12: Voltage and Currents (Band 1) FIGURE 6-13: Voltage and Currents (Band 2)

FIGURE 6-14: Voltage and Currents (Band 3) FIGURE 6-15: Voltage and Currents (Band 4)

Lastly, to ensure the CGH60030D is operated as a Class E amplifier, the time domain drain voltage and current waveforms are evaluated and shown in FIGURE 6-12 through FIGURE 6-15 for the center of each band. The voltage and current waveforms closely resemble the desired Class E responses. Additionally, the load current is sustained through the parallel resonator capacitor as the transistor current drops below zero. An interesting observation is that the transistors drain currents drops below zero for a certain time period by which the parallel resonator capacitor begins to source current. This is caused by the transistor "C<sub>ds</sub>" which could not be evaluated outside of the locked transistor model.

### 6.5 Output Impedance Transformer

The Class E amplifier circuit design is predicated on presenting a  $33\Omega$  load impedance to the output impedance network. To physically realize the design requirement, it will be necessary to transform the desired load impedance to the system characteristic impedance of  $50\Omega$  over the operating frequency range. Realizing the impedance transformation over multi-octave RF bandwidths requires a multi-section transformer as was implemented in the input matching circuit. Each section can be physically implemented using a lumped element low-pass filter approach, or by utilizing quarter-wave micro-strip transformers.

A distributed lumped element approach has the benefit of very small space requirements, however low component quality factors and large manufacturing tolerances result in high losses making it impractical in maintaining high efficiency. Alternatively, quarter-wave micro-strip transformers require larger form factors, but exhibit low loss mechanisms and can be made with higher manufacturing tolerance control. This design implementation provides the best approach for the multi-band high efficiency power amplifier.

The transformer is realized by achieving a low quality factor transformation ratio between each section. The simplest impedance steps are determined using the Binomial multisection matching transformer as outlined by Pozar [6]. This approach realizes a maximally flat pass-band response and a gradual reactance variation across the pass-band frequency. The disadvantage of using a Binomial transformer is that the relative bandwidth capability is smaller than alternative designs including a Chebychev transformer approach.

The design processes involved in realizing the appropriate impedance steps are also outlined in Pozar [6]. This includes determining each impedance steps reflection coefficient  $[\Gamma_n]$ and the total reflection coefficient  $[\Gamma_N]$ . Utilizing  $[\Gamma_n]$ , the overall reflection coefficient  $[\Gamma(\theta)]$  can be determined based on the Binomial coefficient  $[C_n^N]$  which is determined by the designs number of sections [N]. Substitution back into the impedance steps reflection coefficient  $[\Gamma_n]$ , provides the impedance of each section exclusively. The corresponding equations are detailed by Pozar [6] as:

$$\begin{split} \Gamma_n &= \left(Z_{n+1} - Z_n\right) / \left(Z_{n+1} + Z_n\right) \\ \Gamma_N &= \left(Z_L - Z_N\right) / \left(Z_L + Z_N\right) \\ \Gamma(\theta) &= \Gamma_0 + \Gamma_1 e^{-j2\theta} + \ldots + \Gamma_N e^{-j2N\theta} \\ &= A(1 + e^{-j2\theta})^N \\ &= A * \sum_{n=0}^{N} C_n^n e^{-j2n\theta} \\ |\Gamma(\theta)| &= 2^N |A| |\cos(\theta)|^N \\ \theta &= (2\pi/\lambda_g) * L_g \\ C_n^N &= N! / (N - n)! * n! \\ A &= 2^{-N} * \Gamma(0) \\ \Gamma(0) &= (Z_L - Z_0) / (Z_L + Z_0) \end{split}$$

The number of sections needed to realize the intended bandwidth can be derived by setting an upper limit on the maximum desired pass band reflection coefficient  $[\Gamma_m]$ , or alternatively the return loss. Since the target is to achieve a near uniform response over the intended frequency range, return loss limits were arbitrarily selected to be -15dB [ $\Gamma_m = 0.177$ ]. Therefore, the minimum transformer order can be derived in Pozar [6] using the simplified expression given as:

$$\Gamma_{\rm m} = |A| * [2*\cos(-\pi/4*[(\text{Bandwidth / }F_{\text{center}}) - 2])]^{\rm N}$$

$$N_{\rm min} \rightarrow 4$$

Using the following initial conditions in conjunction with the design equations and objectives detailed above, the corresponding Binomial impedance transformer parameters  $[C_n^N]$  and  $[\Gamma_n]$  can be determined using the solved initial conditions  $[\Gamma(0) = 0.205]$  and [A= 0.013]. The results can be used to find the desired impedance step  $[Z_n]$  yielding the characteristic impedance of the quarter wave line  $[Z_{TL}]$ . Each section is to have an electrical length of ninety degrees

(quarter-wave) in the Alumina Oxide substrate  $[\lambda_g/4]$  at the center band frequency in order to accommodate a purely resistive transformation. Using the following initial conditions, the microstrip transmission line design parameters were obtained by using the Rogers Corporation transmission line calculator [22] with the results summarized in TABLE 6-5.

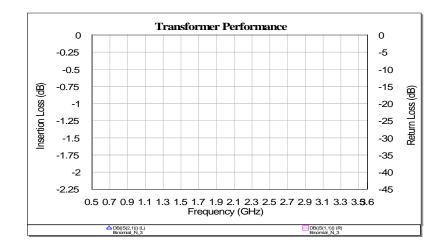

The quarter-wave transformer pass-band performance was modeled and shown in FIGURE 6-16. The model provided an input impedance of  $33\Omega$  and an output impedance of  $50\Omega$ . It can be seen that the design yields the target return loss of -15dB with good symmetry around the center frequency while presenting a maximally flat pass-band response. Consequently, the typical insertion loss is 0.15dB is associated with the dielectric and conductor losses which reduce the output power by 3.4%.

Using the impedance transformer in-line with the transistor output impedance network and the system impedance, the power amplifier performance was re-evaluated as shown in FIGURE 6-17. Comparing the amplifier performance with the output transformer shows a typical power reduction of 0.13dB and a efficiency reduction of 2%. The pass-band response is sustained showing that the transformer is maintaining the desired impedance of  $33\Omega$  to the output network with negligible performance reduction.

| DESCRIPTION            | SYMBOL                      | UNITS | SECTION 1 | SECTION 2 | SECTION 3 | SECTION 4 | FORMULA                                                                     |

|------------------------|-----------------------------|-------|-----------|-----------|-----------|-----------|-----------------------------------------------------------------------------|

| Binomial Coefficient   | C <sup>N</sup> <sub>n</sub> | nH    | 1         | 4         | 6         | 4         | N! / (N - n)! * n!                                                          |

| Reflection Coefficient | Γ(θ)                        | pF    | 0.01      | 0.05      | 0.08      | 0.05      | A * $\sum_{n=0}^{N} C_{n}^{N} e^{-j2n\theta}$                               |

| Line Impedance         | $\mathbf{Z}_{n,TL}$         | Ω     | 33.8      | 37.5      | 43.8      | 48.5      | $\left( {{Z_{n + 1} - Z_n }} \right) / \left( {{Z_{n + 1} + Z_n }} \right)$ |

| Line Width             | W                           | mils  | 39.6      | 33.3      | 25.2      | 20.6      | MWI - TX Line Calc                                                          |

| Line Length            | L                           | mils  | 582       | 582       | 582       | 582       | MWI - TX Line Calc                                                          |

TABLE 6-5: Binomial Transformer Design Parameters

FIGURE 6-16: Micro-strip Transformer Performance Characteristics

FIGURE 6-17: Multi-Band Class E Amplifier Performance with Output Transformer

# **CHAPTER 7**

## 7. Multi-Band Series Switching Networks

Sustaining Class E operation requires a series resonator to be placed on the output network so that a purely sinusoidal current is delivered to the load. A sinusoidal load current is required so that when the transistor is off, the sinusoidal load currents are sustained by the output networks shunt capacitance. To support the multi-band output network approach, the design must provide a physically realizable, switchable series resonator network. This poses significant challenges due to the high frequency and high power levels associated with the design objective.

There are two switching options that can be used in series with the system load network. One option is to use Silicon PIN diode switches capable of supporting 30W of RF power over the intended frequency range. The second switch network can be achieved by utilizing transistor based RF switches. Evaluating RF transistor based switches from Peregrine Semiconductor [20] and Hittite Microwave Corporation [21] show that devices are commercially available that can handle the designs output power. However, neither RF switch proves as a good candidate due to high insertion losses in excess of 0.7dB above 2.4GHz and the need for external matching components.

RF switches are available from Aeroflex Metelics that can support high RF power levels in excess of 100W over the intended frequency range. There are two solutions available in the form of a single position dual throw (SPDT) or a single position three throw (SP3T) switch. To properly implement the switch on the output network, it is necessary to place a switch on both sides of the series resonator. Using two cascaded Aeroflex MSW2031-203 [23] SPDT switches on each side of the series resonator will support all four operating bands, however referencing the manufacturer datasheet shows that the combined insertion loss can be as high as 1.6dB (0.4dB

35

each) whereby adding 31% additional output losses and resulting in an average amplifier drain efficiency reduction of 24%. Alternatively, only one Aeroflex MSW3201-320 [24] SP3T switch can be used on each side of the series resonator to support the target frequency range. The net insertion loss can be as high as 1.0dB over the target frequency range whereby adding 20% additional output losses resulting in an average amplifier drain efficiency reduction of 15%.

The considered RF switches from Aeroflex Metelics are internally matched, series-shunt PIN diode switches yielding return losses better than -15dB. Unfortunately, Aeroflex does not publish any S-parameters, thereby the previous analysis assumes no impedance interaction from the switches to the output impedance network. This idealization cannot be supported with physical devices, therefore greater amplifier efficiency degradation would be expected due to impedance loading upon the series resonator.

To better approximate the impedance loading effects, a discrete solution PIN diode model was constructed based on the series-shunt circuit configuration as shown in FIGURE 7-1. This circuit configuration yields the best isolation at the expense of insertion loss as detailed by Radmanesh [7]:

| Insertion Loss   | $= 20 \log_{10}   0.5 + (Z_0 + Z_0)  0.5 + (Z_0 + Z_0$ | $Z_{r}$ ) ( $Z_{0} + Z_{f}$ ) / $2Z_{0}Z_{r}$         |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|--|--|--|--|

| Isolation        | $= 20 \log_{10}   0.5 + (Z_0 + Z_0)  0.5 + (Z_0 + Z_0$ | $Z_{\rm f}$ ) ( $Z_0 + Z_{\rm r}$ ) / $2Z_0Z_{\rm f}$ |  |  |  |  |

| $Z_0$            | = Load characteristic impedance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                       |  |  |  |  |

| Zr               | $= R_r + j[\varpi L_{int} - (1/\varpi C_j)]$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | (Diodes reverse bias impedance)                       |  |  |  |  |