# UCLA UCLA Electronic Theses and Dissertations

#### Title

Communication Optimization for Customizable Domain-Specific Computing

Permalink https://escholarship.org/uc/item/6tp72870

**Author** Xiao, Bingjun

Publication Date 2015

Peer reviewed|Thesis/dissertation

UNIVERSITY OF CALIFORNIA

Los Angeles

# Communication Optimization for Customizable Domain-Specific Computing

A dissertation submitted in partial satisfaction of the requirements for the degree Doctor of Philosophy in Electrical Engineering

by

**Bingjun Xiao**

2015

© Copyright by Bingjun Xiao 2015

## Communication Optimization for Customizable Domain-Specific Computing

by

#### **Bingjun Xiao**

Doctor of Philosophy in Electrical Engineering University of California, Los Angeles, 2015 Professor Jingsheng Jason Cong, Chair

This dissertation investigates the communication optimization for customizable domain-specific computing at different levels in a customizable heterogeneous platform (CHP) to improve the system performance and energy efficiency.

*Fabric-level optimization driven by emerging devices.* Programmable fabrics (e.g., FPGAs) can be used to improve domain-specific computing by >10x in energy efficiency over CPUs since FPGAs can be customized to the application kernels in the target domain. But the programmable interconnects inside FPGAs occupy >50% of the FPGA area, delay and power. We propose a novel architecture of programmable interconnects based on resistive RAM (RRAM), a type of emerging device with high density and low power. We optimize the layout and the programming circuit of the new architecture. We also extend RRAM benefits to routing buffers. We observe the high defect rate in the emerging RRAM manufacturing and further develop a defect-aware communication mechanism. Conventional defect avoidance leaves a large portion of the chip in the new architecture unusable. So we propose new defect utilization methodologies by treating stuck-closed defects as shorting constraints in the routing of signals. We develop a scalable algorithm to perform timing-driven routing under these extra constraints and successfully suppress the impact of defects.

Chip-level optimization driven by accelerator-centric architectures. A chip can also be cus-

tomized to an application domain by integrating a sea of accelerators designed for the frequently used kernels in the domain. The design of interconnects among customized accelerators and shared resources (e.g., shared memories) is a serious challenge in chip design. Accelerators run 100x faster than CPUs and post a high data demand on the communication infrastructure. To address this challenge, we develop a novel design of interconnects between accelerators and shared memories and exploit several optimization opportunities that emerge in accelerator-rich computing platforms. Experiments show that our design outperforms prior work that was optimized for CPU cores or signal routing. Another design challenge lies in the data reuse optimization within an accelerator to minimize its off-chip accesses and on-chip buffer usage. Since the fully pipelined computation kernel consumes large amounts of data every clock cycle, and the data access pattern is the major difference among applications, existing accelerators use ad hoc data reuse schemes that are carefully tuned per application to fit the data demand. To reduce the engineering cost of accelerator-rich architectures, we develop a data reuse infrastructure that is generalized for the stencil computation domain and can be instantiated to the optimal design for any application in the domain. We demonstrate the robustness of our method over a set of real-life benchmarks.

Server-level and cluster-level optimization driven by big data. In the era of big data, workloads can no longer fit into a single chip. Most data are stored in disks, and we can only load a small part of it into main memories during computation. Due to the low access speed of disks, our primary design goal becomes minimization of the data transfer between disks and the main memory. We select a popular big data application, convolutional neural network (CNN), as a case study. We analyze the linear algebraic properties of CNN, and propose algorithmic modifications to reduce the total computational workload and the disk access. Furthermore, when the application data become even larger, it needs to be distributed among a cluster of server nodes. This motivates us to develop an accelerator-centric computing cluster. We test two machine learning applications, logistic regression and artificial neural network (ANN), on our prototyping cluster and try to minimize the total data transfer incurred during the computation in this cluster. We select the distributed stochastic gradient descent (dSGD) as our training algorithm to eliminate the inter-node communication within a training iteration. We also deploy an in-memory cluster computing infrastructure, Spark, to eliminate the inter-node communication across training iterations. The baseline Spark only supports CPUs, and we develop a software layer to allow Spark tasks to offload their major computation to accelerators which are equipped by each server node. During the computation offloading, we group multiple tasks into a batch and transfer it to the target accelerator in one transaction to minimize the setup overhead of the data transfer between accelerators and host servers. We further realize accelerator data caching to eliminate the unnecessary data transfer of training data based on the properties of iterative machine learning applications. The dissertation of Bingjun Xiao is approved.

Tyson Condie

Dejan Markovic

Mau-Chung Frank Chang

Jingsheng Jason Cong, Committee Chair

University of California, Los Angeles 2015

To my family

for their constant source of

love, concern, support, and strength all these years.

### TABLE OF CONTENTS

| 1 | Intr | oductio | <b>n</b>                                                              | 1  |

|---|------|---------|-----------------------------------------------------------------------|----|

|   | 1.1  | Custor  | nizable Domain-Specific Computing                                     | 1  |

|   | 1.2  | Comm    | unication Optimization for Customizable Domain-Specific Computing     | 4  |

|   |      | 1.2.1   | Programmable Interconnects Driven by Emerging Devices                 | 4  |

|   |      | 1.2.2   | Defect-Aware Routing on Nanodevice-Based Programmable Interconnects   | 6  |

|   |      | 1.2.3   | Optimized Interconnects Between Accelerators and Shared Memories      | 8  |

|   |      | 1.2.4   | Data Reuse Optimization for Stencil Access Patterns                   | 10 |

|   |      | 1.2.5   | Computation and Communication Optimization in Convolutional Neural    |    |

|   |      |         | Network Driven by Big Data                                            | 11 |

|   |      | 1.2.6   | Accelerator-Centric Cluster Computing with Communication Optimization | 12 |

| 2 | Prog | gramma  | ble Interconnects Driven by Emerging Devices                          | 16 |

|   | 2.1  | Introdu | action                                                                | 16 |

|   | 2.2  | Backg   | round                                                                 | 17 |

|   |      | 2.2.1   | Conventional FPGA                                                     | 17 |

|   |      | 2.2.2   | FPGAs with Emerging NVMs                                              | 20 |

|   | 2.3  | The FI  | PGA-RPI Architecture                                                  | 22 |

|   |      | 2.3.1   | Choice of NVMs                                                        | 22 |

|   |      | 2.3.2   | Overall Architecture                                                  | 23 |

|   |      | 2.3.3   | RRAM-Friendly Layout Design                                           | 24 |

|   |      | 2.3.4   | Programming Schematic                                                 | 28 |

|   |      | 2.3.5   | On-Demand Buffering Architecture                                      | 33 |

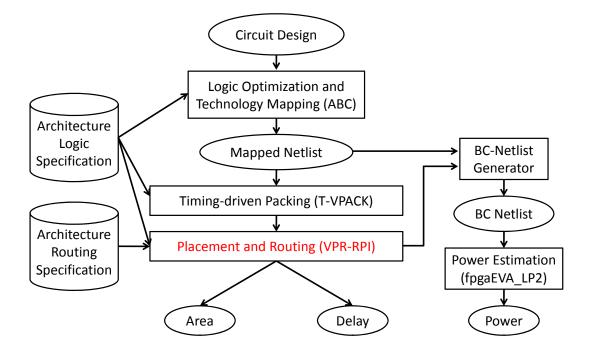

|   | 2.4  | Design  | a Tool Support                                            | 41 |

|---|------|---------|-----------------------------------------------------------|----|

|   |      | 2.4.1   | CAD Flow                                                  | 41 |

|   |      | 2.4.2   | Equivalent Circuit Model for Interconnect                 | 42 |

|   |      | 2.4.3   | On-Demand Buffer Allocation Algorithm                     | 43 |

|   |      | 2.4.4   | VPR-RPI: the P&R Tool for FPGA-RPI                        | 44 |

|   | 2.5  | Simula  | tion Results                                              | 46 |

|   |      | 2.5.1   | Settings                                                  | 46 |

|   |      | 2.5.2   | Optimize the On-Demand Buffering Architecture             | 47 |

|   |      | 2.5.3   | Evaluation of FPGA-RPI                                    | 48 |

|   |      | 2.5.4   | Impact on LB Architectural Design                         | 52 |

|   |      | 2.5.5   | Sensitivity Analysis                                      | 52 |

|   | 2.6  | Interco | onnect Improvement in LBs                                 | 54 |

|   | 2.7  | Conclu  | sion and Future Work                                      | 56 |

| 3 | Defe | ect-Awa | re Routing on Nanodevice-Based Programmable Interconnects | 57 |

|   | 3.1  | Introdu | uction                                                    | 57 |

|   | 3.2  | Quanti  | tative Defect Analysis                                    | 60 |

|   |      | 3.2.1   | Impact on Routing                                         | 60 |

|   |      | 3.2.2   | Impact on Placement                                       | 63 |

|   | 3.3  | Defect  | -Tolerant Routing                                         | 64 |

|   |      | 3.3.1   | Enforcement of Shorting Constraints                       | 65 |

|   |      | 3.3.2   | Prune Invalid Solutions Before Routing                    | 67 |

|   |      | 3.3.3   | Smart Mapping of ES-Clusters to Nets                      | 68 |

|   |      | 3.3.4   | Implementation                                            | 71 |

|   | 3.4  | Defect           | -Tolerant Placement                                               | 73  |

|---|------|------------------|-------------------------------------------------------------------|-----|

|   |      | 3.4.1            | Methodology                                                       | 73  |

|   |      | 3.4.2            | Implementation                                                    | 75  |

|   | 3.5  | Simula           | ation Results                                                     | 79  |

|   |      | 3.5.1            | Settings                                                          | 79  |

|   |      | 3.5.2            | Results                                                           | 79  |

|   | 3.6  | Conclu           | usion                                                             | 83  |

| 4 | Opti | i <b>mized</b> ] | Interconnects Between Accelerators and Shared Memories            | 84  |

|   | 4.1  | Introdu          | uction                                                            | 84  |

|   | 4.2  | Prelim           | inary                                                             | 86  |

|   |      | 4.2.1            | Interconnect Requirement Between Accelerators and Shared Memories | 86  |

|   |      | 4.2.2            | Configurable Crossbar to Meet Accelerator Demand                  | 87  |

|   |      | 4.2.3            | Problem Formulation                                               | 88  |

|   | 4.3  | Optim            | ization Inspired by Accelerators with Multiple Ports              | 89  |

|   |      | 4.3.1            | Identification of Unnecessary Switches                            | 89  |

|   |      | 4.3.2            | Minimum Cost of Accelerator Sub-Crossbar                          | 90  |

|   |      | 4.3.3            | Sub-Crossbar Design for Routing Flexibility                       | 91  |

|   |      | 4.3.4            | Virtualized Interface for Global Optimization Among Accelerators  | 93  |

|   | 4.4  | Optim            | ization Inspired by Accelerators in Dark Silicon Age              | 94  |

|   |      | 4.4.1            | Minimal Design with 100% Routability                              | 94  |

|   |      | 4.4.2            | Design with 100% Routability when Optimality is Unreachable       | 98  |

|   |      | 4.4.3            | Smaller Design with 95% Routability                               | 102 |

|   | 4.5  | Optim            | ization Inspired by Accelerator Heterogeneity                     | 105 |

|   |      | 4.5.1 Bac    | ground                               | <br> | <br> | 105 |

|---|------|--------------|--------------------------------------|------|------|-----|

|   |      | 4.5.2 Met    | odology and Effectiveness            | <br> | <br> | 106 |

|   | 4.6  | Verification | and Comparisons                      | <br> | <br> | 108 |

|   |      | 4.6.1 Veri   | ication on Commodity FPGA            | <br> | <br> | 108 |

|   |      | 4.6.2 Com    | parison with Prior Work              | <br> | <br> | 109 |

|   | 4.7  | Conclusion   | nd Future Work                       | <br> | <br> | 109 |

| 5 | Data | Reuse Opti   | nization for Stencil Access Patterns | <br> | <br> | 112 |

|   | 5.1  | -            |                                      |      |      |     |

|   | 5.2  |              |                                      |      |      |     |

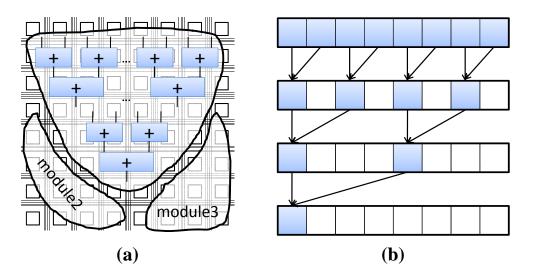

|   |      | 2            | cil Computation                      |      |      |     |

|   |      |              | oarchitecture for Stencil Accesses   |      |      |     |

|   |      |              | gn Objectives                        |      |      |     |

|   |      |              | hedral Model                         |      |      |     |

|   | 5.3  | -            | /                                    |      |      |     |

|   |      | C            | view                                 |      |      |     |

|   |      |              | otations                             |      |      |     |

|   |      |              | king Principle                       |      |      |     |

|   |      |              | hts Gained From RTL Simulation       |      |      |     |

|   |      |              | r Design Issues                      |      |      |     |

|   |      |              | em Integration                       |      |      |     |

|   |      |              | -                                    |      |      |     |

|   | 5 1  |              | ling Bandwidth/Memory Trade-off      |      |      |     |

|   | 5.4  | -            | mation Flow                          |      |      |     |

|   | 5.5  | Experiments  |                                      | <br> | <br> | 137 |

|    |                                                                               | 5.5.1   | Experiment Setup                        | 137 |  |  |  |  |  |

|----|-------------------------------------------------------------------------------|---------|-----------------------------------------|-----|--|--|--|--|--|

|    |                                                                               | 5.5.2   | Results                                 | 138 |  |  |  |  |  |

|    | 5.6                                                                           | Conclu  | sions and Future Work                   | 140 |  |  |  |  |  |

| 6  | 6 Computation and Communication Optimization in Convolutional Neural Networks |         |                                         |     |  |  |  |  |  |

| fo | r Big I                                                                       | Data .  |                                         | 142 |  |  |  |  |  |

|    | 6.1                                                                           | Introdu | action                                  | 142 |  |  |  |  |  |

|    | 6.2                                                                           | Backg   | round                                   | 143 |  |  |  |  |  |

|    |                                                                               | 6.2.1   | Algorithm Review of CNNs                | 143 |  |  |  |  |  |

|    |                                                                               | 6.2.2   | Architecture of Real-Life CNN           | 145 |  |  |  |  |  |

|    |                                                                               | 6.2.3   | Runtime Breakdown of Real-Life CNN      | 146 |  |  |  |  |  |

|    | 6.3                                                                           | Proper  | ties of CNN Computation                 | 146 |  |  |  |  |  |

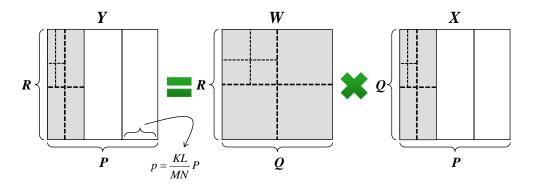

|    |                                                                               | 6.3.1   | Another View of CNN Computation         | 146 |  |  |  |  |  |

|    |                                                                               | 6.3.2   | Enabling New Optimization Opportunities | 148 |  |  |  |  |  |

|    |                                                                               | 6.3.3   | Properties of Convolutional MM          | 148 |  |  |  |  |  |

|    | 6.4                                                                           | Compu   | utation Optimization                    | 149 |  |  |  |  |  |

|    |                                                                               | 6.4.1   | Algorithm                               | 149 |  |  |  |  |  |

|    |                                                                               | 6.4.2   | Experimental Results                    | 151 |  |  |  |  |  |

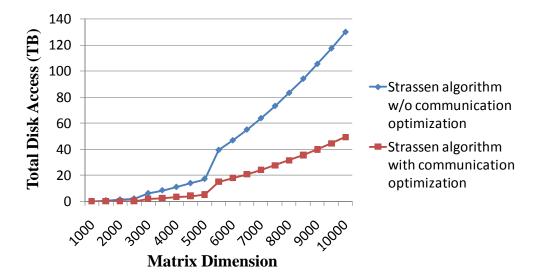

|    | 6.5                                                                           | Comm    | unication Optimization                  | 153 |  |  |  |  |  |

|    |                                                                               | 6.5.1   | Algorithm                               | 153 |  |  |  |  |  |

|    |                                                                               | 6.5.2   | Experimental Results                    | 156 |  |  |  |  |  |

|    |                                                                               | 6.5.3   | Combining with Strassen Algorithm       | 156 |  |  |  |  |  |

|    | 6.6                                                                           | Conclu  | usion                                   | 158 |  |  |  |  |  |

|    |                                                                               |         |                                         |     |  |  |  |  |  |

### 7 Accelerator-Centric Cluster Computing with Communication Optimization . . . . 160

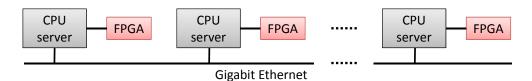

| 7.1 | Introd                      | uction                                         |  |  |  |  |  |

|-----|-----------------------------|------------------------------------------------|--|--|--|--|--|

| 7.2 | MapReduce System with FPGAs |                                                |  |  |  |  |  |

|     | 7.2.1                       | Choice of Accelerators                         |  |  |  |  |  |

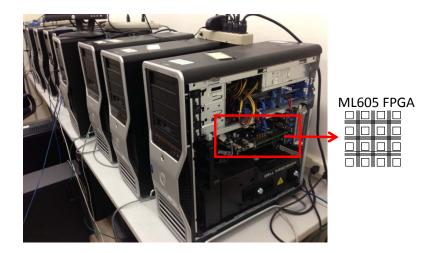

|     | 7.2.2                       | Target Cluster Architecture    165             |  |  |  |  |  |

|     | 7.2.3                       | Execution Flow Overview                        |  |  |  |  |  |

|     | 7.2.4                       | FPGA Management                                |  |  |  |  |  |

| 7.3 | Comm                        | nunication Optimization in Cluster Computing   |  |  |  |  |  |

|     | 7.3.1                       | Application Analysis                           |  |  |  |  |  |

|     | 7.3.2                       | Reducing Inter-Node Communication              |  |  |  |  |  |

|     | 7.3.3                       | Reducing File Accesses                         |  |  |  |  |  |

|     | 7.3.4                       | Reducing Data Transfers between CPUs and FPGAs |  |  |  |  |  |

| 7.4 | Prototy                     | yping and Experiments                          |  |  |  |  |  |

|     | 7.4.1                       | Prototyping Setup                              |  |  |  |  |  |

|     | 7.4.2                       | System Validation                              |  |  |  |  |  |

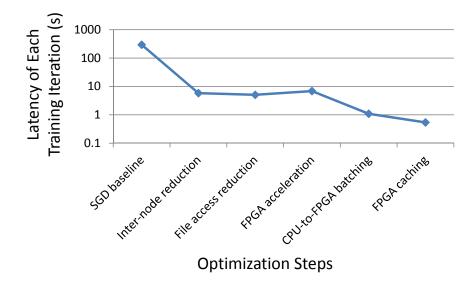

|     | 7.4.3                       | Communication Optimization Breakdown           |  |  |  |  |  |

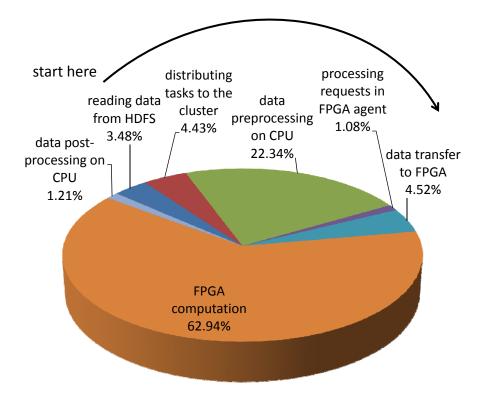

|     | 7.4.4                       | Runtime Breakdown                              |  |  |  |  |  |

|     | 7.4.5                       | Resource Management for Multiple Jobs          |  |  |  |  |  |

|     | 7.4.6                       | System Scalability                             |  |  |  |  |  |

| 7.5 | Conclu                      | usions                                         |  |  |  |  |  |

| Sum | imary a                     | nd Concluding Remarks                          |  |  |  |  |  |

| 8.1 | Techno                      | blogy Summary                                  |  |  |  |  |  |

| 8.2 | Accun                       | nulative Impact                                |  |  |  |  |  |

| 8.3 | Desigr                      | Automation Tools                               |  |  |  |  |  |

8

| 8.4     | Open Issues | <br> | <br> | ••••• |     |

|---------|-------------|------|------|-------|-----|

| Referen | ces         | <br> | <br> |       | 192 |

### LIST OF FIGURES

| 1.1 | Customizable heterogeneous platform for domain-specific computing                                                                                                                                                                                 | 2  |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2 | Rough energy costs for various operations in 45nm 0.9V, adopted from [1]                                                                                                                                                                          | 3  |

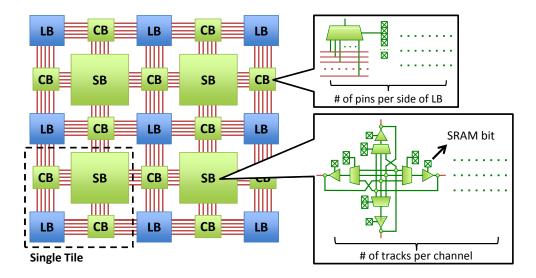

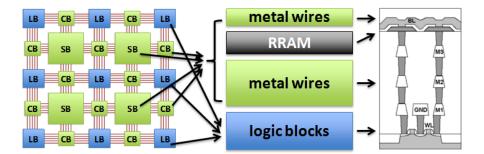

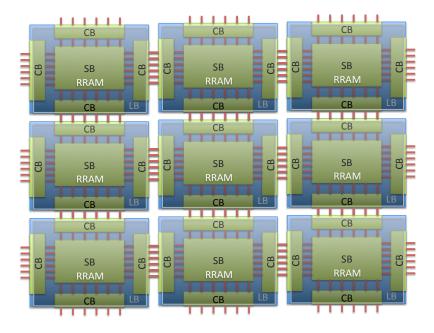

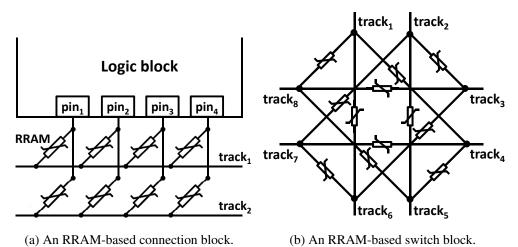

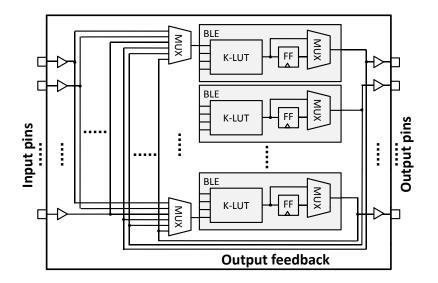

| 2.1 | A typical FPGA architecture. LB = logic block (or CLB). CB = connection block.<br>SB = switch block.                                                                                                                                              | 18 |

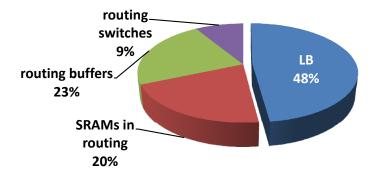

| 2.2 | Area breakdown of different components in an FPGA based on an architectural model [2] that mimics the Xilinx Virtex7 FPGAs [3]. All three components (SRAM bits, routing switches and routing buffers) take up significant area in programmable   |    |

|     | interconnects.                                                                                                                                                                                                                                    | 19 |

| 2.3 | FPGA with emerging nonvolatile memories.                                                                                                                                                                                                          | 20 |

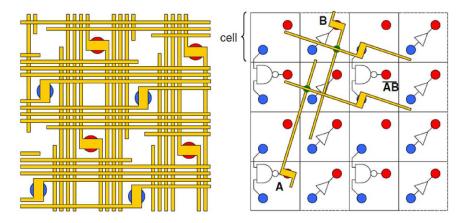

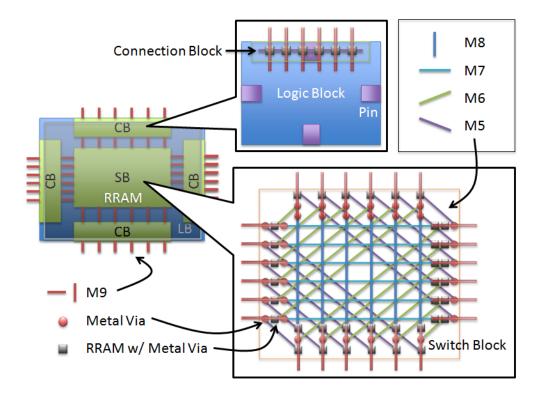

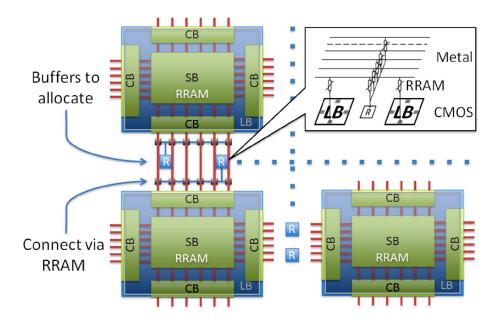

| 2.4 | In FPGA-RPI, switch blocks and connection blocks in transistor-less programmable interconnects are placed over logic blocks in the same die according to existing RRAM fabrication structures [4, 5, 6, 7].                                       | 24 |

| 2.5 | Overview of FPGA-RPI where the FPGA area is mainly contributed by logic blocks instead of programmable interconnects.                                                                                                                             | 25 |

| 2.6 | Circuit schematics of transistor-less programmable interconnects                                                                                                                                                                                  | 25 |

| 2.7 | An RRAM-friendly layout design of the programmable interconnects in FPGA-<br>RPI using the RRAM fabrication structure shown in Fig. 2.4. Here, each metal via<br>(marked as a red point) at the intersection between wires of M9 and M5–M8 refers |    |

|     | to a vertical connection between them through metal via(s). $\ldots$                                                                                                                                                                              | 26 |

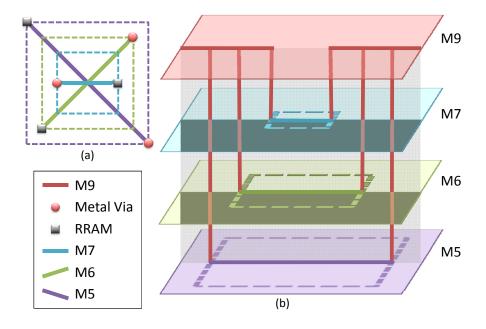

| An illustration of how via blockages are avoided by metal wires in our layout       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| design of switch blocks. (a) An abstract structure of FPGA-RPI switch blocks        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| (M9 and M8 are omitted here for clarity). (b) 3D view to show how via blockages     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| are avoided by metal wires. The RRAM layer is omitted here for clarity. For         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| demonstration purposes, vertical connections are bounded in a plane to construct    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| the case most challenging for via blockage avoidance.                               | 27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

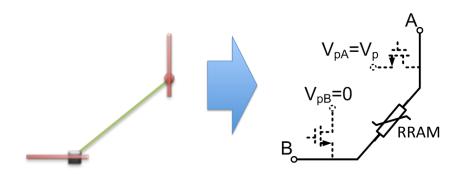

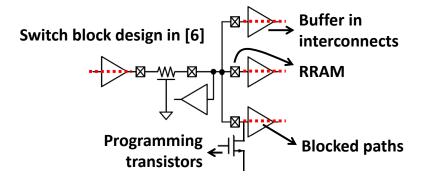

| Programming circuits for RRAMs in interconnects. The two programming transis-       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| tors will apply programming voltages to program the RRAM between them. $V_p$ is     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| the threshold voltage that switches the RRAM state.                                 | 29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| In an existing work [8], sharing paths are blocked by transistors (marked as dotted |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| lines).                                                                             | 30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

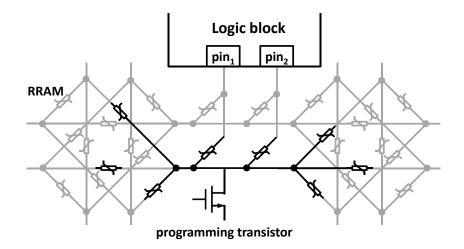

| In our work, one programming transistor can be shared by RRAMs among switch         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| blocks and connection blocks.                                                       | 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

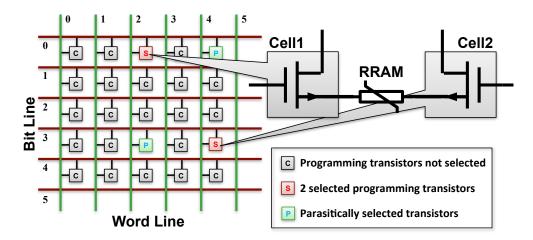

| Row/column addressing for the programming transistor array of RRAMs in inter-       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| connects. If two programming transistors in one array are selected simultaneously,  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| two other transistors will be selected parasitically                                | 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

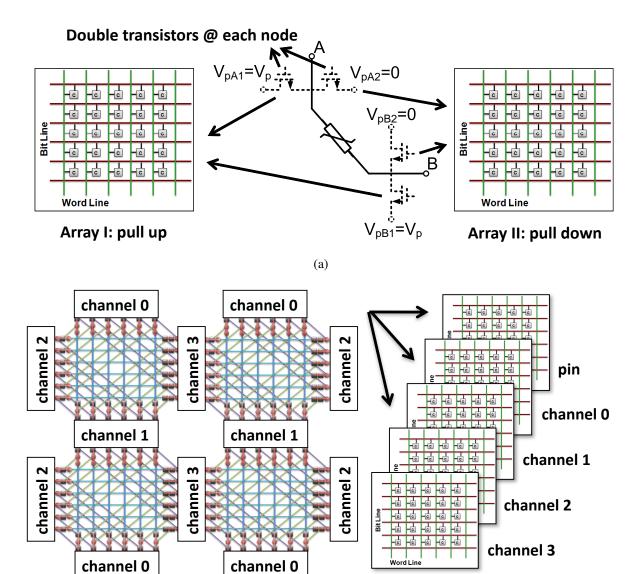

| Two solutions to solve parasitic selection: (a) double programming transistors at   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| each programming node, and (b) partition programming transistors into five banks,   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| where the two programming transistors at the terminals of any arbitrary RRAM lie    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| in two different banks.                                                             | 34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

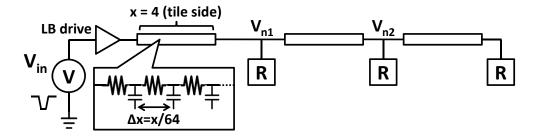

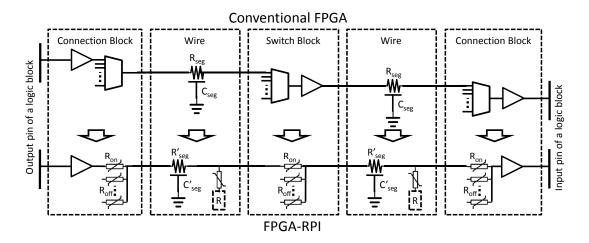

| The circuit structure and layout of the on-demand buffering architecture in our     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| FPGA-RPI. R = repeater.                                                             | 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

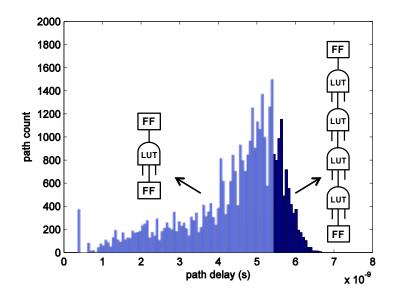

| Delay distribution of all paths in a typical application for mapping onto FPGA.     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Most paths can be relaxed for less use of buffers.                                  | 37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                                     | design of switch blocks. (a) An abstract structure of FPGA-RPI switch blocks (M9 and M8 are omitted here for clarity). (b) 3D view to show how via blockages are avoided by metal wires. The RRAM layer is omitted here for clarity. For demonstration purposes, vertical connections are bounded in a plane to construct the case most challenging for via blockage avoidance Programming circuits for RRAMs in interconnects. The two programming transistors will apply programming voltages to program the RRAM between them. $V_p$ is the threshold voltage that switches the RRAM state |

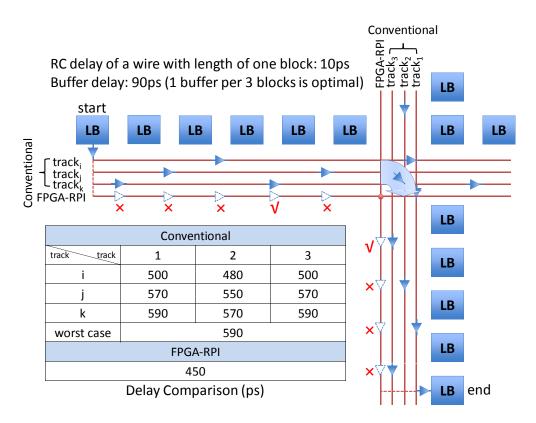

| 2.16 | Performance comparison between the fixed buffer patten in conventional FPGAs            |    |

|------|-----------------------------------------------------------------------------------------|----|

|      | and the on-demand buffering architecture in FPGA-RPI. To simplify, only three           |    |

|      | routings tracks per channel are shown for the conventional FPGA, and one track is       |    |

|      | shown for our FPGA-RPI. Note that the buffers in FPGA-RPI are also shared by            |    |

|      | other tracks in the same channel (not shown here but discussed in Section 2.3.5.1).     |    |

|      | $\checkmark$ = buffer allocated. $\checkmark$ = not allocated                           | 38 |

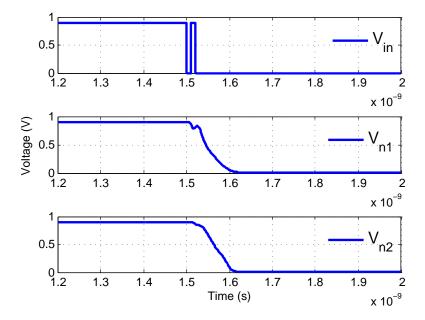

| 2.17 | Illustration of glitch elimination. Glitches $< 0.5t_d$ are filtered out by the RC net- |    |

|      | work of wire segments before regenerative feedback repeaters. Our on-demand             |    |

|      | buffering architecture always guarantee sufficient RC delay of wires for this filter-   |    |

|      | ing                                                                                     | 40 |

| 2.18 | SPICE simulation results of the scenario in Fig. 2.17. Simulation settings can be       |    |

|      | found in Section 2.5.1. Wire segments are modeled as a distributed RC network.          | 40 |

| 2.19 | Customized CAD flow for FPGA-RPI. An enhanced P&R tools is developed for                |    |

|      | FPGA-RPI                                                                                | 41 |

| 2.20 | Extracted equivalent circuit model of the FPGA-RPI routing structure and compar-        |    |

|      | ison with a conventional FPGA.                                                          | 42 |

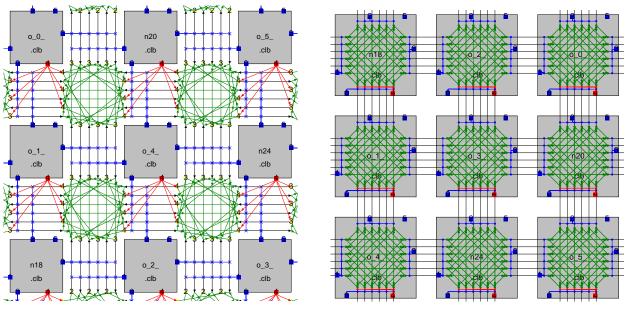

| 2.21 | Overview of the two tools, VPR and VPR-RPI                                              | 45 |

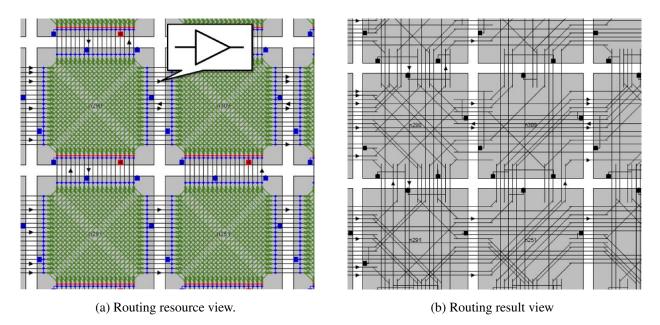

| 2.22 | View of the buffer allocation result generated by VPR-RPI                               | 46 |

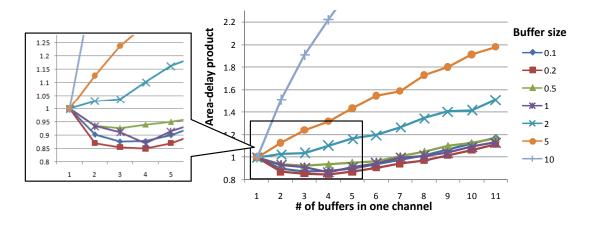

| 2.23 | Exploration of the impact of buffer sizing and richness on the area-delay product.      |    |

|      | Buffer sizes and area-delay products are normalized.                                    | 48 |

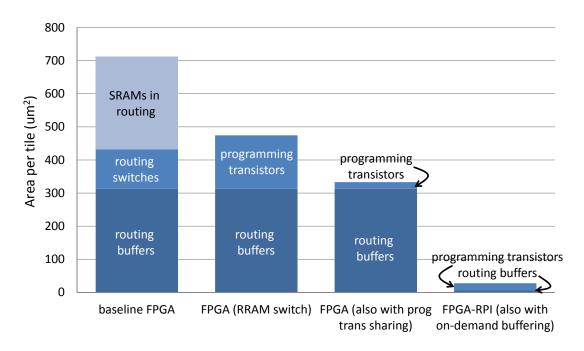

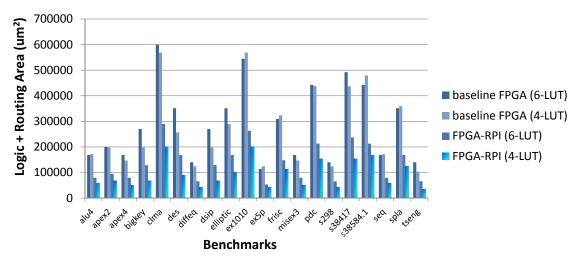

| 2.24 | Area comparison of programmable interconnects in a single tile                          | 49 |

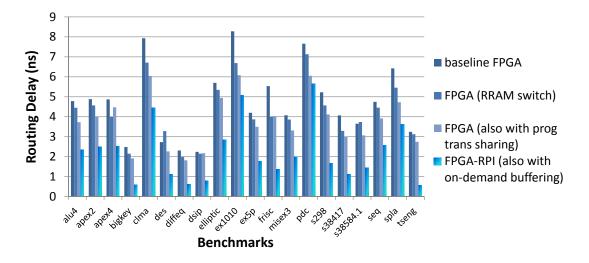

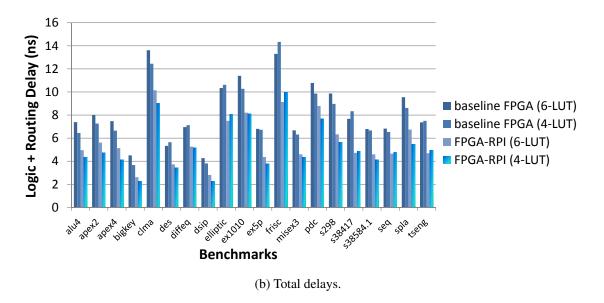

| 2.25 | Comparison of the delays contributed by programmable interconnects in critical          |    |

|      | paths in FPGAs over benchmarks.                                                         | 50 |

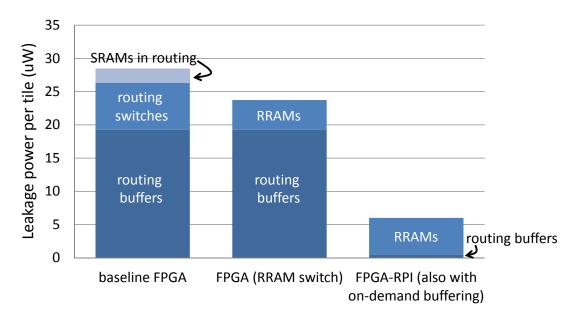

| 2.26 | Comparison of the leakage powers contributed by programmable interconnects in           |    |

|      | a single tile.                                                                          | 51 |

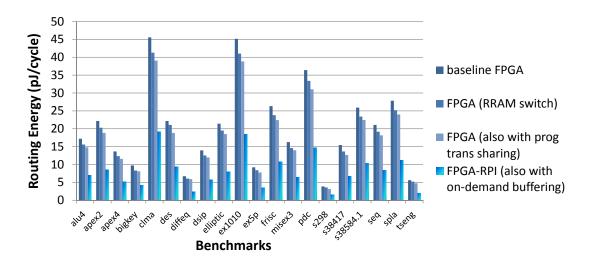

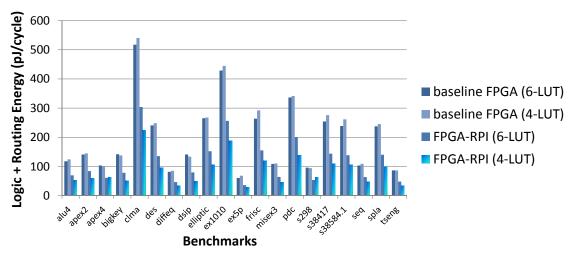

| 2.27 | Comparison of the dynamic powers contributed by programmable interconnects                      |    |

|------|-------------------------------------------------------------------------------------------------|----|

|      | in FPGAs over benchmarks. To separate the impact of the clock period from the                   |    |

|      | dynamic powers, we use pJ/cycle as the metric.                                                  | 51 |

| 2.28 | Comparisons of FPGA architectures with more complicated LBs and simpler LBs.                    | 53 |

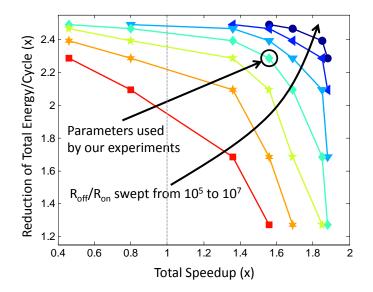

| 2.29 | Sensitivity analysis of the RRAMs on/off ratio for FPGA-RPI. Each line corre-                   |    |

|      | sponds with a fixed on/off ratio. There is a tradeoff between delay and power                   |    |

|      | savings on each line.                                                                           | 54 |

| 2.30 | The internal structure of a state-of-art LB described in [2]                                    | 55 |

| 2.31 | Area comparison of a single tile in an FPGA. The white parts belong to LBs. Each                |    |

|      | LB contains eight 6-LUTs. The number of LB inputs is 27, optimized by design                    |    |

|      | experience in [9]                                                                               | 55 |

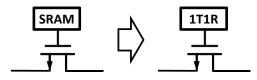

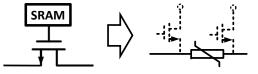

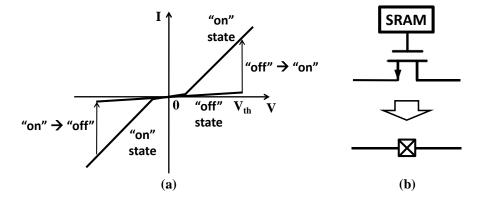

| 3.1  | Illustration of nanodevices. (a) Hysteresis characteristic of a two-terminal RRAM               |    |

|      | nanodevice. (b) Function as a routing switch in place of a pass transistor and its              |    |

|      | six-transistor SRAM cell.                                                                       | 57 |

| 3.2  | Illustration of stuck-open and stuck-closed defects of nanodevice-based routing                 |    |

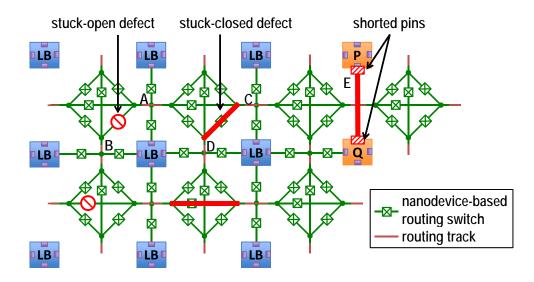

|      | switches in programmable interconnects. LB $\Rightarrow$ logic block                            | 61 |

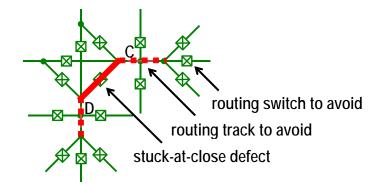

| 3.3  | Solve a stuck-closed defect by simple defect avoidance. All of the 15 switches                  |    |

|      | shown in this figure need to be discarded due to a single stuck-closed switch                   | 61 |

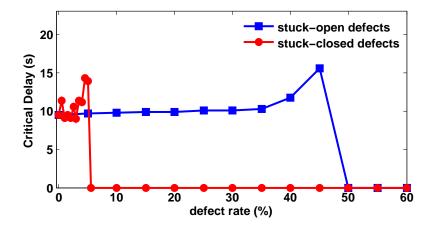

| 3.4  | Impact comparison of the stuck-open and stuck-closed defects on routability. De-                |    |

|      | lay going down to zero $\Rightarrow$ unroutable. $\sim$ 10x gap observed between the impacts of |    |

|      | the two defect types.                                                                           | 63 |

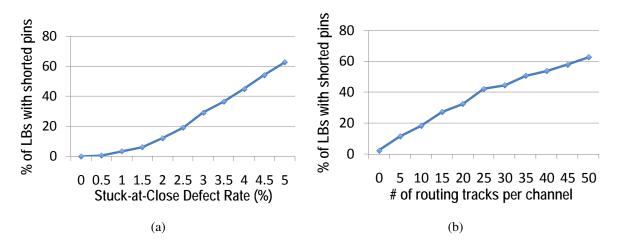

| 3.5  | The number of logic blocks (LBs) with shorted pins over different stuck-closed                  |    |

|      | defect rates and numbers of routing tracks in channel                                           | 64 |

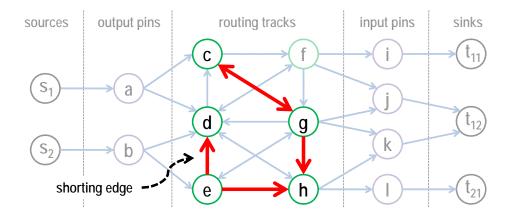

| 3.6  | Example of a routing graph with shorting constraints. Bold red arrows indicate                |    |

|------|-----------------------------------------------------------------------------------------------|----|

|      | shorting edges. Nodes $\{c,d,e,g,h\}$ shorted by the shorting edges form an electri-          |    |

|      | cally shorted cluster (ES-cluster) as highlighted.                                            | 65 |

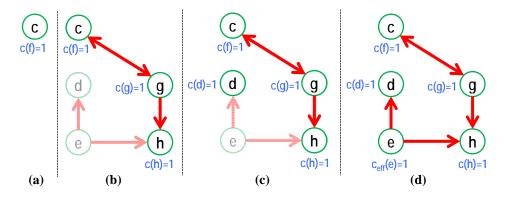

| 3.7  | Our extension of the congestion concept for routing under shorting constraints.               |    |

|      | (a) Add node c to a routing tree. (b) Recursively add all the successor nodes and             |    |

|      | increase congestions. (c) Add node d to another routing tree. (d) Replace the                 |    |

|      | congestion cost with the effective cost for precedent nodes, e.g., node e                     | 66 |

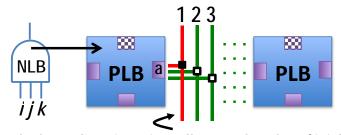

| 3.8  | Example of fast pruning of invalid routing solutions. Any routing solution that               |    |

|      | maps track 1 to the net in set $\overline{\{i, j, k\}}$ can be pruned ahead of time           | 67 |

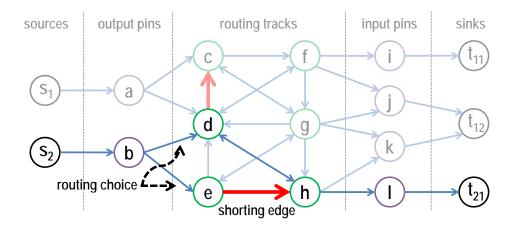

| 3.9  | To route a net from $s_2$ to $t_{21}$ , there exist two shortest paths—one via node d and the |    |

|      | other via node e as highlighted. We guide the router to route via node e for better           |    |

|      | utilization of resources.                                                                     | 68 |

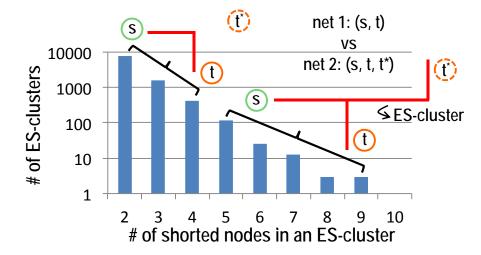

| 3.10 | A distribution of ES-clusters with different sizes in a defective nanodevice-based            |    |

|      | FPGA. Along with it is an example of the different potentials of small ES-clusters            |    |

|      | and large ES-clusters exposed to the same nets.                                               | 69 |

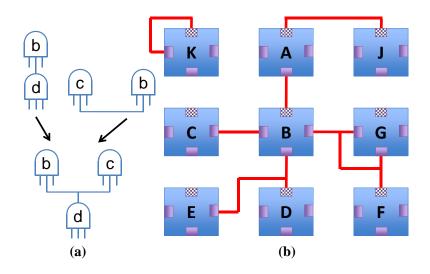

| 3.11 | Example of the challenge in the placement of logic blocks with shorted pins. (a)              |    |

|      | A netlist. (b) Logic blocks with shorted pins (checked pad $\Rightarrow$ output pin). Though  |    |

|      | the connections of (b,d) and (b,c) in the netlist match the shorted pins of (B,D) and         |    |

|      | (B,C) respectively, the connection of (b,c,d) does not match (B,C,D) but matches              |    |

|      | (B,E,D)                                                                                       | 74 |

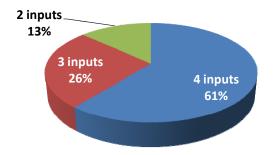

| 3.12 | Distribution of logic blocks over different numbers of used inputs in a netlist after         |    |

|      | logic synthesis. Logic synthesis is performed by the Berkeley ABC tool [10] using             |    |

|      | a 4-LUT FPGA library. Pins are not fully utilized in many logic blocks                        | 74 |

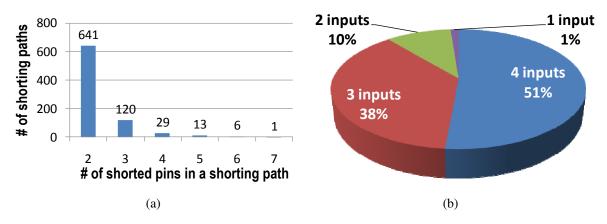

| 3.13 | (a) Count of ES-clusters over different numbers of shorted pins. (b) Distribution             |    |

|      | of physical logic blocks (PLBs) over different numbers of active inputs (i.e., not            |    |

|      | disabled) after pin disabling.                                                                | 75 |

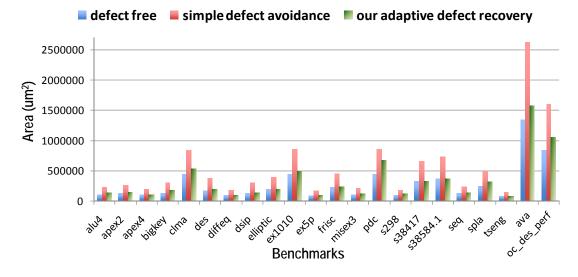

| 3.14 | Area usage of benchmarks after placement.                                             | 80 |

|------|---------------------------------------------------------------------------------------|----|

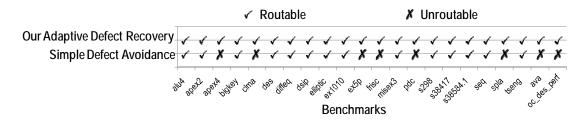

| 3.15 | Routability of benchmarks using simple defect avoidance and our adaptive defect       |    |

|      | recovery                                                                              | 80 |

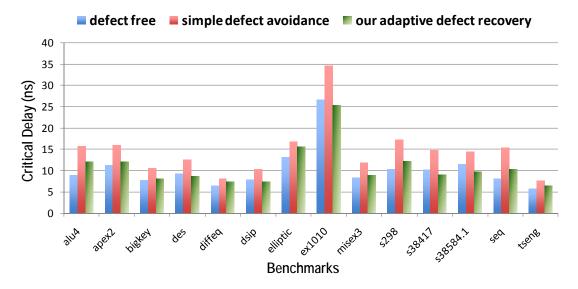

| 3.16 | Critical delay of benchmarks after routing.                                           | 81 |

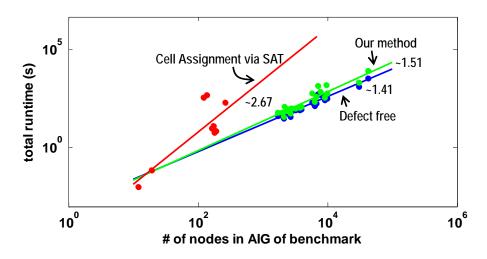

| 3.17 | A comparison of runtime complexity. The scales of benchmarks are evaluated as         |    |

|      | the number of nodes in the form of an and-inverter graph (AIG) of benchmarks          | 82 |

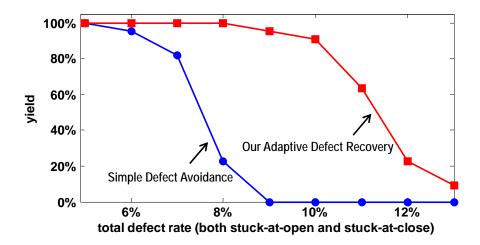

| 3.18 | Yield comparison over multiple defect rates.                                          | 82 |

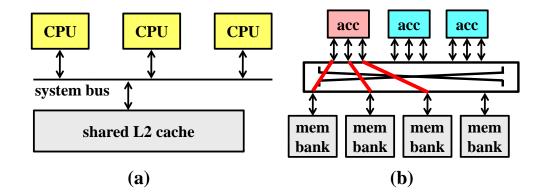

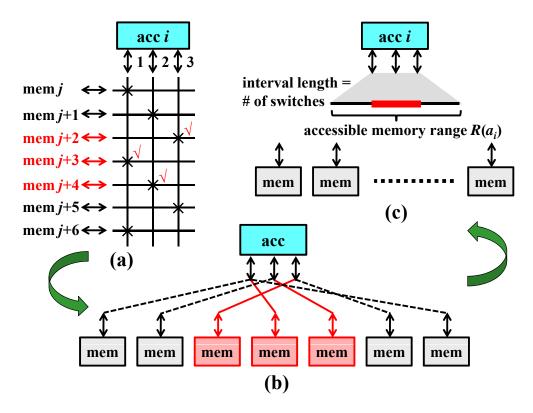

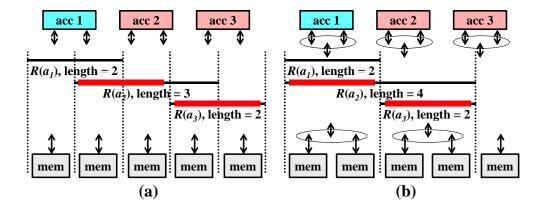

| 4.1  | Difference between memory sharing among general-purpose CPU cores and among           |    |

|      | accelerators. (a) A simple interconnect for CPU cores. (b) Demanding intercon-        |    |

|      | nects for accelerators.                                                               | 86 |

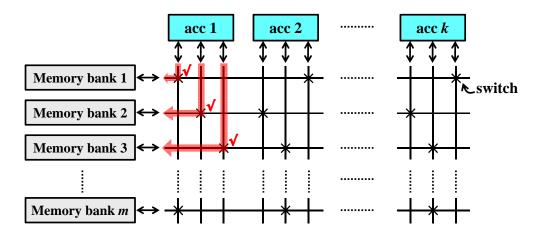

| 4.2  | Interconnects designed as a configurable crossbar between accelerators and shared     |    |

|      | memories to keep data access cost small. $\checkmark$ : switch turned on              | 88 |

| 4.3  | As the multiple ports of the same accelerator are powered on/off together, it is not  |    |

|      | necessary to provide switches to connect them to the same memory banks. Dashed        |    |

|      | switches with (x,y) coordinates (1,1), (2,1), (4,2), (6,3), (5,4) can be removed.     |    |

|      | This shows the different impact of ports from the same accelerator and those from     |    |

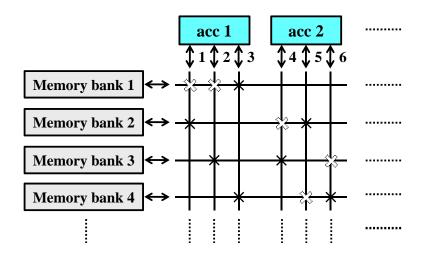

|      | different accelerators on the crossbar design.                                        | 90 |

| 4.4  | Our design with interleaving connections between an accelerator and its accessible    |    |

|      | memory range. (a) Switch positions in the sub-crossbar of the accelerator. (b)        |    |

|      | Connectivity graph. Any three continuous memory banks can be routed to the three      |    |

|      | data ports of the accelerator via separate paths. (c) Our interconnect optimization   |    |

|      | within the single accelerator can be virtualized as an interval (i.e., its accessible |    |

|      | memory range) in which any segment with length of 3 (memory banks) can be             |    |

|      | routed to the accelerator.                                                            | 92 |

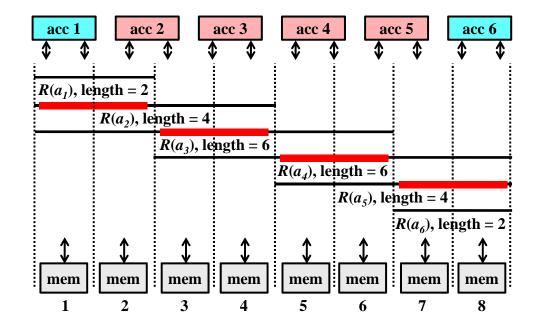

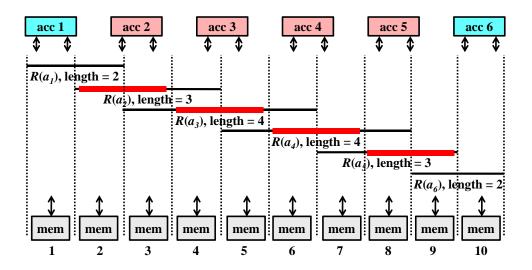

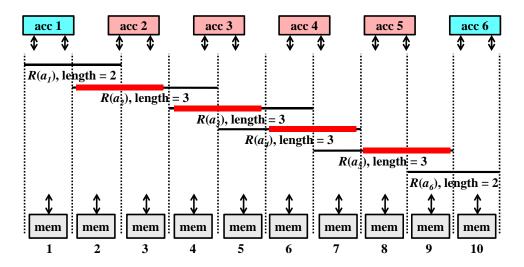

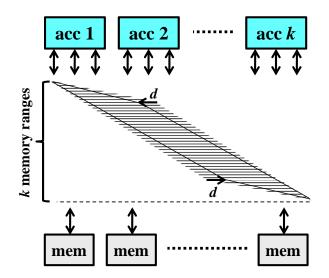

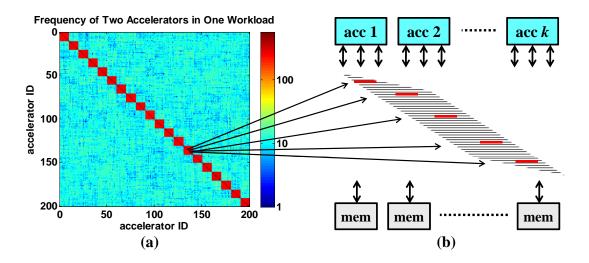

- 4.5 The interface for global optimization among accelerators. (a) Global optimization only needs to consider the lengths and positions of accessible memory ranges of accelerators to reduce the total number of switches while keeping a high probability of finding segments without overlaps. (b) If the multiple data ports of an accelerator are grouped into a larger multi-channel port to converge the interconnect design to the CPU scenario, we will lose a large design space and get an inefficient design. 93

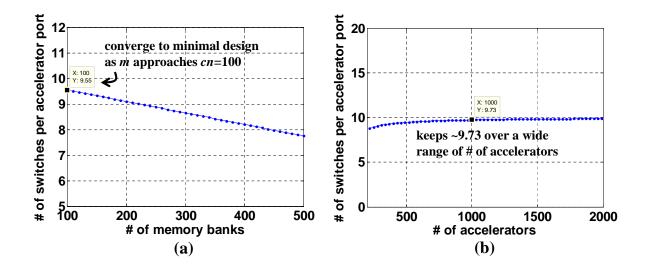

- 4.8 The average number of switches per accelerator port in crossbars generated by Algorithm 6. In this experiment, we initially set k = 200, n = 10, c = 10, and m = 300. (a) Sweep m from 100 to 500. (b) Sweep k from 200 to 2,000. . . . . . 100

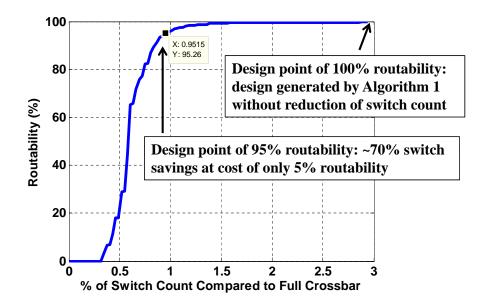

- 4.9 Removal of two switches from Fig. 4.7 to sacrifice routability for switch savings.

In this design, the accelerators 2–5 can still be routed to shared memories after switch removal. Out of all the C<sub>6</sub><sup>4</sup> = 15 possible combinations of four accelerators powered on, only the accelerator set {1, 2, 3, 4} and {3, 4, 5, 6} cannot be routed. 103

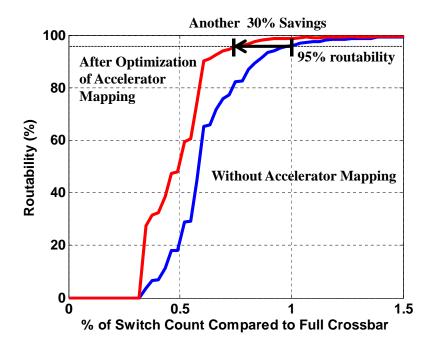

| 4.11 | Experimental results on routability after reduction of switch count. In this experi- |       |

|------|--------------------------------------------------------------------------------------|-------|

|      | ment, $k = 200, n = 10, c = 10$ , and $m = 300$                                      | . 104 |

| 4.12 | Optimization opportunities brought by accelerator heterogeneity. (a) Execution       |       |

|      | correlations among heterogeneous accelerators. Accelerators within the same ap-      |       |

|      | plication domain have a higher probability of being powered on or off together.      |       |

|      | (b) We can scatter the accelerators within the same application domain throughout    |       |

|      | the shared memories so that they have fewer overlaps in their accessible memory      |       |

|      | range and will be easier to route.                                                   | . 106 |

| 4.13 | 30% reduction of switch count at 95% routability after optimization of accelerator   |       |

|      | mapping based on accelerator heterogeneity.                                          | . 107 |

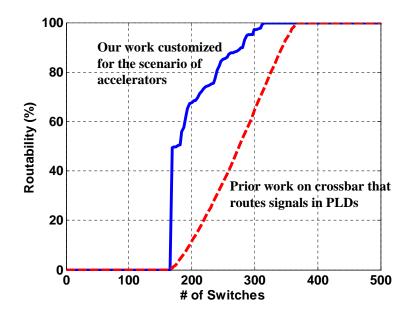

| 4.14 | Comparison of our crossbar design with the design in [11]. Our crossbar design       |       |

|      | outperforms the work in [11] since the work in [11] performs optimization for        |       |

|      | general-purpose signal routing; our crossbar design fully exploits the optimization  |       |

|      | opportunities that emerge in accelerator-rich computing platforms as identified in   |       |

|      | this work.                                                                           | . 110 |

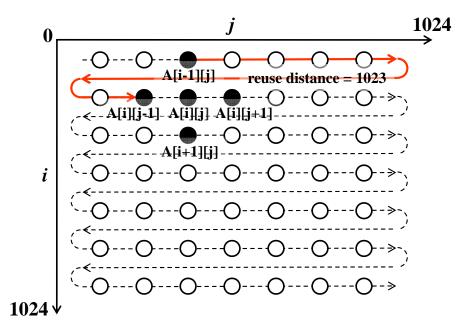

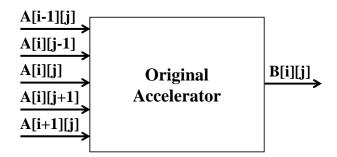

| 5.1  | Iteration domain of the example stencil computation in Listing 5.1                   | . 115 |

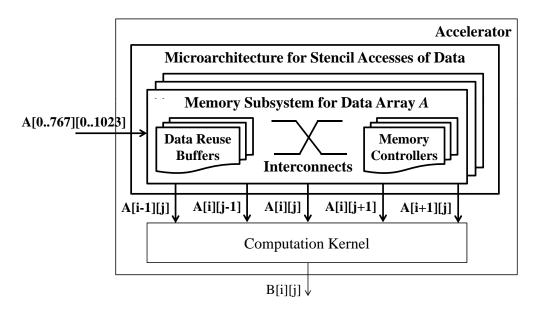

| 5.2  | The overall architecture of our microarchitecture for stencil computation. It de-    |       |

|      | couples stencil accesses from computation.                                           | . 116 |

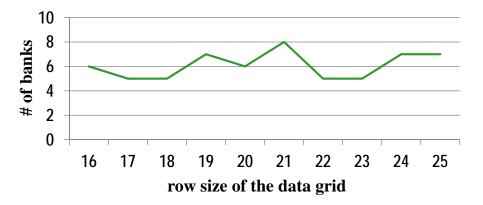

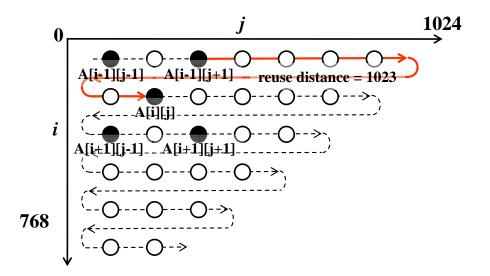

| 5.3  | Even for a constant stencil window in Fig. 5.1, the number of banks varies as the    |       |

|      | row size of the data grid changes [12].                                              | . 118 |

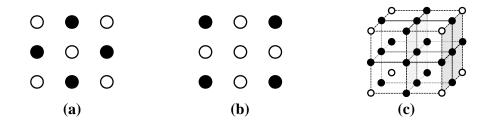

| 5.4  | Example stencil windows where more banks are needed than the # of array ref-         |       |

|      | erences in [13, 14]. (a) 4-point stencil in 'BICUBIC' [15]. (b) 4-point stencil in   |       |

|      | 'RICIAN' [16]. (c) 19-point stencil in 'SEGMENTATION_3D' [14]                        | . 119 |

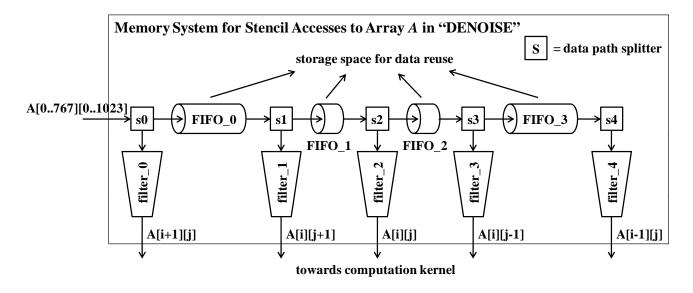

| 5.5  | The example circuit structure of our memory system generated for array $A$ in the    |       |

|      | stencil computation of Listing 5.1                                                   | . 123 |

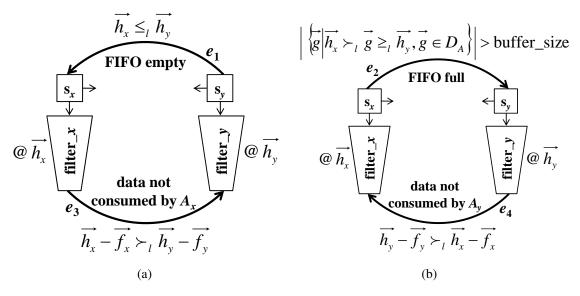

| 5.6  | The dependency graph of data filters 'filter_x' and 'filter_y' where $x < y$ , with       |

|------|-------------------------------------------------------------------------------------------|

|      | polyhedral expressions of dependency relations appended                                   |

| 5.7  | Non-rectangular iteration domain of an example application with dynamically change-       |

|      | able reuse distance                                                                       |

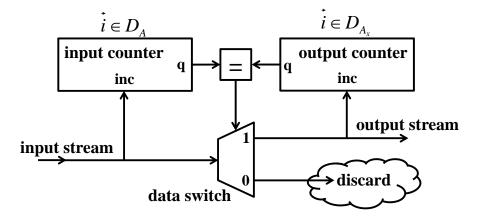

| 5.8  | Structure of the data filter which can be applied to general polyhedral data domains. 132 |

| 5.9  | Integration of an accelerator with our microarchitecture in a system                      |

| 5.10 | Breaking the chain at the largest reuse buffer when the number of off-chip accesses       |

|      | is increased. (a) An example of the original microarchitecture with one off-chip          |

|      | access per cycle. (b) The new microarchitecture with two off-chip accesses per            |

|      | cycle, but smaller total buffer size                                                      |

| 5.11 | Graceful degradation of on-chip memory usage with the increase of off-chip band-          |

|      | width for (a) the example in Fig. 5.10, and (b) the 19-point stencil in SEGMEN-           |

|      | TATION in Fig. 5.4(c)                                                                     |

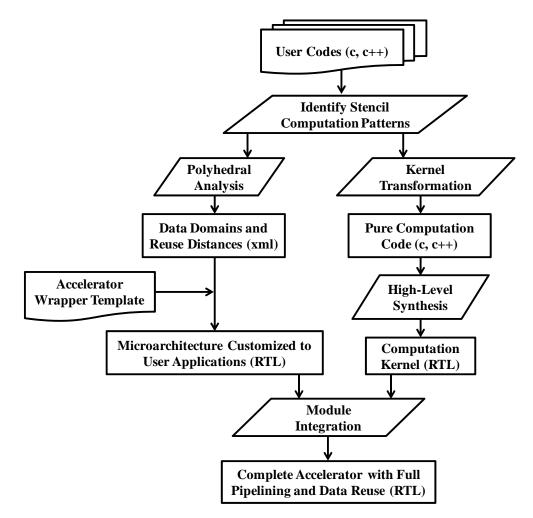

| 5.12 | Design automation flow of accelerator generation for stencil computation 136              |

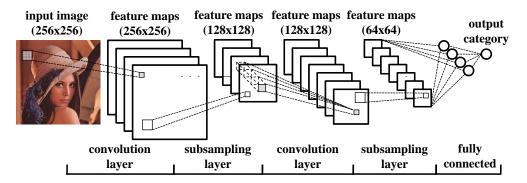

| 6.1  | An example of a convolutional neural network                                              |

| 6.2  | Example loop-nest representing the computation in a convolution layer of a CNN 144        |

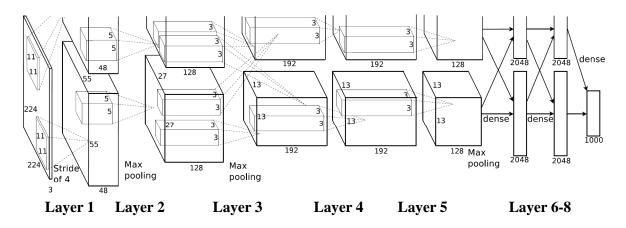

| 6.3  | A real-life CNN that was used in the 2012 ImageNet contest [17]                           |

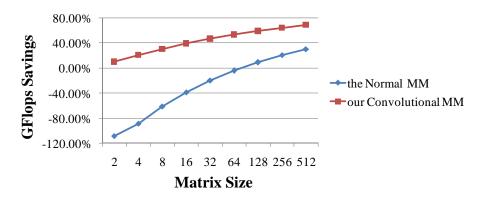

| 6.4  | Comparison of our convolutional MM with the normal MM in terms of the savings             |

|      | of GFLOPS by the Strassen algorithm                                                       |

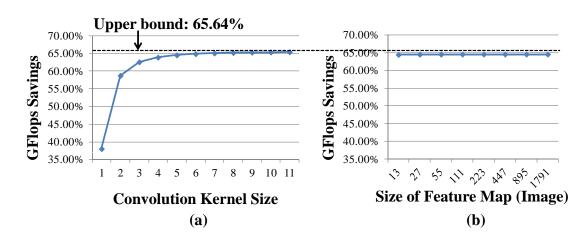

| 6.5  | A sensitivity study on convolution kernel size and feature map size                       |

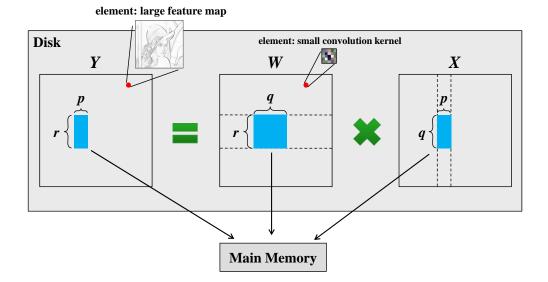

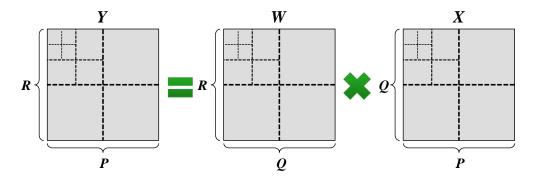

| 6.6  | Partitioning of large matrices into smaller data blocks that can be loaded in the         |

|      | main memory for computation                                                               |

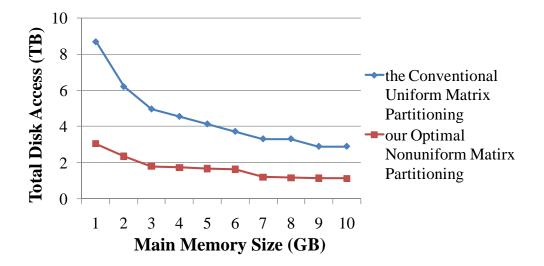

| 6.7  | A comparison of disk accesses using the conventional uniform matrix partitioning          |

|      | and our optimal nonuniform matrix partitioning for CNNs                                   |

| 6.8  | The Strassen algorithm before communication optimization. The different dashed       |

|------|--------------------------------------------------------------------------------------|

|      | lines indicate the matrix partitioning af the different levels of the recursions 157 |

| 6.9  | The Strassen algorithm after our communication optimization. The solid lines         |

|      | indicate the matrix partitioning to optimize the ratio of matrix sizes               |

| 6.10 | A comparison of disk accesses using the Strassen algorithm with and without com-     |

|      | munication optimization                                                              |

| 7.1  | Implementations of the sum of vector elements on (a) an FPGA, and (b) a GPU 164      |

| 7.2  | Our target cluster architecture                                                      |

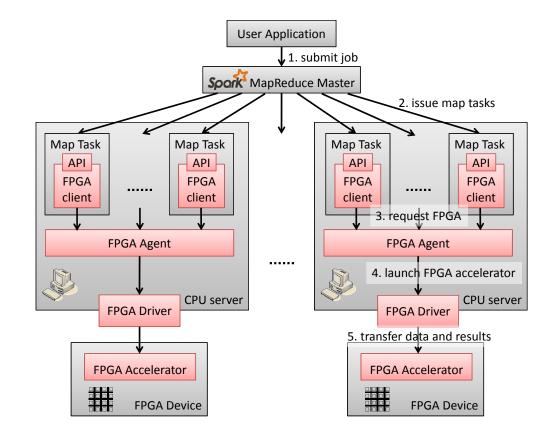

| 7.3  | The overall flow of our MapReduce system with FPGA accelerators                      |

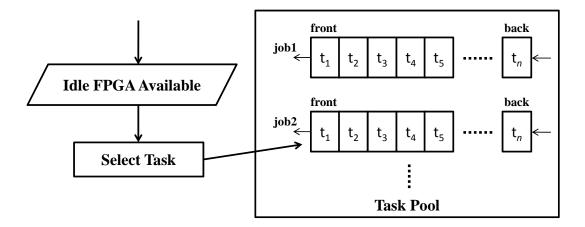

| 7.4  | The task queues maintained in our FPGA agent for resource scheduling 168             |

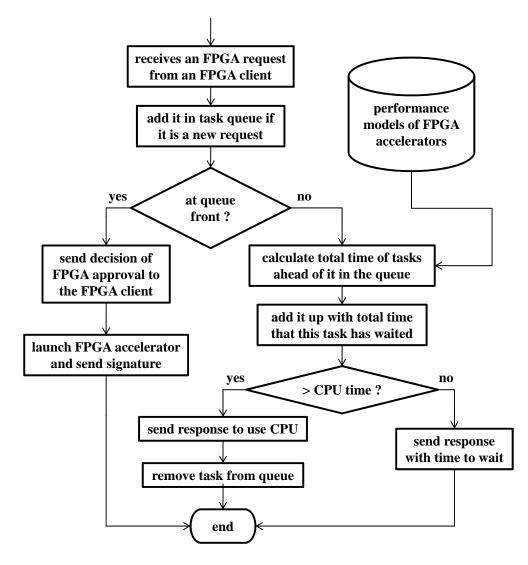

| 7.5  | The flowchart of our FPGA agent to process acceleration requests from FPGA           |

|      | clients                                                                              |

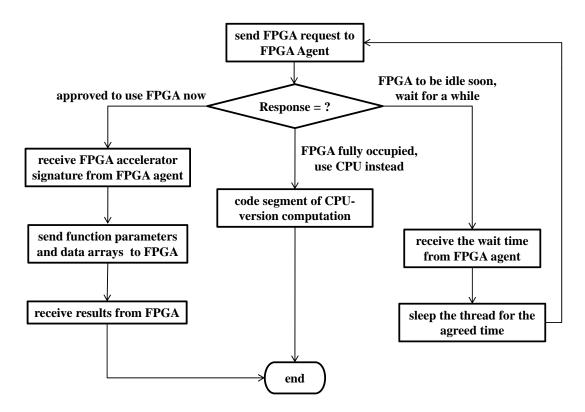

| 7.6  | The flowchart of our FPGA agent to get the computation done as required by the       |

|      | kernel acceleration API called by users                                              |

| 7.7  | A photograph of our cluster with FPGA devices                                        |

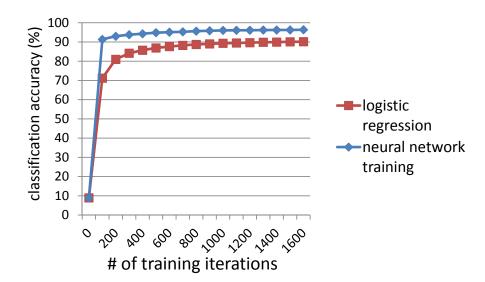

| 7.8  | The classification accuracy during the logistic regression and neural network train- |

|      | ing running on our MapReduce system with FPGA accelerators                           |

| 7.9  | Communication optimization breakdown                                                 |

| 7.10 | Runtime breakdown of an application running on our MapReduce system with             |

|      | FPGA accelerators                                                                    |

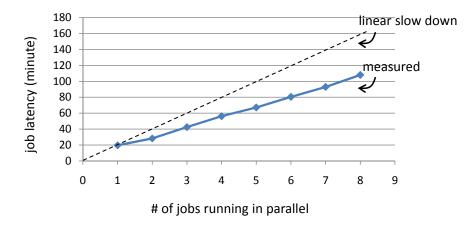

| 7.11 | Latency of each job when we simultaneously run multiple jobs in our MapReduce        |

|      | system with FPGA accelerators                                                        |

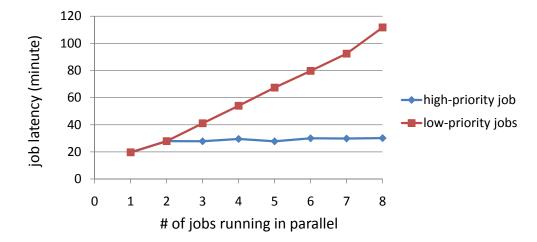

| 7.12 | Latency of each job when we simultaneously run multiple jobs with different pri-     |

|      | orities in our MapReduce system with FPGA accelerators                               |

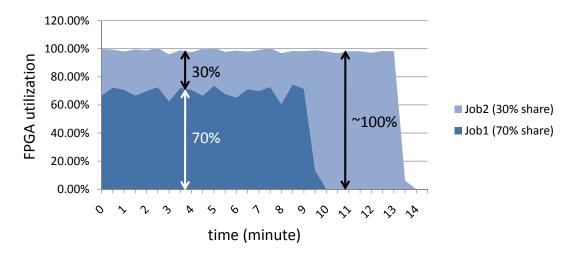

| 7.13 | FPGA utilization of each job when we run parallel jobs in our system              |

|------|-----------------------------------------------------------------------------------|

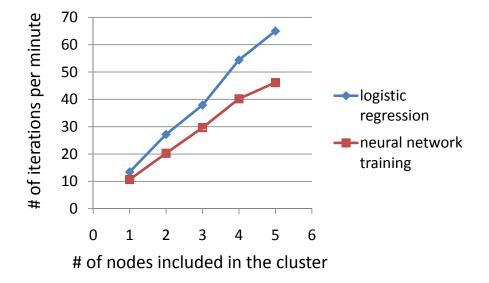

| 7.14 | The performance of our MapReduce system with FPGA accelerators scales with        |

|      | the number of nodes included in the cluster                                       |

|      |                                                                                   |

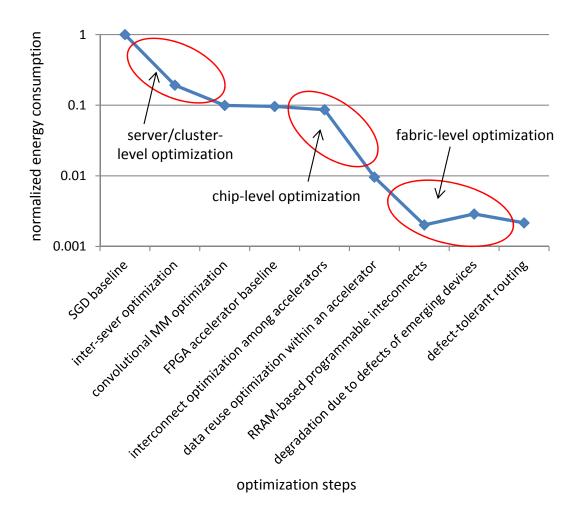

| 8.1  | A generalized case study that can benefit from all the communication optimization |

|      | technologies proposed in this thesis                                              |

| 8.2  | Power measurement of our system                                                   |

| 8.3  | Step-by-step optimization breakdown of the example in Fig. 8.1 by the different   |

|      | technologies proposed in this thesis                                              |

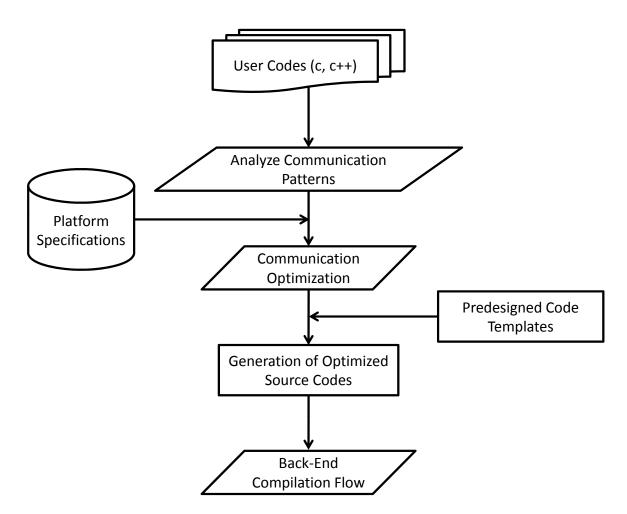

| 8.4  | The general framework of our design automation tools with the integration of com- |

|      | munication optimization                                                           |

### LIST OF TABLES

| 2.1 | Comparison of programming transistor counts in programmable interconnects based   |

|-----|-----------------------------------------------------------------------------------|

|     | on CMOS, the schematic in [8], and this work. $N$ represents the routing channel  |

|     | width. $M$ represents the number of logic block pins accessible by one routing    |

|     | channel                                                                           |

| 3.1 | Denotation of settings for defect impact analysis                                 |

| 3.2 | Denotation table for defect-tolerant routing                                      |

| 4.1 | Comparison of private memories, shared memories via buses [18], and our crossbar  |

|     | in FPGA implementation and testing                                                |

| 5.1 | Denotations used in the working principle of our memory system                    |

| 5.2 | Reuse FIFOs with nonuniform sizes calculated from maximum reuse distances of      |

|     | adjacent array references and mapped to different physical implementations (block |

|     | memory, distributed memory, or register) if targeted an FPGA platform 126         |

| 5.3 | The execution flow of our microarchitecture in the example of Listing 5.1. The    |

|     | latency among the data streams at different modules is ignored here for demon-    |

|     | stration purpose only                                                             |

| 5.4 | High-level partitioning results                                                   |

| 5.5 | Synthesis experimental results                                                    |

| 6.1 | Breakdown of CNN runtime in the recognition of 256 images                         |

| 6.2 | The FLOPS comparison of different operations in the normal MM and our convo-      |

|     | lutional MM                                                                       |

| 6.3 | Workload reduction by extending the Strassen algorithm to the real-life CNN in    |

|     | Fig. 6.3 via our convolutional MM                                                 |

| 8.1 | Summary of proposed communication optimizations for customizable domain-        |

|-----|---------------------------------------------------------------------------------|

|     | specific computing                                                              |

| 8.2 | Power numbers of different components at different working states measured by a |

|     | power meter for the estimation of energy consumption                            |

#### **ACKNOWLEDGMENTS**

Here I would like to offer my sincerest gratitude to my advisor, Professor Jason Cong. Professor Cong is a Chancellor's Professor at the Computer Science Department and Electrical Engineering Department of UCLA, Director of the Center for Customizable Domain-Specific Computing, and Co-Director of the UCLA VAST Lab. His insightful guidance, professional advice, and constant support helped me throughout the time of my PhD study at UCLA. I would not have reached so far without our weekly group meetings, offline discussions, and email exchanges which inspired my research ideas and pinpointed my focus. From him I learned not only ideas and ways to conduct research, but also many other things beyond research. It is my great fortune and honor to have him as my adviser.

I am also very grateful to my doctoral committee members, Professor M.-C. Frank Chang, Professor Dejan Markovic, and Professor Tyson Condie, for their time, interest, and insightful comments. Their rich experience in circuit design, architecture design, and system design brought further improvements to this thesis.

I would like to thank Janice Wheeler for her help in editing the language of my papers and this thesis. Whenever a conference submission deadline approaches, Janice receives many paper drafts to edit. There were several times when I sent her my paper drafts rather late. This left her with a tight time constraint, but she always worked very hard to ensure that my paper and the other papers were carefully proofread, with attention to details of word choice, spelling, and punctuation. Her great job prevented my paper submissions from losing scores—at least in the aspect of writing quality.

Moreover, I would like to thank all my fellow researchers who contributed in some way to this thesis. In Chapter 4, my interconnect design serves as a component of the CHP prototyping on FPGA devices. Yu-Ting Chen, Mohammad Ali Ghodrat, Chunyue Liu, Muhuan Huang and Zou Yi contributed to this prototyping effort. In Chapter 5, the proposed work initiated from a discussion with Peng Li and Peng Zhang. Peng Zhang also helped develop the compiler flow to analyze the data access patterns in user applications. In Chapter 7, the proposed work is part of a joint project for accelerator management in heterogeneous clusters. In this project, Muhuan Huang worked on the global resource management, and Hui Huang worked on the application resource management. Last, Karthik Gururaj, Sen Li and Di Wu maintained the servers in the VAST Lab and provided a stable platform for me to do most of the experiments.

I am also thankful to my fellow researchers and friends in the VAST Lab who made my graduate study in UCLA colorful and joyful. Moreover, I would like to thank all the faculty and the staff in the Electrical Engineering Department and Computer Science Department at UCLA for helping me get through the PhD program.

My love and thanks to my parents for their constant source of love, concern, support and strength all these years.

The work in this thesis is partially supported by the Center for Domain-Specific Computing (CDSC) which is funded by the NSF Expeditions in Computing Award CCF-0926127, CFAR (Center for Future Architecture Research, one of six centers of STARnet, a Semiconductor Research Corporation program sponsored by MARCO and DARPA), and grants from Altera Corporation and Xilinx Inc.

#### VITA

| 2010      | B.S. (Microelectronics),                                  |

|-----------|-----------------------------------------------------------|

|           | Peking University, China.                                 |

| 2012      | M.S. (Electrical Engineering),                            |

|           | University of California, Los Angeles.                    |

| 2010-2015 | Research Assistant, Department of Electrical Engineering, |

|           | University of California, Los Angeles, U.S.A.             |

#### PUBLICATIONS

Jason Cong, Hui Huang, Muhuang Huang, Bingjun Xiao, Peng Zhang\*, "CMOST: A System-Level FPGA Compilation Framework", *Design Automation Conference (DAC)*, 2015.

Cheng Zhang\*, Peng Li, Guangyu Sun, Yijin Guan, Bingjun Xiao, Jason Cong, "Optimizing FPGA-based Accelerator Design for Deep Convolutional Neural Networks: An Analytical Approach based on Roofline Model", *International Symposium on FPGAs*, 2015.

Jason Cong, and Bingjun Xiao\*, "Minimizing Computation in Convolutional Neural Networks", International Conference on Artificial Neural Networks (ICANN), 2014.

Jason Cong, Peng Li, Bingjun Xiao\*, and Peng Zhang, "An Optimal Microarchitecture for Stencil Computation Acceleration Based on Non-Uniform Partitioning of Data Reuse Buffers", *Design Automation Conference (DAC)*, 2014. Jason Cong, and Bingjun Xiao\*, "FPGA-RPI: A Novel FPGA Architecture With RRAM-Based Programmable Interconnects", *IEEE Transactions on Very Large Scale Integration Systems (TVLSI)*, 2014.

Jason Cong, Hui Huang, Chiyuan Ma, Bingjun Xiao\*, and Peipei Zhou, "A Fully Pipelined and Dynamically Composable Architecture of CGRA", *International Symposium on Field-Programmable Custom Computing Machines (FCCM)*, 2014, pp. 9-16.

Jason Cong, and Bingjun Xiao\*, "Optimization of Interconnects Between Accelerators and Shared Memories in Dark Silicon", *International Conference on Computer-Aided Design (ICCAD)*, 2013.

Yu-Ting Chen, Jason Cong, Mohammad, Ali Ghodrat, Muhuan Huang, Chunyue Liu, Bingjun Xiao\*, and Yi Zou, "Accelerator-Rich CMPs: From Concept to Real Hardware", *International Conference on Computer Design (ICCD)*, 2013, pp. 169-176.

Jason Cong, Muhuan Huang, Sen Li, and Bingjun Xiao\*, "Energy-Efficient Computing Using Adaptive Table Lookup Based on Nonvolatile Memories", *International Symposium on Low Power Electronics and Design (ISLPED)*, 2013.

Jason Cong, and Bingjun Xiao\*, "Defect Tolerance in Nanodevice-Based Programmable Interconnects: Utilization Beyond Avoidance", *Design Automation Conference (DAC)*, 2013.

Jason Cong, Guojie Luo, Kelly Tsota\* and Bingjun Xiao, "Optimizing Routability in Large-Scale Mixed-Size Placement", *Asia and South Pacific Design Automation Conference (ASPDAC)*, 2013.

Jason Cong, Karthik Gururaj, Muhuan Huang, Sen Li, Bingjun Xiao\* and Yi Zou, "Domain-Specific Processor with 3D Integration for Medical Image Processing", *International Conference*  on Application-specific Systems, Architectures and Processor (ASAP), 2011, pp. 247-250.

Jason Cong, and Bingjun Xiao\*, "mrFPGA: A Novel FPGA Architecture with Memristor-Based Reconfiguration", *International Symposium on Nanoscale Architectures*, 2011, pp. 1-8.

## **CHAPTER 1**

### Introduction

#### 1.1 Customizable Domain-Specific Computing

As pointed out in [19], in order to meet ever-increasing computing needs and overcome power density limitations, the computing industry has halted simple processor frequency scaling and entered the era of parallelization, with tens to hundreds of computing cores integrated in a single processor, and hundreds to thousands of computing servers connected in a warehouse-scale data center. However, such highly parallel, general-purpose computing systems still face serious challenges in terms of performance, power, heat dissipation, space, and cost. Recently the research focus has moved from parallelization to domain-specific customization as the next disruptive technology [19], based on three observations:

First, each user or enterprise typically has a high computing demand in one or a few selected application domains (e.g., graphics for game developers, circuit simulation for integrated circuit design houses, financial analytics for investment banks). Therefore, it is possible to develop a customizable computing platform where computing engines and communication infrastructures can be specialized to a particular application domain, thereby gaining significant improvements in power-performance efficiency compared to a general-purpose architecture.

Second, the performance gap between a totally customized solution (using an applicationspecific integrated circuit (ASIC)) and a general-purpose solution can be very large. A case study of the 128-bit key AES encryption algorithm was presented in [20]. An ASIC implementation in 0.18um CMOS achieves 3.86 Gbits/second at 350mW, while the same algorithm coded in Java and executed on an embedded SPARC processor yields 450bits/second at 120mW. This difference implies a performance/power efficiency (measured in Gbits/second/W) gap of roughly 3 million.

Last, it is extremely costly and impractical to implement each application in ASIC. The nonrecurring engineering cost of an ASIC design at the current 45nm CMOS technology is over \$50M [21], and the design cycle can easily exceed a year. There is a strong need for a novel architecture platform that can be efficiently customized to a wide range of applications in a domain or a set of domains to bridge the huge performance/power gap between ASICs and general-purpose processors.

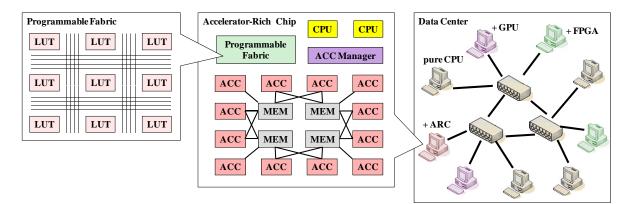

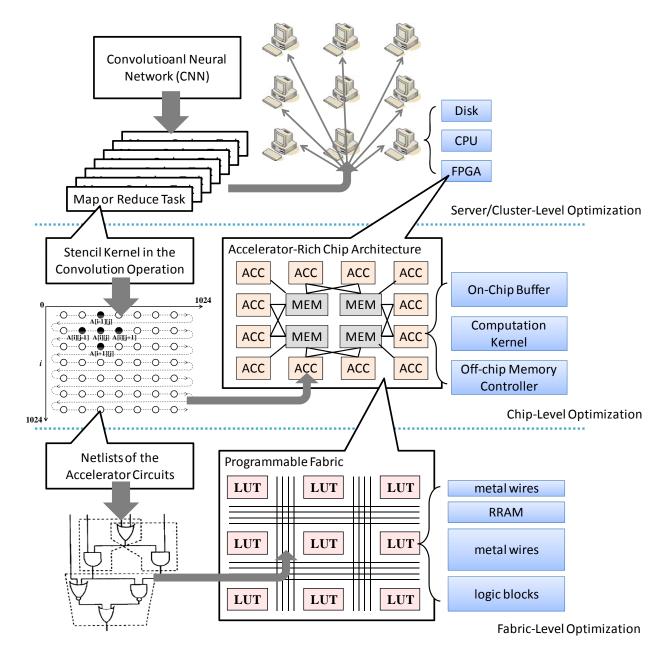

To realize the order-of-magnitude performance/power efficiency improvement via customization, yet still leverage economy of scale, Center for Customizable Domain-Specific Computing (CDSC) is developing a customizable heterogeneous platform (CHP), consisting of a heterogeneous set of adaptive computational resources with communication optimization at three different levels. Fig. 1.1 illustrates an example CHP configuration. A CHP-oriented data center includes

Figure 1.1: Customizable heterogeneous platform for domain-specific computing.

a sea of heterogeneous processor nodes equipped with CPUs, GPUs, FPGAs and accelerator-rich chips to serve different user tasks for high energy efficiency. All of these processor nodes communicate with each other for joint tasks decomposed from big data applications. A CHP-oriented accelerator-rich chip includes a sea of heterogeneous accelerators to execute different application kernels in user tasks for high energy efficiency. All of these accelerators communicate through an

on-chip network which can be reconfigured to meet the data demand imposed by working accelerators. A CHP-oriented programmable fabric includes a sea of look-up tables (LUTs) which are programmed to different basic operations in user application kernels. All of these LUTs are connected by programmable interconnects which can be reconfigured to route the Boolean network among basic operations.

As we can see, each level of the CHP is composed of the computing units and the communication infrastructure. While we can easily increase the number of computing units, it is usually a big challenge to design a corresponding communication infrastructure to feed data into the huge amount of these computing units in a timely manner. In addition, the data access consumes much more energy than the arithmetic operation and has a high impact on the system energy efficiency. Fig. 1.2 adopted from [1] shows the data for various operations in a 45nm technology, and gives the energy breakdown of a simple in-order processor. While the architecture customization in

| Integer |        | FP     |       | Data Acces | SS        |

|---------|--------|--------|-------|------------|-----------|

| Add     |        | FAdd   |       | Cache      | (64bit)   |

| 8 bit   | 0.03pJ | 16 bit | 0.4pJ | 8KB        | 10pJ      |

| 32 bit  | 0.1pJ  | 32 bit | 0.9pJ | 32KB       | 20pJ      |

| Mult    |        | FMult  |       | 1MB        | 100pJ     |

| 8 bit   | 0.2pJ  | 16 bit | 1.1pJ | DRAM       | 1.3-2.6nJ |

| 32 bit  | 3.1pJ  | 32 bit | 3.7pJ |            |           |

Add

Figure 1.2: Rough energy costs for various operations in 45nm 0.9V, adopted from [1].

**Register File**

Access

**I-Cache Access**

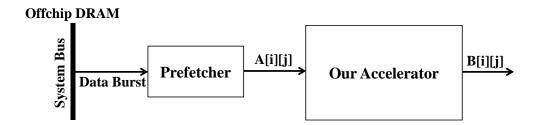

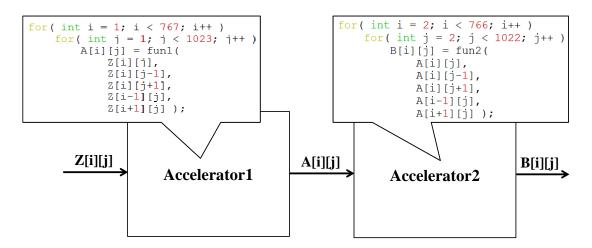

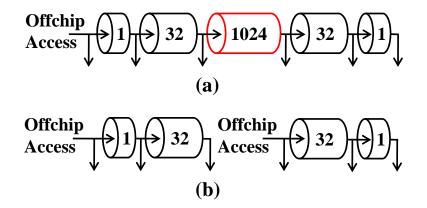

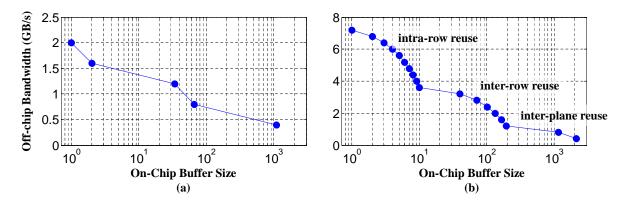

our CHP can save energy consumption via the control part in the professor, the data access still remains a big problem. This thesis focuses on the communication optimization in the CHP.