# UC San Diego UC San Diego Electronic Theses and Dissertations

### Title

Tackling nanoscale IC failures through noise-aware testing and silicon debugging

## Permalink

https://escholarship.org/uc/item/6zj4d9mw

### Authors

Chen, Mingjing Chen, Mingjing

# Publication Date

2012

Peer reviewed|Thesis/dissertation

### UNIVERSITY OF CALIFORNIA, SAN DIEGO

### Tackling Nanoscale IC Failures through Noise-aware Testing and Silicon Debugging

A dissertation submitted in partial satisfaction of the requirements for the degree Doctor of Philosophy

in

Computer Science (Computer Engineering)

by

Mingjing Chen

Committee in charge:

Professor Alex Orailoglu, Chair Professor Chung-Kuan Cheng Professor Sadik Esener Professor Ian G. Harris Professor William E. Howden

2012

Copyright Mingjing Chen, 2012 All rights reserved. The dissertation of Mingjing Chen is approved, and it is acceptable in quality and form for publication on microfilm and electronically:

Chair

University of California, San Diego

2012

# DEDICATION

To my family.

## TABLE OF CONTENTS

| Signature Pag  |                                | . iii                                                                                                          |

|----------------|--------------------------------|----------------------------------------------------------------------------------------------------------------|

| Dedication .   |                                | . iv                                                                                                           |

| Table of Cont  | nts                            | . v                                                                                                            |

| List of Figure |                                | . viii                                                                                                         |

| List of Tables |                                | . x                                                                                                            |

| Acknowledge    | ents                           | . xi                                                                                                           |

| Vita           |                                | . xiii                                                                                                         |

| Abstract of t  | Dissertation                   | . xv                                                                                                           |

| Chapter 1      | <ul> <li>ntroduction</li></ul> | $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                           |

| Chapter 2      | Related Work                   | $\begin{array}{cccc} . & 16 \\ . & 17 \\ . & 18 \\ . & 19 \\ . & 19 \\ . & 23 \\ . & 24 \\ . & 24 \end{array}$ |

| Chapter 3 | Design-guided, noise-aware test and diagnosis framework overview                                                                                       | 29 |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|           | 3.1 Yield and quality co-optimization                                                                                                                  | 29 |

|           | 3.2 Embedding functional view in structural test                                                                                                       | 33 |

|           | 3.3 Failure hypothesis pruning using design information 3                                                                                              | 36 |

| Chapter 4 | Overtesting avoidance in scan mode                                                                                                                     | 39 |

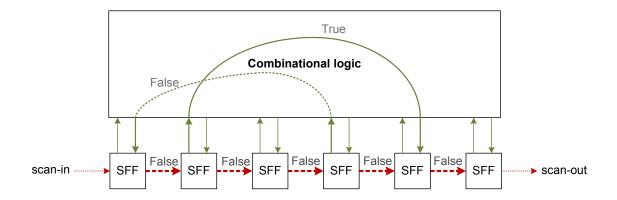

|           | 4.1 Linear compression based scan architecture 4                                                                                                       | 40 |

|           | 1                                                                                                                                                      | 43 |

|           | 8                                                                                                                                                      | 45 |

|           |                                                                                                                                                        | 46 |

|           | 4.3.2 Seed space transformation $\ldots \ldots \ldots \ldots \ldots 4$                                                                                 | 47 |

|           | 1                                                                                                                                                      | 49 |

|           | 4.4 Concurrent compaction/compression for low noise scan . 6                                                                                           | 60 |

|           | 1                                                                                                                                                      | 52 |

|           | 4.6 Conclusions $\ldots$ $7$                                                                                                                           | 70 |

| Chapter 5 | Detecting functional-mode marginal failures                                                                                                            | 72 |

|           | 5.1 Handling noise in delay testing                                                                                                                    | 73 |

|           | 5.1.1 Higher or lower noise? A dilemma for testing $\ldots$ 7                                                                                          | 73 |

|           | 5.1.2 Approximating functional mode noise in testing . 7                                                                                               | 75 |

|           | 5.2 Multi-functional-cycle delay test                                                                                                                  | 78 |

|           | 5.2.1 Test application scheme $\ldots \ldots \ldots \ldots \ldots $                                                                                    | 78 |

|           | 5.2.2 Test generation flow adaptation $\ldots \ldots \ldots \ldots $                                                                                   | 79 |

|           | 5.3 Power ground noise estimation                                                                                                                      | 80 |

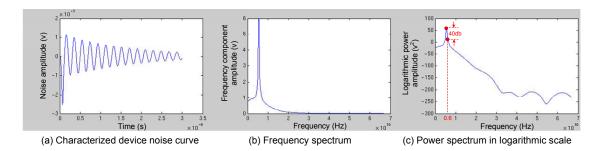

|           | 5.3.1 Noise development time analysis $\ldots \ldots \ldots \ldots $                                                                                   | 31 |

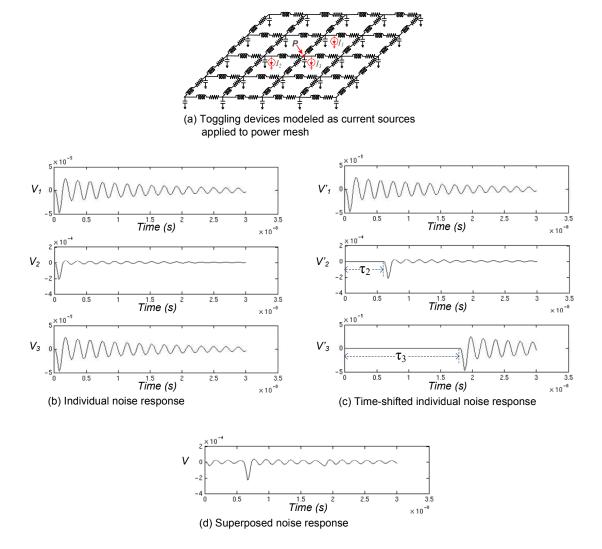

|           | $5.3.2$ Noise profile creation through linear superposition $\delta$                                                                                   | 33 |

|           | 5.4 Test pattern transformation for noise failure detection $\delta$                                                                                   | 87 |

|           | 5.5 Simulation results $\ldots \ldots $                                          | 92 |

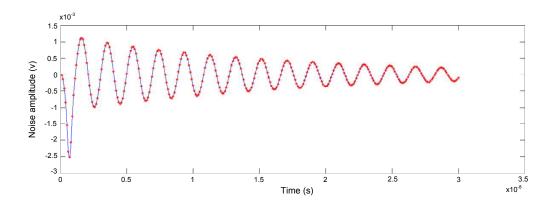

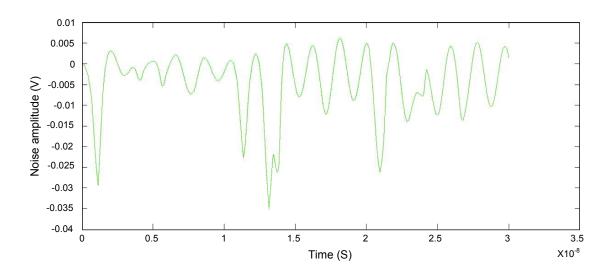

|           | 5.5.1 Accuracy $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                                                                                            | 93 |

|           | 5.5.2 Effectiveness $\ldots \ldots $                                      | 94 |

|           | 5.5.3 Efficiency $\ldots$ $\ldots$ $\ldots$ $\ldots$                                                                                                   | 98 |

|           | 5.6 Conclusions $\ldots \ldots $                                          | 99 |

| Chapter 6 | Marginal failure diagnosis in scan circuitry                                                                                                           | )1 |

|           | 6.1 Scan Timing Failure Diagnosis Overview 10                                                                                                          | )2 |

|           | $6.1.1  \text{Technical challenges} \dots \dots$ | )3 |

|           | $6.1.2 Proposed approach \dots \dots$            | )5 |

|           | 6.2 Scan cell timing failure diagnosis                                                                                                                 | )6 |

|           | $6.2.1  \text{Preliminaries}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                                                         | )6 |

|           | 6.2.2 Fault location and type identification $\ldots \ldots \ldots 10$                                                                                 | )8 |

|           | 6.2.3 Manifestation probability computation 11                                                                                                         | 17 |

|           | 6.3 Scan clock delay fault diagnosis                                                                                                                   |    |

|           | $6.3.1  \text{Problem formulation}  \dots  \dots  \dots  \dots  \dots  12$                                                                             | 21 |

|              | 6.3.2 Establishing Fault Hypotheses                                                                |

|--------------|----------------------------------------------------------------------------------------------------|

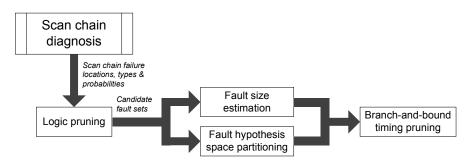

|              | 6.3.3 Diagnosis Flow $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 126$   |

|              | $6.4  \text{Simulation results}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  130$      |

|              | $6.4.1  \text{Scan cell diagnosis results}  \dots  \dots  \dots  \dots  131$                       |

|              | 6.4.2 Scan clock buffer diagnosis results                                                          |

|              | $6.5  \text{Conclusions}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  140$                    |

| Chapter 7    | A functional flow for fast-to-revenue                                                              |

| -            | 7.1 Production ramp-up $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 142$ |

|              | 7.2 Integration implementation                                                                     |

|              | 7.2.1 Yield and quality characterization                                                           |

|              | 7.2.2 Failure-adaptive test optimization                                                           |

|              | 7.2.3 Re-spin verification $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 146$           |

| Chapter 8    | Conclusions                                                                                        |

| Bibliography |                                                                                                    |

### LIST OF FIGURES

| Figure 1.1:    | Discrepancy between structural test and "ideal" functional test | 6            |

|----------------|-----------------------------------------------------------------|--------------|

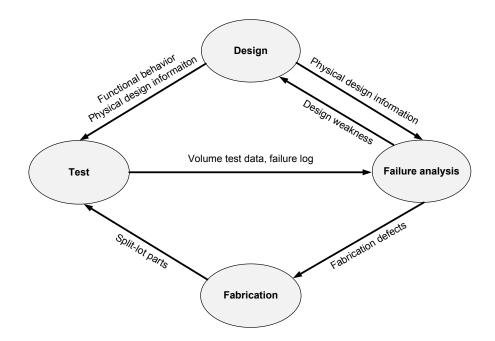

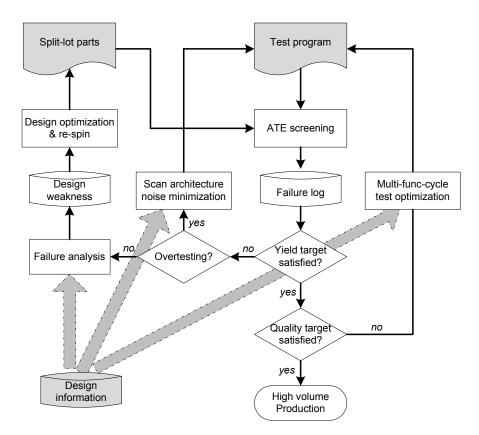

| Figure 3.1:    | Design-guided test and diagnosis framework                      | 31           |

| Figure 3.2:    | Timing path differentiation                                     | 33           |

| 0              |                                                                 |              |

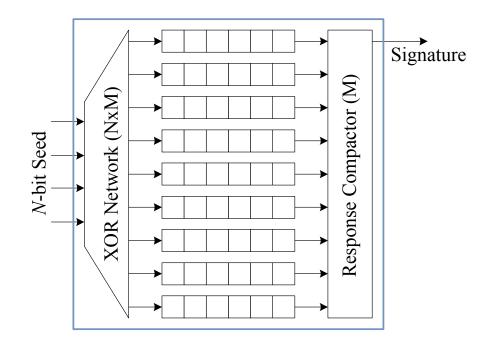

| Figure 4.1:    | Scan architecture using XOR network-based decompression hard-   |              |

|                | ware                                                            | 41           |

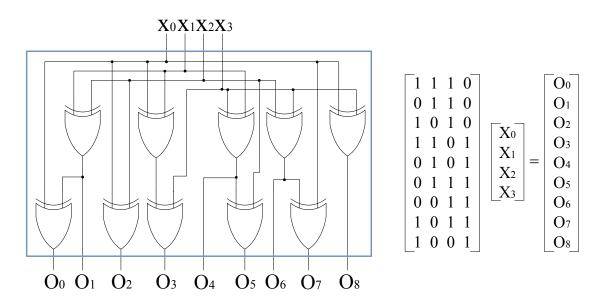

| Figure 4.2:    | Example XOR network and its matrix representation               | 42           |

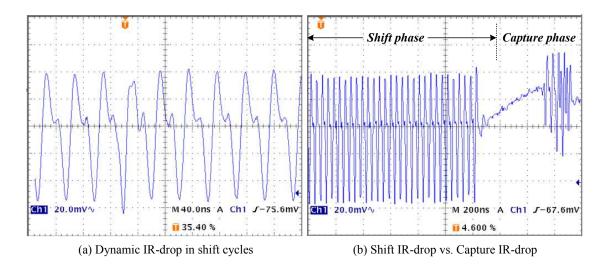

| Figure 4.3:    | High dynamic IR-drop during scan phase                          | 43           |

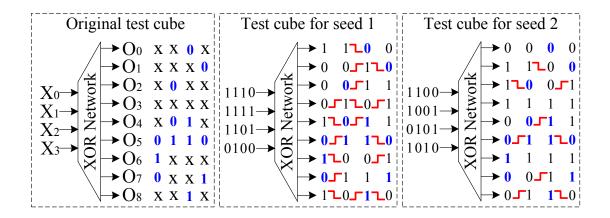

| Figure 4.4:    | Noise reduction through seed selection                          | 45           |

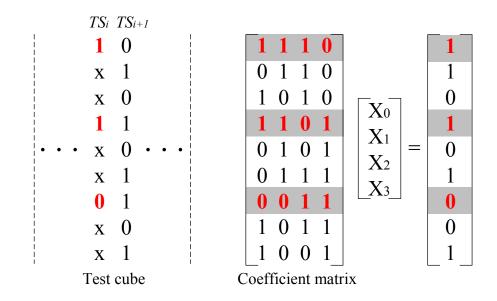

| Figure 4.5:    | Matrix representation for slice matching                        | 46           |

| Figure 4.6:    | Extracting independent bits of the seed                         | 47           |

| Figure 4.7:    | Constructing a reduced system in independent bit space          | 48           |

| Figure 4.8:    | Primitive inconsistent group                                    | 49           |

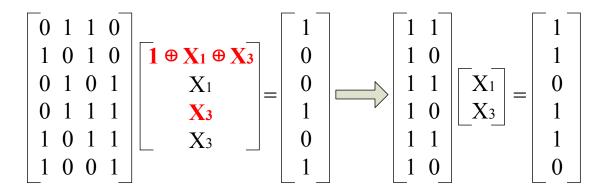

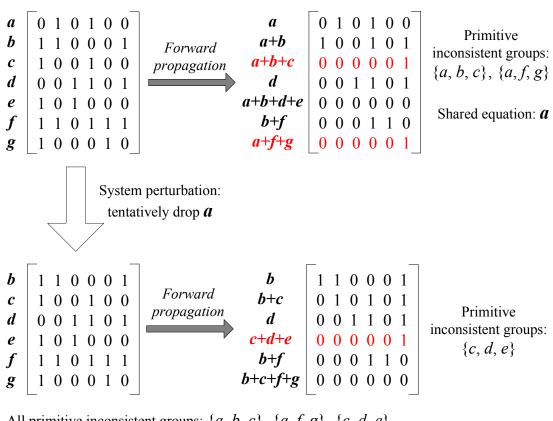

| Figure 4.9:    | PI group identification through forward propagation             | 51           |

| Figure 4.10:   | Iterative PI group identification through system perturbation . | 57           |

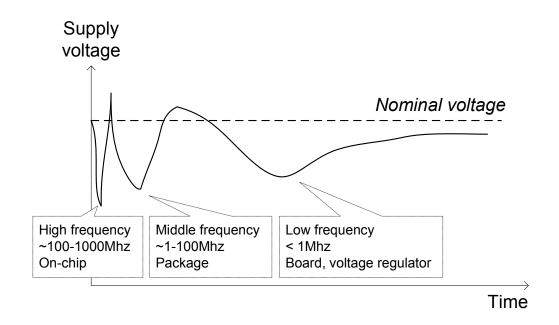

| Figure 5.1:    | Power ground noise frequency at different circuit levels        | 74           |

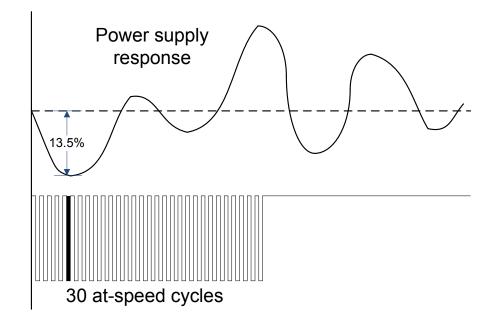

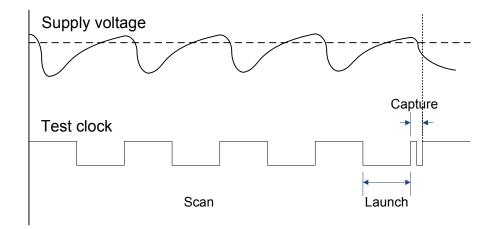

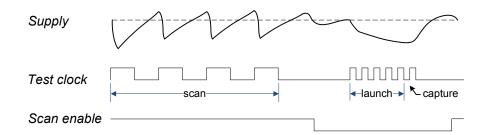

| Figure 5.2:    | Power supply noise during at-speed cycles                       | 76           |

| Figure 5.3:    | Power supply noise during at-speed cycles                       | 76           |

| Figure 5.4:    | Test clock diagram of proposed test scheme                      | 78           |

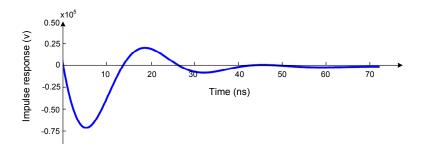

| Figure 5.5:    | Impulse response                                                | 80           |

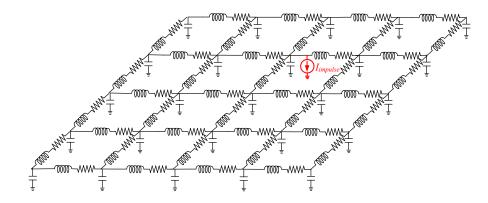

| Figure 5.6:    | Simulation model for impulse response                           | 82           |

| Figure 5.7:    | Noise estimation through superposition                          | 85           |

| Figure 5.8:    | Sampling frequency selection based on noise spectrum            | 90           |

| Figure 5.9:    | Comparison between full-resolution and sampled curves           | 91           |

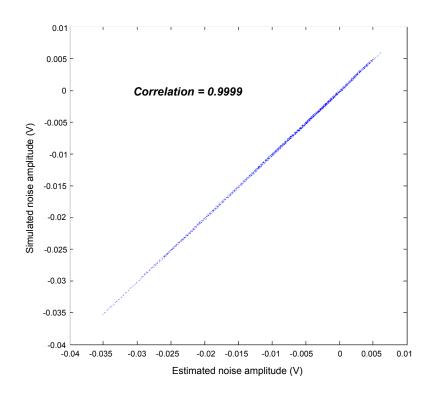

| Figure 5.10:   | Noise curve comparison                                          | 94           |

| Figure 5.11:   | Correlation between simulated and estimated results $\ldots$ .  | 95           |

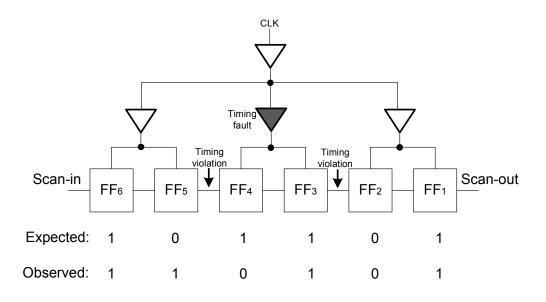

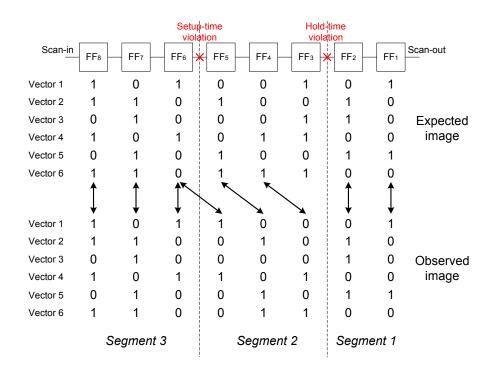

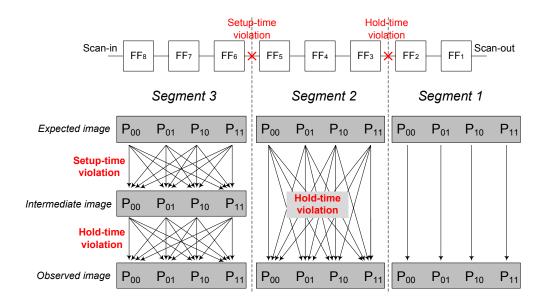

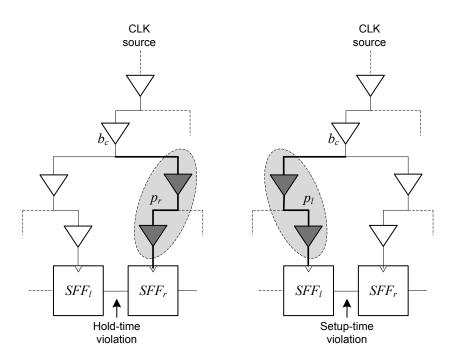

| Figure 6.1:    | Scan timing fault manifestation                                 | 103          |

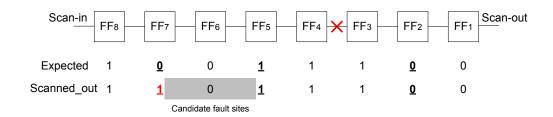

| Figure 6.2:    | Incorrect diagnosis of intermittent faults                      |              |

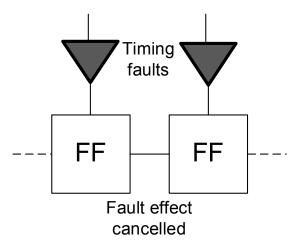

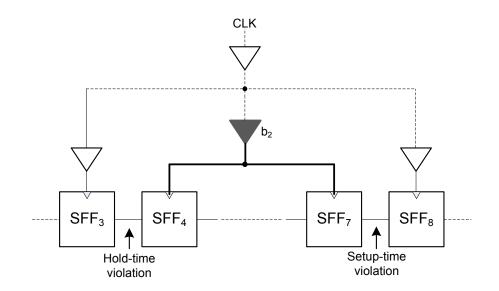

| Figure 6.3:    | Scan clock fault interaction                                    |              |

| Figure 6.4:    | A scan image formed by $n$ scan vectors                         |              |

| Figure 6.5:    | Column-wise correlation computation                             |              |

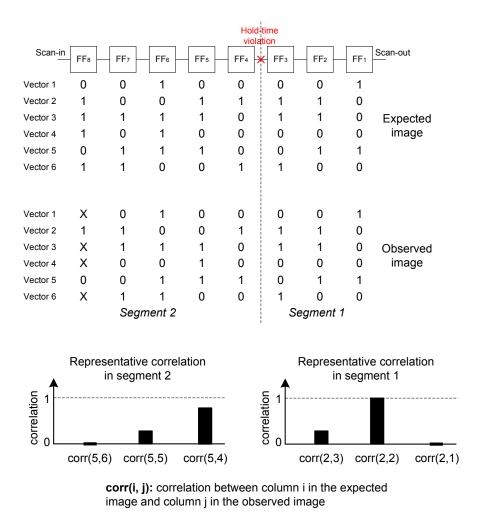

| Figure 6.6:    | Phase skews induced by permanent faults                         |              |

| Figure 6.7:    | Correlation change in intermittent fault scenarios              |              |

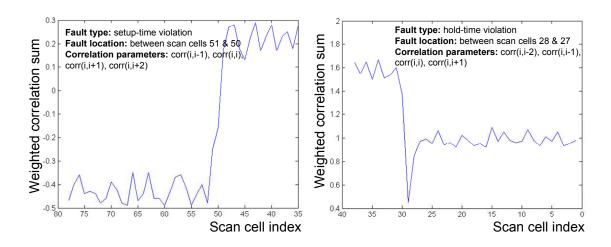

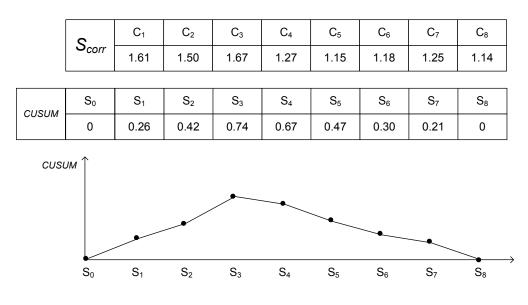

| Figure 6.8:    | Curves of weighted correlation sum                              |              |

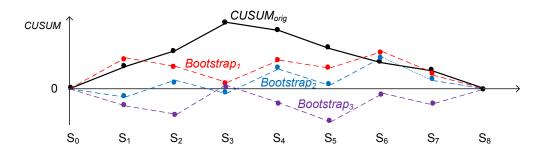

| Figure 6.9:    | CUSUM chart of $S_{corr}$ sequence                              |              |

| 0              | Bootstrap analysis                                              |              |

|                | Variation of two-bit pattern distribution                       |              |

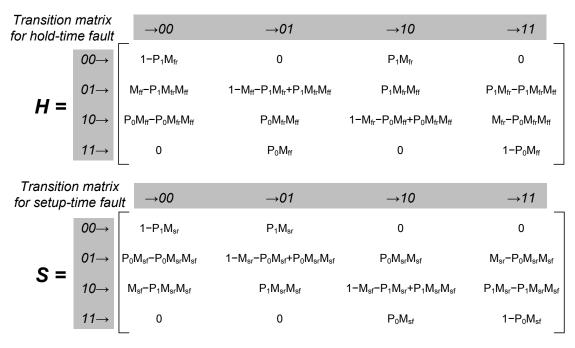

|                | Transition matrices for timing faults                           |              |

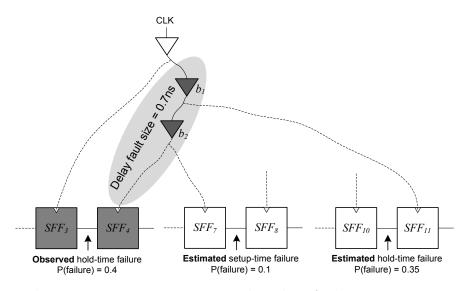

| 0              | Scan chain timing failures induced by clock faults              |              |

| - 18 and 0.10. |                                                                 | <i>± = ±</i> |

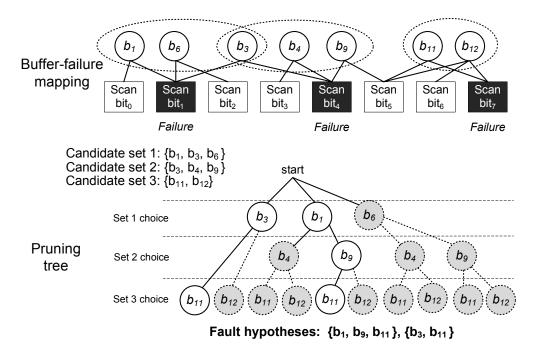

| Figure 6.14: | Logic pruning based on scan chain failure locations and types $\ . \ 123$ |

|--------------|---------------------------------------------------------------------------|

| Figure 6.15: | Timing reasoning based on fault size estimation                           |

| Figure 6.16: | Fault hypothesis space partitioning                                       |

| Figure 6.17: | Branch-and-bound pruning                                                  |

| Figure 6.18: | Diagnosis flow                                                            |

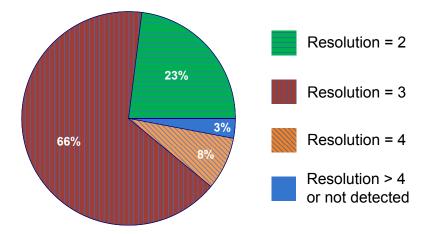

| Figure 6.19: | Diagnostic resolution distribution                                        |

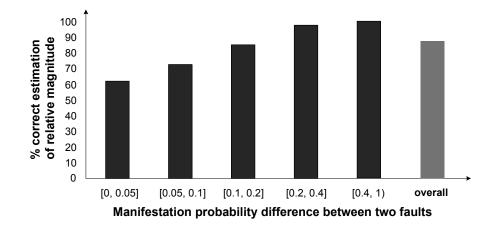

| Figure 6.20: | Accuracy of relative magnitude estimation                                 |

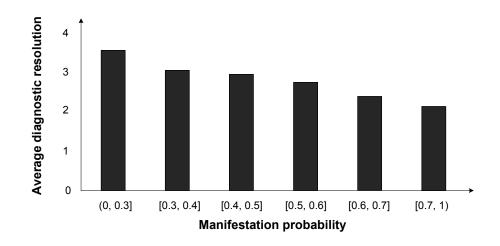

| Figure 6.21: | Diagnostic resolution distribution in fault manifestation proba-          |

|              | bility                                                                    |

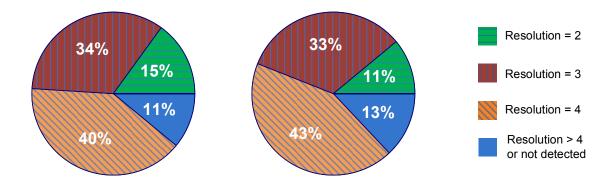

| Figure 6.22: | Diagnostic resolution distribution of unidirectional faults 136           |

| Figure 7.1:  | Production ramp-up flow                                                   |

### LIST OF TABLES

| Table 3.1: | Impact on yield, test quality, and time-to-revenue 32 |

|------------|-------------------------------------------------------|

| Table 4.1: | Benchmark circuits                                    |

| Table 4.2: | Average scan noise comparison                         |

| Table 4.3: | Peak scan noise comparison                            |

| Table 4.4: | Compression ratio comparison                          |

| Table 4.5: | Comparison to schemes in [66] in average noise        |

| Table 4.6: | Comparison to schemes in [66] in peak noise           |

| Table 4.7: | Comparison to schemes in $[103]$                      |

| Table 4.8: | Algorithm execution time in minutes                   |

| Table 5.1: | Length of capture phase                               |

| Table 5.2: | Average noise amplitude comparison                    |

| Table 5.3: | Peak noise amplitude comparison                       |

| Table 5.4: | Worst-case simulation time in seconds                 |

| Table 5.5: | Test pattern transformation time in seconds           |

| Table 6.1: | Fault model                                           |

| Table 6.2: | Intermittent fault diagnosis                          |

| Table 6.3: | CPU time of scan cell diagnosis in seconds            |

| Table 6.4: | Scan clock buffer diagnosis results                   |

| Table 6.5: | CPU time of scan clock buffer diagnosis in seconds    |

|            |                                                       |

#### ACKNOWLEDGEMENTS

I would like to express my deepest gratitude to my advisor, Professor Alex Orailoglu, for the great guidance he provided during my Ph.D years. Through multiple drafts, many debates and many long nights, his guidance has proved to be invaluable. His enthusiasm and intelligence in research is always a model for me to follow in my future career.

Many thanks go to the other professors I have met during the years in UCSD, as well as my academic siblings in the Architecture, Reliability, and Testing (ART) group, including Chengmo Yang, Baris Arslan, Garo Bournoutian, Wenjing Rao.

I also want to thank my friends in UCSD, for sharing with me the unforgettable campus life.

I would also like to thank my parents for always encouraging me with their best wishes.

In the end, I would like to thank my wife, Zeyan Li, for always being there. Without her love, support, tolerance and advice, I would never have gone so far.

The text of Chapter 4, is in part a reprint of the material as it appears in M. Chen and A. Orailoglu, "Scan power reduction in linear test data compression scheme," International Conference on Computer-Aided Design, 2009; and in M. Chen and A. Orailoglu, "Scan power reduction for linear test compression schemes through seed selection," IEEE Transactions on VLSI. The dissertation author was the primary researcher and author of the publications [16] and [15].

The text of Chapter 5, is in part a reprint of the material as it appears in *M. Chen and A. Orailoglu*, "Cost-effective IR-drop failure identification and yield recovery through a failure-adaptive test scheme," Design, Automation and Test in Europe, 2010; and in *M. Chen and A. Orailoglu*, "Examining timing path robustness under wide-bandwidth power supply noise through multi-functional-cycle delay test," submitted to IEEE Transactions on VLSI. The dissertation author was the primary researcher and author of the publications [17] and [13].

The text of Chapter 6, is in part a reprint of the material as it appears in

M. Chen and A. Orailoglu, "Diagnosing scan chain timing faults through statistical feature analysis of scan images," Design, Automation and Test in Europe, 2011; in M. Chen and A. Orailoglu, "Diagnosing scan clock delay faults through statistical timing pruning," Design Automation Conference, 2011; and in M. Chen and A. Orailoglu, "On diagnosis of timing failures in scan architecture," IEEE Transactions on CAD. The dissertation author was the primary researcher and author of the publications [18], [19] and [14].

#### VITA

| 2002      | B. S. in Microelectronics, Tsinghua University, Beijing                                                    |

|-----------|------------------------------------------------------------------------------------------------------------|

| 2005      | M. S. in Electronic Science and Technology, Tsinghua University, Beijing                                   |

| 2006-2010 | Teaching Assistant, Department of Computer Science and<br>Engineering, University of California, San Diego |

| 2005-2012 | Research Assistant, Department of Computer Science and<br>Engineering, University of California, San Diego |

| 2012      | Ph. D. in Computer Science (Computer Engineering), University of California, San Diego                     |

### PUBLICATIONS

#### Journal papers

M. Chen and A. Orailoglu, "Scan power reduction for linear test compression schemes through seed selection," *IEEE Trans. on VLSI*, accepted

C. Yang, M. Chen and A. Orailoglu, "Squashing code size in microcoded IPs while delivering high decompression speed," *Design Automation for Embedded Systems*, vol. 14, no. 3, pp. 265-284, 2010

M. Chen and A. Orailoglu, "On diagnosis of timing failures in scan architecture," *IEEE Trans. on CAD*, accepted

M. Chen and A. Orailoglu, "Examining timing path robustness under widebandwidth power supply noise through multi-functional-cycle delay test," submitted to *IEEE Trans. on VLSI*

### Conference papers

M. Chen and A. Orailoglu, "Diagnosing scan clock delay faults through statistical timing pruning," *IEEE/ACM Design Automation Conference*, 2011

M. Chen and A. Orailoglu, "Diagnosing scan chain timing faults through statistical feature analysis of scan images," *IEEE/ACM Design, Automation and Test in Europe*, 2011

M. Chen and A. Orailoglu, "VDDmin test optimization for overscreening minimization through adaptive scan chain masking," *IEEE VLSI Test Symposium*, 2010 M. Chen and A. Orailoglu, "Cost-effective IR-drop failure identification and yield recovery through a failure-adaptive test scheme," *IEEE/ACM Design, Automation and Test in Europe*, 2010

M. Chen and A. Orailoglu, "Scan power reduction in linear test data compression scheme," *IEEE/ACM International Conference on Computer-Aided Design*, 2009

C. Yang, M. Chen and A. Orailoglu, "Squashing microcode stores to size in embedded systems while delivering rapid microcode accesses," *CODES+ISSS*, 2009

M. Chen and A. Orailoglu, "Flip-flop hardening and selection for soft error and delay fault resilience," *IEEE International Symposium on Defect and Fault Tolerance* in VLSI Systems, 2009

M. Chen and A. Orailoglu, "Deflecting crosstalk by routing reconsideration through refined signal correlation estimation," ACM Great Lakes Symposium on VLSI, 2009

M. Chen and A. Orailoglu, "Test cost minimization through adaptive test development," *IEEE International Conference on Computer Design*, 2008

M. Chen and A. Orailoglu, "Circuit-level mismatch modeling and yield optimization for CMOS analog circuits," *IEEE International Conference on Computer De*sign, 2007

M. Chen and A. Orailoglu, "Improving circuit robustness with cost-effective softerror-tolerant sequential elements," *IEEE Asian Test Symposium*, 2007

M. Chen, H. Haggag and A. Orailoglu, "Decision tree based mismatch diagnosis in analog circuits," *IEEE VLSI Test Symposium*, 2006

#### ABSTRACT OF THE DISSERTATION

Tackling Nanoscale IC Failures through Noise-aware Testing and Silicon Debugging

by

Mingjing Chen

Doctor of Philosophy in Computer Science (Computer Engineering)

University of California, San Diego, 2012

Professor Alex Orailoglu, Chair

The continued device scaling trend and the aggressive integrated circuit design style have shifted the major device failure mechanism from stuck-at fault types to marginal failures induced by timing uncertainty and signal noise. The production test methodologies currently employed by industry, however, are still based on the traditional structural test schemes that focus on the detection of permanent defects, failing to account for emerging failure mechanisms in nanometer scale designs. The inability of current test methodologies in adapting to the failure mechanism shift imposes critical challenges to the IC providers, mainly observed as significant product quality degradation and yield loss. To make things worse, the marginal failures result in highly ambiguous failure syndromes, invalidating traditional assumptions employed in silicon debugging. The degraded test quality and yield, combined with inaccurate failure diagnosis, lead to a lengthened designfabrication-debugging cycle needed for ramping up the yield and quality for final production, significantly slowing down the time-to-market and boosting the overall product cost.

Maintaining high quality yet low cost production test for nanometer scale integrated circuits necessitates a comprehensive examination of marginal failure scenarios while minimizing yield loss. Reducing the time-to-market cycle relies on an accurate identification of marginal failure locations and causalities to pinpoint the design and fabrication weaknesses that have gross quality impact. The challenges, though, are the resolution to the paradox between overscreening and underscreening that are simultaneously taking place in today's industrial testing practice, and the extraction of sensible diagnostic signals from highly ambiguous fault behaviors of marginal failures. The presented thesis work overcomes these challenges through the proposition of an innovative marginal failure aware test and diagnosis scheme, capable of thoroughly targeting the functional mode failure scenarios with a low cost structural test platform and the accurate identification of failure-induced feature change in large volume test data. A comprehensive production ramp-up flow, constructed based on the proposed test and diagnosis schemes, is furthermore presented to guide the silicon debugging, test optimization, and yield/quality learning activities, so as to minimize the time-to-market.

From a technical point of view, this thesis work analyzes the power ground noise in functional and testing modes and its impact on circuit timing robustness, with a focus on the differentiation of the functional mode timing failures from the pure testing mode ones, thus enabling a clear decomposition of the noise treatment strategies for different operation scenarios. A set of tightly-coupled approaches, including 1) noise resilience in testing related circuitry for overscreening minimization, 2) approximation of worst-case functional mode noise in structural testing for marginal timing failure detection, and 3) diagnosis of noise-induced timing failure diagnosis in scan paths and scan clock trees for design optimization, are presented to attain the overall goal of high yield, low test escape rate, and fast silicon re-spin. These techniques are developed with the consideration of enabling a seamless adaptation of industrial flows by delivering maximal compatibility to mainstream design-for-testability architectures and testing platforms employed in nanometer scale designs. The successful incorporation of these techniques will significantly expedite the silicon production ramp-up process with highly reduced risk and cost.

# Chapter 1

# Introduction

Manufacturing testing and failure analysis have been utilized for decades in semiconductor industry as the most important approach for verifying and improving the quality of integrated circuit (IC) products. The fast device integration trend as projected by Moore's law, although strongly pushing the advancement in circuit performance, inevitably increases the difficulty in maintaining high device quality in production. One of the most affected aspects in the testing domain consists of the testing and diagnosis of digital circuit failures, as the device scaling and integration are most aggressively performed in digital circuits. The everincreasing transistor density, the diminishing pin-to-transistor ratio, and the high process variability in small devices all contribute to a highly elevated failure rate in today's digital integrated circuits. On the other hand, the fierce competition in the digital product marketplace strongly forces the IC vendors to reduce the defective device rate measured as *Defective Parts Per Million* (DPPM). The development of a robust and efficient test and failure analysis methodology, therefore, becomes a vital task that determines the success of digital IC products.

Traditionally, the digital testing and diagnosis approaches have mainly focused on the detection of gross manufacturing defects. Fault models based on gross defects, such as stuck-at faults and transition faults, have been utilized to develop test application schemes and test generation algorithms. Fault coverage, consequently, has constituted a natural metric in the industry for measuring the test quality. For a long period of time, such a scheme, as a stand-alone process separated from the chip design practice, was able to guarantee a very low DPPM, as chips fabricated in old technology nodes were mainly sensitive to gross fabrication defects rather than second-order effects such as process variability and design weakness.

As device feature sizes scale to the nanometer range, the testing and failure analysis of digital circuits have started to tightly couple with the design process during product development, as a number of non-traditional and design-related failure mechanisms have gradually become the dominating factors that impact product quality. The shift in failure mechanisms significantly degrades the quality of standard testing and failure analysis flow, resulting in a low yield and high test escape rate. This in turn slows down the time-to-market, as the IC vendors typically have to perform many more re-spins before ramping up to high volume production. The increased difficulty in performing correct testing and diagnosis furthermore lengthens the cycle between re-spins, as more effort and time are needed to collect the test escape data and identify the failure causality. Given the early time-to-revenue pressure, the learning and optimization of the test and diagnosis methodologies constitute a key task during the industrial product development cycle.

# 1.1 Need for design information in test and diagnosis

### 1.1.1 Failure mechanism shift

A semiconductor device can fail the test due to multiple reasons. The failure can possibly be the result of a design weakness, a defect in the fabrication process, or even a false alarm due to an inappropriately applied test. Over a long period of time, the fabrication defects have been considered the major failure mechanisms, since designs with old technology nodes were relatively simple and the design houses typically had rather robust verification strategies to rule out potential design risks. The scaling of the device feature size pushes the utilization of much more aggressive design styles for performance enhancement. This, unfortunately, increases the difficulty in verifying the design robustness under various operation conditions, resulting in a number of reliability concerns.

From a design perspective, a number of power and timing related changes can be evidently observed as a result of technology scaling. First of all, the technology node change is typically accompanied by the design parameter adjustment such as higher clock frequency and lower operation voltage, which results in an increased power demand and rapidly reduced design margins. Secondly, the device integration trend significantly increases the difficulty in routing the signal and power ground nets. To provide enough routing flexibility, more metal layers have to be incorporated in physical design. However, the increase in routing space barely matches the needs. Such a routing space shortage mainly impacts global signals such as power ground nets and clocks, as a strong degradation in routing balancing and an increased routing length can be observed on their distribution networks. Thirdly, the incorporation of multiple clock and power domains in the circuit further increases the design verification complexity as the impact of the inter-domain variability is even harder to model and predict.

The aggressive voltage scaling trend significantly reduces the noise margin in VLSI circuits. On the other hand, excessive power density in nanometer chips debilitates the delivery of sufficient current by the power supply network, causing significant power ground noise in the circuit. Current supply voltage variations are directly implicated in high timing uncertainties. It has been reported that a 10 - 15% voltage drop can induce a 20 - 30% increase in gate delay [47]. This constitutes a critical reliability challenge for modern VLSI systems designed with very tight timing slacks.

The current commercial design flow handles power ground noise through appropriate power budgeting and timing closure at a lower voltage corner, say, 10% lower than the nominal operation voltage. However, the noise amplitude in modern designs typically ranges from tens to even hundreds of millivolts, resulting in circuits frequently operating in a situation that is far from the range where timing is closed in design. As a result, marginal timing failures induced by power ground noise become one of the dominating failure mechanisms in nanometer scale circuits, even for designs that have been strictly verified before tape-out [2].

In contrast to traditional failure types such as stuck-at and transition faults, the marginal failures as outlined above exhibit a set of highly distinct characteristics. The manifestation of such failures is inherently a probabilistic behavior, as multiple factors such as voltage and temperature fluctuation can disturb timing in unpredictable ways. The manifestation condition of marginal failures is also much more complicated than the traditional ones, as the activation and observation of marginal failures not only rely on appropriate logic values on the associated signal nets, but necessitate a certain noise environment to be established. Moreover, the syndromes of marginal failures are highly ambiguous and unpredictable. For example, the device delay variation induced by power ground noise can manifest itself as intermittent and hybrid timing failures. The extra delay imposed on critical paths can possibly raise setup-time violations, whereas hold-time violations also have high likelihood of taking place if the clock on the launching flip-flops are relatively delayed. It is expected that these issues will become even more severe when the fabrication technology scales to 28nm and below, as the design timing margin in these technology nodes can possibly reduce to tens of picoseconds, far less than the noise induced timing variation.

### 1.1.2 Breaking through structural test limitation

Ideally, a test methodology should examine exactly all the cases that can occur during the functional operation of a chip, no more, no less. An exhaustive functional test program would be the best approximation of such an ideal test; nevertheless, it is a highly impractical option due to the difficulty in developing such a program and the prohibitive cost of applying such a test. Therefore, structural test has been developed as an alternative to functional test. Instead of examining the chip from a functional perspective, the structural test checks whether the modeled faults on the internal nodes of a chip can be correctly activated and observed, so as to flag any failures that contaminate the signal values. Such a test idea, especially the scan-based test, enables easy *automated test pattern generation*  (ATPG), rapid test application as well as high fault coverage, thus being utilized in almost the entire semiconductor industry as the sole solution for production test.

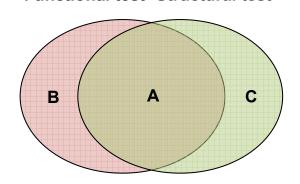

Being a model-based test system, the structural test shares the same shortcomings with any other test system, that is, it can only approach the ideal test goal, but never perfectly match what is desired. The relationship between a structural test and an "ideal" functional test can be illustrated in the Venn diagram shown in Figure 1.1. The two circles in this graph denote the failure coverage of functional and structural tests, respectively. The common region A stands for the failures that are covered by both tests, whereas regions  $\mathbf{B}$  and  $\mathbf{C}$  denote the failures that only manifest themselves in functional test or structural test. If a failure can be detected by both tests, then it is a true functional failure that can be flagged during production screening. Chips with such failures should definitely be discarded to maintain product quality. If a failure can only be detected by the functional test, it will escape from the production screening, thus resulting in an increased DPPM. On the other hand, if a failure only manifests itself in the structural test, then it is from a functional perspective a redundant failure which will be unnecessarily failed by production screening. Discarding chips with solely such failures would result in yield loss. Apparently, a good structural test plan needs to maximize region **A** and minimize regions **B** and **C**.

A further investigation on the failure characteristics reveals that the failure distribution in the aforementioned Venn diagram is skewed. The manifestation of traditional fault types such as stuck-at and transition faults only requires the faults being logically sensitized and propagated for observation. Such a fault manifestation condition can be easily fulfilled in both functional and structural tests. Therefore, the majority of traditional faults is distributed in the common region **A** of the Venn diagram. Marginal failures, such as noise-induced timing violations, though necessitate a much more complex manifestation condition, as a certain noise profile on specific timing paths needs to be developed for fault activation. Since the noise distribution and the status of timing paths in test mode can differ significantly from those of the functional mode, the marginal failures have a high

Functional test Structural test

### A: covered by both functional & structural tests B: covered solely by functional test C: covered solely by structural test

Figure 1.1: Discrepancy between structural test and "ideal" functional test

likelihood to be distributed in either region  $\mathbf{B}$  or  $\mathbf{C}$  of the Venn diagram, thus constituting the major reason for test escape or yield loss.

In old technology nodes where the design margins are large, the signal noise and the associated timing uncertainty can be reasonably well tolerated in both the testing and functional modes, thus resulting in a rather small area of regions **B** or **C**. This ensures a high test quality and low yield loss cost for chips fabricated with these technologies. The failure mechanism shift that occurs with device scaling, as outlined previously, results in the marginal failures being the dominant failure scenarios for nanometer scale designs. This significantly increases the area of regions **B** and **C**, leading to a highly elevated DPPM and yield loss.

Maintaining high test quality and low test cost forces the test methodology to adapt to the failure mechanism shift. Yet such a change is subject to a strong practical constraint that needs to be enforced for current and prospective IC technologies, that is, the compatibility of the test methodology innovation with the structural test platform needs to be guaranteed in order to reuse the expensive hardware and software infrastructure currently employed in the test floor. Such a goal can be achieved if the structural test can approximate the functional mode behavior so as to detect functional-mode-only failures and avoid the manifestation of test-mode-only failures. The approximation of functional operation, though, requires the understanding of design knowledge that is tightly coupled with the behavioral and physical level behavior of the circuit. From a behavioral design perspective, the differentiation between functional-mode and test-mode paths can help determine the noise optimization targets for different timing paths in the circuit. The estimation of noise profile and the resulting timing impact can be attained through the use of physical design information such as the clock tree structure, power distributed network, and the layout parasitics. A coherent ATPG and test application scheme, guided by the aforementioned design knowledge, is needed to model the circuit behavior in different modes and generate/apply such tests.

### 1.1.3 Exploring design perspectives in diagnosis

The failure mechanism shift not only raises the need for test methodology adaptation, but also degrades and even invalidates the traditional failure analysis techniques. With the high power ground noise and the associated timing uncertainty in nanometer scale designs, multiple faults with mixed timing violation types can exist. The intermittent fault manifestation, and the possible interaction between multiple faults, result in a highly ambiguous fault syndrome, making it almost impossible to create clear fault dictionary for diagnosis. Furthermore, the syndromes of marginal faults can be highly conflicting with the ones of gross defects. Therefore, traditional diagnosis approaches based on gross fault assumptions can lead to incorrect conclusions in a marginal failure scenario.

The key to resolving a diagnostic problem is the establishment of a small set of valid failure hypotheses and the extraction of strong signals that can differentiate distinct hypotheses. The design knowledge, especially the physical design information, is needed once again to attain these goals in the ambiguous diagnosis space induced by marginal failures. For example, the statistical timing information can be utilized to estimate the failure likelihood of different circuit nodes in the volume diagnostic data, thus filtering out the ambiguity induced by the randomness in individual failure manifestation. Using the design information to guide diagnosis not only avoids the search of irrational failure scenarios, but provides information regarding the criticality of valid failure hypotheses. This enables the designers to focus on the most yield-critical design weakness during re-spin, significantly expediting the time-to-revenue.

## 1.2 Challenges to be addressed

The development of the aforementioned marginal failure aware test and diagnosis scheme encounters a number of challenges.

#### **1.2.1** Paradox between overtesting and undertesting

Due to the difficulty of pre-silicon verification of marginal failures, at-speed test is incorporated as a standard procedure and plays an important role in today's manufacturing test flow in order to screen out any timing-related failures. Nonetheless, due to the discrepancy between the test mode and functional mode outlined previously, this test potentially yields misleading results from a product quality point of view. More specifically, two major disadvantages can be observed for conventional at-speed test.

- The test operations, especially the scan steps, result in highly non-functional transitions of circuit states, resulting in a large deviation of the noise profile from the functional operation. In scan mode, the density of device toggling activities is typically much higher than that of functional mode, potentially leading to an overtesting of good parts. This in turn causes yield loss of the products.

- The noise profile of modern chips is a compound behavior of high, middle and low frequency noises introduced by different components of the design. The single at-speed capture cycle can only target the high speed noise of the chip, as it terminates before the middle and low frequency noise has time to fully develop. On the other hand, the regular operation of the chip needs to execute through a sequence of functional cycles, which gives sufficient time for full noise development. As a result, current at-speed test can also lead

to under-testing of marginal parts, as it fails to examine the worst-case noise situation. This introduces a risk of test escape and increases the DPPM of the products.

Delivering high quality test for noise-induced timing failures necessitates the resolution to the paradox between two somewhat conflicting requirements: avoiding over-testing incurred by excessive non-functional noise and reducing test escapes incurred by the lack of functional noise coverage. This raises a number of challenging questions for production test development. Which set of timing paths mainly contributes to overtesting? Which set of timing paths has not been examined thoroughly during at-speed testing? How to organize the design information during test generation? How to transform the test patterns to change the noise level on a target timing path? How to account for other ATPG constraints, such as test compression and compaction, during test pattern transformation? All these issues need to be clearly addressed in order to develop a test program that can fulfill both requirements.

### **1.2.2** Noise estimation and control in test generation

Developing appropriate tests for marginal failures necessitates accurate estimation of power ground noise. Traditional noise aware test generation techniques mainly utilize the weighted switching activity (WSA) metric for noise estimation. This metric has a high correlation with the current amplitude drawn in each cycle, thus being reasonably accurate in estimating the amplitude of high frequency noise. However, as a cycle-based current metric, it does not take into consideration the resonance effect of the noise, thus being incapable of estimating the middle frequency noise which spans multiple cycles.

In nanometer scale ICs which typically operate within a high clock frequency range, the development of the worst-case noise in functional operation requires multiple at-speed cycles. An accurate noise estimation framework, considering the noise accumulation effect across multiple cycles, is thus needed to guide test generation. In contrast to the simple WSA metric, this estimation necessitates the consideration of multiple factors, such as the noise resonance period, the characteristics of the power distribution network, the positions of the cells in the layout, and so on. Creating a mathematical model that accurately quantifies the impact of the aforementioned factors is a critical technical challenge that needs to be overcome.

An even more challenging issue is the development of the desired noise level during test generation. For example, delivering the highest test quality necessitates the approximation of the worst-case noise on the targeted functional-mode path. Yet there are multiple degrees of freedoms during test generation that can impact the ultimate noise level. Firstly, a test cube contains a large set of unspecified bits. Different filling strategies of these unspecified bits will result in a completely distinct noise profile in the circuit. Secondly, the number of at-speed cycles used in the test determines the length of the noise accumulation process, thus also having a strong impact on the noise profile. A test generation engine needs to examine all these variables in order to identify the test pattern that generates the expected noise level.

Both the noise estimation and test generation processes face the challenge of high computational cost. The search of the most appropriate test pattern is in fact an intertwined process of noise estimation and test transformation. The large number of unspecified bits in the test cube results in a huge search space, whose size exponentially increases with the number of scan cells in the design, not to mention the need for examining the impact of each test pattern candidate across multiple clock cycles. If dynamic noise simulation is used during the search process, the overall search time cost would become prohibitive. Improving the efficiency of noise estimation and test transformation methodology with negligible impact on accuracy, thus becomes imperative for this test scheme to be practically applicable in the industrial flow.

### **1.2.3** Extracting clear diagnostic information

Most traditional diagnosis approaches rely on logic tracing and simulation to establish a mapping between the fault hypotheses and syndromes. The effectiveness of such a somewhat deterministic strategy highly depends on the uniqueness and the strictness of the assumed fault behavior. If the fault behavior can be strictly simulated, accurate fault information can be derived by analyzing the logic information extracted from the scan patterns. The permanent fault assumption defines a highly strict behavior model. Therefore, the utilization of the logic analysis strategy on such models delivers a good diagnostic resolution.

Traditional methodologies approach the diagnosis problem using both positive and negative information. They not only use the observed failure syndromes to identify the range where the fault locates, but also utilize the correct portion of the circuit output to exclude certain regions being the fault candidate. However, the failure mechanism shift has invalidated the fundamental assumptions of traditional approaches. For nanometer designs, marginal defects introduced by design and process weakness have become the dominating factor for yield loss, thus constituting one of the top priorities in silicon debugging. The intermittent manifestation and the multitude of such faults result in a highly ambiguous fault behavior, significantly increasing the difficulty in diagnosis. The inherent ambiguity of the failure mechanism observed in nanometer designs reduces the information that can be extracted through logic analysis, leading to a degraded diagnosis resolution, as detailed subsequently. One contributing factor to the ambiguity consists of the unpredictable fault manifestation. Under this situation, a correct circuit output does not necessarily mean the absence of faults. In fact, it can be due to the quietness of the fault in an individual diagnosis run. Another source of ambiguity stems from the interaction between multiple faults. Due to the fault interaction, the fault effect of individual defects can possibly be canceled. This once more shows that the absence of failure syndromes cannot be used for fault exclusion, significantly reducing the information that can be extracted through logic analysis.

The degraded effectiveness of logic analysis results in a large ambiguity space that requires further pruning. Overcoming this challenge necessitates solutions to the following fundamental questions:

• How to extract extra information to guide the pruning of the ambiguity space?

• How to explore the large pruning space in a computationally efficient manner?

# 1.3 Contributions of This Thesis

To address the industrial need for a fast-to-revenue silicon verification plan in current and forthcoming decades, this thesis work focuses on the development of a marginal-failure-aware test and failure analysis framework. Multiple innovative techniques, which resolve the challenges outlined in the last section and provide the theoretical underpinnings of the proposed framework, are presented in this thesis. The contributions of this work are summarized as follows.

- A scan-mode noise minimization technique for scan architecture utilizing linear compression circuitry, the most widely used DFT architecture in industry. This methodology is capable of identifying the noise-friendly compression seeds of a linear compression system in the face of the strong ATPG constraints imposed by the linear compression scheme, thus minimizing the overtesting risk induced by the excessive scan-mode noise and timing uncertainty. A concurrent compression/compaction framework is furthermore presented based on the noise minimization technique to ensure a noise-safe scan process with negligible impact on the test volume compression ratio.

- A multi-functional-cycle delay test scheme to detect the marginal timing failures under worst-case functional noise situation. This test scheme applies a pre-calculated number of at-speed functional cycles, with the last cycle sensitizing the target path. This strategy not only enables the worst-case noise development, but results in a more "functional" circuit state transition in the capture cycle, thus creating a noise profile that is highly similar to the true functional one. This test delivers higher delay test quality at a lower risk of false alarm, thus benefiting the product cost from both the yield improvement and the DPPM reduction perspectives.

- A failure analysis methodology, capable of diagnosing both permanent and marginal timing failures in scan circuitries. This diagnosis technique closely

approximates the behavior of the realistic failure mechanisms observed in silicon, and presents a new perspective of understanding and analyzing the syndrome of the marginal failures. The diagnostic results not only pinpoint the physical region of the failures, but indicate the relative criticality of each failure, thus providing a strong guidance to the design optimization and respin task.

• A fast-to-revenue silicon optimization framework, capable of coordinating the test optimization, failure analysis and design re-spin tasks for early production. This framework explores the possibility of performing failure-aware design verification using the diagnostic information before each tape-out. Such a highly guided process can significantly reduce the number of re-spins.

All the aforementioned techniques are developed with the consideration of enabling algorithmic automation and delivering compatibility with the mainstream hardware/software infrastructure so as to ensure a seamless embedding of these techniques into the industrial flow. The successful utilization of these techniques in industry will enable a low cost yet high quality production with a highly reduced time-to-revenue cycle for current and next generation integrated circuits.

## 1.4 Roadmap

The rest of the thesis is organized as follows. Chapter 2 reviews the stateof-art and analyzes the limitations of existing solutions of handling noise in testing and diagnosis. Chapter 3 presents an overview of the envisioned marginal-failureaware test and failure analysis framework, focusing on the utilization of design knowledge in guiding test optimization and diagnostic feature extraction. Chapter 4 introduces a scan-mode noise minimization technique which reduces the yield loss due to overtesting of test-mode-only paths. Chapter 5 focuses on the undertesting issue and presents a technique to detect functional timing path failures induced by wide-bandwidth power ground noise. The collaborative use of techniques in Chapters 4 and 5 engenders a comprehensive test plan that maximally approximates the effectiveness of an "ideal" functional test in a low cost structural test platform. Chapter 6 presents a diagnosis methodology, targeting the marginal timing failures in the scan architecture. Chapter 7 presents a flow of integrating the proposed test and failure analysis approaches into a fast-to-revenue silicon verification framework, with a special focus on the failure-aware design verification guided by diagnostic information. Finally, Chapter 8 summarizes the proposed framework and subsequently outlines a set of possible future research directions.

# Chapter 2

# **Related Work**

While the failure mechanisms of the VLSI circuits become increasingly complex, the development of innovative test and diagnosis methodologies for addressing these emerging failures constitutes a focal point in the VLSI test community. Researchers from both industry and academia have started to address this issue from various perspectives.

The research practice on this topic is mainly driven by the industrial observation and needs. First of all, it has been observed in almost all industrial designs that the scan activity induces an exceedingly high power and noise level due to the high toggling rate, resulting in a large number of scan chain timing failures. Therefore, researchers have focused on the development of scan power/noise reduction techniques. Various approaches, ranging from test software optimization to hardware design modification, have been proposed to tackle this problem. In addition to the scan issue, the noise-induced timing failures in the capture phase of the structural testing have become an increasingly critical problem, especially in high frequency designs. The noise treatment in the capture phase is even much more complicated than that in the scan phase, as the determination of the proper noise level and distribution in the capture phase is a highly controversial issue. A number of techniques, with possibly conflicting perspectives, have been proposed to handle the noise as well as the timing failures in capture phase. Some approaches focus on the minimization of capture noise to avoid false alarms, whereas the others aim to increase the noise so as to detect more faults. The need for controlling noise during testing has also motivated the research on test noise estimation. A variety of noise estimation models, at distinct abstraction levels, has been proposed to guide the ATPG process. The effort in ATPG and DFT optimization outlined above mainly helps improve test quality and reduce yield loss. Nonetheless, the improvement of the design and fabrication quality necessitates a deep understanding of the root causality of the emerging failures in the chip. This has motivated a large amount of research work devoted into the diagnosis of timing failures, especially the ones occurring in scan circuitries. These techniques aim to identify the locations of the failures, thus providing clues about possible design and fabrication weakness.

Although the previous efforts exhibit a certain level of effectiveness in addressing some representative marginal failures observed in a few application domains, they fall short of resolving the fundamental challenges faced by the industry, namely, the discrepancy between functional operation and structural test, and the complicated syndrome of hybrid failure manifestation. The rationales and assumptions behind these approaches are typically based on the empirical knowledge of certain designs and extreme situations<sup>1</sup>. These rather simplified assumptions fail to deliver satisfactory test and diagnosis quality in real silicon, thus leading to a much lengthened time to revenue. A detailed review is presented in the remaining parts of this chapter to clearly illustrate the limitations of the current state-of-art.

## 2.1 Noise estimation in ATPG

Controlling noise effect in test generation requires an accurate estimation of the noise waveform. The noise estimation models proposed in the literature can be mainly grouped into two categories, namely, the switching activity based models and simplified voltage-drop models. This section provides an in-depth overview of these models from the perspectives of efficiency and accuracy.

<sup>&</sup>lt;sup>1</sup>For example, most diagnosis approaches assume ideal timing fault models with deterministic fault manifestation behavior, a situation that typically cannot occur in real silicon.

#### 2.1.1 Switching activity based model

It has been widely observed that the switching activity and the noise amplitude exhibit a positive correlation. The switching activities of transistors cause current to be drawn from the power supply or to the ground, resulting in a rapid change of the instantaneous current. This in turn results in a sharp droop of the power supply voltage or a strong bounce of the ground voltage. Given this observation, the intensity of the switching activity has been utilized as a noise metric in a large number of works.

The basic switching activity model simply counts the number of toggles in each clock cycle. Although computationally highly efficient, this model only captures the first order effect of switching activity on noise generation, thus being highly inaccurate. This simple model has been utilized in a number of early poweraware ATPG and DFT techniques [32, 22, 25, 75, 110]. In order to improve the model accuracy, the load capacitance of each toggling gate has been incorporated into the model so as to reflect the impact of the load on the amplitude of the current. Based on this idea, the weighted switching activity (WSA) model has been developed and widely utilized in the test literature [76, 77, 107, 105, 80, 72, 4]. This metric assigns distinct weights to the switching activities of different gates, with the weight being the number of gate fan-outs plus one. The weight value to some extent tracks the current contribution of the toggling gate and its loads, thus approximating the realistic situation more accurately. Although the use of the WSA metric provides a computationally efficient way of estimating the current demands and noise intensity in global power ground nets, it fails to consider the noise distribution and fluctuation in local regions of the layout. In fact, the noise amplitudes in distinct layout regions can skew significantly as a result of skewed switching activity and different power distribution network design. To provide the regional noise information, the layout-aware weighted-switching activity metric [56, 67, 116, which considers the noise effect of each local regions in the layout, has been proposed by several works that focus on the noise optimization in certain timing critical areas.

The switching activity based models in general provide reasonably accu-

rate noise estimation at very low computational cost. Especially under low clock frequency situation where the cycle-based dynamic noise constitutes the major noise type, these metrics exhibit a very high correlation with the noise amplitude. Therefore, this approach is highly preferable in estimating the noise in low frequency modes such as the scan phase of structural testing. Nonetheless, these metrics fail to account for the possible noise accumulation across multiple cycles, thus being highly inaccurate in a high clock frequency mode such as the at-speed capture phase of structural testing.

### 2.1.2 Voltage-drop model

The switching activity based models provide an indicator of the noise amplitude, but fail to estimate the noise waveforms. For certain applications such as noise-aware timing simulation, it is necessary to attain the profile of the noise as a function of time, thus necessitating a voltage based noise estimation model. A number of voltage-drop estimation models have been proposed in the literature [51, 50, 27, 100, 5, 101, 12, 11, 60, 7]. Despite the diversity in the specific forms, these models share the similar principle of estimating the voltage variation in an extracted RLC (Resistance, Inductance and Capacitance) model of the circuit. The circuit model characterizes the silicon parameters at different levels, including:

- The package RLC information such as the leads, the ball grids, and the power planes

- The RLC information of redistribution layers (RDL)

- The RLC information of power switches

- The RLC information of the on-chip power distribution network (PDN)

- The RC information of device parasitics

- The RC information of intentionally added decoupling capacitance

With the extracted circuit model, the supply voltage waveform as a result of the device toggling current can be attained through an analytical computation or simulation. These approaches in general provide more comprehensive noise information compared to the switching activity based models, delivering more flexibilities in noise optimization during the ATPG process. The estimation accuracy highly depends on the quality of the circuit models and the simulation/computation algorithm. The computational cost of these approaches is typically much higher than the switching activity based estimation, necessitating the ATPG algorithm to intelligently utilize the noise information so as to minimize the number of noise estimation runs.

### 2.2 Handling noise in testing

The noise estimation techniques outlined in the previous section enable the researchers to tune the noise level in order to fulfill certain testing goals. Because of the strong industrial interest, the treatment of noise during ATPG and DFT design becomes a focal point of the testing research when the technology nodes enter the nanometer range. An appreciable number of techniques, with possibly conflicting perspectives and goals, have been proposed in the literature to address this issue. One category of techniques focuses on the minimization of test mode noise in order to avoid yield loss, whereas others aim to increase the noise level to guarantee the detection of noise related failures. Both opinions come with their own rationales that might be related to the specific characteristics of chip design, application domain, and quality requirement. Nonetheless, these experience-based optimization strategies fail to provide a coherent theoretical framework for guiding the noise handling in large designs that face complex failures. In this section, we provide a review of these techniques and illustrate their limitations.

### 2.2.1 Test noise minimization

Test noise minimization, as a main strategy for reducing overtesting, has been extensively studied in the literature. A set of approaches utilizes special ATPG algorithm to attain the noise reduction goal, whereas the other methodologies focus on the development of DFT architectures that can restrain the noise generation.

### ATPG for noise reduction

This category of approaches exploits the flexibility of the ATPG process in order to generate test patterns capable of reducing the test noise in addition to meeting classic ATPG goals.

A number of techniques have been proposed to process the *don't cares* in the test cubes to reduce the transition densities during test mode [9, 113, 107, 106, 62, 104, 24, 109, 66, 103, 70, 102, 57]. These techniques aim to identify an appropriate 0/1 assignment of the *don't care* bits in test cubes to reduce switching activity during test application, thus lowering the power ground noise. Wen et al. [107], for example, propose an X-filling method for reducing the number of transitions in scan flip-flops during capture mode. This approach increases the matching level between the launch cycle and the capture cycle flip-flop states by performing a set of matching heuristics. Several extended approaches [70, 106], following a similar basic strategy, are proposed to improve the effectiveness of this methodology.

The basic X-filling approaches only consider the fault activation and propagation constraints during ATPG, which is a highly impractical assumption. Since almost all modern industrial designs heavily use test compression techniques, the X-filling strategy of an ATPG process needs to maximally fulfill the constraints for both the noise reduction and test compression goals. Several research works have been proposed to resolve this challenge. The work in [62] proposes a capture power reduction technique dedicated to the nonlinear encoding compression scheme proposed in [104]. The work in [109] performs X-filling instead of DFT insertion to reduce test power. The X-bits are sequentially filled in a greedy manner according to their power impact. Linear constraint propagation is performed during the X-filling process to guarantee the compressibility of the filled test cubes. The technique proposed in [66] improves the aforementioned X-filling technique by filling the X values according to the power impact of the free bits in the seeds and performing a post-processing adjustment of the filled test cube. A low power compression technique based on scan chain partitioning is proposed in [103]. This technique clusters scan cells that have similar test data distribution, thus enabling an easy encoding of the test data within the same scan chain partition and reducing the toggling activities during scan.

In addition to the standard X-filling approaches, researchers have proposed several other ATPG ideas for test power and noise reduction. The technique proposed in [41] identifies an input control pattern at the primary inputs of a full-scan circuit. During test application, the input control values freeze a large number of switching activities at the immediate logic load of the scan flip-flops, thus reducing the power and noise in the combinational part of the circuit. Sankaralingam et al. propose a static compaction technique to minimize the test power dissipation [83]. Appropriately selecting the merging order of test cubes during test compaction reduces both average and peak power of the final test set. A similar approach is proposed in [56], which guides the test compaction algorithm using a layout-aware switching activity metric in order to meet a pre-defined test noise threshold in every local region of the chip layout. The noise threshold employed in these techniques is typically determined based on the designers' experience, which might be error-prone for today's large designs.

The aforementioned software-based approaches can be easily adopted into the ATPG algorithm without incurring hardware overhead. Nonetheless, the successful utilization of these approaches necessitates the resolution of the challenge imposed by various ATPG constraints which possibly limit the effectiveness in noise reduction.

#### DFT architecture for noise reduction

A set of approaches focuses on reducing test power through scan architecture modifications [25, 88, 30, 110, 111, 82, 108, 9, 3]. Sinanoglu et al. propose a technique of performing bijective transformations on scan patterns through the insertion of simple logic gates into the scan chains [88]. The transformed patterns that traverse through the scan chains have a low level of toggling activities, thus being able to reduce the power and noise in the scan phase with no impact on test application time. The technique proposed in [108] transforms the standard scan architecture to a set of selectable, separate scan paths. In low power testing mode, each scan path is loaded and observed individually through a bypassing circuitry. An adaptor circuit is inserted into the DFT structure to control the adaptation of the scan chains during the scan phase. This technique restrains the scan behavior in local scan paths, and enables the majority of the scan architecture to remain quiet, thus significantly reducing the overall toggling activities in the scan chains. Lee et al. propose an interleaving scan architecture based on adding delay buffers among the scan chains [58]. This scheme results in staggered toggling activities within the scan chains. Although the average power consumption remains almost unchanged, the peak power and noise can be reduced with the skewed toggling activities.

In addition to scan chain modification, techniques based on scan data or clock suppression have also been proposed to attain power and noise reduction [24, 84, 8, 71, 10, 99, 112, 31]. In [24], a DFT design is proposed to reduce the test power in a linear compression environment by inserting gating circuitry to generate sequences of constant values in the test cube. Sankaralingam et al. propose a scan architecture that can disable the clocks of a subset of scan chains [84]. Since the fault detection process typically requires very few scan chains to be activated, the clock of a large number of scan chains can be disabled during test application. This not only reduces power and noise in the logic circuitry, but lowers power in the clock tree as well. A similar approach is proposed in [8], which gates off the clock of partial scan chains during test application. Some researchers also look into the utilization of a clock gating approach in reducing the power ground noise in capture mode. The technique proposed in [112] selectively gates off for each test pattern the clock paths of circuit modules that have no impact on the activation and observation of the targeted faults. Furukawa et al. propose a technique which utilizes the clock-gating and X-filling in a collaborative manner to reduce the toggling activity in at-speed capture cycle [31].

The hardware-based techniques typically are quite effective in power and

noise reduction as they encounter much fewer ATPG constraints compared to the software-based ones. Nonetheless, these techniques necessitate either the insertion of special DFT circuitries or the modification of traditional test application schemes. The resultant hardware overhead and design difficulty restrain the application of these techniques.

### **Technical limitations**

The noise minimization approaches outlined previously are able to reduce the marginal failure rate during production test, thus significantly improving the yield. However, a blind minimization of the noise can result in the design weakness escaping from the test, as the test fails to examine the normal noise level encountered during functional operation. This leads to a degraded test quality and an increased DPPM. To avoid this unpalatable undertesting issue, the test minimization process needs to intelligently differentiate the test mode noise from the functional one and focus on the noise reduction in test-only area. None of the aforementioned techniques have looked into this issue, thus failing to deliver a satisfactory solution to production test plans that require high test quality.

### 2.2.2 Noise failure detection

Given the undertesting risk induced by the noise minimization techniques, another set of methodologies, in contrast, focuses on the maximization of power ground noise in order to reduce test escapes [79, 80, 68, 65, 67].

The work in [79] provides a silicon case study of an Intel microprocessor design, and shows that regular at-speed test is incapable of detecting the worst-case noise in functional operation. The technique proposed in [80] presents an algorithm to generate test patterns that result in high switching activities at targeted wires so as to stress the circuit with higher voltage droop. In [68], layout information is utilized to guide the IR-drop maximization in the neighborhood of the target devices. The techniques in [65, 67] extract functional constraints of the circuit and embed them into the search for a test pattern with maximal IR-drop so as to approximate the functional operations more closely. The utilization of these techniques to some extent improves the test coverage on marginal failures induced by design weakness, potentially delivering higher test quality. Nonetheless, these techniques share the same shortcomings as the noise minimization techniques, that is, there is no differentiation between test mode and functional mode behavior. In all probability, the increased noise level can worsen the timing margins of non-functional paths, thus resulting in the good parts failing the test. As a result, the test quality improvement is attained at the cost of highly increased yield loss. Moreover, since these techniques are all based on the conventional single-capture cycle schemes and fail to consider the impact of the noise effect that spans multiple at-speed cycles, their capability to approximate the true functional noise profile and detect noise-induced failures still remains highly limited.

### 2.3 Scan architecture failure analysis

The improvement on the design and test flow needs to be accompanied by the innovation in failure analysis techniques, as any optimization on the design and test side needs to be based on the silicon information learned during failure analysis. As a result of intensive test mode noise, marginal failures in scan architecture have become one of the most dominating and complex failure mechanisms for failure analysis, and have drawn increasing research attention. The fault diagnosis flow for a scan architecture can be typically decomposed into two stages, namely, a scan chain diagnosis step that provides the information about the scan cell failure locations and probabilities, and a clock buffer pruning step to identify the faulty clock buffers based on the failing scan cell information. In this section, we provide an overview of the previous work for both steps.

### 2.3.1 Scan chain diagnosis techniques

A considerable number of approaches have been proposed in the literature to address the scan chain diagnosis problem. A comprehensive survey of this area has been provided in [46]. In general, these approaches can be categorized into three groups.