# UCLA UCLA Electronic Theses and Dissertations

**Title** Neural Spike Sorting in Hardware: From Theory to Practice

Permalink https://escholarship.org/uc/item/73x6m54x

Author Gibson, Sarah Paige

Publication Date 2012

Peer reviewed|Thesis/dissertation

UNIVERSITY OF CALIFORNIA

Los Angeles

# Neural Spike Sorting in Hardware: From Theory to Practice

A dissertation submitted in partial satisfaction of the requirements for the degree Doctor of Philosophy in Electrical Engineering

by

### Sarah Paige Gibson

© Copyright by Sarah Paige Gibson 2012

# Neural Spike Sorting in Hardware: From Theory to Practice

by

### Sarah Paige Gibson

Doctor of Philosophy in Electrical Engineering University of California, Los Angeles, 2012 Professor Dejan Marković, Chair

Brain-machine interfaces require real-time, wireless signal acquisition systems. However, wireless transmission of raw data is impossible for high-channel-count systems given the power constraints. Data rates could be reduced, thereby enabling wireless data transmission, by performing spike sorting—mapping each recorded action potential to the neuron that generated it—on a DSP at the recording site and transmitting only the sorting results. Our first objective was to design such a DSP. We first developed a standardized dataset and methodology in order to perform an extensive, unbiased comparison of published spike-sorting algorithms to determine which would be most appropriate for hardware implementation. We then considered various implementation issues, such as whether analog or digital spike detection is more efficient and how best to quantize neural signals. This work led to two low-power digital spike-sorting chips.

Our second objective was to provide an offline solution for the research setting that would accelerate the processing of data that has already been recorded using conventional data-acquisition systems. Here, we present an FPGA-based spike-sorting platform that can increase the speed of offline spike sorting by at least 25 times, effectively reducing the time required to sort data from long experiments from several hours to just a few minutes. We attempted to preserve the flexibility of software by implementing several different algorithms in the design, and by providing user control over parameters such as spike detection thresholds. The dissertation of Sarah Paige Gibson is approved.

Richard Joseph Staba Abeer A. H. Alwan Jack W. Judy Dejan Marković, Committee Chair

University of California, Los Angeles

2012

# TABLE OF CONTENTS

| 1        | Intr | oducti  | on                                            | 1  |

|----------|------|---------|-----------------------------------------------|----|

|          | 1.1  | Electr  | ophysiology and Extracellular Recording       | 1  |

|          | 1.2  | Curre   | nt State of the Art                           | 3  |

|          | 1.3  | Objec   | tives                                         | 4  |

|          |      | 1.3.1   | Need for Wireless Recording Systems           | 5  |

|          |      | 1.3.2   | Need for Hardware-Accelerated Data Processing | 7  |

| <b>2</b> | Spil | ke Sort | ting                                          | 8  |

|          | 2.1  | Signal  | Composition                                   | 8  |

|          |      | 2.1.1   | Unit Activity                                 | 8  |

|          |      | 2.1.2   | Local Field Potential (LFP)                   | 2  |

|          | 2.2  | The S   | pike-Sorting Process                          | 3  |

|          | 2.3  | Classi  | fying Spike-Sorting Algorithms                | 4  |

|          | 2.4  | Overv   | iew of Spike-Sorting Algorithms               | 6  |

|          |      | 2.4.1   | Detection                                     | 6  |

|          |      | 2.4.2   | Alignment                                     | 9  |

|          |      | 2.4.3   | Feature Extraction    2                       | 21 |

|          |      | 2.4.4   | Dimensionality Reduction                      | 24 |

|          |      | 2.4.5   | Clustering                                    | 27 |

|          |      | 2.4.6   | Alternative Methods for Spike Sorting         | 34 |

|          | 2.5  | Challe  | enges in Spike Sorting                        | 87 |

|          |      | 2.5.1   | No Ground Truth                               | 37 |

|          |      | 2.5.2   | Non-Gaussian Noise                            | 0  |

|   |     | 2.5.3    | Non-Stationarities                      |  | 40 |

|---|-----|----------|-----------------------------------------|--|----|

|   |     | 2.5.4    | Overlapping Spikes                      |  | 41 |

|   | 2.6 | Single   | vs. Multichannel Signal Processing      |  | 41 |

|   | 2.7 | Contro   | wersy                                   |  | 42 |

|   | 2.8 | Conclus  | sion                                    |  | 45 |

| 3 | Alg | orithm   | Evaluations                             |  | 47 |

|   | 3.1 | Introdu  | uction                                  |  | 47 |

|   | 3.2 | Test Da  | ata                                     |  | 48 |

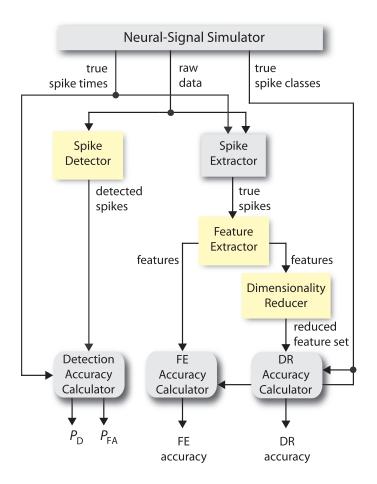

|   | 3.3 | Testing  | g Methodology                           |  | 49 |

|   |     | 3.3.1    | Accuracy Calculations                   |  | 49 |

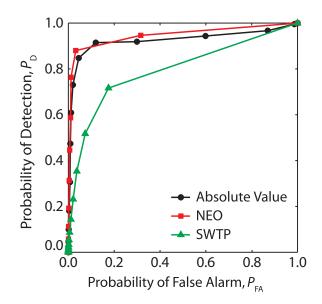

|   |     | 3.3.2    | Receiver Operating Characteristic (ROC) |  | 53 |

|   |     | 3.3.3    | Complexity Calculations                 |  | 53 |

|   |     | 3.3.4    | Assumptions                             |  | 55 |

|   | 3.4 | Algorit  | hms                                     |  | 56 |

|   | 3.5 | Results  | 5                                       |  | 57 |

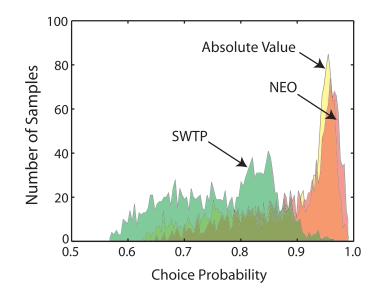

|   |     | 3.5.1    | Spike Detection                         |  | 57 |

|   |     | 3.5.2    | Feature Extraction                      |  | 58 |

|   |     | 3.5.3    | Dimensionality Reduction                |  | 60 |

|   | 3.6 | Discuss  | $\operatorname{sion}$                   |  | 63 |

|   | 3.7 | Conclus  | sion                                    |  | 64 |

| 4 | Ana | alog vs. | Digital Spike Detection                 |  | 66 |

|   | 4.1 | Introdu  | uction                                  |  | 66 |

|   | 4.2 | Method   | $\mathrm{ds}$                           |  | 67 |

|   |     | 4.2.1    | Algorithms                              |  | 67 |

|   |                 | 4.2.2 Analog-to-Digital Converter (ADC)                       | 68  |

|---|-----------------|---------------------------------------------------------------|-----|

|   |                 | 4.2.3 Analog Spike Detection                                  | 69  |

|   |                 | 4.2.4 Effect of SNR and Firing Rate on Analog Detection Power | 74  |

|   |                 | 4.2.5 Digital Spike Detection                                 | 75  |

|   | 4.3             | Results                                                       | 78  |

|   | 4.4             | Conclusion                                                    | 78  |

| 5 | The             | e Effects of Quantization on Spike Sorting                    | 81  |

|   | 5.1             | Introduction                                                  | 81  |

|   | 5.2             | Spike-Sorting Algorithms                                      | 82  |

|   | 5.3             | Quantization                                                  | 84  |

|   |                 | 5.3.1 Detection                                               | 87  |

|   |                 | 5.3.2 Clustering                                              | 87  |

|   | 5.4             | Simulation Results                                            | 88  |

|   | 5.5             | Conclusion                                                    | 92  |

| 6 | $\mathbf{Spil}$ | ke-Sorting ASICs                                              | 94  |

|   | 6.1             | Spike-Sorting Chip                                            | 94  |

|   | 6.2             | Osort Chip                                                    | 95  |

|   |                 | 6.2.1 Clustering Algorithm Evaluations                        | 97  |

|   |                 | 6.2.2 Chip Results                                            | 98  |

| 7 | FPO             | GA-Based Spike-Sorting Platform                               | 103 |

|   | 7.1             | Introduction                                                  | 103 |

|   |                 | 7.1.1 Motivation                                              | 103 |

|   |                 | 7.1.2 Proposed Solution                                       | 104 |

|   |       | 7.1.3  | Design Features                                                                                                                                  |

|---|-------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------|

|   | 7.2   | Functi | ionality of Current Prototype 106                                                                                                                |

|   |       | 7.2.1  | Inputs                                                                                                                                           |

|   |       | 7.2.2  | Processing                                                                                                                                       |

|   |       | 7.2.3  | Outputs                                                                                                                                          |

|   |       | 7.2.4  | Modes of Operation                                                                                                                               |

|   |       | 7.2.5  | <b>GUI</b>                                                                                                                                       |

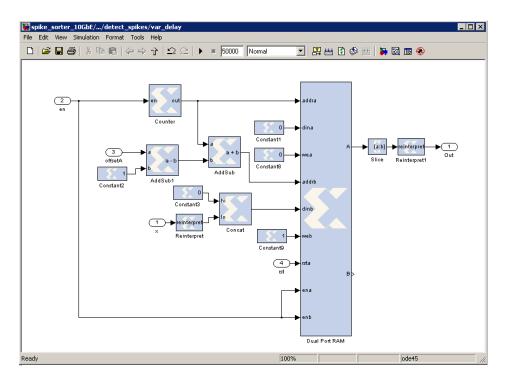

|   | 7.3   | Imple  | mentation $\ldots \ldots \ldots$ |

|   |       | 7.3.1  | <b>Overview</b>                                                                                                                                  |

|   |       | 7.3.2  | Targeted Hardware                                                                                                                                |

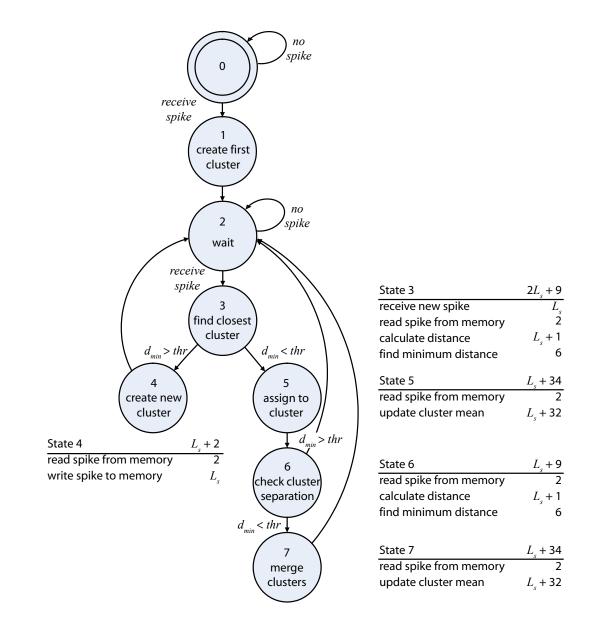

|   |       | 7.3.3  | FPGA Implementation                                                                                                                              |

|   |       | 7.3.4  | Python Wrapper                                                                                                                                   |

|   |       | 7.3.5  | MATLAB Wrapper                                                                                                                                   |

|   | 7.4   | Perfor | mance                                                                                                                                            |

|   |       | 7.4.1  | Accuracy                                                                                                                                         |

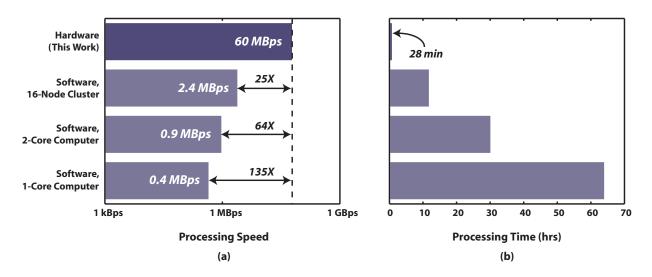

|   |       | 7.4.2  | Processing Speed                                                                                                                                 |

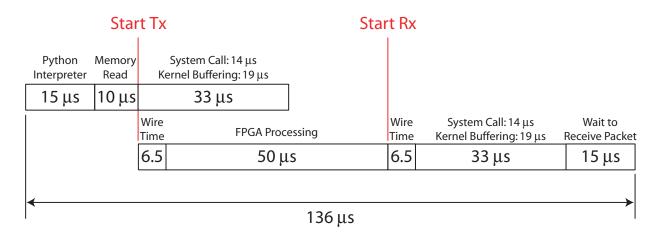

|   |       | 7.4.3  | Timing Analysis    120                                                                                                                           |

|   | 7.5   | Tool A | Availability                                                                                                                                     |

|   | 7.6   | Conclu | usion                                                                                                                                            |

|   | 7.7   | Ackno  | wledgments                                                                                                                                       |

| 8 | Con   | clusio | n                                                                                                                                                |

|   | 8.1   |        | $\mathbf{butions}$                                                                                                                               |

|   | 8.2   |        | ng to the Future                                                                                                                                 |

|   |       |        |                                                                                                                                                  |

| R | efere | nces . |                                                                                                                                                  |

# LIST OF FIGURES

| 1.1  | Example of an electrical signal recorded from a microelectrode                 | 3  |

|------|--------------------------------------------------------------------------------|----|

| 1.2  | Block diagram of the conventional neural recording system                      | 3  |

| 1.3  | Screenshot of a commercial spike-sorting program                               | 4  |

| 1.4  | Example of an experimental setup for neural recordings from rat                | 6  |

| 1.5  | Block diagram of the proposed wireless neural recording system                 | 6  |

| 2.1  | Left: Examples of intracellular action potential and corresponding extracel-   |    |

|      | lular spike. <i>Right</i> : Diagram of a neuron                                | 10 |

| 2.2  | Electrical circuit models of extracellular recording                           | 11 |

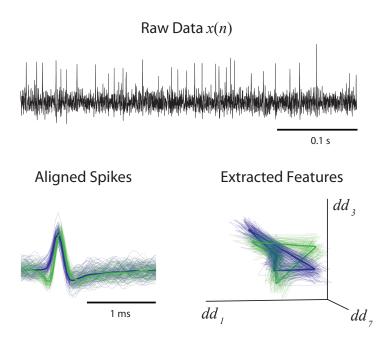

| 2.3  | The signal-processing chain used to obtain single-unit activity                | 14 |

| 2.4  | Examples of pre-emphasized signals and threshold values for three different    |    |

|      | detection methods                                                              | 17 |

| 2.5  | Examples of two different alignment methods                                    | 20 |

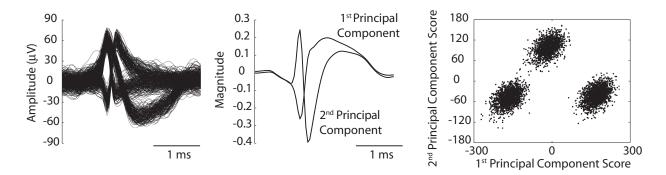

| 2.6  | Sample results of feature extraction using PCA                                 | 22 |

| 2.7  | Example showing the DWT of raw data                                            | 23 |

| 2.8  | Illustration of feature extraction using the integral transform                | 23 |

| 2.9  | Illustration of how feature distribution information can be used in dimension- |    |

|      | ality reduction                                                                | 25 |

| 2.10 | Example showing the calculation of the "dip" statistic for Hartigan's Dip Test | 27 |

| 2.11 | Example execution of the Maximum-Difference Test                               | 28 |

| 2.12 | Example of results of manual cluster cutting on PCA features                   | 29 |

| 2.13 | Example results from clustering 30 seconds of real human data using three      |    |

|      | different clustering methods                                                   | 35 |

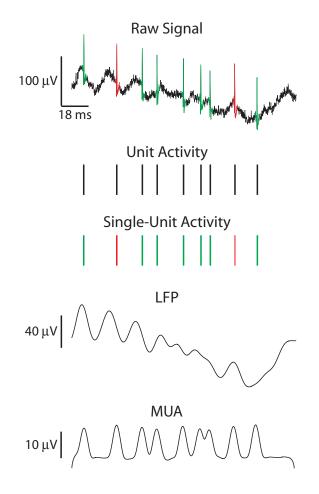

| 2.14 | Example of an MUA signal, compared to the raw signal, unit activity, and LFP   | 44 |

| 3.1  | Signal-processing chain used to evaluate algorithm accuracies                        | 50 |

|------|--------------------------------------------------------------------------------------|----|

| 3.2  | Average spike waveforms used as templates in the test datasets                       | 51 |

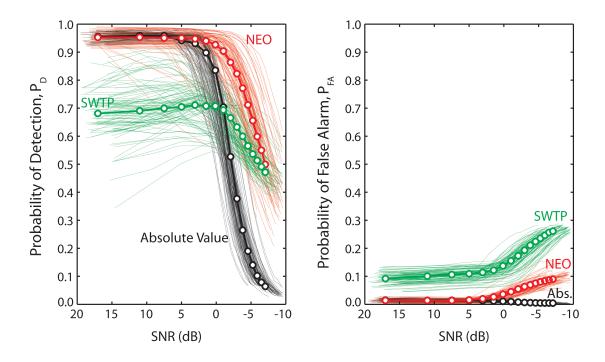

| 3.3  | Median ROC curve for each detection method                                           | 58 |

| 3.4  | Histograms of choice probabilities for each detection method                         | 59 |

| 3.5  | Left: Probability of detection $(P_{\rm D})$ vs. SNR and Right: probability of false |    |

|      | alarm $(P_{\rm FA})$ vs. SNR for each detection method                               | 59 |

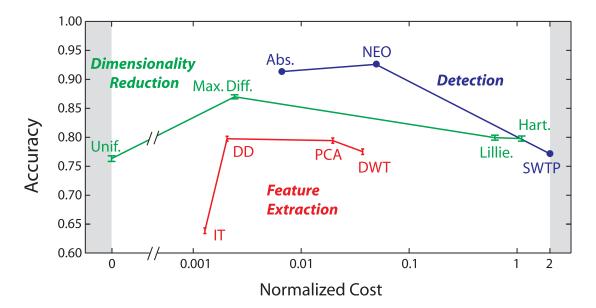

| 3.6  | Accuracy of all datasets and noise levels vs. normalized computational cost for      |    |

|      | each spike-detection, feature-extraction, and dimensionality-reduction algorithm     | 60 |

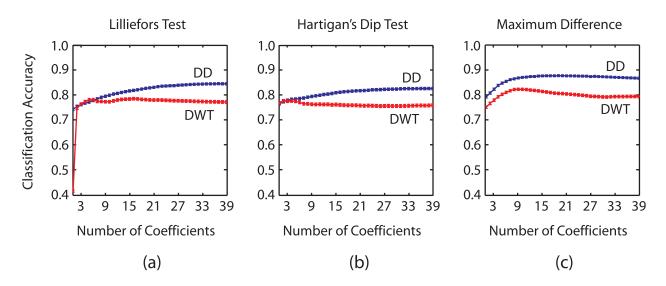

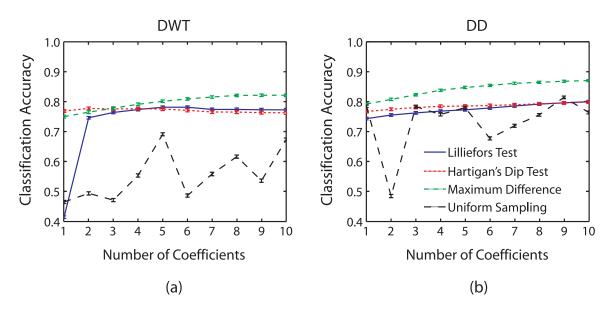

| 3.7  | Mean classification accuracy of each dimensionality-reduction algorithm              | 62 |

| 3.8  | Mean classification accuracy of each dimensionality-reduction algorithm when         |    |

|      | using (a) DWT feature extraction and (b) DD feature extraction                       | 62 |

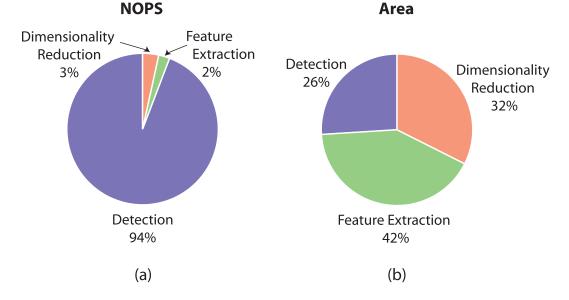

| 3.9  | Pie charts indicating total system complexity: (a) OPS, (b) area                     | 63 |

| 3.10 | Example of data-rate reduction provided by each step of the spike-sorting            |    |

|      | process                                                                              | 64 |

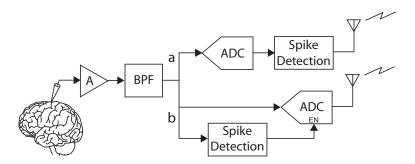

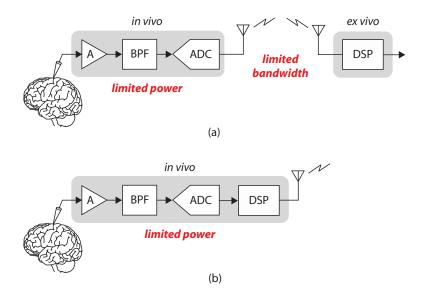

| 4.1  | Block diagram for (a) digital spike detection and (b) analog spike detection .       | 67 |

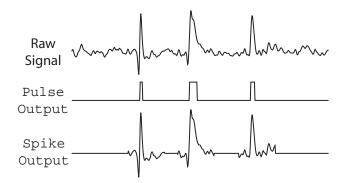

| 4.2  | Outputs of spike detector for each mode of operation                                 | 68 |

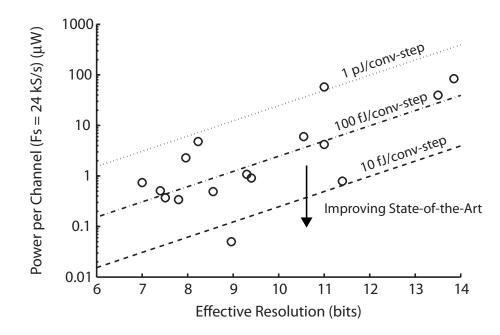

| 4.3  | Performance of recent ADCs, and <i>FoM</i> contours                                  | 70 |

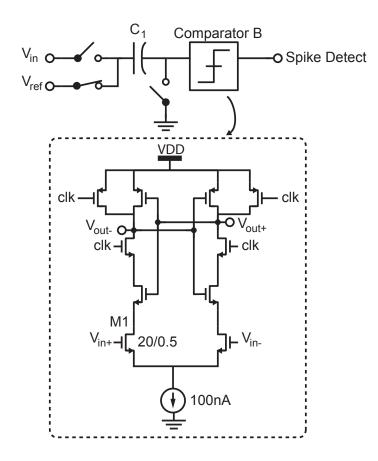

| 4.4  | Schematic for a low-power dynamic comparator                                         | 71 |

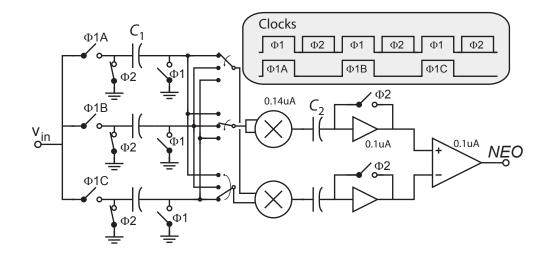

| 4.5  | Implementation of the Nonlinear Energy Operator algorithm in the discrete-           |    |

|      | time analog domain                                                                   | 72 |

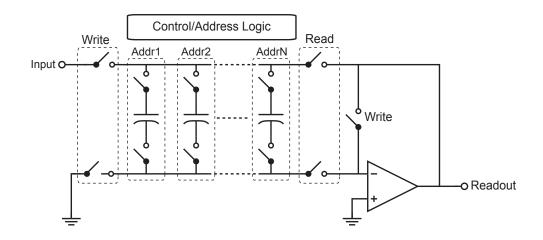

| 4.6  | Implementation of analog memory for buffering of the signal before a spike           |    |

|      | has been detected                                                                    | 73 |

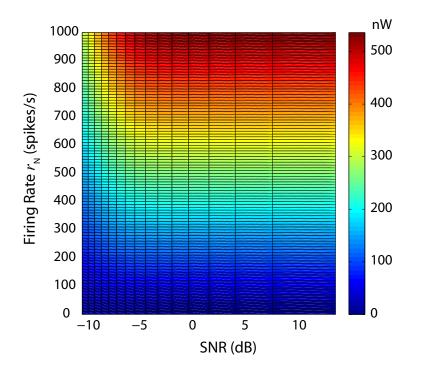

| 4.7  | Variation in power of analog NEO spike detection due to changes in SNR and           |    |

|      | neuronal firing rates                                                                | 75 |

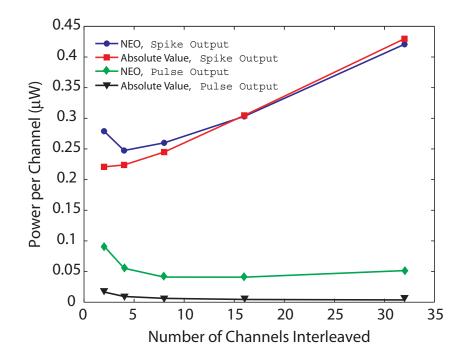

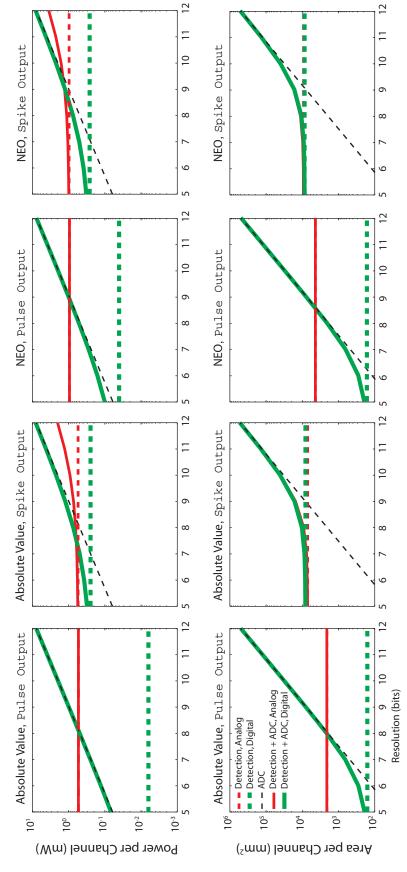

| 4.8  | Power estimates obtained from Synopsys for NEO                                       | 77 |

| 4.9  | Area estimates for NEO as a function of the number of channels interleaved                                                     | 77  |

|------|--------------------------------------------------------------------------------------------------------------------------------|-----|

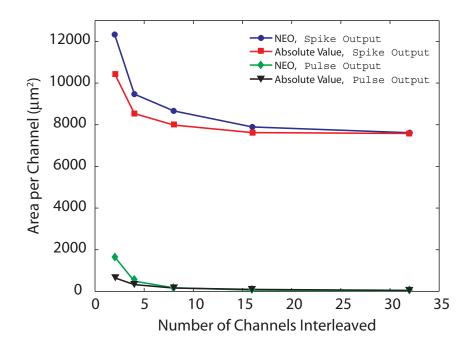

| 4.10 | Power per channel and area per channel for each algorithm and output mode                                                      | 79  |

| 5.1  | Block diagrams for two potential recording systems                                                                             | 82  |

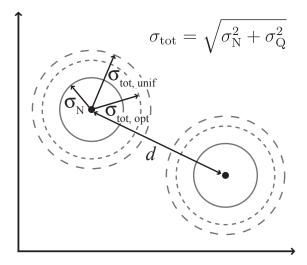

| 5.2  | Plot of received signals in 2-dimensional space                                                                                | 84  |

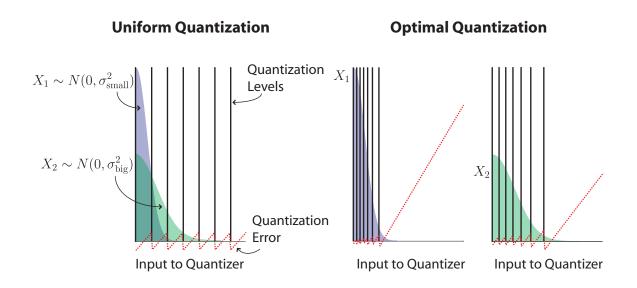

| 5.3  | Examples of uniform and optimal quantization levels for narrow and wide                                                        |     |

|      | Gaussian pdfs                                                                                                                  | 86  |

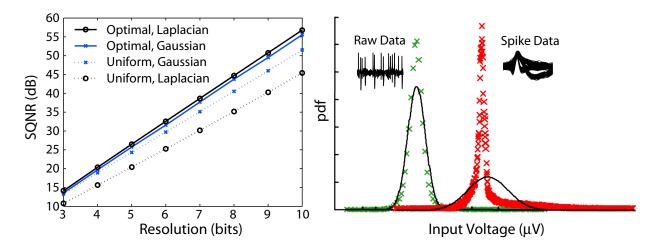

| 5.4  | Left: SQNR vs. resolution for a uniform quantizer compared to the optimal quantizer. Right: Input pdfs for spikes and raw data | 88  |

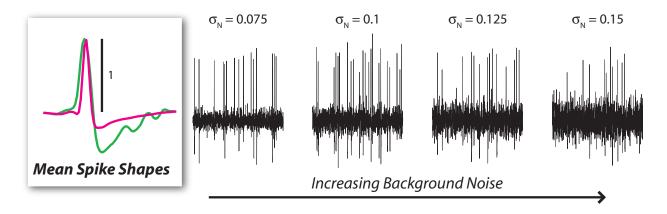

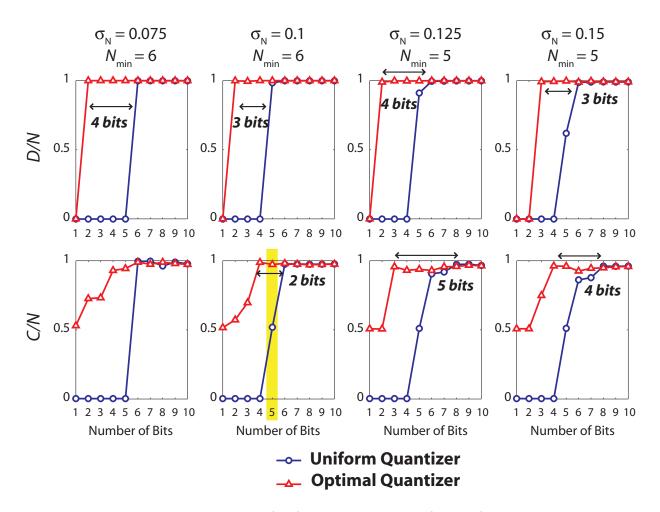

| 5.5  | Example of a synthetic dataset composed of spikes from two neurons                                                             | 89  |

| 5.6  | Comparison of detection and classification results when a uniform vs. an                                                       |     |

|      | optimal quantizer is used                                                                                                      | 91  |

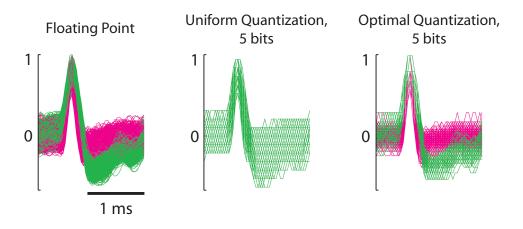

| 5.7  | Example of the benefits to clustering of using an optimal quantizer                                                            | 92  |

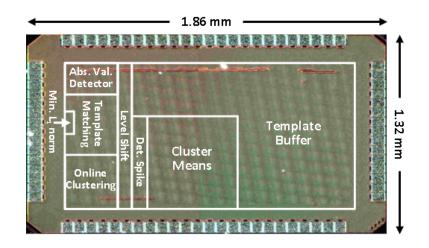

| 6.1  | Micrograph of spike-sorting chip                                                                                               | 95  |

| 6.2  | Sample of spike-sorting chip output                                                                                            | 96  |

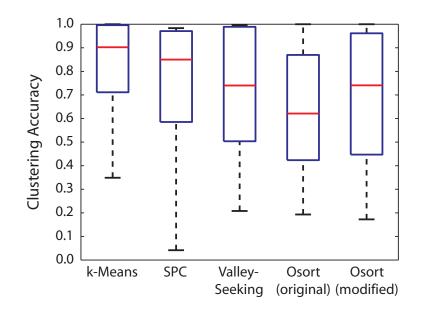

| 6.3  | Box plots showing accuracy for each clustering algorithm tested                                                                | 98  |

| 6.4  | Sample output from one of the channels processing human neural data                                                            | 100 |

| 6.5  | Die photo the 16-channel Osort chip                                                                                            | 101 |

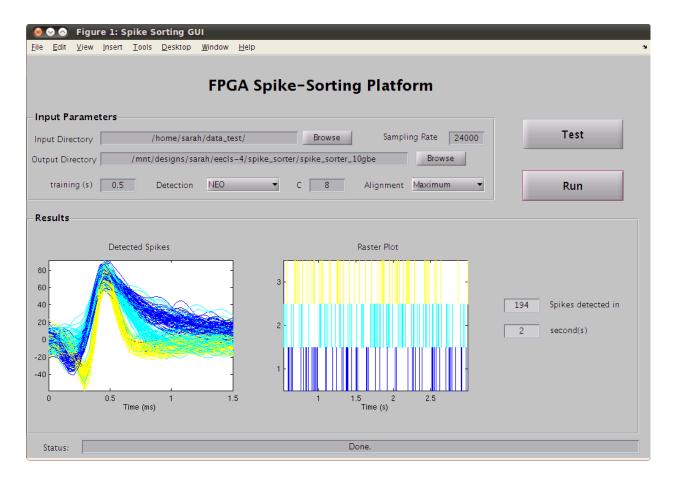

| 7.1  | Spike Sorter GUI                                                                                                               | 108 |

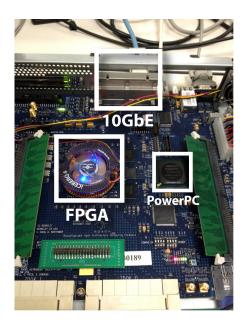

| 7.2  | Photograph of the ROACH FPGA processing board                                                                                  | 109 |

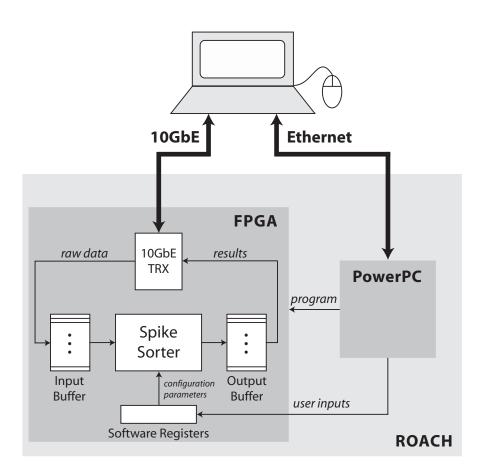

| 7.3  | Data-streaming interface                                                                                                       | 112 |

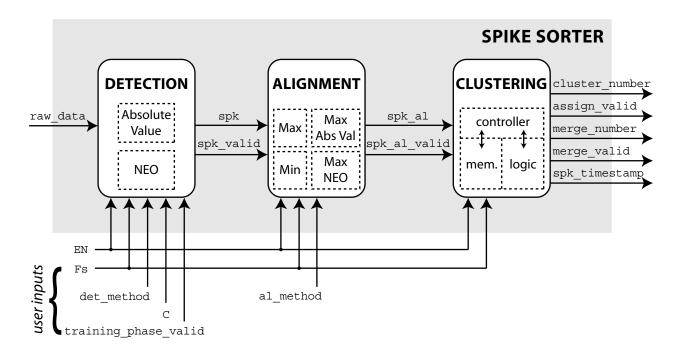

| 7.4  | Block diagram of the processing elements on the FPGA                                                                           | 113 |

| 7.5  | Implementation of a variable-length delay used in spike buffering for arbitrary                                                |     |

|      | sampling rates                                                                                                                 | 115 |

| 7.6  | State diagram of Osort                                                                                                         | 117 |

| 7.7 | Speed improvements of this hardware tool over the equivalent software running |     |

|-----|-------------------------------------------------------------------------------|-----|

|     | on three different computers with different processing powers                 | 119 |

| 7.8 | Breakdown of how various system components contribute to the total time to    |     |

|     | process one packet.                                                           | 120 |

## LIST OF TABLES

| 2.1 | Summary of Clustering Algorithm Characteristics   | 35  |

|-----|---------------------------------------------------|-----|

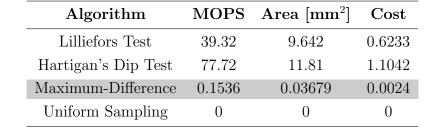

| 3.1 | Complexity of Spike-Detection Algorithms          | 58  |

| 3.2 | Complexity of Feature-Extraction Algorithms       | 60  |

| 3.3 | Complexity of Dimensionality-Reduction Algorithms | 63  |

| 3.4 | Overall System Complexity                         | 64  |

| 6.1 | Spike-Sorting Chip Summary                        | 95  |

| 6.2 | Comparison with Prior Work                        | 96  |

| 6.3 | Osort Chip Summary                                | 99  |

| 6.4 | Comparison with Prior Work                        | 100 |

| 7.1 | Latency of Clustering Operations                  | 116 |

| 7.2 | Computer Specifications                           | 119 |

#### ACKNOWLEDGMENTS

Portions of Chapters 1–2 have been reprinted, with permission, from: S. Gibson, J. W. Judy, and D. Marković, "Spike Sorting: The First Step in Decoding the Brain," *IEEE Signal Process. Mag.*, vol. 29, no. 1, pp. 124–143, Jan. 2012. Copyright © 2012, IEEE. J. W. Judy and D. Marković were the PIs.

Portions of Chapter 3 have been reprinted, with permission, from: S. Gibson, J. W. Judy, and D. Marković, "Technology-Aware Algorithm Design for Neural Spike Detection, Feature Extraction, and Dimensionality Reduction," *IEEE Trans. Neural Syst. Rehabil. Eng.*, vol. 18, no. 4, pp. 469–478, Oct. 2010. Copyright © 2010, IEEE. J. W. Judy and D. Marković were the PIs.

Portions of Chapter 4 have been reprinted, with permission, from: S. Gibson, R. Chandler, V. Karkare, D. Marković, and J. W. Judy, "An Efficiency Comparison of Analog and Digital Spike Detection," in *Proc. 4th Int. IEEE EMBS Conf. Neural Eng.*, Antalya, Turkey, 2009, pp. 423–428. Copyright © 2009, IEEE. R. Chandler provided the analog circuit analysis, and V. Karkare provided the digital circuit analysis. D. Marković and J. W. Judy were the PIs.

Portions of Chapter 5 have been reprinted, with permission, from: S. Gibson, V. Wang, and D. Marković, "Effects of Quantization on Neural Spike Sorting," in *Proc. 2011 IEEE Int. Symp. Circuits Syst.*, Rio de Janeiro, Brazil, 2011, pp. 2099–2102. Copyright © 2011, IEEE. V. Wang proposed the idea of using nonlinear quantization for spike sorting and provided the code for the quantizers. D. Marković was the PI.

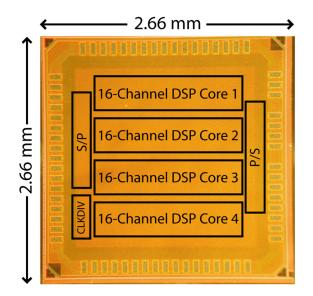

Portions of Chapter 6 have been reprinted, with permission, from: V. Karkare, S. Gibson, and D. Marković, "A 130- $\mu$ W, 64-Channel Neural Spike-Sorting DSP Chip," *IEEE J. Solid-State Circuits*, vol. 46, no. 5, pp. 1214–1222, May 2011. Copyright © 2011, IEEE. V. Karkare performed all chip design. D. Marković was the PI.

Other portions of Chapter 6 have been reprinted, with permission, from: V. Karkare, S. Gibson, C.-H. Yang, H. Chen, D. Markovic, "A 75µW, 16-Channel Neural Spike-Sorting Processor with Unsupervised Clustering," in *Proc. Int. Symp. on VLSI Circuits*, Kyoto, Japan, 2011, pp. 252–253. Copyright © 2011, IEEE. V. Karkare performed all chip design.

C.-H. Yang contributed to the memory-bank design. H. Chen helped with chip testing.

D. Marković was the PI.

# VITA

| 1982        | Born, Houston, TX.                                                                                                          |

|-------------|-----------------------------------------------------------------------------------------------------------------------------|

| 1997 - 2001 | Alief Hastings High School, Houston, TX.                                                                                    |

| 2005        | B.S., Electrical and Computer Engineering,<br>Baylor University, Waco, TX.                                                  |

| 2006        | Mars Flight Project Intern, Jet Propulsion Laboratory, Pasadena, CA.<br>HiRISE instrument team, Mars Reconnaisance Orbiter. |

| 2006 - 2007 | Graduate Fellowship, Department of Electrical Engineering,<br>University of California, Los Angeles.                        |

| 2007        | Intern, Northrop Grumman Space Technology, Redondo Beach, CA. Systems Engineering, James Webb Space Telescope.              |

| 2007 - 2012 | Graduate Student Researcher, Department of Electrical Engineering,<br>University of California, Los Angeles.                |

| 2008        | Teaching Assistant, Signals and Systems,<br>University of California, Los Angeles.                                          |

| 2008        | M.S., Electrical Engineering,<br>University of California, Los Angeles.                                                     |

| 2009        | Intern, Sigenics Inc., Sierra Madre, CA.<br>Systems Engineering, wireless telemetry for neural recording devices.           |

| 2010 - 2012 | Writing Consultant, Graduate Writing Center,<br>University of California, Los Angeles.                                      |

### PUBLICATIONS

- S. Gibson, J. W. Judy, and D. Markovic, "Spike Sorting: The First Step in Decoding the Brain," *IEEE Signal Process. Mag.*, vol. 29, no. 1, pp. 124–143, Jan. 2012.

- V. Karkare, S. Gibson, C.-H. Yang, H. Chen, D. Markovic, "A 75µW, 16-Channel Neural Spike-Sorting Processor with Unsupervised Clustering," in *Proc. Int. Symp. on VLSI Circuits* (VLSI'11), Kyoto, Japan, 2011, pp. 252–253.

- Z. Charbiwala, V. Karkare, S. Gibson, D. Markovic, and M. Srivastava, "Compressive Sensing of Neural Action Potentials Using a Learned Union of Supports," in *Proc. Int. Conf.* on Body Sensors Networks (BSN'11), Dallas, Texas, 2011, pp. 53–58.

- S. Gibson, V. Wang, and D. Markovic, "Effects of Quantization on Neural Spike Sorting," in *Proc. 2011 IEEE Int. Symp. Circuits Syst.* (ISCAS'11), Rio de Janeiro, Brazil, 2011, pp. 2099–2102.

- V. Karkare, S. Gibson, and D. Markovic, "A 130-µW, 64-Channel Neural Spike-Sorting DSP Chip," *IEEE J. Solid-State Circuits*, vol. 46, no. 5, pp. 1214–1222, May 2011.

- S. Gibson, J. W. Judy, and D. Markovic, "Technology-Aware Algorithm Design for Neural Spike Detection, Feature Extraction, and Dimensionality Reduction," *IEEE Trans. Neural Syst. Rehabil. Eng.*, vol. 18, no. 4, pp. 469–478, Oct. 2010.

- V. Karkare, S. Gibson, and D. Markovic, "A 130-µW, 64-Channel Spike-Sorting DSP Chip," in *IEEE Asian Solid-State Circuits Conf.* (ASSCC'09), Taipei, Taiwan, 2009, pp. 289–292.

- R. Chandler, S. Gibson, V. Karkare, S. Farshchi, D. Markovic, and J. W. Judy, "A System-Level View of Optimizing High-Channel-Count Wireless Biosignal Telemetry," in *Proc. Int. IEEE Engineering in Medicine and Biology Conf.* (EMBC'09), Minneapolis, Minnesota, 2009, pp. 5525–2230.

- S. Gibson, R. Chandler, V. Karkare, D. Markovic, and J. W. Judy, "An Efficiency Comparison of Analog and Digital Spike Detection," in *Proc. 4th Int. IEEE EMBS Conf. Neural Eng.* (NER'09), Antalya, Turkey, 2009, pp. 423–428.

- S. Gibson, J. W. Judy, and D. Markovic, "Comparison of Spike-Sorting Algorithms for Future Hardware Implementation," in *Proc. Int. IEEE Engineering in Medicine and Biology Conf.* (EMBC'08), Vancouver, Canada, 2008, pp. 5015–5020.

# CHAPTER 1

## Introduction

### 1.1 Electrophysiology and Extracellular Recording

For centuries, scientists have been using electrophysiology to study the electrical properties of biological cells and tissues. In 1791 Luigi Galvani discovered that he could induce contraction in a frog leg muscle by applying an electric current [1]. In 1952 Hodgkin and Huxley, using an experimental technique they developed called the "voltage clamp," made a number of groundbreaking discoveries on the movement of ions across the membranes of nerve cells during action potential generation for which they eventually received a Nobel Prize [2–5]. In 1977 Hubel and Wiesel (also Nobel Prize recipients) used electrophysiological recordings to provide the first information about how the activity of individual neurons contributes to higher visual processing [6].

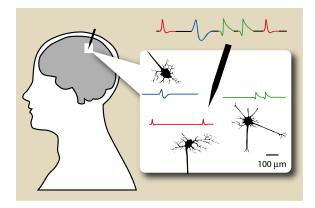

Electrophysiological recordings can be made from within cells (*intracellular*) or from outside cells (*extracellular*). In studies of the central nervous system, small-diameter electrodes can be positioned in the extracellular space to record electrical signals from surrounding neurons (Fig. 1.1). These electrodes are able to detect action potentials from individual neurons. The ability of extracellular recording to provide researchers with neuron-level activity combined with its relatively low level of difficulty to perform (as compared to intracellular recording, for example) has led extracellular recording to become one of the dominant experimental techniques in neuroscience research. For example, there has been a movement towards studying not only individual neurons but networks of neurons in order to understand how the activity of interconnected neurons results in higher-order functions such as perception, understanding, movement, and memory. Such studies require extracellular recording from ensembles of neurons using multichannel electrode arrays. In *Methods for Neural En*semble Recordings, contributing authors Sameshima and Baccalá go so far as to claim that "extracellular recordings are the only practical choice in experiments that intend to establish correlations between neural ensemble responses and behaviors involving awake animals" [7].

Electrophysiology is also used in clinical settings. For example, in presurgical patients with severe medically intractable epilepsy, electrophysiological recordings from depth electrodes placed inside the brain are used to localize brain areas where seizures begin. These larger electrodes mainly record electroencephalogram (EEG) signals, but often microelectrodes are implanted as well for use in research (e.g., [8–10]), since single-unit activity provides greater detail on changes in signal transmission that could distinguish normal from abnormal activity. And over the past decade, the technique of extracellular recording has received additional attention as researchers have begun to tap into its potential use in medical technologies for the treatment of disorders such as paralysis [11, 12], epilepsy [11], and even cognitive and memory loss [13]. Many of these technologies are based upon the idea of brain–machine interfaces (BMIs), in which implanted electronics record and decode brain signals that can be used to control "machines" such as computers or prosthetic limbs.

Whether the application is basic science research, clinical diagnostics, or medical technology, the signals from individual neurons ("single-unit activity") are often of particular interest. In basic science, for example, the researcher may require knowledge of single-unit activity in order to study how a type of neuron responds to a specific stimulus or how the activities of different neurons are correlated. Similarly, most neural prosthetic technologies employ some sort of "decoding" algorithm—which may decode movement [11, 12, 14], intentions [15], or memories [13]—that typically operates on signals from individual neurons. But because of the relatively large sizes of recording electrodes<sup>1</sup>, the recorded signal is the sum of the signals from several (usually 2–10) neurons surrounding the electrode ("multiunit activity," illustrated in Fig. 1.1). In such cases, *spike sorting*, the process of separating multiunit activity into groups of single-unit activity, is necessary.

<sup>&</sup>lt;sup>1</sup>Microwire electrode tips used in extracellular recording typically have diameters of 13 to 80  $\mu$ m [16]. The Cyberkinetics implementation of the popular Utah silicon microelectrode array has conical electrode tips with lengths of about 40  $\mu$ m and surface areas of about 1600  $\mu$ m<sup>2</sup>[17].

Figure 1.1: The electrical signal recorded from a microelectrode is the sum of the postsynaptic and action-potential activity of many neurons in the surrounding area.

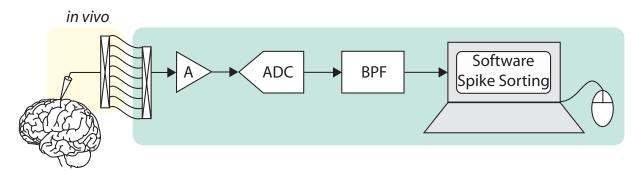

Figure 1.2: Block diagram of the conventional neural recording system.

### **1.2** Current State of the Art

In a traditional neural recording system, shown in Fig. 1.2, electrodes provide the direct interface to the brain, and the unamplified raw data is sent outside the body through wires to the rest of the data-acquisition hardware. The raw data is recorded onto computer hard disks. All data processing, including spike sorting, is performed offline, in software.

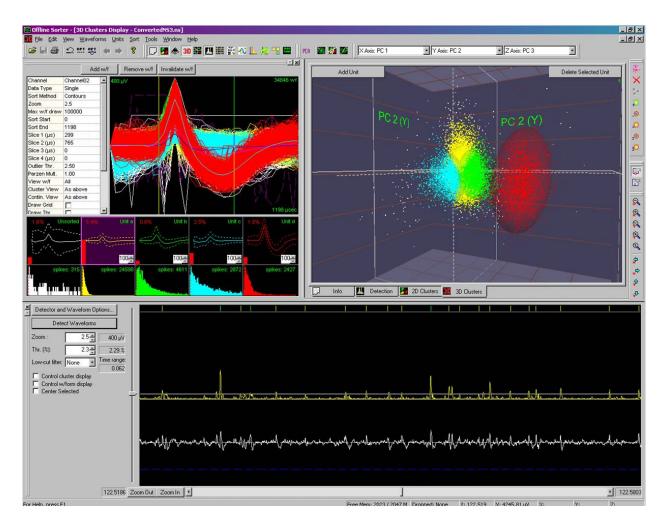

An example of a commercial spike-sorting software package is shown in Fig. 1.3. The yellow waveform in the bottom plot shows the energy of the recorded signal. The user must set a detection threshold by manually adjusting the position of the white horizontal line. Once spikes are detected, the user can choose to plot certain features, such as the spike heights and widths or principal components (shown in the upper right plot), in two or three dimensions. The operator can then use built-in automatic or semi-automatic clustering routines. The results of clustering are then displayed on the left-most plots. Statistics about

Figure 1.3: Screenshot of Offline Sorter, a commercial spike-sorting program by Plexon [18].

each cluster, such as the mean waveform, variance, and interspike interval (ISI) histograms, are given so that the operator can evaluate the clustering results and make manual changes, such as combining two clusters into one, if needed.

### 1.3 Objectives

There are several problems with the state of the art in neural recording, which led to the two main objectives of this thesis:

#### 1.3.1 Need for Wireless Recording Systems

In the current setup, data is transferred from the subject to a computer via thick cables. In the research setting, cables restrict the physical movement of subjects (Fig. 1.4), thereby limiting the quality and diversity of experiments that can be performed. Furthermore, these cables can increase the severity of noise and motion artifacts seen in the recording. Cables are obviously unwanted in BMI applications as well, where the goal is for patients to be able to lead normal lives—meaning they cannot be tethered to electronic equipment. Thus, there is a clear need for wireless recording systems.

Such a wireless recording system would presumably include an on-site radio to wirelessly transmit data off-site. However, the high-channel-count systems of today incur high data rates. Consider the example of a 100-channel system using a sampling rate of 30 kSa/s and a resolution of 10 bits, which would produce data at 30 Mbps [19]. Wireless transmission at this data rate would require about 600 mW of power<sup>2</sup>. This is problematic for two reasons. First, such high power consumption would result in a battery life of only about 40 minutes<sup>3</sup>, which is acceptable neither for experiments that require days of continuous recordings nor for BMIs, which cannot afford such frequent battery changes. Second, such high power dissipation could be dangerous for the surrounding tissue [21].

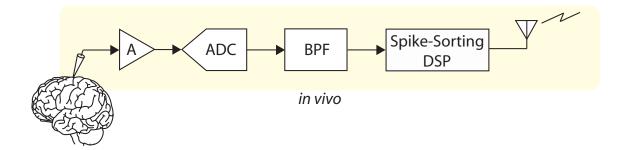

The alternative recording setup shown in Fig. 1.5 would solve this problem: a digital signal processor (DSP) would perform on-site, real-time spike sorting and only the sorting results would be transmitted, thereby achieving enough data reduction to enable the wireless transmission of data. To continue the above example, assume that this new system transmits only 11 bits per spike (4 bits for the cluster ID and 7 bits for the channel number). A spike rate of 100 spikes/s would result in an output data rate of 110 kbps, a transmitter power of 2.25 mW, and a battery life of over 7 days (a 272x improvement). The first objective of this thesis was, therefore, to design the DSP for this wireless recording system.

Towards this objective, we first surveyed the spike-sorting algorithms already published

<sup>&</sup>lt;sup>2</sup>assuming the transmitter in [20], which was designed for a 100-channel wireless neural recording system;  $20.45 \text{ nJ/b} \cdot 30 \text{Mb/s} = 613.5 \text{ mW}$  at 13 cm.

<sup>&</sup>lt;sup>3</sup>assuming an Energizer CR1632, with a capacity of 130 mAh at 3 V = 390 mWh; battery life is 390 mWh  $\div$  613.5 mW = 38 min.

Figure 1.4: Example of an experimental setup for neural recordings from rat. The rat has been implanted with electrodes, and a thick bundle of wires delivers the recorded signals to the data-acquisition equipment. A commutator (seen above the cage) must be used to prevent the rat's movement from applying a torque to the headstage, which could break the delicate wires.

Figure 1.5: Block diagram of the proposed wireless neural recording system.

in the field (Chapter 2) and performed an extensive, unbiased algorithm comparison to determine which are most appropriate for hardware implementation (Chapter 3). We then considered various implementation issues, such as whether analog or digital spike detection is more efficient (Chapter 4) and what the best method is for quantizating neural signals (Chapter 5). Examples of digital chips that have been designed based on this work will be presented in Chapter 6.

#### 1.3.2 Need for Hardware-Accelerated Data Processing

For the time being, many researchers are still working with wired systems and the data that has already been recorded using such systems. This data is usually acquired with sampling rates of 20–30 kHz and resolutions of 12–24 bits per sample [22–27] for 64–128 channels simultaneously. Consider a human epilepsy study in which 64 channels of data are sampled at 27.777 kHz and quantized to 16 bits. An 8-hour experiment would accumulate about 100 GB of data, which would require about 30 hours to sort using conventional software tools<sup>4</sup> (processing rate of 0.94 MBps). Now consider dedicated hardware running at 100 MHz (200 MBps); the processing time would be reduced from 30 hours to 8.5 minutes (212x).

Thus, the second objective of this thesis was to develop a hardware spikesorting tool for accelerating the offline processing of existing neural data. In order to provide a good compromise between speed and flexibility, we proposed an FPGAbased spike-sorting platform. A library of algorithms was developed for each step in the spike-sorting process. That way, rather than being tied down to one particular spike-sorting algorithm, users are able to customize data processing to fit their needs. This library may also be used to generate RTL for future ASIC implementations. This work will be described in Chapter 7.

<sup>&</sup>lt;sup>4</sup>Osort software package [28] running in Windows on an Intel Core2 Duo Processor.

# CHAPTER 2

# Spike Sorting

#### 2.1 Signal Composition

Let us begin by looking at the composition of the signals that are recorded by extracellular electrodes. These signals are usually pre-lowpass-filtered in the analog domain and then sampled at a rate of 20–30 kHz. Different cellular mechanisms are responsible for different frequency components of the recorded signals. The high-frequency content (about 300 to 6000 Hz) is referred to as *unit activity*, while the low-frequency signal content (below about 600 Hz) is referred to as *local field potential*.

#### 2.1.1 Unit Activity

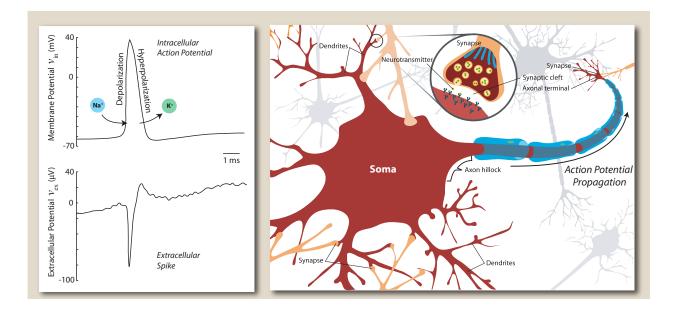

If unit activity is the signal of interest, as it is in this thesis, then the sampled signal is bandpass-filtered with a low cutoff frequency of 100 to 300 Hz and a high cutoff frequency of 3000 to 10000 Hz. As indicated by its name, the source of this "unit activity" is action potentials from individual neurons.

On some level, the action potential can be thought of as the discrete, binary event by which neurons communicate. Much of what we know about the mechanism was discovered in the seminal works of Hodgkin and Huxley [2–5]. Neuronal membranes are impermeable to charged ions except at sites of ligand- and voltage-gated channels, which allow the passage of charged ions between the intra- and extra-cellular space. When the ion channels are closed or inactive, the concentrations of potassium (K<sup>+</sup>) and chloride (Cl<sup>-</sup>) ions inside the cell are high relative to oustide the cell, while the concentration of sodium (Na<sup>+</sup>) ions is high outside the cell relative to inside the cell. At rest, the cell membrane potential, defined with respect to the

inside of the cell, is about -70 mV. When a cell's membrane is depolarized, for example by excitatory synaptic input, this depolarization "activates" (opens) the Na<sup>+</sup> channels, causing Na<sup>+</sup> ions to rush *into* the cell along the concentration gradient. This influx of Na<sup>+</sup> causes the membrane to become even more depolarized, consequently causing more Na<sup>+</sup> channels to become activated. Eventually the membrane potential reaches threshold, at which point external input is no longer needed to depolarize the cell, and the positive feedback caused by the Na<sup>+</sup> current continues the depolarization at an even faster rate. This sharp influx of Na<sup>+</sup> into the cell results in the rising phase of the action potential shown in Fig. 2.1 (lefttop). Once the cell reaches a peak depolarization of about 40 mV, two things happen: the Na<sup>+</sup> channels become "inactivated" such that no more Na<sup>+</sup> ions can pass through, and the voltage-gated  $K^+$  channels open. Now,  $K^+$  ions flow *out* of the cell along the concentration gradient, and the cell membrane begins to "hyperpolarize"; this efflux of  $K^+$  results in the falling phase of the action potential (Fig. 2.1, left-top). This hyperpolarization continues until the cell has returned to its resting potential. In some cases, the hyperpolarization is followed by a slow after-hyperpolarization, where the resting potential is overshot, before the membrane potential returns to rest. The action potential usually begins at the axon hillock, near the cell body (soma), and propagates down the axon (Fig. 2.1, right). Depolarization of the axon terminal then triggers the release of neurotransmitters into the synaptic cleft (the gap between the pre-synaptic cell's axon terminal and the post-synaptic cell's dendrite), in turn depolarizing the post-synaptic cell. It is in this way that neurons communicate with each other.

Extracellularly recorded action potentials are called *spikes*. (The terms "action potential" and "spike" are sometimes used interchangeably; to be precise, however, we will use "action potential" to refer to the intracellular event and "spike" to refer to the captured extracellular waveform.) As shown in Fig. 2.1 (left-bottom), a spike looks slightly different from an intracellular action potential. First, because the recording electrode is placed outside of the cell rather than inside the cell, the polarity is reversed. Second, the filtering properties of the extracellular medium result in an extracellular signal that is about two to three orders of magnitude smaller than the corresponding intracellular signal (~10 to 100  $\mu$ V compared

Figure 2.1: Left: Adapted from [29]. Left, Top: Illustration of the change in membrane potential during a typical action potential. Left, Bottom: Illustration of the corresponding change in potential as seen by an extracellular electrode. Note the difference in vertical-axis scales. Right: Diagram of a neuron. Action potentials begin at the axon hillock and propagate down the axon. Depolarization of the axon terminal then triggers the release of neurotransmitters into the synaptic cleft, in turn depolarizing the post-synaptic cell.

to  $\sim 10 \text{ mV}$ ). Third, because the membrane acts like a resistor and capacitor in parallel, that is, a highpass filter (Fig. 2.2a), the recorded extracellular potential is approximately equal to the derivative of the intracellular potential [30].

The shape of the intracellular action potential depends on a number of cell properties, including the cell type, the cell geometry, and the ion-channel distribution. This shape is generally considered to be constant for a given neuron, except in special cases such as "burst" (high-frequency) firing. Since the extracellular waveform is directly related to the intracellular waveform, the extracellular spike shape also depends on these properties, as well as on the position of the recording electrode relative to the cell, on the distance of the electrode from the cell, and on interference from other nearby neurons ("background noise"). This "biological noise" is the largest source of noise in a neural recording, having amplitudes approaching that of the unit activity. But the recording hardware itself, including the electrode, the amplifier, and the ADC, also adds a significant amount of noise, the scale of which is largely dependent on the given circuit implementation. It is usually assumed that

Figure 2.2: (a): A simple electrical-circuit model of extracellular recording [31]. Assume that an intracellular electrode is placed inside the cell, an extracellular electrode is placed outside but near the cell, and the reference electrode is placed very far away from the cell. The extracellular material can be modeled as pure resistance, while the cell membrane can be modeled as a resistor and a capacitor in parallel. The cell membrane highpass-filters the action potential signal, such that the extracellulary recorded signal  $(v_{\rm ex})$  is approximately equal to the derivative of the intracellularly recorded signal  $(v_{\rm in})$  [30]. (b): As the broadband signal passes through the extracellular medium, the capacitive membranes of nearby cells attenuate its high-frequency components.

the signal and the noise are statistically independent and that they sum linearly. Thus, in a given recording session where the electrode placement is assumed to be constant relative to the tissue, we assume that the extracellular spike shape for each neuron can be modeled as a deterministic waveform plus random noise. Note that while the recording noise usually is Gaussian, the background noise typically is not [32].

Spike trains can be treated as point processes with arrival times following a Poisson distribution. A neuron's *firing rate*, the frequency at which it generates action potentials, depends on the cell type and brain area. Neurons in the visual cortex, for example, which are either silent or firing at a base frequency of around 5 spikes per second (or simply Hz), respond to their preferred stimulus with firing rates of about 15–75 Hz [33]. A bursting neuron, on the other hand, can fire as many as 300 to 800 spikes per second [34].

There is disagreement within the neuroscience community as to exactly how information is encoded in the brain. The dominant theory contends that information is encoded by the *frequency* of action potentials ("rate coding") [35, 36]. Alternative theories propose that information is contained in the absolute *timing* of action potentials ("temporal coding") [36,37] or in the *phase* of action potentials relative to specific oscillations ("phase coding") [38,39]. No matter which of these theories is true, it is clear that the action potential is the main player in encoding, and that precise timing of action potentials must be obtained in order to "decode" neural activity.

#### 2.1.2 Local Field Potential (LFP)

While LFPs are not the focus of this thesis, a brief discussion of their properties is warranted here. We will also refer to these signals again later when we discuss alternative methods of decoding neural signals for BMIs.

A comprehensive description of the physiological basis for LFP was provided by Buzsáki and Traub in [40]. To summarize, LFPs come from several sources, the most significant of which is synaptic activity. Because the capacitive lipid membranes of cells in the brain act as a lowpass filter, the high-frequency components of neuronal signals are greatly attenuated as they travel through the extracellular medium; equivalently, slow signals are able to propagate much farther than are high-frequency signals (Fig. 2.2b). As a result, the low-frequency component of the signal recorded at any given point within the brain is a linear sum of the activity from large populations of cells. Thus, LFP can be interpreted as an indication of the "cooperative actions" of neurons.

Note that this signal is referred to as "LFP" when recorded by a microelectrode inserted into the brain (hence the "local" in LFP) but as "EEG" if recorded using scalp electrodes and as "electrocorticography (ECoG)" if recorded using epidural or subdural grid electrodes. Some scientists favor using ECoG and EEG because these methods are less invasive and easier to perform. However, because LFPs must propagate through a capacitive medium on their way to these recording sites, EEG and ECoG are actually "spatially smoothed" versions of the LFP. As such, EEG and ECoG contain very little information about the activity of the neurons that actually generate the signals. Furthermore, scalp and dural grid electrodes are only sensitive to signals originating in the superficial layers of the cortex; contributions to the signal from neurons in deeper layers of the cortex and from subcortical areas are virtually negligible. Thus, extracellular recording, which provides the experimenter with LFP measurements as well as unit activity, is the experimental technique most capable of providing information about the cooperative actions of neurons at high temporal and spatial resolutions.

### 2.2 The Spike-Sorting Process

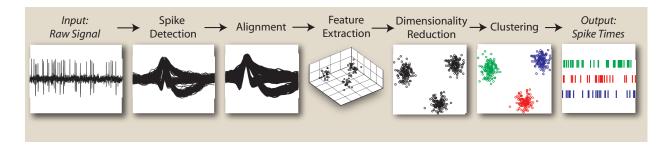

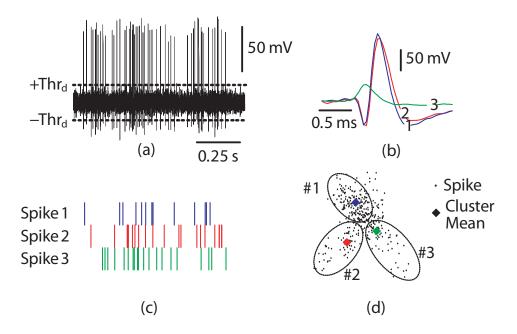

In order to obtain (multi)unit activity, the extracellular data is first bandpass-filtered to remove the LFP and high-frequency noise (as described in Section 2.1.1). To then obtain single-unit activity, we must perform spike sorting by sending this "raw" data through the signal-processing chain shown in Fig. 2.3. The first steps are *spike detection*, the process of separating spikes from background noise, and *alignment*, the process of aligning all detected spikes to a common temporal point relative to the spike waveform. Once the spikes have been identified, spike sorting can take place.

Most spike sorting methods—relying heavily on the previously mentioned assumption that each neuron produces a different, distinct shape (as seen by the electrode) that remains constant throughout a recording session—are based on spike waveform information. Thus, the first step in such methods is *feature extraction*, in which spikes are transformed into a certain set of features, such as principal components, that emphasizes the differences between spikes from different neurons as well as the differences between spikes and noise. After feature extraction, some form of *dimensionality reduction* typically takes place, in which feature coefficients that best separate spikes are identified and stored for subsequent processing while the rest are discarded. Finally, spikes are classified into different groups, corresponding to different neurons, based on the extracted feature coefficients; this process is referred to as *clustering*. The result, the signal of interest to the experimenter and to BMIs, is the train of spike times for each neuron. This information can be represented graphically by a raster plot, where ticks are drawn to indicate spike occurrences versus time, as shown in the right-most plot of Fig. 2.3 for three neurons.

Figure 2.3: The signal-processing chain used to obtain single-unit activity.

### 2.3 Classifying Spike-Sorting Algorithms

Spike-sorting methods can be categorized according to a number of different characteristics. The first is the level of *autonomy*: methods can be "automatic/unsupervised" (fully autonomous) or "manual" (not at all autonomous). Automatic or unsupervised methods require no user input, while manual methods require constant supervision by an operator. Methods can also fall anywhere between these two extremes; a "semi-automatic" method is a method with both a manual stage and an automatic stage. Examples of semiautomatic methods include detection methods that require the manual setting of a threshold, or window-discriminator methods that require the manual definition of windows, but that then work automatically [41], as well as classification methods that require the user to manually re-assign clusters after automatic cluster determination [42]. For neural prosthetic applications, spikes must be sorted in real time, thus precluding manual spike sorting. And because of the growing amount of data resulting from an increase in the number of simultaneously recorded channels, manual spike sorting is no longer a viable option in research settings either. Therefore, automatic methods are now usually required.

A second way to classify spike-sorting algorithms is by whether or not they are *real-time* (also called *online*). The standard practice for many years has been to first record and store all the data and then to perform spike sorting offline after the experiment. As a result, many of the spike-sorting methods that have been developed are noncausal, in that they rely on access to all of the data at once. When using principal component analysis, for example, the principal components are often calculated using all of the detected spikes, and then each spike is projected onto these basis vectors before the actual classification takes place. It is

increasingly common, however, for applications that require spike sorting to require that the spike sorting occur in real time. This requirement renders a number of hitherto commonly used methods inadequate. A compromise would be to modify offline algorithms to include an offline training period followed by a real-time classification period.

The third attribute by which spike-sorting methods can be categorized is *adaptivity*. As we will describe later, extracellular signals are not always stationary. In such cases it would be beneficial to use an algorithm that can adapt to a changing environment, as opposed to a static algorithm. There can be intermediate cases on this scale as well. For example, a static algorithm that requires a training period can be made adaptive by retraining it periodically.

Clustering algorithms can be further classified as either *parametric* or *nonparametric*. Koontz et al. define a nonparametric clustering algorithm as "an algorithm for clustering multivariate data which is not based on a parametric model of an underlying probability density function. In particular, a nonparametric algorithm should identify clusters of arbitrary shape and size" [43]. In other words, any algorithm that assumes a certain structure to the data or that is biased towards a particular cluster shape, such as spherical or ellipsoidal, will be considered parametric. The underlying probability density function for neural data is not known a priori (see Section 2.5.2), so nonparametric clustering algorithms are highly desirable.

Early spike-sorting algorithms were very simple, but not very accurate. In general, the more complex the method, the better the performance. This inherent tradeoff between algorithm accuracy and complexity leads to another characteristic by which to classify algorithms: the *accuracy–complexity* measure. As we described in the introduction, many applications require spike sorting in implantable hardware. Any implantable hardware is subject both to strict power-density constraints and to high reliability requirements. Thus, it is crucial to choose the spike-sorting methods with the optimal balance between accuracy and complexity to implement in hardware.

In the next section, we will give some examples of algorithms that have been used for each step of spike sorting. We will also mention some alternative methods, mostly statistical/probabalistic in nature, that do not conform to the block diagram shown in Fig. 2.3.

### 2.4 Overview of Spike-Sorting Algorithms

Note that Lewicki provided a nice review of spike-sorting methods in 1998 [44]. Here, we provide a relatively high-level description of the evolution of spike-sorting techniques as well as an update of more recent algorithms, and present them in the context of hardware spike sorting.

#### 2.4.1 Detection

Nearly all detection methods involve two main steps: the pre-emphasis of the signal and the application of a threshold. Spike-detection methods vary in how the signal is pre-emphasized and in how the threshold is determined. All of these methods run automatically given the detection threshold, so whether or not the algorithm is fully automatic depends on whether or not the threshold can be determined automatically. All of these methods are also real-time (save a small latency for buffering spikes) given the detection threshold, but automatic calculation of the threshold usually involves a training period.

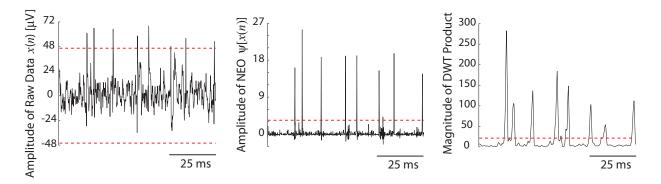

The early days of spike sorting came in a time before personal computers. Processing was done purely in analog hardware. As a result, spike-sorting methods were relatively primitive. Spike detection was typically performed using a simple **voltage trigger** or **Schmitt trigger**, where the voltage threshold was set manually by the user. Any time the voltage signal crossed that threshold, a pulse would be generated to indicate the presence of a spike [44]. Or, if the user needed the spike waveforms for subsequent spike sorting, a threshold crossing would trigger the capture of the spike waveform. This method is appealing because of its simplicity, and, as a result, is still used today by many experimenters. Some researchers have modified this method to include an **absolute-value** operation before the compare (or, equivalently, a compare to  $\pm$  threshold, as shown in Fig. 2.4); the absolute-value threshold was confirmed to be better than a simple threshold in [45].

Figure 2.4: Examples of pre-emphasized signals and threshold values (dashed red lines) for three different detection methods. *Left*: Absolute-Value, *Middle*: NEO, *Right*: DWT Product [48].

For an autonomous spike-sorting system, the threshold must be calculated automatically. An intuitive value for this threshold would be a multiple of the standard deviation of the noise. This would minimize the probability of noise exceeding the threshold. One method for estimating the noise standard deviation would be to calculate the standard deviation of the entire signal (including spikes), under the assumption that spikes are sparse. However, [46] showed that as the firing rate of the data increases, this estimate becomes too high. So they suggested the following estimator:

$$\hat{\sigma}_{\rm N} = \text{median}\left(\frac{|x(n)|}{0.6745}\right),\tag{2.1}$$

where  $\hat{\sigma}_{N}$  is the estimate of the noise SD and x(n) is a sample of the original signal x at time  $n^{1}$ , and proposed the following detection threshold Thr:

$$Thr = 4\hat{\sigma}_{\rm N}.\tag{2.2}$$

Another class of spike-detection algorithms are based on detecting changes in the energy of the signal. One such algorithm is called the **nonlinear energy operator (NEO)** or the Teager energy operator (TEO). Originally described in [49], the NEO has been proposed for

<sup>&</sup>lt;sup>1</sup>This formula may come from the fact that the median absolute deviation (MAD) of a standard normal distribution is 0.6745 [47]. It follows that for a zero-mean normal distribution with non-unit variance,  $\sigma = \frac{\text{MAD}(x)}{0.6745}$ .

use in spike detection by [45, 50, 51]. In discrete time, the NEO  $\psi$  is defined as

$$\psi[x(n)] = x^2(n) - x(n+1) \cdot x(n-1), \qquad (2.3)$$

where x(n) is a sample of the waveform at time n. The NEO is large only when the signal is both high in power (i.e.,  $x^2(n)$  is large) and high in frequency (i.e., x(n) is large while x(n + 1) and x(n - 1) are small). Since a spike by definition is characterized by localized high frequencies and an increase in instantaneous energy [50], this method has an obvious advantage over methods that look only at an increase in signal energy or amplitude without regarding the frequency. This can be seen in Fig. 2.4, which shows that the NEO operation increases the SNR of the signal, making detection less sensitive to the detection threshold. Another advantage of this method is that it is relatively simple to implement, whether in the digital or analog domain. The threshold *Thr* for this method can be automatically set to a scaled version of the mean of the NEO:

$$Thr = C \frac{1}{N} \sum_{n=1}^{N} \psi[x(n)], \qquad (2.4)$$

where N is the number of samples in the signal [50]. The scale can be chosen initially by experiment (e.g., as described in Section 3.3.2) and then used as a constant.

Other spike-detection algorithms are based on **template matching**. If the spike waveforms of interest are known a priori to the user, then matched filters can be used to correlate the incoming signal with the spike templates; if the correlation crosses a certain threshold then a spike has been detected. With known cluster templates, this method can also be used for the actual spike classification. A related method is detection using the **discrete wavelet transform (DWT)**. The DWT, which is ideally suited for the detection of signals in noise (e.g., edge detection, speech detection), has recently also been applied to neural spike detection ([48, 52, 53]). This method has an intuitive appeal in that it is similar to template matching, where we correlate the signal with a known waveform, only it is scale-invariant. The DWT is also appealing because it can be implemented using a series of filter banks, keeping the complexity relatively low. An example of one possible implementation is the DWT Product [48]. First, the stationary wavelet transform (SWT) is calculated at 5 consecutive dyadic scales  $(W(2^j, n), j = 1, ..., 5)$ . Then the scale  $2^{j_{\text{max}}}$  with the largest sum of absolute values is found:

$$j_{\max} = \underset{j \in \{3,4,5\}}{\operatorname{argmax}} \left( \sum_{n=1}^{N} |W(2^{j}, n)| \right).$$

(2.5)

From here, we calculate the point-wise product P(n) (or "SWTP") between the SWT at this scale and the SWTs at the two previous scales:

$$P(n) = \prod_{j=j_{\text{max}}-2}^{j_{\text{max}}} |W(2^j, n)|.$$

(2.6)

This product is then smoothed by convolving it with a Bartlett window w(n) in order to eliminate spurious peaks, and a threshold is applied. The threshold Thr can be set automatically to a scaled version of the mean of this result:

$$Thr = C\frac{1}{N}\sum_{n=1}^{N} w(n) * P(n), \qquad (2.7)$$

where N is the number of samples in the signal and C is a constant. Once again, Fig. 2.4 shows that the pre-emphasized DWT signal has an increased SNR compared to the original signal, making detection less sensitive to the detection threshold.

#### 2.4.2 Alignment

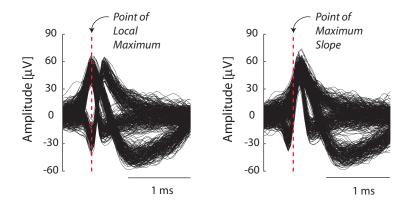

When spike detection is performed in the digital domain, whenever the voltage signal crosses a threshold, a window is applied and a spike waveform is captured. At this point, each spike is essentially aligned to the point of the threshold crossing. However, sampling jitter combined with noise effects may leave features of interest, such as maximum and minimum values, misaligned. This temporal misalignment has the effect of increasing the spread of points in feature space, making clustering more difficult. Thus, alignment should be performed prior to classification.

Figure 2.5: Examples of two different alignment methods. *Left*: alignment to maximum amplitude, *Right*: alignment to maximum slope.

The alignment process usually begins by upsampling the signal (using an interpolation method such as cubic spline) to help reduce the effects of sampling jitter. Then, the signal is aligned to some event in time. The aligned spikes may be downsampled to the original sampling rate after alignment.

The most common method of temporal alignment is to align each spike to the point of its **maximum amplitude** (Fig. 2.5) [44]. Alignment to the point of **maximum slope** (Fig. 2.5) has also been proposed [54], which is intuitive since the rising slope of the action potential has biological significance (Fig. 2.1). This method would be especially convenient if discrete derivatives (described in Sec. 2.4.3) were already being used for feature extraction. Others have proposed alignment to the maximum of an energy measure such as the **NEO** [55], which would be convenient if NEO were already being used for spike detection. Similarly, alignment to the **maximum integral** [56] would be convenient if the integral transform (described in Sec. 2.4.3) were being used for feature extraction. Indeed, it would be convenient to perform alignment with respect to any measure that is already being calculated in the sorting process.

Although the aforementioned alignment methods will usually improve classification accuracy, alignment to a metric that is derived from the whole spike rather than from a single point may be less susceptible to the effects of background noise. One example of such a metric is the spike's **center of mass** [57]. Note that all of the algorithms that have been described in this section are completely automatic and real-time.

#### 2.4.3 Feature Extraction

Feature-extraction methods were also primitive in the early days of spike sorting. Often only very simple features such as the **maximum spike amplitude**, **peak-to-peak amplitude**, and **spike width** were used [44]. This approach, although simple, is quite susceptible to noise, as well as to intrinsic variations in spike shapes.

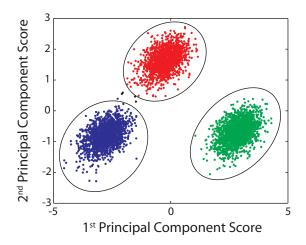

In the 1970s, as digital computers gained popularity and processing capacity, researchers began using more sophisticated algorithms for feature extraction, such as **principal component analysis (PCA)** [58]. In PCA, the orthogonal basis (i.e., the "principal components" or PCs) that captures the directions in the data with the largest variation is calculated by performing eigenvalue decomposition of the covariance matrix of the data. Each spike is then expressed as a series of PC coefficients  $c_i$ :

$$c_i = \sum_{n=1}^{N} PC_i(n) \cdot s(n),$$

(2.8)

where s is a spike, N is the number of samples in a spike/PC, and  $PC_i$  is the *i*<sup>th</sup> PC (Fig. 2.6). These coefficients are then clustered to obtain the spike classifications. This method raised the bar on the classification performance that could be achieved, especially for noisier data. An added bonus is that, because most of the variance is captured in the first few components, the dimensionality can be reduced by keeping only the first two or three PCs, thereby reducing the computation time of PC coefficient calculation and of subsequent clustering. Even today, PCA is the most trusted and most commonly used method of spike sorting. The downside to PCA is that it is not a real-time algorithm. It is usually performed offline after the acquisition of the entire dataset, but it can be modified to include a training period during which the PCs are calculated followed by a real-time PC-coefficient-calculation period. Additionally, PCA is most effective on Gaussian data, while spike data may be non-Gaussian (Section 2.5.2).

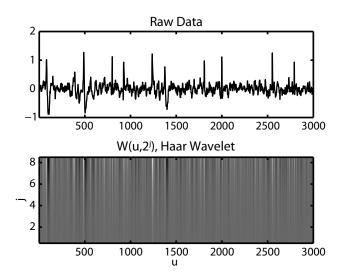

Besides for spike detection, the **DWT** has also been proposed for feature extraction by

Figure 2.6: Sample results of feature extraction using PCA. For the detected spikes (left), principal components are calculated (middle), and each spike is expressed by its first two PC coefficients (right).

[46]. The DWT is given by

$$W(u,2^{j}) = \sum_{n=-\infty}^{\infty} s(n) \cdot \frac{1}{2^{j/2}} \cdot \Psi\left(\frac{n-u}{2^{j}}\right),$$

where u is a translation parameter (analogous to time), j is an integer,  $2^{j}$  is a scale parameter (analogous to frequency), and  $\Psi$  is the wavelet function. The DWT should work well for feature extraction since it is a multi-resolution technique that provides good localization in both time and frequency. As in PCA, performing the DWT on spike waveforms results in a set of "expansion coefficients," which can then be clustered to achieve spike classification. An example showing the DWT of raw data is shown in Fig. 2.7.

Methods have also been developed with the accuracy–complexity tradeoff in mind. One such method is called **discrete derivatives (DD)** and is like a simplified version of DWT [59]. Discrete derivatives are calculated by computing the slope at each sample point, over a number of different time scales:

$$dd_{\delta}(n) = s(n) - s(n - \delta), \qquad (2.9)$$

where s is a spike and  $\delta$  is an integer related to the time scale.

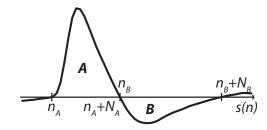

Another such method is called the **integral transform (IT)** [60], in which spikes are classified based on the areas under the positive and negative phases of the spike,  $I_A$  and  $I_B$ ,

Figure 2.7: Example showing the DWT (lower plot) of raw data (upper plot), where u is a translation parameter (analagous to time), j is an integer, and  $2^{j}$  is a scale parameter (analagous to frequency). Vertical axis of upper plot represents the signal amplitude (arbitrary units).

Figure 2.8: Illustration of feature extraction using the integral transform (IT).

respectively:

$$I_A = \frac{1}{N_A} \sum_{n=n_A}^{n_A + N_A - 1} s(n), \quad I_B = \frac{1}{N_B} \sum_{n=n_B}^{n_B + N_B - 1} s(n), \quad (2.10)$$

where s is the spike,  $n_A$  is the first sample of the positive phase,  $N_A$  is the total number of samples in the positive phase,  $n_B$  is the first sample of the negative phase, and  $N_B$  is the total number of samples in the negative phase of the spike (Fig. 2.8). Parameters  $N_A$ ,  $N_B$ ,  $n_A$ , and  $n_B$  are all determined by offline training. This method is appealing because of the simple hardware implementation presented. Since only two features are extracted from each spike ( $I_A$  and  $I_B$ ), the resulting dimensionality of this method is 2, and no dimensionality reduction is required before clustering.

### 2.4.4 Dimensionality Reduction

Dimensionality reduction is a critical step in spike sorting for a number of reasons. The most obvious reason is that it will significantly reduce the required memory and computational complexity of clustering, resulting in significant reductions in the area and power of the spike-sorting hardware. Another obvious benefit is that it reduces the output data rate of spike-sorting hardware configured to output features only. A third reason that makes dimensionality reduction critical is that it improves the accuracy of clustering. Adding dimensions in clustering improves the performance only up to a certain point, after which adding more dimensions can cause the performance of the clusterer to degrade. One reason for this may be that dimensions in which the data is not separated introduce noise or confusion into the clusterer.

The most primitive way that the dimensionality of features can be reduced is with **uni**form sampling, in which to reduce the dimensionality from N to D we simply choose Devenly spaced samples, for example, by choosing every  $N/D^{\text{th}}$  sample beginning with sample number D/2. This is essentially the same as choosing D random samples.

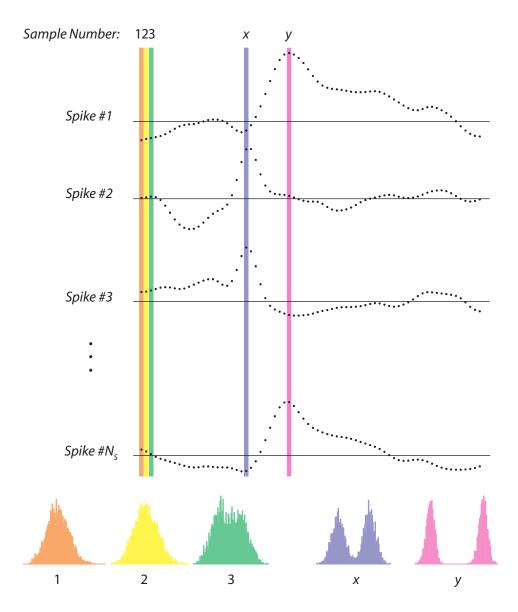

A smarter way to choose the features that can best separate clusters, as shown in Fig. 2.9, is by finding those features that have mulitmodal distributions across spikes, as multimodal distributions are an indication that more than one population (collection of spikes from the same neuron) is present in the dataset. Next, we present three dimensionality-reduction algorithms that use this approach.

The first of these algorithms is called the **Lilliefors Test** [61], a modification of the Kolmogorov-Smirnov Test. The null hypothesis is that the data under question comes from any normally distributed population (whereas the Kolmogorov-Smirnov Test tests the null hypothesis that the data comes from a standard normal distribution). The basic steps of the test are:

- 1. Calculate the population mean and population variance of the data.

- 2. Calculate the empirical distribution function (EDF) of the data.

Figure 2.9: An illustration of how feature distribution information can be used in dimensionality reduction. For visualization purposes, we use the time samples of the spikes as features. In this example, the distributions of the amplitudes for samples 1, 2, and 3 are unimodal, so they would not be good choices of features to be used in clustering. Samples x and y, on the other hand, have bimodal distributions, indicating that clustering of these features would reveal the two underlying populations within the data.

3. Test statistic: The maximum discrepancy between the EDF and the cumulative distribution function (CDF) of a normal distribution having the mean and variance calculated in 1).

The Lilliefors Test has been used by [46] for dimensionality reduction in spike sorting, where the test statistic was used to find the coefficients whose distributions differed most from the normal distribution. The assumption is that the null hypothesis will be rejected for coefficients with multimodal distributions but not for coefficients with unimodal distributions.

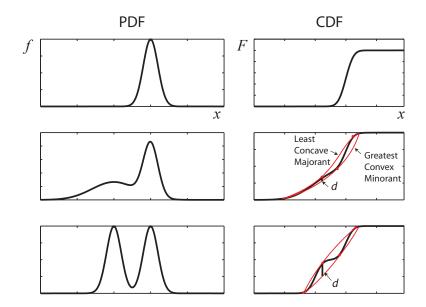

Hartigan's Dip Test [62], [63] is a statistical test that looks specifically for multimodality. The CDF of a unimodal distribution has only one mode and is convex before the mode and concave after the mode. On the other hand, CDFs of multimodal distributions have more than one mode, and therefore have regions alternating between concave and convex. The basic steps in the Dip Test (illustrated in Fig. 2.10) are:

- 1. Calculate the EDF of the data.

- 2. Calculate the greatest convex minorant (GCM) and the least concave majorant (LCM).

- 3. Test statistic: The maximum distance ("dip") between the EDF and the unimodal distribution function that minimizes the maximum difference.

The coefficients whose distributions are "more multimodal" will have larger test statistics. Thus, we choose the coefficients that have the largest test statistics for use in clustering.

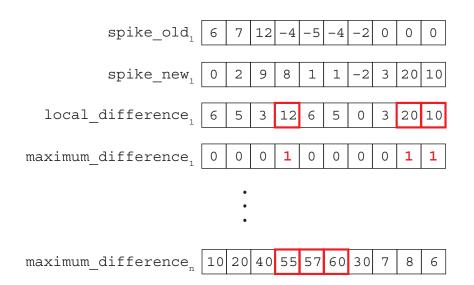

We proposed an alternative to the above algorithms with comparable accuracy yet far less complexity in [64]. In the **Maximum-Difference Test** (illustrated in Fig. 2.11), as in the Lilliefors Test, we seek the coefficients with the most variability, only now under the limited-memory conditions typical of implantable hardware. For an initial feature dimensionality N, four N-sample arrays of memory are initialized to zero: maximum\_difference, local\_difference, spike\_new, spike\_old. Throughout the training period, the  $i^{\text{th}}$  iteration of the algorithm is as follows:

Figure 2.10: Example showing the calculation of the "dip" statistic (d) for Hartigan's Dip Test for various PDFs (f(x) vs. x) and CDFs (F(x) vs. x).

- 1. Write the current feature samples to the array spike\_new.

- Subtract the values in spike\_new, coefficient by coefficient, from the values in spike\_old, and write the absolute value of the result to local\_difference.

- 3. Find the indices corresponding to the 3 largest values in local\_difference.

- 4. Increment the values in maximum\_difference indexed by these 3 indices.

- 5. Overwrite the values in spike\_old with the values in spike\_new.

These steps are repeated until the end of the training period. At this point, assuming that the goal is to reduce the dimensionality from N to D, maximum\_difference is scanned for the locations corresponding to the D largest values, and the coefficients corresponding to these indices are identified as the coefficients that will be used in clustering.

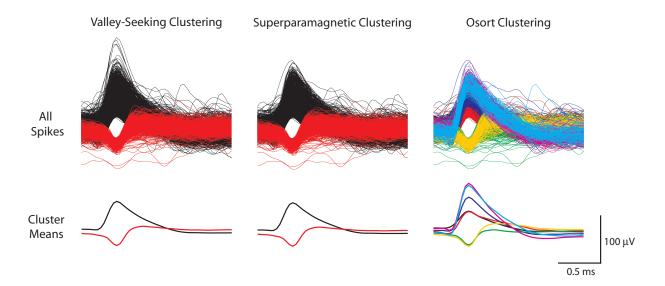

## 2.4.5 Clustering

Clustering, especially unsupervised clustering, is often the most difficult and most complex part of the sorting process.