## UC Riverside UC Riverside Electronic Theses and Dissertations

Title

Pipeline ADC Design Methodology

Permalink https://escholarship.org/uc/item/7cz7229w

**Author** Zhao, Hui

Publication Date 2012

Peer reviewed|Thesis/dissertation

#### UNIVERSITY OF CALIFORNIA RIVERSIDE

Pipeline ADC Design Methodology

A Dissertation submitted in partial satisfaction of the requirements for the degree of

Doctor of Philosophy

in

**Electrical Engineering**

by

Hui Zhao

June 2012

Dissertation Committee:

Prof. Albert Wang, Chairperson Prof. Sheldon Tan Prof. Qi Zhu

Copyright by Hui Zhao 2012 The Dissertation of Hui Zhao is approved:

Committee Chairperson

University of California, Riverside

#### Acknowledgements

This research project would not have been possible without the support of many people. First and foremost, I offer my sincerest gratitude to my advisor, Dr Albert Wang, who has supported me throughout my thesis with his patience and knowledge. I attribute the level of my Ph.D. degree to his encouragement and effort and without him this thesis would not have been completed or written.

I wish to express my love and gratitude to my beloved families; for their understanding & endless love, through the duration of my studies.

Deepest gratitude is also due to my committee members: Prof. Dr Qi Zhu, Prof. Dr. Sheldon Tan and Prof. Albert Wang. I'd like to thank all my graduate friends, especially group members at LICS lab at UC Riverside, Xin Wang, He Tang, Qiang Fan, Zitao Shi, Lin Lin and Jian Liu. Without their knowledge and assistance, this study would not have been successful. Special thanks also to Zongyu Dong, Li Wang, and Rui Ma for teamwork and invaluable layout assistance.

I would also like to convey thanks to the OmniVision Technology Inc. for providing internship and test-chip tape-out opportunity.

Lastly, I offer my regards and blessings to all of those who supported me in any respect during my Ph.D. studies.

To my parents for all the support.

In memory of my grandmother.

#### ABSTRACT OF THE DISSERTATION

Pipeline ADC Design Methodology

by

Hui Zhao

#### Doctor of Philosophy, Graduate Program in Electrical Engineering University of California, Riverside, June, 2012 Prof. Albert Wang, Chairperson

Demand for high-performance analog-to-digital converter (ADC) integrated circuits (ICs) with optimal combined specifications of resolution, sampling rate and power consumption becomes dominant due to emerging applications in wireless communications, broad band transceivers, digital-intermediate frequency (IF) receivers and countless of digital devices. This research is dedicated to develop a pipeline ADC design methodology with minimum power dissipation, while keeping relatively high speed and high resolution.

Pipeline ADC is a mixed-signal system, which consists of sample and hold amplifier (SHA), sub-ADC, multiplying digital-to-analog Converter (MDAC) and bandgap voltage reference, comparator, switch-capacitor circuits and biasing circuits. This project set up a pipeline ADC design flow. It links all the specifications between the system levels and circuit levels together. With this design flow, if the overall ADC specifications are given, such as resolution, sampling rate, voltage supply and input signal range, all the sub-block circuitry specifications are achieved.

This paper studies all the sub-block circuits of pipeline ADC first, and then come up with all the constraints and limitations for all the circuitry in term of speed and noises. Then a system level speed and power trade off consideration is explored in order to optimize the overall performance.

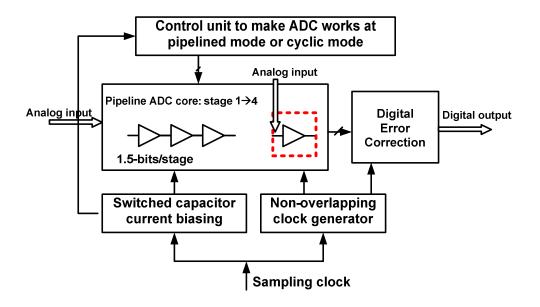

As verification of the proposed design methodology, a 10-bit 40MHz pipeline analog-to-digital converter prototype is developed in commercial TSMC 90nm CMOS technology: using op-amp sharing, dynamic biasing methods, it works in two modes: pipelined ADCs for high speed, cyclic ADC for low speed (only last stage runs, other stages are power off to save power). For pipeline mode, the total power consumption decrease as the sampling frequency drops.

Index terms: pipeline ADC, design methodology, CMOS, mixed-signal circuits

## Contents

| List of Figures                            | Х   |

|--------------------------------------------|-----|

| List of Tables                             | xiv |

| List of Symbols and Abbreviations          | xv  |

| 1 CHAPTER 1 INTRODUCTION                   | 1   |

| 2 CHAPTER 2 OVERVIEW OF ADC                | 13  |

| 3 CHAPTER 3 PIPELINE ADC BLOCK STUDY       | 26  |

| 4 CHAPTER 4 PIPEINE ADC POWER OPTIMIZATION | 73  |

| 5 CHAPTER 5 PIPELINE ADC DESIGN EXAMPLE    | 91  |

| 6 CHAPTER 6 CONCLUSIONS                    | 110 |

| REFERENCE                                  | 112 |

# **List of Figures**

| Figure 1.1 ADC in the Interface between Analog and Digital World.               | 2  |

|---------------------------------------------------------------------------------|----|

| Figure 1.2 ADC Applications.                                                    | 4  |

| Figure 1.3 Analog-to-Digital Converter Block Diagram.                           | 5  |

| Figure 1.4 ADC Static Errors.                                                   | 9  |

| Figure 1.5 ADC Dynamic Parameters.                                              | 12 |

| Figure 2.1 A Typical Structure of A Flash ADC.                                  | 15 |

| Figure 2.2 Two-Step Flash ADC.                                                  | 18 |

| Figure 2.3 First Order Sigma-Delta ADC.                                         | 20 |

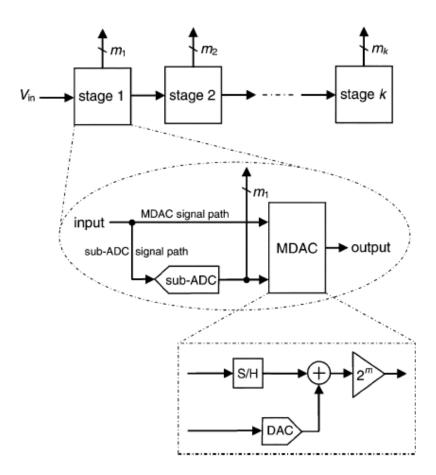

| Figure 2.4 A Pipelined ADC.                                                     | 23 |

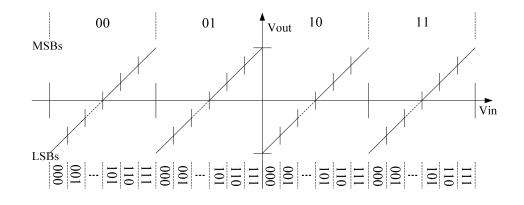

| Figure 3.1 Pipeline ADC Transfer Curve.                                         | 27 |

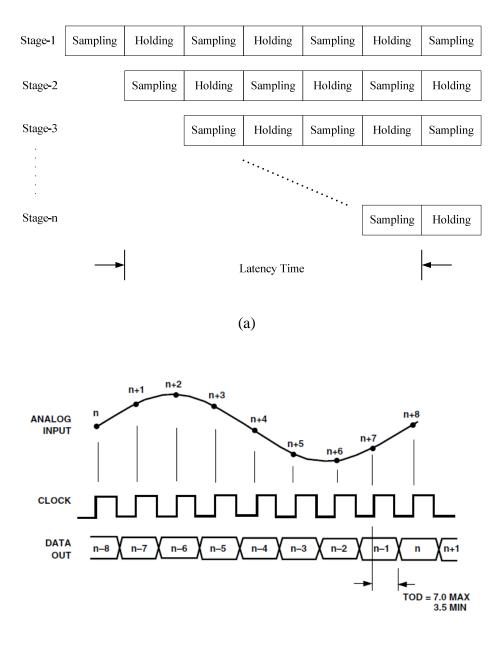

| Figure 3.2 (a) Stage Operation Modes (b) data latency in pipeline ADC           | 28 |

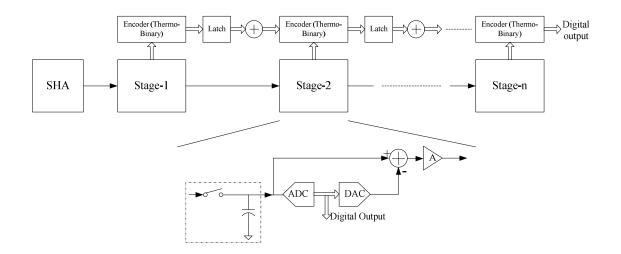

| Figure 3.3 Detailed Pipeline ADC Architecture.                                  | 29 |

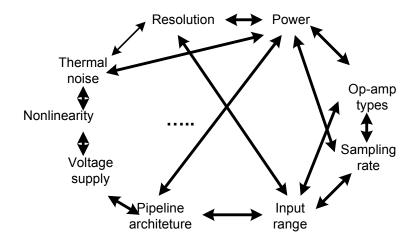

| Figure 3.4 Pipeline ADC Design Matrix.                                          | 30 |

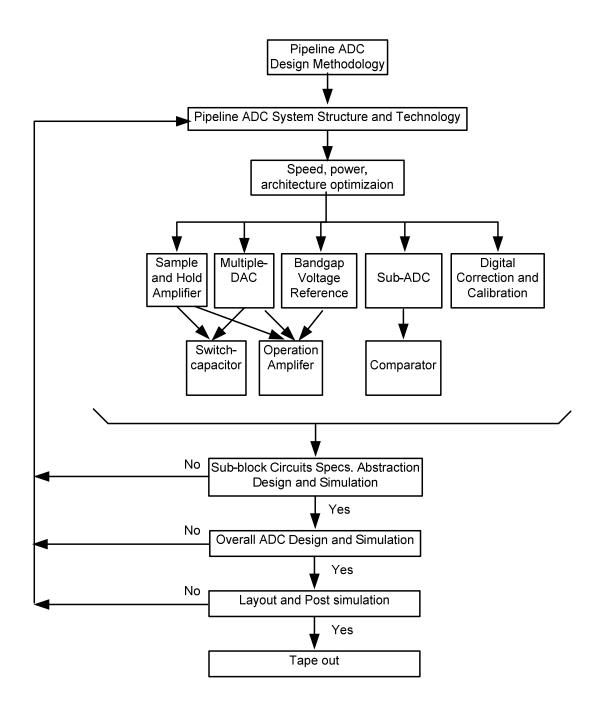

| Figure 3.5 Pipeline ADC Design Flow.                                            | 32 |

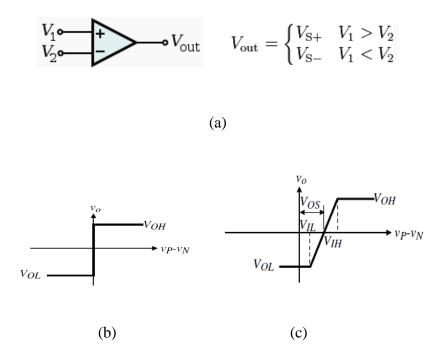

| Figure 3.6 (a) Comparator Symbol (b, c) Ideal/Practical Transform Function.     | 33 |

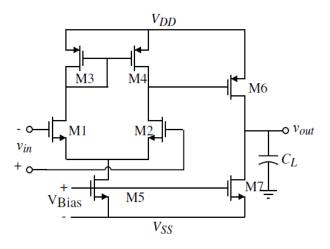

| Figure 3.7 Amplifier-type Comparator.                                           | 34 |

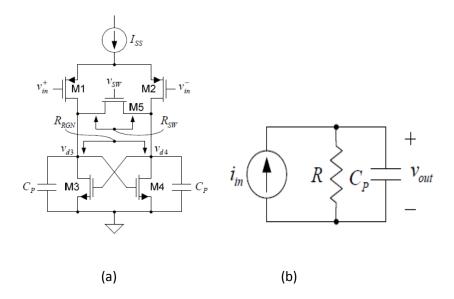

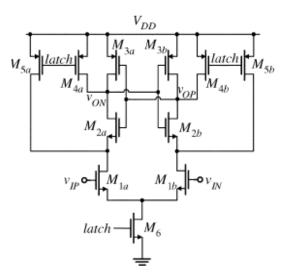

| Figure 3.8 (a) Typical Latch-type Comparator (b) Equivalent Small Signal Model. | 35 |

| Figure 3.9 Kickback Noise.                                                      | 38 |

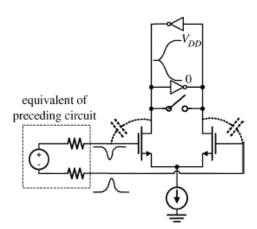

| Figure 3.10 Static Latched Comparator.                                          | 39 |

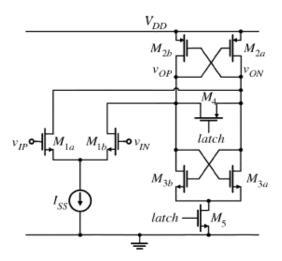

| Figure 3.11 Class-AB Latched Comparator.                                        | 39 |

| Figure 3.12 Dynamic Latched Comparator.                                         | 40 |

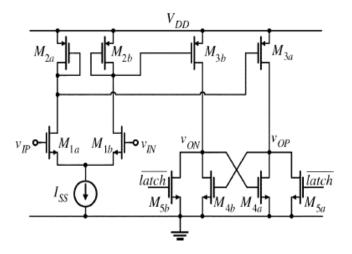

| Figure 3.13 Minimizing Kickback Noise.                                          | 43 |

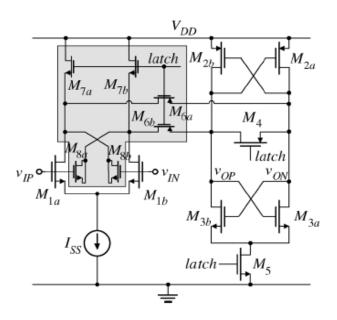

| Figure 3.14 (a) OP-AMP Notation, Ideal op-amp.                                  | 46 |

| Figure 3.15 Two-stage Op-amps.                                                  | 48 |

| Figure 3.16 Telescopic Op-amp.                                               | 49  |

|------------------------------------------------------------------------------|-----|

| Figure 3.17 Folded-cascode Op-amps.                                          | 51  |

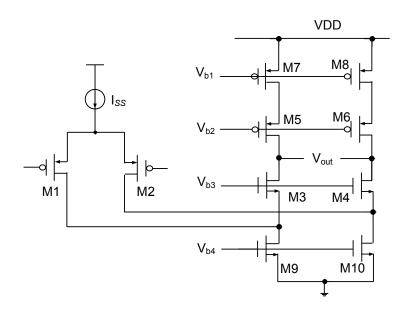

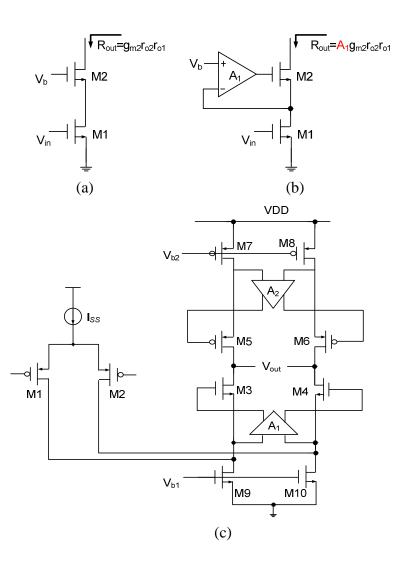

| Figure 3.18(a, b) Gain Boosting Technology.                                  | .53 |

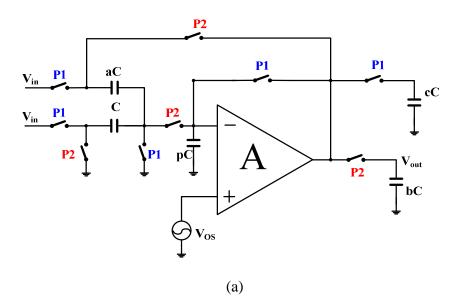

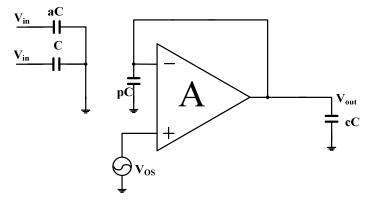

| Figure 3.19 (a) SHA (b) Phase 1 (c) Phase 2.                                 | 56  |

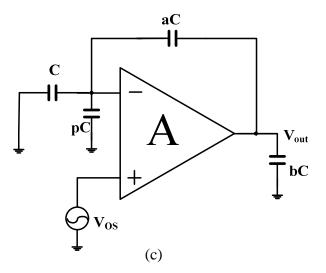

| Figure 3.20 (a) MDAC (b) Phase 1 (c) Phase 2.                                | 62  |

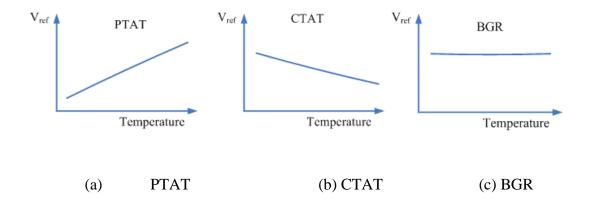

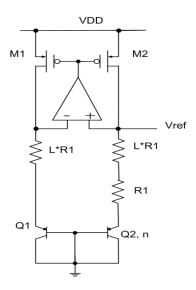

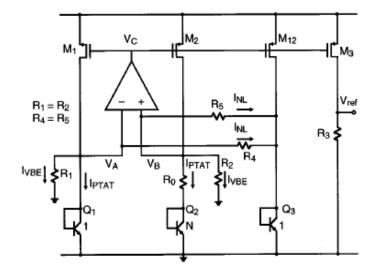

| Figure 3.21 Voltage Reference.                                               | 64  |

| Figure 3.22 Bandgap Voltage Reference.                                       | 65  |

| Figure 3.23 Curvature-compensated BGR.                                       | 67  |

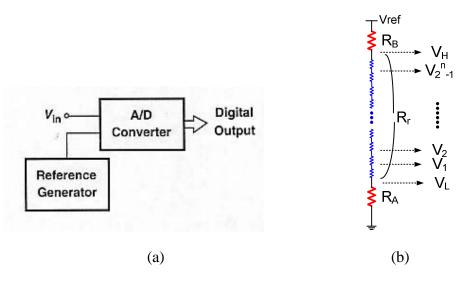

| Figure 3.24 Reference Generator.                                             | 69  |

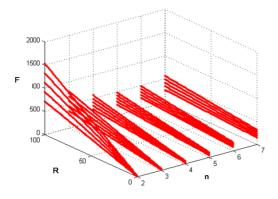

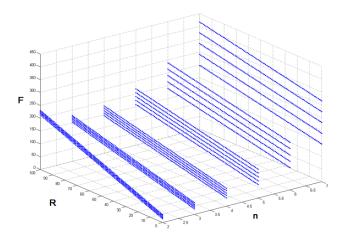

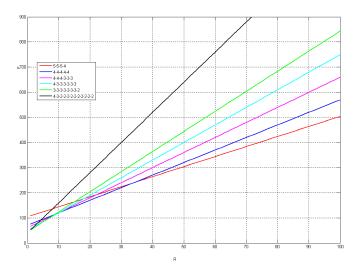

| Figure 4.1 Power F vs. R and n.                                              | 75  |

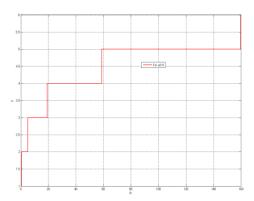

| Figure 4.2 optimized power vs. R.                                            | 76  |

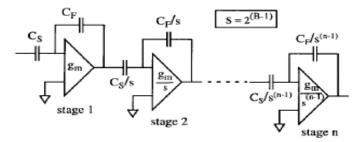

| Figure 4.3 Capacitor Scaling Down.                                           | 77  |

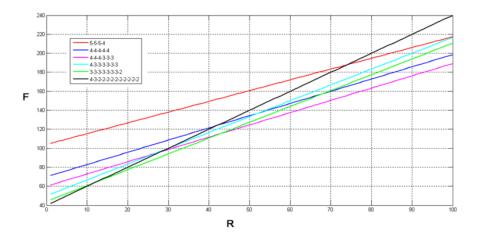

| Figure 4.4 Normalized Power F vs. R and n.                                   | 79  |

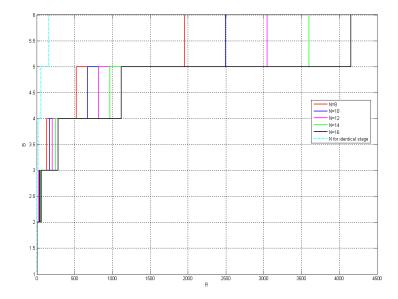

| Figure 4.5 Optimized B vs. R.                                                | 80  |

| Figure 4.6 Optimized Power vs. R.                                            | 82  |

| Figure 4.7 Optimized Power with Both Capacitor and Resolution Scaling vs. R. | 83  |

| Figure 4.8 Pipeline ADC Structures.                                          | 84  |

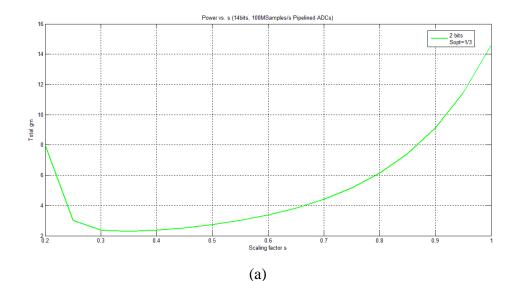

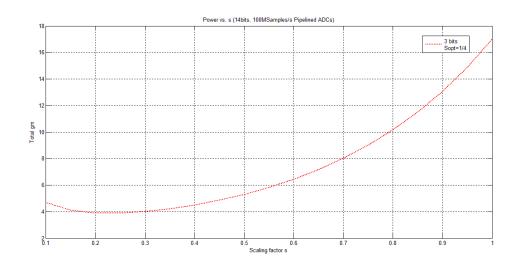

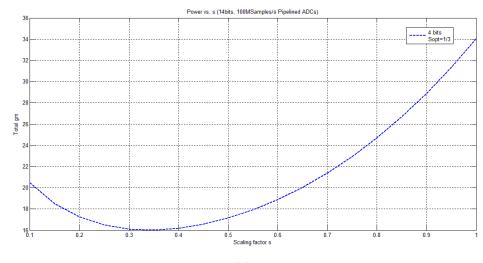

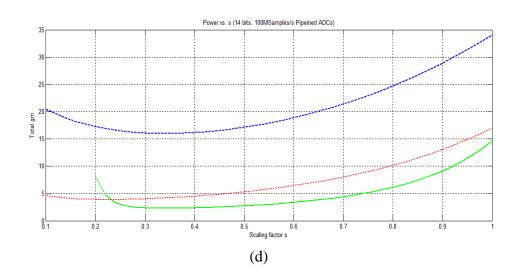

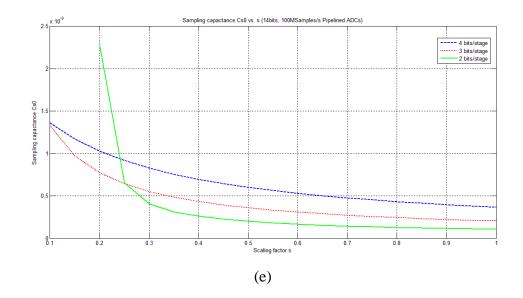

| Figure 4.9 Power vs. Capacitor Scaling Based on Different Stage Partition.   | 90  |

| Figure 5.1 Hybrid ADC.                                                       | 94  |

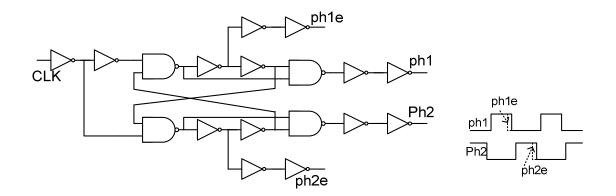

| Figure 5.2 Non-overlapping Clock Generator.                                  | 95  |

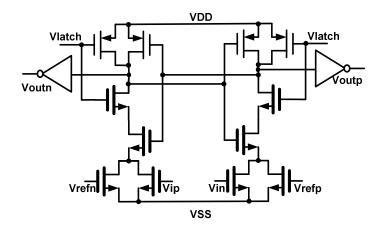

| Figure 5.3 Comparator.                                                       | 95  |

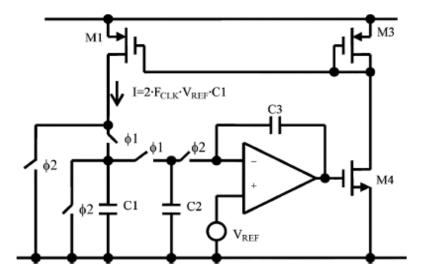

| Figure 5.4 Dynamic Biasing.                                                  | 96  |

| Figure 5.5 (a) Folded-cascade Op-amp with Gain Boosting.                     | 98  |

| Figure 5.6 1st 2nd 3rd MDAC.                                                 | 99  |

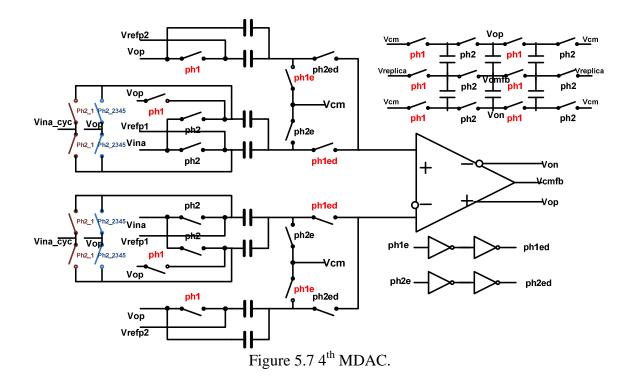

| Figure 5.7 4th MDAC.                                                         | 100 |

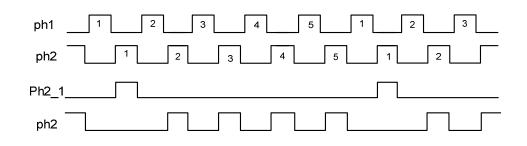

| Figure 5.8 Phase Scheme of Cyclic ADC.                                       | 100 |

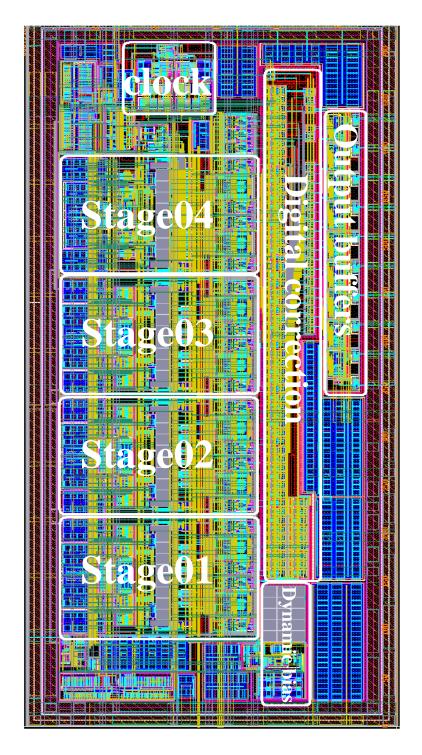

| Figure 5.9 Layout.                                          | 101 |

|-------------------------------------------------------------|-----|

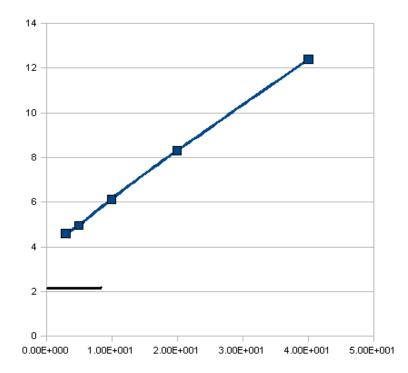

| Figure 5.10 Total Power Consumption vs. Sampling Frequency. | 102 |

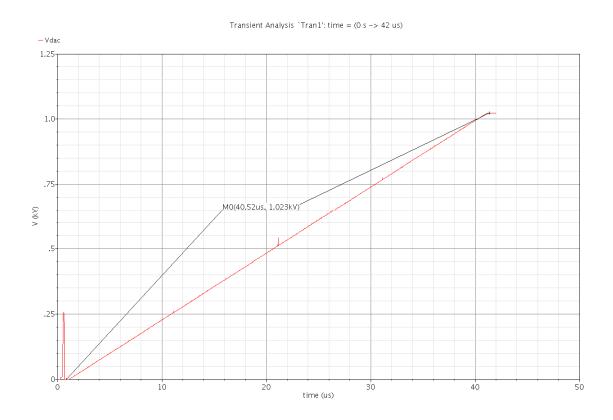

| Figure 5.11 Ramp Signal to Verify Monotonicity.             | 103 |

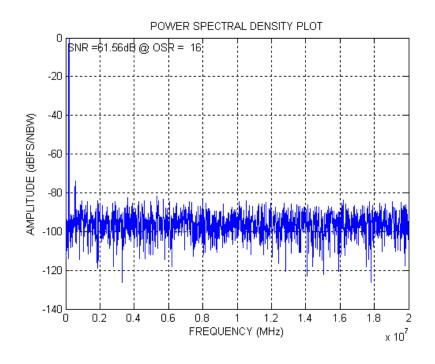

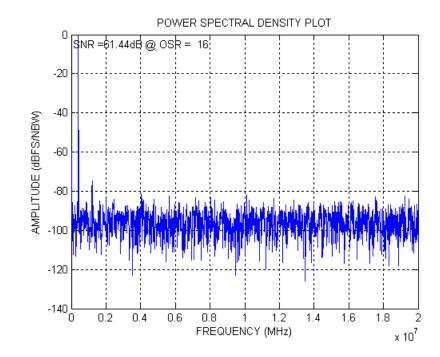

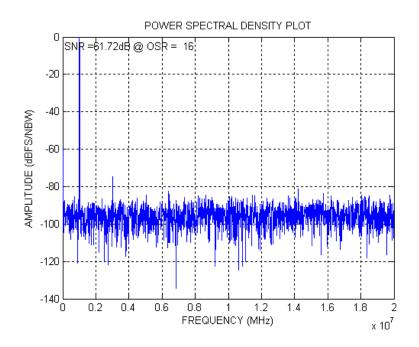

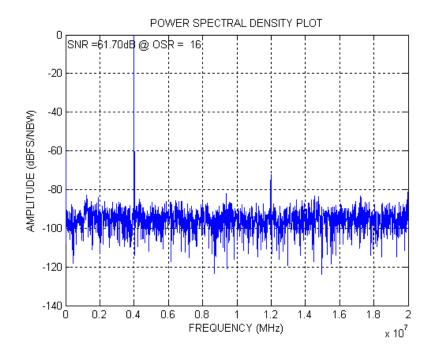

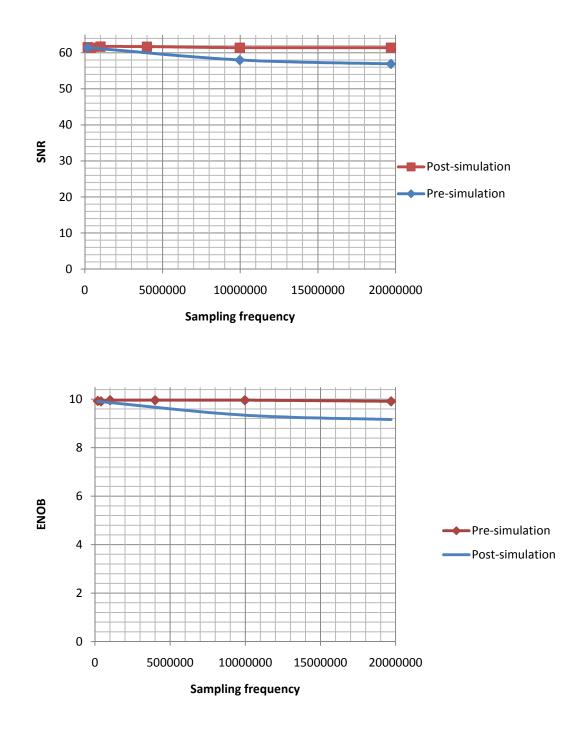

| Figure 5.12 Spectrum Analysis.                              | 106 |

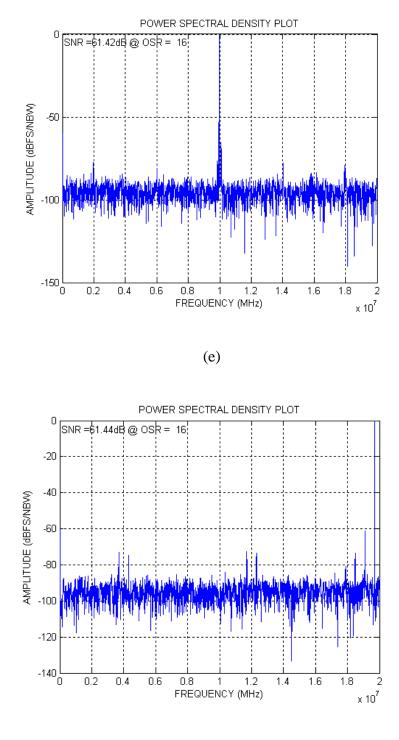

| Figure 5.13 SNR and ENOB.                                   | 107 |

## List of Tables

| Table 2.1 Comparison of Different Types of ADCs.       | 25 |

|--------------------------------------------------------|----|

| Table 3.1 Performance Comparisons.                     | 41 |

| Table 3.2 Time Constant Comparisons.                   | 42 |

| Table 3.3 The Specifications of Two-stage Op-amp.      | 49 |

| Table 3.4 The Specifications of Telescopic Op-amp.     | 50 |

| Table 3.5 The Specifications of Folded-cascode Op-amp. | 52 |

| Table 3.6 The Specifications of Gain-boosting Op-amp.  | 54 |

| Table 3.7 The Performance Comparisons of Op-amps.      | 55 |

| Table 5.1 Hybrid Pipeline ADC Specification.           | 92 |

| Table 5.2 Pins Definition of Pipeline ADC.             | 93 |

# List of Symbols and Abbreviations

| Abbreviations | Definition                              |

|---------------|-----------------------------------------|

| ADC           | Analog-to-Digital Converter             |

| BER           | Bit Error Rate                          |

| BGR           | Band-gap Reference                      |

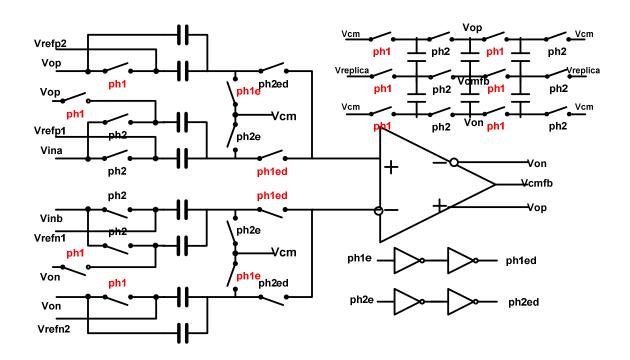

| CMFB          | Common-Mode Feedback                    |

| DAC           | Digital-to-Analog Converter             |

| DNL           | Differential Non-Linearity              |

| DR            | Dynamic Range                           |

| DSP           | Digital Signal Processing               |

| ENOB          | Effective Number Of Bits                |

| FS            | Full Scale                              |

| IF            | Intermediate Frequency                  |

| INL           | Integral Non-Linearity                  |

| LSB           | Least Significant Bit                   |

| MDAC          | Multiplying Digital-to-Analog Converter |

| MSB           | Most Significant Bit                    |

| RF            | Radio Frequency                         |

| SC            | Switched Capacitor                      |

| SFDR          | Spurious-Free Dynamic Range             |

| SNDR          | Signal-to-Noise-and-Distortion Ratio    |

| SNR           | Signal-to-Noise Ratio                   |

| THD           | Total Harmonic Distortion               |

## **CHAPTER 1**

## **INTRODUCTION**

#### **1.1 Motivation of ADC**

In recent years, with the extensive implementation of digital computing and signal processing in communications, instrumentation, image processing and industrial control, analog to digital and digital to analog conversion applications in the field is expanding rapidly. Monolithic integration of technology, the novel circuit structure of integrated circuits, and advances in technology made the analog to digital and digital to analog conversion circuit design a great change, and continue to generate new areas of research and development.

At present, the electronic systems are in a trend of increasingly digitalization. Digital circuits and digital processing is almost everywhere. The main reason is: compared to the analog circuits, digital circuits with low noise sensitivity, strong antiinterference ability, high stability and wide adaptability, easy to design and automated testing, more extensive programmability features, but also because of advances in integrated circuit technology to continuously improve the performance of digital circuits. Large-scale integration (VLSI) technology allows each new generation of digital circuits to achieve higher speed, more features per chip, lower power consumption and cost. In addition, the progress of the improvement of the circuit structure and computer-aided design (CAD) analysis and synthesis tools also promote the development of digital integrated circuits.

Although digital circuits advantages, and in many areas, it is gradually replacing analog circuit, but the physical environment of our existence cannot be separated from analog signal processing. First, the signals appearing in nature are almost always analog, such as temperature, pressure, time, speed, voltage, current, voice, luminous flux, etc. Secondly, the way of human perceives and keeps information is the analog mode.

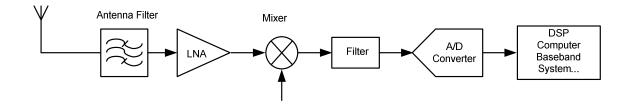

In order to establish the interface of the digital processor and the analog world, data acquisition and reconstruction of the circuit is necessary. Therefore, Analog-to-Digital Convertor (ADC) and Digital-to-Analog Convertor (DAC) is very important and irreplaceable (Shown in Figure 1.1).

Figure 1.1 ADC in the Interface between Analog and Digital World.

ADC is a device that convert analog input signal into digital output signal. With the rapid development of digital computing and signal processing in electronic systems in the past few decades, it virtually transferred the world into a digital era. For a long time, as the bridge between the real analog world and the digital world, Analog-to-Digital Converters (ADCs) have been developed in different uni-directions to meet different

application requirements. Over-sampling sigma-delta ADCs, successive approximation ADCs and algorithmic ADCs pushing the resolution up to 24bits, traded off with the limited bandwidth, are widely employed in audio communication; Flash and folding and interpolating ADCs, featuring highest speed at the cost of low resolution (no more than 10-bit) and large power dissipation and area, are adopted in disk drive channels and magnetic data storage systems. Since 1990s, high-performance ADC ICs with optimized combined specifications of resolution, sampling rate and power consumption (as opposed to individual improvement) are in demand. For example, the IF frequencies in a typical direct-IF (intermediate frequency) receiver vary from 50MHz to 200MHz, which requires an ADC sampling rate up to 400MHz. Practically, the signal-to-noise ratio (SNR), dynamic range and linearity requirements suggest that a better than 14 bits resolution is necessary at affordable power dissipation. In addition, soft radio is proposed to digitize signal at radio frequency (RF) domain and sort everything to the powerful digital signal processing (DSP) IC chip, in order to bypass the obstacle originated from different wireless standards. The critical building block in soft radio is the high sensitivity (that is high SNR and high spurious free dynamic range (SFDR) ADC, with sampling frequency being pushed further to several Giga-Hertz and relatively lower power consumption, since the ADC must share the power budget with the other functional blocks in the same transceiver system.

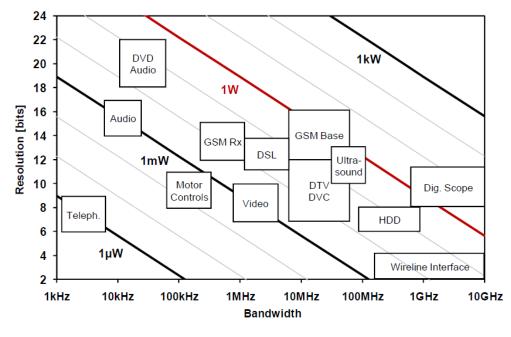

Figure 1.2 ADC Applications.

Market investigation results (shown in Figure 1.2) coming from commercial products of ADC manufactures (Analog Devices Inc.) indicate that ADC are widely used in many areas, such as communication, audio, computer, UWB, also the speed of ADC varies from less 100kHz to over GHz and the resolution varies from 6 to 22bits. To join with IC industry, this research focuses on the pipeline ADC whose resolution is 8~14bits and speed is 100k~200MHz in the mainstream CMOS process.

#### **1.2 A/D Conversion Overview**

### **1.2.1 ADC Definition**

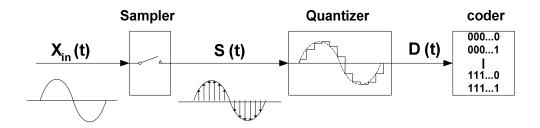

As the interface between the real world signals and the digital codes, ADCs play a major role in the data acquisition and digitizing process. ADC convert continuous change of analog signal with amplitude and time into digital signals, which are discrete changes in the amplitude and time. Shown in Figure 1.3 is a block diagram of this process. Figure 1.3 shows the block diagram of an ADC, which consists of three building blocks – sampler, quantizer and coder. Input signals are converted to discrete time sampled signal by the sample circuit under the sampling clock control. Hold circuits play the role of the circuit to maintain the sampled value unchanged in the transformation process.

Figure 1.3 Analog-to-Digital Converter Block Diagram.

Sampler discretizes analog signal in time domain. The discrete-time continuousamplitude signal is then mapped into a discrete level by quantizer, which implements a many-to-one transformer by approximating the signal to one of sub-divided quantization levels. Uniform quantization provides the minimum quantization error for a statistically equally distributed signal, while non-uniform quantization is a better choice for signals, such as audio one, whose amplitude is not evenly distributed in the input range. For both the uniform and non-uniform quantization, a unique digital code is assigned to each quantization level. The analog-to-digital conversion process is fulfilled by providing a series of digital codes to represent the time-discrete and amplitude-discrete analog signal.

#### **1.2.2 Main design direction of ADC performance**

The first thing is high-speed. As the bandwidth of the signal source needs to be digitalized became wider and wider, so the audio, video, and RF ADC converters have to work at higher sampling rate.

Second is high-precision. Due to the growing dynamic range of the signal source needs to digitize, people have increasingly high quality requirements of data processing, so the accuracy of the converter continues to increase.

Third, it is easy for monolithic integration. At present, low-cost, low power consumption and high reliability of monolithic integration of the system on-chip system (SOC) has become a trend. Complete electronic systems are often mixed-signal systems, including digital circuits, analog circuits, analog to digital and digital to analog conversion circuit.

#### **1.2.3 ADC Characterization**

ADC performance is characterized by resolution, speed, power, INL, DNL and so on. It can be divided into two parts: static features and dynamic feature. **Resolution:** ADC resolution is defined as the minimum input signal to make a change at digital output, usually expressed as the number of bits n of the output binary code. The resolution shows the resolving ability of the input signal. Theoretically, for an n-bit ADC, the minimum input voltage that can be resolved is  $VREF/2^n$ , equivalent to a quantitative unit of input voltage. Another term, called effective number of bits (ENOB), therefore, is introduced to measure the resolution for a pure sinusoidal signal accurately. It is defined as

$$ENOB = \frac{SNDR - 1.76}{6.02}$$

(1.1)

where SNDR represents signal-to-noise and distortion ratio.

- <u>Quantization error</u> (or quantization noise) is the difference between the original signal and the digitized signal. Hence, The magnitude of the quantization error at the sampling instant is between zero and half of one LSB. Quantization error is due to the finite resolution of the digital representation of the signal, and is an unavoidable imperfection in all types of ADCs.

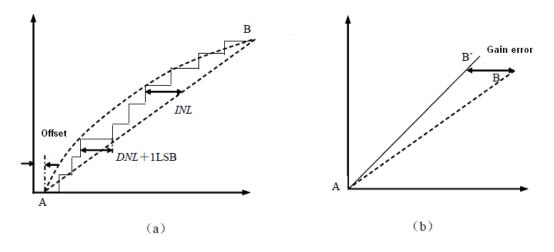

- Differential Non-linearity (DNL). DNL error is defined as the difference between an actual step width and the ideal value of 1LSB (see Figure 1.4). For an ideal ADC, in which the differential nonlinearity coincides with DNL = 0LSB, each analog step equals 1LSB (1LSB = VFSR/ $2^N$ , where VFSR is the full-scale range and N is the resolution of the ADC) and the transition values are spaced exactly 1LSB apart. A DNL error specification of less than or equal to 1LSB guarantees a

monotonic transfer function with no missing codes. An ADC's monotonicity is guaranteed when its digital output increases (or remains constant) with an increasing input signal, thereby avoiding sign changes in the slope of the transfer curve.

- Integral Non-linearity (INL). INL error is described as the deviation, in LSB or percent of full-scale range (FSR), of an actual transfer function from a straight line. The INL-error magnitude then depends directly on the position chosen for this straight line. At least two definitions are common: best straight-line INL and end-point INL. It is defined as the deviation of any single step from the ideal size and measured in LSBs. A less than  $\pm 1LSB$  DNL error and less than  $\pm \frac{1}{2}LSB$ INL error specification guarantees no missing codes and a monotonic transfer function.

- <u>Offset Error</u>. Offset error identifies the horizontal difference between the actual transfer curve and the ideal one at the lowest transfer level. It is a figure-of-merit that measures the transfer curve matching at a single point and indicates the average error of the converter.

- <u>Gain Error.</u> Gain error, given as a percentage of the ideal input full-scale range, is reflected in the input/output transfer function as the slope deviation from the infinite resolution characteristic. Comparing with offset error, which can be measured at 1½ LSB above the most-negative end, gain error may be estimated at

1<sup>1</sup>/<sub>2</sub> LSB below the most-positive end. Linear gain error doesn't introduce distortion as does nonlinear gain error.

Figure 1.4 demonstrates the static errors in the same ADC transfer curve.

Figure 1.4 ADC Static Errors.

**Speed:** Analog-to-digital conversion speed is characterized by input bandwidth and sampling rate, which is defined as how many times the input analog signal is sampled per second and determined by the transient response parameters, such as settling time, slew rate and aperture jitter, of the internal blocks located in the analog signal path. The primary elements in the speed performance matrix are explained in this section.

<u>Aperture jitter.</u> When the input signal has large slewing rate, all the SNR of S/H circuit will decrease because of the special problem introduced by jitter issue from sampling clock. In order to get the relationship between the maximum allowable slewing rate and sampling rate, as well as resolution, let's consider that the voltage uncertainty of the input signal caused by clock jitter is less than 1LSB, so the jitter

impact could be ignored. For a full scaled input signal Vin = Asin  $2\pi ft$ , its maximum changing rate is  $2\pi fmaxA$ , so:

$$2\pi fmaxA \times \Delta t < 1LSB \tag{1.2}$$

$$2\pi fmaxA \times \Delta t < \frac{2A}{2^n} \tag{1.3}$$

- <u>Total harmonic distortion (THD)</u>. THD is the ratio of the rms value of the fundamental signal to the mean value of the root-sum-square of its harmonics (generally, only the first 5 harmonics are significant). THD of an ADC is also generally specified with the input signal close to full-scale, although it can be specified at any level.

- Signal-to-Noise Ratio (SNR). SNR (or sometimes called SNR-without-harmonics) is calculated from the FFT data the same as SINAD, except that the signal harmonics are excluded from the calculation, leaving only the noise terms. In practice, it is only necessary to exclude the first 5 harmonics, since they dominate. The SNR plot will degrade at high input frequencies, but generally not as rapidly as SINAD because of the exclusion of the harmonic terms. A few ADC data sheets somewhat loosely refer to SINAD as SNR, so you must be careful when interpreting these specifications and understand exactly what the manufacturer means. In a well-designed and matching converter, SNR presents an upper limit to both the static and dynamic performance and is characterized by a single tone or a multi tone measurement with a full scale sinusoidal input as

$$SNR_{dB} = 6.02N + 4.77 - 20\log \frac{Signal \_ peak \_ amplitude}{Signal \_ rms \_ value}$$

(1.4)

Where N is the resolution of ADCs. If the signal level is reduced, the value of SNR decreases and the ENOB decreases. It is necessary to add a correction factor for calculating ENOB at reduced signal amplitudes as shown in Equation (1.4)

- Signal-to-Noise and Distortion Ratio (SNDR). SNDR is the ratio of the rms value of the fundamental signal to the mean value of the root-sum-square of its harmonics plus all noise components (excluding dc). The bandwidth over which the noise is measured must be specified. In the case of an FFT, the bandwidth is dc to fs/2. (If the bandwidth of the measurement is dc to fs/2 (the Nyquist bandwidth), THD + N is equal to SINAD—see below). Be warned, however, that in audio applications the measurement bandwidth may not necessarily be the Nyquist bandwidth. The SINAD plot shows that the ac performance of the ADC degrades due to high-frequency distortion and is usually plotted for frequencies well above the Nyquist frequency so that performance in undersampling applications can be evaluated. SINAD plots such as these are very useful in evaluating the dynamic performance of ADCs.

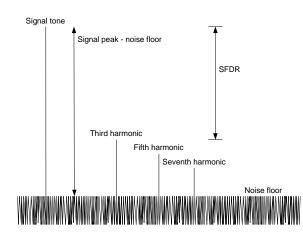

- <u>Spurious Free Dynamic Range (SFDR).</u> Spurious free dynamic range is the ratio of the rms value of the signal to the rms value of the worst spurious signal regardless of where it falls in the frequency spectrum. The worst spur may or may not be a harmonic of the original signal. SFDR is an important specification in communications systems because it represents the smallest value of signal that

can be distinguished from a large interfering signal (blocker). SFDR can be specified with respect to full-scale (dBFS) or with respect to the actual signal amplitude (dBc).

Figure 1.5 illustrates the relationship among these dynamic parameters.

Figure 1.5 ADC Dynamic Parameters.

### **CHAPTER 2**

ADC was first boosted in 1930s because of widely used PCM (Pulse Code Modulation) technology in telecommunication area. It changed the analog coding and decoding technology into digital signal processing technology. Until 1950s, with the emergence of high-speed digital computer and aircraft/missile data processing system, ADC has gained a further development.

After Microprocessors were well-developed in 1970s, it triggered a technological revolution in the field of digital signal processing and computer. In 1971, the first Monolithic ADC was designed as analog/digital interface circuitry. In the past 20 years, due to deep sub-micron integrated technology becomes more popular; it promotes a new area of analog integrated circuits: mixed signal integrated circuit. This chapter will briefly introduce all typical ADC, such as flash ADC, two-step ADC, pipline ADC and so on.

## **OVERVIEW OF ADC**

#### 2.1 AD Classification

According to relationship between sampling rate and signal frequency, ADC can be divided into three types: the Nyquist ADC, subsampling ADC, and oversampling ADC. Nyquist ADC: in order to ensure accurate reconstruction of the original value theoretically, ADC must comply with the sampling theorem, the sampling frequency is greater than or equal to twice the highest frequency of the input signal. Since anti-aliasing filter cannot be an ideal low-pass characteristics, there must be a transition band, so the sampling frequency slightly higher than twice the bandwidth of the analog signal.

Sub-sampling ADC: input signal only occupies a small part of the band pass frequency, it is possible to make the sampling frequency smaller than the highest signal frequency, but to ensure that the sampled spectrum do not overlap.

Oversampling ADC, the sampling frequency is much higher than the Nyquist frequency. The following part of the digital filter circuit is used to remove noise outside the signal bandwidth. Oversampling technique can reduce the quantization noise level, in order to achieve high-precision.

According to performance, ADC can be divided into high-speed AD converter, and high accuracy AD converter.

Based on architecture differences, ADC can be divided into the serial structure (pipeline), parallel structure (time-interleaving), and serial and parallel AD converter.

#### 2.2 Flash AD Converters

Flash converters are extremely fast compared to many other types of ADCs. It is also quite simple and, apart from the analog comparators, only requires logic for the final conversion to binary. It can achieve extremely high speed (over 1Gsamples/second) with low resolution.

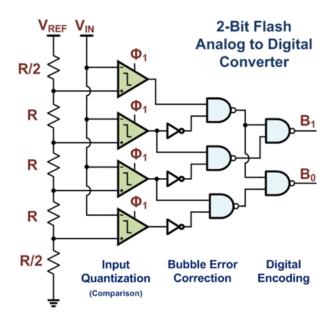

The typical structure of a 2bit flash ADC is shown in Figure 2.1. A Flash converter requires a huge number of comparators compared to other ADCs, especially as the precision increases.

Figure 2.1 A Typical Structure of A Flash ADC.

An N-bit flash ADC needs a resistor ladder composing  $2^{N}$  equal resistors. These resistor ladders generate all possible  $2^{N}$ -1 voltage levels, then followed by $2^{N}$ -1 comparators and digital encoders. Comparators are usually composed of a pre-amplifier used for sampling and amplifying the input signal, and a latch used for making final decision.

Each comparator samples the input signal and compares this signal to the reference voltage. Then the comparator generates a digital output "1" or "0" indicating whether the input signal is larger or smaller than the reference voltage assigned to that comparator. The digital outputs of the comparators are often referred to as thermometer codes, and these codes are encoded as 1-of-n codes. Finally, 1-of-n codes are converted to binary outputs.

This ADC requires a lot of the comparator, and thus the hardware cost of the power, area and other large input capacitance. Its resolution is limited by the accuracy of the reference voltage and the offset voltage of the comparator. For CMOS technology, it also need to trade-off between the small offset voltage and high conversion speed. Therefore, the structure is more commonly used in the occasion of the 6 ~ 8 precision. Flash ADC is the most classic high-speed AD converter, and other structures in the high-speed AD converter are evolved on this basis.

The flash AD converter key weakness is that the hardware cost has grown exponentially with the resolution. The number of comparators is  $2^{n}$ -1. When the resolution is 8 or more, it requires very large power and area. Also, because the heavy used comparators and lack of front end sample and hold amplifier, it will bring some special non-ideal characteristics, such as the variations of the ladder reference voltage, the interference immunity of signal glitches variation, the sensitivity of sampling point of different input signal slew rate. These issues will impact the conversion accuracy. When the difference between two input signals of the comparator is relative small, it will take longer period of time to go through in order to decide a stable logic output. This condition is called comparator metastability. If the instantaneous value of the input signal value of flash AD converter is very close to one of comparators reference voltage, then the comparator output will be a long time uncertain, may bring the wrong digital output.

We can take some approaches to reduce the probability of occurrence of metastable error. For example: adding the number of latch behind each comparator, so as to allow a longer time to rebuild the thermometer code, which is a simple solution, but the power consumption is higher. Thermometer code to binary decoding using pipelining mothed is another way; this method allows the output of the comparator to experience more reconstruction time, but each comparator output level as the input of a logic gate. In addition, using Gray code between thermometer code and binary code can also effectively inhibit the comparator metastability error. In Gray coding circuit, the input signal does not appear in more than one input gate,, allowing to increase the time of reconstruction with pipelining.

#### 2.3 Two-Step Flash ADC

Because of the exponential growth of power dissipation, area, and input capacitance of a flash convert makes it impractical for resolution above 8 bits. Therefore,

trades-offs should be made between the resolution and the conversion rate. A two-step flash ADC is applied to trade speed for power dissipation and resolution.

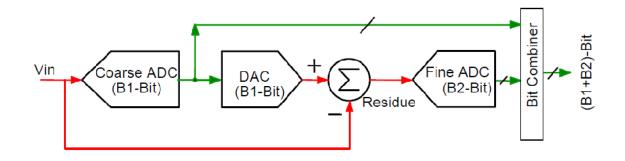

A two-step flash ADC consists of a coarse flash ADC stage, a DAC, a subtractor and a fine flash ADC stage. Normally, a front-end sample-and-hold circuit and an inter-stage gain amplifier between the subtractor and the fine flash ADC are necessary. The block diagram in Figure 2.2.1 illustrates the structure of a two-step flash ADC.

Figure 2.2 Two-Step Flash ADC.

In this type of ADC, the conversion takes two steps. During the first step, the most significant bits of the digital output are determined by the first stage flash ADC. Then a DAC converts this digital result back to an analog signal to be subtracted from the input signal. This residue is amplified by the inter-stage gain amplifier and then sent to the second stage flash ADC. The second stage flash determines the least significant bits of the digital output.

The resolution of the first coarse flash ADC is m bit, and that of second fine flash ADC is n bit. So the total digital output result ion is m+n. If digital correction is used, one of the flash ADC need residual bit, so the total resolution is larger m (or n) bit but smaller

than m+n bit. In flash ADC, comparators track the input signal for half of the sampling period, while make conversion for the other half of sampling period. However, for twostep ADC, because of extra DA conversion, subtraction, and second flash ADC work at same time, the speed of two-step ADC is limited.

The key principle of a two-step flash ADC is to amplify the residue of the coarse ADC, and this will largely reduce the number of comparators. Although the speed the two-step ADC is lower than flash ones. But the number of comparators is much smaller than that of flash ADC with same resolution: from  $2^{n+m}$ -1 to  $2^{n}+2^{m}$ -2. So the power and area are decreased.

#### 2.4 Oversampling AD Converters

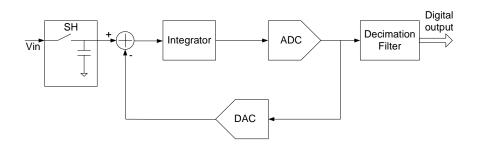

An oversampling converter uses a noise-shaping modulator to reduce the in-band quantization noise to achieve a high degree of resolution. It can shape the quantization noise and push the majority of the inband noise to higher frequencies. It modulates the analog input signal to a simple digital code, normally a one-bit serial stream using a sampling rate much higher than the Nyquist rate.

To understand noise shaping, consider the block diagram of a sigma-delta modulator of the first order (Figure 2.3). It includes a difference amplifier, an integrator, and a comparator with feedback loop that contains a 1-bit DAC. (This DAC is simply a switch that connects the negative input of the difference amplifier to a positive or a negative reference voltage.) The purpose of the feedback DAC is to maintain the average output of the integrator near the comparator's reference level.

The density of "ones" at the modulator output is proportional to the input signal. For an increasing input the comparator generates a greater number of "ones," and vice versa for a decreasing input. By summing the error voltage, the integrator acts as a lowpass filter to the input signal and a high-pass filter to the quantization noise. Thus, most of the quantization noise is pushed into higher frequencies. Oversampling has changed not the total noise power, but its distribution.

If we apply a digital filter to the noise-shaped delta-sigma modulator, it removes more noise than does simple oversampling. This type of modulator (first-order) provides a 9dB improvement in SNR for every doubling of the sampling rate. For higher orders of quantization, we can achieve noise shaping by including more than one stage of integration and summing in the sigma-delta modulator.

Figure 2.3 First Order Sigma-Delta ADC.

The oversampling ratio, called M, is a ratio of the clock frequency to the Nyquist frequency of the input signal. This oversampling ratio can vary from 8 to 256. The resolution of the oversampled converter is proportional to the oversampled ratio. The bandwidth of the input signal is inversely proportional to the oversampled ratio.

It is Very compatible with VLSI technology because most of the converter is digital High resolution. Single-bit quantizers use a one-bit DAC which has no INL or DNL errors. Provide an excellent means of trading precision for speed (16-18 bits at 50ksps to 8-10 bits at sampling rates of 5-10Msps).

Oversampled ADCs allow signal bandwidth to be efficiently traded for resolution. Noise shaping oversampled ADCs preserve the signal spectrum and shape the noise quantization spectrum. The modulator shapes the noise quantization spectrum with a high pass filter. This high-pass characteristic reduces the noise at low frequencies which is the key to extending the dynamic range within the bandwidth of the converter. The quantizer can be single or multiple bits. Single bit quantizers do not require linear DACs because a 1 bit DAC cannot be nonlinear. Multiple bit quantizers require ultra linear DACs. Modulators consist of combined integrators with the goal of high-pass shaping of the noise spectrum and cancellation of all quantizer noise but the last quantizer

#### 2.5 Pipelined ADC

The pipelined analog-to-digital converter (ADC) has become the most popular ADC architecture for sampling rates from a few megasamples per second (Msps) up to 100Msps. Compared to the two-step flash ADC which has just two stages, pipeline ADCs have multiple cascades stages.

Resolutions range from eight bits at the faster sample rates up to 16 bits at the lower rates. These resolutions and sampling rates cover a wide range of applications, including CCD imaging, ultrasonic medical imaging, digital receivers, base stations, digital video (for example, HDTV), xDSL, cable modems, and fast Ethernet.

Applications with lower sampling rates are still the domain of the successive approximation register (SAR) and integrating architectures, and more recently, oversampling/sigma-delta ADCs. The highest sampling rates (a few hundred Msps or higher) are still obtained using flash ADCs. Nonetheless, pipelined ADCs of various forms have improved greatly in speed, resolution, dynamic performance, and low power in recent years.

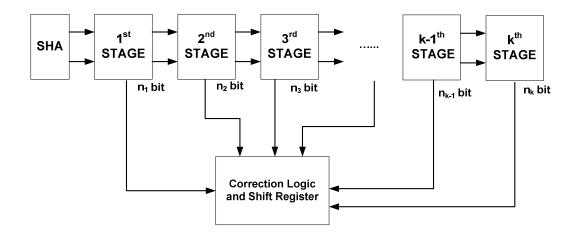

Each stage of the pipeline ADC consists of a sample-and-hold circuit, a sub-ADC, a DAC, a subtractor and an inter-stage gain amplifier. The block diagram of a pipeline ADC is illustrated in Figure 2.4.

Figure 2.4 A Pipelined ADC.

In this schematic, the analog input, IN, is first sampled and held steady by a sample-and-hold (S&H), while the flash ADC in stage one quantizes it to  $n_1$  bits. The  $n_1$  bit output is then fed to a  $n_1$ -bit DAC, and the analog output is subtracted from the input. This "residue" is then gained up by a factor of  $G_1$  and fed to the next stage (Stage 2). This gained-up residue continues through the pipeline, providing  $n_i$  bits per stage until it reaches the  $n_k$ -bit flash ADC, which resolves the last  $B_k$  bits. Because the bits from each stage are determined at different points in time, all the bits corresponding to the same sample are time-aligned with shift registers before being fed to the digital-error-

correction logic. Note when a stage finishes processing a sample, determining the bits, and passing the residue to the next stage, it can then start processing the next sample received from the sample-and-hold embedded within each stage. This pipelining action is the reason for the high throughput.

The concurrency of the pipeline ADC makes the maximum conversion rate almost independent of the number of stages because the first stage determines the conversion rate, but there is a delay time since the signal must work through all stages before the complete digital outputs are generated. This delay could be an issue if the pipeline ADC is part of a feedback system [3]. In addition, the number of stages does have great impact on the noise performance, power dissipation, linearity and accuracy.

#### 2.6 Summary of ADCs

Table 2.1 shows the differences of different ADCs. Flash ADC has the fast speed while lowest resolution. Oversampling (Sigma-delta) ADC can achieve over 20 bits resolution, but the sampling rate is lowest. Two-step flash ADC and pipeline ADC sit in the middle. However, pipeline ADC can get higher resolution but lower speech compared to two-step ADC.

So based on different application and requirement, ADC structure might not be the same. Flash ADC focus on radio, UWB, WiFi applications because of its high speed features. Two-step and pipeline ADC will be used for communication, video, image sensor, and baseband systems. While oversampling ADC will be used for audio, communication, thermal sensing and precision test systems.

| ADC             | Resolution | SNR/dB | Fs/Hz       | Power  | Applications                                 |

|-----------------|------------|--------|-------------|--------|----------------------------------------------|

| Flash           | 4~6        | 30~46  | >1G         | higher | Radio, UWB, WiFi,<br>high speed system       |

| Two-step        | 8~10       | 44~60  | 500M        | High   | Communication, video                         |

| Pipeline        | 8~16       | 48~80  | 1M~20<br>0M | low    | Communication, video,<br>baseband system     |

| Sigma-<br>Delta | 16~24      | 90~130 | 10M         | lower  | Audio, communications, precision test system |

Table 2.1 Comparison of Different Types of ADCs.

## **CHAPTER 3**

# **PIPELINE ADC BLOCK STUDY**

Pipeline ADC uses two or more steps of subranging. First, a coarse conversion is done. In a second step, the difference to the input signal is determined with a digital to analog converter (DAC). This difference is then converted finer, and the results are combined in a last step. This can be considered a refinement of the successiveapproximation ADC wherein the feedback reference signal consists of the interim conversion of a whole range of bits (for example, four bits) rather than just the next-mostsignificant bit. By combining the merits of the successive approximation and flash ADCs this type is fast, has a high resolution, and only requires a small die size.

#### **3.1 Basic Concept of Pipeline ADC**

The principle of sub-ranging ADC can be pushed to the limit of having only one bit per stage. At this point, each flash ADC is nothing more than a simple comparator; also, the data is transferred in a pipeline fashion: when the data is sent to the second stage, another sampled data is fed to the first stage; the result is a latency delay equal to the number of stages. Since the pipeline ADC is pipelining the subranging structure, and the binary search in the sub-ADCs runs just as the mathematic division, the first stage decides the MSBs and the last stage sets the LSBs. The MSBs divide the full reference range, while LSBs divide the sub reference range. The relationship between MSBs and LSBs is revealed in Figure 3.1.

Figure 3.1 Pipeline ADC Transfer Curve.

A Pipeline ADC consists of a cascade of stages, each of which contains a low resolution ADC, DAC and amplifier, which successively convert the analog input into its digital representation, while processing the data in a pipe-lined manner.

Pipeline ADCs are commonly used for power-efficient high-speed conversion of wide bandwidth input signals (e.g. 10 to 100 MHz). The ADC sampling frequency is usually the Nyquist frequency or lower using small OSRs (e.g. 2 or 4) and the ADC output code resolution is typically between 8 and 14-bit.

As a well-organized data processing system, the operation of the pipeline ADCs is under stringent timing control. Each stage performs data conversion in sampling and holding modes serially. The sampling and holding modes interleave between two adjacent stages and the digital output is valid after some clock cycles, called latency time, decided by the number of stages. This process is illustrated in Figure 3.2(a). Because each sample must propagate through the entire pipeline before all its associated bits are available for combining in the digital-error-correction logic, data latency is associated with pipelined ADCs. In the example in Figure 3.2(b), this latency is about seven cycles.

(b)

Figure 3.2 (a) Stage Operation Modes in Pipeline ADC (b) data latency in pipeline ADC.

This timing scheme of the pipeline ADC is built up by the sample and hold circuit in each stage. During sampling mode, the switch controlled by the sampling clock is connected to the residue generated from the preceding stage and the signal is sampled on the sampling capacitor. When the hold clock comes, the switch is turned off and the signal stored on the sampling capacitor on one hand is converted to the thermometer codes by the sub-flash ADC, on the other hand, subtracts the estimated analog signal that is re-constructed by the D/A converter, to create the new residue as the input signal of the following stage. The thermometer codes from each stage are encoded to the binary ones and latched and added together to form the final m-bit digital output (where m is the resolution of the pipeline ADC). The detailed pipeline architecture is shown in Figure 3.3.

Figure 3.3 Detailed Pipeline ADC Architecture.

Pipeline ADC design includes system level design and block level design. For system level consideration, it consists of architecture, stages partition, power optimization, specification of sub-block circuits. Designer should consider what kind of architecture the pipeline ADC should be: op-amp sharing, S/H circuits, dithering or not, how many bit one stage of MDAC should handle, how to minimize power and what the specification of sub-block should be, like op-amp DC gain and close-loop gain bandwidth.

So, it's a complex design trade-off matrix among resolution, thermal noise, power, input range, voltage supply, op-amp types, nonlinearity, and so on. It is shown on Figure 3.4. This work comes up with an optimized methodology of pipeline ADC design trade-off and finds all the connection among these important features. For example, as resolution increase, the requirement of thermal noise, which is related to KT/C, also become tight (SNR also increase). So as to minimize thermal noise, the sample capacitance in MDAC will increase; however, it will burn more power. If the input range goes up, the requirement of thermal noise will drop, but the selection of op-amp becomes to be one dominant issue.

Figure 3.4 Pipeline ADC Design Matrix.

So, the methodology study of pipeline ADC design flow shows as following figures 3.5.

- Before designing pipeline ADC, first thing to know all the specification of ADC, like resolution, input signal range, maximum sampling rate, voltage supply and so on.

- 2.) Then, decide what kind of ADC architecture will be used, number of stages, sampling capacitor value.

- 3.) Define the block level circuits specification based on the first two steps. Like op-amp types, DC gain, closed-loop gain bandwidth, switch selections and so on.

- 4.) Design and simulation the block level circuits to beat the specification.

- 5.) Design and simulation the top level ADC.

- 6.) Run post simulation and corner, Monte Carlo simulation.

- 7.) If everything passes, the layout could be tape-out.

All the block level design is important, so we first study the block level circuits and will discuss the system level power optimization in the following chapter.

Figure 3.5 Pipeline ADC Design Flow.

### 3.2 Comparator

A comparator is a device which compares two voltages or currents and switches its output to indicate which is larger. The most widely used ADCs process voltage signal, so here we only discuss voltage comparator. Its symbol is in figure 3.6 (a) and its ideal transform function is figure 3.6(b).

Figure 3.6 (a) Comparator Symbol (b) Ideal Transform Function

(c) Practical Transform function.

The important Specifications of voltage comparator are gain  $A_V$ , offset  $V_{OS}$ , speed (step response), kickback noise and power consumption. The gain of ideal comparator is infinite, however the practical comparator gain is:

$$A_V = \frac{V_{OH} - V_{OL}}{V_{IH} - V_{IH}} \tag{3.1}$$

$V_{OS}$  is the input voltage necessary to make the output equal to half of  $(V_{OH}+V_{OL})$ when  $V_P=V_N$ . Comparator speed, kickback noise and power issue will be discussed in details in the following sections. There are mainly two type of voltage comparator: amplifier-type comparator and Latch-type comparator which is also called regenerative comparator.

### 3.2.1 Amplifier-type comparator

The natural choice to design a comparator is to use an amplifier. A small voltage at the input is then amplified to a value large enough to be detected by the following digital logic circuits.

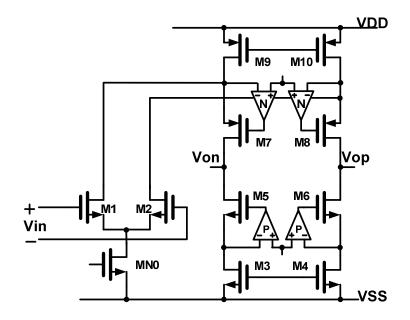

Figure 3.7 Amplifier-type Comparator.

For pipeline/flash ADC design, we seldom use amplifier-type comparator. The reasons are:

- 1. It will always consume static power which means it is costly. The power of comparator in Figure 3.7 is  $P=I_{M5} *V_{DD}+I_{M7}*V_{DD}$

- 2. The speed of amplifier-type comparator is slow, compared to latch-type comparator, there is no positive feedback in amplifier-type one, so the time response is slow. As a result it's difficult to achieve the performance needed for a 12 bit 50 MS/s AD converter [1].

#### **3.2.2 Latch-type comparator**

Figure 3.8 shows a typical latch-type comparator [9]. The most important feature of this type comparator is that the output of one amplifier is connected to the input of the other amplifier. These cross-couple connection makes a positive feedback in that loop, which results in faster time response compared with amplifier-type one.

Figure 3.8 (a) Typical Latch-type Comparator (b) Equivalent Small Signal Model.

The input differential voltage is applied to a source-coupled pair, which produces signal currents that are loaded by the resistance  $R_{SW}//R_{RGN}$ .  $R_{SW}$  is the drain-source resistance of  $M_5$  (drain-source resistances of  $M_1$ - $M_4$  are neglected).  $R_{RGN}$  is the resistance due to the regeneration of  $M_3$ - $M_4$  which has been shown to be equal to  $-2/g_{m3}$ .  $C_P$  represents parasitic capacitance on node  $V_{d3}$  and  $V_{d4}$ . The comparator works in two non-overlapped phases.

Phase one is reset mode: when the signal  $V_{SW}$  is high, the reset mode requires that the value of  $R_{SW}//R_{RGN}$  be positive, which will be the case if  $M_5$  is in triode and  $R_{SW} < 2/g_{m3}$ . In this mode, the stage behaves as a stable, low-gain differential amplifier with ( $v_{d4} - v_{d3}$ ) being the differential output voltage. Phase two is regeneration mode: When  $V_{SW}$  goes low,  $R_{SW}$  becomes very large and hence  $R_{SW}//R_{RGN}$  becomes negative. Under this condition, the stage is unstable and the magnitude of the output voltage will increase exponentially with time due to the negative time constants at the nodes  $v_{d3}$  and  $v_{d4}$ . Hence, this is called the regeneration mode. In operation, when the clock transitions from high to low any existing output voltage will regenerate until either  $v_{d3}$  or  $v_{d4}$  goes low and the other goes high.

Considering symmetry, the input current source  $i_{in}$  represents the drain current of  $M_1$ , the capacitor  $C_p$  represents the parasitic capacitance at  $v_{d3}$ , and the resistor R represents one-half of  $R_{SW}//R_{RGN}$ .

- Reset mode:

- $R = R1 = (R_{SW} / / R_{RGN}) / 2 > 0$

- Time constant

$$\tau_1 = C_P R_1 = \frac{R_{SW} \parallel R_{RGN}}{2} C_P > 0 \tag{3.2}$$

- Output voltage

$$\Delta V_0 = A \Delta V_{in} (1 - e^{-\frac{t}{\tau_1}})$$

(3.3)

- regeneration mode:

- $R = R_2 = R_{RGN}/2 = -1/g_{m3} < 0$

- Time constant

$$\tau_2 = C_P R_2 = -\frac{1}{g_{m3}} C_P < 0 \tag{3.4}$$

- Output voltage

$$\Delta V = \Delta V_0 e^{\omega_u t} = \Delta V_0 e^{\frac{t}{\tau_2}}$$

(3.5)

The final output voltage of these two phases is:

$$\Delta V_{finial} = \Delta V_0 e^{\frac{t}{\tau_2}} = A \Delta V_{in} (1 - e^{-\frac{t_1}{\tau_1}}) e^{\frac{t_2}{\tau_2}}$$

(3.6)

A smaller regeneration time constant  $\tau_2$  will create a full-scale output sooner. But it will reduce the sensitivity of the comparator to inputs after the start of regeneration. The reset time constant  $\tau_1$ : A longer reset time constant will increase the sensitivity of the comparator to inputs before the start of regeneration. There are mainly 3 types of latch-type comparator [10]: Static latched comparator, Class-AB latched comparator and Dynamic latched comparator. Before discuss these comparators, kickback noise is first introduced in figure 3.9: The large voltage variations on the regeneration nodes are coupled, through the parasitic capacitances of the transistors, to the input of the comparator. Since the circuit preceding it does not have zero output impedance, the input voltage is disturbed, which may degrade the accuracy of the converter. This disturbance is usually called kickback noise.

Figure 3.9 Kickback Noise.

#### 3.2.3 Static latched comparator

The regeneration is done by two cross-coupled inverters  $(M_{3a}/M_{4a} \text{ and } M_{3b}/M_{4b})$ . The power efficiency is poor, since the consumption is purely static. But it has low kickback noise because of slow regeneration process.

Figure 3.10 Static Latched Comparator.

# **3.2.4 Class-AB latched comparator**

Figure 3.11 Class-AB Latched Comparator.

The regeneration is done by two cross-coupled CMOS inverters. Their current increases momentarily, during the regeneration process, to charge the output nodes faster. The drains of the input differential pair are directly connected to the regeneration nodes. The circuit reacts quicker to input variations, because there is only one pole. However, this increases the kickback noise; it still has supply current in the reset phase and after the regeneration finishes.

#### 3.2.5 Dynamic latched comparator

Figure 3.12 Dynamic Latched Comparator.

In dynamic latched comparators [10], the current only flows during the regeneration. After regeneration is completed, one output node is at  $V_{DD}$ ; the other output and both drains of the differential pair have a 0-V potential. There is no supply current. This comparator has two kickback noise sources: voltage variations and the variation of the operating region of the differential pair transistors. In the reset mode: all the

transistors are cut-off (The gate, source and drain of  $M_{2a}$  and  $M_{2b}$  are all at  $V_{DD}$ ). In the regeneration mode: at the very beginning,  $M_{1a}$  and  $M_{1b}$  are in saturation;  $M_{2a}$  and  $M_{2b}$  are cut-off, so no current runs through  $V_{DD}$  to ground. The current discharges parasitic capacitors  $C_{P1}$  at the  $M_1$ 's drain. Until one of the transistor  $M_2$  is turn on. When one of  $M_2$  turns on, the voltage of its drain will decrease first, leading the opposite PMOS turns on. Then the regeneration begins to work.

Table 3.1 shows all the comparisons among those four types of comparators. And table 3.2 compares the time response of these comparators which indicate the speed performance.

| Performance    | Speed   | Positive | Power | Kickback | Area transistors |  |

|----------------|---------|----------|-------|----------|------------------|--|

|                |         | feedback |       | noise    |                  |  |

| Amplifier      | Slowest | None     | Most  | None     | 7                |  |

|                |         |          |       |          |                  |  |

| Static latch   | Slow    | Y        | More  | Less     | 11               |  |

| Class-AB latch | Faster  | Y        | Less  | More     | 9                |  |

| Dynamic latch  | Fastest | Y        | Least | Most     | 11               |  |

Table 3.1 Performance Comparisons.

| Time constant  | $	au_1$                                 | τ2                                  | Poles in pre-amp |

|----------------|-----------------------------------------|-------------------------------------|------------------|

| Staticlatch    | $\frac{1}{g_{m2}}C_{P1} + R_{SW}C_{P2}$ | $-\frac{1}{g_{m3}}C_p$              | 2                |

| Class-AB latch | $\frac{R_{SW}    R_{RGN2}}{2} C_{P}$    | $-(\frac{1}{g_{m2}+g_{m3}})C_p$     | 1                |

| Dynamic latch  |                                         | $-(\frac{1}{g_{m2}+g_{m3}})C_{p_2}$ | 1                |

Table 3.2 Time Constant Comparisons.

From these tables, dynamic latch comparator is the fastest one and consumes least power. It doesn't even need reset time because of no RC time constant in that phase, but it has the largest kickback noise. Amplifier-type comparator is the most costly since it has a static current run through  $V_{DD}$  to ground all the time, however, it doesn't has kickback noise for no positive feedback loop exists.

#### **3.2.6** Non-ideal problems in comparator

Offset and kickback noise interference are the mainly problems in comparators. In order to get offset as small as possible, one way is minimization; and anther is compensation or cancellation, that mechanism is much similar to offset compensation in OP-AMP, which will discussed in that section.

In order to minimize offset, pre-amplifier which is prior to comparator is introduced. The total offset is:

$$V_{os,in2} = V_{os,in,amp} + \frac{V_{os,in,latch}}{A}$$

(3.7)

The offset of latch is minimized by the factor of A (A is the gain of pre-amplifier). As we all the due to the well- symmetric topology of pre-amplifier, the pre-amplifier offset is rather smaller than latch one. We can also increase the area of pre-amplifier to get a less mismatching.

Isolation can minimize the voltage variations on the drains of the differential pair [10]. Those nodes are isolated from the regeneration nodes using switches, which open during the regeneration phase. An alternative path for the current of the differential pair must be provided, in order to keep the drain voltages near the values found in the reset phase. (Figure 3.13)

Figure 3.13 Minimizing Kickback Noise.

# 3.2.7 Specification abstraction

Offset requirement: the offset of comparator is required less than 1LSB in order to achieve no missing code.  $V_{os} < V_{ref}/2^N$

Speed requirement:

1. Preamplifier:

Any signal which is larger than 1LSB, should be amplified during reset mode.

(a) For small differential input signal, which is a little bit larger than 1LSB: if the pre-amplifier has only one pole:

$$t_{setting} = \tau_1 \ln \frac{1}{1 - \frac{\Delta V_0}{A}} < \frac{1}{2f_{sample}}$$

(3.8)

(b) For large differential input signal,

$$t_{setting} = \frac{\Delta V}{SR} = \frac{\Delta V \times C_P}{I} < \frac{1}{2f_{sample}}$$

(3.9)

Sampling rate:

$$f_{sample} < \min\left\{\frac{I}{2\Delta V \times C_P}, \frac{1}{2\tau_1 \ln \frac{1}{1 - \frac{\Delta V_0}{A}}}\right\}$$

(3.10)

2. Latch

$$\begin{split} \Delta V &= \Delta V_0 e^{\omega_u t} = \Delta V_0 e^{\frac{t}{\tau_2}} > V_{OH} - V_{OL} \Longrightarrow t_{setting} > \tau_2 \ln\left(\frac{V_{OH} - V_{OL}}{\Delta V_0}\right) \\ &=> f_{sample} < \frac{1}{2t_{setting}} = \frac{1}{2\tau_2 \ln\left(\frac{V_{OH} - V_{OL}}{\Delta V_0}\right)} \end{split}$$

(3.11)

As a result, the final specifications of comparator are:

$$f_{sample} < \min\left\{\frac{I}{2\Delta V \times C_{P}}, \frac{1}{2\tau_{1}\ln\frac{1}{1-\frac{\Delta V_{0}}{A}}}, \frac{1}{2\tau_{2}\ln\left(\frac{V_{OH}-V_{OL}}{\Delta V_{0}}\right)}\right\}$$

(3.12)

$$\Delta V_{0} > V_{os,latch}$$

# 3.3 Operational amplifier

An operational amplifier, which is often called an op-amp, is a DC-coupled highgain electronic voltage amplifier with differential inputs and single or differential outputs. It is widely used as key block in SHA, MDAC and bandgap voltage reference of pipeline ADC. The notation of ideal op-amp is figure 3.14.

Figure 3.14 (a) OP-AMP Notation, Ideal op-amp.

V+ is non-inverting input, V- is inverting input, Vout is op-amp output,  $V_{S+}$  is positive power supply and  $V_{S-}$  is negative power supply. For open loop op-amp  $V_{out}=(V_+$ - V\_)\*A<sub>open-loop</sub>. A<sub>open-loop</sub> is the open-loop voltage gain of op-amp. The magnitude of the open-loop gain is typically very large, so open-loop operation results in op-amp saturation unless the differential input voltage is extremely small. Op-amps are usually applied to negative-feedback configurations system.

Since practical boundary conditions limit the op-amp performance, such as process specification (Vth, Cox, mobility, etc.), supply voltage and range, operating temperature and range and so on. So op-amp specifications are crucial constraints for the system. These features should be paid attention to:

- a. Open loop gain

- b. 3-dB bandwidth (dominant pole, Gain bandwidth product)

- c. Settling time

- d. Offset

- e. Slew rate

- f. Input common mode range (ICMR)

- g. Output-voltage swing

- h. Common-mode rejection ratio (CMRR)

- i. Power supply rejection ratio (PSRR)

- j. Output impedance

- k. Noise (Dynamic range=Input swing/Noise)

- 1. Power consumption

The following section will discussed these configurations with different op-amp architectures.

## 3.3.1 Differential Op-amp architecture

This section only discusses four most popular and fundamental op-amp architectures.

- a. Two-stage Op-amp

- b. Telescopic Op-amp

- c. Folded-cascode Op-amp

- d. Gain-boosting Op-amp

# 3.3.2 Two-stage Op-amp

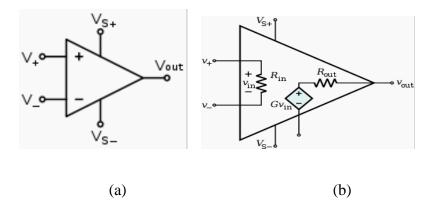

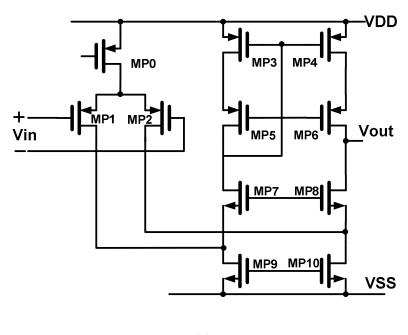

Figure 3.15 Two-stage Op-amps.

This is the simplest op-amp and it only consists of 8 transistors. The gain of the first stage is often larger than the gain of second stage. Because the higher gain the first stage has, the lower input referred noise and offset the op-amp it is. And in order to achieve high output swing, the second stage gain should be smaller. All the specifications of two-stage op-amp are in table 3.3.

| DC Gain       | $G = g_{m1}(r_{o2}    r_{o4}) \cdot g_{m6}(r_{o6}    r_{o7})$                                                                                  |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| Dominant pole | $\omega_{-3dB} = p_1 = \frac{-1}{G_{II}C_C(r_{o2} \parallel r_{o4})} = \frac{-1}{g_{m6}(r_{o6} \parallel r_{o7})C_C(r_{o2} \parallel r_{o4})}$ |

| Unity gain    | $GB = G \cdot \omega_{-3dB} = \frac{g_{m1}}{C_{c}}$                                                                                            |

| bandwidth     | $C_c$                                                                                                                                          |

| Non-dominant  | $p_2 = \frac{-g_{m6}}{C_{II}} = \frac{-g_{m6}}{C_{gs6} + C_{gs7} + C_{db6} + C_{db7} + C_L},$                                                  |

| poles         |                                                                                                                                                |

|               | $p_3 = \frac{-g_{m3}}{C_{gs3} + C_{gs4} + C_{gd3} + C_{gd1} + C_{b3}}$                                                                         |

| Slew rate               | $SR = \frac{I_{M5}}{C_L}$                                                                                                             |

|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| ICMR                    | $V_{DS5(sat)} + V_{GS1} \le V_{IC} \le V_{DD} - V_{SG3} + V_{th1}$                                                                    |

| Output swing            | $V_{out,pp} = V_{DD} - \left  V_{OD6} \right  - V_{OD7}$                                                                              |

| Power dissipation       | $P_{diss} = V_{DD}(I_{D5} + I_{D7}) = \frac{1}{2}V_{DD}(g_{m5}V_{OD5} + g_{m7}V_{OD7})$                                               |

| Input referred<br>noise | $\overline{V_n}^2 \approx 4kT \left( 2\frac{2}{3g_{m1,2}} + 2\frac{2g_{m3,4}}{3g_{gm1,2}^2} \right) + 2\frac{K_N}{(WL)_{1,2}C_{ox}f}$ |

|                         | $+2\frac{K_{P}}{(WL)_{3,4}C_{ox}f}\frac{g_{m3,4}^{2}}{g_{gm1,2}^{2}}$                                                                 |

\*  $V_{OD}$  is transistor overdrive voltage.  $V_{OD} = V_{GS} - V_{th}$

| Table 3.3 The | Specifications | of Two-stage | Op-amp. |

|---------------|----------------|--------------|---------|

|               |                |              |         |

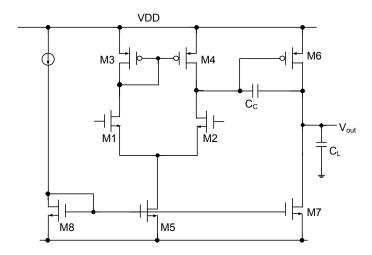

# 3.3.3 Telescopic Op-amp

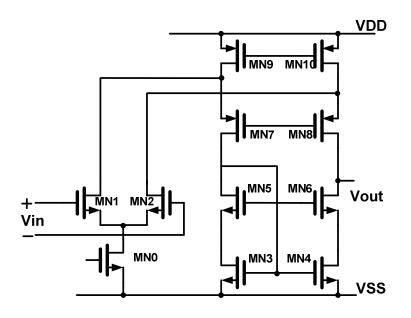

Figure 3.16 Telescopic Op-amp.

Telescopic op-amp only has one stage compared with two-stage op-amp. And its gain is as large as two-stage one. However, its output swing is  $2*V_{OD}$  less than that of two-stage one. All the specifications of two-stage op-amp are in table 3.4.

| DC Coin              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

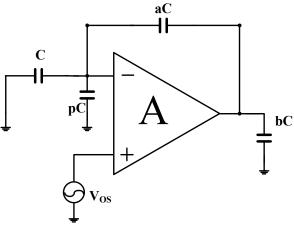

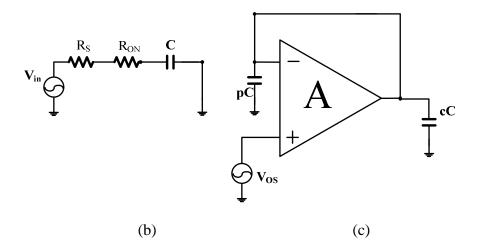

| DC Gain              | $G = g_{m1}[(g_{m3}r_{o3}r_{o1})    (g_{m5}r_{o5}r_{o7})]$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |