## **UC Berkeley**

### **UC Berkeley Electronic Theses and Dissertations**

#### **Title**

Compact Models for Future Generation CMOS

#### **Permalink**

https://escholarship.org/uc/item/7qn9x2jd

#### **Author**

Lu, Darsen Duane

#### **Publication Date**

2011

Peer reviewed|Thesis/dissertation

#### Compact Models for Future Generation CMOS

By

Darsen Duane Lu

A dissertation submitted in partial satisfaction of the requirements for the degree of Doctor of Philosophy

in

Engineering — Electrical Engineering and Computer Sciences

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Professor Chenming Hu, Chair Professor Ali M. Niknejad Professor Sourav Chatterjee

Spring 2011

#### Compact Models for Future Generation CMOS

Copyright 2011 by Darsen Duane Lu

#### Abstract

Compact Models for Future Generation CMOS

by

Darsen Duane Lu

Doctor of Philosophy in Engineering — Electrical Engineering and Computer Sciences

University of California, Berkeley

Professor Chenming Hu, Chair

Multiple-gate MOSFETs with superior short channel control are expected to replace planar CMOS in the near future. An accurate and computationally efficient compact transistor model is necessary to simulate circuits in multiple-gate MOSFET technologies. In this dissertation research, a compact multiple-gate MOSFET model, BSIM-MG is developed. BSIM-MG includes independent multi-gate compact model BSIM-IMG and common multi-gate compact model BSIM-CMG. We focus on BSIM-IMG for multiple-gate MOSFETs with independent front- and back-gates. The basic formulations for surface potential, drain current and charge are derived and verified against TCAD simulations with excellent agreements. The model preserves important property of multi-gate MOSFETs such as volume inversion. Non-ideal effects including short channel effects, length dependent back-gate coupling, transport models, leakage currents, parasitic resistances and capacitances, temperature effects and self heating are considered in the model. The model expressions are carefully formulated so that the symmetry of the source and drain is preserved. Rules for maintaining symmetry are discussed in this dissertation.

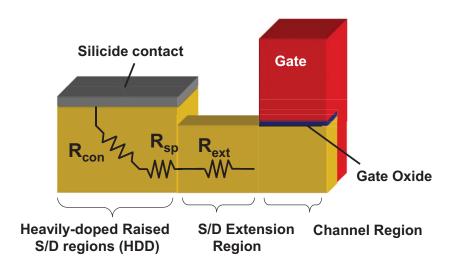

For the common multi-gate transistor model BSIM-CMG, the basic expressions have been improved so that it is compatible with a novel non quasi-static effects modeling technique — charge segmentation. In addition, a parasitic source/drain resistance model is developed, including three components: the contact resistance, the spreading resistance, and the bias-dependent extension resistance. Both BSIM-CMG and BSIM-IMG models are verified against TCAD and measured data.

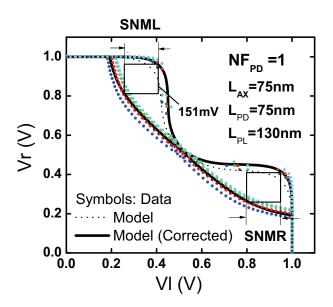

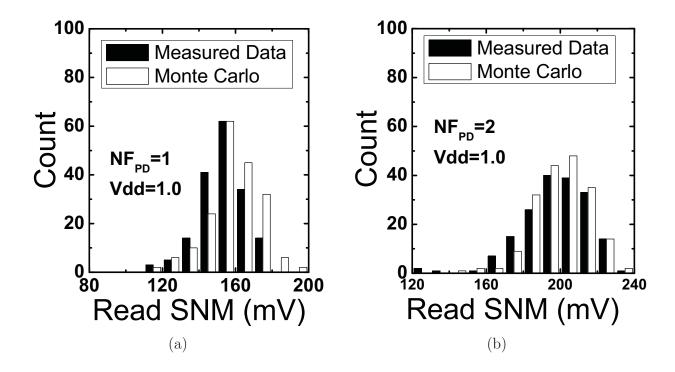

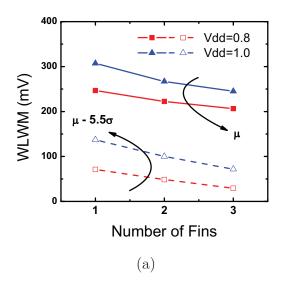

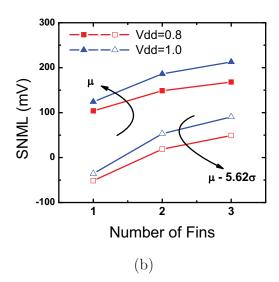

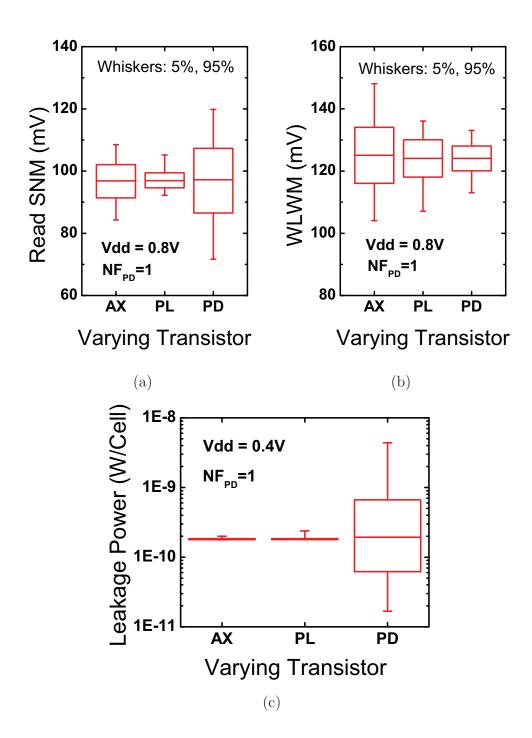

The use of the FinFET compact model to model manufacturing variation in a FinFET technology is further explored. The model matches measured data well for both the nominal case and the statistical distribution for NMOS threshold voltage as well as the read static noise margin. A non-Gaussian threshold voltage distribution is observed for nFET devices, and the compact model successfully captures the distribution. We further outlined and demonstrated a Monte-Carlo based procedure for designing FinFET SRAM cells using the extracted variation information.

Technology scaling has enabled numerous CMOS analog circuits for low cost radio-frequency applications. The modeling of MOSFET thermal noise becomes very important. In the final part of this dissertation research, a new thermal noise model is developed for the industry standard BSIM4 model that enhances the existing thermal noise formulation in BSIM4. The model is verified against a segmented channel MOSFET model as well as measured data. It is implemented in Berkeley SPICE3 and is ready for industry use. A method to port the model to BSIM-MG for thermal noise modeling in multi-gate MOSFETs is also presented.

Dedicated to my family

## Contents

| $\mathbf{C}$ | Contents  Acknowledgements |                                                                          |    |

|--------------|----------------------------|--------------------------------------------------------------------------|----|

| A            |                            |                                                                          |    |

| 1            | Inti                       | roduction                                                                | 1  |

|              | 1.1                        | CMOS Scaling and its Challenges                                          | 1  |

|              | 1.2                        | Multi-gate MOSFET — the Future CMOS Transistor Structure                 | 2  |

|              |                            | 1.2.1 Advantages of Multi-gate MOSFETs                                   | 2  |

|              |                            | 1.2.2 Various Flavors of Multi-gate MOSFET                               | 2  |

|              | 1.3                        | Multi-gate CMOS Modeling                                                 | 3  |

|              |                            | 1.3.1 BSIM-MG: A BSIM-family Model for Multi-gate MOSFET                 | 3  |

|              |                            | 1.3.2 BSIM-IMG and BSIM-CMG                                              | 5  |

|              | 1.4                        | Modeling Parasitic Resistances and Capacitances in the FinFET Multi-Gate |    |

|              |                            | Device                                                                   | 5  |

|              | 1.5                        | Variation in FinFET SRAM Cells                                           | 6  |

|              | 1.6                        | Thermal Noise Modeling for Planar and Multi-gate Transistors             | 7  |

|              | 1.7                        | Dissertation Goals and Outline                                           | 7  |

| <b>2</b>     | Bas                        | sic Formulations of Multiple-Gate MOSFET Compact Models                  | 9  |

|              | 2.1                        | Core Models of BSIM-CMG and BSIM-IMG                                     | 9  |

|              | 2.2                        | Modeling Double-gate Fully-depleted SOI MOSFETs with BSIM-IMG            | 10 |

|              | 2.3                        | Core Model of BSIM-IMG                                                   | 11 |

|              |                            | 2.3.1 Modeling Framework                                                 | 11 |

|              |                            | 2.3.2 Explicit Approximation for Surface Potential                       | 11 |

|              |                            | 2.3.3 Drain Current Model                                                | 15 |

|              |                            | 2.3.4 Capacitance Model                                                  | 23 |

|              | 2.4                        | Core Model of BSIM-CMG                                                   | 24 |

|              |                            | 2.4.1 Background                                                         | 24 |

|              |                            | 2.4.2 Simple Non Charge Sheet I-V Model                                  | 26 |

|              | 2.5                        | Real Device Effects and Source Drain Symmetry                            | 28 |

|              | 2.6                        | Model Convergence                                                        | 30 |

|   | 2.7 | - • • • • • • • • • • • • • • • • • • •                                  | 33 |

|---|-----|--------------------------------------------------------------------------|----|

|   |     |                                                                          | 33 |

|   |     | 2.7.2 Computational Efficiency of Surface Potential Calculation in BSIM- |    |

|   |     |                                                                          | 35 |

|   |     | I v                                                                      | 35 |

|   | 2.8 | <u> </u>                                                                 | 37 |

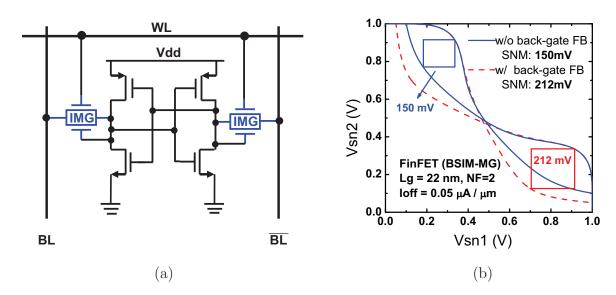

|   |     | 2.8.1 FinFET SRAM with Back-gate Dynamic Feedback                        | 37 |

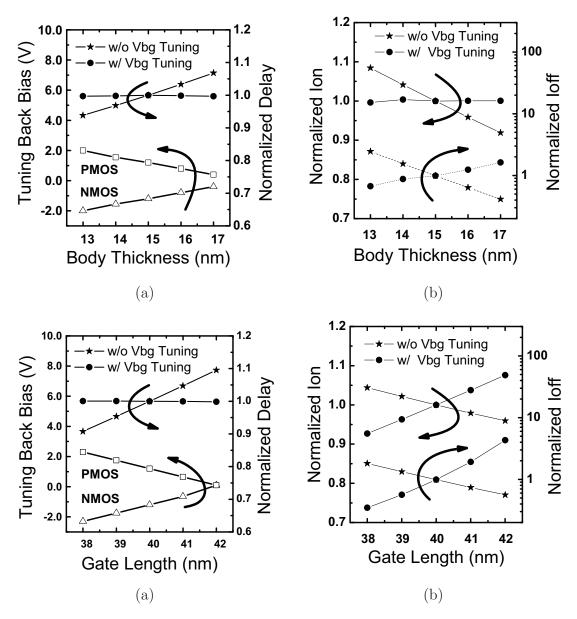

|   |     | 2.8.2 Dynamic Threshold Voltage Tuning to Combat Variation in Back-      |    |

|   |     | gated FDSOI                                                              | 38 |

|   | 2.9 | Summary                                                                  | 38 |

| 3 | Svn | nmetry in MOSFET Compact Models                                          | 41 |

|   | 3.1 |                                                                          | 41 |

|   | 3.2 |                                                                          | 42 |

|   |     |                                                                          | 42 |

|   |     |                                                                          | 43 |

|   |     |                                                                          | 43 |

|   | 3.3 |                                                                          | 44 |

|   | 3.4 | 1 0                                                                      | 48 |

|   | 3.5 | ,                                                                        | 49 |

|   | 3.6 |                                                                          | 49 |

| 4 | Mo  | deling of FinFET Parasitic Source and Drain Resistances                  | 52 |

| • | 4.1 | 0                                                                        | 53 |

|   | 4.2 | · ·                                                                      | 57 |

|   |     | C I                                                                      | 57 |

|   |     |                                                                          | 60 |

|   |     |                                                                          | 62 |

|   | 4.3 |                                                                          | 65 |

|   |     |                                                                          | 66 |

|   |     |                                                                          | 66 |

|   |     |                                                                          | 69 |

|   | 4.4 | Discussion                                                               | 73 |

|   | 4.5 | Conclusion                                                               | 76 |

| 5 | Cor | npact Modeling of Variation in FinFET SRAM Cells                         | 77 |

| • | 5.1 |                                                                          | 77 |

|   | 5.2 |                                                                          | 78 |

|   | 5.3 |                                                                          | 81 |

|   | 5.4 |                                                                          | 81 |

|   | 5.5 | 0                                                                        | 82 |

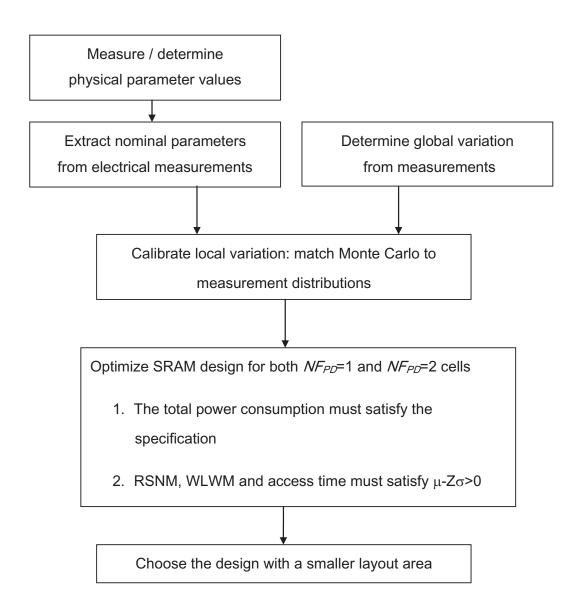

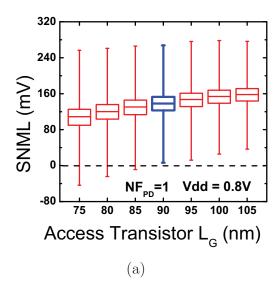

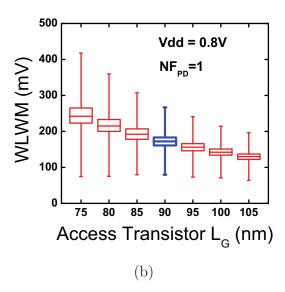

|   | 5.6  | Statistical Design Procedure for FinFET SRAMs                             | 83  |

|---|------|---------------------------------------------------------------------------|-----|

|   | 5.7  | Experimental Verification                                                 | 85  |

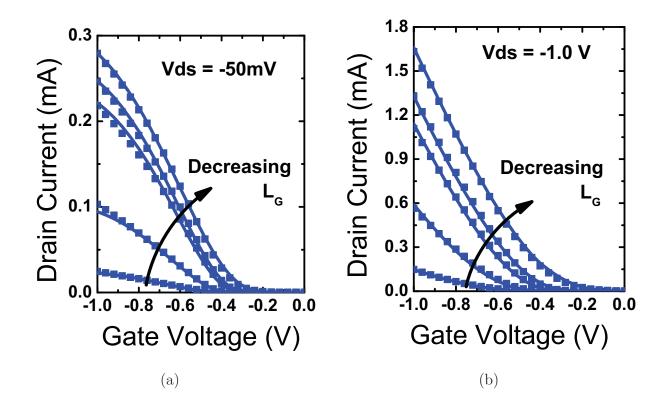

|   |      | 5.7.1 Device Fabrication                                                  | 85  |

|   |      | 5.7.2 Nominal Parameter Extraction                                        | 85  |

|   |      | 5.7.3 Adjustment for SRAM FETs                                            | 85  |

|   |      | 5.7.4 Calibration of Variation                                            | 85  |

|   | 5.8  | FinFET SRAM Cell Design Exercise                                          | 89  |

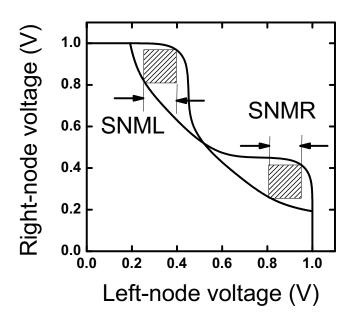

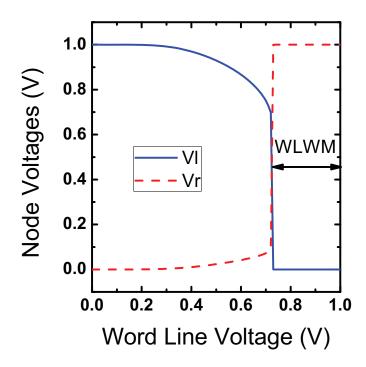

|   | 0.0  | 5.8.1 Design Criterion for Read and Write Operations                      | 89  |

|   |      | 5.8.2 Cell Optimization                                                   | 89  |

|   | 5.9  | Sensitivity Analysis                                                      | 91  |

|   | 5.10 | Improved Variation Calibration Method                                     | 91  |

|   |      | Conclusion                                                                | 94  |

|   | 0.11 | Conclusion                                                                | 0 1 |

| 6 | The  | rmal Noise Modeling for BSIM4 and BSIM-MG                                 | 95  |

|   | 6.1  | Review: BSIM4 Thermal noise model                                         | 96  |

|   |      | 6.1.1 Charge-Based Thermal Noise Model                                    | 96  |

|   |      | 6.1.2 Holistic Thermal Noise Model                                        | 97  |

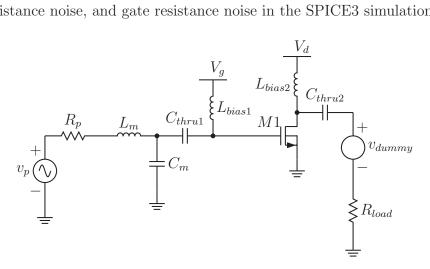

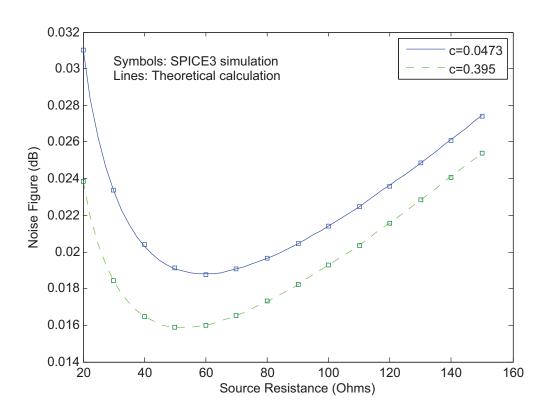

|   |      | 6.1.3 Verification with Circuit Simulation                                | 101 |

|   | 6.2  | Derivation of New Thermal Noise Model                                     | 101 |

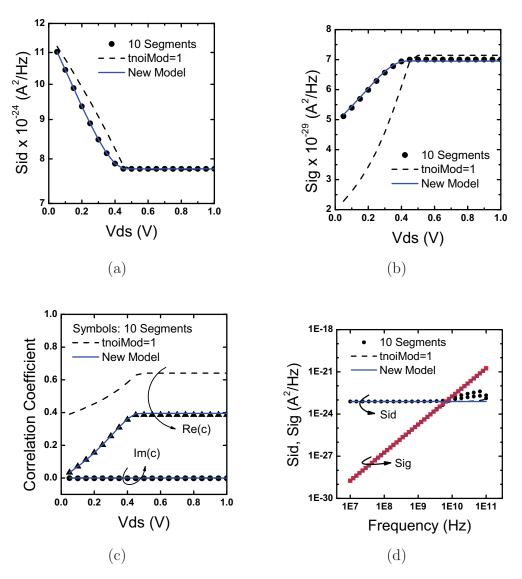

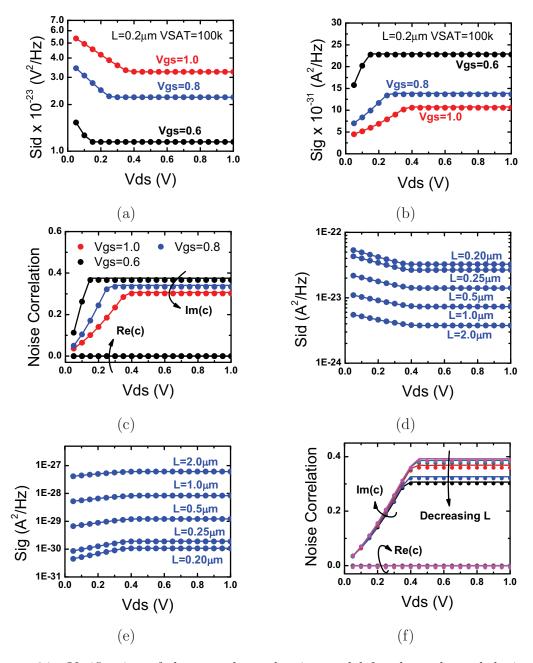

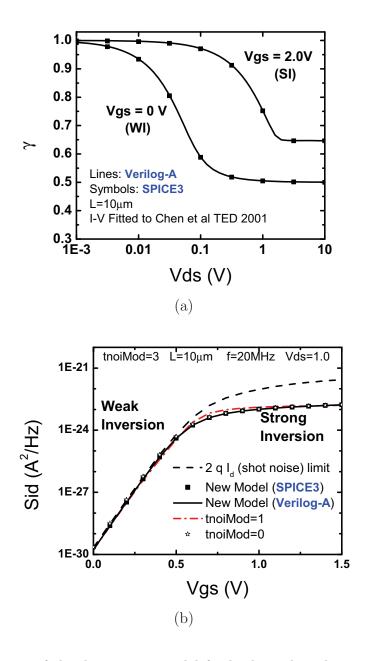

|   |      | 6.2.1 Drain Noise                                                         | 103 |

|   |      | 6.2.2 Induced Gate Noise                                                  | 105 |

|   |      | 6.2.3 Correlation                                                         | 106 |

|   |      | 6.2.4 Verification                                                        | 107 |

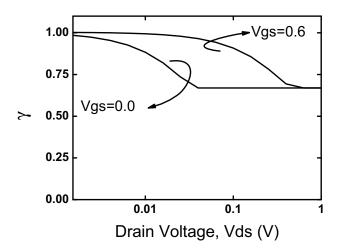

|   | 6.3  | Thermal Noise in the Weak Inversion Region                                | 109 |

|   |      | 6.3.1 Derivation of Thermal Noise Expressions Valid in All Regions of Op- |     |

|   |      | eration                                                                   | 112 |

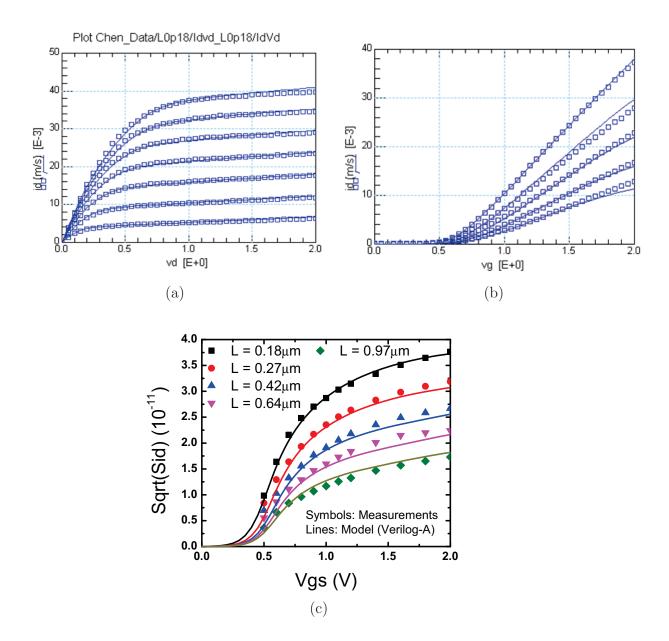

|   |      | 6.3.2 Verifications                                                       | 115 |

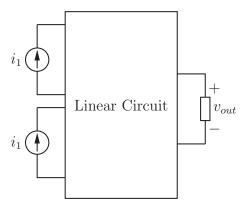

|   | 6.4  | Implementing Correlated Noise Sources in SPICE3                           | 118 |

|   |      | 6.4.1 Implementation                                                      | 118 |

|   |      | 6.4.2 Verification                                                        | 119 |

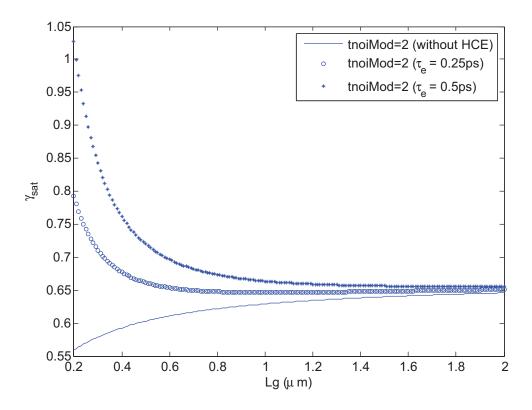

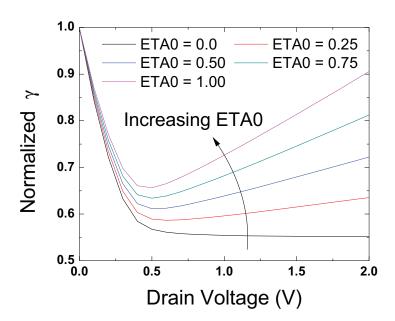

|   | 6.5  | Modeling Excess Noise for Short Channel Devices                           | 121 |

|   | 6.6  | Thermal Noise Modeling for BSIM-MG                                        | 125 |

|   | 6.7  | Conclusion and Future Work                                                | 125 |

| 7 | Con  | clusions                                                                  | 127 |

|   | 7.1  | Summary and Future Research Directions                                    | 127 |

|   |      | 7.1.1 Independent Multi-gate MOSFET Model BSIM-IMG                        | 127 |

|   |      | 7.1.2 Common Multi-gate MOSFET Model BSIM-CMG                             | 128 |

|   |      | 7.1.3 Symmetry of MOSFET Compact Models                                   | 128 |

|   |      | 7.1.4 Modeling Source and Drain Resistances for the FinFET                | 129 |

|   |      | 7.1.5 Compact Modeling of Variation in FinFETs                            | 129 |

|              | 7.2                  | 7.1.6 Thermal Noise Modeling                                         |     |

|--------------|----------------------|----------------------------------------------------------------------|-----|

| Bi           | bliog                | graphy                                                               | 131 |

| A            | Bacl                 | k Surface Potential and Inversion Charge Calculation in BSIM-IMG     | 142 |

| В            | Mor                  | nte Carlo Based Framework for FinFET SRAM Variation Simulation       | 146 |

| $\mathbf{C}$ | Sim                  | ple Segmentable BSIM                                                 | 148 |

| D            | $\operatorname{Cod}$ | le Listing: Evaluating Output Noise Contribution of Correlated Noise | :   |

|              | Sour                 | rces                                                                 | 154 |

#### Acknowledgments

First of all, I would like to express my sincere gratitude to my research advisor, Professor Chenming Hu. Without his guidance this work would not have been possible. During the brainstorming sessions in our weekly meetings, he has helped me developed a clear technical understanding of device physics, CAD, and technology. His everlasting enthusiasm about research has motivated me and my fellow graduate students to move forward even in the face of great challenges. I admire his vision — the ability to anticipate the use of multi-gate CMOS technology more than ten years before it is in production. He has taught us the importance of thinking about the future. In addition, I would also like to thank him for his immense guidance when I served as a teaching assistant of the course *Integrated Circuit Devices*. He is also a kind supervisor, who would almost always accommodate to my personal needs.

I am also highly indebted to Professor Ali M. Niknejad for being my co-advisor over the past six years. His insightful comments and questions during our technical discussion has had benefited me in almost all aspects of my dissertation research. As a student in the area of physical electronics, I was lucky to be able to also have some understanding about RF CMOS circuit design and modeling through research and coursework interaction with him.

I would also like to thank Professor Sourav Chatterjee in the statistics department for serving on my qualifying exam and dissertation committees, as well as Professor Ming Wu for serving as chair of my qualifying exam committee. Thanks to Professor Andrew Neureuther, Professor Borivoje Nikolić, Professor Costas Spanos, Professor Tsu-Jae King Liu and Professor William Kahan for the fruitful discussions with them regarding my research.

I am also grateful to Professor Ali Niknejad, Professor Chenming Hu, Professor Vivek Subramanian at UC Berkeley, Professor Jing-Jia Liou at National Tsing Hua University in Taiwan, and Dr. Phil Oldiges at IBM for writing recommendations letters for me in numerous occasions during my Ph.D study.

Additionally, it has been a great privilege for me to have frequent interaction with the industry, which has allowed me to better understand the practical aspects of CMOS technology and modeling. I would like to thank Anda Mocuta, Bruce Doris, Chung-Hsun Lin, David Frank, Isaac Lauer, Jeff Sleight, Leland Chang, Liyang Song, Masafumi Hamaguchi, Melanie Sherony, Paul Solomon, Phil Oldiges, Steve Laux, Tak Ning, Wilfried Haensch at IBM for the two internship arrangements and the feedbacks they have given me on my research. I would like to thank Bich-Yen Nguyen (SOITEC), Claude Cirba (TI), James Ma (Proplus), Joddy Wang (Synopsys), Jung-Suk Goo (Globalfoundries), Jushan Xie (Cadence), Ke-wei Su (TSMC), Keith Green (TI), Krishnanshu Dandu (TI), Lawrence Wagner (IBM), Peter Lee (Elpida Memories), Richard Williams (IBM), Wade Xiong (Sematech), and many others for working with me on compact model development. I would also like to thank Kwok Ng at Semiconductor Research Corporation for arranging review meetings and coordinating funding activities, as well as Changrui Yin for coordinating biannual research reviews for the IMPACT project.

As a member of the Berkeley Device Group, I am also privileged to be able to work with talented and hard-working fellow graduate students, postdocs, and industrial fellows. I would like to thank Mohan Dunga and Chung-Hsun Lin for guiding me to start my dissertation research. I would like to thank Alvaro Padilla, Andrew Carlson, Anupama Bowonder, Jack Yuang, Jane Xi, Jodie Zhang, Koichi Fukuda, Maryam Tabesh, Morgan Yang, Nuo Xu, Pankaj Kalra, Reinaldo Vega, Rumi Karim, Shijing Yao, Sriram Balasubramanian, Sriramkumar Venugopalan, Tanvir Hasan Morshed, Wei-Hung Chen, Xin Sun, Yogesh Singh Chauhan, Yu-Chih Tseng, Yuri Masuoka, Zhiming Deng for invaluable discussions on a wide variety of research topics and the training of tool usage, and undergraduate students Vivian Lin and Walter Li for participating and helping out on the BSIM project. I would also like to thank Alejandro de la Fuente Vornbrock, Angada Sachid, Blake Lin, Byron Ho, Changhwan Shin, Cheul Chi Lo, Chun Win Yang, David Carlton, Dan Good, Daniel Soltman, Donovan Lee, Hei Kam, Hiu Yung Wong, Jemin Park, Jaeseok Jeon, Joanna Lai, Kinyip Phoa, Kun Qian, Louis Hutin, Lynn Wang, Min Hee Cho, Nattapol Damrongplasit, Noel Arellano, Peter Matheu, Philip Chen, Pratik Patel, Rhesa Nathanael, Shong Yin, Steve Volkman, Sung Hwan Kim, Taro Osabe, Teymur Bakhishev, Tim Chen, Vidya Varadarajan, Vincent Pott, Wesley Chang, Zachary Jacobson for their friendship and company. I enjoyed lively discussions/debates with them on various topics, as well as once-in-a-while soccer games and lunch picnics over the years. They have made my time at UC Berkeley truly enjoyable. Thanks to Kanghoon Jeon for being my fellow TA in the integrated circuit devices course, and Reinaldo Vega, Justin Valley, Li-Wen Hung for organizing and participating in the EEGSA outreach program at Berkeley High School with me.

I am thankful for the assistance from administrative staff in the EECS Department. Thanks to Charlotte Jones, Dana Jantz, Elise Mills, Patrick Hernan for their warmhearted support. Special thanks to Ruth Gjerde for her timely information regarding department policy.

While most of my family members are in Taiwan during my study at Berkeley, I am very fortunate to have relatives and friends in the U.S. to help me and provide company. I would like to thank Mr. J. C. Sheu for inviting me to their family activities. I would like to thank uncle Bor-Shyue and aunt Louise, Mr. and Mrs. Hung, Karen and John, Chris and Chia-mei for their caring, advices, and numerous Thanksgiving and Christmas gatherings. I want to also thank my friends from the Berkeley International House and Berkeley Association of Taiwanese Students for their timely help and the fun social activities they have organized.

Most importantly, I would like to thank my family for their lasting love, support and encouragement, without whom none of this would have been possible. Last but most certainly not the least, I want to thank my lovely girlfriend Ruoning Wu for her company, support, and patience. She has truely enriched my life.

## Chapter 1

## Introduction

#### 1.1 CMOS Scaling and its Challenges

Over the past several decades, the size reduction of CMOS circuits has fueled the growth of the microelectronics industry. The manufacturing cost of integrated circuits has decreased exponentially, making countless new applications available to the general public. In the past CMOS technology advances relied on the improving manufacturing capabilities. The minimum manufacturable line width has decreased year by year. Surprisingly, the basic structure of the MOSFET has not changed much.

Simple scaling has become more and more challenging due to fundamental device-physics reasons [1]. At the device gate length (L) less than 100nm, further reduction in L has yielded limited improvements in performance due to velocity saturation [2] and source velocity limit [3]. For this reason, the strained silicon technology has been put into production [4]. The scaling of gate dielectric also poses a challenge. As the physical thickness of the SiO<sub>2</sub> gate dielectric  $(T_{ox})$  is scaled beyond 1.2nm, quantum mechanical tunneling current from the gate into the channel becomes significant [5]. Further reduction in  $T_{ox}$  will result in large static leakage current and large power consumption even when the device is turned off. Therefore at around the 45nm node, high-K gate dielectric is used to scale down the effective oxide thickness (EOT) without increasing the gate tunneling current. Metal gate electrodes are also used to eliminate the unwanted poly-silicon gate depletion effect [6]. Even with these advances, there is little room left for EOT scaling. This means the gate control of the channel can not be made much stronger, therefore channel length can not be made much shorter lest the drain exerts a proportionately large control leading to excessive short-channel effects and high off-state transistor leakage. A new approach is needed to allow future reduction of channel length. The multi-gate structure is a promising approach [7].

## 1.2 Multi-gate MOSFET — the Future CMOS Transistor Structure

#### 1.2.1 Advantages of Multi-gate MOSFETs

The main advantage of the multi-gate devices is the improved short channel effects. Since the channel (body) is controlled electrostatically by the gate from multiple sides, the channel is better-controlled by the gate than in the conventional transistor structure. Unwanted leakage components are reduced and a small transistor can be used to continue the cost reduction through miniaturization. Improved gate control also provide lower output conductance, i.e., smaller  $\frac{dI_{ds}}{dV_{ds}}$  in the current saturation region. This provides greater voltage gain, which is beneficial to analog circuits as well as to the noise tolerance of digital circuits.

A second advantage of the multi-gate devices is the improved on-state drive current  $(I_{on})$  and therefore faster circuit speed.  $I_{on}$  improvement arises from several reasons [8]. Reduction of channel doping reduces impurity coulombic scattering. Reduced channel doping reduces the electric field normal to the  $SiO_2$  interface and therefore reduces the surface roughness scattering. Finally, a promising multi-gate structure, FinFET, provides a larger channel width with a small footprint area. This raises  $I_{on}$ , which is handy for driving a large capacitive load such as long interconnect.

A third advantage is the reduced manufacturing variation. In the absence of channel dopants, the effect of random dopant fluctuation (RDF) is minimized. Lower SRAM supply voltage for the FinFET multi-gate technology compared to traditional bulk MOSFET technology has been experimentally demonstrated [9].

The advantages of multi-gate devices is well known and demonstrated in many FinFET technologies [10, 11, 12, 13].

#### 1.2.2 Various Flavors of Multi-gate MOSFET

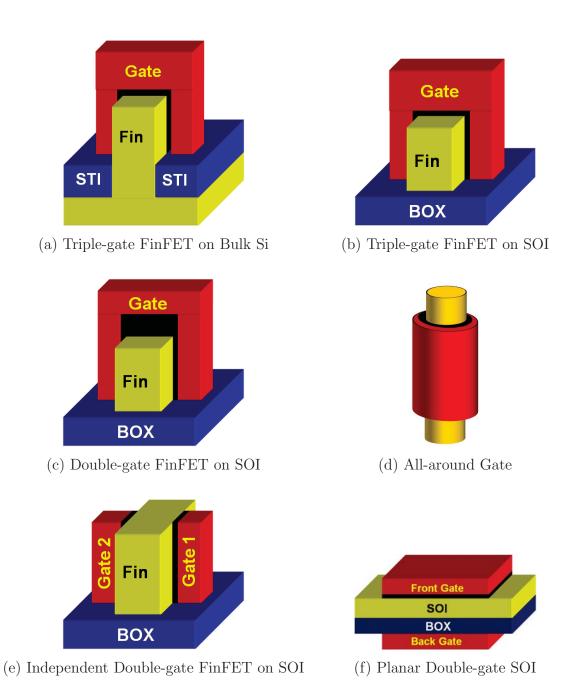

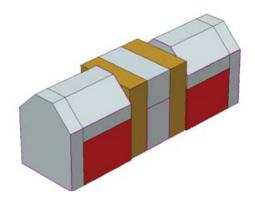

There are different flavors of multi-gate MOSFETs. Several examples are shown in Fig. 1.1. Perhaps the best known example is the FinFET [14]. The FinFET consists of a thin silicon body (the fin) and a gate wrapping around its top and two sides. The ITRS [15] considers it the candidate to replace planar MOSFETs for the aforementioned benefits of multi-gate transistor and because a FinFET is relatively easy to fabricate. FinFETs can be made on either bulk or SOI substrates, creating the bulk FinFET (Fig. 1.1(a)) or the SOI FinFETs (Fig. 1.1(b)). In some FinFET processes the oxide hard mask on top of the fin is not removed, creating the double-gate FinFET (Fig. 1.1(c)). In double-gate FinFETs the top surface of the fin does not conduct current, whereas in triple-gate FinFETs (Figs. 1.1(a)(b)) the side surfaces and the top surface all conduct current.

Another example of multi-gate MOSFET is the all-around gate device (Fig. 1.1(d)). It consists of a pillar-like body surrounded by the gate dielectric and the gate. The nanowire

MOSFET [16] is one example of all-around gate devices. Depending on the fabrication process, the channel may be either vertically [17] or horizontally [16] oriented.

Optionally, a FinFET can have two separated gates that are independently biased. This can be achieved by removing the top portion of the gate of a regular FinFET using chemical mechanical polishing, forming the independent double-gate FinFET (Fig. 1.1(e)) [18].

Independent double-gate MOSFETs may also be made as a planar device [19]. The planar double-gate SOI (Fig. 1.1(f)) is essentially a planar SOI MOSFET with a thin buried oxide (labeled as BOX). A heavily-doped region in silicon under the buried oxide acts as the back-gate. Unlike the front-gate, the back-gate is primarily used for tuning the device  $V_{th}$ . The buried oxide is usually thick such that the back-gate cannot induce an inversion layer at the back surface.  $V_{th}$  tuning can be used to compensate for variability in IC manufacturing from chip to chip or even circuit to circuit within the same chip. Doing so improves the IC speed and power consumption. It can also be used to dynamically raise or lower  $V_{th}$  circuit by circuit within a chip in response to the need for less leakage or more speed. This is a very effective means of managing power consumption.

#### 1.3 Multi-gate CMOS Modeling

#### 1.3.1 BSIM-MG: A BSIM-family Model for Multi-gate MOSFET

Given the advantages of multi-gate MOSFETs, it is likely that they will be used in future CMOS technologies. A production-worthy multi-gate compact model (SPICE model) which allows efficient circuit design is needed.

The BSIM (Berkeley Short-channel IGFET Model) series compact models have served the industry for 20 years [20, 21, 22]. BSIM3 and BSIM4 industry standard models have been widely used for the simulation of planar bulk MOSFETs. As technology advances, new compact models are developed to support new device architectures and incorporate new device physics. BSIMSOI [23, 24] was developed to model partially-depleted, fully-depleted and dynamically-depleted SOI devices. In this dissertation research, BSIM-MG [25] [26] is developed for circuit simulation of multi-gate MOSFETs.

The difference between BSIM-MG and other BSIM models lies not only in the difference in device structure, but also in the modeling technique it has used. In particular, source-drain symmetry [27] is maintained for BSIM-MG. Therefore unlike BSIM3 and BSIM4, the second derivative of the drain current and charge are continuous across  $V_{ds} = 0$ . This is a result of careful mathematical derivation and thorough testing to ensure the modeling or each physical effect in the compact model does not violate source/drain symmetry. During the course of developing BSIM-MG, we have learned several rules which ensures MOSFET symmetry is not broken. These rules will be discussed in this thesis.

Figure 1.1: Illustration of various flavors of multi-gate FETs. (SOI: silicon-on-insulator layer; BOX: buried oxide)

#### 1.3.2 BSIM-IMG and BSIM-CMG

It is likely that more than one flavor of multi-gate MOSFETs will be used in production for different purposes. Therefore the compact model should ideally cover as many of these flavors as possible. We have classified multi-gate MOSFETs into two main categories: independent multi-gate (IMG) and common multi-gate (CMG) MOSFETs.

IMG refers to independent double-gate MOSFETs with two separate gates. The frontand back-gate stacks are allowed to have different gate workfunctions, biases, dielectric thicknesses and materials. Independent-gate FinFET (Fig. 1.1(e)) and the planar doublegate SOI (Fig. 1.1(f)) belong to this category.

CMG refers to a special case where the gates are "on and the same." The gate stacks of CMG MOSFETs have identical gate workfunction, bias and dielectric thickness and material. Regular FinFETs and all-around gate MOSFETs (Figs. 1.1(a)-(d)) fall into to this category.

Two separate compact models BSIM-IMG and BSIM-CMG are developed for IMG and CMG devices, respectively.

## 1.4 Modeling Parasitic Resistances and Capacitances in the FinFET Multi-Gate Device

Despite the advantages of multi-gate structures, there are a few challenges. From a device point of view, one of the challenges is the larger parasitic resistances and capacitances in the three-dimensional structure.

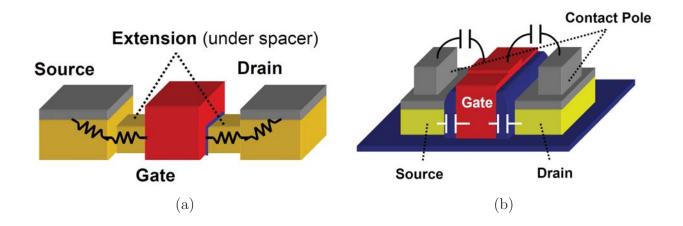

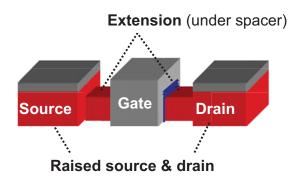

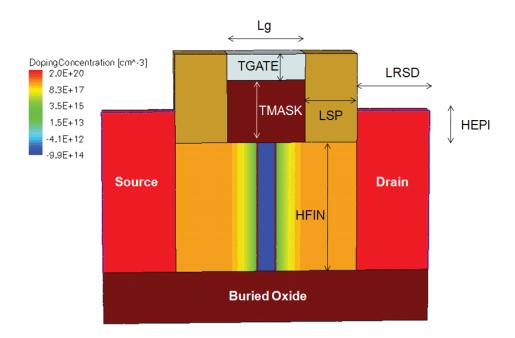

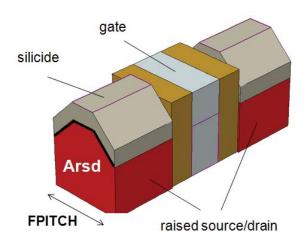

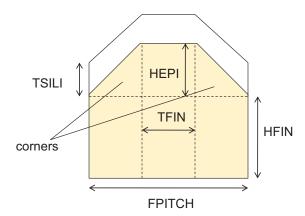

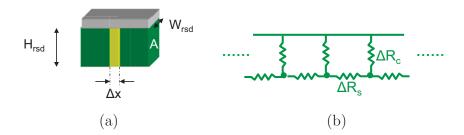

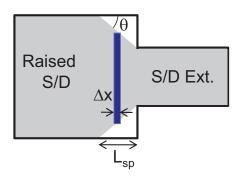

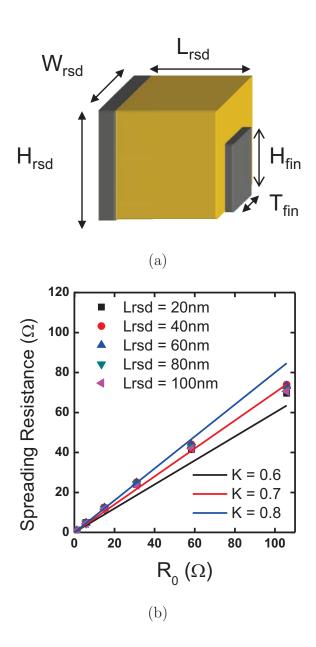

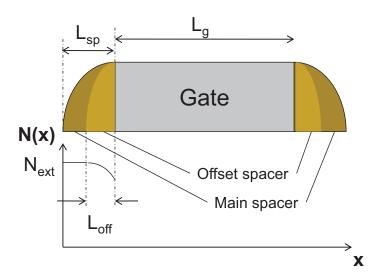

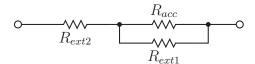

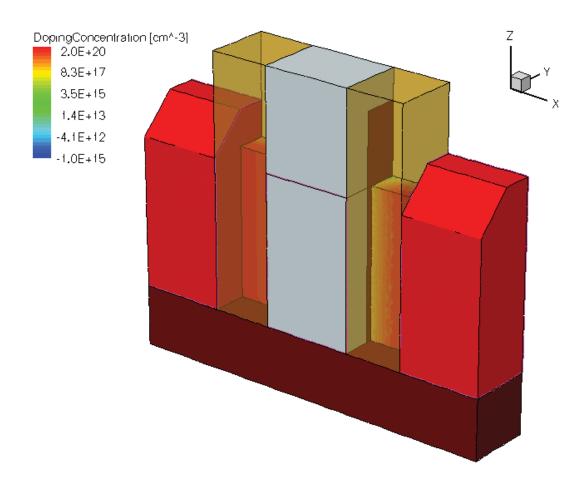

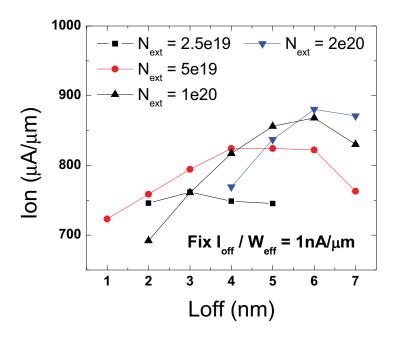

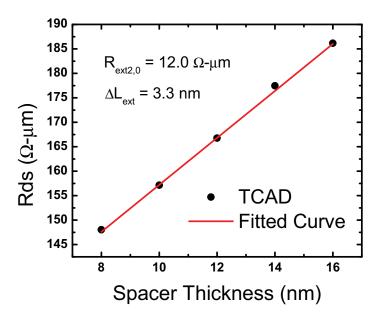

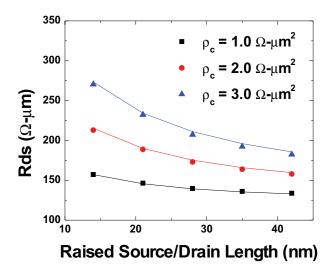

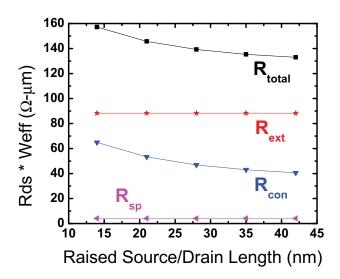

Take the FinFET multi-gate structure for example, a thin fin must be used for good short channel control. This results in a larger parasitic source/drain series resistance ( $R_{ds}$ ) due to the small cross sectional area of the fin extension (Fig. 1.2(a)). In order to minimize  $R_{ds}$ , a raised source/drain structure is often used [28]. The raised source/drain is often formed by a selective epitaxial growth process, which creates a non-rectangular raised source/drain cross section. Modeling of this three dimensional structure becomes very different from bulk MOSFETs. Therefore in this dissertation we investigated in the modeling of parasitic source/drain resistances in FinFETs.

Another important parasitic component is the outer fringe capacitances (Fig. 1.2(b)), which is made larger after enlarging the source and drain with a raised source/drain structure. The modeling of capacitances are becomes difficult in the three-dimensional FinFET compared with planar MOSFETs. We will briefly discuss about the modeling of parasitics capacitances as well.

Figure 1.2: (a) Illustration of source/drain series resistance in the FinFET structure (b) parasitic fringe capacitances

#### 1.5 Variation in FinFET SRAM Cells

One important roadblock for transistor size reduction is the random fluctuation of the number of dopant atoms in the MOSFET channel, called random dopant fluctuation (RDF) effect, which increases the variation in device threshold voltage  $(V_{th})$  [1] [29]. Since the standard deviation of  $V_{th}$  due to RDF is inversely proportional to  $\sqrt{WL}$ , circuits with small device dimensions such as the SRAM cell is especially susceptible to RDF.

RDF is a fundamental source of variation, which can not be eliminated as long as the channel is highly doped. Perhaps the only way to fight RDF is to reduce the channel doping. This is not possible for conventional bulk MOSFETs since heavy doping is required to control the short channel effects and subthreshold leakage. However, ultra thin-body (UTB) devices such as silicon-on-insulator (UTBSOI) MOSFETs [30] and especially UTB multi-gate devices like the FinFET [14] have much better short-channel behavior. In fact reducing the body thickness presents a new scaling path to allow future device size reduction in addition or in lieu of the past dependence on EOT reduction and channel doping escalation.

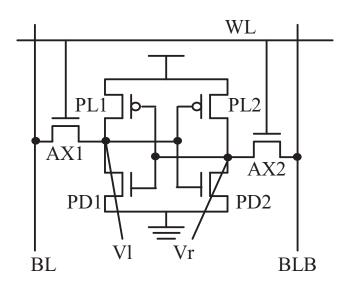

In the absence of doping in multi-gate devices, RDF is reduced. Perhaps the largest impact of this is on SRAM cells, since it typically has much smaller width compared to digital logic circuits and much larger variation. FinFET presents an excellent opportunity to reduce the variation of SRAM, enabling lower supply voltages and lower power consumption.

However, this is not to say that the variation in FinFET is unimportant. Line edge roughness [31] is expected to dominate FinFET variation through short channel effects. Therefore, unlike planar bulk MOSFETs, the resulting  $V_{th}$  distribution, for example, may be non-Gaussian, and is more difficult to model.

Simulation study that focuses on FinFET SRAM variation is often carried out using TCAD tools [32]. However, when a large number of simulation is needed, TCAD tools may

not be fast enough, and a compact model may be necessary.

In this dissertation, we will discuss about a simulation study that we have carried out using BSIM-MG. We extracted parameters for the BSIM-MG model using stand alone Fin-FET drain current data. Subsequently variation sources are added to the BSIM-MG model. A Monte Carlo simulation script is constructed in order to translate physical parameter variation to the distribution of electrical characteristics such as threshold voltage, read/write static noise margin, and power consumption. We adjusted the standard deviation of physical parameter variation so that the simulated electrical characteristic distribution matches measurement distribution. We then use the calibrated statistical model to re-design the SRAM, and analyze the sensitivity of variation to various design parameters.

One interesting result we have found is the non-Gaussian distribution of  $V_{th}$  in SRAM transistors. This could be the result of a non-linear mapping of physical dimensions of the FinFET to  $V_{th}$ . BSIM-MG is able to account for this because it models the dependence of  $V_{th}$  on the gate length and fin thickness well.

## 1.6 Thermal Noise Modeling for Planar and Multi-gate Transistors

Scaling is important for digital circuits for lower cost, enhanced performance and lower power per function. Thus multi-gate MOSFETs was introduced. Scaling is also important for analog circuits for high frequency applications of CMOS. With the advance of technology, recently a 60GHz transceiver has been demonstrated in 90nm CMOS [33].

In CMOS wireless/RF applications, the modeling of thermal noise is particularly important. In an RF receiver, a low noise amplifier (LNA) boosts the incoming wireless signal to prevent further degradation of the signal-to-noise ratio. One of the main factor that determines the noise performance of an LNA is the channel thermal noise of the amplifying MOSFETs. Therefore accurate modeling of thermal noise is required.

We have enhanced the industry standard BSIM4 [22] with a new thermal noise model. This model accurately accounts for the drain thermal noise, induced gate thermal noise, as well as the correlation between the two. It is implemented in Berkeley SPICE3 and released for industry use.

For the future multi-gate MOSFETs, very little thermal noise data is available. Nevertheless, we believe the physics remains similar to planar MOSFETs and the same thermal noise model can be easily adopted for multi-gate MOSFETs as well.

#### 1.7 Dissertation Goals and Outline

The goal of this dissertation research is to develop compact models for nanoscale CMOS technology, with particular emphasis on multi-gate MOSFET compact models.

Chapter 2 focuses on the derivation of the core model for multi-gate MOSFETs with independent front- and back-gates, BSIM-IMG. This includes the calculation of surface potential and the derivation of the basic drain current and terminal charge formulations. The model is verified with TCAD tools. We also briefly describe the enhancements to the BSIM-CMG drain current model. For a complete description of the core model of BSIM-CMG, the readers may refer to [34].

Chapter 3 summarizes the techniques we have used to maintain model symmetry in BSIM-MG. We present five basic rules for formulating equations to ensure symmetry, and several examples for the rules.

Chapter 4 describes a parasitic source/drain resistance model for the FinFET multi-gate structure, including the bias-dependent extension resistance, the spreading resistance, and a transmission line based contact resistance component. The model is verified against three dimensional numerical simulation.

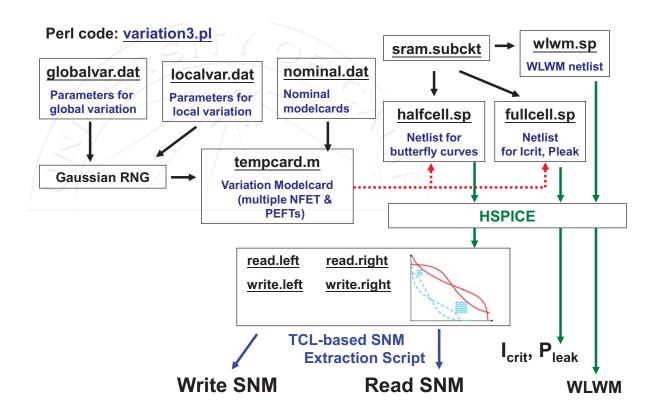

In chapter 5, we applied the BSIM-MG model to study the modeling of manufacturing variation of FinFET SRAM cells. A Monte Carlo simulation framework that simultaneously accounts for both global and local variation is developed. The model is calibrated to measured FinFET threshold voltage and static noise margin distributions.

Finally, chapter 6 describes a new thermal noise model that is derived for the industry standard BSIM4. The model is verified against segmented channel transistor, as well as measured thermal noise data.

An overall summary of this dissertation is presented in Chapter 7. Chapter 7 highlights the key research contributions and future research directions are suggested.

## Chapter 2

# Basic Formulations of Multiple-Gate MOSFET Compact Models

#### 2.1 Core Models of BSIM-CMG and BSIM-IMG

As we mentioned in chapter 1, the common multi-gate (CMG) and independent multi-gate (IMG) MOSFETs are modeled separately due to the different device structure and operation. The models are named BSIM-CMG and BSIM-IMG, respectively. The difference in device structures leads to different boundary conditions for the Poisson's equation. Therefore BSIM-CMG and BSIM-IMG have very different core models<sup>1</sup>.

First of all, BSIM-CMG has one less terminal compared to BSIM-IMG because all the gates are tied together. A reduced number of nodes means faster SPICE simulation. Therfore, for computational efficiency reasons the two devices should use two different models.

In addition, the core model for BSIM-CMG is somewhat simpler than that of BSIM-IMG. For both models, the values of surface potential need to be computed by finding the root of the non-linear input voltages equation (IVE) that relates the surface potential to terminal voltages. For BSIM-CMG the IVE has only one unknown. Good convergence is achieved through either Newton Raphson iteration or non-iterative analytical approximations [25]. On the other hand, the IVE of BSIM-IMG contains two equations and two unknowns. A special treatment is needed for surface potential computation in BSIM-IMG, making the model more complex than BSIM-CMG.

Furthermore, BSIM-CMG models common multi-gate MOSFETs, in which channel doping is likely needed to achieve multiple  $V_{th}$ . Therefore channel doping is included as part of the core model for BSIM-CMG. On the other hand, BSIM-IMG models independent-gate devices, which has a back-gate terminal that can be used to achieve multiple  $V_{th}$ . Therefore the channel is likely lightly doped. In BSIM-IMG, a lightly-doped channel is assumed for

<sup>&</sup>lt;sup>1</sup>The core model includes the calculation of surface potential, and the basic drain current and terminal charge formulations

core model derivation. This simplifies the mathematics and improves computational efficiency. For IMG devices with a lightly doped body, a bias-independent  $V_{th}$  correction term is sufficient to model doping.

Although the core model are different, they have very similar real device effect models. These include mobility degradation, velocity saturation, gate tunneling current, channel length modulation, gate induced drain leakage current, and many others. Some of the equations are conveniently taken from bulk transistor models such as BSIM4, since the physics are the same.

In this dissertation, we will focus on the core model of BSIM-IMG, as a treatment on the BSIM-CMG core model is already available in [34]. For BSIM-CMG, an improvement to the core I-V model is presented in the end of this chapter.

## 2.2 Modeling Double-gate Fully-depleted SOI MOS-FETs with BSIM-IMG

The fully-depleted SOI (FDSOI) MOSFET is a promising CMOS replacement. It has the advantage of superior control of short channel effects when the body is very thin because unwanted leakage paths through the buried channel are eliminated.

However, the field originating from the drain can still be coupled to the channel through the buried oxide (BOX) [35]. To prevent this the buried oxide thickness must be scaled as well [36]. The silicon beneath the buried oxide is heavily doped to act as a back-gate that shield the field from the drain. An addition advantage for a back-gated design is that it allows dynamic threshold voltage  $(V_{th})$  control. By selectively raising  $V_{th}$  in idle circuit blocks by back-gate biasing, static leakage current can be significantly reduced without hurting the active-state performance [19]. Furthermore, multiple  $V_{th}$  flavors in the same circuit can be achieved with back-gate biasing instead of channel doping, which causes larger variation, or multiple work function gates, which significantly increases process complexity. Therefore from a device point of view, an ideal FDSOI has a thin BOX.

BSIM-IMG models FDSOI devices with a thin BOX. With a heavily doped layer beneath the BOX acting as a second gate, the thin BOX FDSOI MOSFET is essentially an independent double-gate MOSFET. In fact we have developed BSIM-IMG with this target device in mind.

Several compact models for independent double-gate MOSFETs are available in the literature [37, 38, 39, 40, 41, 42, 43, 44]. Pei et al. [37] and Reyboz et al. [38] model the current and charge of independent DG MOSFETs with explicit expressions. Both models show good agreements with TCAD simulations. However, the formulations used in the models are known to violate source-drain symmetry — an important requirement for certain analog applications [45]. Other independent DG models do not have this symmetry issue [39, 40, 41, 42, 43, 44]. However, they are surface potential based and the surface potential

is described in implicit forms. Iterative techniques such as Newton Raphson are required inside the model, which from our experience significantly degrades computational efficiency [46].

Recently, explicit approximations of surface potential have been developed for planar bulk MOSFETs [47] and symmetric (common) double-gate MOSFETs [25, 48] and are robust and computationally efficient. In this work, we developed such explicit approximation for independent DG MOSFETs. The computational efficiency of the new approximation are proven by measuring the runtime of the compiled and optimized version of the approximation. In addition, drain current and terminal charge expressions are derived. The results are verified by comparing it with TCAD [49] simulations without the use of fitting parameters.

Non-ideal effects such as short channel and quantum effects, field dependent mobility, leakage currents and device parasitics are added to model real devices. The Gummel Symmetry Test [27, 45] is performed to verify the symmetry of drain current and charge with respect to  $V_{ds} = 0$ . The full model including non-ideal effects is implemented in Verilog-A [50]. Good convergence is demonstrated through transient simulation of a large coupled ring oscillator circuit.

#### 2.3 Core Model of BSIM-IMG

#### 2.3.1 Modeling Framework

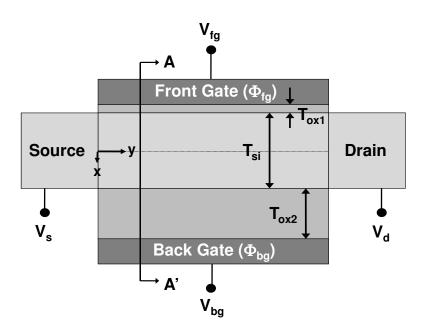

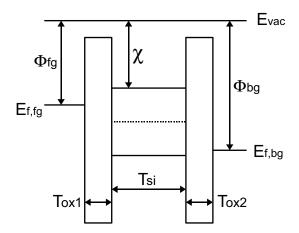

The basic model formulation for the independent double-gate FDSOI MOSFET is developed based on the 2-dimensional schematic cross section shown in Fig. 2.1. This view corresponds to a horizontal cross section of the independent-gate FinFET (Fig. 1.1(e)) or a vertical cross section along the length direction of the planar double-gate SOI MOSFET (Fig. 1.1(f)). A silicon channel with thickness  $T_{si}$  is sandwiched between the front- and back-gate stacks. The two gate stacks are allowed to have different work functions ( $\Phi_{g1}$ ,  $\Phi_{g2}$ ), materials (metal or heavily doped semiconductor), dielectric thicknesses ( $T_{ox1}$ ,  $T_{ox2}$ ), and dielectric constants ( $\epsilon_{ox1}$ ,  $\epsilon_{ox2}$ ). The energy band diagram of this system at the flat-band condition is shown in Fig. 2.2. Without loss of generality, we focus on an n-type device throughout this chapter.

The silicon body is assumed to be lightly-doped and fully-depleted. Back-gated FDSOI MOSFETs will likely have a lightly-doped body to minimize random fluctuation effects [29] and to increase mobility. In addition, with a thin body, heavy doping is not needed for controlling short channel effects.  $V_{th}$  is set by back-gate biasing or work function adjustment instead of channel doping.

### 2.3.2 Explicit Approximation for Surface Potential

In this section, we develop a method to approximately solve the Poissons equation and obtain explicit analytical expressions for the surface potentials and the inversion carrier density per

Figure 2.1: Basic framework for modeling independent double-gate MOSFETs.

area  $(Q_{inv})$ . The results are verified with TCAD simulations. Since there is no neutral body for fully-depleted devices, it is convenient to choose the quasi-Fermi level at the source as a reference for the potential  $(\psi)$ . In this dissertation we define  $\psi$  in the silicon body as follows:

$$\psi = -\frac{E_c - E_f(source)}{q} \tag{2.1}$$

where  $E_c$  is the conduction band energy and  $E_f(source)$  is the quasi Fermi level at the source. The surface potentials,  $\psi_{s1} = \psi|_{x=-Tsi/2}$  and  $\psi_{s2} = \psi|_{x=+Tsi/2}$  are the potentials at the front- and back-silicon/oxide interfaces, respectively.

In the ideal long channel case, the potential distribution in the silicon channel is governed by the 1-dimensional Poisson's equation:

$$\epsilon_{si} \frac{d^2 \psi(x, y)}{dx^2} = q N_c \cdot \exp\left[\frac{q(\psi(x, y) - V_{ch}(y))}{kT}\right]$$

(2.2)

where  $\epsilon_{si}$  is the dielectric constant of silicon,  $N_c$  is the conduction band density of states of silicon, and  $V_{ch}$  is the channel voltage (the electron quasi Fermi level potential relative to the source). The Boltzmann's approximation is used for the inversion carrier density. The charge contribution of ionized dopants is neglected since the body is lightly-doped. We focus on an n-type device and neglect the contribution of holes.

Figure 2.2: Energy band diagram at flat-band condition corresponding to the A-A' cutline in Fig. 2.1.  $\chi$  is the electron affinity.

The continuity of displacement field at the front and back interfaces gives the following relation of the surface electric fields  $(E_{s1} = -\frac{d\psi}{dx}|_{x=-Tsi/2})$  and  $E_{s2} = -\frac{d\psi}{dx}|_{x=Tsi/2})$  and surface potentials:

$$C_{ox1(2)} \left( V_{fg(bg)} - \Delta \Phi_{1(2)} - \psi_{s1(2)} \right) = \epsilon_{si} E_{s1(2)}$$

(2.3)

where  $C_{ox1(2)} = \epsilon_{ox1(2)}/T_{ox1(2)}$  are the front(back) oxide capacitances, and  $\Delta\Phi_{1(2)}$  are the workfunction differences of the front-gate (back-gate) and the N+ source.

Equation (2.3) is the boundary condition for the ordinary differential equation (ODE), equation (2.2). The analytical solution to this problem is known [51, 52]. However, it requires the solving of a set of two coupled non-linear equations:

$$V_{fg} - \Delta\Phi_1 - V_{ch} = r_0 + \frac{2kT}{q} \ln \left[ \frac{2\beta}{\sinh(\alpha - \beta)} \right] + r_1\beta \coth(\alpha - \beta)$$

(2.4)

$$V_{bg} - \Delta\Phi_2 - V_{ch} = r_0 + \frac{2kT}{q} \ln\left[\frac{2\beta}{\sinh(\alpha + \beta)}\right] - r_2\beta \coth(\alpha + \beta)$$

(2.5)

$r_0$ ,  $r_1$  and  $r_2$  are constants;  $\alpha$  and  $\beta$  are unknowns. Unfortunately this set of coupled equations is very difficult to solve. Iterative techniques are either computationally expensive or have convergence problems [46]. A non-iterative technique is therefore desirable for a compact model. In the rest of this section we will show how this can be achieved.

Multiplying  $\frac{d\psi}{dx}$  on both sides of Equation (2.2) and integrating from  $x = -\frac{T_{si}}{2}$  to  $x = \frac{T_{si}}{2}$ , we obtain:

$$E_{s1}^2 - E_{s2}^2 = \frac{2N_c kT}{\epsilon_{si}} \left\{ \exp\left[\frac{q(\psi_{s1} - V_{ch})}{kT}\right] - \exp\left[\frac{q(\psi_{s2} - V_{ch})}{kT}\right] \right\}$$

(2.6)

For FDSOI devices it is desired to have inversion carriers concentrated at the front surface, since short channel effects such as  $V_{TH}$  roll-off and drain induced barrier lowering (DIBL) are less prominent in such a condition. For this reason we can assume the carrier density at the back interface is negligible compared to that at the front interface, and the second exponential term in Equation (2.6) can be neglected. Neglecting that term and substituting  $E_{s1}$  with 2.3, we obtain,

$$\left[\frac{C_{ox1}(V_{fg} - \Delta\Phi_1 - \psi_{s1})}{\epsilon_{si}}\right]^2 = E_{s2}^2 = \frac{2N_c kT}{\epsilon_{si}} \exp\left[\frac{q(\psi_{s1} - V_{ch})}{kT}\right]$$

(2.7)

In Equation (2.7),  $E_{s2}$  is a function of  $\psi_{s2}$ , making it difficult to find an explicit approximation. To overcome this difficulty,  $E_{s2}$  is approximated by assuming a constant displacement field in the vertical direction between the two gates, including the front oxide, the silicon body, and the back oxide,

$$E_{s2} = \frac{(V_{fg} - \Delta\Phi_1) - (V_{bg} - \Delta\Phi_2)}{\frac{\epsilon_{si}}{\epsilon_{\alpha r}}(T_{ox1} + T_{ox2}) + T_{si}}$$

$$(2.8)$$

This simplification reduces the number of unknowns in Equation (2.7) to one. We can then solve Equation (2.7) and obtain  $\psi_{s1}^{(1)}$  ( $\psi_{s1}$  without perturbation) using a computationally efficient explicit approximation similar to that described in [47]. The details of this explicit approximation are described in [46].

Equation (2.8) is a good approximation when the transistor is biased in weak inversion and the carrier density in the body is insignificant. In strong inversion, however, a two-dimensional electron gas forms at the front surface, and the displacement field in the front oxide is quite different from that in the body and the back oxide. To further improve the accuracy of the model in strong inversion, a perturbation step is employed to refine  $\psi_{s1}$ . The back surface field is estimated using.

$$E'_{s2} = \frac{\psi_{s1}^{(1)} - (V_{bg} - \Delta\Phi_2)}{\frac{\epsilon_{si}}{\epsilon} T_{ox2} + T_{si}}$$

(2.9)

where a constant displacement field is assumed in the body and the back oxide, but this field is not assumed to be the same as that in the front oxide. Substituting  $E_{s2}$  with  $E'_{s2}$  in Equation (2.7), we obtain  $\psi_{s1}^{(2)}$  ( $\psi_{s1}$  with perturbation).

The inversion carrier per area,  $Q_{inv}$  and the back surface potential,  $\psi_{s2}$ , are computed as functions of  $\psi_{s1}$  through the Poissons Equation (2). The details on the calculation of

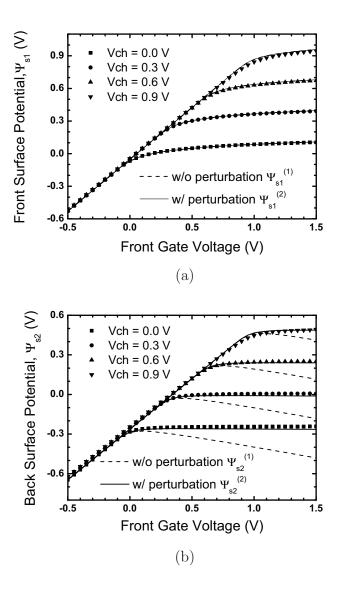

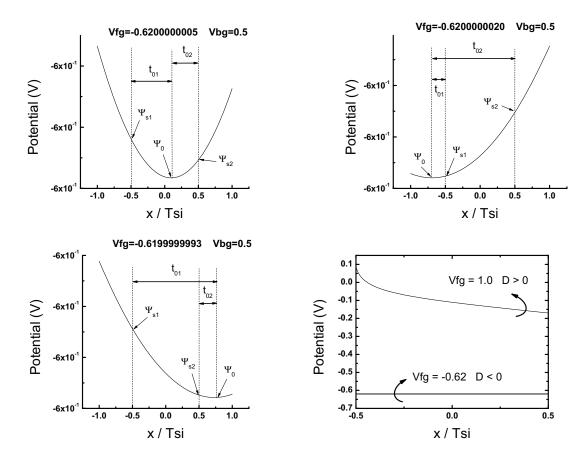

$\psi_{s2}$  and  $Q_{inv}$  are given in the Appendix A. The model is verified with TCAD for an ideal long channel device without the use of any fitting parameters. In Fig. 2.3,  $\psi_{s1}$  and  $\psi_{s2}$  are plotted versus front-gate voltage  $(V_{fg})$  for different values of  $V_{ch}(y)$ , corresponding to different positions along the channel. Good agreement between the model and TCAD is achieved. In Fig. 2.3 we compared the surface potential solutions with and without perturbation. Without perturbation,  $\psi_{s1}$  is reasonably accurate (In Fig. 2.3(a) the curves with and without perturbation overlap). But a large deviation is observed for  $\psi_{s2}$  (Fig. 2.3(b)). Since  $\psi_{s1}$  is accurate we use it to compute  $E'_{s2}$  in Equation (2.8). We then obtain accurate  $\psi_{s1}$  and  $\psi_{s2}$ .

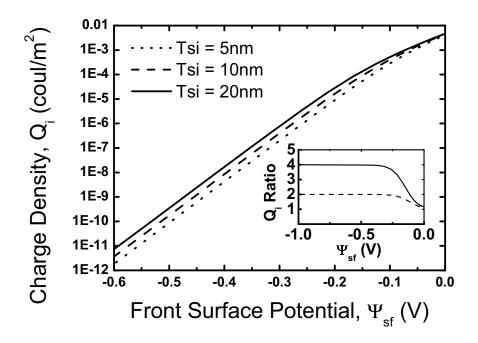

For an FDSOI device with a thick buried oxide in sub-threshold operation, the potential throughout the body is almost constant. Therefore the inversion carrier density is proportional to the body thickness. This is sometimes referred to as volume inversion [53]. The surface potential approximation preserves this important property, as shown in Fig. 2.4.

#### 2.3.3 Drain Current Model

In this subsection, a drain current model for long channel FDSOI MOSFETs is derived and verified with TCAD.

The charge sheet approximation [54] is often used for deriving the MOSFET drain current, as in [26]. Although it simplifies the derivation of drain current and charge, it introduces some error in the moderate inversion region. In this work we show that Ids can be derived for FDSOI MOSFETs in closed form without involving the charge sheet approximation.

The drain current is derived based on drift diffusion transport:

$$I_{ds} = \mu \cdot W \cdot Q_{inv}(y) \cdot \frac{dV_{ch}(y)}{dy}$$

(2.10)

where  $\mu$  is the carrier mobility. For simplicity  $\mu$  is treated as a constant during derivation. However, in the final compact model  $\mu$  is replaced with the vertical field-dependent effective mobility. For a lightly-doped body, the unit area inversion charge density can be expressed as:

$$Q_{inv} = \sqrt{2N_c k T \epsilon_{si} \exp\left[\frac{q \left[\psi_{s1}(y) - V_{ch}(y)\right]}{kT}\right] + \left(\epsilon_{si} E_{s2}\right)^2} - \epsilon_{si} E_{s2}$$

(2.11)

based on Equations (2.3), (2.7) and the Gauss law. We differentiate Equation (2.11) with respect to the channel position, y and simplify it into a form suitable for Ids integration:

$$\eta \cdot \frac{kT}{q} \cdot \frac{dQ_{inv}(y)}{dy} = Q_{inv}(y) \frac{d}{dy} \left[ \psi_{s1}(y) - V_{ch}(y) \right]$$

(2.12)

where

$$\eta = 2 - \frac{2\epsilon_{si}\tilde{E}_{s2}}{\tilde{Q}_{inv} + 2\epsilon_{si}\tilde{E}_{s2}} \tag{2.13}$$

Figure 2.3: (a) Front surface potential versus front-gate bias with varying channel voltage. The curves with and without perturbation overlaps. (b) Back surface potential versus front-gate bias ( $T_{ox1} = 1.2$  nm,  $T_{ox2} = 20$  nm,  $T_{si} = 15$  nm,  $V_{bg} = 0$ ,  $q\Phi_{g1} = 4.05$  eV,  $q\Phi_{g2} = 5.17$  eV). The surface potentials are obtained in TCAD by setting  $V_{ds} = V_{ch}$  in a long channel (L =  $10\mu m$ ) DG MOSFET structure and extracting the surface potential at the drain end of the channel. (Symbols: TCAD; Lines:Model)

Figure 2.4: Inversion charge density  $(Q_{inv})$  versus front surface potential  $(\psi_{s1})$  for  $T_{si}=5$  nm, 10 nm and 20 nm. In sub-threshold operation carrier density is proportional to the body thickness if  $T_{ox2}$  is very large. This important property is preserved by the newly developed surface potential approximation. Inset shows  $Q_{inv}$  for  $T_{si}=10$  nm and  $T_{si}=20$  nm, both normalized to the  $T_{si}=5$  nm case.  $(T_{ox1}=1.2 \text{ nm}; T_{ox2}=10 \mu m)$ .

$\eta$  varies from 1 in sub-threshold to 2 in strong inversion. The exact form of  $\eta$  is with  $\tilde{E}_{s2} = E_{s2}(y)$  and  $\tilde{Q}_{inv} = Q_{inv}(y)$ , both being a function of y. However to simplify the derivation of  $I_{ds}$  we approximate  $E_{s2}(y)$  and  $Q_{inv}(y)$  using their average source-side (y = 0) and drain-side (y = L) values,  $\bar{E}_{s2}$  and  $\bar{Q}_{inv}$  so that  $\eta$  becomes independent of position. In equation (2.12),  $Q_{inv}(y)$  can be expressed based on Gauss law as

$$Q_{inv}(y) = C_{ox1} \left[ V_{fg} - \Delta \Phi_1 - \psi_{s1}(y) \right] - \epsilon_{si} E_{s2}(y)$$

(2.14)

To make integration possible, we interpolate  $E_{s2}(y)$  as a linear function of the surface potential [55]. We substitute Equations (2.12) and (2.14) into Equation (2.10) and perform integration from source to drain. This gives:

$$I_{ds} = \mu \cdot \frac{W}{L} \cdot \left[ \frac{Q_{inv,s} + Q_{inv,d}}{2} (\psi_{s1,d} - \psi_{s1,s}) + \eta \cdot \frac{kT}{q} (Q_{inv,s} - Q_{inv,d}) \right]$$

(2.15)

$\psi_{s1,s}$  and  $\psi_{s1,d}$  are obtained by solving for surface potential at  $V_{ch} = 0$  and  $V_{ch} = V_{ds}$ , respectively.  $Q_{inv,s}$  and  $Q_{inv,d}$  are calculated from  $\psi_{s1,s}$  and  $\psi_{s1,d}$ , respectively. For long channel devices, Equation (2.15) naturally saturates at high drain bias due to pinch-off. For short channel devices, however, saturation happens before pinch-off due to velocity saturation. This is modeled by replacing Vds with an effect drain voltage, as in [55].

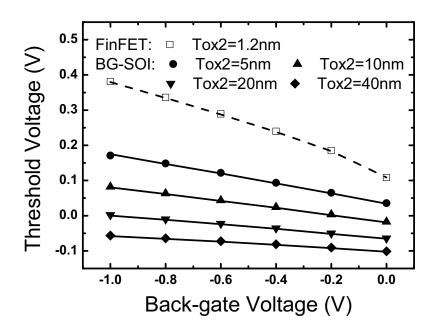

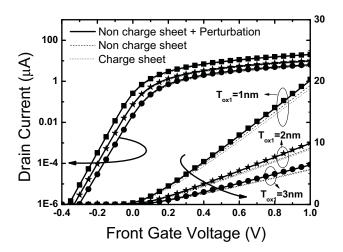

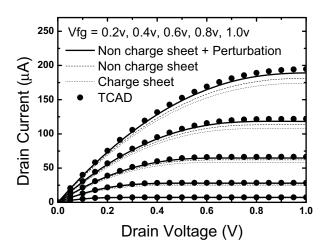

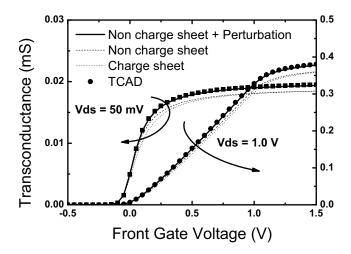

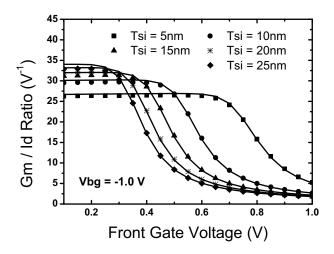

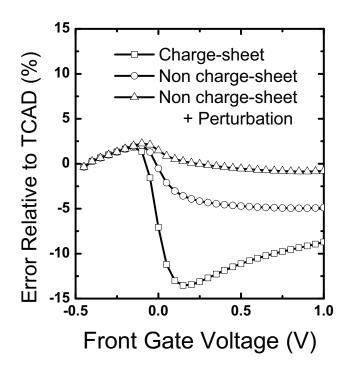

Figs. 2.5 - 2.10 verify the drain current model by comparing it with TCAD. In Fig. 2.5,  $V_{TH}$  is plotted versus back-gate voltage  $(V_{bg})$  for both symmetric and asymmetric double-gate devices operating in the independent-gate model. The independent-gate FinFET [18] is one example of independent-gate devices with symmetric gate stacks. The model agrees well with TCAD at different  $T_{ox2}$ . The larger slope for thin back-oxide devices is due to the stronger coupling from the back-side. Fig. 2.6 shows  $I_{ds}$  versus  $V_{fg}$  for different  $T_{ox1}$ . Fig. 2.7 shows  $I_{ds}$  versus  $V_{ds}$  at several  $V_{fg}$ . Fig. 2.8 shows the transconductance  $(g_m)$  versus  $V_{fg}$  at both linear and saturation modes. In all cases, the model agrees well with TCAD simulations without the use of any fitting parameters, reflecting the inherent predictability and scalability of the model. The effect of not using perturbation and the effect of using the charge sheet approximation (obtained by setting  $\eta = 1$  in Equation (2.15)) are also shown in Figs. 2.6 - 2.8 for comparison.

Fig. 2.9 verifies the transconductance efficiency,  $g_m/I_{ds}$ . Fig. 2.10 shows the relative error of various models compared to TCAD. With the charge sheet approximation the Ids peak error is about 14% in moderate inversion (without perturbation for  $\psi_{s1}$  calculation). Replacing the Ids equation with (2.15) improves the accuracy. Perturbation further improves the accuracy so that the peak error becomes about 2%. This error can be simply reclaimed by using some amount of flexible fitting parameters if needed, as is done in a practical compact model.

Figure 2.5: Threshold voltage versus front-gate bias. Solid lines and closed symbols: backgated FDSOI structure with varying back oxide thickness ( $T_{si} = 15nm$ ,  $T_{ox1} = 1.2nm$ ,  $V_{ch} = 0$ ,  $\Phi_{g1} = 4.05V$ ,  $\Phi_{g2} = 5.17V$ ); dashed lines and open symbols: independent-gate FinFET structure [18] ( $T_{ox1} = T_{ox2} = 1.2nm$ ,  $T_{si} = 15nm$ ,  $\Phi_{g1} = 4.4V$ ,  $\Phi_{g2} = 4.4V$ ). The threshold voltage is extracted using a constant current definition ( $100nA \cdot W/L$ ). (Symbols: TCAD; Lines: Model)

Figure 2.6: Drain current versus front-gate voltage for different front dielectric thicknesses.  $(T_{si}=15nm,\,T_{ox2}=20nm,\,V_{bg}=0,\,V_{ds}=50mV,\,\Phi_{g1}=4.05V,\,\Phi_{g2}=5.17V)$  (Symbols: TCAD; Lines: Model)

Figure 2.7: Drain current versus drain voltage for different front-gate bias. ( $T_{si}=15nm$ ,  $T_{ox1}=1nm$ ,  $T_{ox2}=20nm$ ,  $V_{bg}=0$ ,  $\Phi_{g1}=4.05V$ ,  $\Phi_{g2}=5.17V$ ) (Symbols: TCAD; Lines: Model)

Figure 2.8: Transconductance versus front-gate voltage at  $V_{ds} = 50mV$  and  $V_{ds} = 1.0V$ . The transconductance in TCAD is extracted from small-signal simulations. ( $T_{si} = 15nm$ ,  $T_{ox1} = 1.2nm$ ,  $T_{ox2} = 20nm$ ,  $V_{bg} = 0$ ,  $\Phi_{g1} = 4.05V$ ,  $\Phi_{g2} = 5.17V$ ) (Symbols: TCAD; Lines: Model).

Figure 2.9: Transconductance efficiency  $(g_m/I_{ds})$  versus front-gate voltage for different silicon body thicknesses.  $(T_{ox1}=T_{ox2}=1.2\text{nm},\ V_{bg}=-1V,\ \Phi_{g1}=4.4\text{V},\ \Phi_{g2}=4.4\text{V})$  (Symbols: TCAD; Lines: Model).

Figure 2.10: Percentage error in  $I_{ds}$  versus  $V_{fg}$  relative to TCAD for the charge-sheet model, the non-charge-sheet model, and the non-charge-sheet model with surface potential perturbation. ( $T_{si}=15nm,\,T_{ox1}=1.0nm,\,T_{ox2}=20nm,\,V_{bg}=0,\,\Phi_{g1}=4.05V,\,\Phi_{g2}=5.17V$ )

#### 2.3.4 Capacitance Model

The C-V model for long channel back-gated FDSOI MOSFETs is derived using the charge-based approach, which preserves charge conservation [56]. In FDSOI, the exact expression for inversion charge density  $(Q_{inv})$  is quite complex. Nevertheless, as long as the back surface does not enter inversion, we may approximate  $Q_{inv}$  as follows:

$$Q_{inv}(y) = C_{ox1} \left[ V_{fg} - \Delta \Phi_1 - \psi_{s1}(y) \right] + \frac{C_{ox2} C_{si}}{C_{ox2} + C_{si}} \left[ V_{bg} - \Delta \Phi_2 - \psi_{s1}(y) \right]$$

(2.16)

where  $C_{si} = \epsilon_{si}/T_{si}$  is the body capacitance. Here  $Q_{inv}$  is decomposed into two components: the first term representing the charge due to the front oxide capacitor; the second term representing the charge due to the back oxide capacitance  $(C_{ox2})$  in series with the body capacitance  $(C_{si})$ . Substituting Equation (2.16) into Equation (2.15) and utilizing current continuity, we obtain the relation of  $\psi_{s1}$  and y as follows:

$$y = \mu C_{ox1} \frac{W}{I_{ds}} (\psi_{s1}(y) - \psi_{s1,s})$$

$$\left\{ V_{fg} - \Delta \Phi_1 - \frac{\psi_{s1,s} + \psi_{s1}(y)}{2} + \gamma_c \cdot \left[ V_{bg} - \Delta \Phi_2 - \frac{\psi_{s1,s} + \psi_{s1}(y)}{2} \right] + \eta \cdot \frac{kT}{q} (1 + \gamma_c) \right\}$$

(2.17)

where  $\gamma_c = (C_{ox2} \parallel C_{si})/C_{ox1}$ . Utilizing Equation (2.17) we may derive expressions for the total charge associated with each terminal of the device. The charge associated with the front-gate is obtained by integrating the front-gate charge density from source to drain:

$$Q_{fg} = W \int_{0}^{L} C_{ox1} \left[ V_{fg} - \Delta \Phi_{1} - \psi_{s1}(y) \right] dy$$

$$= C_{ox1} W L \left\{ V_{fg} - \Delta \Phi_{1} - \frac{\psi_{s1,s} + \psi_{s1,d}}{2} + \frac{B(\psi_{s1,d} - \psi_{s1,s})^{2}}{6 \left[ A - B(\psi_{s1,d} + \psi_{s1,s}) \right]} \right\}$$

(2.18)

where

$$A = V_{fg} - \Delta\Phi_1 + \gamma_c \cdot (V_{bg} - \Delta\Phi_2) + \eta \cdot \frac{kT}{q} (1 + \gamma_c)$$

(2.19)

$$B = \frac{1 + \gamma_c}{2} \tag{2.20}$$

Similarly, the charge associated with the back-gate is derived:

$$Q_{bg} = W \int_{0}^{L} \frac{C_{ox2}C_{si}}{C_{ox2} + C_{si}} \left[ V_{bg} - \Delta\Phi_{2} - \psi_{s1}(y) \right] dy$$

$$= \gamma_{c} \cdot \left\{ Q_{fg} - C_{ox1} \cdot WL \cdot \left[ (V_{fg} - \Delta\Phi_{1}) - (V_{bg} - \Delta\Phi_{2}) \right] \right\}$$

(2.21)

To obtain the drain charge we follow the Ward-Dutton charge partition scheme [57].

$$Q_{d} = W \left( \int_{0}^{L} C_{ox1} \left[ V_{fg} - \Delta \Phi_{1} - \psi_{s1}(y) \right] \frac{y}{L} dy \right)$$

$$+ \int_{0}^{L} (C_{ox2} \parallel C_{si}) \left[ V_{bg} - \Delta \Phi_{2} - \psi_{s1}(y) \right] \frac{y}{L} dy \right)$$

$$= -\frac{C_{ox1} W L}{2} \left\{ (V_{fg} - \Delta \Phi_{1}) + \gamma_{c} (V_{bg} - \Delta \Phi_{2}) - (1 + \gamma_{c}) \cdot \left[ \frac{\psi_{s1,s} + 2\psi_{s1,d}}{3} + \frac{B(\psi_{s1,d} - \psi_{s1,s})^{2}}{6[A - B(\psi_{s1,s} + \psi_{s1,d})]} - \frac{B^{2} (\psi_{s1,d} - \psi_{s1,s})^{3}}{30[A - B(\psi_{s1,s} + \psi_{s1,d})]^{2}} \right\}$$

$$(2.22)$$

Finally, the source charge is calculated from all the other components by charge neutrality:

$$Q_s = -Q_{fg} - Q_{bg} - Q_d (2.23)$$

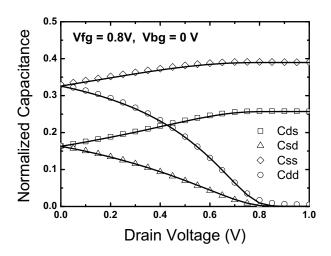

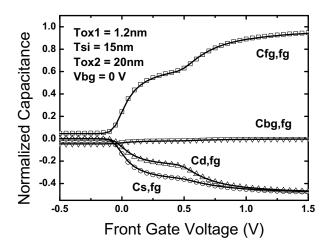

The C-V model is verified by comparing transcapacitances to small-signal TCAD simulations in Figs. 2.11 and 2.12. In Fig. 2.11, transcapacitances  $C_{sd}$ ,  $C_{ds}$ ,  $C_{ss}$  and  $C_{dd}$  are plotted versus  $V_{ds}$ . At  $V_{ds}=0$ ,  $C_{ss}$  and  $C_{dd}$  are equal;  $C_{sd}$  and  $C_{ds}$  are equal, reflecting the source-drain symmetry of the C-V model. In Fig. 2.12, transcapacitances  $C_{fg,fg}$ ,  $C_{s,fg}$ ,  $C_{d,fg}$  and  $C_{bg,fg}$  are plotted versus  $V_{fg}$ . In both plots, the model matches TCAD very well in both linear and saturation mode without the use of any fitting parameters.

### 2.4 Core Model of BSIM-CMG

The core model of BSIM-CMG is described fairly well in [34, 52]. In this section we present and enhanced I-V model that makes it compatible with a charge segmentation based non quasi-static core model.

#### 2.4.1 Background

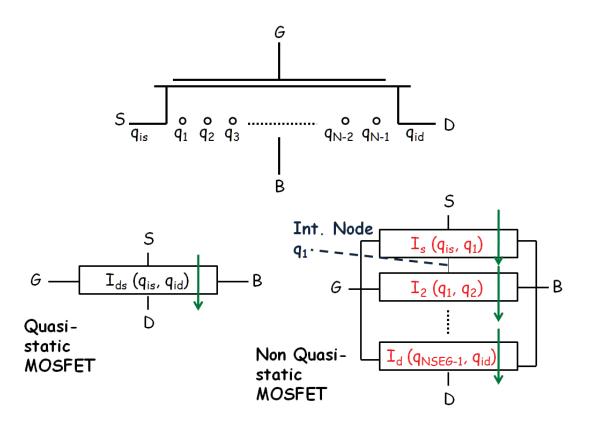

Non quasi-static (NQS) effects is important for devices operating near its cutoff frequency. Since the device cutoff frequency is a strong function of L, NQS is often encountered in circuits with a mixture of long channel and short channel devices [58].

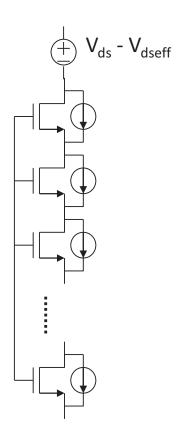

In BSIM-CMG, NQS effects is modeled using the charge segmentation method<sup>2</sup>. Fig. 2.13 illustrates the basic concept. The transistor in question is divided into N segments

$<sup>^2</sup>$ In BSIM-CMG, there are many options for modeling NQS effects, selected by the user through the parameter NQSMOD. When NQSMOD=1 the equivalent gate resistor NQS model is activated. When NQSMOD=3 the charge segmentation method is activated.

Figure 2.11: Transcapacitances  $C_{ds}$ ,  $C_{sd}$ ,  $C_{ss}$  and  $C_{dd}$ , normalized to  $C_{ox1}WL$ , versus drain voltage.  $(T_{si} = 15nm, T_{ox1} = 1.2nm, T_{ox2} = 20nm, V_{fg} = 0.8V, V_{bg} = 0, q\Phi_{g1} = 4.05eV, q\Phi_{g2} = 5.17eV)$  (Symbols: TCAD; Lines: Model)

Figure 2.12: Transcapacitances  $C_{fg,fg}$ ,  $C_{d,fg}$ ,  $C_{s,fg}$  and  $C_{bg,fg}$ , normalized to  $C_{ox1}WL$ , versus front-gate voltage. ( $T_{si}=15nm,\ T_{ox1}=1.2nm,\ T_{ox2}=20nm,\ V_{ds}=0.5V,\ V_{bg}=0,\ \Phi_{g1}=4.05V,\ \Phi_{g2}=5.17V$ ) (Symbols: TCAD; Lines: Model)

with equal length. The voltage at the segment boundary is used to represent the inversion charge density  $(q_i)$  at the location. The quasi-static DC current and charge can be expressed in terms of inversion charge densities at the source  $(q_{is})$  and drain  $(q_{id})$  ends. For the non quasi-static case, the same expression is used to calculate the DC current and charge associate with each segment. They are expressed as function of the inversion carrier density at the segment boundaries.

The advantage of this approach is the input voltage equation does not have to be solved for each segment (to calculate surface potential). Instead, SPICE automatically computes the inversion charge density at each segment boundary. This is the main advantage of this approach compared to the NQS effect model in [59].

One requirement for this type of segmentation is the consistency of current with the quasistatic case. In other words, at low operating frequency the NQS effects model must give the same result as the quasi-static model. The current expression of BSIM-CMG automatically satisfy this because [34]

$$I_{ds,qs} = \frac{1}{L} \left[ h(Q_{is}) - h(Q_{id}) \right]$$

(2.24)

. For an N-segmented NQS model we can show that

$$I_{ds,nqs} = \frac{1}{N} \cdot \left\{ \frac{1}{L/N} \left[ h(Q_{is}) - h(Q_{i1}) + h(Q_{i1}) - h(Q_{i2}) + \dots - h(Q_{id}) \right] \right\} = I_{ds,qs} \quad (2.25)$$

. We have also verified this through simulation.

On the other hand, the quasi-static C-V model as described in [34] is not perfectly consistent with the I-V. The quasi-static C-V is derived using a simpler charge sheet based I-V as the current continuity relation, since the full I-V is too complicated. As a result, the quasi-static C-V becomes inconsistent with the NQS C-V, which utilizes the full I-V to compute inversion charges at each segment boundary.

We would like to have to have an accuracy of the full I-V. We would also like a simpler I-V so that C-V can be consistently derived based on that. In the next section, we propose a solution that satisfies both requirements.

#### 2.4.2 Simple Non Charge Sheet I-V Model

The drain current expression derived in [34] is repeated here for convenience:

$$I_{ds} = \mu \cdot \frac{W_{eff}}{L} \cdot \left[ \frac{Q_i^2}{2C_{ox}} + 2V_t Q_i - V_t \cdot (5C_{Si}V_t + Q_B) \ln (5V_t C_{Si} + Q_B + Q_i) \right]_d^s$$

(2.26)

The last term in the above equation is what causes difficulty in terminal charge integration. We simplify it using the relation

$$Q_0 \cdot \ln \frac{Q_0 + Q_s}{Q_0 + Q_d} \approx \frac{Q_0}{Q_0 + \frac{Q_{is} + Q_{id}}{2}} \cdot (Q_{is} - Q_{id})$$

(2.27)

Figure 2.13: Illustration of the charge-segmentation method for non quasi-static effects modeling

The full  $I_{ds}$  expression becomes

$$I_{ds} = \mu \cdot \frac{W_{eff}}{L} \cdot \left[ \frac{Q_{is}^2 - Q_{id}^2}{2C_{ox}} + \eta \cdot V_t \cdot (Q_{is} - Q_{id}) \right]$$

(2.28)

where

$$\eta = 2 - \frac{Q_0}{Q_0 + \frac{Q_{is} + Q_{id}}{2}} \tag{2.29}$$

Equation (2.28) is simple enough that analytical expressions for terminal charges can be derived, provided that  $\eta$  is treated as a constant during integration.

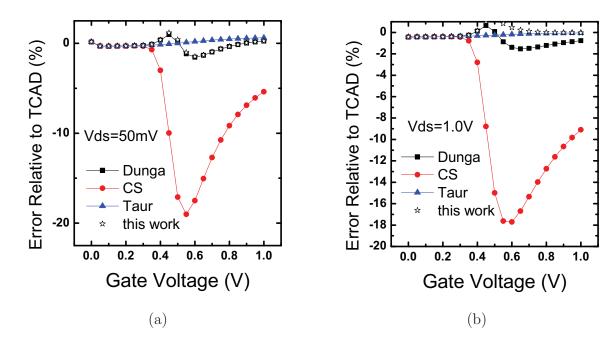

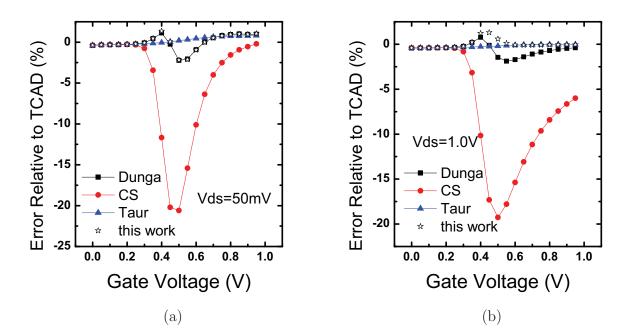

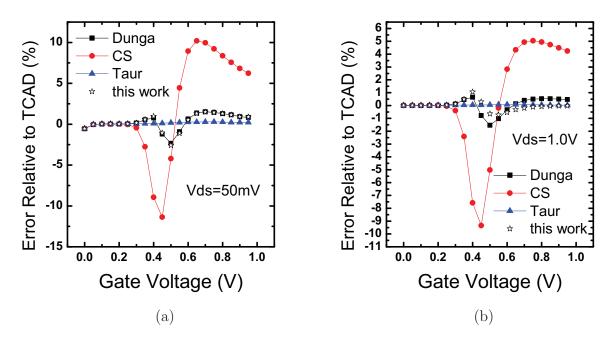

To verify the accuracy of the newly derived expression, we compare it with two-dimensional TCAD simulations [49]. Fig. 2.14 - 2.16 show the errors of drain current, transconductance, and transconductance efficiency for a common multi-gate device with a lightly-doped body. On the same graph we showed the results for four different cases: charge sheet (CS), original BSIM-CMG I-V model (Dunga),  $I_{ds}$  model given in [48] (Taur), and equation (2.28). As expected, the charge sheet model has the largest error. The error for the remaining cases are all below 3%. [48] has the smallest error. The difference between the original BSIM-CMG I-V and this work is only visible for the high drain bias case. Fig. 2.17 verifies that for the heavy doping case the difference due to the equation change is also small. [48] is not included in Fig. 2.17 because it only models the lightly-doped case.

#### 2.5 Real Device Effects and Source Drain Symmetry

The core model itself is insufficient to model real devices since it is derived under several assumptions such as constant carrier mobility and the gradual channel approximation. **Real device effect** corrections are necessary in order to capture all non-ideal effects observed in silicon data. BSIM4 model already models planar bulk transistors well. BSIM-MG takes a similar approach accounted for these effects.

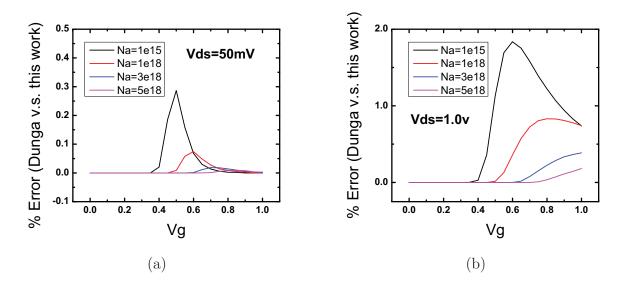

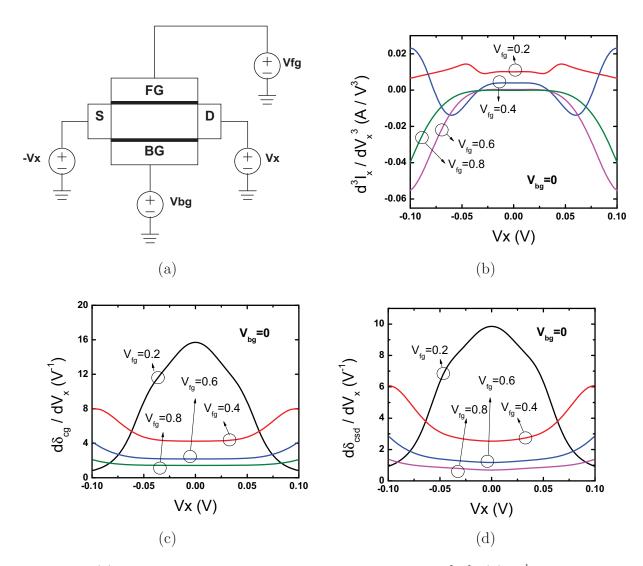

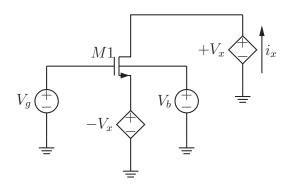

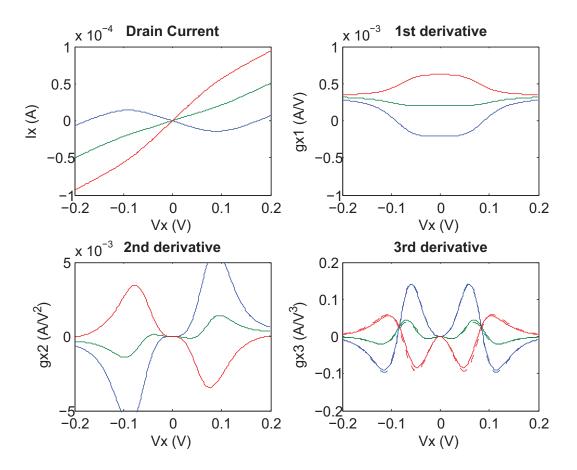

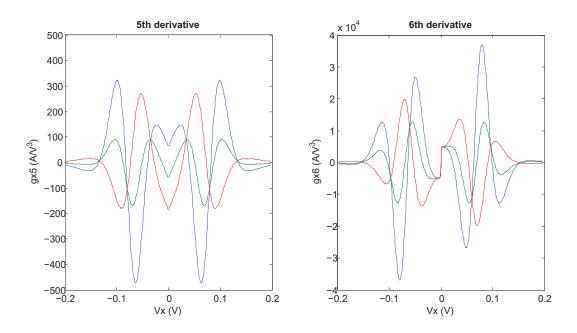

One challenge of real device effect modeling is to maintain the physical symmetry of the MOSFET source and drain. Some of the real device effect corrections in BSIM4 have caused symmetry problems. Although many of them are used in BSIM-MG, they are modified and carefully tested so that source-drain symmetry is no longer an issue. The source/drain symmetry is often validated using the Gummel Symmetry Test [27]. Fig. 2.18 is an example of the Gummel Symmetry Test that confirms the symmetry of BSIM-IMG. The same test has been done for BSIM-CMG as well. The symmetry of terminal charge expression is conducted using the charge symmetry test as proposed in [45]. A detailed discussion about symmetry is provided in chapter 3.

Some real device effects considered in BSIM-CMG and BSIM-IMG are listed as follows:

1.  $V_{th}$  roll off with L

Figure 2.14: Error plot for drain current using TCAD as a reference

- 2. Drain induced barrier lowering

- 3. Sub-threshold swing degradation

- 4. Degradation of back-gate  $V_{th}$  control with reduced L (BSIM-IMG only)

- 5. Vertical field dependent carrier mobility

- 6. Quantum Mechanical Effects

- 7. Velocity saturation

- 8. Channel length modulation

- 9. Output resistance degradation due to DIBL

- 10. Gate-induced drain leakage

- 11. Gate tunneling current

- 12. Parasitic source/drain resistances

- 13. Overlap, inner fringe and outer fringe capacitances

Figure 2.15: Error plot for the transconductance using TCAD as a reference

- 14. Impact ionization current

- 15. Temperature effects and self-heating

With these models implemented, BSIM-IMG is able to capture most real device characteristics. Detailed description of these real device effect models are available in the BSIM-MG user's manuals [60, 61] and two book chapters [62, 52].

The full BSIM-MG models including real device effects are validated by performing global extraction on measured data. BSIM-CMG is calibrated to measured FinFET data [63, 64] and BSIM-IMG is calibrated to an ETSOI technology [65] through an internship.

#### 2.6 Model Convergence

To use a compact model in practical circuit simulation applications, its convergence property is essential. We have tested the convergence of the BSIM-IMG Verilog-A model in a circuit consisting of ten 101-stage ring oscillators. The ring oscillators are coupled together by  $1k\Omega$  resistors, forming a circuit with a total of 2,020 transistors. Both DC and transient simulations are performed in HSpice [66] with its internal Verilog-A compiler. No convergence issue is observed.

Figure 2.16: Error plot for transconductance efficiency,  $g_m/I_d$  using TCAD as a reference.

Figure 2.17: Error plot for drain current at different doping levels.

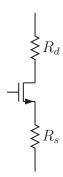

Figure 2.18: (a) Simulation setup for the Gummel symmetry test [27]. (b)  $3^{rd}$  derivative of  $I_x$  with respect to  $V_x$ . (c)(d)  $3^{rd}$  derivative of  $\delta_{cg}$  and  $\delta_{csd}$  with respect to  $V_x$ .  $\delta_{cg}$  and  $\delta_{csd}$  are evaluated using the methodology given in [45]. The continuity of curves at  $V_x = 0$  reflexes symmetry. Real device effects are turned on for these tests.

Both BSIM-CMG and BSIM-IMG have been extensively evaluated by the industry for use in future multiple-gate technologies. This ensures the convergence of both models are thoroughly tested.

#### 2.7 Computational Efficiency Study

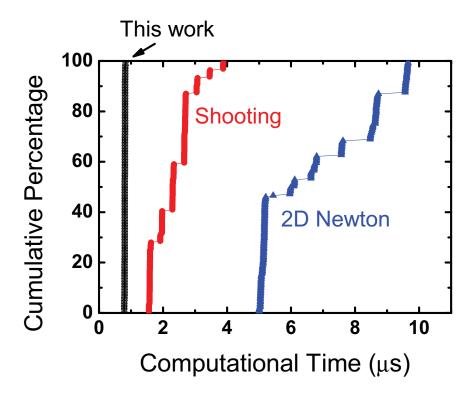

Surface potential based model eliminates the need for empirical smoothing between the weak and strong inversion regions. At the same time, however, the calculation of surface potential itself may be time consuming. In this section, we present a study on the computational time of several numerical methods for multi-gate MOSFET surface potential calculation.

#### 2.7.1 Evaluation Methodology

To evaluate the computation time for a numerical task, we implement it as a function in C language. A piece of time evaluation code calls the function N times. The times at the start and the end of this entire process are recorded and the time difference is divided by N. The result is recorded as  $t_{sample}$ .

$t_{sample}$  evaluated using our method can be expressed as:

$$t_{sample} = \frac{t_{init} + N \cdot (t_{actual} + t_{loop})}{N}$$

(2.30)

where  $t_{init}$  time is the overhead associated with reading the system timer and starting the loop which calls the function N times;  $t_{loop}$  is the overhead associated with the loop control and the function call. By choosing a large N we can eliminate  $t_{init}$ .  $t_{loop}$  can be computed by evaluating an empty function call. The empty function call serves as the control group in this experiment.

In a real computing environment the speed may change depending on the load of the machine, even without other computationally expensive task running. Therefore we measure many samples and take the average. A small standard deviation usually reflexes a stable system condition.

To demonstrate the use of this evaluation methodology, we evaluated the time of several transcendental functions (Table 2.1). The results show that transcendental functions are much more time consuming than floating point division and multiplication <sup>3</sup>. Therefore it is important to reduce the number of transcendental functions used in the compact model. Observe that the computation time of transcendental functions depends on its input parameter. It may also depend on the processor (e.g. whether there is built in instruction sets for trigonometric functions) and the math library used.

<sup>&</sup>lt;sup>3</sup>After examining the assembly code it was found that each multiplication or division instructions are accompanied with two memory operations

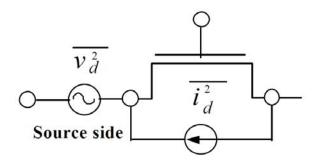

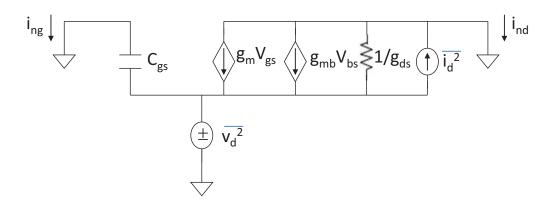

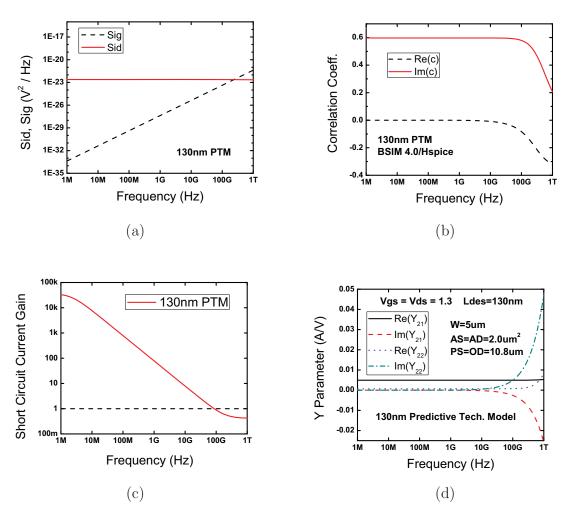

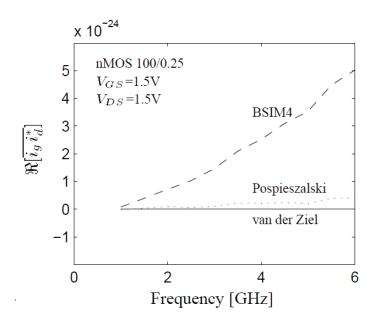

Table 2.1: Computation time evaluation results for transcendental functions ( $N=10^7$ ; 10 samples measured; Processor: Intel Quad Core Xeon CPU 2.9GHz; OS: Linux Kernel 2.6.18 64 bit; C Library: glibc-2.5)