## UC Santa Cruz UC Santa Cruz Previously Published Works

## Title

Silicon microrefrigerator

## Permalink

https://escholarship.org/uc/item/7rc9p03w

### Journal

IEEE Transactions on Components and Packaging Technologies, 29(3)

**ISSN** 1521-3331

### Authors

Zhang, Y Zeng, G H Shakouri, A

## **Publication Date**

2006-09-01

Peer reviewed

# Silicon Microrefrigerator

Yan Zhang, Member, IEEE, Gehong Zeng, and Ali Shakouri, Member, IEEE

Abstract-We fabricated a silicon microrefrigerator on a 500- $\mu$ m-thick substrate with the standard integrated circuit (IC) fabrication process. The cooler achieves a maximum cooling of 1 °C below ambient at room temperature. Simulations show that the cooling power density for a 40 imes 40  $\mu$ m<sup>2</sup> device exceeds 500 W/cm<sup>2</sup>. The unique three-dimensional (3-D) geometry, current and heat spreading, different from conventional onedimensional (1-D) thermoelectric device, contribute to this large cooling power density. A 3-D finite element electrothermal model is used to analyze non-ideal factors inside the device and predict its limits. The simulation results show that in the ideal situation, with low contact resistance, bulk silicon with 3-D geometry could cool  $\sim 20$  °C with a cooling power density of 1000 W/cm<sup>2</sup> despite the low thermoelectric figure-of-merit (ZT) of the material. The large cooling power density is due to the geometry dependent heat and current spreading in the device. The non-uniformity of current and Joule heating inside the substrate also contributes to the maximum cooling of silicon microrefrigerator, exceeding 30% limit given in one-dimensional thermoelectric theory  $\Delta \bar{T}_{max} = 0.5 Z T_c^2$ , where  $T_c$  is the cold side temperature. These devices can be used to remove hot spots on a chip.

*Index Terms*—Cooling, cooling power density, hot-spot cooling, microrefrigerator, silicon, three-dimensional (3-D) microrefrigerator.

#### NOMENCLATURE

| ZT                 | Thermoelectric figure of merit.                 |

|--------------------|-------------------------------------------------|

| S                  | Seebeck coefficient, V/K.                       |

| $S_{\text{metal}}$ | Seebeck coefficient of metal, $\mu$ V/K.        |

| $S_{si}$           | Seebeck coefficient of silicon, $\mu$ V/K.      |

| $\sigma$           | Electrical conductivity, $(\Omega * cm)^{-1}$ . |

| $\kappa$           | Thermal conductivity, W/mK.                     |

| T                  | Temperature, K or °C.                           |

| W                  | Heat flux, W/cm <sup>2</sup> .                  |

| Q                  | Cooling power, W.                               |

| Ι                  | Current sent to the TE elements, mA.            |

| $\Delta V$         | Voltage difference across the device, V.        |

| $\Delta T$         | Temperature difference, K or °C.                |

| R                  | Electrical resistance of the device, $\Omega$ . |

| $\beta$            | Thermal resistance of the device, K/W.          |

| π                  | Peltier coefficient, V.                         |

#### I. INTRODUCTION

CCORDING to the predictions of the ITRS roadmap, microprocessors will have increasing heating problems due to increasing power in the next 10–15 years, e.g., the overall power dissipation for high-performance microprocessors could reach  $\sim$ 300 W [1]. The rising temperature limits device minimization and decreases its lifetime. According to Morrison *et al.* [2], a 10–20 °C temperature increase will double the failure rate, on the other hand 1 °C temperature drop will lower the failure rate by 2%–4%. Thus, temperature control is very important in integrated circuits (ICs). Another characteristic of the chip is uneven temperature distribution, leading to "hot spots." The hot spots are normally on the order of hundreds of microns in diameter with temperatures over 100 °C and a heat flux four to five times more than the chip average value [3], [4]. If these hot spots could be removed, the system's overall thermal design requirements could be alleviated.

The materials thermoelectric cooling capability is usually evaluated by the figure-of-merit, ZT, which has the expression of ZT =  $S^2 \sigma T / \kappa$ , S is the Seebeck coefficient;  $\sigma$  electrical conductivity;  $\kappa$  thermal conductivity; and T, ambient temperature. BiTe has been widely used in the current commercial thermoelectric coolers because its ZT is close to 1, which is the best bulk material that we could find so far. There are still many drawbacks due to low efficiency and low cooling power density [5], [6]. Thus, many researchers are looking for substitutes with a better ZT: Venkatasubramanian et al. reported a ZT of 2.4 for BiTe/SbTe superlattice in 2001 [7]. Harman et al. also showed a prototype of their PbTe quantum dots cooler with ZT of 2.0 in 2002 [8], [9]. We have demonstrated Si/SiGe superlattice microrefrigerators [10]-[12] and SiGeC/Si microrefrigerators in the last couple of years [13]. We have achieved room temperature cooling by more than 4.5 °C and cooling power densities exceeding 500 W/cm<sup>2</sup> [14]. However, bulk silicon has been neglected in the thermoelectric field because of its poor material figure-of-merit, ZT,  $\sim 0.01$ .

On the contrary, silicon has been the heart of microelectronics because of its low cost, availability, and good electrical performance. If silicon can be effectively utilized for spot cooling, this could significantly simplify the thermal design complications. Microrefrigerators could capitalize on a three-dimensional (3-D) device geometry, where current spreading takes heat from one local spot, the device region, into the large substrate. Meanwhile, silicon has a good thermal conductivity,  $\sim$ 125 W/mK, so the heat could be easily spread out. When the local hot spots are removed, the peak temperature of the die drops with very minimal increases of the average temperature. In this case, the device ability to remove hot spots is not limited by its material's ZT.

Let's consider a single element Peltier cooler. In order to understand the physical principle behind the operation of the device, one has to consider two effects. One is called the Peltier effect. When the current goes through a material with two junctions, e.g., metal/semiconductor/metal, one junction cools and the other junction heats up. The Peltier effect occurs because

Manuscript received October 12, 2004; revised November 1, 2005. This work was supported by DARPA HERETIC, Packard Foundation, and Intel Corporation. This work was recommended for publication by Associate Editor T. Lee upon evaluation of the reviewers' comments.

The authors are with the Electrical Engineering Department, University of California, Santa Cruz, CA 95064 USA (e-mail: ali@soe.ucsc.edu).

Color versions of Figs. 1–10 are available online at http://ieeexplore.ieee.org. Digital Object Identifier 10.1109/TCAPT.2006.880508

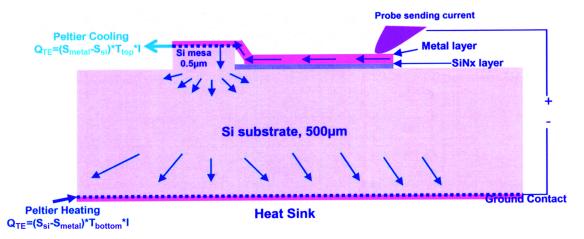

Fig. 1. Schematic of the cross section of a silicon microrefrigerator. The current flow is indicated by the red arrows. The Peltier cooling and heating are generated at interfaces as indicated.

the electric current (I) also drives heat current (Q) in a homogeneous conductor even at constant temperature. The heat current is given by  $Q = \pi I$  [15], [16],  $\pi$  is the Peltier coefficient. The second effect, the Seebeck effect, arises when there is a temperature difference across a material, generating a voltage difference. The Seebeck coefficient (S) is defined as S = dV/dT [15], [16]. The relation of the Peltier coefficient and the Seebeck coefficient could be expressed as  $\pi = ST$ . Thus, the heat current could also be expressed as Q = STI. Normally, the Peltier element is made of semiconductor materials with a certain resistance, which results in Joule heating inside the material as current flows. Thus, when we take heat conduction between hot and cold junctions and Joule heating into consideration, the net cooling power of the Peltier device can be expressed as

$$Q = \text{STI} - \frac{1}{2}I^2R - \beta\Delta T \tag{1}$$

(*R* is the resistance of the device and  $\beta$  is its thermal conductance) [15], [16]. This equation is valid for typical Peltier devices.

As illustrated in Fig. 1, the silicon wafer was etched down 0.5  $\mu$ m to form a mesa, which helps to confine the current and inject electrons perpendicular to the interface. The microrefrigerator works when we send the current from the metallization on the side to the top of the device: Peltier cooling happens at the interface between the top metal and silicon; the Peltier heating happens at the interface between silicon and ground metal contact at the bottom of the substrate as illustrated in Fig. 1. Different from the conventional one-dimensional (1-D) thermoelectric device, the 3-D silicon microrefrigerator removes the heat from a localized top surface and distributes it into a large area in the substrate.

In this paper, we will analyze, theoretically and experimentally, maximum cooling and cooling power density of silicon microrefrigerators, 40 to 75  $\mu$ m in diameter, fabricated on a 500- $\mu$ m-thick substrate. The 3-D finite element electrothermal simulation using ANSYS software is used to analyze the experimental results and investigate the potentials of silicon microrefrigerator. In order to reduce the computation time, we chose a small substrate size of 1250 × 800  $\mu$ m<sup>2</sup> in the simulations. In a typical silicon chip, the silicon substrate size is

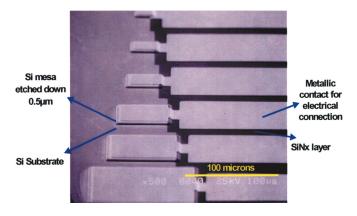

Fig. 2. Scanning electron microscope (SEM) picture of silicon microrefrigerator array, size ranging from  $40 \times 40 \sim 100 \times 100 \ \mu m^2$ .

on the order of  $1 \times 1$  cm<sup>2</sup>. However, experimental results have demonstrated that the size of the substrate does not affect the cooling on top of the device when the substrate is in good contact with the heatsink. The role of parasitic non-ideal effects such as metal-semiconductor contact resistance will be described. A similar enhanced cooling effect was predicted for the 3-D BiTe thermoelectric cooler and the corresponding results are discussed in another publication [17], [18]

#### II. DEVICE FABRICATION

Fig. 2 illustrates an array of silicon microrefrigerators under a scanning electron microscope (SEM). Device sizes range from  $40 \times 40 \sim 100 \times 100 \ \mu \text{m}^2$ . The bulk silicon is *p*-type Boron-doped with a resistivity ranging from  $0.001 \sim 0.006 (\Omega-\text{cm})^{-1}$ . The device was fabricated with the standard dry etching, lithography, and metal evaporation techniques. The mesa was etched down  $\sim 0.5 \ \mu \text{m}$  to confine the current and make sure that electrons are injected perpendicular to metal-semiconductor interface. A Pt/Al/Pt/Au layer with thickness of  $0.1/1.0/0.1/1.5 \ \mu \text{m}$  was deposited as a metal contact. The probe contact area is extended to side to avoid Joule-heating of the probe directly applying to the top of the cooling surface. There is a thin SiN<sub>x</sub> layer underneath the probe contact area to guide the current, without any leaking into substrate until it reaches device region.

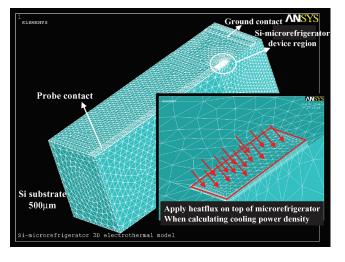

Fig. 3. Three-dimensional electrothermal model of silicon microrefrigerator with meshing.

#### **III. DEVICE MODEL**

We developed a 3-D electrothermal model of the silicon microrefrigerator using finite element analysis ANSYS software, which is powerful in solving coupled-field problems [19]. Fig. 3 shows the device modeled with finite element meshing. Due to the large aspect ratio of the device—the thinnest insulating layer composed of SiN<sub>x</sub> is only 0.3  $\mu$ m compared to the substrate with 500- $\mu$ m thickness—the meshing of this device was very challenging. The element was tetrahedral-shaped with element size ranging from 0.15–50  $\mu$ m depending on the location of the devices, for example, the device region has a much finer meshing than the substrate.

As mentioned earlier, performance of the conventional thermoelectric coolers could be easily modeled by (1). However, in the case of silicon microrefrigerator, the current and heat both spread in 3-D, thus we have to develop a 3-D electrothermal transport model to replace the 1-D balance equation. In the current model, the bulk Joule heating and heat conduction are automatically calculated by solving Fourier heat conduction equation, Poisson equation for electrostatics, and current continuity equation with the defined materials' properties. The heat conduction is described by

$$\rho(\vec{x})c(\vec{x})\frac{\partial T(\vec{x},t)}{\partial t} = H(\vec{x},t) + \nabla_{\vec{x}} \cdot (\lambda(\vec{x})\nabla_{\vec{x}}T(\vec{x},t))$$

where,  $T, H, \rho, c$ , and  $\lambda$  denote temperature, heat generation density, mass density, specific heat, and thermal conductivity, respectively. This study is in steady-state, thus the left part of the equation equals zero. The Poisson equation is represented by

$$\nabla^2 \mu = -\frac{\rho}{\varepsilon}$$

where  $\mu$  is potential,  $\rho$  is charge density, and  $\epsilon$  is permittivity of the material. The current continuity equation for electrons is defined as

$$q\frac{\partial n}{\partial t} = \nabla \cdot \overrightarrow{J} - q(R - G)$$

where q is the electron charge, n is the electron concentration, t is the time,  $\vec{J}$  is the current density, and G, R represents the generation and recombination rates, respectively. A similar equation could be written for holes. Because the ANSYS 8.0 version still doesn't have the thermoelectric element, a self-consistent subroutine was used to calculate the temperature at the microre-frigerator surface. The Peltier effect is modeled as an interface cooling/heating source at the designated interfaces, as illustrated in Fig. 1. The accuracy of the program has been verified with the cooling of commercial BiTe thermoelectric elements compared to the manufacturer data [17]. Furthermore, for the silicon micro refrigerator, the calculated cooling is also compared with the experimental measured values for various device sizes.

In calculation of microrefrigerator cooling versus supplied current, we define the boundary condition as follows. Heat sink temperature is fixed at the bottom of the substrate, 25 °C; and the whole device is placed in an adiabatic environment, no convection applied to all surface. One of the main non-ideal factors of the device is the electrical contact resistance between metal and semiconductor layer. The Joule-heating generated by this contact resistance is happening where thermoelectric cooling is generated. Thus, it is one of the key limiting factors. The metal/semiconductor contact resistance was experimentally characterized by the transmission line measurement (TLM) method and a value of  $\sim 2 \times 10^{-6} \Omega$ -cm<sup>2</sup> was obtained. This contact resistance was added as a surface heating effect in the model.

The heat balance equation for a thermoelectric cooler can be represented by

$$Q_c = STI - 0.5I^2 R_e - \frac{\Delta T}{R_{th}}$$

$(Q_c \text{ is the cooling power; } S \text{ is the Seebeck coefficient; } T \text{ is the}$ cold side temperature; I is the supplied current;  $R_e$  is the electrical resistance;  $\Delta T$  is the temperature difference between hot and cold sides; and  $R_{\rm th}$  is the thermal resistance). When there is no heat applied on top of the microrefrigerator,  $Q_c = 0$ , at an optimized current, the microrefrigerator reaches its maximum cooling. If we start to apply heat on top of the microrefrigerator,  $Q_c$  increases and  $\Delta T$  decreases. When  $\Delta T = 0$ , the  $Q_c$ reaches the maximum value, which is defined as the maximum cooling power. Thus, we defined the maximum cooling power as the heat flux that the microrefrigerator could absorb at the point where the maximum cooling equals to zero. The cooling power density (CPD) equals the cooling power divided by the device area. This cooling power density represents the amount of heat that the microrefrigerator could pump assuming that hot spots are right on top of the microrefrigerator. Using this model, we directly apply the heat flux on top of the microrefrigerator in the ANSYS model and find the maximum heat flux for  $\Delta T =$ 0. This is illustrated in the insert of Fig. 3, the enlarged device region.

#### IV. DEVICE COOLING MEASUREMENT

The cooling of the device was measured using an Omega Type E thermocouple with a 50  $\mu$ m tip diameter. We use differential thermocouples to measure the temperature difference:

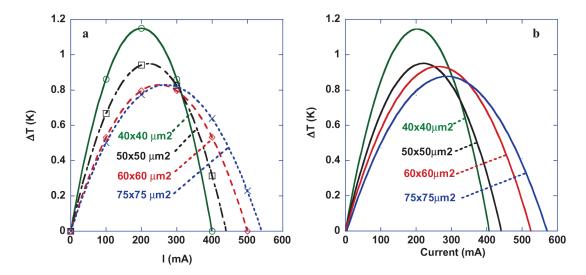

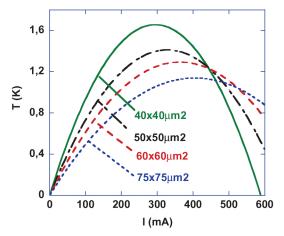

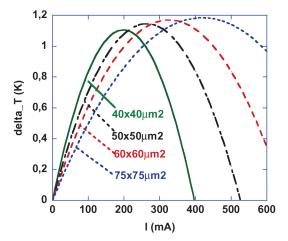

Fig. 4. Experimental measured (a) cooling and (b) simulated cooling versus current for Si-microrefrigerator devices ranging in size from  $40 \times 40 \,\mu$ m<sup>2</sup> to 75 × 75  $\mu$ m<sup>2</sup>.

one thermocouple tip is on top of the device and the other one on the substrate far away from device. We tested temperature variation versus time of this set-up and got a maximum value of +/-0.05 °C. The comparison of thermocouple measurements with the non-contact optical measurement technique was described in an earlier study [20]. Thermocouple data is accurate within  $\sim 0.1$  °C. Even though the thermocouple is on the order of the microrefrigerator size, since the cooling power density is very large, heat conduction through thermocouple wires is negligible. The sample was placed on a temperature-controlled stage to keep the substrate temperature constant. Labview was used to control measurement process. A constant current was supplied to the refrigerator stepping from 0 to 500 mA with a step size of 25 mA; the temperature difference was recorded at every step. Thus a plot of the microrefrigerator cooling versus supplied current is obtained.

#### V. COMPARISON OF EXPERIMENTS AND SIMULATIONS

Fig. 4(a) illustrates the experimental measured cooling results of various size silicon microrefrigerators, the maximum of ~ 1.2 °C cooling was measured on 40 × 40  $\mu$ m<sup>2</sup> device and  $\sim 0.80$  °C was measured on the largest device with 75 × 75  $\mu$ m<sup>2</sup> area. Fig. 4(b) is the 3-D electrothermal model simulated results. It includes all the non-ideal effects such as Joule heating at the contact probe and metal-semiconductor contact resistance. The two figures show a good match for all device sizes. The standard deviation of the simulation from the experiments is 0.1 for the smaller device  $(40 \times 40 \ \mu m^2)$  and 0.2 for the larger devices  $(75 \times 75 \ \mu m^2)$ . This variance is mainly due to the Joule heating calculated by the program is very sensitive to the meshing element size. The larger device requires larger supplied current thus has a larger standard deviation. However, all of these results still fit into a tolerable error range, +/-10%. In Table I, we list various materials' properties used in the simulation.

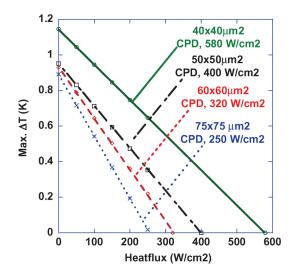

The maximum cooling temperature versus applied heat flux of the device is illustrated in Fig. 5, from which a maximum cooling power density is estimated. Surprisingly, the cooling power density for small devices,  $40 \times 40 \ \mu m^2$ , is about

TABLE I MATERIALS PARAMETERS USED IN Si-MICROREFRIGERATOR 3-D ELETROTHERMAL SIMULATION

| Thermal Conductivity |             |      |              |               |  |  |

|----------------------|-------------|------|--------------|---------------|--|--|

| Unit                 | Metal layer | SiNx | Si Substrate | Contact layer |  |  |

| W/mK                 | 200         | 1    | 125          | 125           |  |  |

| Resistivity          |             |      |              |               |  |  |

| Ohm-cm               | 1.00E-05    | 1000 | 0.003        | 0.066         |  |  |

Fig. 5. Simulated max.  $\Delta T$  versus applied heatflux on top of microrefrigerator. The cooling power density (CPD) for each device is also shown.

580 W/cm<sup>2</sup>, with only about 1. 2 °C cooling; the largest device, 75 × 75  $\mu$ m<sup>2</sup>, also could reach 250 W/cm<sup>2</sup> cooling power density with only 0.8 °C cooling. This is over hundreds times better than what one may estimate based on conventional 1-D thermoelectric theory with a leg thickness of 500  $\mu$ m (substrate thickness). This also compares quite favorably with current commercial thermoelectric coolers which produce only a few W/cm<sup>2</sup> cooling power density [21]. The reported cooling power density for commercial BiTe devices might underestimate the

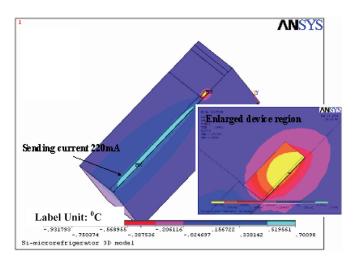

Fig. 6. Simulated temperature profile for  $60 \times 60 \ \mu m^2$  device at a supplied current of 300 mA. The maximum cooling is 0.9 °C.

actual cooling power density that one element TE device could achieve because of the unfilled areas and non-ideal factors. To have a fair comparison of the actual cooling power density of one element TE device with the silicon microrefrigerator, we studied the cooling power density of one BiTe TE element with the same method and presented the results elsewhere [22]. Those studies demonstrated a cooling power density of 93.8 W/cm<sup>2</sup> for a 200- $\mu$ m-thick BiTe TE element (one of the thinnest TE elements found in the market, BiTe materials properties are collected from the Thermion company datasheet) [23]. The simulated results matched well with the reported value by the manufacturer [20]. This also conforms to the conclusion: 3-D silicon microrefrigerator has a higher cooling power density than conventional 1-D devices with the same thickness. The reason for this enhancement involves an interplay of several parameters (heat and current spreading in the substrate, boundary conditions for current and voltage, etc.). We could not derive an analytical solution for these 3-D devices using heat conduction, current continuity, and Poisson equations because of the non-uniform heat and current distribution at the contact area. We believe that we can rely on the finite element analysis to study the spot cooling using silicon material. Our simulation results match very well the experimental cooling for various device sizes. Though the total heat power that these microrefrigerators could remove is only in the order of mW, the target of using this microrefrigerator is to remove the heat generated by a few transistors. To cool a large hot spot, hot spots next to each other, an array of these microrefrigerators could be used.

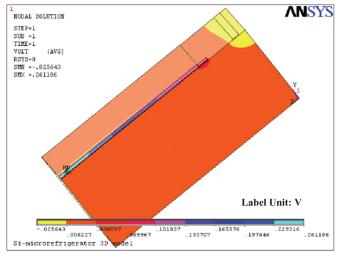

Fig. 6 shows the temperature map for a  $60 \times 60 \ \mu m^2$  device. With 300-mA supplied current, the device shows a localized cooling of 0.9 °C. Fig. 7 illustrates the potential distribution of an operating device. The potential distribution clearly shows the 3-D current spreading. The potential slowly drops along the probe and radically spreads into the substrate. The heat will spread in the same manner as the current.

In the conventional theory of thermoelectric devices, neglecting non-ideal factors, the maximum cooling is geometry independent and it is given by the figure-of-merit,  $\Delta T_{\text{max}} = 0.5\text{ZT}_c^2$ , which is derived from 1-D model. Using

Fig. 7. Potential distribution of an operating device.

Fig. 8. Improved cooling  $\Delta T$  of Si-microrefrigerator with reduced metalsemiconductor contact resistance to 1e-9  $\Omega$ -cm<sup>2</sup>.

Fig. 9. Improved cooling  $\Delta T$  of Si-microrefrigerator with ideal side probe contact (less Joule heating with resistivity of 1e-9  $\Omega$ -cm and very minimum heat conductivity, 0.1 W/mK).

this model, we should expect a maximum cooling of 1.5 °C for bulk silicon. Experimentally, we only observed 1 °C considering all the non-ideal factors: metal-semiconductor contact resistance and probe-Joule-heating propagating to the top of the refrigerator. If fabrication process could be improved by reducing the contact resistance to 1e-9  $\Omega$ -cm<sup>2</sup>, simulations

Fig. 10. Improved cooling  $\Delta T$ : (a) and cooling power densities (CPDs) (b) of Si-microrefrigerator with very low metal-semiconductor contact resistance, 1e-9  $\Omega$ -cm<sup>2</sup> and nearly ideal side probe contact (less Joule heating with resistivity of 1e-9  $\Omega$ -cm and very minimum heat conductivity, 0.1 W/mK).

show that we could improve the  $\Delta T_{\text{max}}$  by 50%. As illustrated in Fig. 8, the improved  $\Delta T_{\rm max}$  ranges from 1.2–1.5 °C for device sizes from 75  $\times$  75  $\mu$ m<sup>2</sup> to 40  $\times$  40  $\mu$ m<sup>2</sup> as compared with the current  $\Delta T_{\text{max}}$  of 0.8–1.1 °C. As mentioned earlier, another non-ideal factor is the Joule heating from the probe as seen in Fig. 6. With 300-mA supplied current, the probe could heat up to 1 °C. Through the 3-D model, we could also analyze "ideal probe contact" scenarios, where the probe has a very small heat conductivity, 0.1 W/mK, and very small electrical resistivity, 1e-9  $\Omega$ -cm. Of course in typical metals thermal conductivity and electrical resistivity are related through the Wiederman-Franz law. The ideal probe contact analysis removes the parasisitic effect of the probe which can be minimized in practice by using much thicker metallic layers and with n- and p-thermoelectric legs electrically in series and thermally in parallel. As illustrated in Fig. 9, with ideal probe contact, the maximum cooling of the larger device can be improved; the 60  $\times$  60  $\mu$ m<sup>2</sup> and 75  $\times$  75  $\mu$ m<sup>2</sup> device almost reached  $\sim 1.2^{\circ}$ C cooling. But improvement is not observed for small devices, like  $40 \times 40 \ \mu m^2$  as compared with the current experimental device. This is because the larger devices require a higher supplied current to reach their  $\Delta T_{\rm max}$ , thus Joule heating from the probe becomes significant. However, for small devices, the maximum cooling occurs at relatively small current,  $\sim 200$  mA. Joule-heating along the probe is negligible at such small currents. When removing both non-ideal factors in Fig. 10(a), we could see the small device,  $40 \times 40 \ \mu m^2$ , improved to cool over 2 °C and the largest device,  $75 \times 75 \ \mu m^2$ could cool  $\sim 1.5^{\circ}$ C. At this ideal situation, we noticed the  $\Delta T_{\rm max}$  of 2 °C, which exceeded predicted  $\Delta T_{\rm max}$  by 0.5ZT<sup>2</sup>, 1.5 °C, for an ideal 1-D bulk silicon material. This contributes from the 3-D geometry, heat, and current spreading effect as well as the current non-uniformity at the contact area [17].

#### VI. CONCLUSION

We have discussed the silicon microrefrigerator's maximum cooling,  $\Delta T$ , and cooling power densities for different device

sizes, ranging from  $40 \times 40 \sim 75 \times 75 \ \mu m^2$ . Experimental results showed that a 3-D geometry-silicon microrefrigerator could cool a maximum of 1.2 °C. Simulations match well with experimental results for various device sizes and predict a cooling power density of 580 W/cm<sup>2</sup>. We used the 3-D electrothermal model to analyze the non-ideal factors of silicon microrefrigerators and predicted the potentials of these devices. It is interesting to note that by removing all non-idealities, the device could reach a maximum of 2 °C cooling exceeding the theoretical limit of 1.5 °C calculated by 0.5 ZT<sub>c</sub><sup>2</sup>, and achieve an estimated cooling power density of 1000 W/cm<sup>2</sup>. All these advantages benefit from the 3-D geometry, current and heat spreading, and current non-uniformities in the device. Silicon microrefrigerators will be useful to remove hot spots from one small area and spread it into the large substrate thus lowering the thermal design requirements for the whole chip. In the application of these 3-D microrefrigerators to hot spot cooling, the thermoelectric figure-of-merit ZT is not the only material parameter that matters. Power factor  $(S^2\sigma)$  and thermal conductivity influence the cooling results differently. Further study of the material optimization will be described in an upcoming paper. [24]

#### REFERENCES

- [1] Sematech, "Heat Dissipation Trend for Microprocessors," ITRS Roadmap, 2001.

- [2] G. N. Morrison, J. M. Kallis, L. A. Strattan, I. R. Jones, and A. L. Lena, "RADC Thermal guide to reliability engineers," Tech. Rep. RADC-TR-82-172, Rome Air Development Center, Air Force Systems Command, Griffith AFB, NY, 1982.

- [3] W. Prasher, "Presence/effect of nonuniform on-chip power distribution," in *Proc. Int. Mech. Eng. Congr. Expo*, New York, Nov. 11–16, 2001, [CD ROM].

- [4] G. M. Chrysler, "Building blocks for thermal management of electronics," in *Proc. Next-Generation Thermal Manag. Mater. Syst.*, Dallas, TX, Oct. 2002, [CD ROM].

- [5] P. E. Phelan, V. A. Chiriac, and T. Y. T. Lee, "Current and future miniature refrigeration cooling technologies for high power microelectronics," *IEEE Trans. Compon. Packag. Technol.*, vol. 25, no. 3, p. 356, Sep. 2002.

- [6] Y. Zhang, J. Christofferson, A. Shakouri, G. Zeng, and J. Bowers, "High speed localized cooling using SiGe superlattice microrefrigerators," in *Proc. 19th Annu. IEEE Semi-Therm*, San Jose, CA, Mar. 2003, p. 61.

- [7] R. Venkatasubramanian, E. Siivola, T. Colpitts, and B. O'Quinn, "Thin-film thermoelectric devices with high room-temperature figures of merit," *Nature*, vol. 413, pp. 597–602, Oct. 11th, 2001.

- [8] T. C. Harman, P. J. Taylor, M. P. Walsh, and B. E. LaForge, "Quantum dot superlattice thermoelectric materials and devices," *Science*, vol. 297, pp. 2229–2232, Sep. 27, 2002.

- [9] T. C. Harman, P. J. Taylor, D. L. Spears, and M. P. Walsh, "Thermoelectric quantum-dot superlattices with high ZT," *J. Electron. Mater.*, vol. 29, no. 1, p. L1, 2000.

- [10] X. Fan, G. Zeng, C. LaBounty, E. Croke, D. Vashaee, A. Shakouri, C. Ahn, and J. E. Bowers, "High cooling power density SiGe/Si micro coolers," *Electron. Lett.*, vol. 37, no. 2, Jan. 18, 2001.

- [11] X. Fan, G. Zeng, E. Croke, G. Robinson, C. LaBounty, A. Shakouri, and J. E. Bowers, "SiGe/Si superlattice coolers," *Phys. Low-Dimen. Struct.*, no. 5–6, p. 1, 2000.

- [12] G. Zeng, A. Shakouri, C. L. Bounty, G. Robinson, E. Croke, P. Abraham, X. Fan, H. Reese, and H. Bowers, "SiGe micro-cooler," *J. E. Electron. Lett.*, vol. 35, no. 24, p. 2146, Nov. 25, 1999.

- [13] X. Fan, G. Zeng, E. Croke, C. LaBounty, C. C. Ahn, A. Shakouri, and J. E. Bowers, "Integrated SiGeC/Si micro cooler," *Appl. Phys. Lett.*, vol. 78, no. 11, Mar. 12, 2001.

- [14] G. Zeng, X. Fan, C. LaBounty, E. Croke, Y. Zhang, J. Christofferson, D. Vashaee, A. Shakouri, and J. Bowers, "Cooling power density of SiGe/Si superlattice micro-refrigerators," in *Proc. Symp. Mater. Res. Soc.*, Boston, MA, Dec. 2003, pp. S2.2.1–S2.2.7.

- [15] H. J. Godsmid, "Electronic Refrigeration," Tech. Rep., Pion, Ltd., 1986.

- [16] D. M. Rowe, CRC Handbook of Thermoelectrics. New York: CRC, 1995.

- [17] Y. Zhang and A. Shakouri, "Three-dimensional high cooling power density thermoelectric coolers," in *Proc. 23rd Int. Conf. Thermoelect.*, Adelaide, Australia, Jul. 25–29, 2004, [CD ROM].

- [18] Y. Zhang, Z. Bian, and A. Shakouri, "Improved maximum cooling by optimizing the geometry of thermoelectric leg elements," in *Proc. 24th Int. Conf. Thermoelect.*, Clemson, SC, Jun. 19–23, 2005, pp. 248–251.

- [19] ANSYS, Inc., "ANSYS Release 7.0," Tech. Rep., Canonsburg, PA, 2003.

- [20] J. Christofferson, D. Vashaee, A. Shakouri, and P. Melese, "High resolution noncontact thermal characterization of semiconductor devices," in *Proc. SPIE—Int. Soc. Opt. Eng.*, vol. 4275, San Jose, Ca, Jan. 20–26, 2001, pp. 119–125.

- [21] P. E. Phelan, V. A. Chiriac, and T. Y. T. Lee, "Current and future miniature refrigeration cooling technologies for high power microelectronics," *IEEE Trans. Compon. Packag. Technol.*, vol. 25, no. 3, p. 356, Sep. 2002.

- [22] Y. Zhang, G. Zeng, and A. Shakouri, "High power density spot cooling with bulk thermoelectrics," *Appl. Phys. Lett.*, vol. 85, no. 14, p. 2977, 2004.

- [23] V. Semenyuk, "Thermoelectric micro modules for spot cooling of high density heat sources," in *Proc. 20th Int. Conf. Thermoelect.*, Beijing, China, Jun. 8–11, 2001, pp. 391–396.

- [24] Y. Zhang, G. Zeng, A. Bar-Cohen, and A. Shakouri, "Is ZT the main performance factor for hot spot cooling using 3-D microrefrigerators?," in *Proc. IMAPS'05*, Palo Alto, CA, Oct. 24–26, 2005.

**Yan Zhang** (M'01) received the B.S. degree from Shanghai University, Shanghai, China, in 1997, the M.Sc degree from the National University of Singapore in 2000, and the Ph.D degree from the Electrical Engineering Department, University of California, Santa Cruz.

Her current research is on nano-scale heat and current transport in semiconductor devices, microrefrigerator for on-chip cooling solution, and thermionic energy conversion for waste heat recovery.

**Gehong Zeng** received the B.S. degree from the South China Institute of Technology, Guangzhou, China, in 1982 and the M.S. and Ph.D. degrees from Shaanxi Microelectronics Research Institute, Xi'an, China, in 1987 and 1992, respectively.

He was with the Kunming Institute of Physics, Kunming, China, working on infrared detectors and imagers. His research interests include design, fabrication, and testing of optoelectronic devices.

**Ali Shakouri** (M'98) received the M.S. degree from Ecole Nationale Superieure des Telecommunications de Paris, Paris, France, in 1990 and the Ph.D. degree from the California Institute of Technology, Pasadena, in 1995.

He is is an Associate Professor of electrical engineering with the University of California, Santa Cruz. His current research is on nanoscale heat and current transport in semiconductor devices, submicron thermal imaging, micro refrigerators on a chip and novel optoelectronic integrated circuits. He is the Director of the Thermionic Energy Conversion Center (a multi university research initiative aiming to improve direct thermal to electric energy conversion technologies).

Dr. Shakouri received the Packard Fellowship in 1999 and the NSF Career Award in 2000.