## UC San Diego UC San Diego Electronic Theses and Dissertations

## Title

Variability assessment and mitigation in advanced VLSI manufacturing through designmanufacturing co-optimization

**Permalink** https://escholarship.org/uc/item/7s97613n

Author Jeong, Kwangok

**Publication Date** 2011

Peer reviewed|Thesis/dissertation

#### UNIVERSITY OF CALIFORNIA, SAN DIEGO

#### Variability Assessment and Mitigation in Advanced VLSI Manufacturing Through Design-Manufacturing Co-Optimization

A dissertation submitted in partial satisfaction of the requirements for the degree Doctor of Philosophy

in

Electrical Engineering (Computer Engineering)

by

Kwangok Jeong

Committee in charge:

Professor Andrew B. Kahng, Chair Professor Chung-Kuan Cheng Professor Larry Larson Professor Lawrence Saul Professor Yuan Taur

2011

Copyright Kwangok Jeong, 2011 All rights reserved. The dissertation of Kwangok Jeong is approved, and it is acceptable in quality and form for publication on microfilm and electronically:

Chair

University of California, San Diego

2011

#### DEDICATION

- To my loving parents, without whose love and encouragement this thesis would not have started.

- To my wife, Sumi, without whose love and sacrifice this thesis would not have finished.

- To my son, Hoejin, for always being there smiling even though I could not always take care of him.

## TABLE OF CONTENTS

| Signature Pag   | e                         | iii                                                                                                                                                                                                                                                     |

|-----------------|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Dedication .    |                           | iv                                                                                                                                                                                                                                                      |

| Table of Conte  | ents .                    | v                                                                                                                                                                                                                                                       |

| List of Figures | s                         | vi                                                                                                                                                                                                                                                      |

| List of Tables  |                           | vii                                                                                                                                                                                                                                                     |

| Acknowledgm     | nents .                   | viii                                                                                                                                                                                                                                                    |

| Vita            |                           | xiii                                                                                                                                                                                                                                                    |

| Abstract of the | e Diss                    | ertation                                                                                                                                                                                                                                                |

| Chapter 1       | Intro<br>1.1              | duction       1         Traditional Design and Manufacturing                                                                                                                                                                                            |

|                 | 1.2                       | Optimization Techniques21.1.1Manufacturing-Side Approaches21.1.2Design-Side Approaches9Problems: Left and Emerging on the Table12                                                                                                                       |

| ~               | 1.3                       | This Thesis         18           0.7         17                                                                                                                                                                                                         |

| Chapter 2       | Impa<br>2.1<br>2.2<br>2.3 | act of Guardband Reduction25Related Literature27Model Guardband Reduction292.2.1Impact of PVT on Circuit Delay292.2.2Liberty Model Scaling332.2.3Interconnect Model Scaling35Analysis Flow and Testcases38                                              |

|                 | 2.4                       | 2.3.1Timing-Driven Implementation Flow382.3.2Testcases and Tools39Analysis on the Impact of Guardband Reduction402.4.1Impact on Quality of Results412.4.2Impact on Critical Paths432.4.3Impact on Design Turnaround Time452.4.4Impact on Design Yield48 |

|                 | 2.5<br>2.6                | Conclusions and Research Directions58Acknowledgments59                                                                                                                                                                                                  |

| Chapter 3          | Variat | ion Modeling                                            | 60  |

|--------------------|--------|---------------------------------------------------------|-----|

|                    | 3.1    | Classification of Variation                             | 60  |

|                    | 3.2    | Previous Approaches to Variation Modeling               | 62  |

|                    |        | 3.2.1 Regression: Closed-Form Modeling                  | 62  |

|                    |        | 3.2.2 Set of Expected Values Modeling                   | 64  |

|                    | -      | 3.2.3 Smoothing: Moving Average versus Meshed Spline .  | 66  |

|                    | ,      | 3.2.4 Hierarchical Decomposition of Variation           | 67  |

|                    | ,      | 3.2.5 Combined Techniques                               | 70  |

|                    | ,      | 3.2.6 Experimental Results                              | 71  |

|                    | 3.3    | Variation Mapping Using Compressed Sensing              | 74  |

|                    |        | 3.3.1 Variation Mapping and Least-Squares               | 76  |

|                    |        | 3.3.2 DCT-Based Compressed Sampling                     | 79  |

|                    |        | 3.3.3 CD Variation Modeling Using Timing Path Delays .  | 82  |

|                    |        | 3.3.4 Other Variation Modeling Applications             | 87  |

|                    |        | 3.3.5 Experiments with Real Design and Libraries        | 91  |

|                    | 3.4    | Conclusions and Research Directions                     | 94  |

|                    | 3.5    | Acknowledgments                                         | 94  |

| Chapter 4          | Variał | bility Assessment in Advanced Lithography               | 95  |

| - · · <b>I</b> · · |        | Double Patterning Lithography (DPL)                     | 96  |

|                    |        | 4.1.1 DPL Options                                       | 96  |

|                    | 4      | 4.1.2 Taxonomy of Sources for Additional Variability in |     |

|                    |        | DPL                                                     | 100 |

|                    | 4.2    | Impact of DPL-Induced BEOL Variation                    | 104 |

|                    | 2      | 4.2.1 TCAD-Based BEOL Analysis                          | 107 |

|                    | 2      | 4.2.2 Signoff Tool-Based Chip-Level BEOL Analysis       | 108 |

|                    | 2      | 4.2.3 Experiments                                       | 111 |

|                    | 4.3    | Impact of DPL-Induced FEOL Variation                    | 125 |

|                    | 4      | 4.3.1 Impact on Coupling Capacitance in FEOL Layers     | 125 |

|                    | 4      | 4.3.2 Impact on Via Resistance Variation                | 127 |

|                    | 4      | 4.3.3 Impact of Bimodal CD Distribution                 | 129 |

|                    | 4.4    | IAL Focus-Exposure Process Window Analysis              | 142 |

|                    | 4      | 4.4.1 Considerations in IAL                             | 143 |

|                    | 2      | 4.4.2 Process Window Analysis                           | 144 |

|                    | 4.5    | Conclusions and Research Directions                     | 146 |

|                    | 4.6    | Acknowledgments                                         | 148 |

| Chapter 5          | Desig  | n-Aware Manufacturing Process Optimization              | 149 |

| -                  | e      | Cost-Driven Reticle Strategy Optimization               | 150 |

|                    |        |                                                         | 151 |

|                    | :      | 5.1.2 Cost Model                                        | 151 |

|                    |        |                                                         | 157 |

|                    |        |                                                         | 161 |

|           |     | 5.1.5 Defect-Aware Parametric Yield for EUVL            | 162 |

|-----------|-----|---------------------------------------------------------|-----|

|           |     | 5.1.6 EUVL Parametric Yield Comparison                  | 169 |

|           | 5.2 | Timing Yield-Aware Dose Map Optimization                | 173 |

|           |     | 5.2.1 Preliminaries of Dose Map Optimization            | 175 |

|           |     | 5.2.2 Problem Formulation of Dose Map Optimization      | 182 |

|           |     | 5.2.3 Timing and Leakage Power Optimization Flow        | 186 |

|           |     | 5.2.4 Experimental Results                              | 190 |

|           | 5.3 | Conclusions and Research Directions                     | 199 |

|           | 5.4 | Acknowledgments                                         | 200 |

| Chapter 6 | Man | nufacturing-Aware Design Optimization                   | 201 |

|           | 6.1 | Dose Map-Aware Placement Optimization                   | 201 |

|           |     | 6.1.1 Dose Map-Aware Placement                          |     |

|           |     | 6.1.2 Cell-Swapping Heuristic                           |     |

|           |     | 6.1.3 Experimental Results                              |     |

|           | 6.2 | Bimodality-Aware Mask Assignment and Detailed Placement |     |

|           |     | for Double Patterning Lithography                       |     |

|           |     | 6.2.1 A New Metric: Coloring Sequence Cost              |     |

|           |     | 6.2.2 Optimal Color Assignment: OPT-COLOR               |     |

|           |     | 6.2.3 Coloring Conflict Removal: DPL-CORR               |     |

|           |     | 6.2.4 Experimental Setup                                |     |

|           |     | 6.2.5 Experimental Results                              |     |

|           | 6.3 | 1-D Gridded Design for IAL                              |     |

|           |     | 6.3.1 Concept of Gridded Design Rule (GDR)              |     |

|           |     | 6.3.2 IAL-Friendly SRAM Bitcell Layout                  |     |

|           |     | 6.3.3 Manufacturability Study                           |     |

|           |     | 6.3.4 Electrical Characteristics                        |     |

|           | 6.4 | Conclusions and Research Directions                     |     |

|           | 6.5 | Acknowledgments                                         | 249 |

| Chapter 7 |     | ign-Manufacturing Co-Optimization                       |     |

|           |     | Introduction                                            |     |

|           | 7.2 | Non-Uniform Gate Model                                  |     |

|           |     | 7.2.1 Superellipse                                      |     |

|           |     | 7.2.2 Capacitance Model                                 |     |

|           |     | 7.2.3 $I_{on}$ Model                                    |     |

|           |     | 7.2.4 $I_{off}$ Model                                   |     |

|           |     | 7.2.5 Overlay Error Model                               |     |

|           | 7.3 | Electrical Assessment of Line-End Shapes                |     |

|           |     | 7.3.1 Model Accuracy                                    |     |

|           |     | 7.3.2 Evaluation of Line-End Shapes                     | 262 |

|           | 7.4 | Tradeoff: Design Rule versus Manufacturing Cost versus  | ~   |

|           |     | Electrical Characteristics                              | 266 |

|              | 7.4.1 Co-Optimization 1: Area versus Leakage Tradeoff . 266 |

|--------------|-------------------------------------------------------------|

|              | 7.4.2 Co-Optimization 2: Design-Rule versus OPC/Litho       |

|              | Cost versus Leakage Tradeoff                                |

|              | 7.5 Conclusions and Research Directions                     |

|              | 7.6 Acknowledgments                                         |

| Chapter 8    | Conclusions                                                 |

| Bibliography |                                                             |

### LIST OF FIGURES

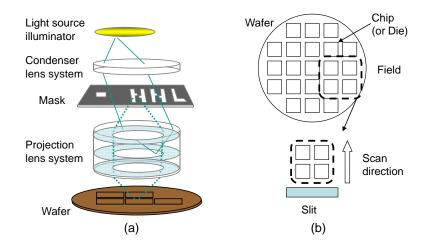

| Figure 1.1:  | Schematic of photolithography system: (a) a step-and-scan system                |    |

|--------------|---------------------------------------------------------------------------------|----|

|              | and (b) exposure field scanned by slit                                          | 3  |

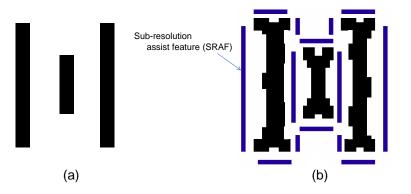

| Figure 1.2:  | Examples of resolution enhancement techniques: (a) drawn layout                 |    |

|              | and (b) mask patterns after OPC and SRAF insertion                              | 5  |

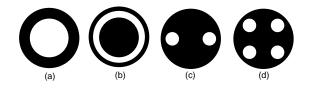

| Figure 1.3:  | Examples of aperture shapes for OAI: (a) circular, (b) annular, (c)             |    |

|              | dipole and (d) quadrupole apertures                                             | 6  |

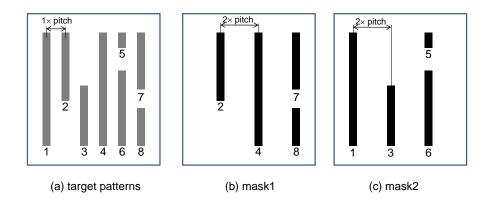

| Figure 1.4:  | DPL partitions target patterns in a critical layer (with $1 \times$ pitch) into |    |

|              | two masks (with $2 \times$ pitch)                                               | 7  |

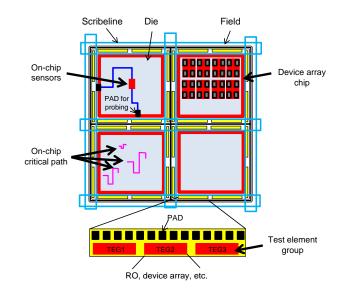

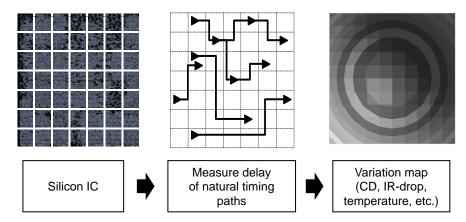

| Figure 1.5:  | Examples of variation measurements.                                             | 13 |

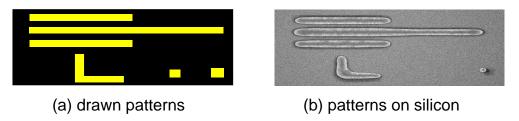

| Figure 1.6:  | Examples of the pattern imperfection. Drawn patterns do not appear              |    |

|              | exactly on silicon.                                                             | 14 |

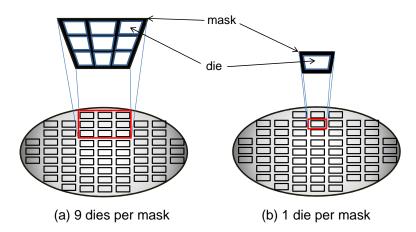

| Figure 1.7:  | A typical large-sized mask (left) and a small-sized mask (right)                | 15 |

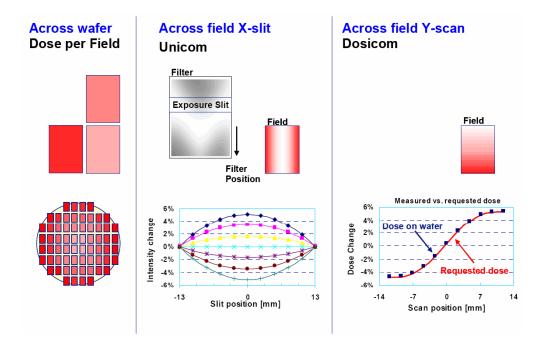

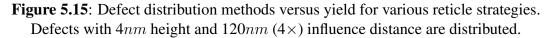

| Figure 1.8:  | Three methods of dose correction using the Dose Mapper. Exposure                |    |

|              | dose can be changed per field to reduce AWLV (left) and can be                  |    |

|              | changed within a field by Unicom (center) and Dosicom (right) to                |    |

|              | reduce ACLV. Figure reproduced from [113]                                       | 16 |

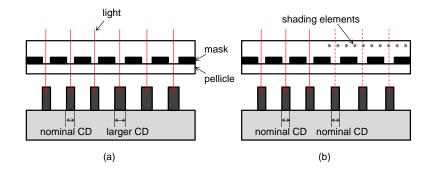

| Figure 1.9:  | An illustration of the Zeiss/Pixer critical dimension control (CDC)             |    |

|              | technique. (a) CD variation with an initial mask. (b) CD correction             |    |

|              | by locally adding shading elements on the mask                                  | 17 |

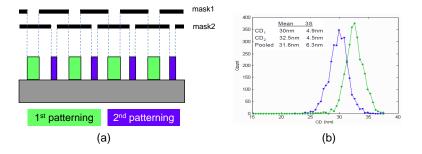

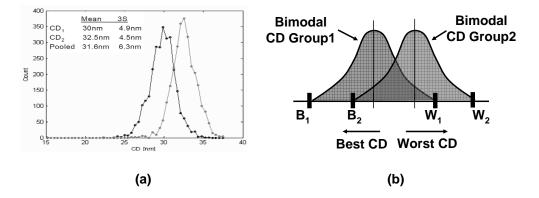

| Figure 1.10: | Two lithography steps result in bimodal CD distribution: (a) CD                 |    |

|              | variation in DPL and (b) bimodal CD distribution (reproduced from               |    |

|              | [64])                                                                           | 17 |

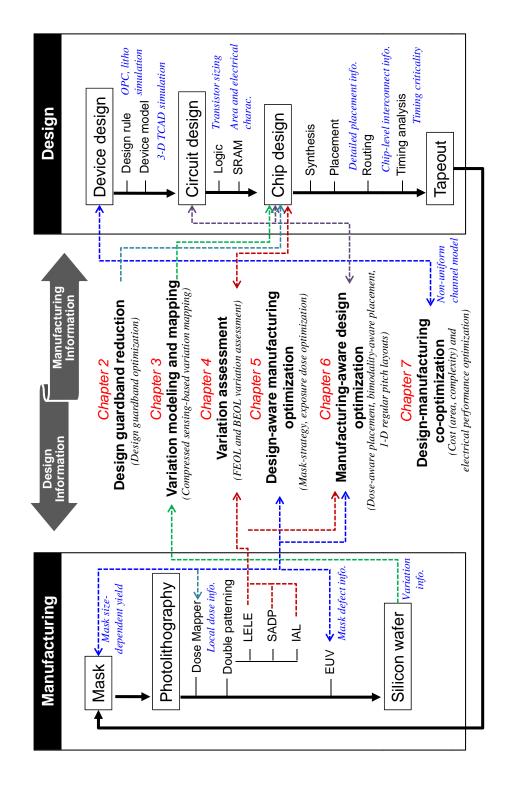

| Figure 1.11: | Scope and organization of this thesis.                                          | 19 |

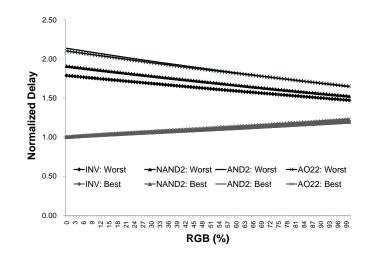

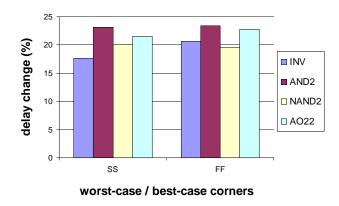

| Figure 2.1:  | Worst-/best-case delay changes of an inverter (INV), a 2-input AND              |    |

| C            | gate (AND2), a 2-input NAND gate (NAND2), and a 2-input AND-                    |    |

|              | OR gate (AO22) versus the process guardband.                                    | 31 |

| Figure 2.2:  | Worst-/best-case delay change percentage across 0%-100% RGB.                    | 32 |

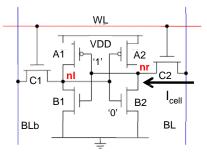

| Figure 2.3:  | Schematic circuit diagram for a 6-T SRAM bitcell.                               | 32 |

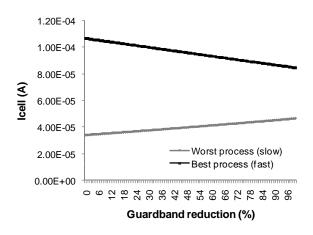

| Figure 2.4:  | Worst-/best-case $I_{cell}$ changes of a 65nm SRAM bitcell versus pro-          |    |

| -            | cess guardband                                                                  | 33 |

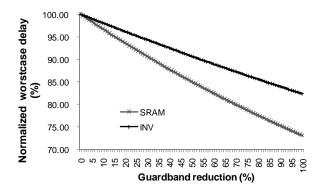

| Figure 2.5:  | Normalized worst-case delay of 65nm inverter (INV) and SRAM                     |    |

|              | bitcell versus process guardband.                                               | 33 |

| Figure 2.6:  | Illustration of steps in guardband reduction for timing tables of the           |    |

|              | Liberty (.lib) files. (a) Original best-/worst-case tables. (b) New             |    |

|              | best-case table with input slew time indices matched up with those              |    |

|              | of the worst-case table. (c) 10% guardband reduction, computed on               |    |

|              | an entry-by-entry basis, across all the table entries                           | 36 |

| Figure 2.7:  | Index matching procedure                                                        | 37 |

| Figure 2.8:  | Guardband reduction procedure                                                   | 37 |

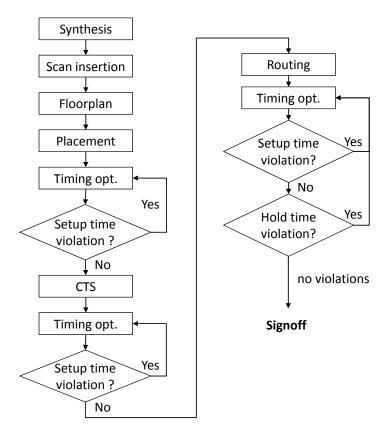

| Figure 2.9:  | Implementation (synthesis, placement and routing) flow.                         | 39 |

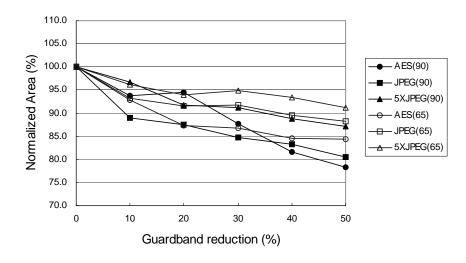

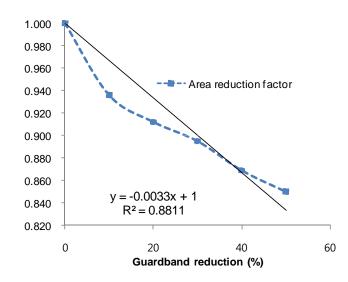

| Figure 2.10: | Area versus guardband reduction.                                                   | 44 |

|--------------|------------------------------------------------------------------------------------|----|

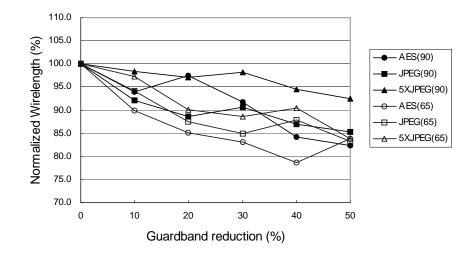

| Figure 2.11: | Total wirelength versus guardband reduction.                                       | 44 |

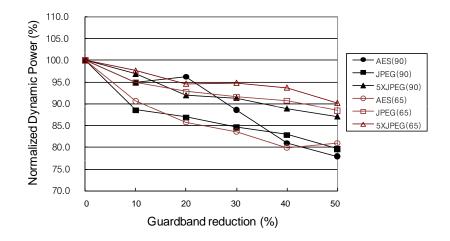

|              | Total dynamic power versus guardband reduction                                     | 45 |

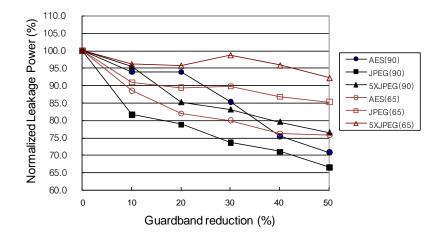

|              | Total leakage power versus guardband reduction.                                    | 45 |

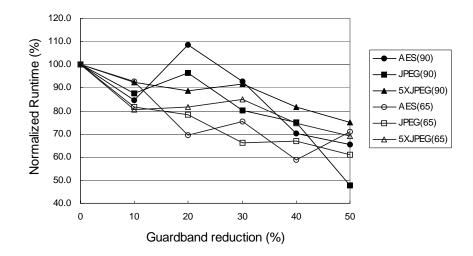

| Figure 2.14: | Guardband reduction versus total SP&R flow runtime.                                | 48 |

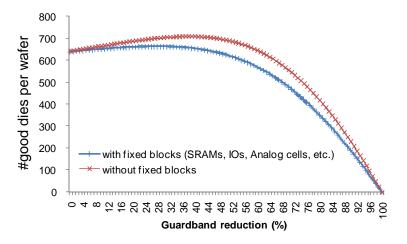

| Figure 2.15: | Change in the number of good dies per wafer, versus guardband                      |    |

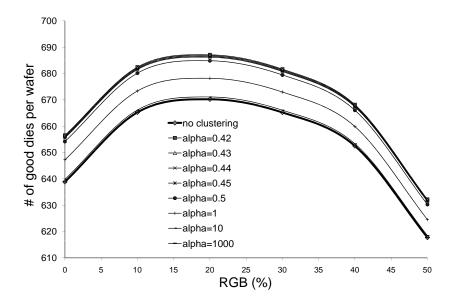

| C            | reduction (%) and defect clustering.                                               | 55 |

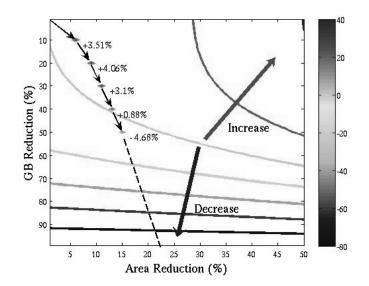

| Figure 2.16: | Change (%) in the number of good dies per wafer, versus guardband                  |    |

| U            | reduction (%) and area reduction (%).                                              | 56 |

| Figure 2.17: | Linear fit for area reduction (%) versus guardband reduction (%).                  | 56 |

| -            | Change in the number of good dies per wafer only for the process                   |    |

| C            | guardband reduction (%)                                                            | 57 |

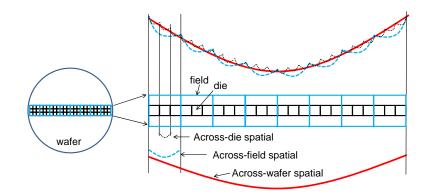

| Figure 3.1:  | Conceptual decomposition of 1-D systematic spatial variations at                   |    |

| I iguie 5.1. | different levels of hierarchy.                                                     | 62 |

| Figure 3.2:  | Original full-wafer CD measurements. Figure reproduced from [65].                  | 68 |

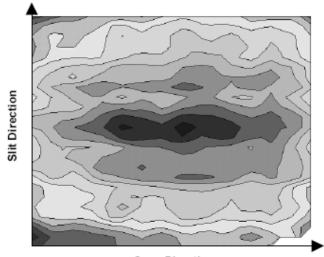

| Figure 3.3:  | Pointwise-averaged variation within a field. Figure reproduced from                | 00 |

| 1 igule 5.5. | [65]                                                                               | 68 |

| Figure 3.4:  | Modeled within-field variation. Figure reproduced from [65].                       | 69 |

| Figure 3.5:  | Full-wafer CD map after average within-die (field) CD fingerprint                  |    |

|              | removed. Figure reproduced from [65]                                               | 69 |

| Figure 3.6:  | Modeled across-wafer variation with die (field) effects removed.                   |    |

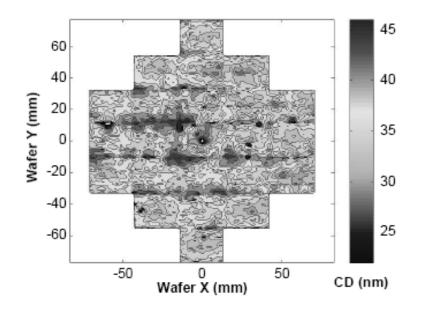

|              | Figure reproduced from [65]                                                        | 70 |

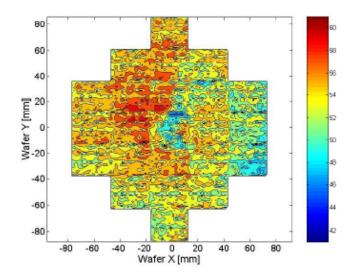

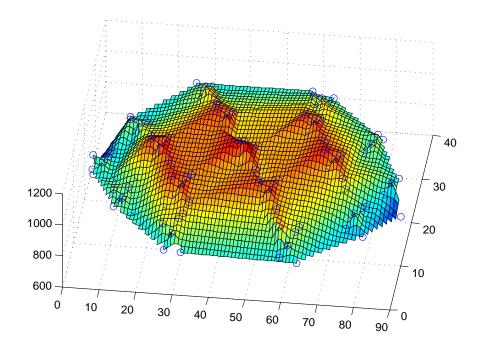

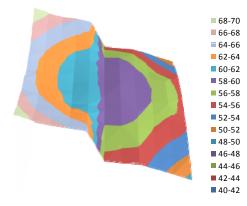

| Figure 3.7:  | A baseline variation map of the measured data in $28nm$ technology,                |    |

|              | constructed from pointwise average for all wafers (i.e., blue circles              |    |

|              | in the figure), followed by an interpolation using Matlab's griddata               |    |

|              | function [12]                                                                      | 71 |

| Figure 3.8:  | Conceptual high-level flow of variation mapping from measured de-                  |    |

| -            | lay of "natural" timing paths to physical parameter variation                      | 75 |

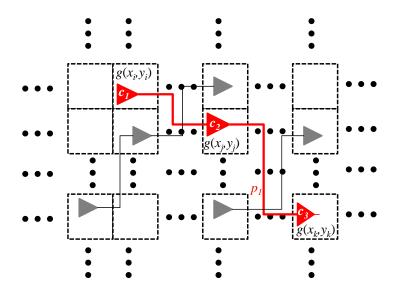

| Figure 3.9:  | Example of natural timing paths in 2-D array. Path $p_1$ consists of               |    |

| C            | three cells $c_1, c_2$ , and $c_3, \ldots, \ldots, \ldots, \ldots, \ldots, \ldots$ | 77 |

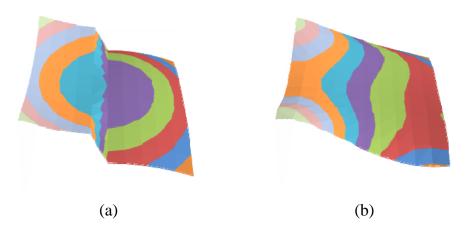

| Figure 3.10: | (a) Example of a complex variation map. (b) Restored variation                     |    |

| U            | map using least-squares regression.                                                | 80 |

| Figure 3.11: | SPICE-calculated delay values versus CD in an inverter implemented                 |    |

| U            | in $65nm$ technology.                                                              | 83 |

| Figure 3.12: | Restored variation map for the complex CD variation shown in Fig-                  |    |

| 0            | ure $3.10(a)$ .                                                                    | 85 |

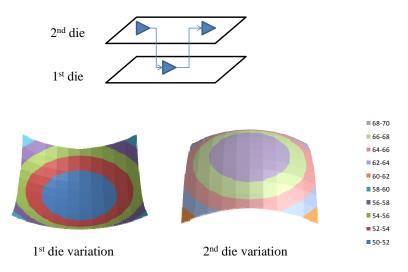

| Figure 3.13: | 3-D stacking with two dies (upper). Second-order CD variation map                  |    |

|              | on an $11 \times 11$ grid is assumed for each die (lower).                         | 88 |

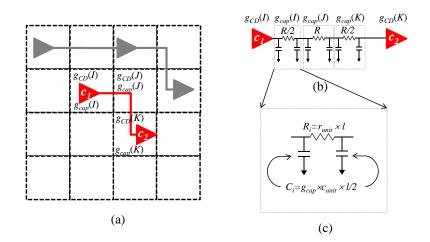

| Figure 3.14: | Interconnect model: (a) a timing path, (b) grid-based segmentation                 | 20 |

|              | of interconnect, and (c) interconnect model for a grid                             | 90 |

|              |                                                                                    | 20 |

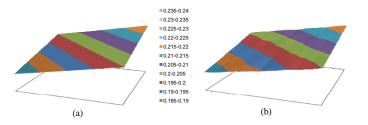

| Figure 3.15: | Given interconnect capacitance variation map in (a) and restored interconnect variation in (b). Minimum and maximum variations from the nominal capacitance of $0.2pF$ are assumed to be -10% at location (1,1) and +10% at location (11,11), respectively                                                                                                                | 91  |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

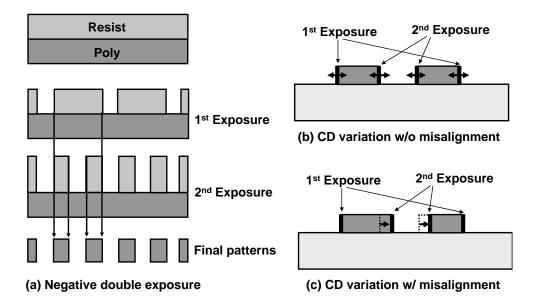

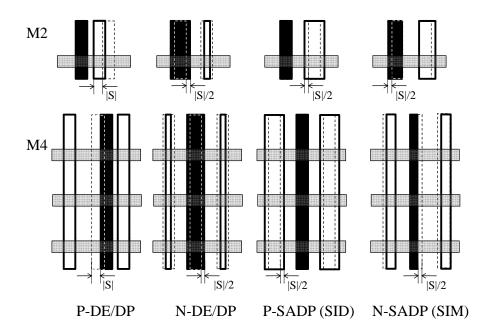

| Figure 4.1:  | An implementation of double exposure (DE) lithography                                                                                                                                                                                                                                                                                                                     | 98  |

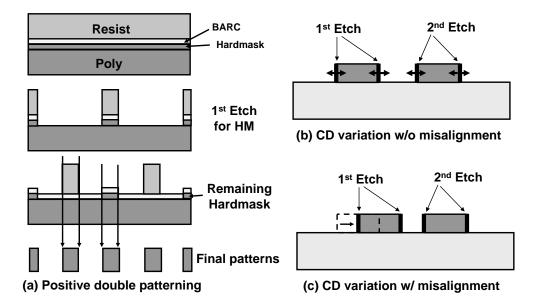

| Figure 4.2:  | An implementation of double patterning (DP) lithography                                                                                                                                                                                                                                                                                                                   | 99  |

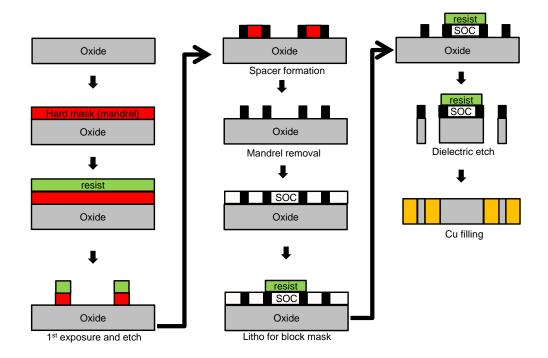

| Figure 4.3:  | An implementation of SID-type SADP.                                                                                                                                                                                                                                                                                                                                       | 100 |

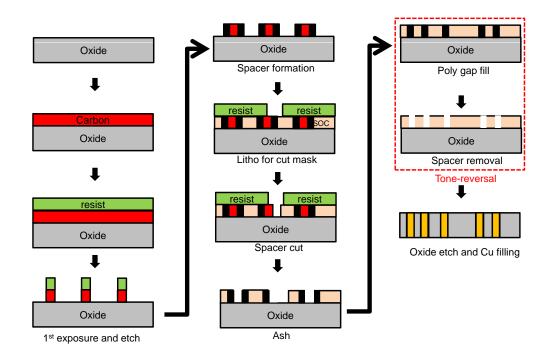

| Figure 4.4:  | An implementation of SIM-type SADP                                                                                                                                                                                                                                                                                                                                        | 101 |

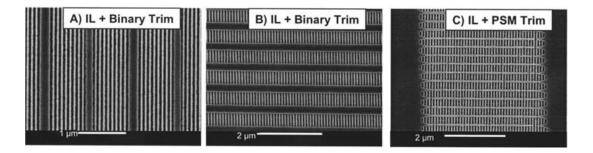

| Figure 4.5:  | Experimental results of a dual-resist IAL reported by Fritze et al. [66].                                                                                                                                                                                                                                                                                                 | 101 |

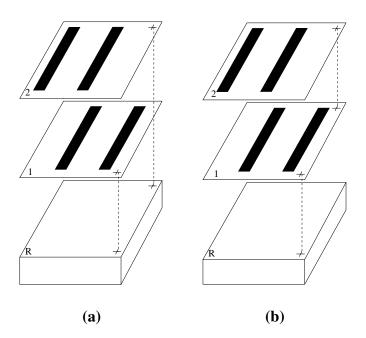

| Figure 4.6:  | Two masks (1 and 2) and a printed reference layer (R). (a) Indirect                                                                                                                                                                                                                                                                                                       |     |

| Eigung 47.   | alignment. (b) Direct alignment.                                                                                                                                                                                                                                                                                                                                          | 103 |

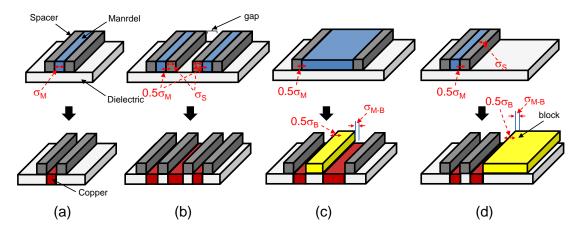

| Figure 4.7:  | A BEOL line in various implementations of SID-type SADP: (a) both line edges are defined by only mandrel edges, (b) both line edges are defined by spacer edges, (c) one line edge is defined by a mandrel edge and the other line edge is defined by a block edge, and (d) one line edge is defined by a spacer edge and the other line edge is defined by a block edge. | 104 |

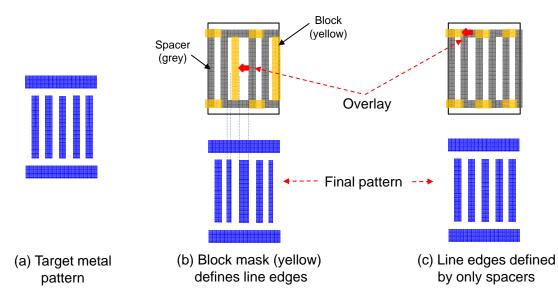

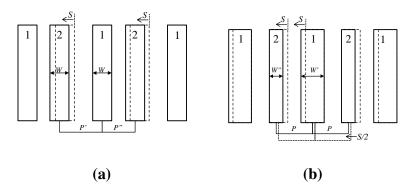

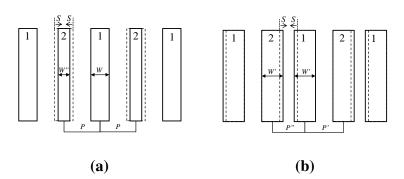

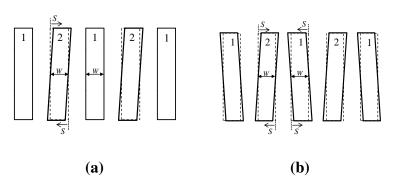

| Figure 4.8:  | Different layout decompositions result in different linewidth varia-<br>tions: (a) a target layout, (b) a layout decomposition solution (top)<br>and resulting final patterns due to overlay (bottom), and (c) another<br>layout decomposition solution (top) and resulting final patterns due<br>to overlay (bottom)                                                     | 106 |

| Figure 4.9:  | (a) P-DE/DP process. Patterns printed using <i>mask2</i> are shifted by $S$ due to overlay, which causes pitch and space variation between patterns ( $P^{"} \leq P \leq P^{"}$ ). (b) N-DE/DP process. Overlay varies linewidth ( $W^{"} \leq W \leq W^{"}$ ), but does not affect pitch and space.                                                                      |     |

| Figure 4.10: | (a) P-SADP process. Patterns printed after spacer formation can differ in width due to spacer thickness variations $S$ ( $W'' \le W$ ). Spacer thickness variation does not affect pitch but varies space.<br>(b) N-SADP process. Linewidth, space and pitch are varied due to spacer thickness variation. ( $P'' \le P \le P'$ and $W \le W'$ .)                         | 109 |

| Figure 4.11: | (a) Rotational overlay due to <i>mask1</i> in DE/DP. (b) Worst-case rotational overlay due to <i>mask1</i> and <i>mask2</i> in different directions                                                                                                                                                                                                                       | 109 |

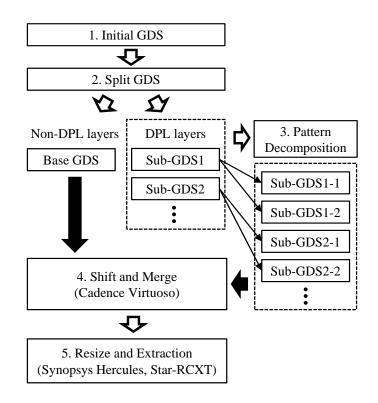

| Figure 4.12: | Extraction flow for double patterning lithography considering over-<br>lay.                                                                                                                                                                                                                                                                                               | 119 |

| Figure 4.13: | Simplified configurations of a net having the largest delay variation due to coupling in the testcase before metal fill.                                                                                                                                                                                                                                                  | 121 |

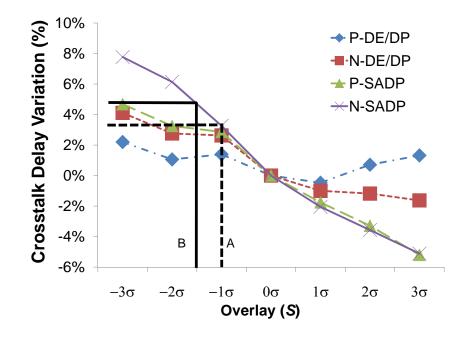

| Figure 4.14: | Coupling-induced delay variation (%) ( $y$ -axis) due to M4 overlay                                                                                                                                                                                                                                                                                                       | 141 |

| -            | ( <i>x</i> -axis)                                                                                                                                                                                                                                                                                                                                                         | 122 |

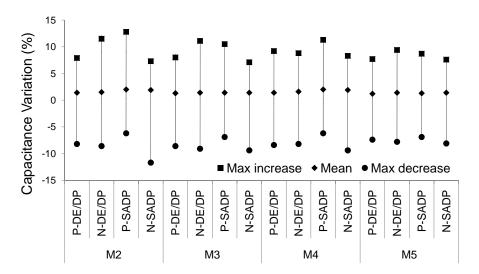

| Figure 4.15: | Capacitance changes (%) of high-capacitance nets ( $\geq 2fF$ ) from $3\sigma$ overlay.                                                                                                                                                                                                                                                                                   | 123 |

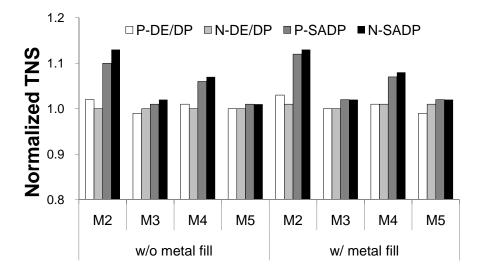

| Figure 4.16:  | Normalized total negative slack (y-axis) due to $3\sigma$ overlay in each                                   | 104 |

|---------------|-------------------------------------------------------------------------------------------------------------|-----|

|               | layer (x-axis) for each double patterning lithography option. $\ldots$                                      | 124 |

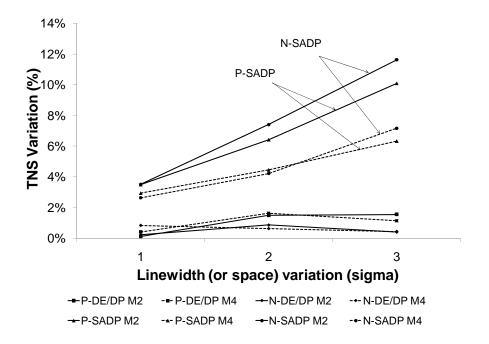

| Figure 4.17:  | Total negative slack variation (%) from the nominal value in each                                           |     |

|               | double patterning lithography option with respect to overlay $S$ vari-                                      |     |

|               | ation                                                                                                       | 125 |

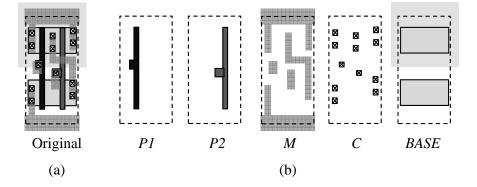

| Figure 4.18:  | Mask decomposition for FEOL overlay simulation. (a) Original                                                |     |

|               | NAND2_X2 layout. (b) Five decomposed sub-layouts                                                            | 127 |

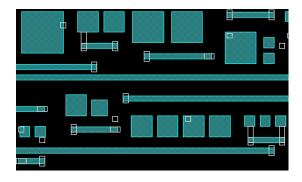

| Figure 4.19:  | Bimodal CD distribution. Left figure reproduced from [64]                                                   | 130 |

| Figure 4.20:  | Example of two different DPL colorings for a NOR3 cell                                                      | 132 |

| Figure 4.21:  | Delay variations of 4-inverter and 4-buffer chains. Path configura-                                         |     |

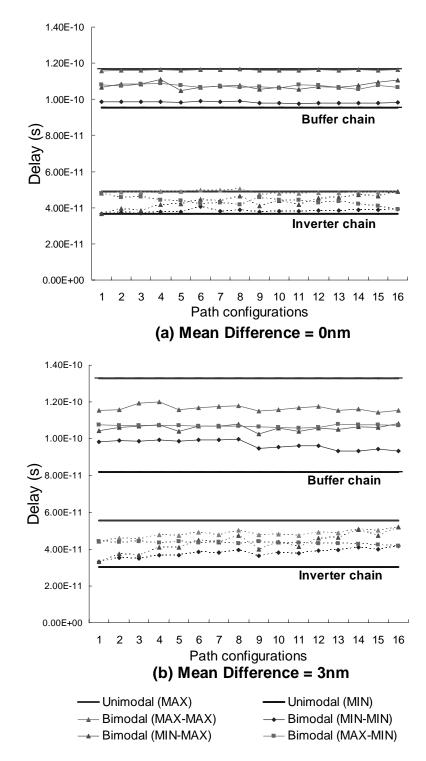

| C             | tions are as given in Table 4.14.                                                                           | 136 |

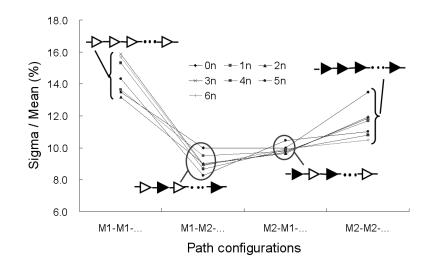

| Figure 4.22:  | Relative delay variation $\sigma/\mu$ (%) over all process corners                                          | 137 |

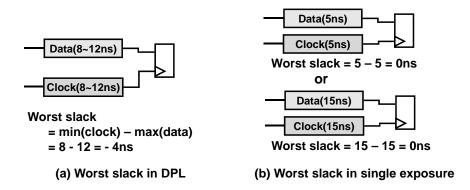

|               | Worst timing-slack calculation in the DPL and (traditional) single-                                         |     |

| 8             | exposure regimes.                                                                                           | 138 |

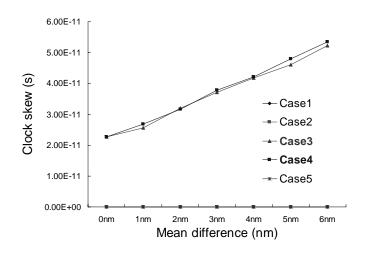

| Figure 4.24:  | Clock skew versus CD mean difference between CD groups, across                                              |     |

| 1.8010        | combinations of process corners. Cases 1, 2 and 5 are superposed                                            |     |

|               | on the $x$ -axis                                                                                            | 140 |

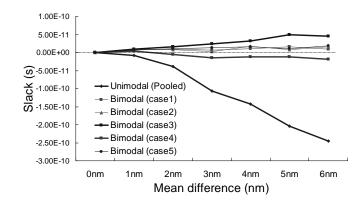

| Figure 4 25.  | Timing slack versus CD mean difference between CD groups across                                             | 110 |

| 1 iguie 1.25. | combinations of process corners                                                                             | 141 |

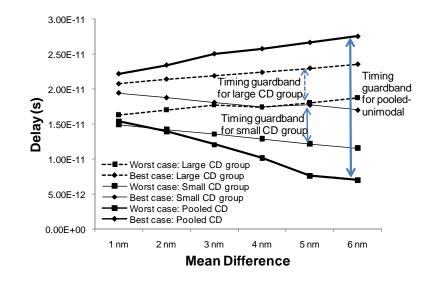

| Figure 4 26.  | Timing guardband for each characterization method.                                                          |     |

| -             | Problems of IAL application due to dummy metal fill.                                                        | 142 |

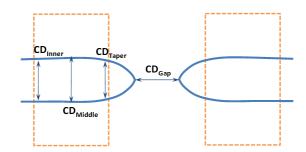

| -             | Lithographic metrics for critical dimension (CD).                                                           | 144 |

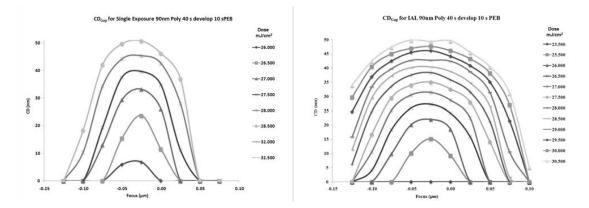

| -             | Focus-exposure simulation results of the reference single exposure                                          | 144 |

| Figure 4.29.  | (left) and IAL (right) for $CD_{Gap}$ .                                                                     | 145 |

| Eiguro 4 20:  | •                                                                                                           | 145 |

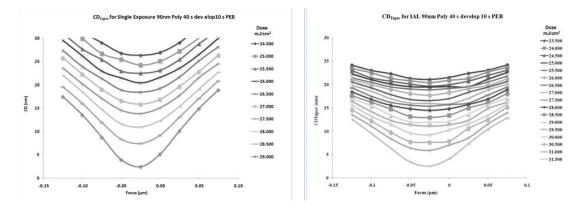

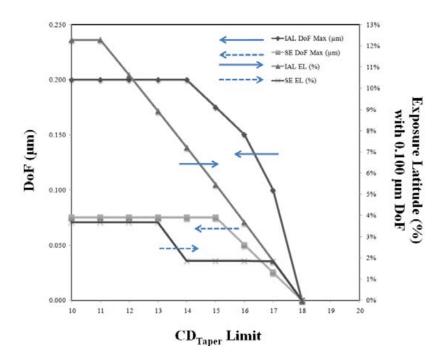

| Figure 4.50.  | Focus-exposure simulation results of the reference single exposure                                          | 145 |

| Eigung 4 21.  | (left) and IAL (right) for $CD_{Taper}$ .                                                                   | 145 |

| Figure 4.51:  | Process window comparison for IAL and single exposure process                                               | 146 |

|               | with respect to the minimum allowable $CD_{Taper}$                                                          | 146 |

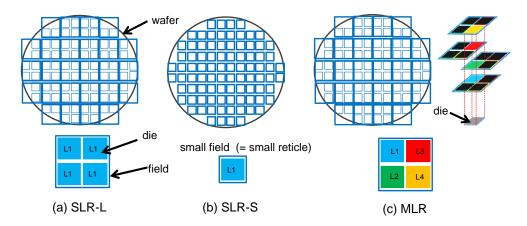

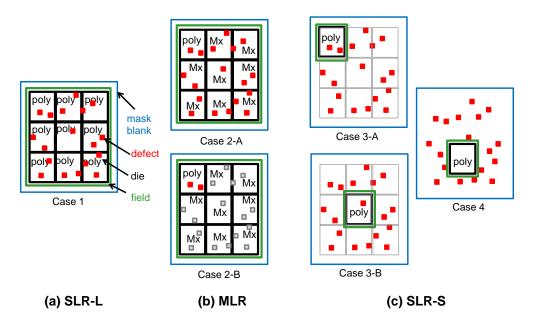

| Figure 5.1:   | Examples of mask strategies: (a) single-layer reticle on a traditional                                      |     |

| 1.8010 0111   | large field, (b) single-layer reticle on a small field, and (c) multi-                                      |     |

|               | layer reticle on a large field.                                                                             | 152 |

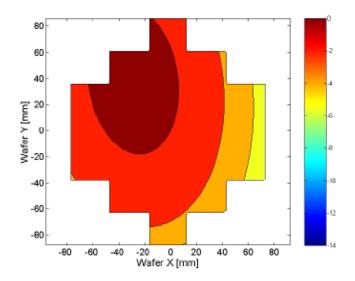

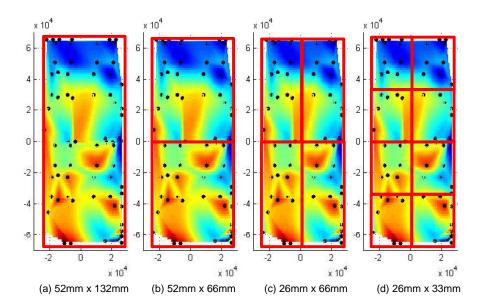

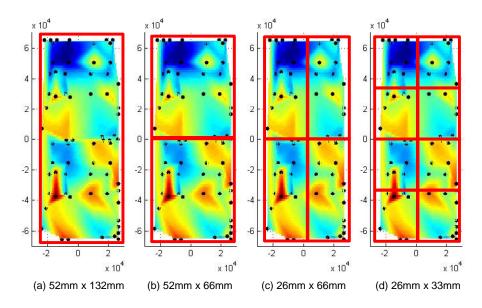

| Figure 5.2:   | Mask CD variation map for a $90nm$ product.                                                                 | 157 |

| Figure 5.3:   | Mask CD variation map for a $65nm$ product.                                                                 | 158 |

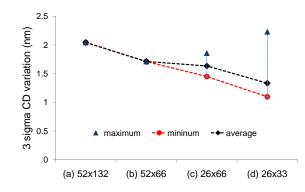

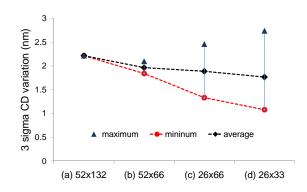

| Figure 5.4:   | $3\sigma$ CD variation ( <i>nm</i> ) versus field size ( <i>mm</i> <sup>2</sup> ) for the 90 <i>nm</i> mask | 150 |

| 1 iguie 5.4.  | CD map in Figure 5.2.                                                                                       | 158 |

| Figure 5.5:   | $3\sigma$ CD variation ( <i>nm</i> ) versus field size ( <i>mm</i> <sup>2</sup> ) for the 65 <i>nm</i> mask | 150 |

| I iguie 5.5.  | CD map in Figure 5.3.                                                                                       | 159 |

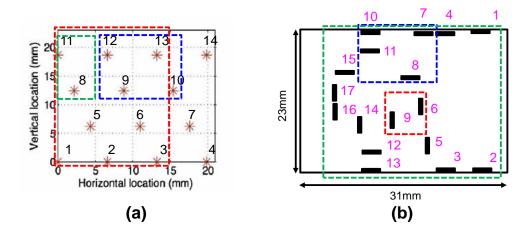

| Figure 5.6:   | Measurement point locations in fields from Foundry A data in (a)                                            | 139 |

| 1 iguie 3.0.  | and Foundry B data in (b)                                                                                   | 150 |

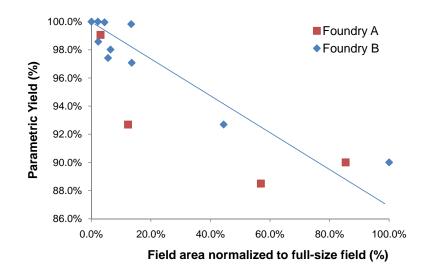

| Figure 57.    | Field size normalized to a full-size field in <i>x</i> -axis, versus parametric                             | 159 |

| Figure 5.7:   | -                                                                                                           | 160 |

|               | yield assuming 90% yield for full-size field in <i>y</i> -axis                                              | 162 |

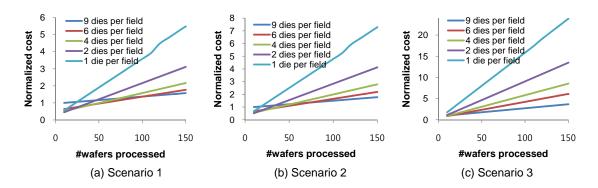

| Figure 5.8:  | Overall manufacturing cost in <i>y</i> -axis versus the number of wafers processed. Cost values are normalized to the cost of processing 10 wafers with a $100 \times 100 mm^2$ field.                                                                                  | 162 |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 5.9:  | Reticle strategies: (a) SLR-L, (b) MLR with same weight for<br>all layers (top) and different weights for different layers (bottom),<br>(c) SLR-S with random location (top-left) and lowest defect<br>location in a gridded mask blank (bottom-left), and with optimal | 162 |

| Eigung 5 10. | location (right)                                                                                                                                                                                                                                                        |     |

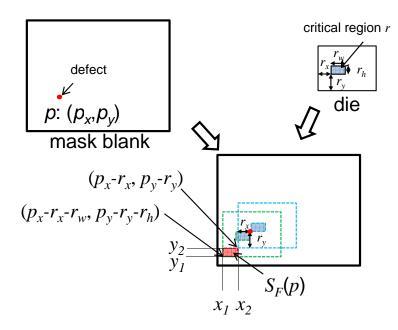

| e            | 6 6                                                                                                                                                                                                                                                                     | 168 |

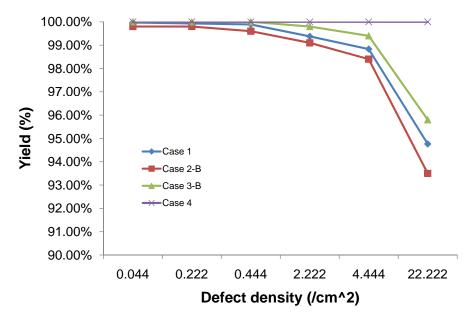

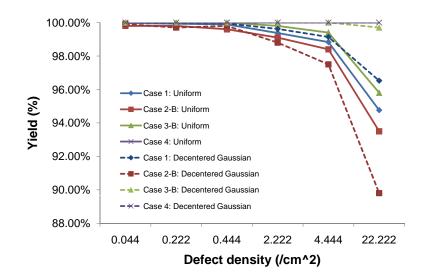

| -            | An example of forbidden region calculation for a single defect Defect density versus yield for various reticle strategies. $4nm$ defect height and $120nm$ (4×) defect influence distance are assumed,                                                                  | 169 |

|              | with defects uniformly distributed.                                                                                                                                                                                                                                     | 170 |

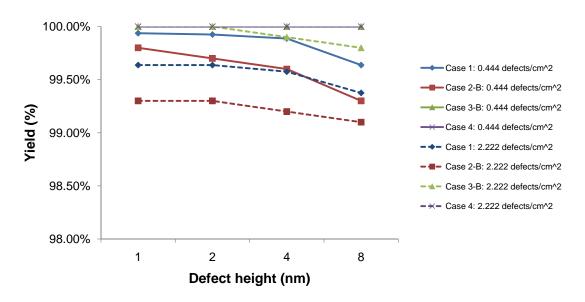

| Figure 5.13: | Defect height versus yield for various reticle strategies. $0.444-2.222$<br>defects/ $cm^2$ defects are uniformly distributed and defect influence                                                                                                                      | 170 |

|              | distance is assumed as $120nm(4\times)$ .                                                                                                                                                                                                                               | 171 |

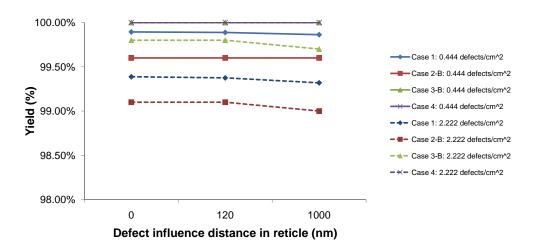

| Figure 5.14: | Defect influence distance versus yield for various reticle strategies.<br>$0.444-2.222$ defects/ $cm^2$ defects with $4nm$ height are uniformly                                                                                                                         |     |

|              | distributed                                                                                                                                                                                                                                                             | 172 |

| Figure 5.15: | Defect distribution methods versus yield for various reticle strate-<br>gies. Defects with $4nm$ height and $120nm$ (4×) influence distance                                                                                                                             |     |

|              | are distributed.                                                                                                                                                                                                                                                        | 173 |

| Figure 5.16: | Unicom and Dosicom, which respectively change dose profiles in slit and scan directions. Figure reproduced from [2]                                                                                                                                                     | 176 |

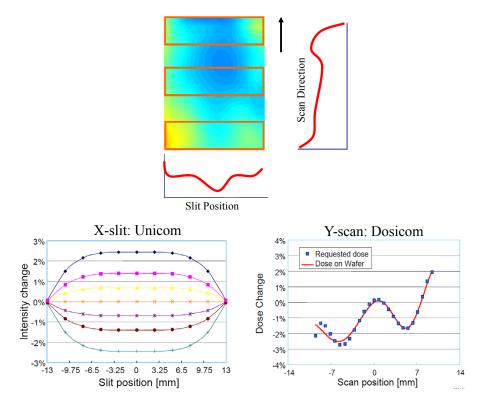

| Figure 5.17: | Dose sensitivity: increasing dose (red color) decreases the CD [1].                                                                                                                                                                                                     | 176 |

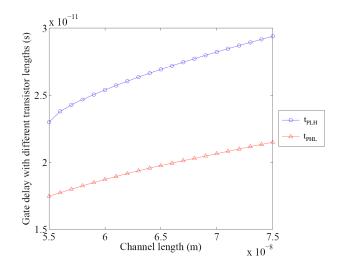

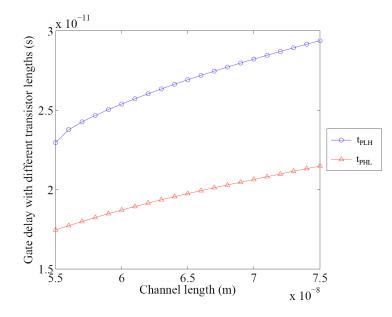

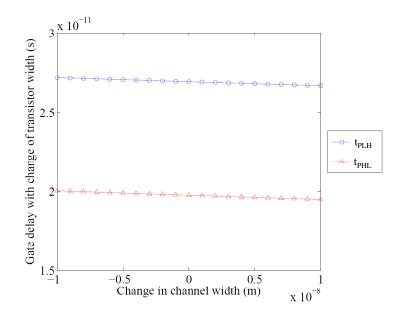

| Figure 5.18: | Delay of an inverter versus gate length                                                                                                                                                                                                                                 | 178 |

| Figure 5.19: | Delay of an inverter versus change in gate width                                                                                                                                                                                                                        | 179 |

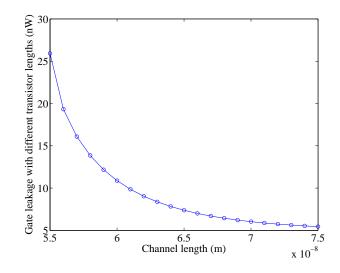

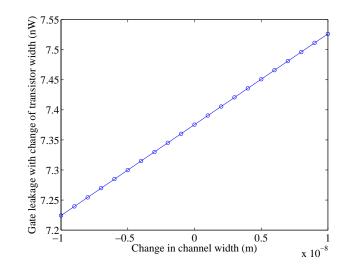

| Figure 5.20: | Average leakage of an inverter (INV_X1) versus gate length (VDD = $1.0V$ , Temperature = $25^{\circ}C$ , Process = TT).                                                                                                                                                 | 180 |

| Figure 5.21: | Average leakage of an inverter (INV_X1) versus the change in gate width (VDD = 1.0V, Temperature = $25^{\circ}C$ , Process = TT)                                                                                                                                        | 181 |

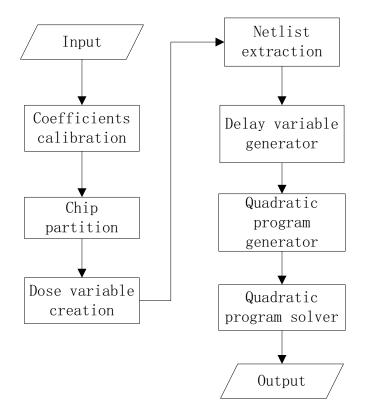

| Figure 5.22: | Flow of the timing and leakage power optimization with integrated <i>DMopt</i> and <i>dosePl</i> (in Section 6.1).                                                                                                                                                      | 187 |

| Figure 5.23: | Detailed view of design-aware dose map optimization flow                                                                                                                                                                                                                | 188 |

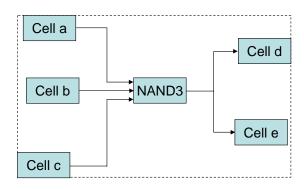

| Figure 6.1:  | Bounding box of a 3-input NAND (NAND3) cell: moving the cell within its bounding box has a lower likelihood of increasing total wirelength.                                                                                                                             | 202 |

| Figure 6.2:  | One round of cell swapping heuristic in <i>dosePl</i>                                                                                                                                                                                                                   | 202 |

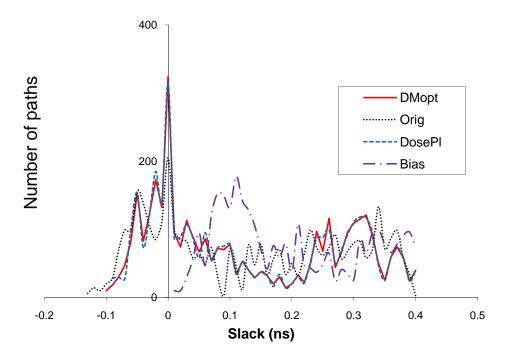

| Figure 6.3:  | Slack profiles of $AES65$ (used in Section 5.2.4) before <i>DMopt</i> , after <i>DMopt</i> , after <i>dosePl</i> , and after biasing where all of the gates in the top 10,000 critical paths receive maximum possible exposure dose (+5%).                              | 207 |

|              |                                                                                                                                                                                                                                                                         |     |

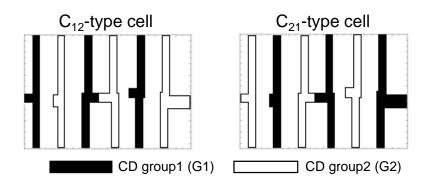

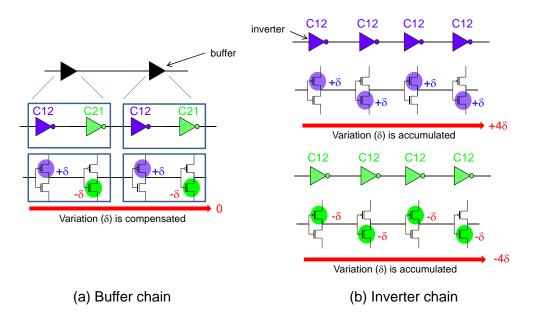

| Figure 6.4:   | Delay variations of timing paths due to bimodal CD distribution                    |     |

|---------------|------------------------------------------------------------------------------------|-----|

|               | in DPL. (a) In a path consisting of only buffers, variation of each                |     |

|               | inverter stage is compensated. (b) In a path consisting of only in-                |     |

|               | verters, variation of each inverter stage accumulates                              | 209 |

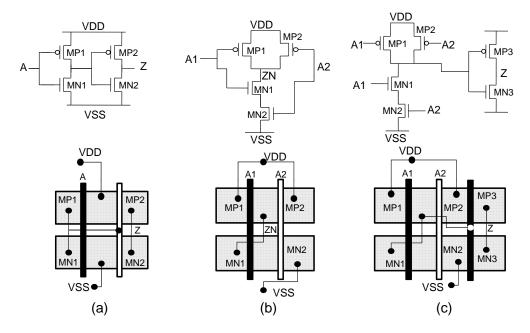

| Figure 6.5:   | Schematic and layout of $C_{12}$ -type (a) BUF, (b) NAND2, and (c)                 |     |

|               | AND2 cells.                                                                        | 210 |

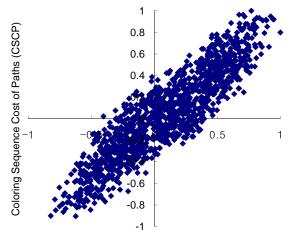

| Figure 6.6:   | Correlation between CSCP and the delay difference between the                      |     |

|               | two bimodal-aware timing libraries G1L-G2S and G1S-G2L, for                        |     |

|               | 1,300 different colorings of the timing path                                       | 213 |

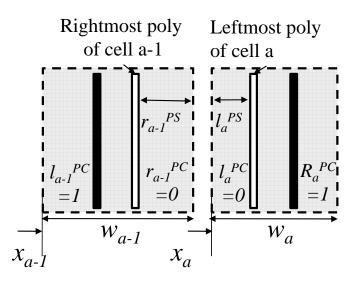

| Figure 6.7:   | Variables used in the DP problem formulation.                                      | 216 |

| Figure 6.8:   | <i>HCost</i> algorithm for coloring-conflict removal                               | 218 |

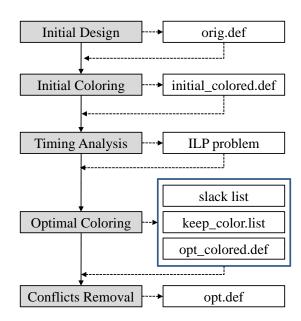

| Figure 6.9:   | Design framework for bimodal-aware timing optimization                             | 224 |

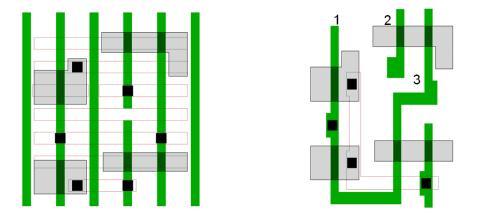

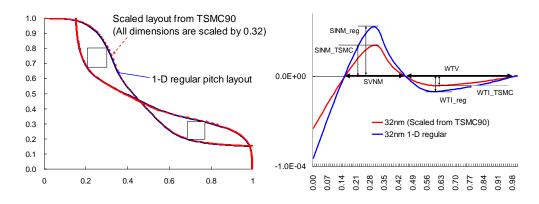

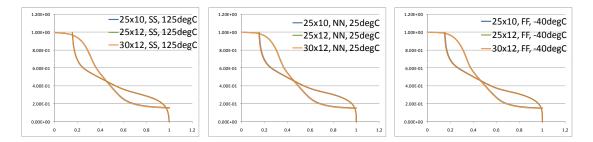

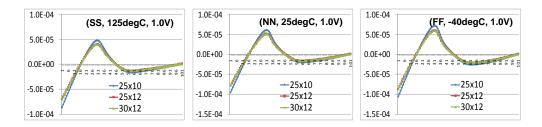

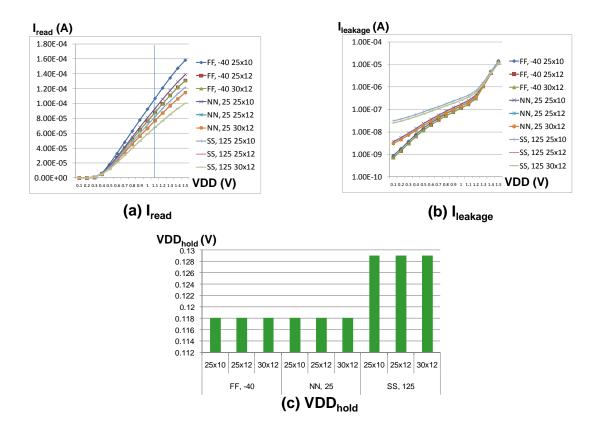

| Figure 6.10:  | 1-D GDR layout (left) compared to 2-D CDR layout (right)                           | 235 |

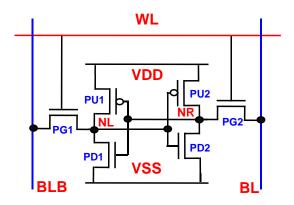

| -             | Schematic of 6-T SRAM bitcell.                                                     | 236 |

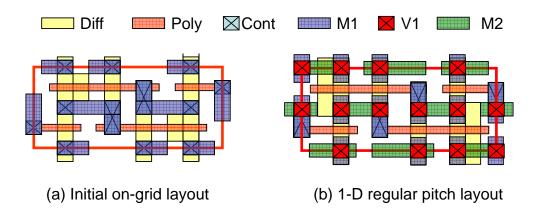

| e             | IAL-friendly bitcell layout.                                                       | 239 |

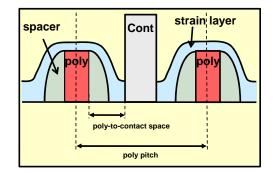

|               | Vertical cut-view of SRAM bitcell.                                                 |     |

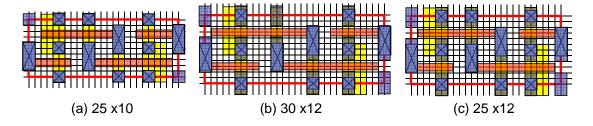

| -             | Three candidate bitcell layouts.                                                   |     |

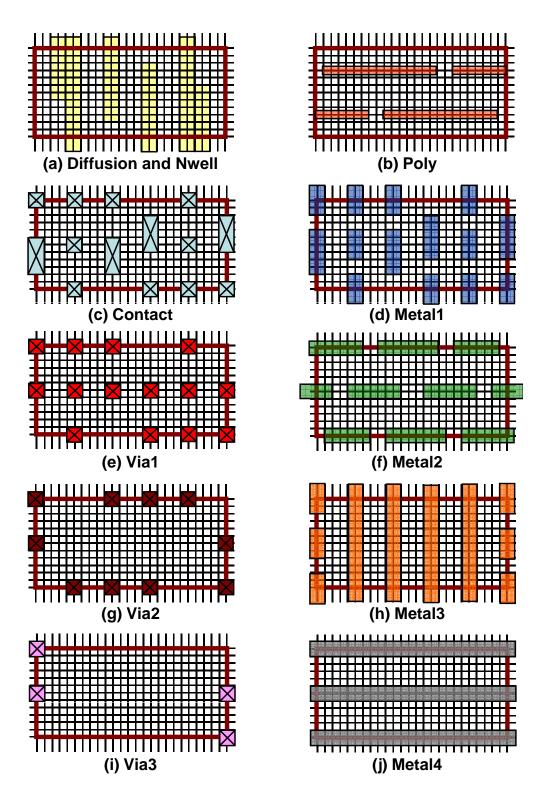

|               | Layout for each layer.                                                             | 242 |

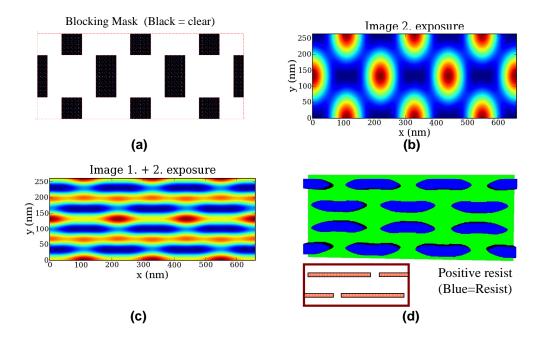

| -             | Lithography simulation results on poly layer using a binary mask.                  |     |

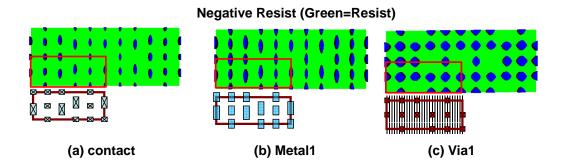

| -             | Resist (negative-tone) patterns for (a) contact layer, (b) M1 layer                |     |

| 1.8010 0111   | using a CPA mask and 2-beam IL, and (c) V1 layer using CPA mask                    |     |

|               | and 4-beam IL.                                                                     | 244 |

| Figure 6 18.  | Butterfly curve and N-curve for the reference and proposed bitcells.               | 245 |

| e             | Butterfly curve comparison at different operating conditions                       | 246 |

| -             | N-curve comparison at different operating conditions.                              | 247 |

|               | $I_{read}$ , $I_{leakage}$ and $VDD_{hold}$ comparison at different operating con- | 271 |

| 1 iguie 0.21. | ditions.                                                                           | 247 |

|               |                                                                                    | 247 |

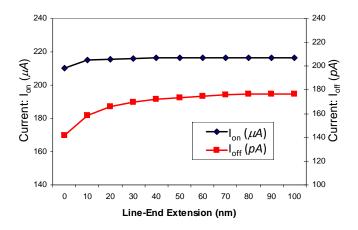

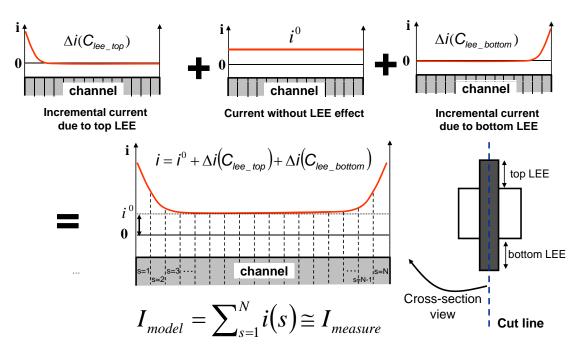

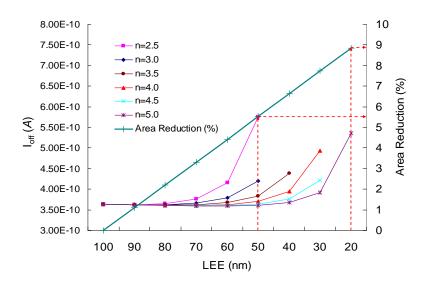

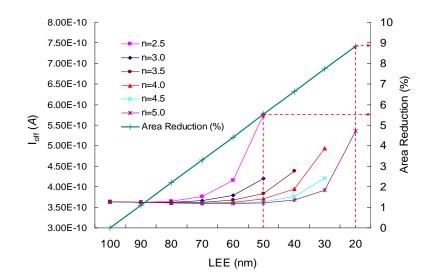

| Figure 7.1:   | $I_{on}$ and $I_{off}$ change due to line-end extension length                     | 252 |

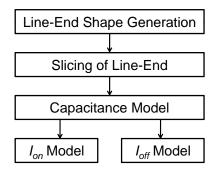

| Figure 7.2:   | Line-end extension modeling flow. $I_{on}$ and $I_{off}$ can be modeled as         |     |

| e             | functions of line-end extension capacitance.                                       | 253 |

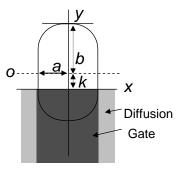

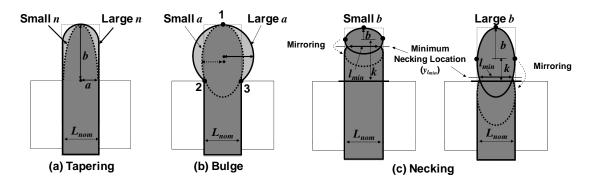

| Figure 7.3:   | An example of a line-end shape represented by superellipse equa-                   |     |

| 8             | tion.                                                                              | 254 |

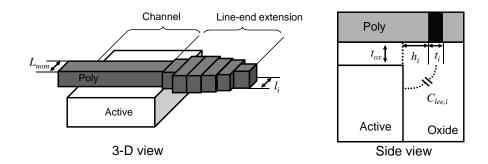

| Figure 7.4:   | Modeling line-end capacitance.                                                     |     |

| Figure 7.5:   | Line-end shapes represented by the superellipse equation                           |     |

| Figure 7.6:   | Non-uniform channel modeling procedure.                                            |     |

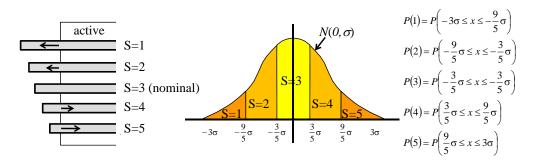

| Figure 7.7:   | Overlay error model: (a) five discretized overlay errors, and (b)                  |     |

| 1.9010        | probability $P(S)$ calculation for each overlay error $S$                          | 260 |

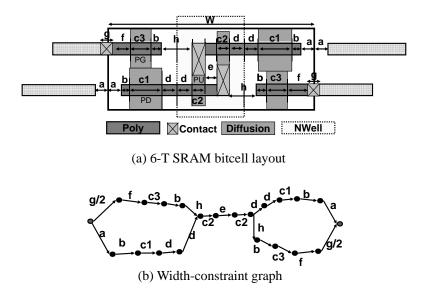

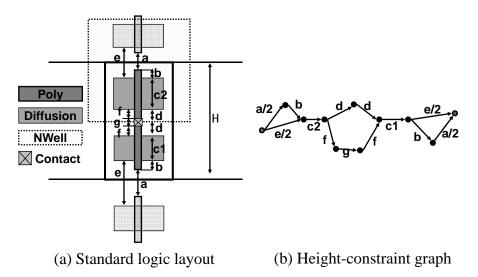

| Figure 7.8:   | SRAM layout and width constraint graph.                                            |     |

| Figure 7.9:   | Area-leakage tradeoff for an SRAM bitcell.                                         |     |

| Figure 7.10:  | Inverter cell layout and height constraint graph.                                  |     |

| 0             | Area-leakage tradeoff for a logic cell.                                            |     |

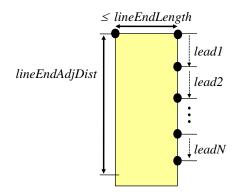

| -             | OPC parameters for line-end fragmentation.                                         |     |

| 1 15010 /.12. |                                                                                    |     |

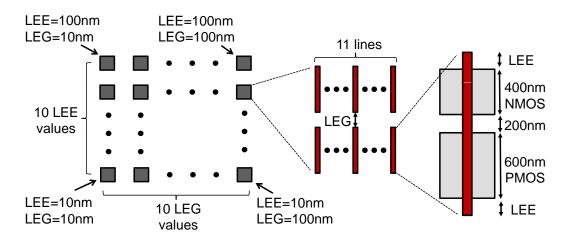

| Figure 7.13: | Layout of the test patterns for OPC/litho simulation.                             | 273 |

|--------------|-----------------------------------------------------------------------------------|-----|

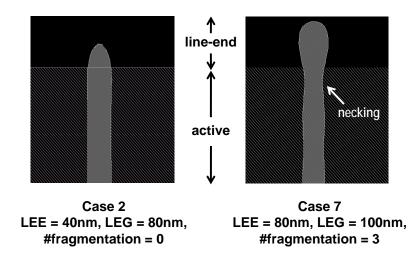

| Figure 7.14: | Litho images for Cases 2 and 7 in Table 7.8                                       | 275 |

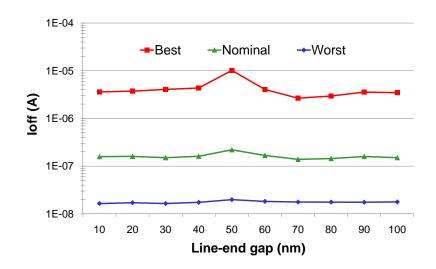

| Figure 7.15: | I <sub>off</sub> variations at best-/nominal-/worst-case process corners with re- |     |

|              | spect to LEG design rules.                                                        | 275 |

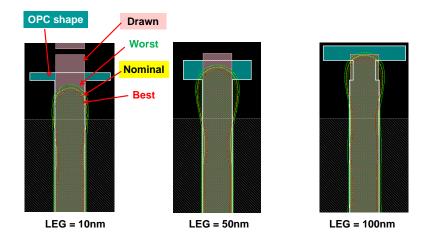

| Figure 7.16: | Litho contours at best-case (red), nominal-case (yellow), and worst-              |     |

|              | case (green) corners, for $10nm$ , $50nm$ and $100nm$ LEG rules                   | 276 |

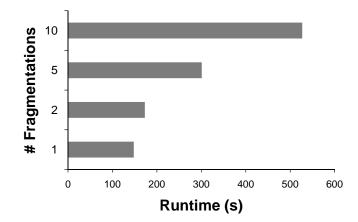

| Figure 7.17: | OPC/litho simulation runtime due to the number of fragmentations.                 | 277 |

| Figure 7.18: | Lithographic errors at the line-end                                               | 279 |

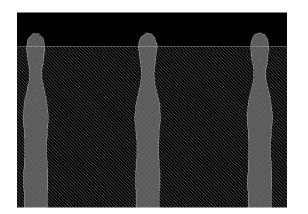

| Figure 7.19: | Significant tapering when the number of fragmentations is 4 and                   |     |

|              | LEG is 20 <i>nm</i>                                                               | 281 |

|              |                                                                                   |     |

### LIST OF TABLES

| Table 2.1:  | Inverter delay for different P, V and T corners                                                                                         | 30       |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------|----------|

| Table 2.2:  | R and C comparison and scaling method for 90nm interconnect                                                                             | 38       |

| Table 2.3:  | Area versus guardband reduction for $90nm JPEG$ at $300MHz$                                                                             | 42       |

| Table 2.4:  | Total wirelength versus guardband reduction for $90nm$ JPEG design at $300MHz$ .                                                        | 42       |

| Table 2.5:  | Dynamic power versus guardband reduction for $90nm$ JPEG design at $300MHz$ .                                                           | 42       |

| Table 2.6:  | Leakage power versus guardband reduction for $90nm JPEG$ design at $300MHz$ .                                                           | 43       |

| Table 2.7:  | Area versus guardband reduction for $45nm$ embedded processor core at $500MHz$ .                                                        | 43       |

| Table 2.8:  | Dynamic power versus guardband reduction for $45nm$ embedded processor core at $500MHz$ .                                               | 43       |

| Table 2.9:  | Leakage power versus guardband reduction for $45nm$ embedded processor core at $500MHz$                                                 | 43       |

|             | Critical-path delay variations across different guardband reductions.                                                                   | 46       |

| Table 2.11: | Guardband reduction versus SP&R flow runtime for $90nm$ JPEG design at $300MHz$ .                                                       | 48       |

| Table 2.12: | Guardband reduction versus SP&R flow runtime for $45nm$ embedded processor core at $500MHz$ .                                           | 48       |

| Table 2.13: | Guardband reduction versus number of violations, worst negative slack (WNS) and total negative slack (TNS).                             | 49       |

| Table 2.14: | Random defect yield for $65nm 5XJPEG$ design                                                                                            | 51       |

| Table 2.15: | The number of good dies per wafer for Scenario (1) guardband re-<br>duction.                                                            | 54       |

| Table 2.16: | The number of good dies per wafer for Scenario (2) guardband re-<br>duction.                                                            | 55       |

| Table 3.1:  | Average mean squared error (MSE) from $k$ -fold cross-validation, and standard deviation (STDEV) of remaining variations after removing | 70       |

| Table 3.2:  | the modeled variation from the original data                                                                                            | 73<br>86 |

| Table 3.3:  | Maximum CD error $(nm)$ with respect to $k$ , $n_{stage}$ , and $r$ for artificial CD variation maps of two stacked dies.               | 89       |

| Table 3.4:  | Root mean squared error (RMSE) $(nm)$ and maximum error with respect to the number of timing paths $(k)$ in $AES$ design.               | 93       |

| Table 4.1:  | CD and overlay requirements ( $3\sigma$ variation) for DE/DP and SADP processes in ITRS 2010 [11].                                      | 105      |

| Table 4.2:               | $3\sigma$ linewidth variations in SID-type SADP due to different imple-         |      |

|--------------------------|---------------------------------------------------------------------------------|------|

|                          | mentation methods for $32nm$ , $28nm$ and $22nm$ technology nodes.              | 105  |

| Table 4.3:               | Nominal dimensions of an intermediate layer interconnect for $45nm$ ,           |      |

|                          | 32nm, $28nm$ and $22nm$ technology nodes                                        | 112  |

| Table 4.4:               | Inter-layer capacitance $(aF/\mu m)$ comparison for a 45nm technology.          | 113  |

| Table 4.5:               | Intra-layer capacitance $(aF/\mu m)$ comparison and total capacitance           |      |

|                          | $(aF/\mu m)$ comparison for a 45nm technology.                                  | 114  |

| Table 4.6:               | Intra- and inter-layer capacitance $(aF/\mu m)$ comparison for a $32nm$         |      |

|                          | technology.                                                                     | 115  |

| Table 4.7:               | Intra- and inter-layer capacitance $(aF/\mu m)$ comparison for a 28nm           |      |

|                          | technology.                                                                     | 116  |

| Table 4.8:               | Intra- and inter-layer capacitance $(aF/\mu m)$ comparison for a $22nm$         |      |

|                          | technology.                                                                     | 117  |

| Table 4.9:               | Ratio of variation to nominal value (%) for total capacitance (i.e.,            | 117  |

| 10010 4.7.               | $C^{intra} + C^{inter}$ ) with respect to technology nodes                      | 118  |

| Table 4.10:              | Technology stack parameters for a $45nm$ technology.                            | 120  |

|                          |                                                                                 | 120  |

|                          | Fall delay variation (%) of INV_X4 for each overlay scenarios.                  | 128  |

| Table 4.12:              | Critical-path delay $(ns)$ and total negative slack $(ns)$ with original        | 100  |

| <b>T</b> 1 1 4 1 0       | via resistance and with $2 \times$ larger via resistance.                       | 129  |

|                          | Mean and sigma of bimodal and pooled unimodal CD distributions                  | 131  |

|                          | Path configurations for 4-stage inverter and buffer chains                      | 135  |

|                          | Coloring configurations of the critical path example                            | 139  |

| Table 4.16:              | Critical dimension targets.                                                     | 144  |

| Table 5.1:               | 90 <i>nm</i> mask cost from Pramanik et al. [147]                               | 155  |

| Table 5.1:<br>Table 5.2: | 45nm mask cost scaled from $90nm$ mask cost                                     | 155  |

|                          |                                                                                 | 150  |

| Table 5.3:               | Delay variation and parametric yield with respect to field size in              | 1(0  |

| T 11 5 4                 | 65nm test chip from Foundry A                                                   | 160  |

| Table 5.4:               | $I_{d,sat}$ variation and parametric yield with respect to field size in $45nm$ | 1.61 |

|                          | test chip from Foundry B                                                        | 161  |

| Table 5.5:               | Assumed defect densities.                                                       | 164  |

| Table 5.6:               | Surface defect height, CD variation ( $\Delta L$ ), and resulting timing vari-  |      |

|                          | ation ( $\Delta T$ ) from a 45nm open-source design kit [14]                    | 165  |

| Table 5.7:               | Proportion of timing-critical regions in real designs. Area of timing-          |      |

|                          | critical region is calculated as the sum of areas of cells for which            |      |

|                          | timing slack is less than $20ps.$                                               | 173  |

| Table 5.8:               | Characteristics of 65nm and 90nm designs implemented with Arti-                 |      |

|                          | san TSMC library.                                                               | 190  |

| Table 5.9:               | Delay and leakage values of $65nm$ design <i>AES65</i> when dose change         |      |

|                          | $d_{i,j}^P$ is swept from 0% to $-5\%$ and from 0% to $+5\%$ on the poly        |      |

|                          | layer. The simplistic, uniform increase of dose cannot obtain delay             |      |

|                          | improvement without incurring leakage increase                                  | 191  |

|                          | 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0                                         |      |

| Table 5.10:     | Delay and leakage values of $90nm$ design <i>AES90</i> when dose change $d_{i,j}^P$ is swept from $0\%$ to $-5\%$ and from $0\%$ to $+5\%$ on the poly layer. The simplistic, uniform increase of dose cannot obtain delay |     |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|                 | improvement without incurring leakage increase                                                                                                                                                                             | 191 |

| Table 5.11:     | Results of dose map optimization on poly layer, i.e., gate length                                                                                                                                                          |     |

|                 | $(L_{qate})$ modulation with smoothness bound $B = 2$ , dose correction                                                                                                                                                    |     |

|                 | range $\pm 5\%$ and $5 \times 5um^2$ grids.                                                                                                                                                                                | 192 |

| Table 5.12:     | Results of dose map optimization on poly layer, i.e., gate length                                                                                                                                                          |     |

|                 | $(L_{gate})$ modulation with smoothness bound $B = 2$ , dose correction                                                                                                                                                    |     |

|                 | range $\pm 5\%$ and $10 \times 10 um^2$ grids                                                                                                                                                                              | 193 |

| Table 5.13:     | Results of dose map optimization on poly layer, i.e., gate length                                                                                                                                                          |     |

|                 | $(L_{gate})$ modulation with smoothness bound $B = 2$ , dose correction                                                                                                                                                    |     |

|                 | range $\pm 5\%$ and $30 \times 30 um^2$ grids.                                                                                                                                                                             | 194 |

|                 | Percentage of critical timing paths in testcases                                                                                                                                                                           | 195 |

| Table 5.15:     | Results of dose map optimization on both poly and active layers us-                                                                                                                                                        |     |

|                 | ing quadratic program for improved leakage power, i.e., gate length                                                                                                                                                        |     |

|                 | $(L_{gate})$ and gate width $(W_{gate})$ modulation, with smoothness bound                                                                                                                                                 |     |

|                 | $B = 2$ and dose correction range $\pm 5\%$ .                                                                                                                                                                              | 196 |

| Table 5.16:     | Results of dose map optimization on both poly and active layers us-                                                                                                                                                        |     |

|                 | ing quadratically constrained program for improved timing, i.e., gate                                                                                                                                                      |     |

|                 | length ( $L_{gate}$ ) and gate width ( $W_{gate}$ ) modulation, with smoothness                                                                                                                                            | 107 |

|                 | bound $B = 2$ and dose correction range $\pm 5\%$ .                                                                                                                                                                        | 197 |

| Table 6.1:      | Results of dose map optimization on poly layer using quadratically-                                                                                                                                                        |     |

|                 | constrained programming (Section 5.2.2) for improved timing, fol-                                                                                                                                                          |     |

|                 | lowed by incremental placement optimization (dosePl)                                                                                                                                                                       | 206 |

| Table 6.2:      | Delay and leakage values of $AES65$ when dose change $d_{i,j}^P$ is swept                                                                                                                                                  |     |

|                 | from $0\%$ to $-5\%$ and from $0\%$ to $+5\%$ on poly layer.                                                                                                                                                               | 207 |

| Table 6.3:      | Delay changes due to the CD changes of the transitioning input gates                                                                                                                                                       |     |

|                 | of a 2-input NAND gate which has two poly lines corresponding to                                                                                                                                                           |     |

|                 | two input pins A1 and A2                                                                                                                                                                                                   | 211 |

| Table 6.4:      | Applicable design stages.                                                                                                                                                                                                  |     |

| Table 6.5:      | Bimodal-aware timing libraries.                                                                                                                                                                                            |     |

| Table 6.6:      | Testcase information.                                                                                                                                                                                                      | 223 |

| Table 6.7:      | Average $CSCP$ of the top-k critical paths and TNS $(ns)$ reduction via                                                                                                                                                    |     |

|                 | the alternate color assignment (OPT-COLOR).                                                                                                                                                                                | 226 |

| Table 6.8:      | WNS $(ns)$ comparison before (Init.) and after (Alt.) alternate color-                                                                                                                                                     |     |

| <b>m</b> 11 C O | ing (OPT-COLOR) for different testcases.                                                                                                                                                                                   | 227 |

| Table 6.9:      | TNS ( <i>ns</i> ) comparison before (Init.) and after (Alt.) alternate color-                                                                                                                                              | 000 |

| Table ( 10      | ing (OPT-COLOR) for different testcases. $\dots$                                                                                                   | 228 |

| 1able 6.10:     | Performance comparison of <b>MINMAX</b> and <b>SHIFT</b> for $AES70$                                                                                                                                                       | 229 |

| Table 6.11: | DP-based coloring-conflict removal using SHIFT. SDTC and SD-                                                                  |     |

|-------------|-------------------------------------------------------------------------------------------------------------------------------|-----|

|             | NTC denote sum of displacements $(\mu m)$ of timing-critical cells and                                                        |     |

|             | of non-timing critical cells, respectively. (Results for other testcases                                                      |     |

|             | are available at [30].)                                                                                                       | 231 |

| Table 6.12: | DP-based coloring-conflict removal using <b>SHIFT+RECOLOR</b> .                                                               |     |

|             | SDTC and SDNTC denote sum of displacements ( $\mu m$ ) of timing-                                                             |     |

|             | critical cells and of non-timing critical cells, respectively. FCCD                                                           |     |

|             | represents the number of recolored cells during DPL-CORR. (Re-                                                                |     |

|             | sults for other testcases are available at [30].)                                                                             | 232 |

| Table 6.13: | Comparisons of WNS and TNS, before and after OPT-COLOR and                                                                    |     |

|             | DPL-CORR SHIFT optimizations.                                                                                                 | 233 |

| Table 6.14: | Comparisons of WNS and TNS before and after OPT-COLOR and                                                                     |     |

|             | DPL-CORR SHIFT+RECOLOR optimizations.                                                                                         | 234 |

| Table 6.15: | Example of 6-T SRAM bitcell device sizing.                                                                                    | 238 |

|             | Two sets of design rules for IAL-friendly layout.                                                                             |     |

|             | Lithography simulation conditions.                                                                                            |     |

|             | Comparison of $I_{read}$ , $I_{leakage}$ and $VDD_{hold}$ .                                                                   |     |

| 10010 0.10. | Comparison of Treaa, Treakage and V D D nota.                                                                                 | 210 |

| Table 7.1:  | Model accuracy and impact of overlay error on rectangular line-end                                                            |     |

|             | extension.                                                                                                                    | 261 |

| Table 7.2:  | $I_{on}$ and $I_{off}$ changes with line-end extension length and <i>sharpness</i>                                            |     |

|             | for $200nm$ width NMOS                                                                                                        | 263 |

| Table 7.3:  | $I_{on}$ and $I_{off}$ changes with line-end extension length and <i>fatness</i> for                                          |     |

|             | 200nm width NMOS                                                                                                              | 264 |

| Table 7.4:  | $I_{on}$ and $I_{off}$ changes with line-end extension length and <i>necking</i> for                                          |     |

|             | 200 <i>nm</i> width NMOS                                                                                                      | 265 |

| Table 7.5:  | Design rules from the Nangate 45nm Open Cell Library [14], and                                                                |     |

|             | the width of transistors in an SRAM bitcell.                                                                                  | 267 |

| Table 7.6:  | SRAM bitcell area reduction (%) with respect to allowed leakage                                                               |     |

|             | increase (%)                                                                                                                  | 268 |

| Table 7.7:  | Logic area reduction (%) under allowed leakage increase (%)                                                                   |     |

| Table 7.8:  | $I_{off}$ variation for the same $45nm$ linewidth at the gate edge (LW0).                                                     |     |

| Table 7.9:  | Best fragmentation locations when $I_{off}$ for LEE = 100nm and LEG                                                           |     |

|             | $= 100 nm. \dots \dots$ | 277 |

| Table 7.10: | Normalized area (%), $C_{LEE,LEG}$ according to LEE and LEG design                                                            |     |

| 10010 /1101 | rules, relative to the area when both LEE and LEG are 100 <i>nm</i>                                                           | 278 |

| Table 7.11: | $I_{off}$ ( <i>nA</i> ) with respect to the LEE and LEG design rules for the best                                             | 270 |

|             | fragmentation location cases that lead to smallest $I_{off}$ for $N_f = 0$ .                                                  | 280 |

| Table 7.12: | $I_{off}$ ( <i>nA</i> ) with respect to the LEE and LEG design rules for the best                                             | 200 |

| 14010 /.12. | * *                                                                                                                           |     |

|             | fragmentation location cases that lead to smallest $I_{off}$ for $N_f = 1$                                                    | 701 |

|             | (lead1 = 60nm).                                                                                                               | 281 |

| Table 7.13: | $I_{off}$ ( <i>nA</i> ) with respect to the LEE and LEG design rules for the best |     |

|-------------|-----------------------------------------------------------------------------------|-----|

|             | fragmentation location cases that lead to smallest $I_{off}$ for $N_f = 2$        |     |

|             | (lead1 = 10nm, lead2 = 30nm).                                                     | 282 |

| Table 7.14: | $I_{off}$ ( <i>nA</i> ) with respect to the LEE and LEG design rules for the best |     |

- Table 7.15:  $I_{off}$  (nA) with respect to the LEE and LEG design rules for the best<br/>fragmentation location cases that lead to smallest  $I_{off}$  for  $N_f = 4$ <br/>(lead1 = 60nm, lead2 = 10nm, lead3 = 10nm, lead4 = 20nm). . . . 284

#### ACKNOWLEDGMENTS

I would like to thank to my parents (my father Jaechoon Jeong and my mother Imsoon Lee), my wife Sumi Hong, her mother Heungyun Ryu, my son Hoejin Jeong, and my sister Yongok Jeong and her family for their patience of my absence and endless love throughout the years. Their continuous support and belief on me have been the most important contribution to my course.

I certainly feel privileged and grateful to work under my advisor Professor Andrew B. Kahng's guidance, and I thank him for all his invaluable support and advice. Especially, his enthusiasm always stimulates me, and his attitude on research and logical ways of thinking will remain in the rest of my life as great lessons.

I am thankful to my thesis committee members, Professor C. K. Cheng, Professor Larry Larson, Professor Lawrence Saul, and Professor Yuan Taur, for taking time out of their busy schedules to review and evaluate my research work. I am grateful for their encouragement and valuable feedback.

I certainly feel lucky to work with a great group of friends and collaborators in VLSI CAD Laboratory – former members Professor Puneet Gupta, Professor Bao Liu, Dr. Swamy Muddu, Dr. Kambiz Samadi, Dr. Chul-Hong Park, Dr. Puneet Sharma, Dr. Rasit O. Topaloglu, and Professor Hailong Yao, and current members Tuck-Boon Chan, Seokhyeong Kang, Jingwei Lu and Vaishnav Srinivas. We had wonderful projects and spent great times together, and I would like to especially thank all of the current members for proofreading this thesis. I wish continuous cooperation and correspondence with all of them.

I also miss the times with Mohit Gupta, Sung Kyu Han, Neelmani Kumar, Yen-Kuan Wu and Ruixin Yang. I wish them the best in their future.