### UC Riverside UC Riverside Electronic Theses and Dissertations

### Title

Parallel and Statistical Analysis and Modeling of Nanometer VLSI Systems

### Permalink

https://escholarship.org/uc/item/7ts542v4

# Author

Liu, Xue-Xin

# Publication Date 2013

Peer reviewed|Thesis/dissertation

### UNIVERSITY OF CALIFORNIA RIVERSIDE

Parallel and Statistical Analysis and Modeling of Nanometer VLSI Systems

A Dissertation submitted in partial satisfaction of the requirements for the degree of

Doctor of Philosophy

in

**Electrical Engineering**

by

Xue-Xin Liu

March 2013

Dissertation Committee:

Professor Sheldon X.-D. Tan, Chairperson Professor Jian-Lin Liu Professor Qi Zhu

Copyright by Xue-Xin Liu 2013 The Dissertation of Xue-Xin Liu is approved:

Committee Chairperson

University of California, Riverside

#### Acknowledgments

My thanks and appreciation go to my thesis committee members, Prof. Jian-Lin Liu and Prof. Qi Zhu for their direction, dedication, and invaluable advice. I would like to express my deepest gratitude to my adviser, Prof. Sheldon X.-D. Tan, for his help, trust and guidance. There exist wonders as well as frustrations in academic research. His kindness, insight and suggestions always lead me to the right way.

A special word of thanks for all the members in our lab should be dedicated here. I thank especially Ning, Bo-Yuan, Duo, Rui-Jing, Hai, Zao, Sahana, Rui, Santiago, Adair, Kuang-Ya, Jacob, Nema, Thom, Ryan, Eric, Jaqueline, and Omar for the collaborative research works and help, which lead to the presented works in this thesis. I appreciate the friendship of my fellow students in UCR. There are too many of them and this page does not allow me to list, but they are all in my heart.

Last but not least, I would like to thank my parents and all my friends for their constant support during the years of my study. It is the love and the light warmly shared by them that guides me to grow up.

#### ABSTRACT OF THE DISSERTATION

Parallel and Statistical Analysis and Modeling of Nanometer VLSI Systems

by

Xue-Xin Liu

#### Doctor of Philosophy, Graduate Program in Electrical Engineering University of California, Riverside, March 2013 Professor Sheldon X.-D. Tan, Chairperson

Electronic design automation (EDA) is an important part of the integrated circuit (IC) industry, and has been evolving together with design and fabrication technologies. This evolution is reflected in both the advent of new algorithms and the rapid upgrade of software implementation. Innovative algorithms deliver accurate and reliable results in shorter computation time, and thus saves human resource and R&D cost. Smartly designed software can utilize hardware resources efficiently and improve computing performance.

However, EDA is now facing many complicated cases in current VLSI technology. As integration scales to the sub-90 nm regime, the performance of ICs is becoming less predictable. Different sources of variations are caused from manufacturing process and these variations will finally end up with parametric yield loss. To deal with yield loss, efficient algorithms are required to accurately predict the performance of a circuit at the design stage. Unfortunately, given the high complexity of VLSI systems, software tools with traditional algorithm and implementation suffer from the "curse of dimensionality" problem. For instance, Monte Carlo (MC) method, which is the most trustworthy way to capture statistical information of a design, becomes inefficient as a large number of samplings are needed for an accurate analysis of the variations of the circuit response. Also, many verification tasks require transient simulation or frequency domain simulation of the full-chip design in order to guarantee an optimized product. A typical power grid circuit has a tremendous size of over billion nodes, and takes several days for traditional transient simulation to calculate transient response. With chips getting smaller and more complicated, the modeling and analysis will certainly become more difficult challenging.

In this thesis, we study the tough issues in statistical analysis such as Monte Carlo method and performance bound analysis, as well as modeling and simulating large scale circuit systems, such as power grid circuit and thermal circuit. Our algorithm and software solutions are proposed to reduce the computation cost without hurting the accuracy. We also take the benefits of modern multi-core and many-core computer architectures, such as multi-core CPU and general purpose GPU (GPGPU), to gain speedup in our simulation. Computational independency in MC simulation is exploited and hence we have developed a GPU parallel Monte Carlo analysis based on symbolic technique. Our parallel MC of circuit transfer functions has been verified using statistics extracted from classical MC, and the proposed method is proved to be effective. We also study optimization based method to derive the performance bounds as a non-Monte Carlo solution. The bounds from this method are accurate without over-conservativeness.

To accelerate linear algebra operations in equation solving tasks, which are common in our power grid analysis, 3D IC thermal analysis, and RF and power converter simulation, we apply GPU on fine-grained tasks in GMRES solver and attain impressive speedup over traditional CPU method. The management of different levels of GPU resources, such as thread organization and memory assignment, are discussed so that the data intensive feature of GPU can be fully rendered and its weakness like long memory access latency be well hidden by its superb data throughput. All algorithms and implementations are demonstrated with representative numerical experiments and thorough comparisons among different methods and platforms.

## Contents

| List of Figures        |              | xi                                                                  |          |

|------------------------|--------------|---------------------------------------------------------------------|----------|

| $\mathbf{L}\mathbf{i}$ | ist of       | Tables                                                              | xv       |

| 1                      | Inti         | roduction                                                           | 1        |

|                        | 1.1          | Circuit simulation in nanometer regime of VLSI                      | 1        |

|                        | 1.2          | CUDA GPU architecture and programming                               | 4        |

|                        | 1.3          | Objectives and results of this thesis                               | 10       |

|                        | 1.4          | Organization of the thesis                                          | 11       |

| <b>2</b>               | DD           | D based Monte Carlo analysis on GPU                                 | 14       |

|                        | 2.1          | Introduction                                                        | 15       |

|                        | 2.2          | DDD symbolic analysis                                               | 17       |

|                        | 2.3          | Parallel evaluation of DDD                                          | 21       |

|                        |              | 2.3.1 The overall algorithm flow                                    | 22       |

|                        |              | 2.3.2 Continuous and levelized DDD structure                        | 22       |

|                        | 2.4          | Parallel Monte Carlo analysis                                       | 26       |

|                        |              | 2.4.1 Random number assignment to MNA elements and DDD nodes        | 26       |

|                        |              | 2.4.2 Parallel frequency sweep of MC simulation                     | 29       |

|                        | 2.5          | Experimental results                                                | 32       |

|                        | 2.6          | Summary                                                             | 36       |

| 3                      | Don          | formance bound analysis of analog circuits in frequency and time do |          |

| J                      |              | in considering process variations                                   | 37       |

|                        | 3.1          | Introduction                                                        | 37       |

|                        | $3.1 \\ 3.2$ | Variational transfer functions due to process variations            | 40       |

|                        | 3.2          | Computation of frequency domain bounds                              | 40<br>41 |

|                        |              |                                                                     |          |

|                        | 3.4          | Time domain bound analysis                                          | 49       |

|                        |              | 3.4.1 Review of transient bound analysis driven by impulse signals  | 50       |

|                        | 0.5          | 3.4.2 Proposed transient bound analysis with general input signal   | 52       |

|                        | 3.5          | Numerical results                                                   | 57       |

59

|          | 3.6               | 1                                                                 | $1\\6$ |

|----------|-------------------|-------------------------------------------------------------------|--------|

| 4        |                   |                                                                   |        |

| 4        |                   | 1 8                                                               | 0      |

|          | 4.1               |                                                                   | 1      |

|          | 4.2               |                                                                   | 4      |

|          |                   | 1 1 0                                                             | 4      |

|          |                   |                                                                   | 5      |

|          | 4.3               | 1 1                                                               | 7      |

|          |                   | 4.3.1 The overall algorithm flow                                  |        |

|          |                   |                                                                   | 8      |

|          |                   | 0 1                                                               | 1      |

|          | 4.4               | Numerical results                                                 | 3      |

|          | 4.5               | Summary 8                                                         | 7      |

| <b>5</b> | Par               | allel thermal analysis of 3D ICs on GPU-CPU platforms 8           | 8      |

|          | 5.1               | Introduction                                                      | 9      |

|          | 5.2               | Finite difference model of 3D ICs with micro-channels 9           | 1      |

|          |                   | 5.2.1 3D-ICs with integrated inter-tier micro-channels 9          | 1      |

|          |                   | 5.2.2 The proposed thermal model                                  | 4      |

|          | 5.3               | Parallel GMRES solver on GPU-CPU platform                         | 7      |

|          |                   | 5.3.1 Relevant previous arts                                      | 7      |

|          |                   | 5.3.2 Parallelization on GPU-CPU platforms                        | 9      |

|          |                   | 5.3.3 GPU-friendly implementation of preconditioners              |        |

|          | 5.4               | Numerical results                                                 |        |

|          | 0.1               | 5.4.1 Comparison in matrix solving                                |        |

|          |                   | 5.4.2 Comparison in transient thermal analysis                    |        |

|          | 5.5               | Summary                                                           |        |

| C        | CD                | U parallel shooting algorithm for RF/MM ICs 11                    | c      |

| 6        | <b>G</b> г<br>6.1 | ·                                                                 |        |

|          | 0.1               | Introduction                                                      |        |

|          | 6.2               | Background                                                        |        |

|          |                   | 6.2.1 Review of the shooting-based PSS analysis methods           |        |

|          |                   | 6.2.2 Traditional GMRES and matrix-free GMRES                     |        |

|          | 6.3               | GMRES with periodic structured Krylov subspace                    |        |

|          |                   | 6.3.1 Periodic Krylov subspaces                                   | 5      |

|          |                   | 6.3.2 GMRES with periodic Krylov subspaces                        | 8      |

|          |                   | 6.3.3 More independent tasks for better parallelization           | 2      |

|          | 6.4               | Parallelism strategy on GPUs for <i>p</i> -cyclic GMRES method 13 | 3      |

|          |                   | 6.4.1 Task and data assignments between CPU and GPU 13            | 6      |

|          |                   | 6.4.2 Optimization of memory accesses in subspace construction 13 | 8      |

|          | 6.5               | Numerical experiments                                             |        |

|          | 6.6               | Summary                                                           |        |

| 7  | GP           | U envelope-following method for power converter simulation | 152 |  |

|----|--------------|------------------------------------------------------------|-----|--|

|    | 7.1          | Introduction                                               | 153 |  |

|    | 7.2          | Review of envelope-following method                        | 156 |  |

|    | 7.3          | New parallel envelope-following method                     | 158 |  |

|    |              | 7.3.1 GMRES Solver for Newton update equation              | 158 |  |

|    |              | 7.3.2 Gear-2 based sensitivity calculation                 | 161 |  |

|    | 7.4          | Experimental results                                       | 165 |  |

|    | 7.5          | Summary                                                    | 168 |  |

| 8  | Con          | clusion                                                    | 169 |  |

|    | 8.1          | Summary of research contributions                          | 169 |  |

|    | 8.2          | Future research topics                                     | 173 |  |

| Bi | Bibliography |                                                            |     |  |

# List of Figures

| 1.1        | NVIDIA Tesla GPU unified graphics and computing architecture C2070.<br>Each texture/processor cluster, or TPC, is composed of two streaming multi-<br>processors. The off-chip DRAMs are accessible to all threads and are referred                                                                                                                                                                                            |          |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|            | to as global memory. L/S is short for load/store                                                                                                                                                                                                                                                                                                                                                                               | 5        |

| 1.2        | Diagram of a streaming multiprocessor in NVIDIA Tesla C2070. (SP is short for streaming processor, L/S for load/store unit, and SFU for Special                                                                                                                                                                                                                                                                                |          |

| 1.3        | Function Unit.)                                                                                                                                                                                                                                                                                                                                                                                                                | 6        |

|            | a 3-by-2 grid of 6 thread blocks is created, and each block in Kernel 1 is organized into a 5-by-3 array of threads.                                                                                                                                                                                                                                                                                                           | 9        |

| 2.1        | DDD representation for matrix $\mathbf{M}$                                                                                                                                                                                                                                                                                                                                                                                     | 19       |

| 2.2        | A RC filter circuit.                                                                                                                                                                                                                                                                                                                                                                                                           | 20       |

| 2.3        | A matrix determinant and its DDD representation.                                                                                                                                                                                                                                                                                                                                                                               | 21       |

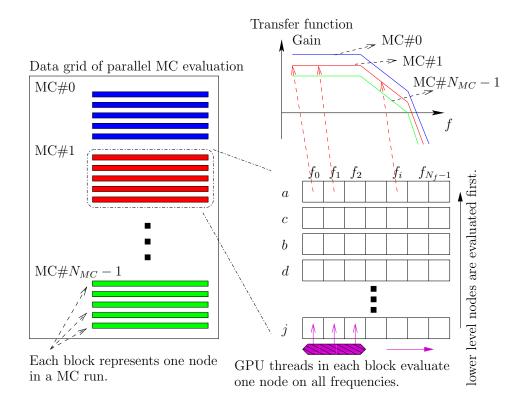

| 2.4        | The flow of GPU-based parallel Monte Carlo analysis                                                                                                                                                                                                                                                                                                                                                                            | 23       |

| 2.5        | Levelized continuous storage of a DDD, and levelwise GPU evaluation of the                                                                                                                                                                                                                                                                                                                                                     |          |

|            | DDD in Fig. 2.1.                                                                                                                                                                                                                                                                                                                                                                                                               | 25       |

| 2.6        | GPU parallel evaluation of the DDD in Fig. 2.1.                                                                                                                                                                                                                                                                                                                                                                                | 30       |

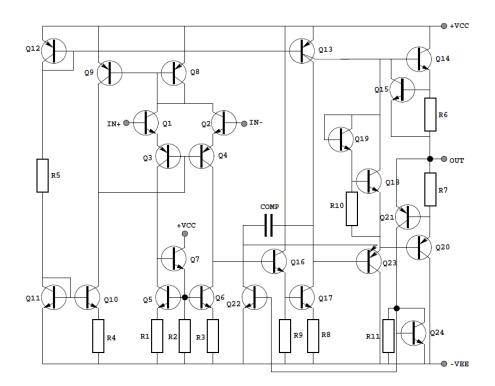

| 2.7        | The circuit schematic of $\mu A741$                                                                                                                                                                                                                                                                                                                                                                                            | 33       |

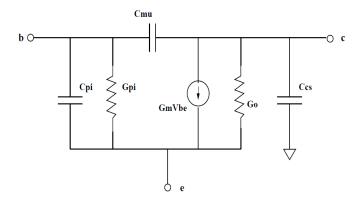

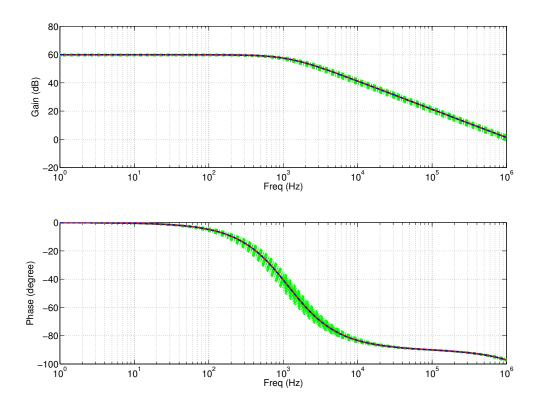

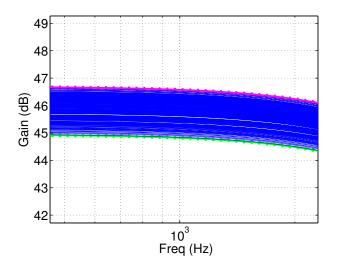

| 2.8<br>2.9 | The small signal model for bipolar transistor $\dots \dots \dots$<br>The cluster of frequency responses of the tested $\mu$ A741 circuit. Red curve is<br>the CPU golden result, blue curve is the GPU result, and all green curves<br>are GPU MC samples from the parallel computation. $\dots \dots \dots$ | 33<br>34 |

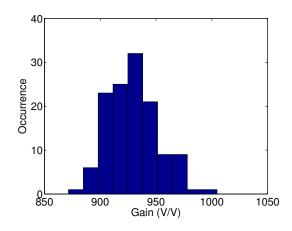

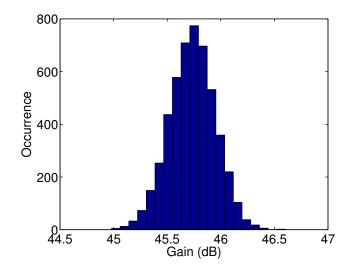

| 2.10       |                                                                                                                                                                                                                                                                                                                                                                                                                                | 34<br>34 |

| 2.10       | instogram diagram of the gam samples of privil at nequency 514 Hz                                                                                                                                                                                                                                                                                                                                                              | 01       |

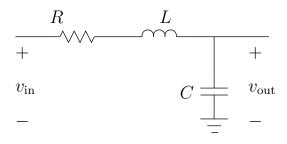

| 3.1        | An RLC ladder circuit                                                                                                                                                                                                                                                                                                                                                                                                          | 42       |

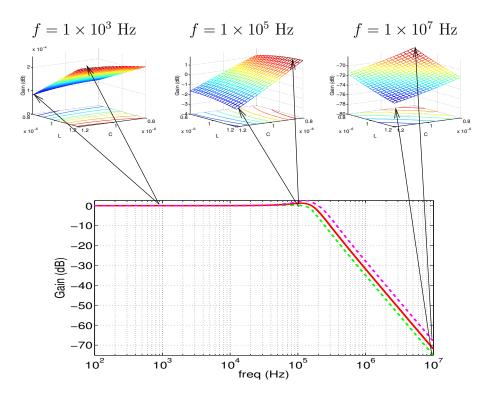

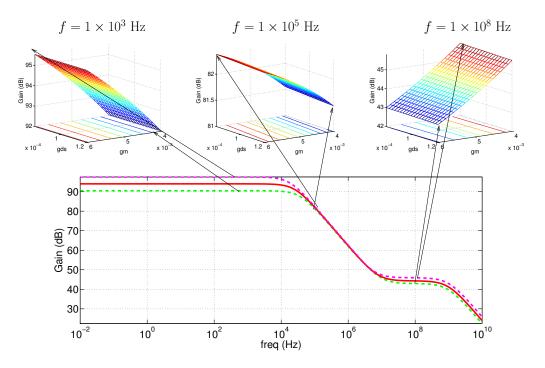

| 3.2        | Frequency response of the RLC circuit. Solid curve is the magnitude response<br>with nominal parameters, while the two dashed curves are lower and upper<br>bounds due to process variation. The three surfaces at top, with $L$ and<br>C as x-axis and y-axis accordingly, and magnitude as z-axis, illustrate the                                                                                                            |          |

|            | variations of magnitude at three sampling frequencies.                                                                                                                                                                                                                                                                                                                                                                         | 43       |

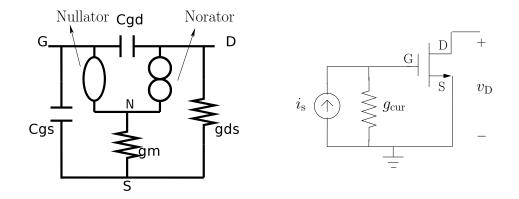

| 3.3        | The small-signal model for MOS transistors                                                                                                                                                                                                                                                                                                                                                                                     | 45       |

| 3.4          | Frequency response of the simplified MOS model driven by Norton current source. Solid curve is the magnitude response with nominal parameters,                                              |            |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

|              | while the two dashed curves are lower and upper bounds due to process                                                                                                                       |            |

|              | variation. The three surfaces at top, with $g_{\rm ds}$ and $g_{\rm m}$ as x-axis and y-axis                                                                                                |            |

|              | accordingly, and magnitude as $z$ -axis, illustrate the variations of magnitude                                                                                                             |            |

|              |                                                                                                                                                                                             | 15         |

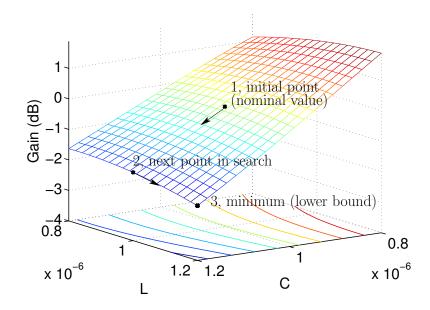

| 3.5          | Optimization space searching for the RLC circuit in Fig. 3.1, where both $C$ and $L$ have 20% variation in this illustration. This surface shows the                                        |            |

| 0.0          |                                                                                                                                                                                             | 18         |

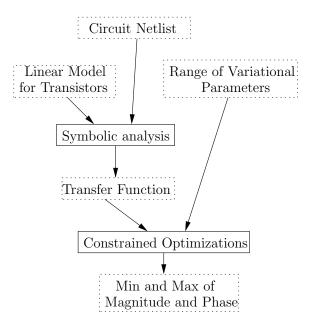

| 3.6          |                                                                                                                                                                                             | 18         |

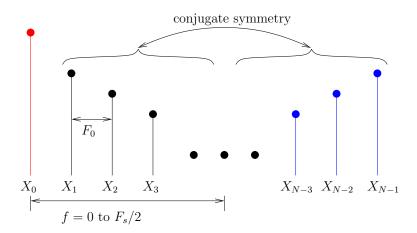

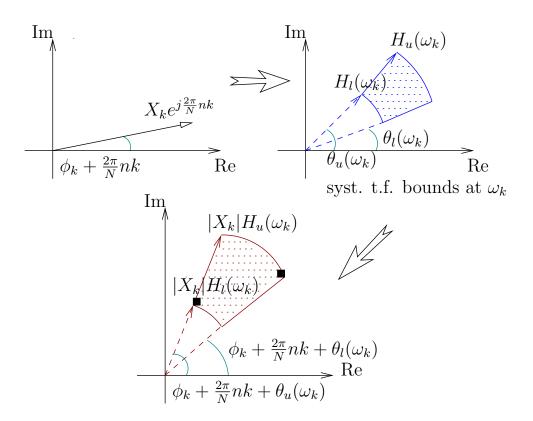

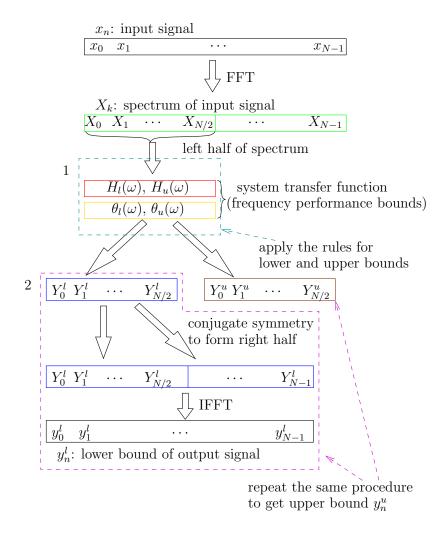

| 3.7          | Conjugate symmetry between left half and right half of the FFT series $X_k$ ,<br>$k = 0, \ldots, N - 1, \ldots, 55$ | 54         |

| 3.8          | The magnification and rotation of input spectrum by the transfer function                                                                                                                   |            |

|              |                                                                                                                                                                                             | 66         |

| 3.9          |                                                                                                                                                                                             | 58         |

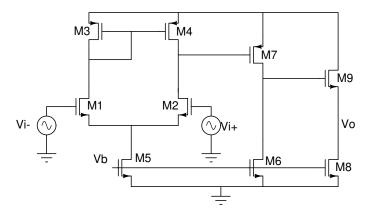

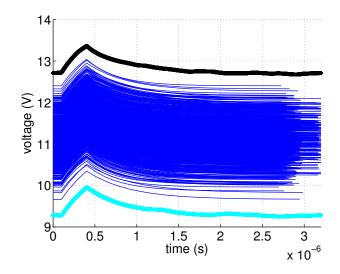

| 3.10         | * *                                                                                                                                                                                         | 60         |

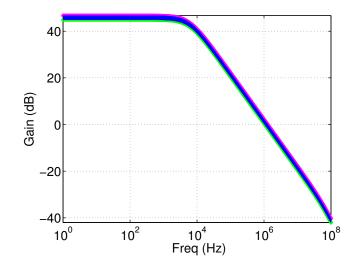

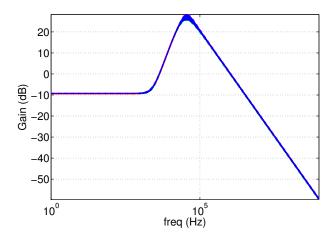

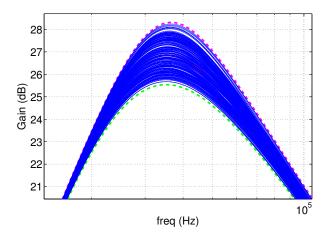

| 3.11         | Monte Carlo simulations and magnitude bounds of op-amp circuit. The thick                                                                                                                   |            |

|              | dashed lines are lower and upper bounds, and the thin solid lines are Monte                                                                                                                 |            |

| ~            |                                                                                                                                                                                             | 52         |

| 3.12         | The histogram of gain distribution of the CMOS op-amp at frequency $f =$                                                                                                                    |            |

| 0 1 0        |                                                                                                                                                                                             | 53         |

| 3.13         | Monte Carlo simulations and magnitude bounds of active filter. The thick dashed lines are lower and upper bounds, and the thin solid lines are Monte                                        |            |

|              | Carlo results                                                                                                                                                                               | 34         |

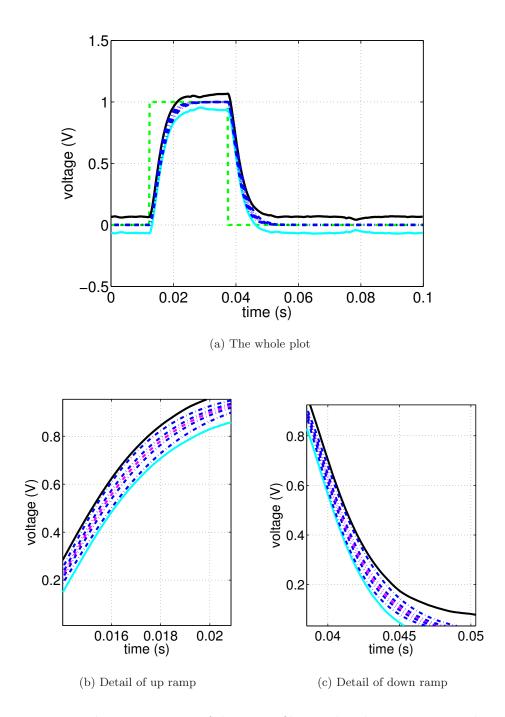

| 3.14         | Time domain response of CMOS op-amp with pulse input. The two thicker<br>curves are the lower and upper bounds from TIDBA, while the thinner lines                                          | 26         |

| 3.15         | Time domain response of the active filter with pulse wave input. The two                                                                                                                    | 66         |

|              | solid curves are the lower and upper bounds, while the region marked by dot-dashed lines are possible output waveforms from Monte Carlo simulation                                          |            |

|              | affected by variations                                                                                                                                                                      | 57         |

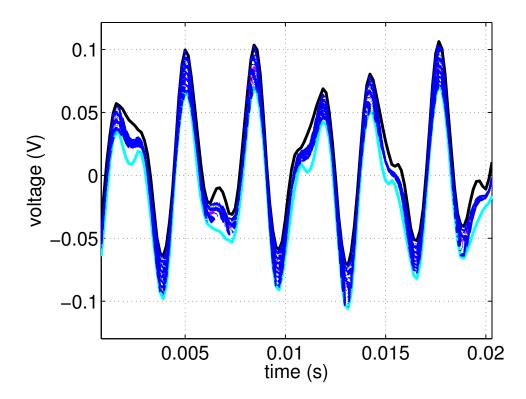

| 3.16         | Time domain response of the active filter with sinusoidal wave input. The                                                                                                                   |            |

|              | two solid curves are the lower and upper bounds, while the region marked by                                                                                                                 |            |

|              | dot-dashed lines are possible output waveforms from Monte Carlo simulation                                                                                                                  |            |

|              | affected by variations                                                                                                                                                                      | 58         |

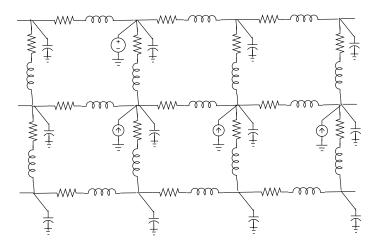

| 4.1          | An RLC model of power grid network                                                                                                                                                          | 75         |

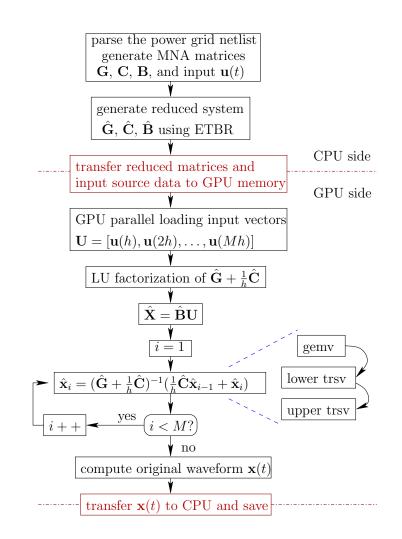

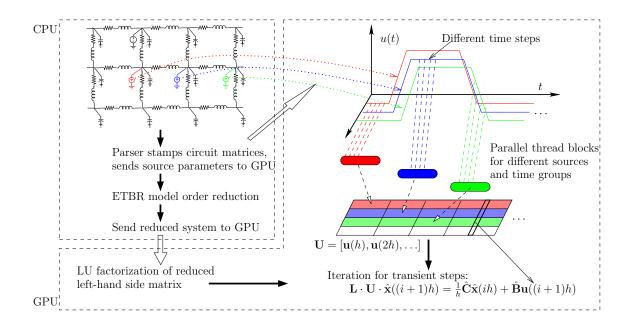

| 4.2          | * 0                                                                                                                                                                                         | <b>'</b> 9 |

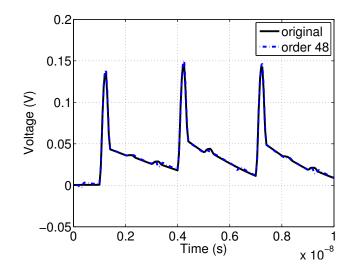

| $4.3 \\ 4.4$ | ETBR-GPU flow and GPU-accelerated current source evaluation 8<br>Transient waveforms of standard LU and ETBR-GPU at one port node of                                                        | 31         |

|              |                                                                                                                                                                                             | 35         |

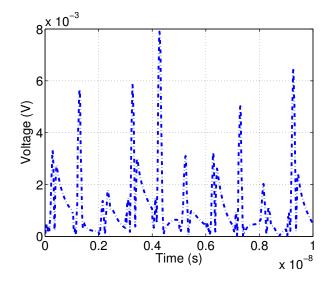

| 4.5          | The simulation error of ETBR-GPU result of ibmpg1t using reduced model                                                                                                                      |            |

|              | of order 48                                                                                                                                                                                 | 35         |

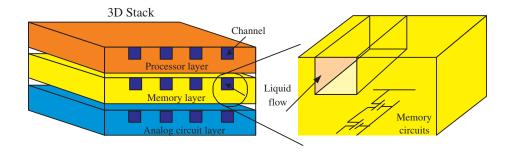

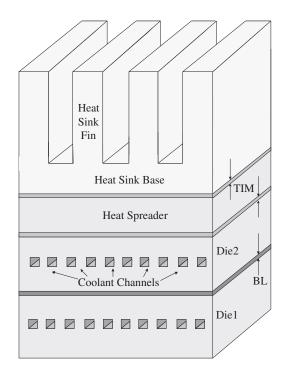

| 5.1          | 3D stacked IC with inter-tier liquid cooling                                                                                                                                                | )2         |

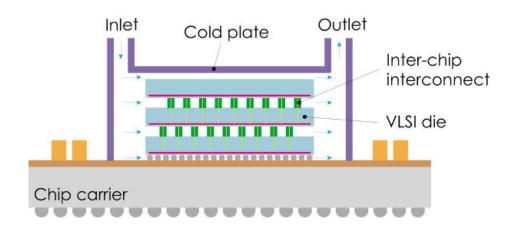

| 5.2  | Interlayer cooling for 3D IC packages.                                                                                                                    | 93    |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

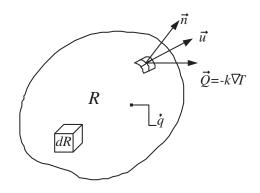

| 5.3  | Energy conservation for a control volume                                                                                                                  | 93    |

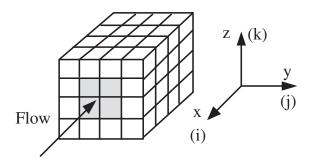

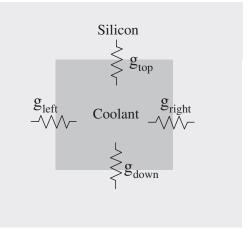

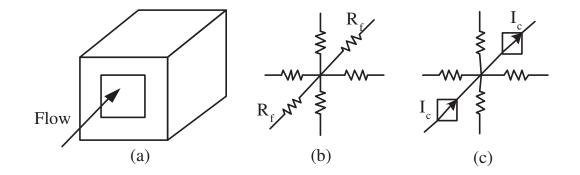

| 5.4  | Meshed chip cell with coolant channel                                                                                                                     | 93    |

| 5.5  | A view of 3D IC stack. BL denotes the bounding layer between two dies,                                                                                    |       |

|      | and TIM denotes the thermal interface material                                                                                                            | 96    |

| 5.6  | Model of heat transfer between coolant and the sidewall of the channel                                                                                    | 96    |

| 5.7  | (a) Coolant flow inside a channel; (b) Modeling heat convection in the direc-                                                                             |       |

|      | tion of the channel using thermal resistor $R_f$ ; (c) Modeling heat convection in                                                                        |       |

|      | the direction of the channel using current sources $I_c$ derived from the energy                                                                          |       |

|      | equation.                                                                                                                                                 | 96    |

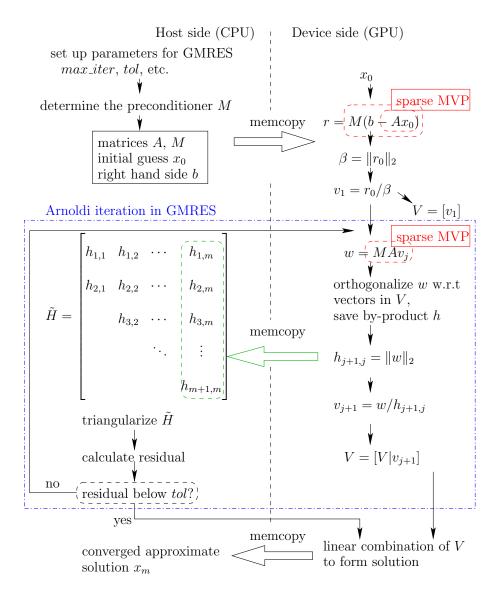

| 5.8  | The proposed GPU-accelerated parallel preconditioned GMRES solver. We                                                                                     |       |

|      | also show the partitioning of the major computing tasks between CPU and                                                                                   |       |

|      | GPU here                                                                                                                                                  | 102   |

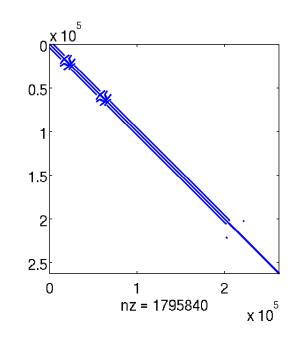

| 5.9  | Sparsity pattern of thermal circuit model from example "therm5"                                                                                           | 107   |

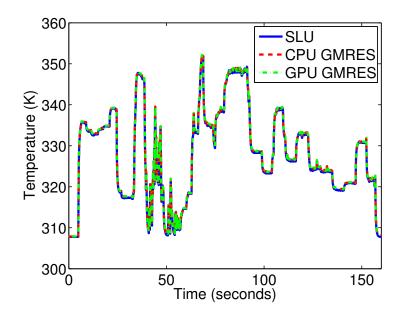

| 5.10 | Temperature waveform of the 3D IC model "therm5". Solid curve is the result                                                                               |       |

|      | of SuperLU, dashed curve is from CPU GMRES, and dash-dotted curve is                                                                                      |       |

|      | from GPU GMRES.                                                                                                                                           | 112   |

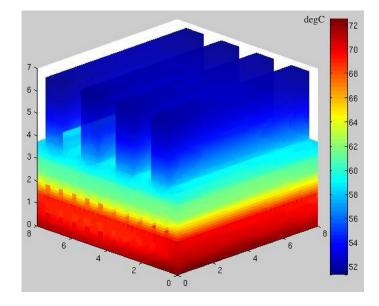

|      | Temperature profile of the 3D IC with two active layers.                                                                                                  | 114   |

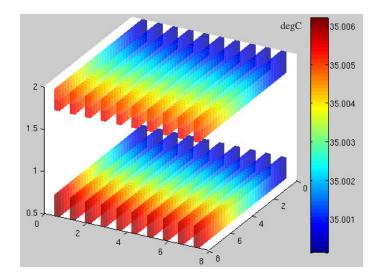

| 5.12 | Temperature profile inside the coolant channels                                                                                                           | 115   |

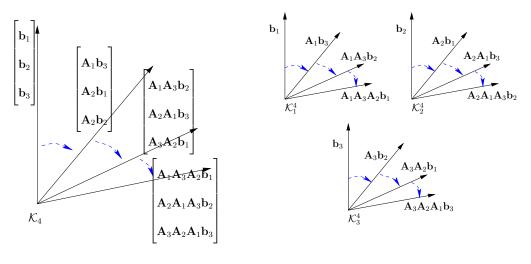

| 6.1  | The comparison of standard Krylov subspace and <i>p</i> -periodic-block-structured                                                                        |       |

|      | Krylov subspace. Order $m = 4$ , and $p = 3$ time steps                                                                                                   | 129   |

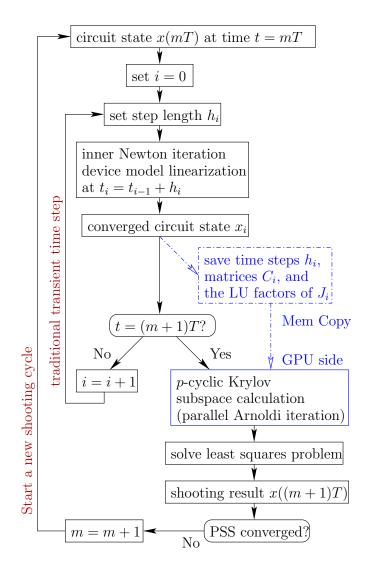

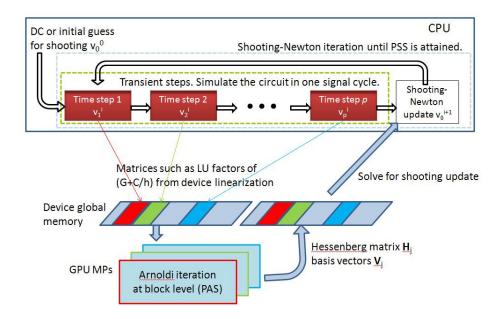

| 6.2  | The flow of shooting-Newton update with <i>p</i> -cyclic GMRES solver on GPU                                                                              |       |

|      | side                                                                                                                                                      | 135   |

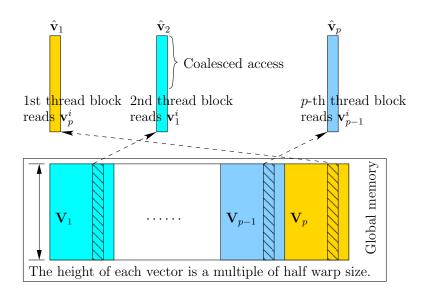

| 6.3  | Parallel <i>p</i> -cyclic basis vector copy using GPU thread blocks. (Line 11 in                                                                          |       |

|      | Algorithm 10)                                                                                                                                             | 139   |

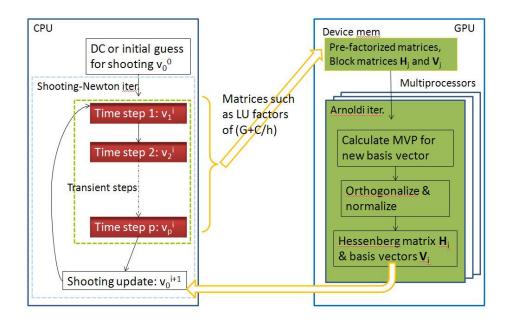

| 6.4  | CPU-GPU collaboration inside a shooting cycle.                                                                                                            | 142   |

| 6.5  | Parallel computation of Krylov-subspaces on GPU                                                                                                           | 142   |

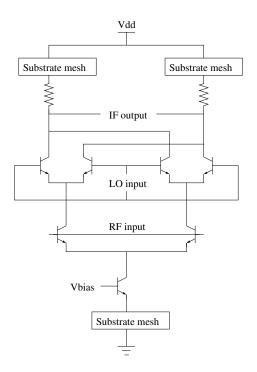

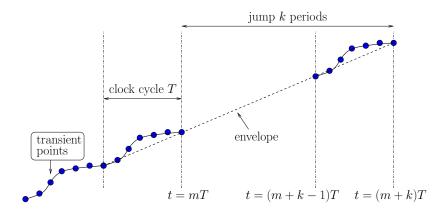

| 6.6  | A double-balanced BJT mixer.                                                                                                                              | 146   |

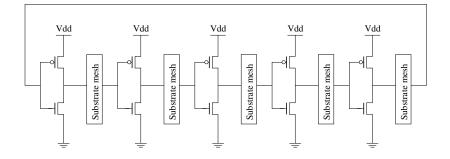

| 6.7  | A CMOS ring oscillator.                                                                                                                                   | 146   |

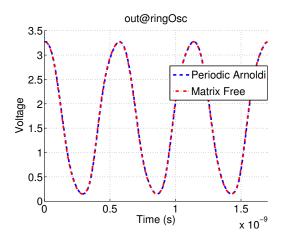

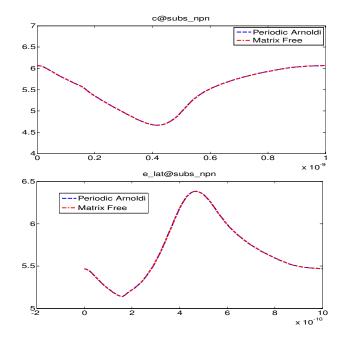

| 6.8  | The PSS waveform accuracy comparison at the output node of a CMOS ring                                                                                    |       |

|      | oscillator. The red line is the non-structured MF-GMRES, and the blue line                                                                                |       |

|      | is the structured PAS-GMRES.                                                                                                                              | 147   |

| 6.9  | The PSS waveform accuracy comparison at two nodes of a BJT mixer. The                                                                                     |       |

|      | red line is the non-structured MF-GMRES, and the blue line is the structured                                                                              |       |

| 0.10 | PAS-GMRES.                                                                                                                                                | 147   |

| 6.10 | The PSS waveform accuracy comparison at two nodes of a CMOS switch                                                                                        |       |

|      | cap. The red line is the non-structured MF-GMRES, and the blue line is the                                                                                | 1 4 0 |

| C 11 | structured PAS-GMRES.                                                                                                                                     | 148   |

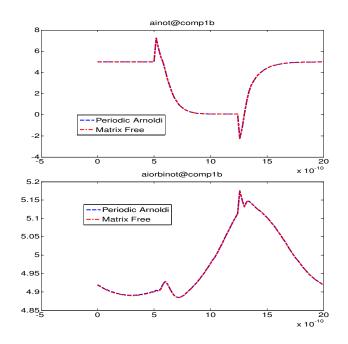

| 0.11 | The running time scalability comparison for a CMOS DC converter with increased gives of manufacture. The red line is the costs of manufacture of the      |       |

|      | increased sizes of parasitic. The red line is the scale of running time of the CDU scale version of BAS CMPES, and the blue line is the scale of running. |       |

|      | CPU serial version of PAS GMRES, and the blue line is the scale of running time of our CPU percellel CAPAS                                                | 151   |

|      | time of our GPU parallel GAPAS.                                                                                                                           | 151   |

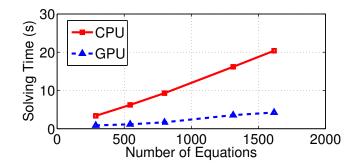

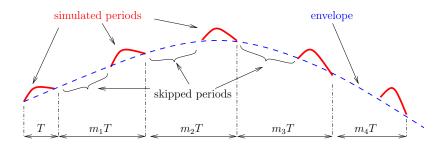

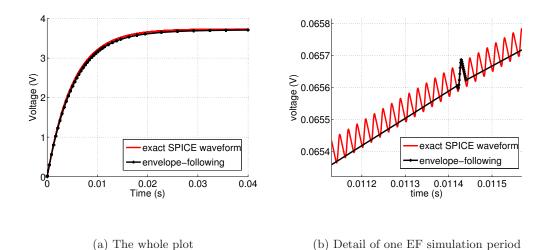

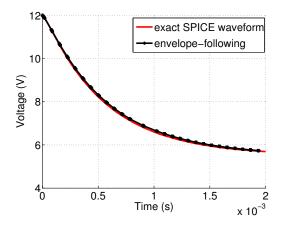

| 7.1 | Transient envelope-following analysis. (Both two figures reflect backward-  |     |

|-----|-----------------------------------------------------------------------------|-----|

|     | Euler style envelope-following.)                                            | 154 |

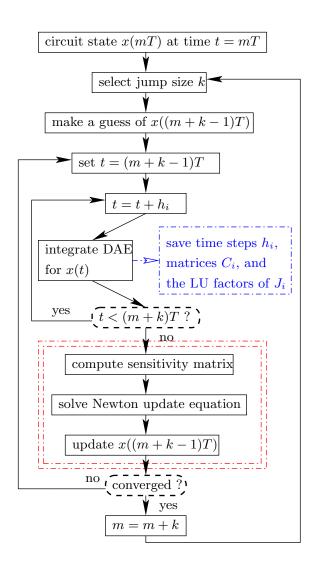

| 7.2 | The flow of envelope-following method                                       | 159 |

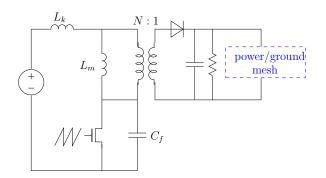

| 7.3 | Diagram of a zero-voltage quasi-resonant flyback converter                  | 165 |

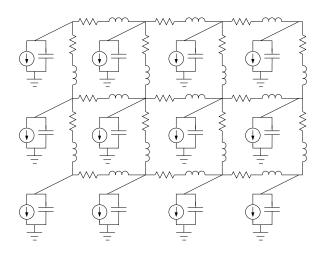

| 7.4 | Illustration of power/ground network model.                                 | 166 |

| 7.5 | Flyback converter solution calculated by envelope-following. The red curve  |     |

|     | is traditional SPICE simulation result, and the back curve is the envelope- |     |

|     | following output with simulation points marked.                             | 166 |

| 7.6 | Buck converter solution calculated by envelope-following                    | 167 |

# List of Tables

| Performance comparison of CPU serial and GPU parallel DDD evaluation<br>for RC tree circuit with different MC runs.                                                                                                                                                                                                                            | 35                                         |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|

| Performance comparison of Monte Carlo simulations using the proposed GPU method, its CPU counterpart, and HSPICE                                                                                                                                                                                                                               | 35                                         |

| Rules for time domain bound determination.                                                                                                                                                                                                                                                                                                     | 56                                         |

| Process variation setup in the benchmarks.                                                                                                                                                                                                                                                                                                     | 60                                         |

|                                                                                                                                                                                                                                                                                                                                                | 63                                         |

| Statistical information of the CMOS filter. (Comparison with 5000 times                                                                                                                                                                                                                                                                        | 63                                         |

| Performance comparison of TIDBA against the Monte Carlo method                                                                                                                                                                                                                                                                                 | 66                                         |

| Performance comparison of standard LU, ETBR and ETBR-GPU methods. $N$ , and $q$ are orders of original system and reduced system, correspondingly. $N_{\text{cur}}$ is the number of current sources. $M$ is the number of transient time step. The average and maximum errors are measured in volts. All time results are measured in seconds | 86                                         |

| Geometrical and material information of the 3D structure.                                                                                                                                                                                                                                                                                      | 97                                         |

| Statistics for thermal circuits. "dim" stands for number of rows and number<br>of columns of the square matrix. "nnz" is the number of nonzero elements,                                                                                                                                                                                       | 0.                                         |

| and density is calculated as $nnz/(\dim \cdot \dim)$                                                                                                                                                                                                                                                                                           | 107                                        |

| Comparison of solvers on $Ax = b$ . For the last five examples from our thermal modeling method, steady state equations for the 3D IC thermal profile are used. SuperLU deploys 4 CPU threads in LU factorization. Run time in seconds. On some examples, GMRES fails to converge without precondi-                                            |                                            |

| and is not shown in the table.                                                                                                                                                                                                                                                                                                                 | 108                                        |

|                                                                                                                                                                                                                                                                                                                                                | for RC tree circuit with different MC runs |

| 5.4 | Comparison of solvers in transient analysis of our 3D IC thermal models.<br>SuperLU deploys 4 CPU threads in LU factorization. Time measurements in<br>Column 2 are the sums of LU factorization times and triangular solve times.          |     |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|     | Runtime in seconds.                                                                                                                                                                                                                         | 114 |

| 6.1 | Comparison of shooting update time using different methods. The number<br>of time steps in one signal cycle is $M = 400$ , and the partition number $p$ is                                                                                  |     |

|     | chosen as 100                                                                                                                                                                                                                               | 144 |

| 6.2 | Selection of the partition number $p$ can affect the performance of the par-<br>allel solver. The measurement in this table is taken from the DC-converter<br>example, with $p$ changed to show the difference. There are totally $M = 400$ |     |

|     | time steps in one signal cycle, which are separated into $p$ partitions                                                                                                                                                                     | 148 |

| 7.1 | CPU and GPU time comparisons (in seconds) for solving Newton update equation with the proposed Gear-2 sensitivity.                                                                                                                          | 167 |

### Chapter 1

### Introduction

### 1.1 Circuit simulation in nanometer regime of VLSI

Current VLSI design and fabrication technologies have marched relentlessly into nanometer scale. With the Moore's Law still dominant in this industry, although challenged more than ever, the term "deep sub-micron" used one decade ago are now fairly outdated. The 45 nm integration has already become the mainstream technology, and 22 nm transistors are not new any longer. To continue the trend of Moore's Law, more integration capability is exploited from 3-dimensional structure in the chip. In a word, the IC industry is still leading, and is expected to do so in the near future, the technology endeavor towards making cheaper, smaller, more efficient, and more powerful electronics devices for us.

This success is made possible in part by the electronic design automation (EDA) community, from both academia and industry parts. The SPICE circuit simulator is a perfect model for the software solution in this area. Originated from a course project in UC Berkeley in the early 1970s, it first evolved into a research tool in the university. Then it was

adopted and commercialized by companies and became the forerunner of the whole EDA area. Through the intensive research and development in the past several decades, SPICE and its variants are now playing crucial parts in almost every EDA software vendor's product solutions. With the facilitation of EDA tools, the IC industry gains much more efficiency and productivity than before. However, the state-of-the-art IC design also raises more tough challenges to EDA algorithms and tools. The cutting edge IC technologies do not only bring sophisticated specification and verification requirements to EDA methodologies, but also introduce more difficult issues on the algorithm and computation level. For example, the modeling and simulation of chip interconnection at the nanometer integration scale need to consider the parasitic effects and process variations, which tend to increase the computation complexity such as huge matrix size in the numerical analysis. Without novel modeling and simulation algorithms, the analysis of a full chip design could take many days to finish. In case several design modification cycles are involved, the total computation cost is too prohibitive to meet the time to market demand. Therefore, new EDA algorithm and implementation are always essential driving forces to make IC product competitive in this industry's evolution.

Among all the issues in EDA applications in nano-scale integration, variability in IC design and fabrication is a critical challenge to the continued scaling and effective utilization of CMOS technologies. While people at foundry part are doing their best to minimize transistor variation through technology optimization, the designer and EDA tools should also ensure robust product functionality and performance during their design phase.

Transistor mismatch is the primary obstacle to reach a high-yield rate for analog

designs in sub-90 nm technologies. For example, due to an inverse-square-root-law dependence with the transistor area, the mismatch of CMOS devices nearly doubles for every process generation less than 90 nm, and the 3- $\sigma$  variation of drain currents reaches beyond 30% [1,2]. Since the traditional worst-case or corner-case based analyses are so pessimistic that they sacrifice the speed, power, and area, the statistical approach [2–7] thereby becomes a trend to estimate the analog mismatch. Same as the process variation, there are two types of mismatch. One is systematical or global spatial variation, and the other is stochastic or local random variation. Analog circuit designers usually perform Monte Carlo (MC) analysis to analyze the stochastic mismatch and predict the statistical functionality of their designs. As MC analysis requires a large number of repeated circuit simulations, its computational cost is expensive. Moreover, the pseudo-random generator in MC introduces numerical noises that may lead to errors.

This thesis is motivated by the aforementioned two aspects: fast and scalable computation and accurate and reliable results. We want to develop efficient and accurate algorithm for circuit simulation and statistical analysis, while we obtain additional speedup by digging out the parallelizable part underlying the algorithm, or by rearranging the algorithm so that parallelizable part becomes outstanding. In this way, GPU platforms will perform their marvelous data parallel power in our applications.

In the next section, we will review briefly the CUDA GPU computing platform, where a majority of the researches in this thesis are done.

### 1.2 CUDA GPU architecture and programming

We stress at the beginning that most of the features of GPU, both advantages and limitations, comes from the fundamental design philosophy of GPU chips — GPU dedicates much more chip area to processing cores while its control logic and memory models are simpler if compared to multi-core CPU. Therefore, to get the best performance, one should use GPU on those numerically intensive tasks with simple control logic requirements. This execution style is also called single-program, multiple-data (SPMD).

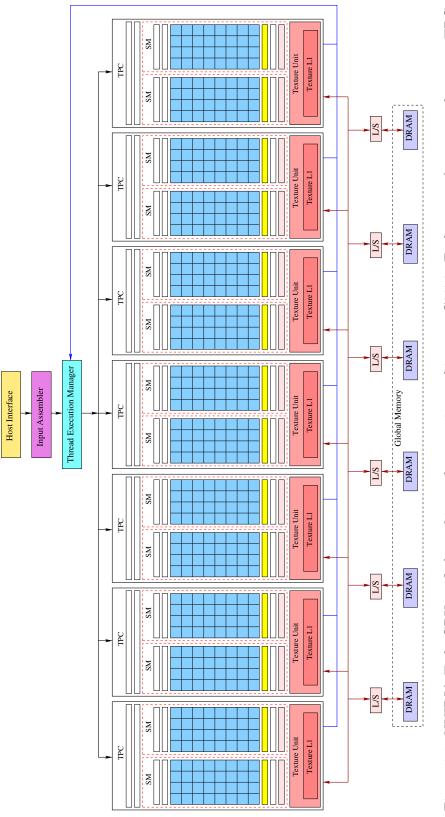

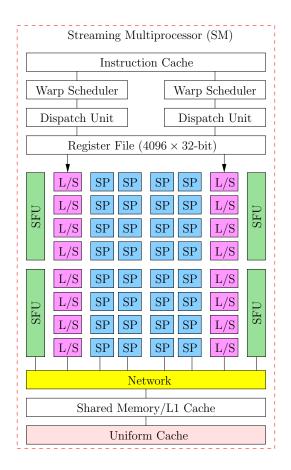

CUDA, short for Compute Unified Device Architecture, is the parallel programming model for NVIDIA's general-purpose GPUs. The architecture of a typical CUDAcapable GPU is built around a scalable array of highly threaded streaming multiprocessors (SM) and comes with the GPU card's own DRAMs, referred to as global memory. Current CUDA GPU cards have from 768 to 12,288 concurrently executing threads. Transparent scaling across this wide range of available parallelism is a key design goal of both the GPU architecture and the CUDA programming model [8]. Take the Tesla C2070 GPU for example. Fig. 1.1 shows the C2070 GPU with 14 SMs interconnected with several external DRAM partitions. Each of these 14 SMs has 32 streaming processors (SPs, or CUDA cores called by NVIDIA), 4 special function units (SFU) for transcendental functions, one multithreaded instruction unit, and its own on-chip shared memory/L1 cache. The SM in C2070 can creates, manages, and executes up to 1,536 concurrent threads in hardware with zero scheduling overhead. The structure of a streaming multiprocessor is shown in Fig. 1.2.

As the programming model of GPU, CUDA extends C into CUDA C and supports tasks such as threads calling and memory allocation, which make programmers able

Figure 1.1: NVIDIA Tesla GPU unified graphics and computing architecture C2070. Each texture/processor cluster, or TPC, is composed of two streaming multi-processors. The off-chip DRAMs are accessible to all threads and are referred to as global memory. L/S is short for load/store.

Figure 1.2: Diagram of a streaming multiprocessor in NVIDIA Tesla C2070. (SP is short for streaming processor, L/S for load/store unit, and SFU for Special Function Unit.)

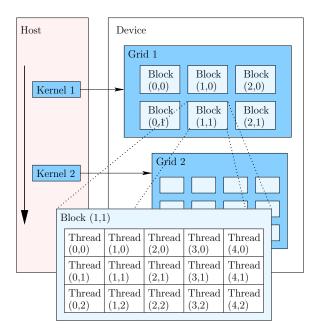

to explore most of the capabilities of GPU parallelism. In CUDA programming model, illustrated in Fig. 1.3, threads are organized into thread blocks; thread blocks are further organized into grids. When a CUDA program on the host CPU invokes a kernel grid, the compute work distribution (CWD) unit enumerates the blocks of the grid and begins distributing them to SMs with available execution capacity. The threads of a thread block execute concurrently on one SM. As thread blocks terminate, the CWD unit launches new blocks on the vacated multiprocessors.

Note that it is not correct, or at least not quite precise, to view a GPU core or CUDA core as a freely controlled processing core equivalent to the ones in a multi-core CPU. Although threads within a block will actually execute on multiple CUDA cores within the SM, the number of thread blocks shall be understood as the analogy to "processor count" in parallel algorithm analysis. It is at the thread block level or SM level where internal communication is cheap and external communication becomes expensive. Therefore, focusing on the decomposition of work into a number of thread blocks with appropriate size is the most important factor in tuning the performance. Developers can write programs running millions of threads with thousands of blocks in parallel. This massive parallelism forms the reason that programs with GPU acceleration can be much faster than their CPU counterparts.

CUDA C programming language creates its extended keywords and built-in variables. For example, in order to distinguish the parallel threads in a kernel launch, two index variable structures,  $blockIdx. \{x,y,z\}$  and  $threadIdx. \{x,y,z\}$ , are provided. They assign unique coordinates, or say IDs, to all blocks and threads in the whole grid partition.

Therefore, programmers can easily map the data partition to parallel threads, and instruct the specific thread to compute its own responsible data elements. Fig. 1.3 shows an example of 2-dim blocks and 2-dim threads in a grid, the block ID and thread ID are indicated by their row and column positions. This figure shows the two-level parallelism in CUDA computing: Parallel SMs compute result blocks, and parallel threads in each block compute result elements.

CUDA also assumes that both the host (CPU) and the device (GPU) maintain their own separate memory spaces, referred to as host memory and device memory, respectively. For every block of threads, the on-chip shared memory is accessible to all threads in that same block, thus providing efficient cooperation and communication amongst threads in a block. And the global memory, i.e., DRAMs on GPU card, is accessible to all threads in all blocks. However, due the lack of large cache and the required time to refresh charges on the DRAM, the latency of reading and writing data on global memory is long. To hide this latency, it is particularly advantageous when a thread block can load a block of global data into on-chip shared memory, process it with the parallel threads, and then write the final result back out to global memory. Coalesced memory access is favored by GPU. When threads of a warp access aligned and consecutive words in memory, the hardware is able to group these accesses into aggregate transactions with the memory system, resulting in substantially higher memory throughput. For instance, a warp of 32 threads gathering from widely separated addresses will issue 32 requests to memory, while a warp reading 32 consecutive words will only issue 2 requests.

To achieve best efficiency, kernels should avoid execution divergence, where threads

Figure 1.3: The programming model of CUDA. When Kernel 1 is launched on GPU, a 3-by-2 grid of 6 thread blocks is created, and each block in Kernel 1 is organized into a 5-by-3 array of threads.

within a warp follow different execution paths. Divergence between warps, however, introduces no performance penalty. This means the programmer should minimize the conditional switches in statements such as if-then-else.

One thing to mention is that for current GPUs, computations of double-precision float number is still slower than single-precision ones due to the limit of ALUs. Thus, for applications whose execution time is dominated by floating point computations, switching from single-precision to double-precision will decrease performance remarkably. However, this situation is being improved. Newer models of NVIDIA GPUs can provide much better double-precision performance than before.

### 1.3 Objectives and results of this thesis

The main objective of this thesis is to explore and improve circuit simulation algorithms, such as Monte Carlo and transient analysis, and propose new implementations on modern computing platforms. Efficient and reliable statistical analysis and parallel methodology of very large scale integrated circuits will be presented through the researches. The key contribution of these researches is the introduction and the exploration of several novel techniques for statistical analysis and circuit simulation on both time domain and frequency domain. The major achievements accomplished in this dissertation are as follows.

- Symbolic based statistical analysis with GPU. This work is based on a powerful graph based symbolic technique. With the proposed new algorithms, we extend the application of this technique to run parallel Monte Carlo simulation on GPU. Experiments show that our GPU MC analysis brings 2–3× speedup over HSPICE MC simulation. In another independent work, this same symbolic technique is used as a fundamental stage where a novel performance bound analysis is built upon to obtain statistical information.

- Fast parallel power grid simulation on heterogeneous CPU-GPU platforms. To cope with the ever increasing size of power grid circuit, model order reduction technique is applied to generate a smaller system with tolerable approximation error. Then GPU parallel computing is introduced in transient simulation of this reduced model for speedup. The fine-grained thread level parallelization of GPU on the transient simulation makes significant speedup on industrial benchmark circuits.

• GPU based iterative GMRES solver in a variety of applications. Krylov subspace based iterative GMRES solver is used in thermal simulation of 3D ICs. For the thermal modeling and simulation of 3D IC with liquid cooling system, we implement GPU GMRES solver suited to the characteristics of 3D IC's equivalent thermal circuit models. The computation intensive procedures in GMRES such as subspace constructions are made parallel. With well chosen preconditioners, we gain further speedup in the equation solving phase.

Variants of GPU GMRES are also applied to PSS shooting method for RF simulation and envelope-following method for power converter simulation, in which a matrix-free technique for subspace basis vector generation is used to avoid the cost incurred from explicitly building the Jacobian matrix. We demonstrate the efficiency of our methods by comparing both accuracy and acceleration in practical design examples.

### **1.4** Organization of the thesis

To carry out statistical analysis on circuits, Chapter 2 and Chapter 3 both start from determinant decision diagram (DDD) based symbolic method, which generates the expressions of circuit transfer functions in frequency domain. Chapter 2 describes a novel data structure and computation algorithm for parallel DDD evaluation on GPU platforms, and hence results in faster parallel Monte Carlo simulation. In contrary to this Monte Carlo analysis, Chapter 3 deploys an optimization approach on symbolic expressions of transfer functions, and calculates the lower and upper performance bounds of magnitude and phase of the transfer function, which is called non Monte Carlo method. With this frequency domain performance bounds and a given time domain input stimulus signal, Chapter 3 further applies uncertainty region method and signal processing techniques to determine time domain performance bounds of the output signal.

Chapter 4 to Chapter 7 focus on fast transient simulation of power grid circuits, 3D thermal circuit models, radio frequency/monolithic microwave circuits (RF/MM IC), and power converter circuits. Various GPU features are used in these works. Chapter 4 first reduces the order of power grid circuit, which is usually large and costs high computation time and memory. Then the reduced system is transferred to GPU, where large number of current sources in the grid can be evaluated independently in parallel and the linear algebra operations such as triangular solves, matrix-vector multiplications, and vector additions can also be accelerated by GPU fine-grained parallelism.

Chapter 5 first describes the background of state-of-the-art modeling of 3D IC with liquid cooling system, and then derives the thermal circuit model for this thermal system. To accelerate the solving of large equations in the transient simulation, GPU based GMRES iterative solver is applied. We also investigate good preconditioners for GMRES in order to accelerate the iterative solver. Various parts in the solver are made parallel on GPU and the programming details are talked about in this chapter.

Chapter 6 uses a modified GMRES solver in shooting problem for steady state analysis of RF/MM circuits. A core problem related to shooting analysis is the solving of a Newton update equation. The benefit of using this modified GMRES as solver of Newton update is the capability to calculate Krylov subspace independently. Hence, parallel GPU thread blocks work on these subspaces simultaneously. The mathematics and formulation of the shooting problem is provided, and detailed GPU algorithm implementation is also discussed. With a similar Newton update problem in the envelope-following method, Chapter 7 develops a tool for the simulation of power converter circuits by using GPU GM-RES solver and Gear-2 integration scheme, both of whom help deliver speedup and ensure accuracy.

Finally, Chapter 8 concludes the thesis with brief summaries of the works, and gives proposal for some future works.

### Chapter 2

# DDD based Monte Carlo analysis on GPU

This chapter shows a new parallel statistical analysis method for large analog circuits using determinant decision diagram (DDD) based graph technique based on GPU platforms. DDD-based symbolic analysis technique enables exact symbolic analysis of vary large analog circuits. But we show that DDD-based graph analysis is very amenable for massively threaded based parallel computing based on GPU platforms. We design novel data structures to represent the DDD graphs in the GPUs to enable fast memory access of massive parallel threads for computing the numerical values of DDD graphs. The new method is inspired by inherent data parallelism and simple data independence in the DDDbased numerical evaluation process. Experimental results show that the new evaluation algorithm can achieve about one to two order of magnitudes speedup over the serial CPU based evaluations and 2–3 times speedup over numerical SPICE-based simulation method on some large analog circuits.

### 2.1 Introduction

It is well known that analog and mixed-signal circuits are very sensitive to the process variations as transistor matching and regularities are required. This situation becomes worse as technology continues to scale to 90 nm and below owing to the increasing processinduced variability [9,10]. For example, due to an inverse-square-root-law dependence with the transistor area, the mismatch of CMOS devices escalates by two times for each process generation less than 90 nm [1,2]. To consider the impacts of process variations on circuit performance, Monte Carlo based statistical approaches are the most reliable solutions to this problem. But the prohibitive computational cost of Monte Carlo method prevents it from solving large analog circuits.

Modern computer architecture has shifted towards designs that employ multiple processor cores on a chip, so called multi-core processor [11,12]. GPUs are one of the most powerful many-core computing systems in mass-market use. For instance, NVIDIA Tesla T10 chips have a peak performance of over 1 TFLOPS versus about 80–100 GFLOPS of Intel i5 series Quad-core CPUs [13]. In addition to the primary use of GPUs in accelerating graphics rendering operations, there has been considerable interest in exploiting GPUs for general purpose computation (GPGPU) [14]. Accordingly, the introduction of new parallel programming interfaces for general purpose computations, such as Computer Unified Device Architecture (CUDA) [15], Stream SDK [16] and OpenCL [17], has made GPUs powerful and attractive for developing high-performance tools of solving practical engineering problems. Parallelization on GPU platforms is an emerging strategy to improve the efficiency of Monte Carlo based statistical analysis method. But traditional numerical simulators such as SPICE are based on LU decomposition, and are difficult to be parallelized on GPUs due to irregular memory access and huge memory-intensive operations.

Graph-based symbolic technique is a viable tool for calculating the behavior or characteristic of analog circuits [18]. The introduction of determinant decision diagrams based symbolic analysis technique (DDD) allows exact symbolic analysis of much larger analog circuits than all the other existing approaches [19,20]. Furthermore, with hierarchical symbolic representations [21,22], exact symbolic analysis via DDD graphs essentially allows the analysis of arbitrary large analog circuits. Once the small-signal characteristics of circuits are presented by DDDs, evaluation of DDDs, whose CPU time is proportional to the size of DDDs, will give exact numerical values. One important observation is that the DDD-based simulation is very amenable for parallel computing as the main computation is distributed to each DDD node (via graph traversals) and the data dependency is very simple due to the simple binary graph structure.

In this chapter, we develop efficient parallel graph-based simulation technique based on GPU computing platforms for Monte Carlo based statistical analysis of analog circuits. We design novel data structures to represent the DDD graphs in the GPUs to enable fast memory access of massive parallel threads for computing the numerical values of DDD graphs. The new method is inspired by inherent data parallelism and simple data independence in the DDD-based numerical evaluation process. Experimental results show that the new evaluation algorithm can achieve about one to two orders of magnitudes speedup over the serial CPU based evaluations of analog circuits and 2–3 times speedup over numerical SPICE-based simulation method on some large analog circuits. Besides, the proposed parallel techniques can be used for the parallelization of many decision diagrams based applications, such as logic synthesis, optimization and formal verifications, which are based on binary decision diagrams (BDDs) and its variants [23, 24].

Section 2.2 outlines DDD-based symbolic analysis techniques. Then, we introduce the flow of the proposed GPU Monte Carlo simulation. Section 2.4 describes the proposed GPU parallel algorithm, followed by several numerical examples in section 2.5. Last, Section 2.6 makes a summary.

#### 2.2 DDD symbolic analysis

In this section, we first provide a brief overview of determinant decision diagrams (DDDs) [19] and its application to symbolic analysis.

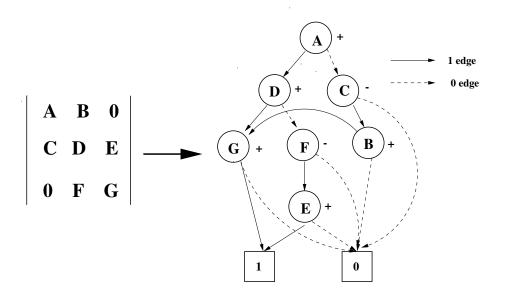

The DDD technique uses directed binary graphs to represent a determinant. The paths in the graph represent those product terms in the determinant. Since the number of paths in a graph can be much larger than the number of nodes, DDD representation enables symbolic analysis of much larger analog circuits than before [19]. The concept of DDD representation is briefly reviewed as follows. The determinant of a matrix can be expressed as the symbolic product terms from the subset of all elements in the matrix. For example, consider the following matrix determinant.

$$\det(\mathbf{M}) = \begin{vmatrix} a & b & 0 & 0 \\ c & d & e & 0 \\ 0 & f & g & h \\ 0 & 0 & i & j \end{vmatrix} = adgj - adhi - aefj - bcgj + cbih$$

(2.1)

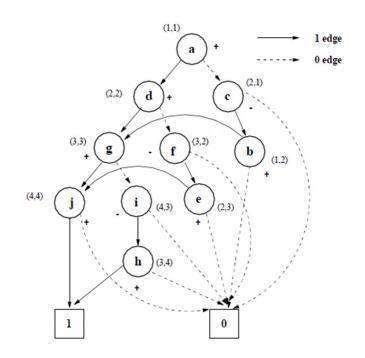

We can express each element using a node in a diagram and each product term using a path going through four nodes. For every node, it has a value of itself and a sign attached to it. The sign of each product term is decided by multiplying the sign of every node in the corresponding path. When the matrix **M** is a circuit matrix (such as modified nodal analysis (MNA) matrix), the value for each node represents the RLC value for the element in the MNA matrix. The diagram for the above matrix is shown in Fig. 2.1.

A DDD is a signed, rooted, directed acyclic graph with two terminal nodes, namely the 0-terminal node and the 1-terminal node. Each non-terminal DDD node is labeled by a symbol in the determinant denoted by  $a_i$  (a to j in Fig. 2.1), and a positive or negative sign denoted by  $s(a_i)$ . It originates two outgoing edges, called 1-edge and 0-edge. Each node  $a_i$ represents a symbolic expression  $D(a_i)$  defined recursively as follows:

$$D(a_i) = a_i \cdot s(a_i) \cdot D_{a_i} + D_{\overline{a}_i}, \qquad (2.2)$$

where  $D_{a_i}$  and  $D_{\overline{a}_i}$  represent, respectively, the symbolic expressions of the nodes pointed by the 1-edge and 0-edge of  $a_i$ . The 1-terminal node represents expression 1, whereas the 0-terminal node represents expression 0. For example, node h (in Fig. 2.1) represents expression h, and node i represents expression -ih, and node g represents expression gj-ih. We also say that a DDD node q represents an expression defined the DDD sub-graph rooted

Figure 2.1: DDD representation for matrix **M**.

at g. For each node, there are two values,  $v_{\text{self}}$  and  $v_{\text{tree}}$ . In (2.2),  $v_{\text{self}}$  represents the value of the element itself, which is  $D_{a_i}$ ; while the  $v_{\text{tree}}$  represents the value of the whole tree (or sub-tree), which is  $D(a_i)$ .

A 1-path in a DDD corresponds with a product term in the original DDD, which is defined as a path from the root node (a in our example) to the 1-terminal including all symbols and signs of the nodes that originate all the 1-edges along the 1-path. In our example, there exist five 1-paths representing five product terms: adgj, adhi, aefj, bcgj, and cbih. The root node represents the sum of these product terms. Size of a DDD is the number of DDD nodes, denoted by |DDD|.

Once a DDD has been constructed, its numerical values of the determinant it represents can be computed by performing the depth-first type search of the graph and performing (2.2) at each node, whose time complexity is linear function of the size of the graphs (its number of nodes). The computing step is called the evaluation of D, where D is a DDD root. With proper node ordering and hierarchical approaches, DDD can be very efficient to compute transfer functions of large analog circuits [19, 22].

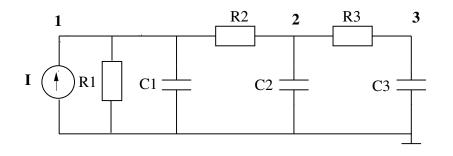

Now we use a circuit example to illustrate the idea of DDD. A simple RC filter circuit is shown in Fig. 2.2. Its MNA formulation can be written as  $\mathbf{Y} \cdot \mathbf{v} = \mathbf{i}$ , where  $\mathbf{Y}$  is the MNA matrix, i.e.,

$$\begin{bmatrix} \frac{1}{R_1} + sC_1 + \frac{1}{R_2} & -\frac{1}{R_2} & 0\\ -\frac{1}{R_2} & \frac{1}{R_2} + sC_2 + \frac{1}{R_3} & -\frac{1}{R_3}\\ 0 & -\frac{1}{R_3} & \frac{1}{R_3} + sC_3 \end{bmatrix}$$

$\mathbf{i} = [I(s), 0, 0]^{\mathrm{T}}$  is the right-hand side vector of current stimulus, and the vector of nodal voltages to be solved is  $\mathbf{v} = [v_1(s), v_2(s), v_3(s)]^{\mathrm{T}}$ .

We view each entry in the circuit matrix as a distinct symbol, and rewrite its system determinant in the left part of Fig. 2.3. Then its DDD representation is shown in the right part.

Figure 2.2: A RC filter circuit.

Figure 2.3: A matrix determinant and its DDD representation.

## 2.3 Parallel evaluation of DDD

In this section, we first provide an overview of our graph-based GPU-based parallel statistical analysis before the detailed explanation.

As mentioned before, in DDD-based analysis, computing numerical value of the determinant of the DDD essentially boils down to the depth-first traversal of the graph. The data dependency is very simple: a node can be evaluated only after its children are evaluated. Such dependency implies the parallelism where all the nodes satisfying this constraint can be evaluated at the same time. Also, in statistical frequency analysis of analog circuits, evaluation of a DDD node at different frequency points and different Monte Carlo runs can be performed in parallel. We show that all those parallelism will be explored by the new statistical analysis approach on GPU platforms.

#### 2.3.1 The overall algorithm flow

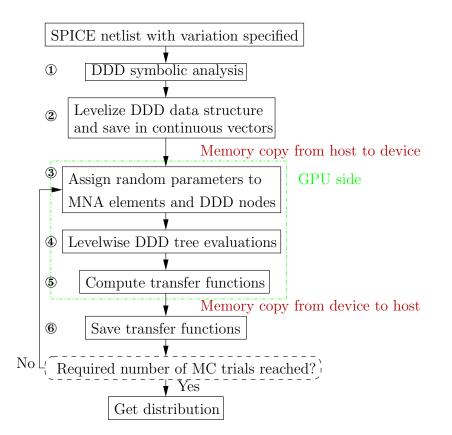

Fig. 2.4 gives the overall flow of our statistical method. The whole algorithm has two main parts, the CPU part (host) and GPU part (device) as clearly marked in the figure. CPU part mainly reads the netlist, generate the original DDD tree structures and builds new continuous DDD vector array structure (for GPU) and outputs the final numerical results. GPU part takes care of the main parallel DDD evaluation and communicates with CPU. The new program reads input netlist containing variation information of the relevant circuit devices. Then, the analyzer builds the MNA (modified nodal analysis) matrix and DDD binary tree data structure [19] as shown in step ①.

#### 2.3.2 Continuous and levelized DDD structure

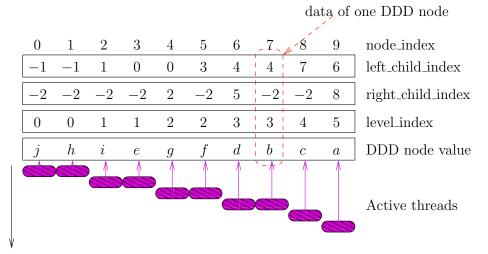

To prepare for the GPU computing, we need to build new data structures from the original binary tree DDD structures. This will be done in the CPU as the construction only needs to be performed once and traversal of original DDD linked trees is still sequential in nature and will be difficult to handle in GPU, as labeled <sup>(2)</sup> in Fig. 4.2.

For GPU computing, the main challenge is to allow fast memory access by threads or reduce memory traffic as much as possible by using shared memory (or texture memory) within blocks so that GPU cores can be busy all the time. In GPU, fast global memory access by threads can be done by coalesced memory access where a half warp (or a warp) of threads (16 or 32 threads respectively) can read their data from the global memory in one read access. Coalesced memory access requires that data are arranged continuously in memory and consecutive with respective to involved thread indexes. As a result, we need

Figure 2.4: The flow of GPU-based parallel Monte Carlo analysis.

to remap the linked DDD trees into a memory-continuous data structure.