# **UCLA**

## **UCLA Electronic Theses and Dissertations**

### **Title**

Coated Silicon Nanowires as Anodes in Lithium Ion Batteries

### **Permalink**

https://escholarship.org/uc/item/9396h6hk

### **Author**

Watts, David James

## **Publication Date**

2014

Peer reviewed|Thesis/dissertation

## UNIVERSITY OF CALIFORNIA

Los Angeles

Coated Silicon Nanowires as Anodes in Lithium Ion Batteries

A thesis submitted in partial satisfaction of the requirements for the degree Master of Science in Chemistry

by

**David James Watts**

#### ABSTRACT OF THE THESIS

Coated Silicon Nanowires as Anodes in Lithium Ion Batteries

by

#### **David James Watts**

Master of Science in Chemistry

University of California, Los Angeles, 2014

Professor Sarah H. Tolbert, Chair

Even though it has the highest known theoretical specific capacity of any material (~3600 mAh/g), silicon has limited use as an anode in lithium ion batteries due to the mechanical instability caused by the large volume expansion that occurs upon Li insertion. This volume expansion not only contributes to mechanical instability in the active silicon, but it also contributes to mechanical instability in the solid electrolyte interphase (SEI), a film formed at the end of the first lithiation step. The result of this mechanical instability in the SEI is diminished cycling performance. Modifying the SEI formation by growing a SiO<sub>2</sub> layer on silicon nanowires (SiNW) or coating them with Li<sub>x</sub>Al<sub>y</sub>Si<sub>z</sub>O (LASO), we report improved cycle life and rate capability. Here we show SiNW with a thin SiO<sub>2</sub> layer achieved nearly 400 cycles at a capacity of 2400 mAh/g and LASO-coated SiNW cycled stably at 5.5C.

The thesis of David James Watts is approved.

Laurent G. Pilon

Xiangfeng Duan

Sarah H. Tolbert, Committee Chair

University of California, Los Angeles

2014

# TABLE OF CONTENTS

| List of Figures                                                 | V         |

|-----------------------------------------------------------------|-----------|

| List of Tables                                                  | vii       |

| Acknowledgments                                                 | viii      |

|                                                                 |           |

| CHAPTER 1: Coated Silicon Nanowires as Anodes in Lithium Ion Ba | atteries1 |

| 1.1 Introduction                                                | 1         |

| 1.2 Experimental                                                | 7         |

| Silicon Nanowire Array Preparation                              | 7         |

| Silicon Dioxide Coatings                                        | 7         |

| LASO Coating.                                                   | 8         |

| SEM/TEM/SAED/XRD Characterization                               | 8         |

| Electrochemical Studies                                         | 9         |

| Sample Weight                                                   | 10        |

| 1.3 Results                                                     | 11        |

| 1.4 Conclusion                                                  | 28        |

| 1.5 Acknowledgments                                             | 28        |

| 1.6 References                                                  | 28        |

## LIST OF FIGURES

## **CHAPTER 1: Coated Silicon Nanowires as Anodes in Lithium Ion Batteries**

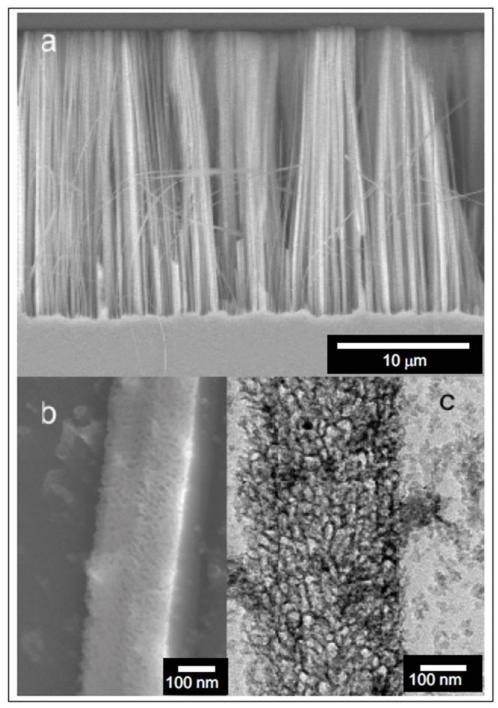

| Figure 1.1 | The structure of as-synthesized porous S1NW. a) SEM cross section view of S1NW                  |

|------------|-------------------------------------------------------------------------------------------------|

|            | arrays formed from the etching of p-Si in HF/Ag+, b) close up SEM of a single                   |

|            | porous SiNW showing the thin pore walls and continuous nature of the nanowires, c)              |

|            | TEM of a single SiNW showing pores and the 5-10 nm thick walls between the                      |

|            | pores                                                                                           |

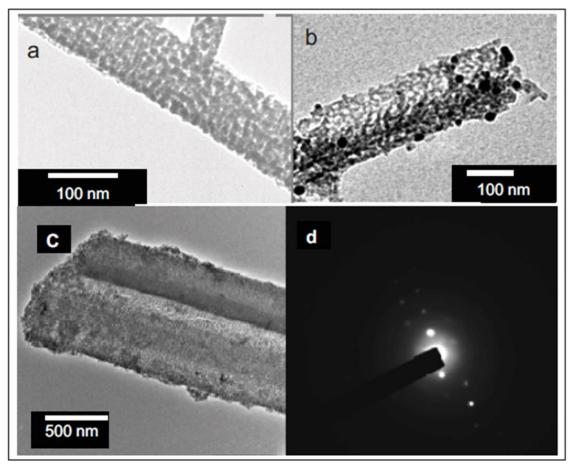

| Figure 1.2 | TEM studies of SiNW before cycling. a) TEM of the SiNW after formation and                      |

|            | etching in 10% HNO <sub>3</sub> showing the porous nature of the wire, b) SiNW without          |

|            | washing in HNO <sub>3</sub> showing the presence of Ag nanoparticles ranging in size from 3-    |

|            | 15 nm on the surface. These nanoparticles cause the porosity of the wires by                    |

|            | burrowing through them during wire formation. c) and d) Nanowire image and the                  |

|            | corresponding SAED showing the as-formed wires to be single crystalline14                       |

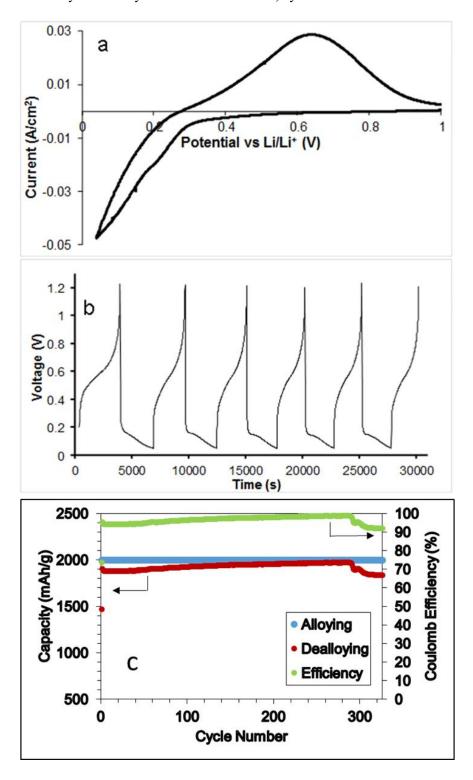

| Figure 1.3 | Electrochemical characterization of SiNW. (a) Cyclic voltammogram of Li <sup>+</sup> alloying   |

|            | with SiNW, cycled at 5 mV/s, (b) Representative galvanostatic alloying/dealloying               |

|            | curves for SiNW, cycled at 0.4 mA/cm <sup>2</sup> , (c) Alloying Capacity, Dealloying Capacity, |

|            | and Coulomb Efficiency versus Cycle Number for SiNW, cycled at 0.72C18                          |

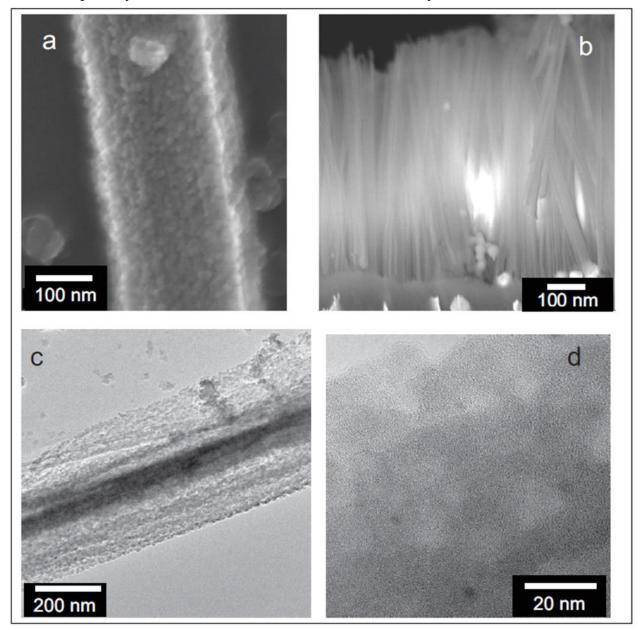

| Figure 1.4 | The structure of the SiNW after cycling 100x at IC. Parts a and b are SEM, and parts       |

|------------|--------------------------------------------------------------------------------------------|

|            | c and d are TEM. Parts (a) and (b) show that both the nanoscale porosity and the           |

|            | nanowire array itself are stable to cycling. High resolution images (c) and (d) further    |

|            | show that both porosity and a connected network are retained in the cycled                 |

|            | wires                                                                                      |

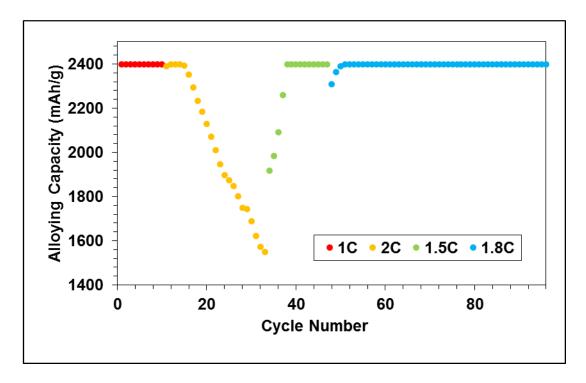

| Figure 1.5 | Rate Capabilities of bare SiNW                                                             |

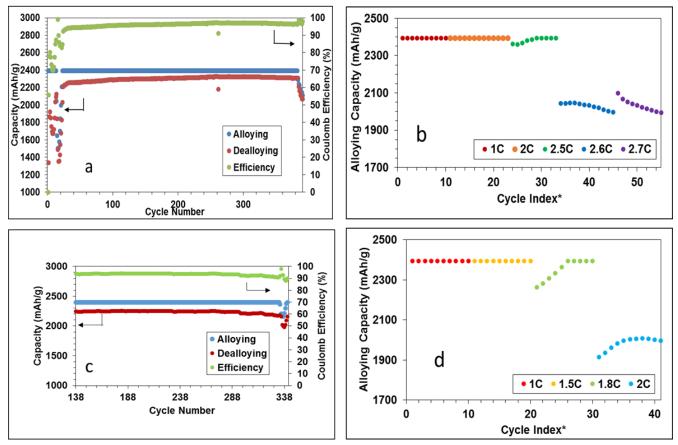

| Figure 1.6 | Cycling data for silica-coated SiNW. a) Alloying Capacity, Dealloying Capacity, and        |

|            | Coulomb Efficiency versus Cycle Number for a SiNW sample dipped in HNO <sub>3</sub> for    |

|            | 30 seconds and cycled at rates below the max rate, b) Rate capabilities for SiNW           |

|            | sample dipped in HNO <sub>3</sub> for 30 seconds, *The cycling data was not necessarily    |

|            | collected chronologically in the order presented. c) Alloying Capacity, Dealloying         |

|            | Capacity, and Coulomb Efficiency versus Cycle Number for this 26 hour sample               |

|            | cycled at 1.8C. Before cycle 138, this sample was cycled at a range of rates between       |

|            | 1C and 2.5C. d) Rate capabilities for SiNW sample dipped in HNO <sub>3</sub> for 26 hours, |

|            | *The cycling data was not necessarily collected chronologically in the order               |

|            | presented                                                                                  |

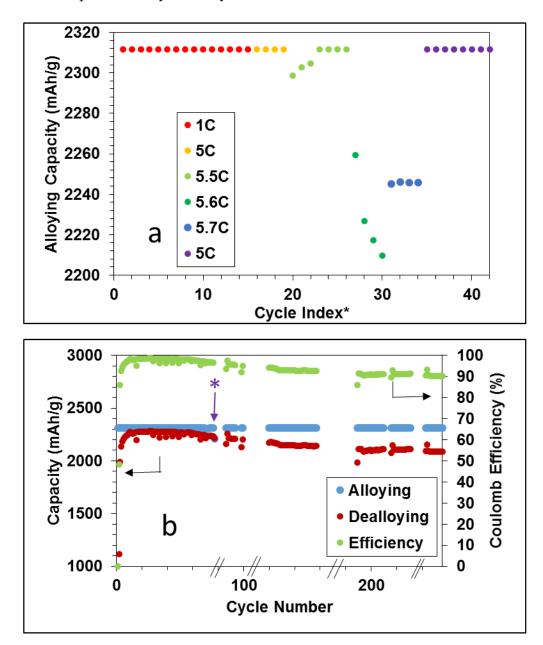

| Figure 1.7 | Cycling data for LASO-coated SiNW. a) Rate capabilities for LASO-coated sample,            |

|            | *The cycling data was not necessarily collected chronologically in the order               |

|            | presented. b) Alloying Capacity, Dealloying Capacity, and Coulomb Efficiency               |

|            | versus Cycle Number for this LASO-coated sample cycled at a range of rates                 |

|            | between 1C and 5.8C. The purple asterisk (*) indicates cycle 77, where the max rate        |

|            | (5.5C) was first exceeded. There are breaks (//) in the Cycle Number axis where the        |

|            | sample did not cycle stably                                                                |

# LIST OF TABLES

| CHAPTER 1: Coated Silicon Nanowires as Anodes in Lithium Ion Batteries |                                                                                      |     |  |  |

|------------------------------------------------------------------------|--------------------------------------------------------------------------------------|-----|--|--|

| Table 1.1                                                              | Summary of galvanostatic cycling studies of bare, thin silica, thick silica, and LAS | SO- |  |  |

|                                                                        | coated SiNW samples.                                                                 | .27 |  |  |

#### ACKNOWLEDGMENTS

In all honesty, I don't think I went to graduate school for the right reasons. After spending a few years at UCLA, I felt like I had to do something else with my life. On April 19, 2013, my p. i., Professor Sarah Tolbert gave me a necessary kick in the pants. I began working a lot more in lab and I began seeing promising data. Eventually, I had what I believed was a respectable amount of good data. When I decided that I needed to leave graduate school for my mental health's sake, I had to make a decision. I could do one of three things: I could take a leave of absence, I could immediately leave with a course-work Master's, or I could spend an extra quarter at UCLA writing a Master's thesis. I chose the latter option and I decided to write this Master's thesis because I felt like it was worth reporting some of the exciting cycling data that I had collected while working in the Tolbert group.

I'd like to thank Professor Sarah Tolbert. While she has supervised my research, she has also gone above and beyond to help me with some of my life challenges. I am especially grateful for her willingness to take me to counseling services at UCLA when I was going through a very rough time mentally.

I'd also like to thank my best friend, coworker, and roommate Abraham Buditama. I met Abraham my first day of graduate school in August 2010. He has been and continues to be a positive influence in my life, especially when I am struggling mentally with many of the disappointments I've experienced in graduate school and life in general.

I'd also like to thank my coworker and friend John Cook. John has been and continues to be a great asset to our lab.

Another coworker I owe a lot of thanks to is Chris Kang. He helped me tremendously when I was struggling to make sense of silicon cycling data and was a great person to talk to when times were hard in graduate school.

Of course, I cannot forget to thank my collaborator Jay Cho, a student in Professor Jane Chang's group, for coating my silicon nanowires and continuing to provide immense help with the silicon anode project.

While I did not get to meet E. Joseph Nemanick and Jacob T. Cox, I do want to say thank you to them for laying the ground work for my silicon anode project and especially Dr. Nemanick for the advice he has provided to me via e-mail.

I'd also like to thank Lisa Dudek. Now Dr. Dudek, Lisa was my first mentor in graduate school. She taught me how to do useful things for my silicon anode project, such as how to use HF safely and how to use the potentiostat software.

Prof. Sarah H. Tolbert has directed the research presented in this thesis. This work was supported by the center for Molecularly Engineered Energy Materials (MEEM), an Energy Frontier Research Center funded by the US Department of Energy (D.O.E.), Office of Science, Office of Basic Energy Sciences under Award Number DE-SC0001342.

#### **CHAPTER 1**

#### **Coated Silicon Nanowires as Anodes in Lithium Ion Batteries**

#### 1.1 Introduction

Lithium ion batteries are widely used in small portable electronic devices.<sup>1–3</sup> Replacing the typical graphitic carbon anode with a silicon anode has the potential to increase power and energy density of lithium ion batteries. Silicon is an attractive anode material because it has the highest known theoretical lithium ion storage capacity of any material. At room temperature, silicon can alloy with lithium to form the Li<sub>15</sub>Si<sub>4</sub> state, reaching a theoretical capacity of about 3579 mAh/g. At elevated temperatures, silicon can alloy with lithium to form the Li<sub>22</sub>Si<sub>5</sub> state, reaching a theoretical capacity of 4200 mAh/g. These are both about 10 times that of the theoretical capacity of graphitic carbon (372 mAh/g).<sup>4–6</sup>

The main challenge with using silicon in batteries is the large volume expansion (approximately 300%) that occurs when lithium ions are repeatedly inserted into and removed out of silicon in the aforementioned alloying process. This volume expansion can crack the active material and shorten the battery's cycle life.<sup>7–9</sup> Many research groups have synthesized various nanostructures of silicon, which have a large surface area to volume ratio and, as a result, can better handle this volume expansion.<sup>10–13</sup> Of these nanostructures, silicon nanowires have shown superior cycling capabilities over bulk silicon anodes and many other silicon nanostructures. The rationale for this superior performance is silicon nanowires have short

lithium ion diffusion distances in the radial direction and fast electron charge transport in the axial direction.<sup>3,10,14</sup>

While nanoscale porosity is often considered to be just another form of nanostructuring, it has several distinct advantages for the work described here. Nanoporous materials combine the surface area and diffusion lengths of very small nanocrystals with a multiply-interconnected network for improved electrical conductivity. Nanoporous materials can also be much more flexible than their bulk counterparts. Conventionally, high surface area porous silicon is formed by etching bulk Si in a F<sup>-</sup> containing electrolyte at an oxidizing potential (50-100V)<sup>16</sup> or a high light flux. These porous films have features on the order of 50 nm and greater, and attempting to form thinner pore walls causes pore merging and collapse. Tollapse Previous work on porous Si for Li<sup>+</sup> anode materials has shown an improvement in the cycling of the material as the feature size, such as pore walls or particle diameter, decreases below 50 nm. Research from our group on nanoporous cathodes with 10 – 15 nm sized pores also indicates that such porosity can increase material flexibility upon cycling. Promation of Si with small, controlled pore sizes should thus allow for fast cycling and a retention of structural integrity during alloying/dealloying and the associated volume changes.

Recently, nanoporous SiNW have been synthesized from Ag<sup>+</sup>/HF etched single crystal Si. The nanowire formation process is similar to other procedures for the etching of Si, with the oxidation (injection of holes) coming from the reduction of Ag<sup>+</sup> in solution to Ag(s) in the presence of the Si and F<sup>-</sup> to form the (SiF<sub>6</sub>)<sup>2-</sup> ion.<sup>24–26</sup> The Ag(s) is then redissolved in the HF solution, regenerating the Ag<sup>+</sup> and forming H<sub>2</sub>. The wires maintained 2000 mAh/g, 1600 mAh/g, and 1100 mAh/g capacity when cycled at 0.5C, 1C, and 4.5C, respectively with alignate binder.<sup>9</sup>

Here we describe the formation of Li<sup>+</sup> secondary battery electrodes consisting of binderfree porous SiNW arrays from Ag<sup>+</sup>/HF etched single crystal Si.<sup>24</sup> These SiNW arrays form high

capacity, stable anode materials for Li<sup>+</sup> alloying and charge storage. Since we can cycle the

porous SiNW without detaching them from the Si substrate, this technology has the potential to

be integrated with other lithographically-produced devices or circuits for on-chip charge

storage.<sup>8,14</sup> These wires are electrically conductive and attached to a conductive substrate, so they

do not require the use of an inert binder and the specific capacity of electrodes can be much

higher. Also, since the Si wires are intrinsically connected to a Si substrate, volume expansion

does not ruin connection to current collector and hence, they have exciting potential for

integrated, on chip power. Matching this high capacity anode material with a similarly high

capacity cathode material could produce major strides in the field of high capacity/light weight

power sources.

In addition to cycling this binder-free all Si system, we also cycled coated SiNW. Coating the wires to improve cycling performance usually involves controlling growth of the solid electrolyte interface (SEI layer). When cycling the SiNW anode at potentials close to metal lithium, the solvent and lithium salt in the electrolyte are electrochemically reduced, forming an insoluble film called the SEI layer. This layer is electrically insulating, but conducts lithium ions. Due to expansion and contraction of the SiNW during cycling, the SEI layer is not static. When the lithium ions are intercalated into silicon, the wires expand in volume and decomposition of the electrolyte causes the formation of an SEI layer. When lithium ions are removed from silicon, the wires decrease in volume. This large volume decrease can cause cracking in the SEI layer, exposing fresh silicon to the electrolyte. During the next cycle, more SEI film is formed when the electrolyte decomposes on newly-exposed, fresh silicon. This

results in an SEI layer which grows with cycling. The growing SEI layer can hurt cycle life by increasing the lithium ion diffusion distance through the SEI film, applying extra mechanical stress to the electrode, and irreversibly consuming lithium ions and electrolyte. Clearly, forming a stable SEI layer is critical for a stable cycling in silicon anodes.<sup>6,27–29</sup>

In order to grow an SEI layer with a constant morphology, there have been significant research efforts put into growing various silicon oxides on SiNW to extend cycle life. 3,6,27,28 For example, it was found that SiNW with a 2-5 nm thick amorphous native oxide are less likely to have electrolyte reduced to form SEI than wires which have had their native oxide stripped off by HF. The result of this is the native oxide wires have a longer cycle life than oxide-free wires. It was also found that wires with an optimized surface oxide thickness can mechanically limit the volume expansion. Using this and a hollow nanostructure, double wall silicon nanotubes were synthesized. The outer silicon oxide wall was mechanically rigid and the inner hollow space allowed for the volume expansion upon lithiation. Upon cycling, the material showed a stable SEI, long cycle life, good capacity retention, and good rate capabilities. 28

Some studies have focused specifically on growing  $SiO_2$  layers on Si anodes.<sup>3,31,32</sup> In one of these studies, they varied the thickness of the  $SiO_2$  and examined the cycling behavior of these structures. They found that a thin  $SiO_2$  can suppress the volume expansion, but too thick of an  $SiO_2$  coating can diminish the specific capacity and coulomb efficiency.<sup>32</sup>

In this work, we aim to build upon these previous studies, using methods developed for precise  $SiO_2$  on Si wafer processing to grow nearly defect-free thin 0.7 to 1.4 nm thick  $SiO_2$  layers on our silicon wires. We use methods optimized to avoid high leakage current density and to avoid the high oxidation rates that can arise as a result of thermal oxidation. We use methods

based on dipping Si samples in HNO<sub>3</sub>, and varying temperature and time of immersion. This method produced samples with leakage current density as low as that for thermally grown SiO<sub>2</sub> layers and showed good reproducibility of SiO<sub>2</sub> thickness ( $\pm$  0.05 nm), since the thickness saturates within a short time of immersion in acid.<sup>33</sup>

While controlled silica layer thickness may allow us to optimize coatings for Li<sup>+</sup> conductivity, silica is still fundamentally an ionic insulator, and so only very thin coatings can be used. By moving away from silica, more chemical functionality can be achieved. For example, there has been extensive work over the past few years using both sol-gel chemistry and atomic layer deposition (ALD) to coat electrodes and improve performance. A,8,34-36 These coatings can provide physical support, preserve the mechanical structure of cycled material, protect electronic conduction pathways, and inhibit side reactions between the electrolyte and active silicon. Ald,37-39 While some non-ALD coatings seem to modify the SEI layer, ALD alumina coating applied can substitute for the SEI layer. Nguyen et. al. applied this alumina coating to SiNW and noted that the coating can act like an artificial SEI layer by forming a Li-Al-O glass film upon the first lithiation. Like the SEI layer, Li-Al-O is a lithium ion conductor and electronic insulator. Even if the ALD alumina coating cracks during cycling, it can still shield some of the active silicon material from the electrolyte. Overall, Nguyen et. al. showed that ALD alumina-coated silicon nanowires.

Despite these improvements, alumina, like silica, is still fundamentally an ionic insulator, and so only very thin coatings can be used. To address this problem, we turn to ALD coatings of  $\text{Li}_x \text{Al}_y \text{Si}_z \text{O}$  (LASO), which is an intrinsic ion conductor. Lithium aluminosilicates,  $\text{Li}_{4-3x} \text{Al}_x \text{SiO}_4$ , are Li-ion conducting metal oxide family, with a single-phased solid solution over the range of x=0 to 0.05.40 Within Lithium aluminosillicates, LiAlSiO<sub>4</sub> (x=1, also known as Beta-

eucryptite) attracted a great deal of interest as a possible electrolyte in high-temperature batteries because of its high ionic conductivity above 400 °C. 41,42 It is a derivative of high quartz, with half of the SiO<sub>4</sub>-tetrahedra of high quartz replaced by AlO<sub>4</sub> tetrahedra, where Li-ions are stuffed in the structural channels for charge neutrality. Additionally, its ionic conductivity is known to experience increase in magnitude with a decrease in its thickness, which makes it far more advantageous than other solid oxide lithium ion conductors in applications on powering micro/nanoscale devices; thereby making beta-eucryptite more favorable material to investigate for a solid electrolyte in micro lithium-ion battery applications.

Like the aforementioned ALD alumina, ALD LASO acts like an artificial SEI layer during cycling. ALD LASO is a lithium ion conductor and one benefit LASO-coated wires may have over alumina-coated wires is that a pre-lithiated anode material can be more readily paired with lithium-free cathode materials in order to make a full battery.<sup>44</sup>

Here, we made porous SiNW using the aforementioned well-developed electroless etching method. We immersed some samples in nitric acid to grow SiO<sub>2</sub> layers and we coated other samples with LASO using ALD. We present the characterization of our wires and then analyze the potentiostatic cycling data, comparing the max C-rate, initial coulomb efficiency, max coulomb efficiency, and cycle life. We found that all coated wires have similarly long cycle life. For the samples tested, there is sample-to-sample variation, but all samples are in the range from 200 – 400 cycles. The coatings differ significantly in terms of rate capability, however. For samples cycled at a capacity of 2300-2400 mAh/g, LASO-coated SiNW could accommodate the highest rate of our samples, cycling stably at 5.5C.

### 1.2 Experimental

## **Silicon Nanowire Array Preparation**

Silicon nanowire arrays were etched into 500 micrometer thick prime grade p-doped (B) silicon (100) wafers (0.001 – 0.005  $\Omega$  cm). These wafers were cut into approximately 1 cm<sup>2</sup> pieces and the back, unpolished side of the wafer pieces were marked with a small dot of nail polish. The samples were cleaned with ethanol and immersed in 5 mL of 20mM AgNO<sub>3</sub> dissolved in 10% HF at 60°C for between 10 minutes and 3 hours. Soon after immersing the samples in the etching solution, hydrogen evolution is observed and the sample becomes encased in a silver cocoon. After the nanowire arrays were etched, the sample was rinsed with 18 M  $\Omega$  water, the silver cocoon was dissolved in 69% nitric acid, and the sample was rinsed again with 18 M  $\Omega$  water. Then, the sample was rinsed with ethanol and air dried. Before cycling bare silicon nanowire arrays, samples were dipped in 48% HF for 30 seconds, rinsed with water, dipped in ethanol, and dried under flowing N<sub>2</sub>.

### **Silicon Dioxide Coatings**

Dipping the nanowire arrays in HNO<sub>3</sub> to remove the silver cocoon leaves a thin oxide layer on the nanowires. To remove this thin oxide layer and grow new SiO<sub>2</sub> layers, the nanowire arrays were dipped in 48% HF for 30 seconds, rinsed with 18 M  $\Omega$  water, then immersed in 69% HNO<sub>3</sub>. One set of nanowire arrays was removed from the HNO<sub>3</sub> bath after 30 seconds, growing a thin SiO<sub>2</sub> layer, and another set was removed after 26 hours, growing a thicker SiO<sub>2</sub> layer. Both of these samples were then rinsed with 18 M  $\Omega$  water, dipped in ethanol, and air dried.

### **LASO Coating**

Li<sub>x</sub>Al<sub>y</sub>Si<sub>z</sub>O (LASO) thin films were synthesized via atomic layer deposition in a hot-wall reactor where the chamber wall temperature was 290°C with a base pressure of 60 mTorr. Metalorganic precursors, lithium *tert*-butoxide (LTB, Strem Chemicals, 98%), trimethylaluminum (TMA, Sigma-Aldrich, 97%), and tetraethyl orthosilane (TEOS, Sigma-Aldrich, 99.999%) were used as the sources for Li, Al and Si, respectively, while H<sub>2</sub>O vapor, the oxidant, was supplied by a deionized water reservoir. LTB is a solid precursor, thus the precursor host and gas line were heated to 160°C during the process to ensure sufficient vapor flux to the surface. The gas lines of TMA, TEOS and water were heated to 60°C to prevent precursor condensation. LASO thin films were deposited by alternating ALD deposition cycles of LiOH, Al<sub>2</sub>O<sub>3</sub> and SiO<sub>2</sub> with a global cycle sequence of 10(Al-O)-6(Li-O)-4(Si-O), where a, b, c represent the local cycle number for each oxide. Five global cycles were performed to achieve a film thickness of ~10nm. Al<sub>2</sub>O<sub>3</sub> was chosen to be the first layer as it is known to have excellent adhesion to silicon.<sup>46</sup>

#### SEM/TEM/SAED/XRD Characterization

TEM images were taken both before and after the nitric acid washing so that the Ag nanoparticles could be imaged. Samples were prepared by sonicating arrays in EtOH for 10 minutes to release the wires from the substrate; the resulting solution was then dropcast onto carbon TEM grids. Low resolution TEM was performed using a Philips CM120 at 120 kV and selected area diffraction (SAED) analysis was performed on a JEOL 2100 at 200 kV. For SEM, samples were imaged either after the nitric acid wash or after both acid washing and HF etching. Samples were dried under flowing nitrogen and affixed to either a 45° stage by carbon tape or mechanically broken and imaged in cross section. For imaging of individual nanowires, arrays

were sonicated in EtOH for 10 minutes and the suspensions of nanowires was dropcast onto Si. Imaging was performed using a field emission SEM (JEOL 6700F). XRD was measured using a Panalytical XPert Pro diffractometer (Cu  $K\alpha$ ).

#### **Electrochemical Studies**

To prepare the nanowire arrays for lithium cycling studies, the nail polish on the unpolished side was removed with acetone. Wires on the unpolished side of the sample were mechanically removed with a Q-tip. Ga/In eutectic was scratched onto the exposed bulk silicon. A copper wire was attached to the sample using conductive Ag epoxy (Ted Pella Conductive Epoxy). To dry the Ag epoxy, the sample was placed in an Isotemp oven set to 80°C for 20 minutes. Then, insulating epoxy (Loctite Hysol 1C, McMaster-Carr) was applied to the entire sample, leaving only the active silicon nanowire material exposed. To dry the insulating epoxy, the sample was dried in room temperature air for 1 hour, then placed in an Isotemp oven set to 80°C for 3 hours. To remove organic compounds that are given off in the curing process, the sample was rinsed with ethanol.

For one set of samples, any surface oxide created from exposure to the air, during this preparation, was stripped away by immersing the samples into 48% HF for 30 seconds, rinsing them with water, then dunking them in ethanol. These samples were labeled as the "bare SiNW" samples. After the HF stripped off the oxide and the wires were rinsed, they were immediately placed in a pressurized  $N_2$  filled glove box for electrochemical cycling.

The other 3 sets of samples, samples with thin SiO<sub>2</sub>, samples with thicker SiO<sub>2</sub>, and LASO-coated samples, were placed in the same glove box without this final exposure to HF.

To cycle the samples, an Arbin Instruments BT-2000 potentiostat was wired into the  $N_2$  filled glove box. The electrolyte was prepared by dissolving 1.07 g lithium perchlorate (LiClO<sub>4</sub>)

in 10 ml of propylene carbonate (PC) to make a 1 M solution. Samples were cycled in a flooded cell, three electrode configuration utilizing the sample as the working electrode and pieces of lithium foil as both the counter and reference electrodes. The voltage window used was between 0.05 V and 1.2 V vs. Li/Li<sup>+</sup>. Samples were tested at cycling rates between 0.2 C to 5.8 C.

### Sample Weight

To measure the active sample mass without interference from the Si substrate, samples were first alloyed to form  $\text{Li}_x\text{Si}_y$ . The sample was then removed from the glove box and immediately dunked into a 25 mL solution of 5% HNO<sub>3</sub> and 0.1% HF, causing the  $\text{Li}_x\text{Si}_y$  to react vigorously forming  $\text{H}_2$  and  $\text{SiF}_6^{2-}$ . The sample was soaked for 30s and then rinsed with the acid solution. The Si content of the solution was then analyzed using ICP-AA. For 20  $\mu$ m SiNW samples, the mass per unit area was approximately 116  $\mu$ g/cm<sup>2</sup> according to ICP.

Because ICP results can be complicated by HF dissolving quartz components of the ICP machine, the reliability of this result was verified using microbalance measurements. Ten 20  $\mu$ m SiNW samples were weighed on a CAHN C-31 Microbalance. Then, the SiNWs on the polished side were removed using a Q-tip and the samples were weighed again. The difference should be the mass of the active SiNWs. The area of these samples was measured and calculated using a ruler. For 20  $\mu$ m SiNW samples, the mass per unit area was approximately  $113 \pm 6.58 \,\mu\text{g/cm}^2$ . Error in this measurement was calculated by propagating errors when the measurement uncertainties were set equal to the instrument limits of error. For the rest of this report, we assumed the mass of our 20  $\mu$ m SiNW samples could be calculated by multiplying the active sample area in cm<sup>2</sup> by 116  $\mu$ g/cm<sup>2</sup>.

## 1.3 Results

Figure 1.1a shows nanowire arrays formed by this etching process. For a given etching condition, the nanowires had uniform lengths, with the length determined by the etch time.  $^{24}$  Nanowire arrays were formed from 5  $\mu$ m long to over 50  $\mu$ m, and the wires formed at a rate of 13  $\mu$ m/h. Figures 1.1b and 1.1c are SEM and TEM images of single nanowires, showing the secondary porous structure of the wires. The nanowires have pores of 5-10 nm inner diameter, with pore walls 5-10 nm thickness.

**Figure 1.1** The structure of as-synthesized porous SiNW. a) SEM cross section view of SiNW arrays formed from the etching of p-Si in  $HF/Ag^+$ , b) close up SEM of a single porous SiNW showing the thin pore walls and continuous nature of the nanowires, c) TEM of a single SiNW showing pores and the 5-10 nm thick walls between the pores.

Figure 1.2 shows TEMs of SiNW freed from the substrate, with Figure 1.2a showing a fully washed SiNW. A similar wire without removal of deposited Ag nanoparticles by washing with nitric acid (Figure 1.2b) shows Ag nanoparticles on the surface as well as inside of the nanowire. These nanoparticles etched the pores in the silicon nanowires in a similar fashion to the etching seen of Si wafers by Au, Pt, and Ag. 47,48 These previous studies either used reduction of metal salts to form nanoparticles, or used direct nanoparticle deposition. The metals were placed in contact with the Si and exposed to an oxidizer such as H<sub>2</sub>O<sub>2</sub>; pores etched preferentially in the {100} family of directions. For the nanowires in this study, while the nanowires formed in the (100) direction, no preferential orientation of the pores within the nanowires was observed, and we believe that the relatively short distances (<100 nm) traveled within the nanowires prevented preferential orientation. We note that in this study, p-type Si was used, but other studies<sup>49</sup> have used n-type to form similar structures, indicating that the dopant type does influence the nanowire formation. Figures 1.2c and d show TEM of a single Si nanowire with the accompanying selected area electron diffraction (SAED) pattern indicating that the initial wires before cycling are crystalline, where only the (100) orientation is apparent.

**Figure 1.2** TEM studies of SiNW before cycling. a) TEM of the SiNW after formation and etching in 10% HNO<sub>3</sub> showing the porous nature of the wire, b) SiNW without washing in HNO<sub>3</sub> showing the presence of Ag nanoparticles ranging in size from 3-15 nm on the surface. These nanoparticles cause the porosity of the wires by burrowing through them during wire formation. c) and d) Nanowire image and the corresponding SAED showing the as-formed wires to be single crystalline.

For materials such as Si, which undergo a large volume change upon Li uptake and removal, it has been seen that the smallest dimension of the material, <sup>50,51</sup> in this case the walls between the pores, determines the maximum rate and cyclability of the material. The thin walls between the pores of the Si nanowires allows for minimal strain upon alloying/dealloying while maintaining good conductivity. The mesoporous network also allows for short diffusion lengths, thus increasing the rate at which the arrays can be cycled.

Figure 1.3 shows the electrochemical characterization of the SiNW arrays in 1 M LiClO<sub>4</sub>/PC. Figure 1.3a shows the cyclic voltammetric characterization of a 20 μm long nanowire array cycled at 5 mV/s. Cycled between 1 V and 0.05 V vs. Li(s)/Li<sup>+</sup>, the nanowires show a strong reductive/alloying peak beginning at ~0.3 V and increasing in magnitude down to 0.05 V, where the voltage polarization was reversed. As shown by the lack of a peak in the reductive current, the Si does not completely lithiate by 0.05 V at this charge rate. The full 4200 mAh/g capacity of the SiNW in forming Li<sub>22</sub>Si<sub>5</sub> cannot be reached at any potential positive enough to avoid lithium plating, so the arrays were not cycled to less than 0.05 V to avoid the electrodeposition of Li(s) rather than the lithium silicide formation. The return oxidation peak from the dealloying reaction was broader than the reductive peak, with the SiNW beginning to release their Li at ~ 0.35 V, only 50 mV positive of the onset of the reductive peak, indicating a fast, kinetically facile alloying process.

The galvanostatic alloying of a 20 µm long nanowire array is shown in Figure 1.3b, with a voltage window between 0.05V and 1.2V (versus Li/Li<sup>+</sup>) and alloying/dealloying at ±0.4 mA/cm<sup>2</sup>. The representative galvanostatic alloying/dealloying curves for the SiNW mirror the cyclic voltammogram, with relatively well-defined regions of alloying and dealloying for the SiNW, made even more distinct by the slower rate. The comparatively narrow reduction peak in the CV and the small potential range of the reduction plateau in the galvanostatic charge starting at ~0.2 V indicates that there was little kinetic overpotential for the lithiation of deeper sites, probably due to the high surface area of the nanowires. The hysteresis seen in the galvanostatic curves (~500 mV separation between the reductive and oxidative plateaus) indicates that the energy storage/extraction process was reasonably efficient.

One challenge of working with SiNW on a Si substrate is that that in some cases, the underlying Si substrate can also be lithiated. Indeed, when these SiNW are cycled slowly over a large potential window, the apparent capacity appeared to increase because additional Si was recruited to the active layer with each cycle. This problem can be alleviated by charging the electrode with a constant number of coulombs that is insufficient to fully alloy the Si wires. The porous wires, due to their high surface area and thin walls, are kinetically easier to alloy than the substrate, and so they will react first. When the total capacity is limited, only the wires will react. Using this capacity-limited cycling only alloys/dealloys the SiNW in the all Si system and thus is a unique binder-free way to cycle SiNW without removing them from the Si substrate.

Here, samples were dealloyed at 0.2 mA/cm<sup>2</sup> for 5000s (1 Coulomb/cm<sup>2</sup>, 0.72C), and alloyed at the same rate/time. This allows us to selectively examine the electrochemical performance of the nanowires without complication from the substrate. Figure 1.3c shows alloying/dealloying capacity as a function of cycle number for 326 cycles. During the capacity-limited lithiation process, a current is applied to alloy lithium with silicon, but some of the lithium is consumed in the formation of the SEI layer. During the capacity-limited delithiation process, the same magnitude of current is used to dealloy lithium. Because the alloying process needs extra lithium for the continuous SEI formation, it takes more Coulombs to complete. Hence, the alloying capacity starts out greater than the dealloying capacity for our wires, but the difference decreases as the SEI stabilizes.

Initially, there is an increase in dealloying capacity which we associate with our capacity-limited cycling and the irreversible conversion of slowly reacting crystalline Si to faster alloying amorphous Si.<sup>52,53</sup> After this initial rise, however, there is no loss of total capacity up to 292 cycles.

The data in figure 1.3c indicates a stable capacity of 2000 mAh/g. This value is lower than the theoretical 4200 mAh/g because our charge-limited technique does not allow the Si to be fully lithiated. Full lithiation requires a voltage near 0V vs. Li/Li<sup>+</sup>, and this capacity-limited cycling stopped alloying at 0.05V. This measurement thus gives a lower bound for the specific capacity of these SiNW arrays.

Figure 1.3c also shows the coulomb efficiency, defined as delithiation capacity/lithiation capacity<sup>14</sup> versus cycle number, for this sample. The initial coulomb efficiency was only 74% when the majority of the SEI was forming, but the coulomb efficiency jumped up to 96% by the second cycle and then slowly climbed up to 99%. We believe this climb in coulomb efficiency upon further cycling is due to a slowly growing SEI layer. During lithiation, as less lithium is consumed in the continuous SEI formation process, more lithium is used for the alloying process. Then, during the delithiation process, more lithium can be removed, resulting in a higher dealloying capacity and therefore, a higher coulomb efficiency.

**Figure 1.3** Electrochemical characterization of SiNW. (a) Cyclic voltammogram of Li<sup>+</sup> alloying with SiNW, cycled at 5 mV/s, (b) Representative galvanostatic alloying/dealloying curves for SiNW, cycled at 0.4 mA/cm<sup>2</sup>, (c) Alloying Capacity, Dealloying Capacity, and Coulomb Efficiency versus Cycle Number for SiNW, cycled at 0.72C.

Analysis of the porous SiNW after Li alloying cycles allows us to understand the stable cycling observed in figure 1.3c. Figure 1.4 shows the retention of individual nanowire structure porosity after cycling 100 times at a rate of 1C. Figure 1.4a shows an SEM of a single nanowire after cycling. While the sharp edges to the porosity seen in Figure 1.1b have been rounded out, the wire still shows clearly defined nanoscale porosity with a length scale similar to that observed in the uncycled wires. Both the individual nanowires and the array in Figure 1.4b show a lack of macroscopic fracturing, in contrast to observations on bulk Si materials.<sup>54,55</sup> TEM analysis of the cycled wires (Figure 1.4 c and d) further confirm the retention of porosity and indicate that pores are now surrounded by a continuous network of nanosized domains, rather than by the straight walls observed in the as-synthesized nanowires. The change is consistent with the conversion of the wire from crystalline Si, which should show well-defined facets, to amorphous Si, which should prefer more spherical domains that minimize surface area. In agreement with this hypothesis, no Si diffraction could be observed in SAED. While the cycled nanowires appear somewhat more disordered than the initial pore structure, they remain porous and structurally intact after cycling, allowing for facile ion transport, good electrical conductivity, and strain minimization during cycling.

**Figure 1.4** The structure of the SiNW after cycling 100x at 1C. Parts a and b are SEM, and parts c and d are TEM. Parts (a) and (b) show that both the nanoscale porosity and the nanowire array itself are stable to cycling. High resolution images (c) and (d) further show that both porosity and a connected network are retained in the cycled wires.

Figure 1.5 shows how we determined the maximum cycle rate for our wires. Our wires were cycled between 0.05 and 1.2V versus Li/Li<sup>+</sup>. During stable cycling, the higher voltage limit, 1.2V was reached before the capacity limit was reached. On the other hand, the lower

voltage limit, 0.05 would not be reached before the capacity limit was reached. Only when cycling at much higher C-rates was it possible to reach 0.05V before the capacity limit was reached. We define the max C-rate as the highest rate at which the full alloying capacity cannot be reached.

To examine this, consider Figure 1.5. For the first 10 cycles, the SiNW were cycled at 1C and the alloying capacity remained stable at 2400 mAh/g. When the rate was increased to 2C for cycle 11 to cycle 33, the set capacity could not be achieved in the allowed time and the alloying capacity decreased very quickly as cycle number increased. To get back to stable cycling, the rate was decreased to 1.5C. After a few cycles at 1.5C, the alloying capacity climbed back to 2400 mAh/g and remained stable at that value. A similar trend was seen when the rate was raised to 1.8C. When the rate was increased to 1.8C from cycle 48 to cycle 96, the alloying capacity dropped but then climbed back up to 2400 mAh/g, indicating that the sample could cycle stably at 1.8C. We thus put the max rate limit for this sample between 1.8C and 2.0C.

Figure 1.5 Rate Capabilities of bare SiNW

When SiNW were dipped in concentrated HNO<sub>3</sub> for 30 seconds, the rate capability and cycle life of the wires were improved. We expect this treatment to produce a silica coating about 0.75 nm thick on the surface of the porous Si wires.

Figure 1.6a shows the alloying and dealloying capacity during galvanostatic cycling of a 20 μm SiNW sample with a thin SiO<sub>2</sub> layer, grown by dipping the sample in acid for 30 seconds, cycled at rates below 2.4 C. The sample maintained a capacity of 2400 mAh/g for 398 cycles before the dealloying capacity faded. We thus record 398 as the cycle life for our wires. Figure 1.6a also shows the coulomb efficiency for this sample. The initial coulomb efficiency was 56%. The coulomb efficiency jumped up to 78% for cycle 2 and slowly climbed up to 99%.

Figure 1.6b shows the rate capability of our SiNW with a thin silica layer. At 2.6C and higher C rates, the set alloying capacity could not be achieved, but at 2.4C and 2.5C, stable

cycling at 2400 mAh/g was achieved.

When SiNW were dipped in concentrated HNO<sub>3</sub> for 26 hours, we expect to produce a silica layer ~1 nm thick. Under these conditions, neither the rate capability nor the cycle life showed improvement. Figure 1.6c shows the alloying and dealloying capacity during galvanostatic cycling of a 20 µm SiNW sample with this thicker SiO<sub>2</sub> layer, grown by dipping the sample in acid for 26 hours. When cycled at 1.8C, this sample maintained a capacity of 2400 mAh/g for over 200 cycles before the dealloying capacity faded. This sample was also cycled for another 138 cycles at a range of rates. As a result, this sample showed cycle life above 300 cycles, which is in the range that is typical for these porous nanowire samples. Figure 1.6c also shows the coulomb efficiency for this sample. The initial coulomb efficiency was just 31%, but the coulomb efficiency slowly climbed up to 94%. This maximum value is significantly lower than that obtained for other samples.

Like the capacity, the rate capability is also not improved by the thick silica coating. Figure 1.6d shows that at 2C, the sample could not maintain the set alloying capacity, but at 1.8C the set capacity of 2400 mAh/g could be achieved. Thus, it appears that a thick silica coating negates all the rate advantages observed in the thin silica and results in performance very similar to uncoated wires. In other words, a thick polymer SEI layer provides similar kinetic limitations to a silica layer that is too thick.

**Figure 1.6** Cycling data for silica-coated SiNW. a) Alloying Capacity, Dealloying Capacity, and Coulomb Efficiency versus Cycle Number for a SiNW sample dipped in HNO<sub>3</sub> for 30 seconds and cycled at rates below the max rate, b) Rate capabilities for SiNW sample dipped in HNO<sub>3</sub> for 30 seconds, \*The cycling data was not necessarily collected chronologically in the order presented. c) Alloying Capacity, Dealloying Capacity, and Coulomb Efficiency versus Cycle Number for this 26 hour sample cycled at 1.8C. Before cycle 138, this sample was cycled at a range of rates between 1C and 2.5C. d) Rate capabilities for SiNW sample dipped in HNO<sub>3</sub> for 26 hours, \*The cycling data was not necessarily collected chronologically in the order presented.

When SiNW were coated with 10 nm thick LASO, the rate capability of the wires was improved compared to that of bare SiNW. As indicated in figure 1.7a, at 5.6C and higher C rates, the set capacity of 2300 mAh/g could not be achieved, but at 5.5C, 2300 mAh/g was achieved.

Figure 1.7b shows the alloying and dealloying capacity during galvanostatic cycling of a  $20~\mu m$  SiNW sample with a LASO layer. When cycled at rates between 1C and 5.5 C, this sample maintained a capacity of 2300~mAh/g for 176~cycles before the dealloying capacity

faded.

Figure 1.7b also shows the coulomb efficiency for this sample. In contrast to other samples where significant SEI formation was needed, the initial coulomb efficiency was 92% and this value reached a maximum of 99%. After cycle 77, where the max rate was first exceeded, the coulomb efficiency decreases noticeably, possibly indicating the LASO coating was damaged.

**Figure 1.7** Cycling data for LASO-coated SiNW. a) Rate capabilities for LASO-coated sample, \*The cycling data was not necessarily collected chronologically in the order presented. b) Alloying Capacity, Dealloying Capacity, and Coulomb Efficiency versus Cycle Number for this LASO-coated sample cycled at a range of rates between 1C and 5.8C. The purple asterisk (\*) indicates cycle 77, where the max rate (5.5C) was first exceeded. There are breaks (//) in the Cycle Number axis where the sample did not cycle stably.

Table 1 compares the max C-rate, initial coulomb efficiency, max coulomb efficiency, and cycle life of bare, thin SiO<sub>2</sub>, thicker SiO<sub>2</sub>, and LASO-coated SiNW samples. Growing a thin

SiO<sub>2</sub> layer on our SiNW improves both the rate capability and cycle life of the sample. Growing a thicker oxide layer doesn't seem to improve the rate capability or the cycle life. A thicker oxide layer also seems to decrease the coulomb efficiency of the sample. This is consistent with other studies which indicate that when the oxide layer gets too thick, it hurts cycling performance. These studies indicate that a thin oxide layer may improve cycling performance by constraining the volume expansion and possibly limiting the extent of lithiation.<sup>3,27,32</sup> By contrast, coating with wires with a lithium ion conductor significantly improves the rate capability, presumably because the LASO coating prevents build-up of a thick SEI layer, and the LASO coating is a better ion conductor than either the polymeric SEI layer or the thin amorphous silica layer.

Also consistent with these studies was the effect of oxide layers on initial coulomb efficiency.<sup>3,27</sup> Comparing the bare SiNW with the oxide-coated NW, one can see that as the SiO<sub>2</sub> layer gets thicker, the initial coulomb efficiency decreases. In addition to improving the rate capability and cycle life of SiNW, LASO coating also increases the initial coulomb efficiency. Assuming a growing coulomb efficiency can be correlated with a growing SEI layer, a near unity initial coulomb efficiency for LASO-coated SiNW is a good indication that the LASO coating is acting as an artificial SEI layer.

**Table 1.1** Summary of galvanostatic cycling studies of bare, thin silica, thick silica, and LASO-coated SiNW samples.

| Sample | Max C-Rate | Initial CE | Max CE | Cycle Life |

|--------|------------|------------|--------|------------|

|        |            | (%)        | (%)    |            |

| Bare   | 1.8        | 74         | 99     | 292        |

| Thin   | 2.5        | 56         | 99     | 398        |

| Silica |            |            |        |            |

| Thick  | 1.8        | 31         | 94     | 338        |

| Silica |            |            |        |            |

| LASO   | 5.5        | 92         | 99     | 260        |

#### 1.4 Conclusion

These results indicate that all-Si porous nanowire array show exciting potential as stable, high capacity anodes. Comparing specifically the max rate, max coulomb efficiency, and cycle life, the results show that SiNW with a thin SiO<sub>2</sub> layer and SiNW with a LASO coating cycle better than bare SiNW. Limiting the capacity to 2400 mAh/g, SiNW with a thin SiO<sub>2</sub> layer had the longest cycle life of our samples with nearly 400 cycles at a capacity of 2400 mAh/g. LASO-coated SiNW had the highest rate capabilities of our samples, cycling stably at 5.5C. Overall, using capacity-limited cycling to minimize the alloying of the Si substrate, we are able to cycle our SiNW arrays at around 200 to 400 cycles at rates above 1C. Stable cycling of our all-Si system indicates exciting potential on-chip energy storage applications.

### 1.5 Acknowledgments

This work was supported by the center for Molecularly Engineered Energy Materials (MEEM), an Energy Frontier Research Center funded by the US Department of Energy (D.O.E.), Office of Science, Office of Basic Energy Sciences under Award Number DE-SC0001342. The authors of this work would like to thank Jacob T. Cox, Lisa Dudek, Chris Kang, and John Cook for their helpful research advice.

### 1.6 References

- 1. Long, J. W., Dunn, B., Rolison, D. R. & White, H. S. Three-dimensional battery architectures. *Chem. Rev.* **104**, 4463–92 (2004).

- 2. Ohzuku, T. & Brodd, R. J. An overview of positive-electrode materials for advanced lithium-ion batteries. *J. Power Sources* **174**, 449–456 (2007).

- 3. McDowell, M. T. *et al.* Novel size and surface oxide effects in silicon nanowires as lithium battery anodes. *Nano Lett.* **11,** 4018–25 (2011).

- 4. He, Y., Yu, X., Wang, Y., Li, H. & Huang, X. Alumina-coated patterned amorphous silicon as the anode for a lithium-ion battery with high coulombic efficiency. *Adv. Mater.* **23**, 4938–41 (2011).

- 5. Hatchard, T. D. & Dahn, J. R. In Situ XRD and Electrochemical Study of the Reaction of Lithium with Amorphous Silicon. *J. Electrochem. Soc.* **151,** A838 (2004).

- 6. Abel, P. R., Lin, Y.-M., Celio, H., Heller, A. & Mullins, C. B. Improving the stability of nanostructured silicon thin film lithium-ion battery anodes through their controlled oxidation. *ACS Nano* **6**, 2506–16 (2012).

- 7. Zhang, X.-W. *et al.* Electrochemical performance of lithium ion battery, nano-silicon-based, disordered carbon composite anodes with different microstructures. *J. Power Sources* **125**, 206–213 (2004).

- 8. Nguyen, H. T. *et al.* Alumina-coated silicon-based nanowire arrays for high quality Li-ion battery anodes. *J. Mater. Chem.* **22,** 24618 (2012).

- 9. Ge, M., Rong, J., Fang, X. & Zhou, C. Porous doped silicon nanowires for lithium ion battery anode with long cycle life. *Nano Lett.* **12**, 2318–23 (2012).

- 10. Chan, C. K. *et al.* High-performance lithium battery anodes using silicon nanowires. *Nat. Nanotechnol.* **3,** 31–5 (2008).

- 11. Park, M.-H. et al. Silicon nanotube battery anodes. Nano Lett. 9, 3844–7 (2009).

- 12. Kim, H., Seo, M., Park, M.-H. & Cho, J. A critical size of silicon nano-anodes for lithium rechargeable batteries. *Angew. Chem. Int. Ed. Engl.* **49**, 2146–9 (2010).

- 13. Magasinski, a *et al.* High-performance lithium-ion anodes using a hierarchical bottom-up approach. *Nat. Mater.* **9,** 353–8 (2010).

- 14. Kohandehghan, A. *et al.* Magnesium and magnesium-silicide coated silicon nanowire composite anodes for lithium-ion batteries. *J. Mater. Chem. A* **1,** 1600 (2013).

- 15. Kirsch, B. L., Chen, X., Richman, E. K., Gupta, V. & Tolbert, S. H. Probing the Effects of Nanoscale Architecture on the Mechanical Properties of Hexagonal Silica/Polymer Composite Thin Films. *Adv. Funct. Mater.* **15**, 1319–1327 (2005).

- 16. Koshida, N. & Koyama, H. Visible electroluminescence from porous silicon z iii. **60**, 347–349 (1992).

- 17. Lehmann, V. & Rönnebeck, S. The Physics of Macropore Formation in Low-Doped p-Type Silicon. **146**, 2968–2975 (1999).

- 18. Granitzer, P., Rumpf, K., Pölt, P., Reichmann, a. & Krenn, H. Self-assembled mesoporous silicon in the crossover between irregular and regular arrangement applicable for Ni filling. *Phys. E Low-dimensional Syst. Nanostructures* **38**, 205–210 (2007).

- 19. Christophersen, M., Carstensen, J., Hasse, G. & Fo, H. Formation and application of porous silicon. **39**, 93–141 (2002).

- 20. Kim, H., Han, B., Choo, J. & Cho, J. Three-dimensional porous silicon particles for use in high-performance lithium secondary batteries. *Angew. Chem. Int. Ed. Engl.* **47**, 10151–4 (2008).

- 21. Shin, H.-C., Corno, J. a., Gole, J. L. & Liu, M. Porous silicon negative electrodes for rechargeable lithium batteries. *J. Power Sources* **139**, 314–320 (2005).

- 22. Brezesinski, T. *et al.* On the Correlation between Mechanical CeO 2 Thin Films. **4,** 967–977 (2010).

- 23. Brezesinski, T., Wang, J., Tolbert, S. H. & Dunn, B. Ordered mesoporous alpha-MoO3 with iso-oriented nanocrystalline walls for thin-film pseudocapacitors. *Nat. Mater.* **9,** 146–51 (2010).

- 24. Hochbaum, A. I., Gargas, D., Hwang, Y. J. & Yang, P. Single crystalline mesoporous silicon nanowires. *Nano Lett.* **9**, 3550–4 (2009).

- 25. Zhang, M.-L. *et al.* Preparation of Large-Area Uniform Silicon Nanowires Arrays through Metal-Assisted Chemical Etching. *J. Phys. Chem. C* **112**, 4444–4450 (2008).

- 26. Peng, K. Q. *et al.* Fabrication of Single-Crystalline Silicon Nanowires by Scratching a Silicon Surface with Catalytic Metal Particles. *Adv. Funct. Mater.* **16,** 387–394 (2006).

- 27. Chan, C. K., Ruffo, R., Hong, S. S. & Cui, Y. Surface chemistry and morphology of the solid electrolyte interphase on silicon nanowire lithium-ion battery anodes. *J. Power Sources* **189**, 1132–1140 (2009).

- 28. Wu, H. *et al.* Stable cycling of double-walled silicon nanotube battery anodes through solid-electrolyte interphase control. *Nat. Nanotechnol.* **7,** 310–5 (2012).

- 29. Hwang, T. H., Lee, Y. M., Kong, B.-S., Seo, J.-S. & Choi, J. W. Electrospun core-shell fibers for robust silicon nanoparticle-based lithium ion battery anodes. *Nano Lett.* **12**, 802–7 (2012).

- 30. Yao, Y. *et al.* Interconnected silicon hollow nanospheres for lithium-ion battery anodes with long cycle life. *Nano Lett.* **11**, 2949–54 (2011).

- 31. Su, L., Zhou, Z. & Ren, M. Core double-shell Si@SiO2@C nanocomposites as anode materials for Li-ion batteries. *Chem. Commun.* (*Camb*). **46**, 2590–2 (2010).

- 32. Sim, S., Oh, P., Park, S. & Cho, J. Critical thickness of SiO2 coating layer on core@shell bulk@nanowire Si anode materials for Li-ion batteries. *Adv. Mater.* **25**, 4498–503 (2013).

- 33. Kobayashi Asuha, H., Maida, O., Takahashi, M. & Iwasa, H. Nitric acid oxidation of Si to form ultrathin silicon dioxide layers with a low leakage current density. *J. Appl. Phys.* **94**, 7328 (2003).

- 34. Riley, L. a *et al.* Conformal surface coatings to enable high volume expansion Li-ion anode materials. *Chemphyschem* **11,** 2124–30 (2010).

- 35. Chen, Z., Qin, Y., Amine, K. & Sun, Y.-K. Role of surface coating on cathode materials for lithium-ion batteries. *J. Mater. Chem.* **20,** 7606 (2010).

- 36. Jung, Y. S. *et al.* Ultrathin direct atomic layer deposition on composite electrodes for highly durable and safe Li-ion batteries. *Adv. Mater.* **22**, 2172–6 (2010).

- 37. Chan, C. K., Patel, R. N., O'Connell, M. J., Korgel, B. a & Cui, Y. Solution-grown silicon nanowires for lithium-ion battery anodes. *ACS Nano* **4**, 1443–50 (2010).

- 38. Yao, Y., Liu, N., McDowell, M. T., Pasta, M. & Cui, Y. Improving the cycling stability of silicon nanowire anodes with conducting polymer coatings. *Energy Environ. Sci.* **5**, 7927 (2012).

- 39. Huang, R., Fan, X., Shen, W. & Zhu, J. Carbon-coated silicon nanowire array films for high-performance lithium-ion battery anodes. *Appl. Phys. Lett.* **95**, 133119 (2009).

- 40. Dunn, B. Solid State Electrochemistry. (Cambridge University Press, 1997).

- 41. Susman, S. 1.1. Scope of this work. **101**, 54–64 (1988).

- 42. Shin-ichi, F. Preparation and ionic conductivity of β-LiAlSiO4 thin film. *Solid State Ionics* **167**, 325–329 (2004).

- 43. Nagel, W. & Bohm, H. Ionic Conductivity Solid Solutions Studies on LiA1Si04 SiOZ of the High Quartz Type. **0**, 625–631 (1982).

- 44. Liu, N., Hu, L., McDowell, M. T., Jackson, A. & Cui, Y. Prelithiated silicon nanowires as an anode for lithium ion batteries. *ACS Nano* **5**, 6487–93 (2011).

- 45. Chiou, A.-H., Chien, T.-C., Su, C.-K., Lin, J.-F. & Hsu, C.-Y. The effect of differently sized Ag catalysts on the fabrication of a silicon nanowire array using Ag-assisted electroless etching. *Curr. Appl. Phys.* **13**, 717–724 (2013).

- 46. Puurunen, R. L. Surface chemistry of atomic layer deposition: A case study for the trimethylaluminum/water process. *J. Appl. Phys.* **97,** 121301 (2005).

- 47. Lee, C.-L., Tsujino, K., Kanda, Y., Ikeda, S. & Matsumura, M. Pore formation in silicon by wet etching using micrometre-sized metal particles as catalysts. *J. Mater. Chem.* **18**, 1015 (2008).

- 48. Huang, Z. *et al.* Ordered Arrays of Vertically Aligned [ 110 ] Silicon Nanowires by Suppressing the Crystallographically Preferred <100> Etching Directions 2009. (2009).

- 49. Zhong, X., Qu, Y., Lin, Y.-C., Liao, L. & Duan, X. Unveiling the formation pathway of single crystalline porous silicon nanowires. *ACS Appl. Mater. Interfaces* **3**, 261–70 (2011).

- 50. Graetz, J., Ahn, C. C., Yazami, R. & Fultz, B. Highly Reversible Lithium Storage in Nanostructured Silicon. *Electrochem. Solid-State Lett.* **6,** A194 (2003).

- 51. Liu, W.-R. *et al.* Effect of electrode structure on performance of Si anode in Li-ion batteries: Si particle size and conductive additive. *J. Power Sources* **140**, 139–144 (2005).

- 52. Cui, L., Ruffo, R., Chan, C. K., Peng, H. & Cui, Y. Crystalline-Amorphous Core Shell Silicon Nanowires for High Capacity and High Current Battery Electrodes 2009. (2009).

- 53. Key, B. *et al.* Real-time NMR investigations of structural changes in silicon electrodes for lithium-ion batteries. *J. Am. Chem. Soc.* **131,** 9239–49 (2009).

- 54. Lee, S. *et al.* Stress effect on cycle properties of the silicon thin- ® lm anode. **c,** 191–193 (2001).

- 55. Bourderau, S., Brousse, T. & Schleich, D. . Amorphous silicon as a possible anode material for Li-ion batteries. *J. Power Sources* **81-82**, 233–236 (1999).