## **UCLA**

## **UCLA Electronic Theses and Dissertations**

#### **Title**

Variability and Heterogeneous Integration of Emerging Device Technologies

### **Permalink**

https://escholarship.org/uc/item/9847f1jb

#### **Author**

Leung, Gregory

## **Publication Date**

2015

Peer reviewed|Thesis/dissertation

## UNIVERSITY OF CALIFORNIA

Los Angeles

Variability and Heterogeneous Integration of Emerging Device Technologies

A dissertation submitted in partial satisfaction of the requirements for the degree Doctor of Philosophy in Electrical Engineering

by

Gregory Kwong-Wah Leung

© Copyright by

Gregory Kwong-Wah Leung

#### ABSTRACT OF THE DISSERTATION

Variability and Heterogeneous Integration of Emerging Device Technologies

by

Gregory Kwong-Wah Leung

Doctor of Philosophy in Electrical Engineering

University of California, Los Angeles, 2015

Professor Chi On Chui, Chair

The continued push for microelectronics scaling has driven many changes in modern transistor design, such as the adoption of non-planar, multi-gate architectures (e.g., FinFETs) starting at the 22nm node. It is envisioned that other solutions such as junctionless FETs (JL-FETs), tunnel FETs (TFETs), or heterogeneous materials integration may be needed to sustain the pace of Moore's law beyond 14nm. To assess the viability of these emerging devices prior to commercial investment, we must consider the impact of process variations such as line edge roughness (LER) and random dopant fluctuation (RDF), both of which are major concerns in the nanoscale regime. The challenges associated with dimensional scaling also compel us to explore heterogeneous integration as a possible end-of-roadmap solution for future micro- and nanoelectronics.

In this dissertation, we first present our findings on the impact of LER and RDF variability on FinFETs, JL-FETs, and TFETs targeted for sub-32nm generations. Using technology computeraided design (TCAD) simulations combined with physical descriptions by which LER and RDF affect the intrinsic operation of different FETs, we compare the impact of LER and RDF on the emerging candidates of interest. We extend the study to include III-V FETs as well to determine if materials like InGaAs are inherently more or less affected by variability compared to equivalently designed silicon devices. Second, we study how heterogeneous integration (HGI) of different material systems can drive a new approach toward improving circuit and system performance outside of traditional scaling concepts. To this end, we develop a cross-layer evaluation framework (spanning process, device, and circuit-level perspectives) to assess the potential benefits of In-GaAs/Ge-based HGI circuits against silicon-only technology. To give credence to the framework, we also present experimental work in developing a nanotransfer printing process to enable featurelevel HGI in real-world settings. Third, we present a method to fabricate coplanar supercapacitors onto silicon substrates for integration with microelectronic circuits. Along with experimental demonstrations, we also develop a physical TCAD model to enable simulation-based design exploration and optimization of on-chip supercapacitors for integrated circuit applications.

Ultimately, the insights gained in this study will help guide the semiconductor industry to choose next-generation device technologies which are best suited for commercial adoption with process variability and the potential for heterogeneous integration in mind.

The dissertation of Gregory Kwong-Wah Leung is approved.

Puneet Gupta

Bruce Dunn

Subramanian Iyer

Chi On Chui, Committee Chair

University of California, Los Angeles

2015

# TABLE OF CONTENTS

| Chapter | 1 Introduction                                                  | 1  |

|---------|-----------------------------------------------------------------|----|

| Chapter | 2 Inversion-Mode Silicon FinFET Variability                     | 5  |

| 2.1     | Background                                                      | 5  |

| 2.2     | IM-FinFET Modeling                                              | 7  |

| 2.3     | Line Edge Roughness Modeling                                    | 9  |

| 2.4     | LER-Induced Variability in IM-FinFETs                           | 12 |

| 2.5     | Random Dopant Fluctuation Modeling                              | 15 |

| 2.6     | RDF-Induced Variability in IM-FinFETs                           | 18 |

| 2.7     | Circuit-Level Variability Impact                                | 20 |

| 2.8     | Summary                                                         | 22 |

| Chapter | 3 Junctionless Silicon FET Variability                          | 24 |

| 3.1     | Background                                                      | 24 |

| 3.2     | JL-FET Modeling                                                 | 25 |

| 3.3     | LER-Induced Variability in JL-FETs                              | 28 |

| 3.4     | RDF-Induced Variability in JL-FETs                              | 32 |

| 3.5     | Circuit-Level Variability Impact                                | 37 |

| 3       | 3.5.1 Variability Impact on 6T SRAM Cells                       | 40 |

| 3       | 3.5.2 LER Impact on Logic Circuit Variability                   | 44 |

| 3.6     | Summary                                                         | 48 |

| Chapter | 4 Silicon Tunnel FET Variability                                | 50 |

| 4.1     | Background                                                      | 50 |

| 4.2     | TFET Modeling                                                   | 51 |

| 4.3     | Baseline TFET Scaling                                           | 55 |

| 4.4     | LER-Induced TFET Variability                                    | 59 |

| 4.5     | RDF-Induced TFET Variability                                    | 62 |

| 4.6     | Summary                                                         | 65 |

| Chapter | 5 Interactions between LER and RDF in Nonplanar FET Variability | 68 |

| 5.1     | Background                                                      | 68 |

| 5.2     | Modeling Approach                                               | 69 |

| 5.3     | IM-FinFET Joint Variability                                     | 72 |

| 5.4     | JL-FinFET Joint Variability                                     | 76 |

| 5.5    | TFI             | ET Joint Variability                                                               | 79    |

|--------|-----------------|------------------------------------------------------------------------------------|-------|

| 5.6    | Sun             | nmary                                                                              | 82    |

| 5.7    | App             | pendix: Mean Parameter Shifts                                                      | 84    |

| Chapte | r 6 <i>Sili</i> | con vs. III-V Junctionless FET Variability                                         | 85    |

| 6.1    | Bac             | kground                                                                            | 85    |

| 6.2    | Effe            | ects of Degenerate Carrier Screening                                               | 88    |

| 6.3    | Bas             | eline Design & Performance of Si and InGaAs JL-FETs                                | 91    |

| 6.4    | Mo              | deling RDF: Approach and Limitations                                               | 97    |

| 6.5    | RD              | F in Doped Semiconductor Slabs                                                     | 99    |

| 6.6    | RD              | F in Silicon and InGaAs JL-FETs                                                    | . 102 |

| 6.7    | Sun             | nmary                                                                              | . 109 |

| 6.8    | App             | pendix I: Details on NEGF Simulations and Scattering Mechanisms                    | . 110 |

|        | 6.8.1           | Impurity Scattering                                                                | . 110 |

|        | 6.8.2           | Phonon and Surface Roughness Scattering                                            | . 113 |

| 6.9    | App             | pendix II: Effect of Barrier Height on Subthreshold Swing                          | . 114 |

| Chapte | r 7 Het         | erogeneous Integration Technology                                                  | . 117 |

| 7.1    | Bac             | kground                                                                            | . 117 |

| 7.2    | Nar             | notransfer HGI Process: Proposed Concept                                           | . 122 |

| 7.3    | Nar             | notransfer HGI Process: Experimental Work                                          | . 126 |

|        | 7.3.1           | Previous Work: Integration of GaAs NR Arrays with Si on Si/SiO <sub>2</sub>        | . 126 |

|        | 7.3.2           | Experiment #1: Transfer of High Aspect Ratio GaAs NR Arrays to Si/SiO2             | . 128 |

|        | 7.3.3           | Experiment #2: Transfer of High Aspect Ratio InAs NR Arrays to Si/SiO <sub>2</sub> | . 135 |

| 7.4    | HG              | I Evaluation Framework                                                             | . 140 |

|        | 7.4.1           | Objective of the Framework                                                         | . 140 |

|        | 7.4.2           | Device Modeling                                                                    | . 142 |

|        | 7.4.3           | Alignment Error and Transfer Accuracy                                              | . 143 |

|        | 7.4.4           | Transfer Yield and Performance Loss Considerations                                 | . 145 |

|        | 7.4.5           | HGI Impact on Circuit Layout and Design Rules                                      | . 146 |

|        | 7.4.6           | Projected HGI Benefits                                                             | . 152 |

|        | 7.4.7           | Evaluation Summary                                                                 | . 162 |

| 7.5    | Cos             | t Analysis                                                                         | . 162 |

| 7.6    | Sun             | nmary                                                                              | . 166 |

| 7.7    | Apr             | pendix I: Experimental Procedure for GaAs Transfer to SiO <sub>2</sub>             | . 168 |

| 7.8     | App          | pendix II: Experimental Procedure for InAs Transfer to SiO <sub>2</sub> | 169 |

|---------|--------------|-------------------------------------------------------------------------|-----|

| Chapter | r 8 Sup      | ercapacitors for Microelectronics                                       | 170 |

| 8.1     | Bac          | kground                                                                 | 170 |

| 8.2     | Prod         | cess Flow Template                                                      | 172 |

| 8.3     | Exp          | perimental Procedure                                                    | 174 |

|         | 8.3.1        | Fluoroalkylsilane (FAS) Treatment of Exposed SiO <sub>2</sub> :         | 174 |

|         | 8.3.2        | Selective Carbon Deposition by Self-Assembly:                           | 175 |

|         | 8.3.3        | Ionogel Synthesis:                                                      | 176 |

|         | 8.3.4        | Electrochemical Characterization:                                       | 176 |

| 8.4     | Exp          | perimental Results and Discussion                                       | 177 |

|         | 8.4.1        | Millimeter-Scale Gold-Ionogel EDLCs                                     | 177 |

|         | 8.4.2        | Sub-Millimeter-Scale Carbon-Ionogel EDLCs                               | 179 |

|         | 8.4.3        | Micrometer-Scale Well EDLCs                                             | 181 |

|         | 8.4.4        | Benchmarking                                                            | 183 |

| 8.5     | EDI          | LC Simulation and Modeling                                              | 185 |

|         | 8.5.1        | Simulation Details                                                      | 187 |

|         | 8.5.2        | Coplanar EDLC Modeling                                                  | 191 |

| 8.6     | Sun          | nmary                                                                   | 195 |

| 8.7     | App          | pendix I: Formulas for EDLC Circuit Elements                            | 197 |

| 8.8     | App          | pendix II: Explanation for Series Resistance in Fig. 83(b)              | 197 |

| Chapter | 9 <i>Con</i> | nclusion                                                                | 200 |

| Rafaran | ACAC         |                                                                         | 205 |

# LIST OF FIGURES

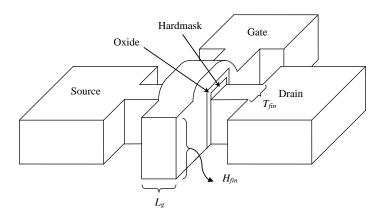

| Fig. 1. | Schematic of the FinFET structure. A vertical fin made up of silicon is straddled by a metal gate layer running perpendicular to the fin length. The metallurgical gate length $L_g$ and the fin body thickness $T_{fin}$ are indicated in the diagram. The effective channel width is the sum of $T_{fin}$ and $2 \times H_{fin}$ , where $H_{fin}$ is the fin height. If the gate oxide covering the top surface of the fin is much larger than on the sidewalls, then the structure resembles a simple double-gate MOSFET and the channel width can be approximated as simply twice the fin height. |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

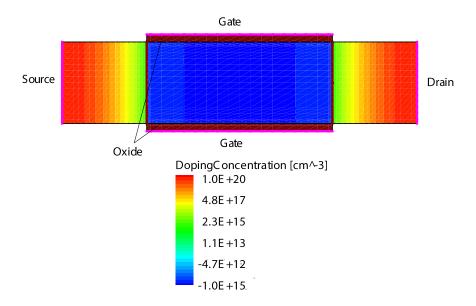

| Fig. 2. | Schematic of the 2D structure used to model IM-FinFET devices (32nm case shown). The structure represents a planar cut across the fin height and parallel to the plane of the wafer                                                                                                                                                                                                                                                                                                                                                                                                                    |

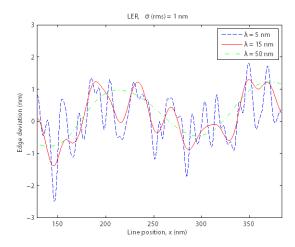

| Fig. 3. | Gaussian LER patterns corresponding to $\sigma_{LER} = 1$ nm and $\lambda = 5$ , 15, and 50 nm. Short segments of these patterns were used as inputs to the simulated FinFETs                                                                                                                                                                                                                                                                                                                                                                                                                          |

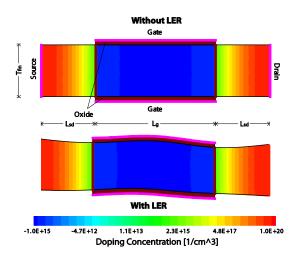

| Fig. 4. | Simulated IM-FinFET structures with and without 1 nm LER along the fin sidewalls 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

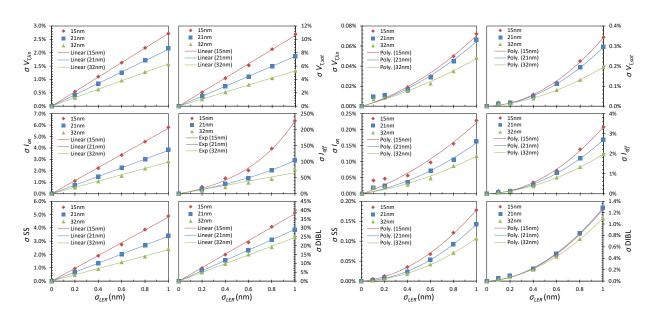

| Fig. 5. | Resist (left) and spacer (right) IM-FinFET device variability as a function of LER amplitude and technology node. Markers indicate actual simulated data while solid lines indicate best fits. Note the zoomed scale for spacer IM-FinFET data compared to resist IM-FinFET data.                                                                                                                                                                                                                                                                                                                      |

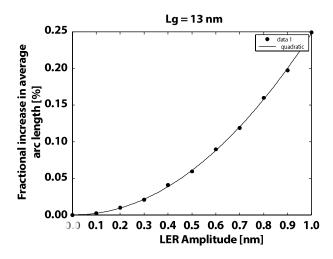

| Fig. 6. | Quadratic rise in average arc length for spacer FinFETs due to LER as a function of root-mean-square amplitude. The nominal arc length corresponds to a 13 nm channel length for the data shown.                                                                                                                                                                                                                                                                                                                                                                                                       |

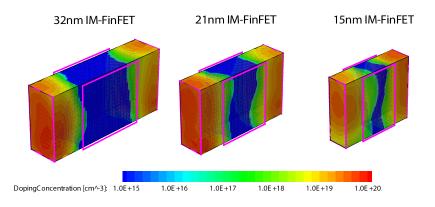

| Fig. 7. | Effective doping profiles resulting from RDF in 32, 21, and 15nm IM-FinFET devices.  The effective channel length becomes nonuniform and reduces on average at smaller nodes                                                                                                                                                                                                                                                                                                                                                                                                                           |

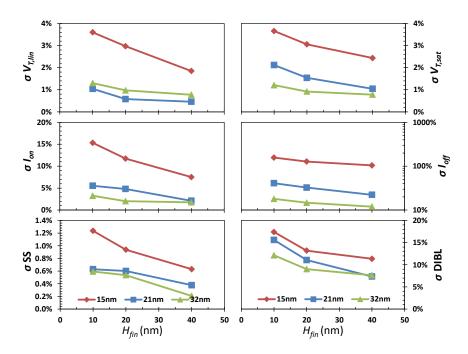

| Fig. 8. | RDF-induced variability in IM-FinFETs as a function of fin height and technology node.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

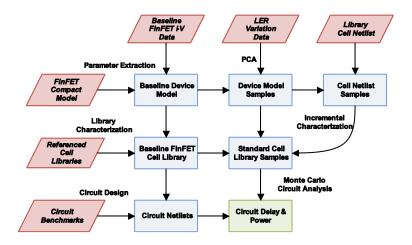

| Fig. 9. | Overall flow of the circuit benchmark evaluation process                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

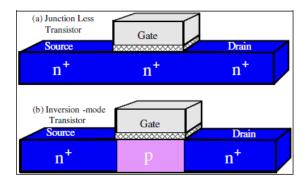

| Fig. 10 | D. Schematic comparison of (a) junctionless and (b) inversion-mode FETs and their associated doping profiles. From [35]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

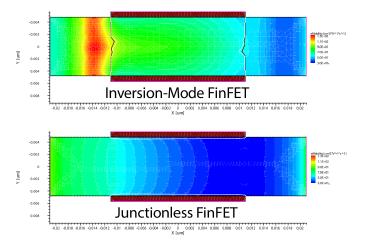

| Fig. 11 | 1. Electron mobility plots in 32nm IM- and JL-FinFETs at $V_{GS} = V_{DS} = V_{DD} = 0.9$ V. The channel mobility is consistently higher in IM-FinFETs compared to JL-FinFETs due to reduced impurity and surface roughness scattering at these geometries                                                                                                                                                                                                                                                                                                                                             |

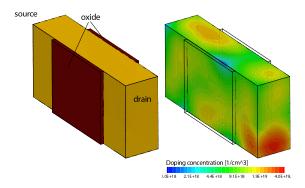

| Fig. 12 | 2. Representative 32nm JL-FinFET with 1 nm LER applied to the fin edges                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

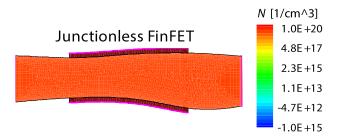

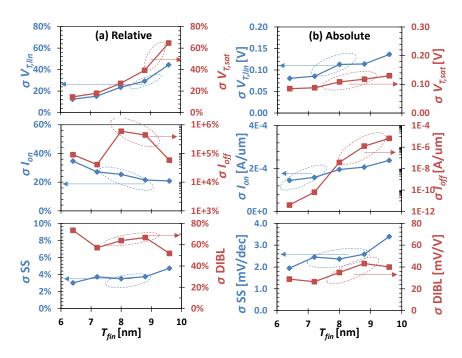

| Fig. 13 | 3. Representative 32nm JL-FinFETs with and without RDF applied. The effective doping concentrations in both cases are shown with the same color legend                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

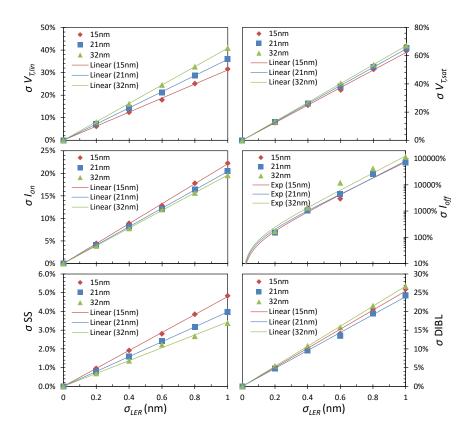

| Fig. 14. Resist JL-FinFET device variability as a function of LER amplitude and technology node. Markers indicate actual simulated data while solid lines indicate best fits 29                                                                                                                |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

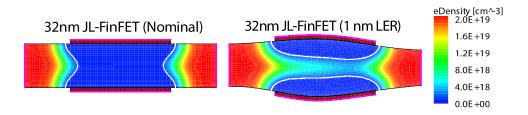

| Fig. 15. Electron density plots for two representative 32nm JL-FinFETs showing the inadvertent formation of a conducting channel due to fin LER at $V_{GS} = 0.1$ V, and $V_{DS} = 0$ . White lines indicate depletion region boundaries                                                       |

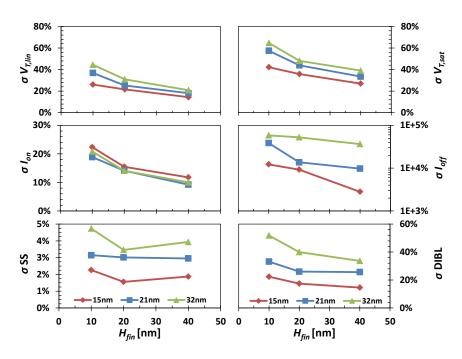

| Fig. 16. RDF-induced variability in JL-FinFETs as a function of fin height and technology node.                                                                                                                                                                                                |

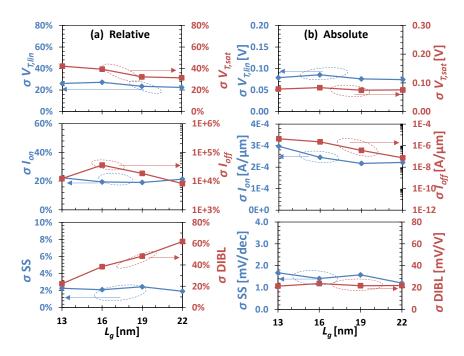

| Fig. 17. (a) Relative variation and (b) absolute variation of JL-FinFET performance due to $L_g$ scaling from 22 nm to 13 nm with $H_{fin} = 10$ nm                                                                                                                                            |

| Fig. 18. (a) Relative variation and (b) absolute variation of JL-FinFET performance due to $T_{fin}$ scaling from 9.6 to 6.4 nm with $H_{fin} = 10$ nm. 34                                                                                                                                     |

| Fig. 19. Electron density plots in a representative 32nm JL-FinFET ( $H_{fin} = 10$ nm) with and without RDF, showing the inadvertent formation of a conducting channel in the off state due to a surplus of dopants in the channel for the device with RDF                                    |

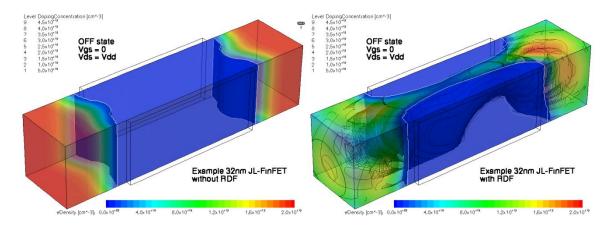

| Fig. 20. Overview of the variability evaluation framework. The evaluation of 6T SRAM cells (left) and microprocessor circuits (right) are divided into two vertical branches as illustrated                                                                                                    |

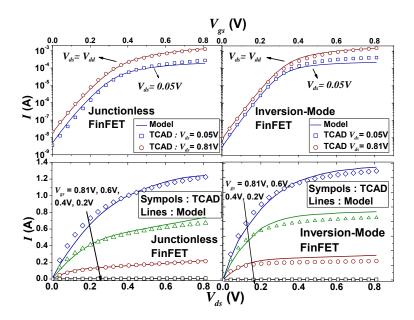

| Fig. 21. Matching of baseline FinFET (a) transfer and (b) output curves between TCAD simulation and compact modeling                                                                                                                                                                           |

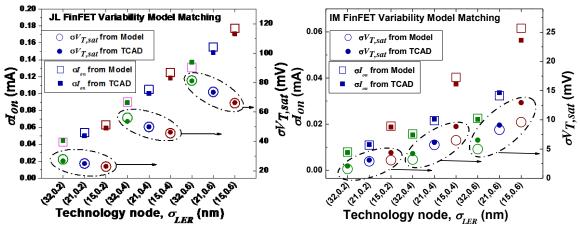

| Fig. 22. Comparison of $\sigma I_{on}$ and $\sigma V_{T,sat}$ extracted from 200 samples between TCAD simulations and fitted variability models for (a) JL FinFETs and (b) IM FinFETs show a good fit 40                                                                                       |

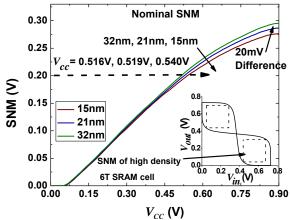

| Fig. 23. Nominal SNM as a function of working $V_{cc}$ for high density design JL FinFET 6T SRAM cells. Note that for successive technology nodes, SNM and $V_{cc,min}$ decrease when the other is held fixed                                                                                  |

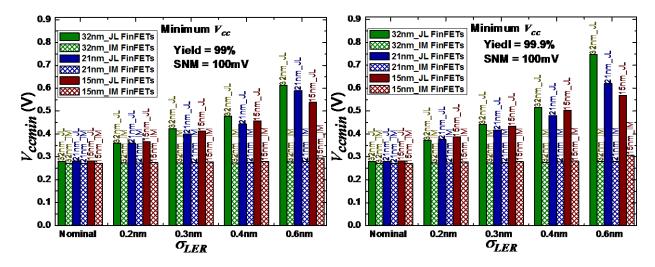

| Fig. 24. $V_{ccmin}$ as a function of technology node and LER amplitude for JL and IM FinFET 6T SRAM. The SNM constraint is 100 mV with 99% yield in the left panel, and 10 mV with 99.9% yield in the right panel.                                                                            |

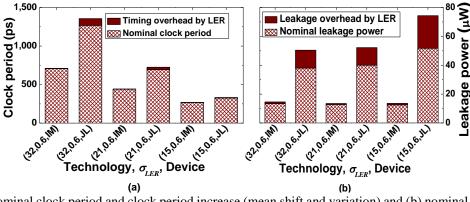

| Fig. 25. (a) Nominal clock period and clock period increase (mean shift and variation) and (b) nominal leakage power and leakage power increase (mean shift and variation) due to LER variation ( $\sigma_{LER} = 0.6$ nm) for IM and JL-FinFET-based MIPS processors at typical clock speeds. |

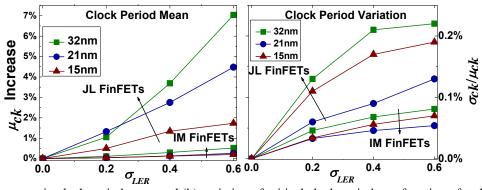

| Fig. 26. (a) Increase in clock period mean and (b) variation of critical clock period as a function of technology node and LER amplitude for JL- & IM-FinFET circuit benchmark (Cortex-M0)                                                                                                     |

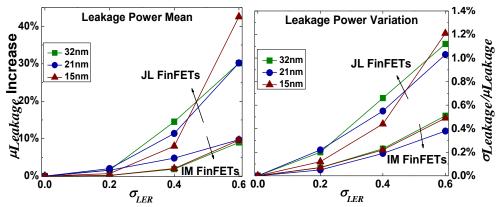

| Fig. 27. (a) Increase in leakage power mean and (b) variation of leakage power mean and (c) variation of leakage power mean and (d) variation of leakage power mean an | enchmarks (Cortex-                                                                                                                     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|

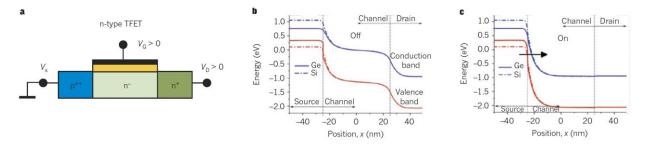

| Fig. 28. (a) Structure of an <i>n</i> -type silicon TFET with <i>p</i> -type source, intrinsidrain. (b) Band diagrams in the "off" state for all-silicon TFET and Ge source. (c) Respective band diagrams in the "on" state. From [6]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | a silicon TFET with a                                                                                                                  |

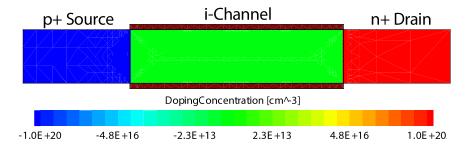

| Fig. 29. Simulated <i>n</i> -type silicon DG TFET structure along with the doping work.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                        |

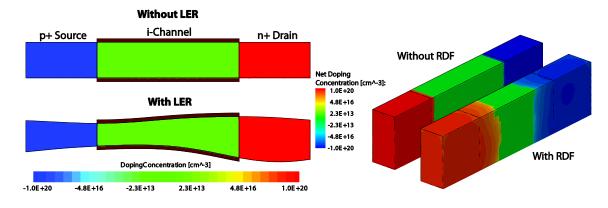

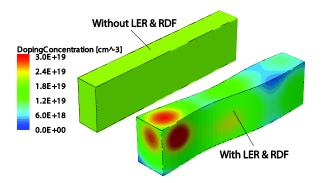

| Fig. 30. Examples of simulated 20/5 TFETs with and without LER and RD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | oF 54                                                                                                                                  |

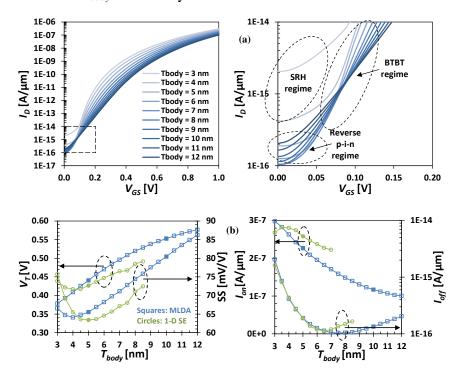

| Fig. 31. (a) Raw $I_D - V_{GS}$ curves for the ideal TFETs with $V_{GS}$ swept from ( $V_{DD}$ . (b) Nominal TFET performance versus body thickness scaling in terms of the metrics $V_T$ , $I_{on}$ , $I_{off}$ , and SS. Solid markers indicate the and 20/10 TFETs. Curves for the 1-D Schrodinger model are incomponent convergence problems.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | g from 3 nm to 12 nm<br>ne performance of 20/5<br>nplete due to                                                                        |

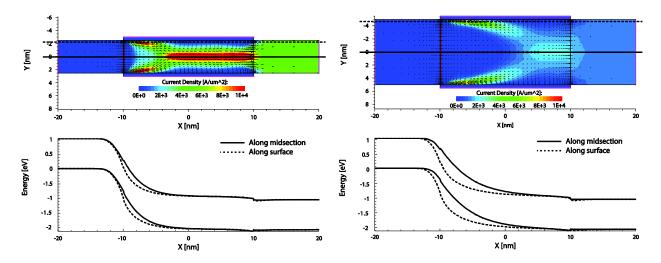

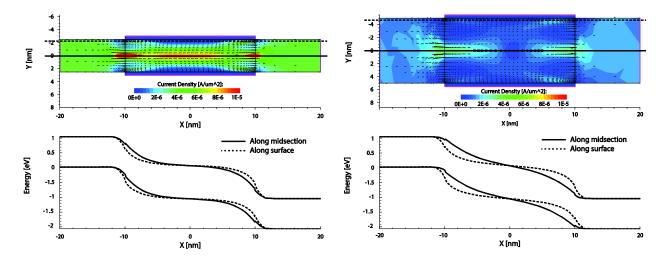

| Fig. 32. On-state ( $V_{GS} = V_{DS} = V_{DD}$ ) current density maps for the ideal 20/5 TFET (right), along with the energy band diagrams along two horiz along the body midsection (solid) and another near the silicon-SiO <sub>2</sub> thin body TFETs, the energy bands are sufficiently lowered by the induce BTBT along the midsection in addition to the two surface channel midsection.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | contal cut lines: one interface (dashed). In high gate voltage to nannels. In thick body els and not along the                         |

| Fig. 33. Off-state ( $V_{GS} = 0$ and $V_{DS} = V_{DD}$ ) current density maps for the idea and 20/10 TFET (right), along with the energy band diagrams along lines: one along the body midsection (solid) and another near the sit (dashed). In thin body TFETs, the barrier height for trap-assisted tu the close proximity of the gate to all vertical locations in the channel body TFETs where the gate loses control of the midsection, resulting prevent significant tunneling through traps.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | g two horizontal cut<br>licon-SiO <sub>2</sub> interface<br>nneling is lowered by<br>el compared to thick<br>ng in a larger barrier to |

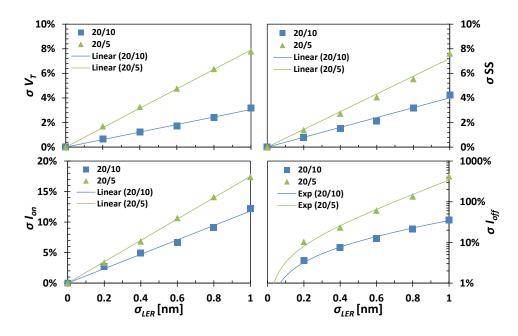

| Fig. 34. Device-level variability of 20/5 and 20/10 TFETs due to body LEF from 0 to 1 nm. Markers indicate actual data while lines indicate be                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                        |

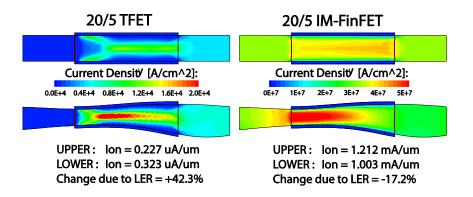

| Fig. 35. Effect of a specific LER pattern ( $\sigma_{LER} = 1$ nm) on the drive current compared to an equivalent IM-FinFET. Only the doping and work to between the two, all other parameters are identical.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | function are different                                                                                                                 |

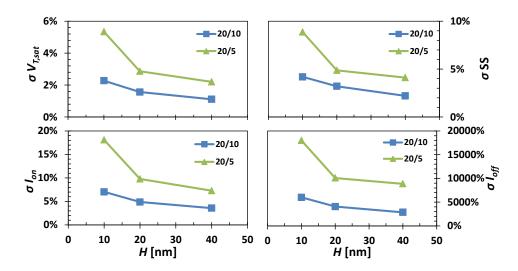

| Fig. 36. Device-level variability of 20/5 and 20/10 TFETs due to RDF for a heights <i>H</i> from 10 to 40 nm.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                        |

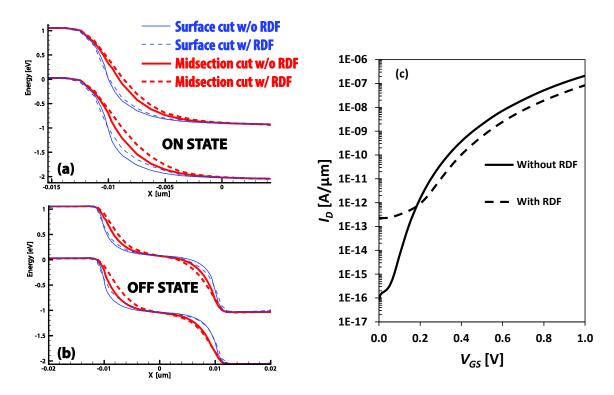

| Fig. 37. (a) On-state and (b) off-state band diagrams for 20/5 TFETs with a along the channel surface and channel midsection. RDF causes the tunneling path to slightly widen in the on-state, while the direct sou                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | source-channel                                                                                                                         |

|         | assisted tunneling path shortens in the off-state. (c) Corresponding $I_D - V_{GS}$ curves with and without RDF, showing severe degradation in performance predicted from the RDF model                                                                                                                                                 |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

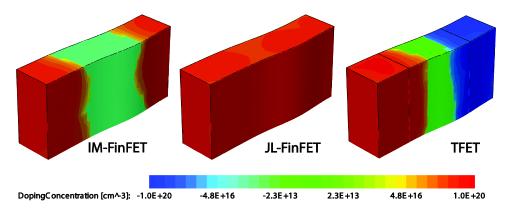

| Fig. 38 | Examples of simulated structures containing body/fin LER and RDF: (left) 32nm IM-FinFET, (center) 32nm JL-FinFET, and (right) 20/10 TFET. All devices are shown with a height of 20 nm                                                                                                                                                  |

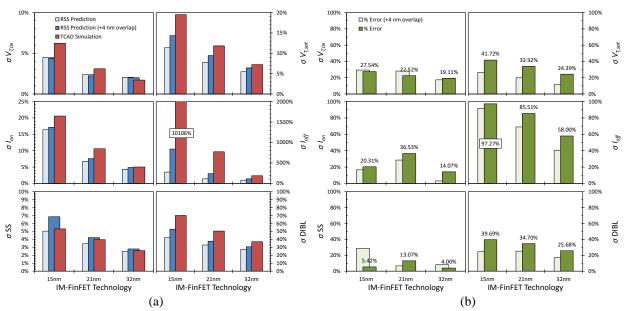

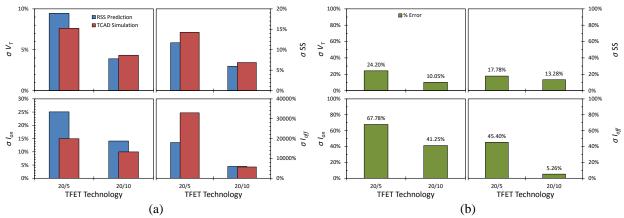

| Fig. 39 | 2. (a) Comparison of expected IM-FinFET variability when LER and RDF are assumed uncorrelated versus direct simulations with LER and RDF present. (b) Percentage error incurred when assuming independence of LER and RDF compared to actual simulated values.                                                                          |

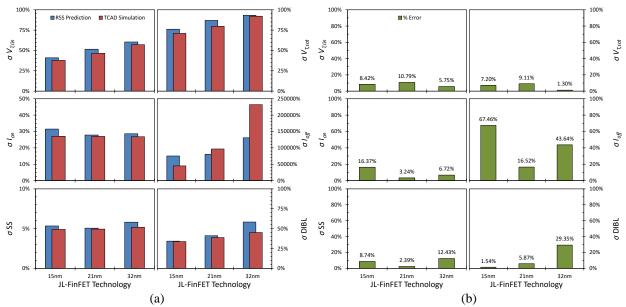

| Fig. 40 | 0. (a) Comparison of expected JL-FinFET variability when LER and RDF are assumed uncorrelated versus direct simulations with LER and RDF present. (b) Percentage error incurred when assuming independence of LER and RDF compared to actual simulated values.                                                                          |

| Fig. 41 | . Simulated resistors with and without LER & RDF. $L=40$ nm, $W=5$ nm, and $H=10$ nm in the structures shown with $\sigma_{LER}=1$ nm and nominal doping of $2\times10^{19}$ cm <sup>-3</sup>                                                                                                                                           |

| Fig. 42 | 2. (a) Comparison of expected TFET variability when LER and RDF are assumed uncorrelated versus direct simulations with LER and RDF present. (b) Percentage error incurred when assuming independence of LER and RDF compared to actual simulated values.                                                                               |

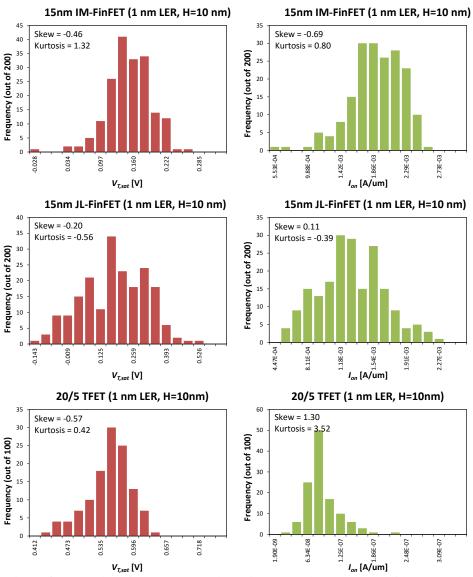

| Fig. 43 | 3. Distributions of $V_{T,sat}$ and $I_{on}$ for 15nm IM and JL-FinFETs and 20/5 TFETs with LER and RDF. The IM-FinFETs and TFETs have noticeable skew while JL-FinFETs appear normal symmetric.                                                                                                                                        |

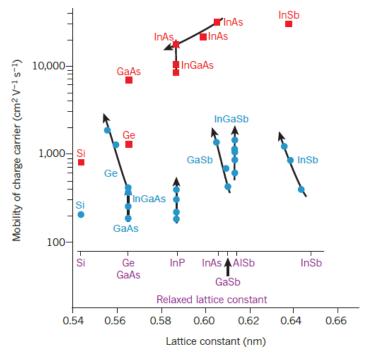

| Fig. 44 | Highest room temperature mobility of electrons (red) and holes (blue) versus semiconductor lattice constant in inversion layers and quantum wells. Data points which lie along a drawn arrow indicate different amounts of semiconductor biaxial strain and their respective strain-enhanced mobility. From [72]                        |

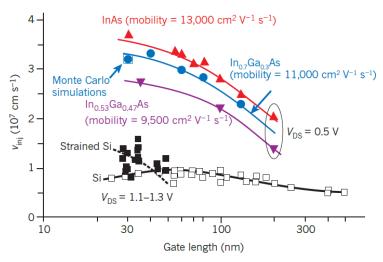

| Fig. 45 | Electron injection velocities of InGaAs and InAs HEMTs and Si MOSFETs as a function of gate length. The saturation of InGaAs channel mobility at shorter gate lengths indicates near-ballistic operation; this observation is supported by ballistic Monte Carlo simulations which lie coincident with the experimental data. From [72] |

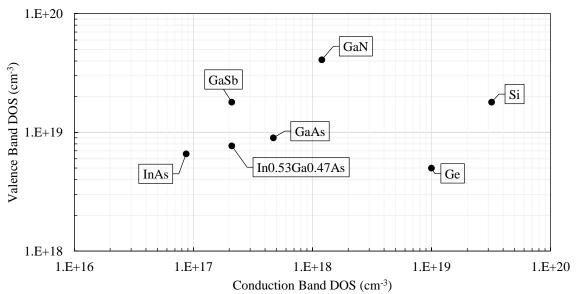

| Fig. 46 | Effective conduction band and valence band density of states in various semiconductors.  Data taken from [91]                                                                                                                                                                                                                           |

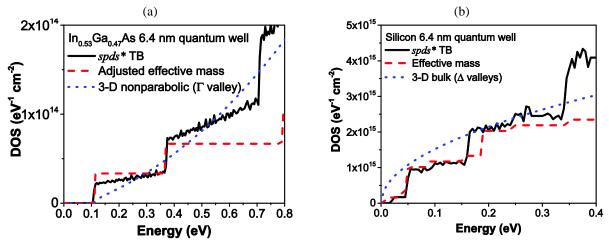

| Fig. 47 | D atomistic tight-binding (TB) and effective mass (EM) Hamiltonians, compared with the equivalent 3-D DOS normalized by the well thickness.                                                                                                                                                                                             |

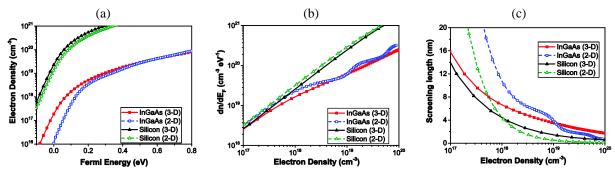

| Fig. 48 | 3. Comparison of (a) $n$ as function of Fermi energy $E_F$ , (b) $dn/dE_F$ versus $n$ , and (c) screening length versus $n$ in InGaAs and silicon. 2-D calculations are performed using the tight binding DOS. 2-D values of $n$ and $dn/dE_F$ are normalized to 3-D by dividing by the channel thickness $T = 6.4$ nm90                                                                                                                                                                                                                              |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

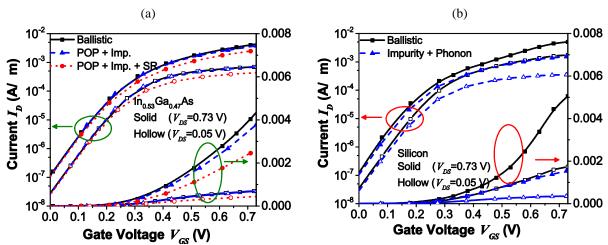

| Fig. 49 | Device characteristics for (a) InGaAs and (b) silicon n-type JL-FETs with $2\times10^{19}$ cm <sup>-3</sup> channel doping from ballistic (solid lines) and scattering (dashed lines) NEGF simulations. For InGaAs, the curve including SR scattering is calculating assuming a roughness amplitude $\Delta=1.76$ nm.                                                                                                                                                                                                                                 |

| Fig. 50 | 0. Spectral current along center of InGaAs and Si $2\times10^{19}$ cm <sup>-3</sup> doped devices in the off- $(V_{GS}=0)$ and on-states $(V_{GS}=0.73 \text{ V})$ . The green lines indicate the position of the source Fermi energy and white lines mark the first subband edge. Note the different energy scales for InGaAs and silicon.                                                                                                                                                                                                           |

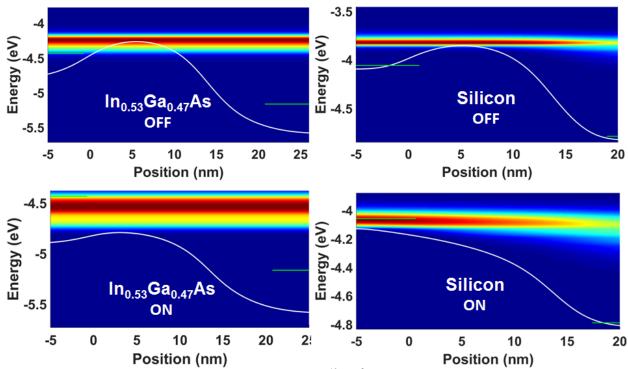

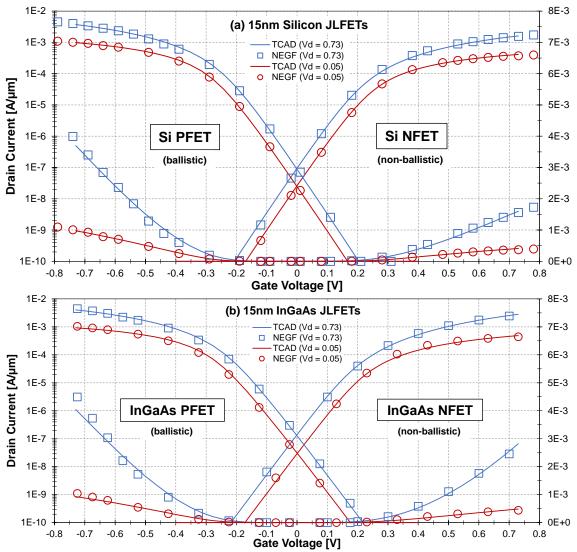

| Fig. 51 | Nominal $I_D$ - $V_G$ curves for 15nm (a) Si and (b) InGaAs JL-FETs showing TCAD calibrations performed against NEGF simulations. The upper curves in each panel correspond to the log scale on the left while the lower curves correspond to the linear scale on the right.                                                                                                                                                                                                                                                                          |

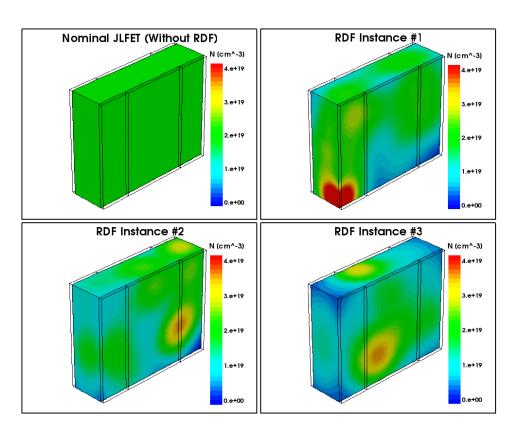

| Fig. 52 | 2. Examples of JL-FETs exhibiting RDF generated from the Sano method. For reference, the nominal structure (without RDF) is shown in the upper left panel, having a uniform doping concentration of 2×10 <sup>19</sup> cm <sup>-3</sup>                                                                                                                                                                                                                                                                                                               |

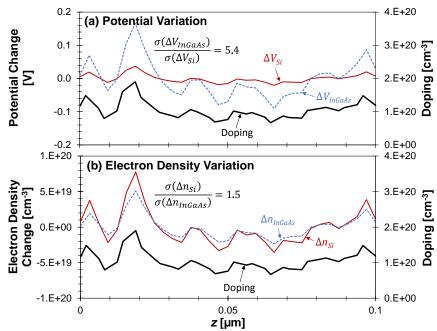

| Fig. 53 | 3. Comparison of spatial fluctuations along a <i>z</i> -cutline in (a) electrostatic potential and (b) electron density in $100\times100\times100$ nm <sup>3</sup> <i>n</i> -Si and <i>n</i> -InGaAs resistor slabs resulting from RDF. The nominal doping concentration (without RDF) for both slabs is $10^{20}$ cm <sup>-3</sup> . Both slabs have exactly the same number and spatial arrangement of dopants                                                                                                                                      |

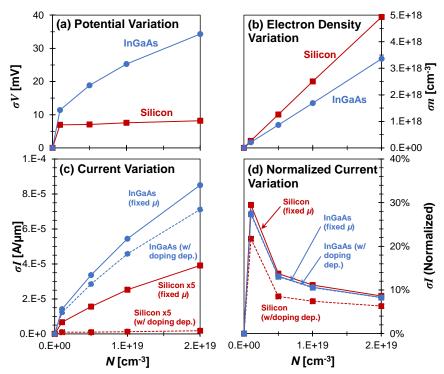

| Fig. 54 | 4. Average fluctuations of (a) potential, (b) electron density, (c) current, and (d) normalized current in ensembles of $20 \times 20 \times 20$ nm <sup>3</sup> Si and InGaAs slabs with RDF for different nominal doping concentration $N$ . The ensemble size is 100 slabs for each combination of material and $N$ . The applied voltage is 10 mV in (c) and (d). In (c), the Si curves are scaled by $5 \times$ for visual clarity. In (d), the current fluctuations are normalized to the ideal current values when RDF is absent from the slab |

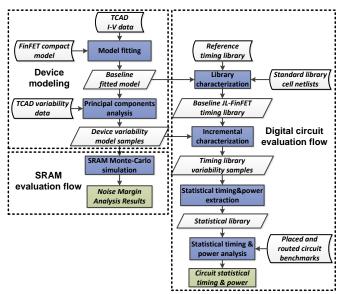

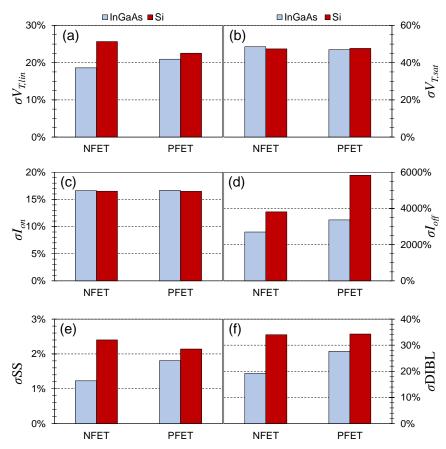

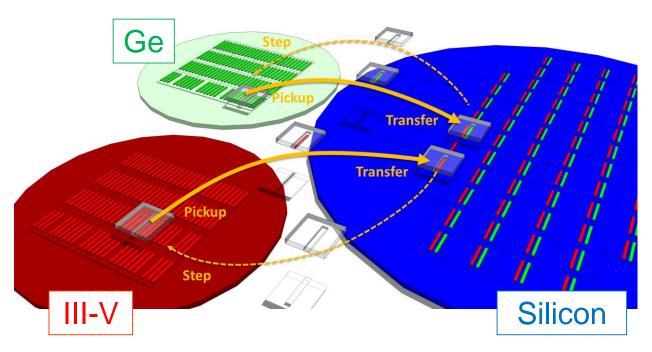

| Fig. 55 | 5. Comparison of raw $n$ -type and $p$ -type InGaAs and Si JL-FET variability due to RDF for the metrics $V_{T,lin}$ , $V_{T,sat}$ , $I_{on}$ , $I_{off}$ , SS, and DIBL                                                                                                                                                                                                                                                                                                                                                                              |

| Fig. 56 | 6. Comparison of normalized $n$ -type and $p$ -type InGaAs and Si JL-FET variability due to RDF for the metrics $V_{T,lin}$ , $V_{T,sat}$ , $I_{on}$ , $I_{off}$ , SS, and DIBL. The standard deviations are normalized to the baseline values given in Table 17                                                                                                                                                                                                                                                                                      |

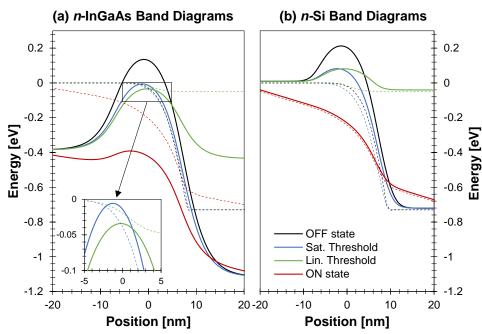

| Fig. 57 | 7. Nominal conduction band diagrams along the center of the channel in <i>n</i> -type (a) InGaAs and (b) Si JL-FETs under the following bias conditions (displayed from top to bottom): off-state, saturation threshold, linear threshold, and on-state. The electron quasi-Fermi energy level is shown in dashed lines for each bias condition. The inset in (a) compares                                                                                                                                                                            |

|         | the bands at linear and saturation threshold near the top of the barrier, indicating great degeneracy at $V_G = V_{T,lin}$ compared to $V_{T,sat}$                                                                                                                                                                                                                                                                                                                   |         |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

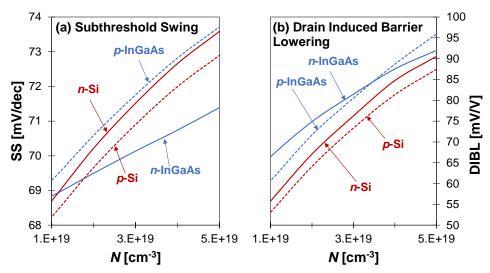

| Fig. 58 | 8. (a) Dependence of SS and (b) DIBL on the nominal channel doping in Si and InGaAs JL-FETs. The sensitivity of SS and DIBL to <i>N</i> is lower for <i>n</i> -InGaAs JL-FETs due to degeneracy effects.                                                                                                                                                                                                                                                             |         |

| Fig. 59 | 9. Pseudo 2-D model subthreshold swing as a function of barrier height using geometric and material parameters from Table 17. The sensitivity of SS to barrier height (equal t $qdSSdETOB$ ) is also shown at $ETOB = 0.2$ eV and $ETOB = 0.4$ eV for Si and InGaAs respectively.                                                                                                                                                                                    | 0<br>S, |

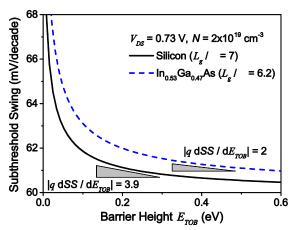

| Fig. 60 | 0. Process flow sequence for NTP-based HGI.                                                                                                                                                                                                                                                                                                                                                                                                                          | 122     |

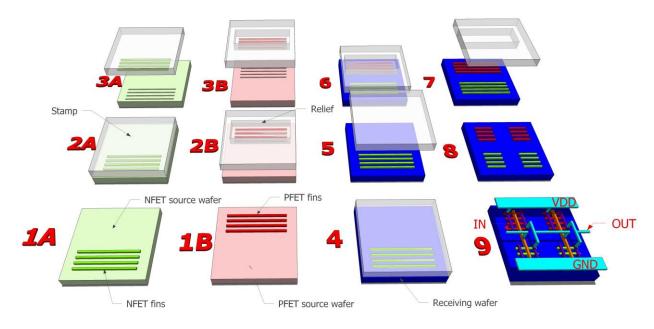

| Fig. 6  | 1. Possible wafer-scalable concept of III-V/Ge HGI on Si realized through a repeatable "step and transfer" NTP process.                                                                                                                                                                                                                                                                                                                                              | 125     |

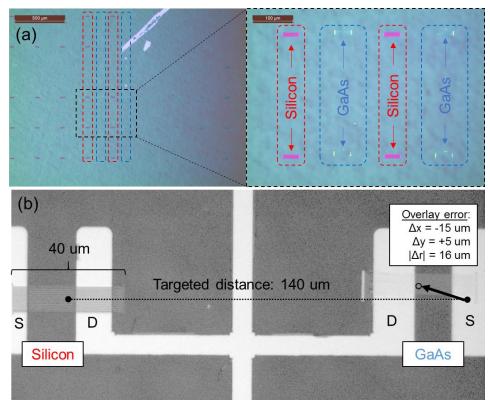

| Fig. 62 | 2. (a) HGI demonstration of 400 nm wide GaAs and Si nanoribbon arrays formed by N on SiO <sub>2</sub> /Si substrate with mm <sup>2</sup> area coverage. (b) Measured overlay error (16 μm) after aligned transfer and source/drain electrode formation using optical lithography                                                                                                                                                                                     | er      |

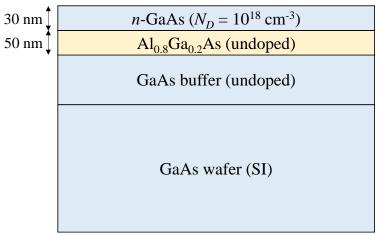

| Fig. 63 | 3. MBE-grown layer stack for <i>n</i> -GaAs/Al <sub>0.8</sub> Ga <sub>0.2</sub> As/GaAs substrate                                                                                                                                                                                                                                                                                                                                                                    | 128     |

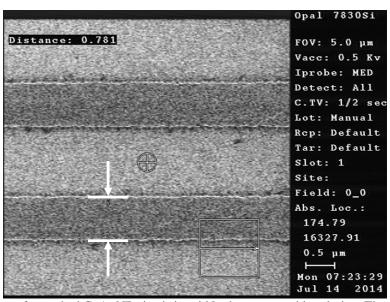

| Fig. 64 | 4. CD-SEM image of as-etched GaAs NRs in citric acid/hydrogen peroxide solution. The nominal width of each ribbon is 0.5 μm, whereas the actual measured width is 0.781 μm.                                                                                                                                                                                                                                                                                          | ım.     |

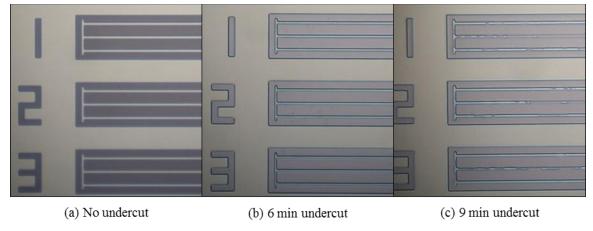

| Fig. 65 | 5. Optical micrographs of GaAs NR arrays being undercut by selective etching of the underlying Al <sub>0.8</sub> Ga <sub>0.2</sub> As after (a) 0, (b) 6, and (c) 9 min in dilute BOE solution. White areas correspond to the top layer <i>n</i> -GaAs while violet corresponds to the bottom GaAs layer. After a 9 min undercut, some NRs began collapsing as indicated by translucent segments at random locations.                                                |         |

| Fig. 66 | 6. A set of $10^{18}$ cm <sup>-3</sup> $n$ -doped GaAs nanoribbon (L/W/T = $400/0.75/0.03$ µm) arrays transferred to SiO <sub>2</sub> /Si. Each individual array is nominally composed of ten parallel ribbons. Discontinuities along the nanoribbons indicate broken segments resulting in <100% yield.                                                                                                                                                             | 132     |

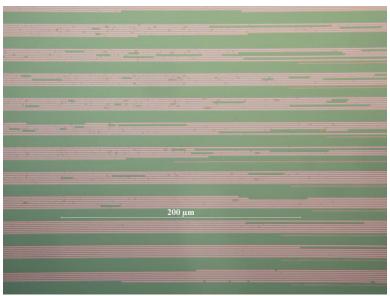

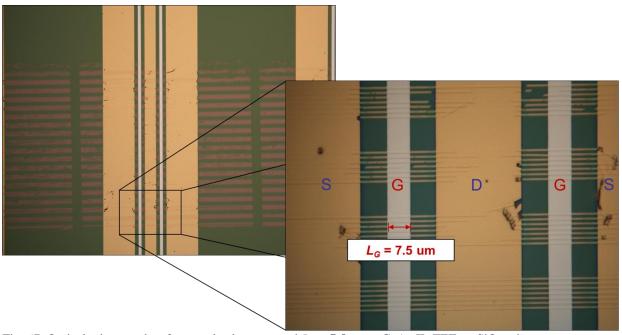

| Fig. 67 | 7. Optical micrographs of a completely processed $L_G = 7.5 \mu m n$ -GaAs JL-FET on SiO <sub>2</sub> substrate.                                                                                                                                                                                                                                                                                                                                                     |         |

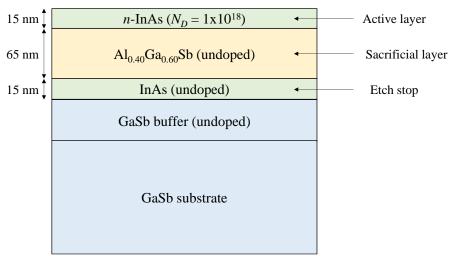

| Fig. 68 | 8. MBE-grown layer stack for <i>n</i> -InAs/Al <sub>0.4</sub> Ga <sub>0.6</sub> Sb/GaSb substrate                                                                                                                                                                                                                                                                                                                                                                    | 136     |

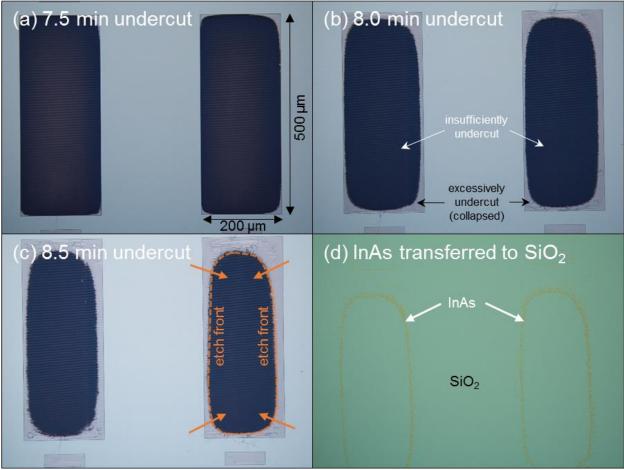

| Fig. 69 | 9. Time progression of InAs NR undercutting by AlGaSb etching after (a) 7.5 min, (b), min, and (c) 8.5 min in dilute NH <sub>4</sub> OH solution. Each 200×500 µm <sup>2</sup> rectangular area contains an array of 500 parallel NRs. The dark blue regions correspond to NRs that a insufficiently undercut, while the lavender regions correspond to bent and/or collapsed NRs that received an excessive undercut. The etch front illustrated by the dashed oran | re<br>d |

|      | outline in (c) corresponds to NR portions that are on the verge of collapse. In (d), broken portions of InAs from the etch front were successfully transferred to SiO <sub>2</sub> , but nothing else.                                                                                                                                                                                                                                  |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

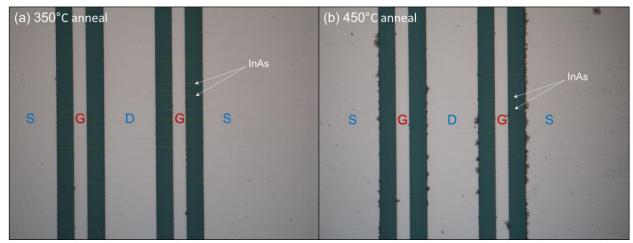

| Fig. | 70. Optical micrographs of a fully processed <i>n</i> -InAs JL-FETs on SiO <sub>2</sub> after annealing in N <sub>2</sub> for (a) 30 min at 350°C and (b) 60 min at 450°C. Discoloration of the InAs near the metal lines is visible after annealing at 450°C.                                                                                                                                                                          |

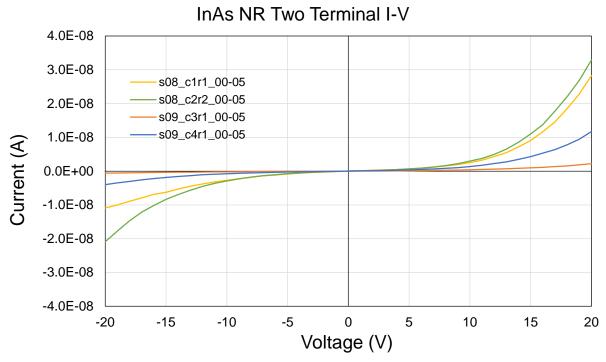

| Fig. | 71. Two-terminal I-V measurements performed on InAs NRs on SiO <sub>2</sub> . The electrode separation is 5 µm and the InAs thickness is 15 nm for each device. The effective width of each device is unknown but lies somewhere between 0.5 and 2 µm                                                                                                                                                                                   |

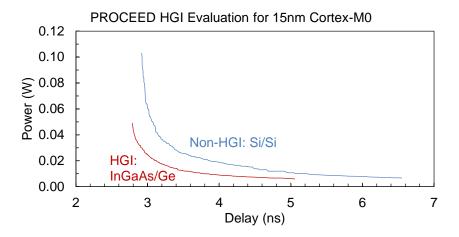

| Fig. | 72. Power-delay tradeoff for 15nm InGaAs/Ge and Si/Si built Cortex-M0 generated by PROCEED [152]                                                                                                                                                                                                                                                                                                                                        |

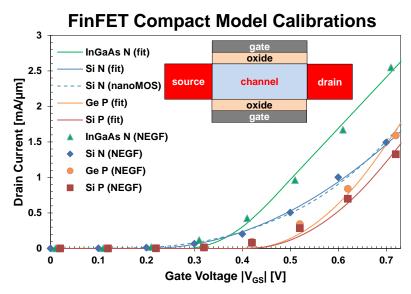

| Fig. | 73. NEGF (symbols) and model fit (lines) $ I_D $ - $ V_{GS} $ curves for Si, Ge, and InGaAs doublegate FinFETs. The dashed line represents the NEGF Si NFET simulation using nanoMOS [153]. All simulations are with drain bias $V_{DS} = 0.73$ V. Inset: double-gate structure used for simulations.                                                                                                                                   |

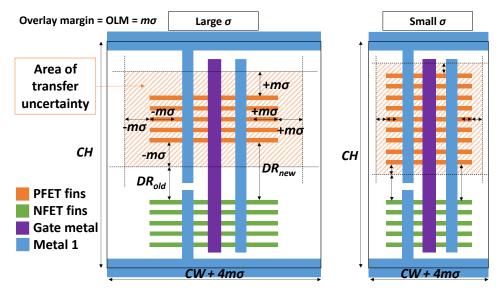

| Fig. | 74. Schematic layouts for heterogeneous FinFET inverters from NTP without fin trimming.  The area of transfer uncertainty indicates the region where PFET fins can land due to misalignment.  147                                                                                                                                                                                                                                       |

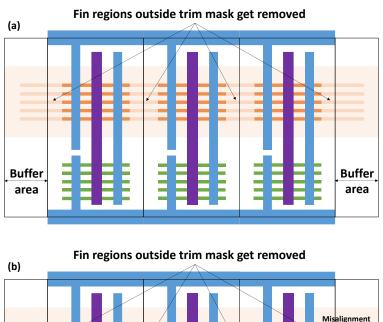

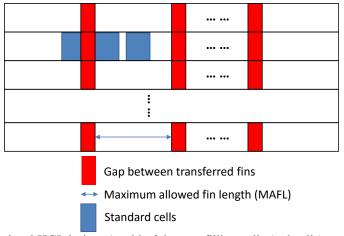

| Fig. | 75. (a) Schematic layout for a row of heterogeneous FinFET inverters made with NTP and fin trimming. (b) The effect of transfer misalignment with fin trimming is now absent within each cell except at the buffer areas on ends of a row                                                                                                                                                                                               |

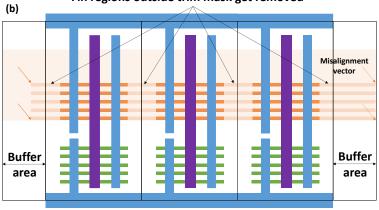

| Fig. | 76. (a) Probability of successful fin placement as a function of transfer misalignment and allotted overlay margin. (b) Alignment yield versus average cell area in reduced MIPS processor. (c) Optimal OLM value search to maximize alignment yield per cell area 153                                                                                                                                                                  |

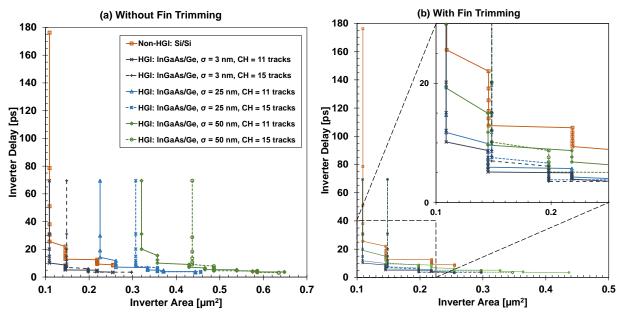

| Fig. | 77. Delay versus area for 15nm InGaAs/Ge (HGI) and Si/Si (non-HGI) inverters for different σ and CHs (a) without fin trimming and (b) with fin trimming. The inset is a magnified view of the dashed region in (b)                                                                                                                                                                                                                      |

| Fig. | 78. Protocol for block-level HGI design. A grid of dummy filling cells (red cells) are inserted pre-placement to represent the effect of finite fin length, and standard cells (blue cells) are then placed in between the filling cells                                                                                                                                                                                                |

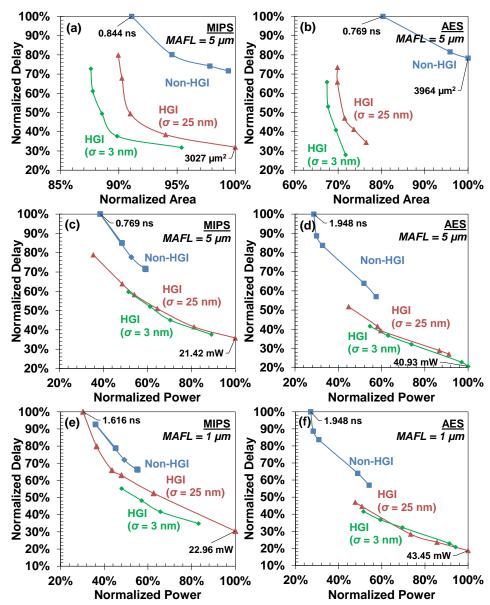

| Fig. | 79. Post-synthesis (pre-P&R) normalized delay and area of (a) MIPS and (b) AES designs. Post-P&R normalized delay and power of MIPS and AES designs with MAFL of (c,d) 5 $\mu$ m and (e,f) 1 $\mu$ m, respectively. In each panel the reported data is normalized to the largest observed delay, power, or area values as indicated by the data labels. The design rules (i.e., OLM values) are chosen to ensure 95% yield in all cases |

| Fig. | 80. Total interconnect length as a function of maximum allowed fin length for HGI-based (a) MIPS and (b) AES designs                                                                                                                                                                                                                                                                                                                    |

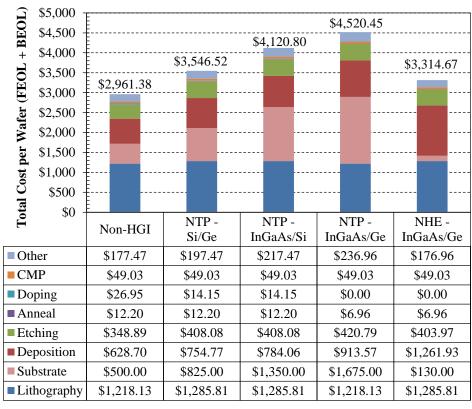

|          | Estimated cost breakdown to implement 22nm FinFET technology in different process scenarios. For HGI processes, the integrated material pair is realized by either nanotransfer printing (NTP) or nanoheteroepitaxy (NHE)                                                                                                          |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

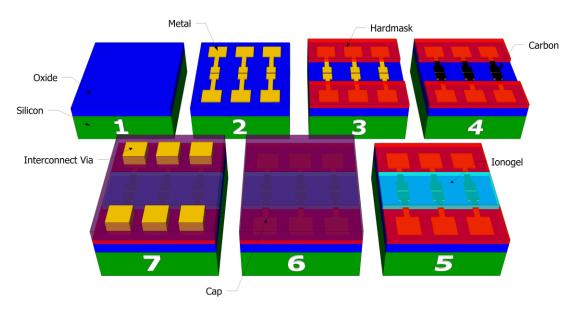

| _        | . Illustration of a generic process flow for integrating planar carbon-ionogel EDLCs on a silicon substrate. The numbers 1-7 indicate the sequence of processing steps                                                                                                                                                             |

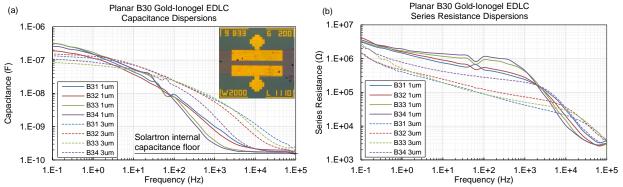

| C        | . Measured (a) capacitance and (b) series resistance dispersions for B30 gold-ionogel EDLCs. Solid (dashed) lines correspond to the 1 $\mu$ m (3 $\mu$ m) gel devices. The inset in (a) is an optical micrograph of one of the measured B33 devices. The color fringing in the ionogel is indicative of film thickness variations. |

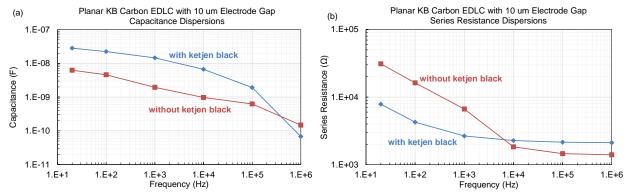

|          | . Comparison of series capacitance and resistance dispersions for 10 μm gap supercapacitors with and without KB in neat ionic liquid                                                                                                                                                                                               |

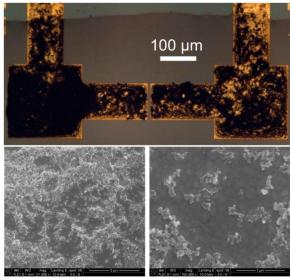

|          | . (top) Optical microscope image of KB self-assembled electrodes coated with $100~\mu m$ thick ionogel. (bottom) SEM images of ketjen black particles self-assembled on the gold electrodes.                                                                                                                                       |

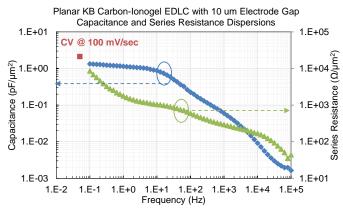

|          | . Comparison of areal capacitance and series resistance measurements on the 10 μm gap carbon-ionogel supercapacitor.                                                                                                                                                                                                               |

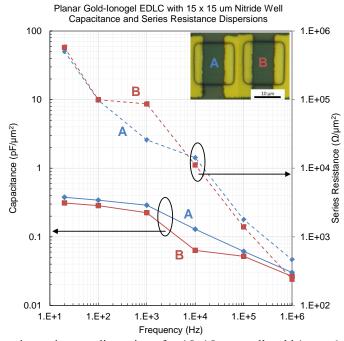

| _        | . Capacitance and series resistance dispersions for 15×15 μm well gold-ionogel supercapacitors. The inset shows optical micrographs of two such devices, denoted "A" and "B". The well openings are indicated by the black square outlines                                                                                         |

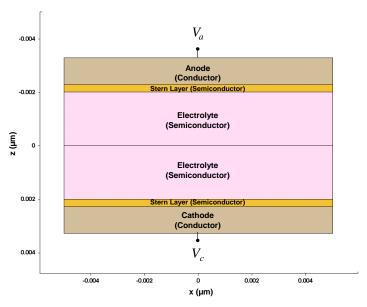

| Fig. 88. | . Simulation model for the sandwich configuration EDLC                                                                                                                                                                                                                                                                             |

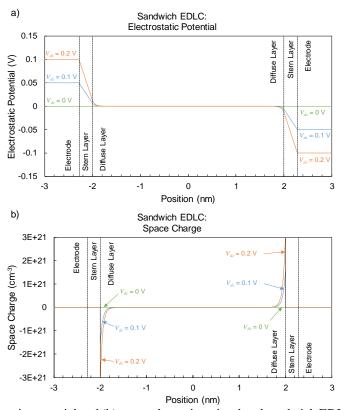

|          | . Plots of (a) electrostatic potential and (b) space charge in a simulated sandwich EDLC for different DC voltage biases. The supercapacitor has a 4 nm thick electrolyte, 2.8 Å thick Stern layer, and 1 nm thick electrodes.                                                                                                     |

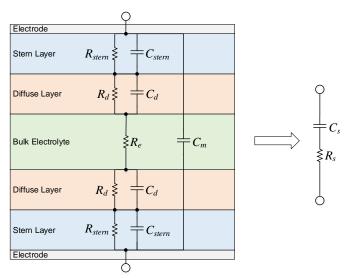

|          | . Equivalent circuit diagram for the simulated EDLC model showing individual contributions from the Stern, diffuse, and bulk electrolyte regions                                                                                                                                                                                   |

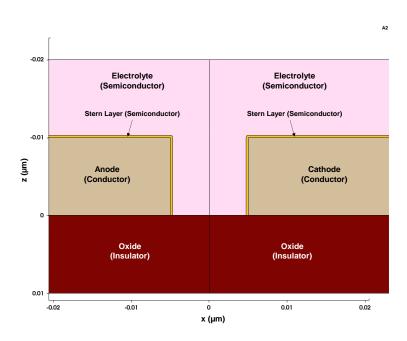

| Fig. 91. | . Simulation model for the coplanar configuration EDLC                                                                                                                                                                                                                                                                             |

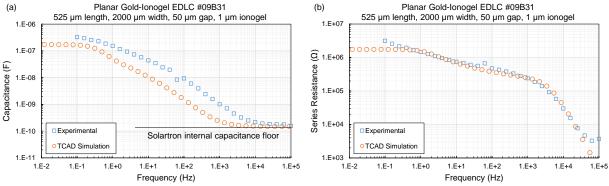

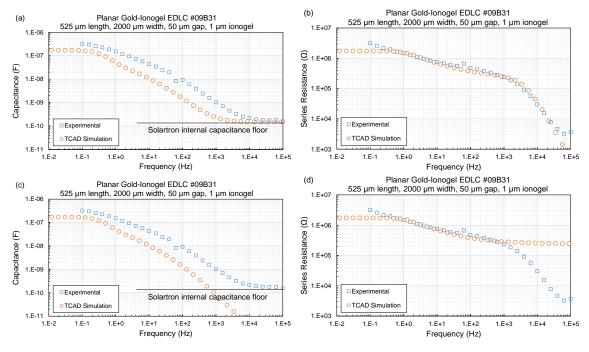

|          | . Comparison of experimental planar EDLC capacitance and series resistance versus simulated values from the TCAD setup                                                                                                                                                                                                             |

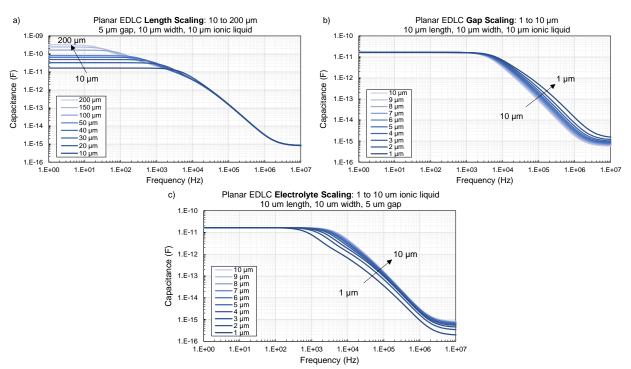

| _        | . Effect of scaling the (a) electrode length, (b) gap distance, and (c) electrolyte thickness on the capacitance dispersion of planar EDLCs. The electrolyte is assumed to be [BMIM][BF4] ionic liquid with 1 mS/cm conductivity and 2.8 Å Stern layer                                                                             |

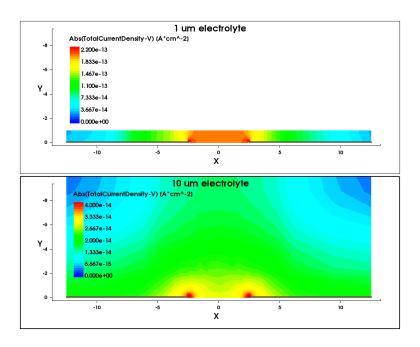

|          | . Spatial current distributions in coplanar EDLCs with 1 um and 10 um thick electrolyte films with a 100 mV applied voltage. Crowding effects are more visible in thinner electrolytes.                                                                                                                                            |

Fig. 95. Comparison of experimental planar EDLC capacitance and series resistance versus simulated values from the TCAD setup (a)–(b) with the addition of a fixed 150 pF capacitance to the simulated results for consistency with the experimental measurements. In (c)–(d), the extra 150 pF capacitor is removed, demonstrating the series resistance drop at f > 3 kHz is introduced by the Solartron.

# LIST OF TABLES

| Table 1. Nominal Parameters for Simulated IM-FinFETs                                                                                    |

|-----------------------------------------------------------------------------------------------------------------------------------------|

| Table 2. Delay and Leakage Mean and Sigma over All Benchmarks with 1 nm LER for Resist (R) and Spacer (S) FinFET Technologies           |

| Table 3. Nominal Parameters for Simulated JL-FinFETs                                                                                    |

| Table 4 Allowed Tuning Range of Fitted Compact Model Parameters                                                                         |

| Table 5. Nominal SNM and SNM Loss from Variability for JL-FinFET Technologies 44                                                        |