# **UC Berkeley**

# **UC Berkeley Electronic Theses and Dissertations**

#### **Title**

SOLUTION-PROCESSED INORGANIC ELECTRONICS

#### **Permalink**

https://escholarship.org/uc/item/99s6310r

#### **Author**

Bakhishev, Teymur

# **Publication Date**

2011

Peer reviewed|Thesis/dissertation

## SOLUTION-PROCESSED INORGANIC ELECTRONICS

by

Teymur T. Bakhishev

A dissertation submitted in partial satisfaction of the requirements for the degree of

Doctor of Philosophy

in

Engineering - Electrical Engineering and Computer Sciences

in the

**Graduate Division**

of the

University of California, Berkeley

Committee in charge:

Professor Vivek Subramanian, Chair

Professor Ali Javey

Professor Oscar D. Dubon

Spring 2011

#### Abstract

#### SOLUTION-PROCESSED INORGANIC ELECTRONICS

by

#### Teymur T. Bakhishev

Doctor of Philosophy in Engineering - Electrical Engineering and Computer Sciences

University of California, Berkeley

Professor Vivek Subramanian, Chair

The field of low-cost and solution-processed electronics has experienced a steady increase in research interest over the past two decades. Fueled by continuous advances in materials development and deposition techniques, low-cost, printable electronics are approaching reality. However, a number of advances remain to be accomplished in order to enable some key, sought after applications, such as displays and RFID tags. In particular, to realize such systems, it will be necessary to facilitate the development of a number of underlying electronic devices, including conductors, transistors, and memory technologies. These particular devices are the focus of this work.

This work is focused on transparent thin film transistors (TFTs) and conductors for flexible displays and memories for printed RFID tags. TFTs and conductors are based on ink-jet printed reduced graphene oxide (rGO). Conditions for achieving good printed features, such as jetting dynamics, ink formulation, and printing temperature control are examined. Effects of these conditions, as well as various annealing schemes, on electrical performance are presented. Physical properties of printed films are investigated by atomic force microscopy (AFM) and X-ray photoemission spectroscopy (XPS). Resulting devices exhibit drive currents up to 1  $\mu$ A, current ON/OFF ratios of up to 10, and field effect mobilities of up to 0.018cm²/V-s. Presented drive currents and mobilities are sufficient to drive a basic display pixel; however, larger ON/OFF ratios are generally required. Potential solutions to achieving higher ON/OFF ratios, such as use of nano-ribbon graphene inks or dual gate structures, are proposed.

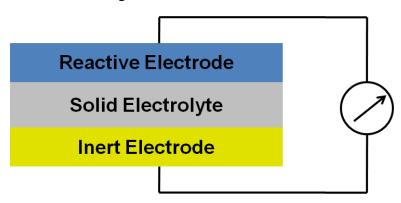

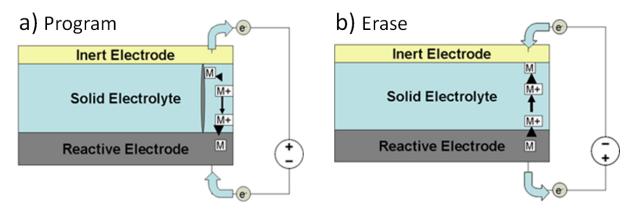

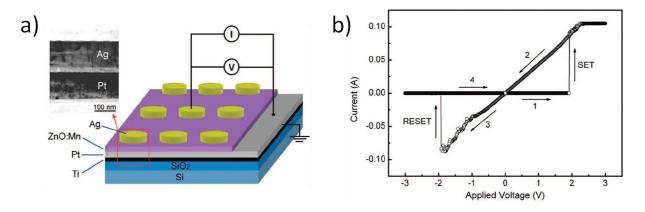

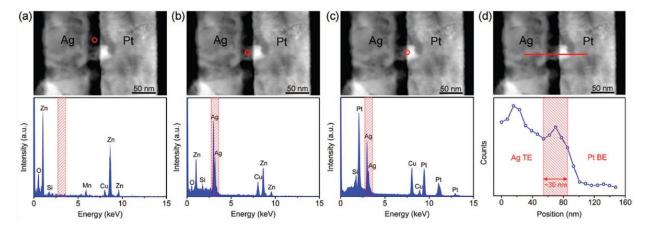

Memory presented in this work is based on filamentary switching in a silver/zinc oxide/gold (Ag/ZnO/Au) stack. There, diffusing Ag ions can reversibly form conducting paths through the ZnO electrolyte, thereby accomplishing data storage by changing the resistive state of the cell. A fully solution-processed cell is presented along with control cells based on evaporated metal contacts. Overall, good memory characteristics are observed: long retention time, cycling endurance of over 2000 cycles, good memory window, and minimum programming time of 200 ns. Filament growth dynamics are examined via potentiostatic, potentiodynamic, and temperature measurements. With the exception of a high temperature ZnO annealing step (350°C), these memories are fully-printable and plastic-compatible. Possible solutions for achieving low-temperature ZnO are presented, such as plasma treatments of deposited films and alternative sol-gel deposition techniques. With the incorporation of plastic-compatible electrolyte, this memory technology presents a promising candidate for printed electronics.

#### Acknowledgements

First and foremost, I would like to thank my parents, Lisa and Tofik. This thesis belongs to them at least as much as it does to me. Their continuous support and encouragement made my education possible. I would also like to thank my sister, Delya, for her moral support and relentless attempts at trying to take an interest in my work. My parents have sacrificed so much to bring us here and give our family a better life and for that I will be forever grateful.

I would like to thank my graduate advisor, Vivek Subramanian. He has provided me with invaluable advice over the years as well as freedom and support to pursue my research interests. He has been a great mentor academically, professionally, and personally. I thank Professor Oscar Dubon for his advice and involvement on various projects; Professors Ali Javey and Nathan Cheung for their help and advice throughout my graduate career. I would also like to thank my collaborators from the Naval Research Laboratory Jeremy Robinson, Paul Sheehan, and Zhongqing Wei for help and advice on the graphene project. Helpful and knowledgeable staff from the Microlab, the machine shop, and the grad office; in particular Phill Guillory, Joe Donnelly, Ben Lake, and Ruth Gjerde.

I am grateful for all the lab mates and fellow students I had the privilege of working with. They are the only ones that can truly understand and relate to the joys and troubles of graduate life. Special thanks to Steve Volkman, Donovan Lee, and Shong Yin for countless conversations about work, life, and just about everything else. David Redinger, Feng Pan, Dan Soltman, and Michael Tseng for help and advice with various projects. Lakshmi Jagannathan, Daniel Huang, Frank Liao, Josei Chang, Ben Weil, and the rest of the Organic Electronics Group students and alumni for being great colleagues and friends. Of course, I am particularly grateful to Alejandro De la Fuente Vornbrock who has welcomed me into the group as a mentor, helped me throughout my career as a colleague, but, most of all, he has been a great friend.

Many people influenced my graduate experience, but I am especially thankful for having Joanna Lai in my life. She has made it more pleasant and enjoyable with her unwavering support, her exciting personality, and her friendship. With her, failures were less hurtful and successes more satisfying.

I would like to acknowledge financial support from the Intel Robert N. Noyce Fellowship and the National Science Foundation.

# **Table of Contents**

| 1       | Intr  | oduct | tion: Solution-processed electronics  | 1    |

|---------|-------|-------|---------------------------------------|------|

|         | 1.1   | Арр   | lications                             | 2    |

|         | 1.1.  | .1    | LCD                                   | 3    |

| 1.1.2   |       | .2    | RFID                                  | 7    |

| 1.2 Org |       |       | anization                             | 9    |

| 2       | Gra   | phen  | e Thin Film Transistors               | . 11 |

|         | 2.1   | TFT   | Background                            | . 11 |

|         | 2.1.  | .1    | TFT Modeling and Parameter Extraction | . 13 |

|         | 2.2   | Acti  | ve Materials                          | . 13 |

|         | 2.2.  | .1    | Organic SCs                           | . 13 |

|         | 2.2.  | .2    | Metal Oxide (Chalcogenide) SCs        | . 14 |

|         | 2.3   | Gra   | phene                                 | . 15 |

|         | 2.3.  | .1    | History                               | . 15 |

|         | 2.3.  | .2    | The Magic of Graphene                 | . 16 |

|         | 2.3.  | .3    | Opening the Bandgap                   | . 17 |

|         | 2.4   | Gra   | phene Oxide                           | . 19 |

|         | 2.4.1 |       | Fabrication                           | . 20 |

|         | 2.4.  | .2    | Reduction                             | . 20 |

|         | 2.4.  | .3    | GO Deposition Methods                 | . 22 |

|         | 2.5   | Ink   | Jet Printed rGO TFTs                  | . 23 |

|         | 2.5.  | .1    | Device Fabrication                    | . 23 |

|         | 2.5.  | .2    | Results and Discussion                | . 26 |

|         | 2.6   | Sum   | ımary                                 | . 31 |

| 3       | Gra   | phen  | e Conductors                          | . 33 |

|         | 3.1   | Арр   | lications and Requirements            | . 33 |

|         | 3.1.  | .1    | LCD Electrodes                        | . 33 |

|         | 3.1.  | .2    | Interconnects                         | . 35 |

|         | 3.2   | Con   | ductive Inks                          | . 36 |

|         | 3.3   | Gra   | phene Conductors                      | . 39 |

|         | 3.3.  | .1    | Properties of graphene conductors     | . 39 |

|         | 3.3.  | .2    | Incorporation of Graphene Conductors  |      |

|         | 3.4   | Fabi  | rication                              |      |

|         | 3.4.  | .1    | Printing Conditions Optimization      | . 44 |

|          | 3.4.2 |                                 | Experimental Setup and Sample Preparation         | 46 |  |  |  |

|----------|-------|---------------------------------|---------------------------------------------------|----|--|--|--|

| 3.4.3    |       | 3                               | Substrate Temperature and Print Frequency Control | 47 |  |  |  |

| 3.5 Ann  |       | Ann                             | eal Effects                                       | 51 |  |  |  |

| 3.6 Disc |       | Disc                            | ussion                                            | 53 |  |  |  |

|          | 3.7   | Sum                             | nmary                                             | 54 |  |  |  |

| 4        |       |                                 |                                                   |    |  |  |  |

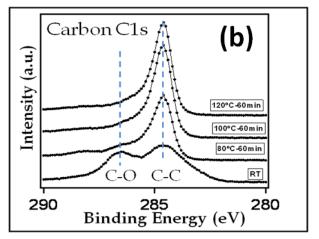

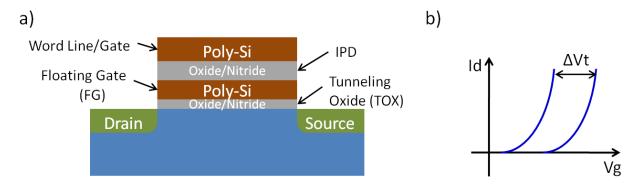

|          | 4.1   | Flas                            | h Memory Background                               | 55 |  |  |  |

|          | 4.2   | Solu                            | ition Processed Memory Background                 | 58 |  |  |  |

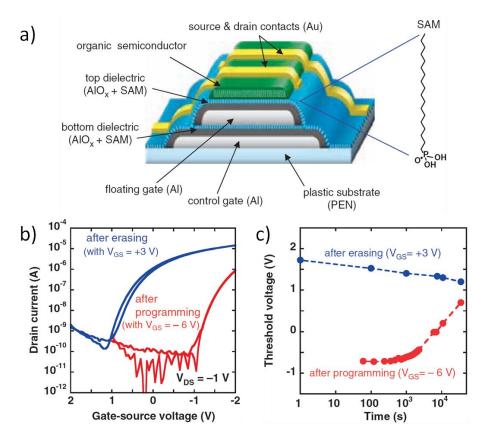

|          | 4.2.  | 1                               | Organic Flash                                     | 58 |  |  |  |

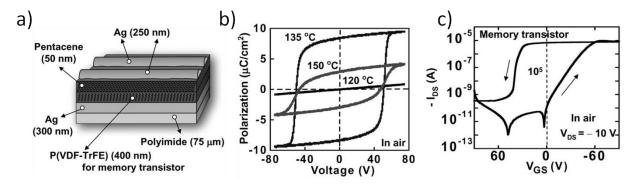

|          | 4.2.  | 2                               | Ferroelectric Memory                              | 60 |  |  |  |

|          | 4.3   | Resi                            | stive Memory Background                           | 61 |  |  |  |

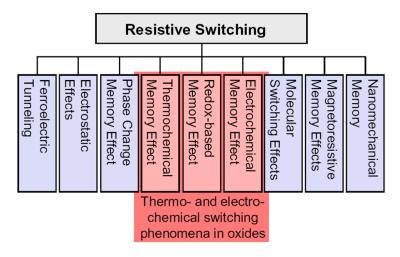

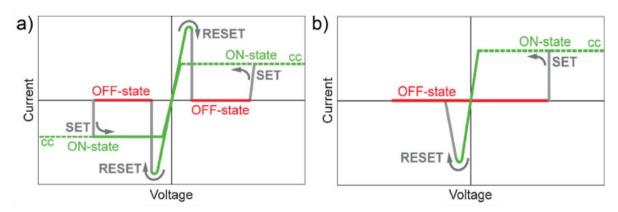

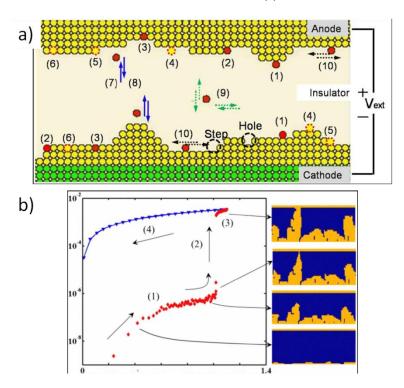

|          | 4.3.  | 1                               | Electrochemical Mechanism Switching               | 62 |  |  |  |

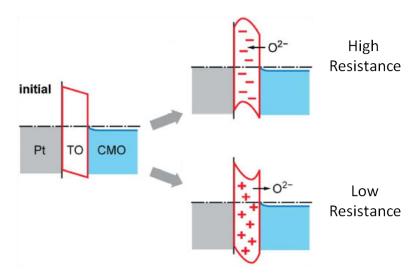

|          | 4.3.  | 2                               | Valence Change Mechanism Switching                | 65 |  |  |  |

|          | 4.3.  | 3                               | Thermo-Chemical Mechanism Switching               | 66 |  |  |  |

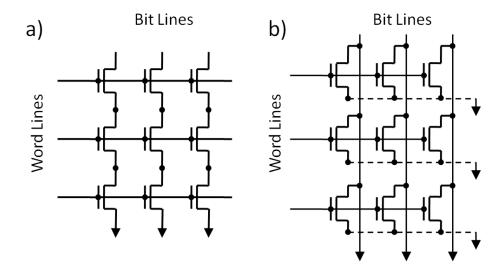

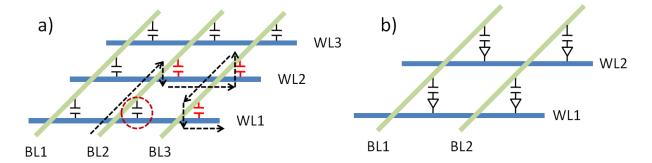

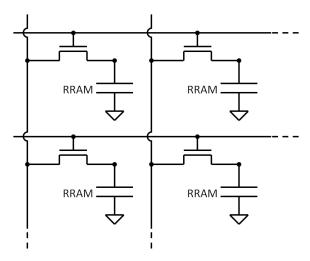

|          | 4.3.  | 4                               | RRAM Circuit Architectures                        | 67 |  |  |  |

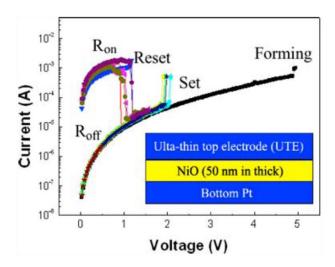

|          | 4.3.  | 5                               | Sputtered Ag/ZnO/Pt                               | 69 |  |  |  |

|          |       | Fabi                            | rication and Materials Characterization           | 70 |  |  |  |

|          | 4.4.  | 1                               | ZnO                                               | 70 |  |  |  |

|          | 4.4.  | 2                               | Cell Fabrication                                  | 73 |  |  |  |

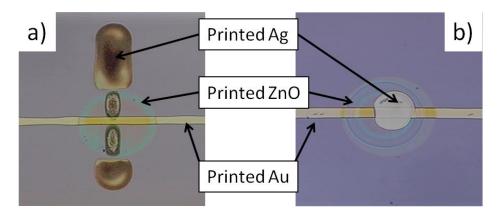

| 4.4.3    |       | 3                               | Ink-Jet Printing                                  | 74 |  |  |  |

|          | 4.4.  | 4                               | Experimental Setup and Sample Preparation         | 75 |  |  |  |

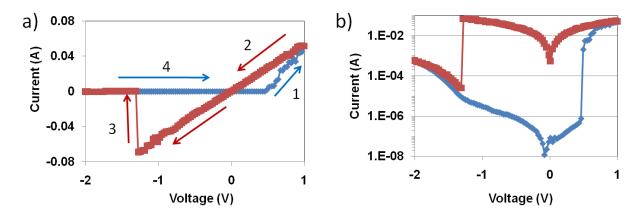

|          | 4.5   | Resi                            | ults and Discussion                               | 75 |  |  |  |

|          | 4.5.  | 1                               | Electrode Study                                   | 75 |  |  |  |

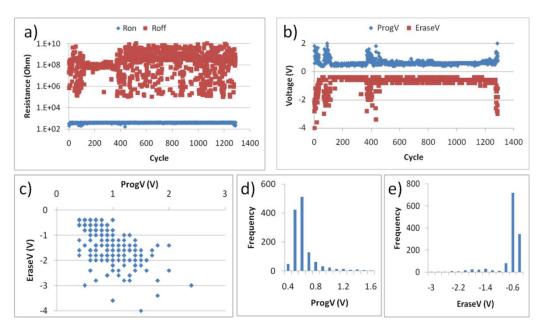

|          | 4.5.  | 2                               | ProgV/EraseV Characteristics                      | 80 |  |  |  |

|          | 4.5.  | 3                               | Data Retention and Voltage Disturb Effects        | 81 |  |  |  |

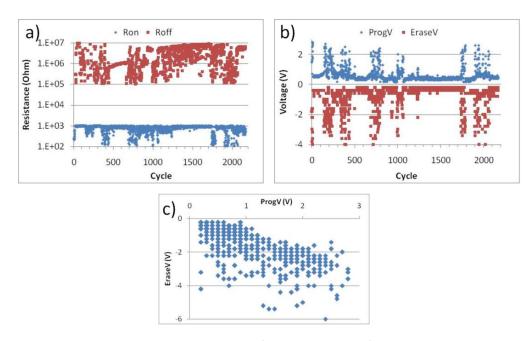

|          | 4.5.  | 4                               | Cell Size Effects                                 | 83 |  |  |  |

|          | 4.5.  | 5                               | Low Temperature Fabrication                       | 83 |  |  |  |

|          | 4.5.  | 6                               | Switching and Filament Growth Dynamics            | 84 |  |  |  |

|          | 4.6   | Sum                             | nmary                                             | 89 |  |  |  |

| 5        | Con   | Conclusions and Future Outlook9 |                                                   |    |  |  |  |

| <u>د</u> | Dibl  | Ribliography                    |                                                   |    |  |  |  |

# 1 Introduction: Solution-processed electronics

The pace of advancements in the field of electronics in recent years has been historically unparalleled and will likely continue to accelerate, particularly in the area of personal and mobile computing. Such progress can be attributed to improvements throughout the entire hierarchy of the field, starting from novel and improved materials all the way to innovative circuits and systems design. Furthermore, the emergence of novel processing techniques has introduced a possibility of drastically reducing the cost of personal electronics and allowing further expansion of the market. Once considered futuristic, products like foldable displays or e-papers and smart e-clothing may not be far away, and that in turn would allow a more ubiquitous integration of information technology into everyday life.

The cost of any electronic gadget is a complicated assortment of factors; however, some of the key components include the cost of the substrate used and the cost of processing (lithography, vacuum, thermal, etc.). Reducing the cost of these components may drastically affect the overall cost of the product. Consider a silicon wafer generally used in standard electronics processing: depending on the size and purity it may cost up to several dollars per square inch. In contrast, a plastic substrate, such as PET or PEN, may cost as low as single cents per square inch. However, said substrates will impose processing temperature restrictions due to plastic deterioration (150C and 200C for PET and PEN, respectively). This restriction on temperature may limit materials compatibility, but it also steers the processing away from potentially costly high-temperature processing steps.

Solution processing of electronic materials has been a research interest for quite a while as a path to ubiquitous electronics. In particular, printing techniques such as ink-jet and gravure are promising candidates for replacement of traditional lithography and deposition techniques. Currently, electronics fabrication consists of multiple deposition, lithography, and etch steps which are costly individually and overall due to the subtractive nature (whereby a blanket film is deposited and parts of it are removed to create a pattern). Printing, on the other hand, provides an additive process where material is only deposited where required, which reduces the net waste and material consumption. This therefore replaces both a deposition step (which may include vacuum and high-temperature), as well as a subsequent lithographical patterning step.

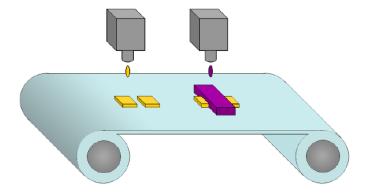

Printing in the context of electronics, whether ink-jet, gravure, or otherwise, generally involves deposition of functional inks in certain patterns to serve a specific purpose. The inks can be of metallic, semiconducting, or insulating nature, thereby covering all the necessary components of semiconductor manufacturing. A multitude of materials have been developed as candidates for such inks including organic insulators, polymer semiconductors and conductors, inorganic nanoparticles, as well as inorganic carbon solutions. Additionally, printing techniques are compatible with roll-to-roll continuous processing which increases throughput and decreases costs. A schematic representation of a basic additive process via ink-

jet printing can be seen in Figure 1.1, where different materials are deposited sequentially to form a device. Printing has been demonstrated as a possible fabrication route for thin film transistors, solar cells, light emitting diodes, sensors, and memory devices. Additionally, there are prototypes of entire electronic systems, such as RFID tags and displays.

Figure 1.1. Ink-jet Printing Process.

# 1.1 Applications

Applications with the potential to utilize solution fabrication routes that garner the most attention are displays and RFID tags. The decrease in the cost of displays has been a key contributor to the expansion of personal media and communication electronics. An interactive display lies at the heart of almost any mobile computing device, such as a smartphone or a tablet. These have been getting smaller and thinner with each successive generation. One of the anticipated next steps in display development is the introduction of flexible displays. Currently displays are manufactured on glass and employ conventional processing techniques (lithography, vacuum, and high temperature steps). However, introduction of flexible technology would require flexible substrates, such as plastics. These substrates would, in turn, enable incorporation of roll-to-roll manufacturing which is compatible with solution-processing techniques. Additionally, a significant decrease in manufacturing cost of displays may allow incorporation into brand new markets, such as smart, interactive packaging and clothing.

Similar to displays, RFID tags and other mobile data and media interface devices are poised to break into the market on an unprecedented scale. An RFID tag could potentially replace a bar code for certain situations (such as checkout counters). It can contain significantly more information about the product than a bar code and requires less human interaction in handling, as the information stored can be read over a larger distance and has no line-of-sight requirements. Such RFID schemes have already been implemented by a wide range of industries to track package shipping, livestock, freight, and card key access. However, at present, tags are too expensive to penetrate more cost sensitive markets such as bar code replacement for supermarkets. Fabrication of RFID tags and displays via solution processing and printing techniques holds the promise of reducing production costs and allowing implementation on a wider scale.

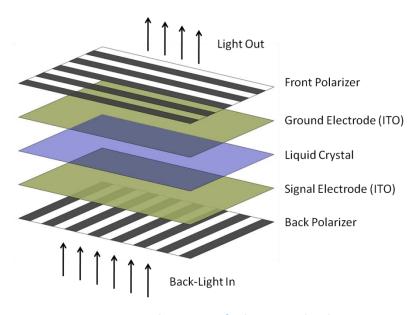

Figure 1.2. Schematic of a basic LC display.

#### 1.1.1 LCD

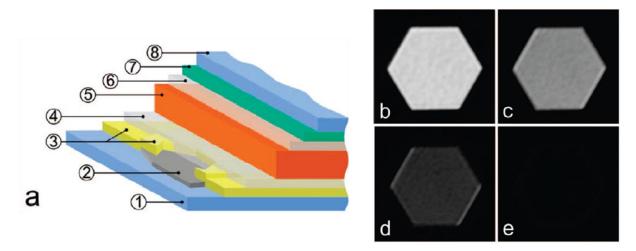

Most current LCD applications employ an active matrix addressing scheme, where a control transistor is implemented for each pixel to enable switching. In this chapter, "LCD" will generally refer to AMLCD, unless otherwise specified. Let us examine the operation of a basic LCD display. A display consists of a large array of pixels/cells that can be individually selected to allow or prevent light passing through the cell, thereby producing a bright or dark pixel, respectively. A basic schematic of an LCD is presented in Figure 1.2. Generally, a display consists of a backlight source, a polarizing filter, a liquid crystal (LC) cell, and a second polarizing filter orthogonal to the first. An LC cell consists of a layer of liquid crystals sandwiched between two transparent electrodes, usually indium tin oxide (ITO). Application of voltage to the electrodes can force a change in alignment of the LC and the polarization of the light passing through. If the polarization of the light matches the polarizing filter on the outside of the cell, light is allowed to pass through, hence creating a bright pixel. If the induced LC alignment is such that light polarization does not line up with the filter, no light passes and a dark pixel is produced. A cell is addressed by properly biasing a control thin film transistor (TFT) attached to the cell, which in turn sets up an electric field across the LC electrodes which forces the liquid crystals into either transparent or opaque alignment. Figure 1.3a shows a schematic of a pixel array. Addressing happens by biasing appropriate gate and signal bus-lines.

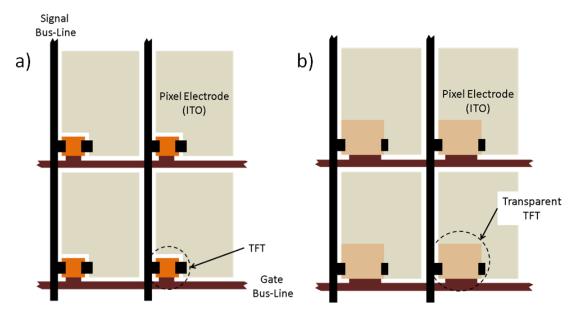

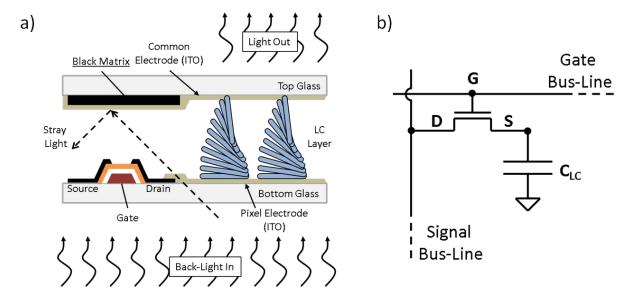

Select TFTs and electrodes are key components of LCD circuitry. Proper selection and optimization of these will directly affect display performance and, thus, must be considered carefully. Parts of this work will address fabrication and characterization of transparent TFTs and electrodes. Benefits of their integration in an LCD will be discussed in this section. Figure 1.4(a) shows a cross section schematic of an LCD pixel. It can be seen that light only passes through the transparent ITO area, whereas some portion of the total screen area is blocked by the interconnect wiring and the control TFT. Such TFTs are generally manufactured from amorphous or poly-crystalline silicon (Si) and are not good transmitters of light. The blocked

Figure 1.3. (a) Schematic of standard LCD pixel array, (b) Schematic of a pixel array with transparent TFTs.

Figure 1.4. (a) Cross section schematic of an LCD pixel, (b) Circuit diagram of a pixel.

light does not contribute to the display signal which has a negative effect on overall brightness and contrast ratio. The relation of useful to wasted light is often called Aperture Ratio and is calculated as follows:

$$A = \frac{transmissive \ area \ of \ a \ pixel}{total \ area \ of \ a \ pixel} * 100\%$$

The aperture ratio is a critical parameter determining performance of an LCD display and a ratio close to one is desired. It can be seen that decreasing the size of the control TFT will

increase the transmissive area of the pixel and improve aperture ratio (Figure 1.3a). However, care should be taken in properly sizing the control device. The function of the TFT is to pass current and effectively charge the ITO/LC/ITO capacitor (CLC), as demonstrated in Figure 1.4b. Size of the TFT directly affects the RC delay of the overall cell, which in turn determines the switching speed of the display. A TFT that is too small would not be able to source enough current, hence resulting in a slow switching display. Conversely, a large TFT would allow faster switching, but would simultaneously degrade the aperture ratio. So a tradeoff between speed and picture quality has to be considered when designing such cells. However, a significant improvement in performance can be obtained if the control TFT is manufactured from a transparent material. Such a design would significantly relax the inherent tradeoffs associated with optimizing the aperture ratio, as the size of the active area of the TFT would not contribute towards the portion of the light that is wasted. Figure 1.3b demonstrates this principle. It can be seen that the overlapping transparent TFT would allow a larger part of an individual pixel to transmit light, hence improving aperture ratio. It should be noted that the transparent TFT was deliberately scaled to appear larger than its conventional counterpart with the purpose of alluding to two points: first, currently proposed replacement TFT materials are not quite ready to compete with conventional technology, particularly in drive current. As such, these devices may have to be larger in size to produce equivalent current sufficient for appropriate switching speed. The second point, however, is to demonstrate that a transparent control device can occupy a large portion of the pixel with potentially negligible degradation in optical performance.

Consider a control TFT in a standard LCD application. Operation of such device can be approximately modeled with a standard square-law drive current formula, given by:

$$I_{D,Sat} = \frac{W}{2L} \mu_{Sat} C_{OX} (V_G - V_T)^2$$

Generally drive current on the order of 1  $\mu$ A is required to drive a cell[1]. Given currently available state-of-the-art printing techniques, a 10  $\mu$ m gate length can be achieved. Assuming a W/L value of 100, which is reasonable for a transistor spanning the entire pixel, an overdrive voltage of 5 V, and oxide thickness of 100 nm, mobility requirements can be calculated. This results in mobility of 0.015 cm²/Vs. This value is achievable with current printing technologies. Current LCD applications generally utilize amorphous silicon ( $\alpha$ -Si) TFT which produce mobilities of about 1 cm²/Vs, and thus can be sized much smaller. It should be noted that the W/L ratio used in the calculation would essentially span the whole pixel width; however, as mentioned before, given TFT transparency optical, performance would not be degraded. Such metrics and performance comparisons will be examined in more detail in the following chapters.

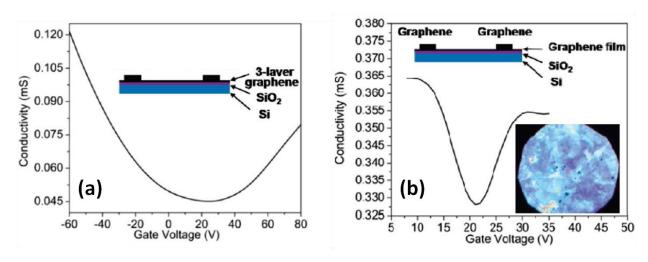

Several materials have been examined in recent years as potential candidates for transparent TFTs including semiconducting polymers, various metal oxides (such as Zn, In and their doped and alloy variants), and graphene. Graphene, a two dimensional form of inorganic carbon, has become a heavily researched material because of its interesting and unique characteristics both as a conductor and a semiconductor. Through chemical processing it can be oxidized and form graphene oxide (GO) which forms stable suspensions in water, which can

subsequently be printed or otherwise solution deposited. Once on a substrate, GO can be reduced back to graphene and regain most of its electronic properties by thermo-chemical processes below 100°C. Both metallic and semiconducting variants of graphene can be deposited from the same starting solution by controlling deposition thickness and post-deposition processing. Graphene's compatibility with low-cost solution processing could make it well suited for low-cost and flexible electronics. Parts of his work will focus on graphene and its properties and the possibility of incorporation into flexible/transparent electronics.

Optical characteristics of an LCD display can be improved further by introducing transparent conductors and interconnects in conjunction with transparent TFTs. Figure 1.4a shows a cross section of a basic LCD cell. It demonstrates how stray light can penetrate through parts of the back plane which are not controlled by a specific cell and introduce light leakage, which degrades optical metrics such as contrast ratio and color fidelity. Light leakage can occur in multiple locations on the back plane: between pixel electrodes and bus lines, around the edges of control TFTs, interconnects, etc. To ameliorate light leakage a Black Matrix (BM) layer is introduced on the top plane. It is a patterned layer of opaque material which covers the areas where light leakage may occur, thereby preventing unwanted light from escaping. As a consequence of the addition of the BM a larger portion of the overall area is wasted by not transmitting light signal, hence the aperture ratio is decreased as well as brightness. However, if the signal bus lines and the interconnects can be replaced with transparent materials, alternative multi-planar cell architectures maybe applied. In such a case the bus lines along with control TFTs could be "folded" underneath the pixel electrode and a larger portion of the cell could transmit light. This may drastically reduce or eliminate the need for the BM layer, improve aperture ratio, brightness and other critical optical characteristics.

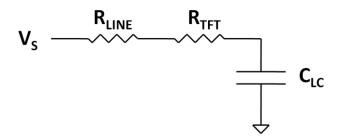

Let us consider the effects of line resistance on charging an LCD cell. In "turned on" state, Figure 4(b) can be simplified as an RC charging circuit, presented in Figure 1.5. The charging time of the LC cell, represented as effective capacitance,  $C_{LC}$ , can be expressed by the following equation:

$$V_{LC} = V_S (1 - e^{-t/R_{TOT} C_{LC}})$$

where  $R_{TOT}$  is total combined resistance of the signal line ( $R_{LINE}$ ) and the control TFT ( $R_{TFT}$ ), and  $V_S$  is the signal voltage. Alternatively, the equation can be rewritten to solve for time:

$$t = -R_{TOT} C_{LC} \ln \left(1 - \frac{V_{LC}}{V_S}\right)$$

For a large cell array, the contribution from the line resistance can get quite large. For simplicity, it is assumed to be equal to  $R_{TFT}$ . Currently, sputtered metal is used for signal lines with low resistivities on the order of  $10^{-7}~\Omega$ -m, and widths on the order of  $10~\mu$ m. As discussed earlier, the width has to be minimized to maximize aperture ratio. However, if the width restriction is relaxed to  $100~\mu$ m or, maximally, to the width of a pixel, charging time will be improved by approximately 50% or more. Alternatively, a lower resistivity material can be used and still maintain appropriate charging time. Thus, a transparent conductor can be utilized as

signal line material with resistivities of 10 - 100 times greater than sputtered metal and still achieve proper switching characteristics.

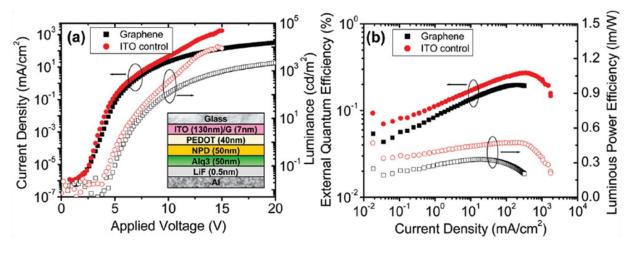

Figure 1.5. A simplified RC circuit representation of a charging LCD cell.

Another key component of an LCD cell is the ITO electrode itself. It has to fulfill two important requirements: first, it has to be highly transparent and cause minimum attenuation of the light. Second, it has to be conductive enough as to not degrade the RC delay of a cell. In the scope of currently available display technology, ITO has performed quite well; however, there are some potential problems with it going forward. One key problem is the rising cost of indium. With the rising demand of indium for the ever growing display market and its increased use in conductive pastes and solders, coupled with the shortage in production, the price of indium has been rising steadily over recent years. This not only causes general concern for the display market, but is particularly detrimental to efforts of incorporating ITO into low-cost electronics. Furthermore, in order to achieve required conductivities, ITO contact film thickness needs to exceed 100 nm. In that thickness range, ITO becomes brittle and unstable while bent, which introduces yet another barrier to its incorporation into flexible, low-cost electronics. The final, and perhaps most important, problem with ITO in regards to low-cost electronics is the fact that currently there is no good way of deposition that is compatible with low-cost routes. Sol-gel processes exist which require temperatures in excess of 500C which eliminates compatibility with inexpensive substrates; whereas room temperature sputtering techniques would still require post deposition patterning involving lithography and subtractive etching. Therefore, an alternative transparent conductor is required for integration with a fully solutionprocessed flow. Graphene is yet again a promising candidate for this role. In its metallic state, graphene has been shown to be an excellent material for both large area transparent electrodes as well as contacts for both organics TFTs and OLEDs. This work will demonstrate the compatibility of graphene with solution processing and will discuss the characteristics of conductors obtained with such techniques.

#### 1.1.2 **RFID**

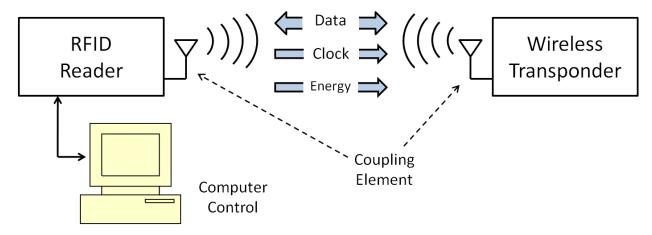

RFID tags and other "smart" devices are expected to allow on-the-go data interactions and such devices will all inevitably require some capacity for memory storage. Let us examine the basic operation of an RFID system as demonstrated in Figure 1.6.

Figure 1.6. Diagram of an RFID system.

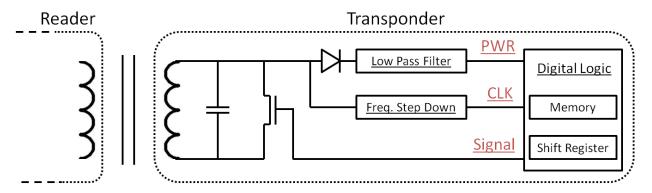

Generally the system consists of a reader and a transponder (or tag), which could be coupled magnetically or electromagnetically via an antenna. A reader produces a signal which, once coupled to the tag, provides both data and energy to power the electrically passive transponder. The tag then sends a signal with a unique identifier back to the reader to be interpreted. A reader system may consist of a single or multiple computers capable of various levels of data processing. As such the reader has no constraints on power, speed, and, to a large extent, cost since it is usually a singular part of a large implementation. Conversely, the cost of a tag plays a more significant role since any given RFID implementation may include hundreds or thousands of tags. Figure 1.7 demonstrates operation of a basic RFID tag. The signal from the reader is coupled through an antenna consisting of an inductor which is coupled to a capacitor to produce a resonant circuit. The signal produced by the antenna is then rectified and used to power the tag. The original signal could also be used as a clock for onboard logic. The clock frequency may be stepped down to be compatible with the logic elements. The logic portion of the tag generally consists of a nonvolatile memory array and output shift registers. Logic output is then fed back to the antenna and transmitted to the reader.

There are a large number of academic and industrial groups that have done extensive research on solution-processing techniques for RFID incorporation. To date, a large portion of the work has been dedicated to printable organic transistors[2-4] and passive components[5,6]. In fact, full tags have been demonstrated based on organic transistor logic[7-10]. Additionally, Jung et. al. have recently demonstrated a fully roll-to-roll printed tag[11]. However, none of these demonstrations had incorporated a printed programmable memory. So far, memory has been achieved by a secondary attached chip, hardwiring the circuitry, or post-fabrication physical alteration, such as mechanical or laser ablation. Mattis has achieved a potentially printable memory architecture based on an organic diode/antifuse stack[12]; however, this is a write-once design and it has not been demonstrated via solution-processing. It is clear that printed memory technology is necessary for a successful implementation of a low-cost, solution-processed RFID tag.

Currently two types of memory are used for conventional RFID tags without batteries: read-only and read/write. Read only memory is achieved by "writing" the data directly during

the manufacturing process, or by using a laser to "burn" data onto a configurable part of the chip after manufacturing. Read-only memory is generally used for price-sensitive applications, where the cost of a read/write memory is prohibitive. To achieve write and erase functionality, EEPROM is generally used. Storage capacity varies between single bytes to tens of kilobytes. EEPROM usually consists of a flash-like transistor design which will be described in more detail in Chapter 4. To program this device, voltages around 20 V are necessary. Since an RFID tag is usually supplied with 3 V - 5 V from the coupling antenna, a charge pump is required to achieve proper programming. This is a very long and energetically expensive process which requires up to tens of milliseconds and hundreds of microjoules. A faster, lower power technology is desired.

Figure 1.7. Schematic of a basic RFID tag.

A few solutions have been proposed for printed memories including ferromagnetic devices and flash-like organic transistors; however, none have shown significant potential for long term, full scale integration. Resistive random access memory (RRAM) variants based on metallic filament formation through a dielectric have shown some promise as a candidate for low-cost implementation. Such memories usually operate on the principle of metal ion (usually silver or copper) diffusion through various dielectrics (often metal oxides or sulfides). Parts of this thesis will demonstrate RRAMs based on silver (Ag) filament formation through a zinc oxide (ZnO) dielectric in an Ag/ZnO/Au cell, which can be fully solution-processed. Various properties of this system will be investigated for potential implementation into low-cost RFID tags.

# 1.2 Organization

This thesis is organized in the following manner:

Chapter 2 will introduce graphene as a potential material for solution-processed TFTs. Graphene's unique electronic properties will be discussed. It will be compared to other transparent semiconducting materials in the context of printed electronics. Ink-jet printed graphene TFTs based on graphene oxide will be presented; fabrication and processing techniques as well as resulting device characteristics will be discussed.

Chapter 3 will discuss ink-jet printed graphene conductors. Other solution-processed conductors will be introduced and compared to printed graphene. Effects of various fabrication and processing steps on the electronic properties of conductive lines will be examined.

Chapter 4 will introduce resistive random access memory (RRAM) and its principle of operation based on zinc oxide (ZnO) nanoparticle films. Various solution-processed memories will be discussed and compared. Data on electric properties, endurance, retention, and temperature effects will be presented.

Chapter 5 will provide conclusions and potential future research related to the topics covered.

# 2 Graphene Thin Film Transistors

# 2.1 TFT Background

A transistor is the most important element in electronics. It responsible for performing crucial tasks in both digital and analog circuits such as signal processing and logic functions. In LCDs, it serves a critical role of controlling individual pixels, as discussed earlier. Most conventional integrated circuits (ICs) are produced from single crystal silicon transistors. However, applications that demand substrates other than standard silicon often require deposition of all the materials necessary to form transistors, usually in form of thin films. An LCD is a perfect example of this, where a glass substrate is used to allow light transmission. A thin film transistor (TFT) is then "grown" on top by sequentially depositing patterned thin films. Currently this field is dominated by amorphous silicon (a-Si) TFTs; consequently, this is the technology against which all novel approaches, including printed transistors, are compared.

Any novel TFT will have to be compared based on metrics such as field effect mobility ( $\mu$ ), drive current, off current, on/off ratio, threshold voltage ( $V_T$ ), and subthreshold slope (SS). Depending on any given application some of these parameters may become more important that others, which in turn may guide materials and processing selection. For example, a low-cost flexible display may require select transistors with a large on/off ratio to allow large array implementation, whereas drive current requirements may be relaxed if switching speed is not critical.

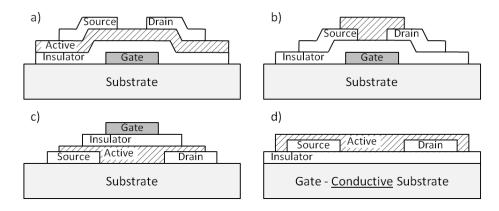

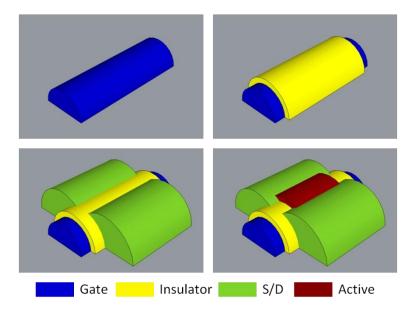

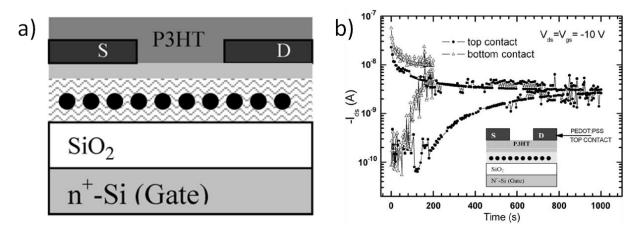

The structures generally used for fabrication of standard TFTs and printed TFTs are quite similar. Those can be gated from either top or bottom, and also have the source and drain (S/D) contacts on either top or bottom (Some examples are presented in Figure 2.1). It should be noted that the structure with a highly conductive bottom substrate as a gate is not practical for real life applications; however, it is very useful for lab prototyping printed transistors, especially for investigating semiconducting (SC) materials and S/D interactions. Usually such substrates consist of thermally oxidized, highly doped silicon.

Figure 2.1. Some TFT structure types.

Depending on the particular desired structure, the fabrication process flow of a printed TFT can proceed in various ways. An example of one such flow is given in Figure 2.2. This is a bottom-gate structure as presented in Figure 2.1(b). First, a gate line is printed, usually from metallic ink such as gold (Au) or silver (Ag), but other options are possible. Second, an insulator layer is deposited. Some of the often used insulator materials are organic polymer dielectrics, such as poly-vinylalcohol (PVA)[13], poly-vinylphenol (PVP)[14]; however, a multitude of other materials are currently being researched for this purpose[15]. Third, S/D contacts are printed. Again, these could be metallic in nature or a conducting polymer, such poly(3,4-ethylenedioxythiophene) poly(styrenesulfonate) (PEDOT:PSS)[16]. Finally, a semiconducting, or "active", material is deposited to bridge the S/D contacts. A variety of semiconductor materials have emerged as potential candidates to fill the role of a printable active material including polymers[14,16], inorganic nanoparticles[17] or sol-gels[18], and inorganic carbon systems[19] and no clear frontrunner has been identified yet.

Figure 2.2. A schematic of a sample printed TFT process flow.

The process, as described, may sound simple enough; however, the complexity of the overall system and the individual component interactions cannot be overstated. The gate lines, for example, cannot be too thin to ensure good conductivity; yet depositing lines of appreciable thickness may lead to surface roughness or cracking. This, in turn, may cause problems with the dielectric layer facilitating pinholes in the insulator or spikes through it, resulting in degraded or unusable devices. The dielectric layer has to be smooth and conformal in order to ensure electrical isolation between the gate and active material. It also has to be chemically favorable to the active material to prevent causing disorder at the insulator-semiconductor interface which will likely result in decreased performance[20]. The S/D contacts have to be energetically matched with the semiconductor to ensure proper carrier injection and transport. This is a commonly encountered problem between metallic contacts and organic semiconductors, which is sometimes overcome by introducing a secondary organic (mono)layer to the metal/SC interface to improve carrier injection. All of the mentioned examples barely scrape the tip of an

iceberg represented by the enormous amount of complexity associated with incorporating different, often dissimilar, materials to produce a transistor.

## 2.1.1 TFT Modeling and Parameter Extraction

In order to properly compare different TFT technologies, it is important to have a meaningful metrics of evaluation. Generally, device characteristics such as mobility, drive current, on/off ratio, threshold voltage ( $V_T$ ), and subthreshold slope (SS) are used for this purpose. Thin film transistors often operate in accumulation mode due to a large number of trap sites associated with impurities and defects in the semiconductor. These imperfections in the active layer cause additional energy states, in particular in the band gap of the material, which act like traps. Consequently, it is often hard or impossible to invert the semiconductor, which limits the operation range to accumulation. However, overall operation is quite similar to ideal transistors, where cut-off, linear, and saturation regimes are clearly present. This enables simple modeling of TFTs with basic square law equations and extraction of operational metrics, such as mobility, threshold voltage, and subthreshold slope. The linear and saturation square law equations are as follows:

$$I_{D,Lin} = \frac{W}{L} \mu_{lin} C_{OX} (V_G - V_T - \frac{V_{DS}}{2}) V_{DS}$$

$$I_{D,Sat} = \frac{W}{2L} \mu_{Sat} C_{OX} (V_G - V_T)^2$$

It is, however, difficult to predict the threshold voltage due to non-idealities and gradual turn on characteristics. It is often more appropriate to extract the transconductance given by:

$$g_{m,Lin} = \frac{dI_{D,Lin}}{dV_G} = \frac{W}{L} \mu_{lin} C_{OX} V_{DS}$$

$$g_{m,Sat} = \frac{dI_{D,Sat}}{dV_C} = \frac{W}{L} \mu_{Sat} C_{OX} (V_G - V_T)$$

then extract mobility by combining the equations. Mobility is quite often gate dependent, which is due to gradual filling of the trap states as a function of transverse electric field.

#### 2.2 Active Materials

The most actively researched aspect of printed TFTs has been the active material. As previously mentioned, there are multiple material systems that have shown promise as candidates for solution-processed semiconductors.

#### 2.2.1 Organic SCs

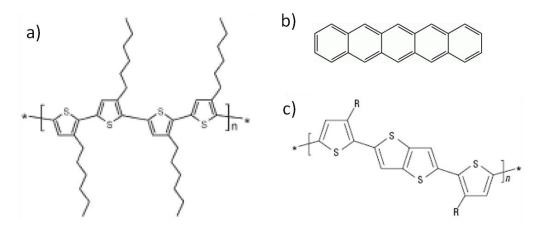

Organic semiconductors were some of the earliest materials widely investigated for printed applications, and are still heavily researched. Original work was done on polythiophene[21], and a good portion of the exploration since dealt with thiophene[22] or pentacene[23] derivatives. Figure 2.3 shows some of the more commonly used semiconductors for organic thin film transistors (OTFT). The basic building block of an organic semiconductor is a conjugated system with sp<sup>2</sup> hybridized carbon-carbon bonds. This bond scheme allows

delocalization of electrons which can effectively become (partially) free carriers[24]. Each molecule or unit of a polymer acts as a site with associated delocalized electrons. An organic film can then be represented as an assembly of such sites and individual delocalized carriers can hop from one site to another, thereby resulting in electrical conductivity.

Although certain properties, such as solvent compatibility and low processing temperatures, make some organic semiconductors attractive for solution processing, these polymers are generally not without significant disadvantages. Organic SCs are often very sensitive to oxygen and moisture, where prolonged, or even minor, exposure can cause significant degradation. Consequently, special care is required while processing these materials, which is usually done in an inert environment such as a glovebox. Furthermore, to ensure reasonable lifetime, OTFTs need to be heavily encapsulated to prevent atmospheric exposure. There have been, however, continuous advancements in the field of organic chemistry that have allowed organic SC performance to approach that of a-Si. Recently, poly(2,5-bis(3-alkythiophen-2-yl)thieno[3,2-b]thiophene has been developed, which exhibits significant improvements in oxygen stability and approaches performance of a-Si in mobility (up to 0.6 cm²/Vs)[25].

Figure 2.3. Some common organic semiconductors: a) poly-3(hexylthiophene) (P3HT), b) pentacene, and c) poly(2,5-bis(3-alkythiophen-2-yl)thieno[3,2-b]thiophene (pBTTT).

#### 2.2.2 Metal Oxide (Chalcogenide) SCs

Metal oxide (MO) binary systems have been investigated as semiconductors for quite a while; in fact, ZnO and its ternary derivatives deposited by sputtering are heavily researched material systems for use in transparent TFTs[26,27]. However, it wasn't until fairly recently that solution processable metal oxide semiconductors started to emerge as candidates for printed electronics[28,29]. The following section will focus on ZnO processing; however, the techniques discussed here are generally applicable to a number of similar systems, such as aluminum-doped zinc oxide (ZnO:Al), indium zinc oxide (IZO), gallium zinc oxide (GaZnO), and combinations thereof.

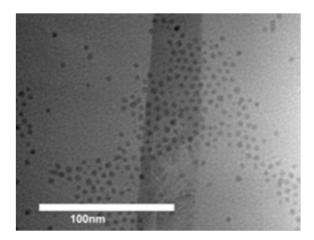

There are two major solution routes towards depositing ZnO: nanoparticle inks[30] and sol-gel[18]. Nanoparticle inks consist of particles in the range of 1-10 nm dissolved in a solvent,

possibly with other additives to increase solubility, stability, etc. Nanoparticles can be passivated or encapsulated with a surfactant to prevent agglomeration. (A more detailed description will also be included in Chapter 4 as it deals more directly with ZnO nanoparticles). After deposition, particles can be annealed and sintered into continuous films. This technique often requires anneal temperatures of up to 400°C for oxides, whereas some sulfide based films have been shown to become electrically active as low as 200°C[31].

In a sol-gel process a precursor is deposited on a substrate first and then converted to form the final product. The precursor is generally a salt of the metal of interest, such as acetate or nitrate, dissolved in a solvent. Again, additives could be introduced to either improve solubility or promote subsequent chemical conversion. For example, ammonium hydroxide can be added to a zinc salt solution. Sol-gel processes often require temperature up to 600°C - 700°C; however, there has been work recently where ZnO TFTs were demonstrated via a sol-gel process at 150°C. In that work, devices deposited by spin-casting exhibited mobilities of ~2 cm²/Vs, although it is unclear from the publication whether transfer to ink-jet printing is likely.

# 2.3 Graphene

## **2.3.1 History**

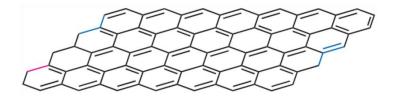

Graphene has become one of the most researched materials since its initial recent demonstration in 2004 by Geim and Novoselov[32]. Graphene is a truly two-dimensional form of carbon where individual atoms are arranged in a hexagonal, "honeycomb" pattern (Figure 2.4). When stacked together these sheets form graphite. The theoretical concept of a 2-D material has been around for over 60 years[33]; however, it was widely assumed that such structure could not exist physically due to thermodynamic instability. It was believed that thermal energy at any appreciable temperature would induce enough fluctuation of the lattice to preclude sustainability of the film and cause it to segregate into islands or decompose [34]. It was not until 2004 that the first demonstration of graphene was achieved with a rather unconventional method. The method involved separating layers from bulk graphite by physically peeling them away with adhesive tape and transferring onto a silicon dioxide (SiO<sub>2</sub>) substrate[32,35]. This has since been referred to as the "scotch tape method", or more formally as micro-mechanical cleavage. The great advantage of this particular technique as compared to previous similar attempt is the ability to distinguish the thickness of a resulting film based on the color it forms when deposited on SiO<sub>2</sub>. Utilizing interference effects, the color of the graphene film can be carefully matched to the thickness, down to single layer, by using an optical microscope. Thus, films could be rapidly examined without the need of vacuum or electron microscopy and areas of interest (i.e. few layer graphene) could be identified for further testing. With significant fine-tuning and careful implementation, the "scotch tape" method can provide single layer films tens of micrometers in size. While sufficient for materials research and preliminary investigations, this method is not usable for real scale manufacturing. Other deposition methods will be discussed later in this chapter.

Figure 2.4. Graphene Lattice.

## 2.3.2 The Magic of Graphene

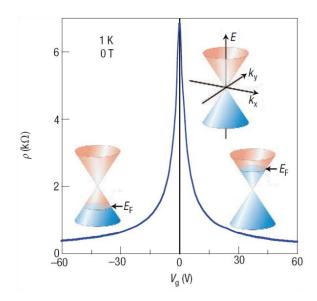

Graphene's unique structure results in a number of fascinating properties otherwise largely unattainable in bulk materials. Single- and double-layer graphene is a zero-bandgap semiconductor, although a gap can be induced in certain instances, which will be discussed later. Beyond three layers, the electronic structure of graphene become significantly more complicated and structures with 10 or more layers effectively act as thin films of graphite[36]. In a graphene sheet, carbon atoms are sp<sup>2</sup> hybridized allowing delocalization of electrons within the  $\pi$  orbitals which act as free carriers. In fact, charge carriers in graphene acts as massless Dirac fermions and have been shown to reach mobilities of up to 15,000 cm<sup>2</sup>/Vs at room temperature[37,38]. Additionally, chirality is observed between electrons and holes and the charge carriers can be tuned from one type to another continuously in the presence of ambipolar electric field. Figure 2.5 demonstrates this principle, where resistivity of a single layer graphene is modulated continuously in both positive and negative bias direction. This will result in (close to) ambipolar transistor characteristics in most cases. The insets show the energy spectra, which are conical at energies below ±1 eV, and the shift in the Fermi level associated with positive and negative V<sub>G</sub>. The linear nature of the low-energy band structure gives rise to massless carriers[39].

Figure 2.5. Ambipolar electric field effect in single-layer graphene. Insets show conical E-k spectra indicating Fermi energy level at positive, neutral, and negative V<sub>G</sub>[34].

#### 2.3.3 Opening the Bandgap

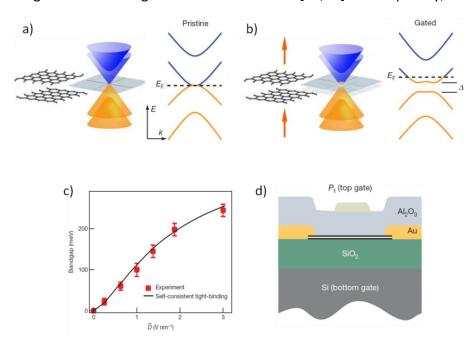

With all its great properties, graphene would likely see little integration into transistors as a gap-less semiconductor. There are, however, ways of inducing (or sometimes forcing) a bandgap in a graphene layer. Perhaps the most elegant and clean way is to utilize the inherent properties of bilayer graphene. It acts similarly to its single layer counterpart, maintaining electron-hole chirality (although the carriers are no longer massless with  $m \approx 0.05m_0$ ) and high mobility. However, it has been shown that upon application of transverse electric field a bandgap can be introduced[40,41]. In its pristine form, bilayer graphene is inversion symmetric AB-stacked and is a zero-gap semiconductor. However, breaking the inversion symmetry introduces a non-zero bandgap, which is precisely the effect of applied electric field. Figure 2.6 shows a schematic representation of the electronic bands separating. Resulting bandgap is a function of applied field and can be up to 300 meV in magnitude. It should be noted, however, that producing this effect requires a double-gate transistor design (Figure 2.6(d)). While quite interesting and useful for material properties investigations, a double-gate design may be prohibitively complicated for full scale, industrial implementation.

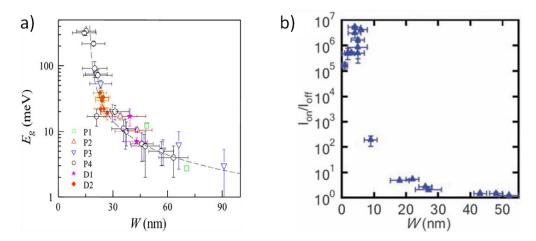

Altering the geometry of a single-layer graphene sheet can also create a bandgap. Most notably, sheets patterned into ribbons with widths of several nanometers have been demonstrated to have a gap. In this case the lattice can no longer be approximated as semi-infinite and a large number of edge states are introduced [42,43]. Subsequently, devices made

Figure 2.6. a) Electronic structure of pristine graphene, showing zero bandgap. b) Field induced band gap opening. c) Band gap as a function of transverse electric field. d) Cross section schematic of a dual gated graphene transistor[40].

Figure 2.7. a) Band gap as a function of ribbon width. b) ION/IOFF ratio as a function of ribbon width.

out of such ribbons appear more like standard transistors and demonstrate significant on/off ratios. Figure 2.7 shows the bandgap of various nanoribbons and the on/off ratio of resulting devices. It can be seen that a gap of several hundred meV can exist in the narrower samples. By comparing parts (a) and (b) of Figure 2.7, it can be seen that the on/off ratio correlates strongly to the bandgap, as expected.

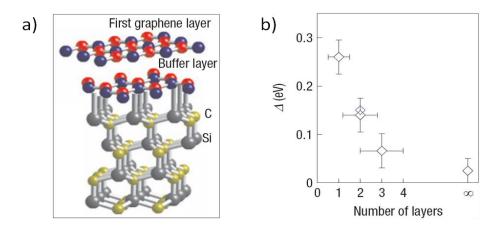

One can alter not only the physical geometry of graphene but also its electronic geometry. This can be accomplished by introducing graphene to a substrate with a precisely matched lattice which acts as an inversely symmetric layer. It has been shown that growing graphene on a silicon carbide (SiC) wafer can induce a bandgap of up to 260 meV[44]. Figure 2.8(a) shows a schematic representation of a graphene layer on a SiC substrate, and demonstrates the difference of potentials on corresponding sublattices. The effect on the induced gap deteriorates quickly with increasing thickness of the film, and disappears entirely after four layers (Figure 2.8(b)). As expected, thicker films act more like bulk graphite and the intricacies of substrate interactions are lost.

Figure 2.8. a) Schematic diagram of graphene of SiC showing interface induced different potentials on the sublattices. b) Band gap as a function of number of layers [44].

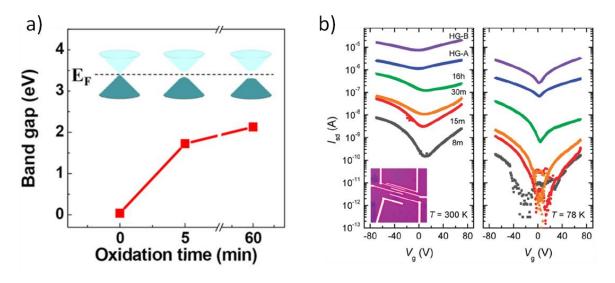

Perhaps the least elegant, and yet most simplistic, way of inducing an effective gap in the energy spectrum of graphene is via chemical alteration, in particular oxidation. Graphene oxide (GO) is an insulator with a bandgap of approximately 2.1 eV[45]. The oxidation causes sp³ hybridization of the carbon atoms, thereby reducing the number of free carriers present in an sp² hybridized lattice. GO possesses many interesting properties which could be utilized in fabrication of solution-processed electronics. These will be introduced in detail later in this chapter. However, for the purposes of current discussion, it is important to note that the bandgap of GO is strongly dependant on the extent of oxidation where a strongly oxidized sample shows a large gap, whereas a pristine graphene sample is a zero-gap material. The gap can be continuously altered based on the level of oxidation[46,47]. When incorporated into a FET, as expected, the resulting devices behave like insulators for strongly oxidized samples and conductors for the pristine ones. Figure 2.9(a) shows the evolution of extracted bandgap based on extent of oxidation. Figure 2.9(b) shows I-V characteristics of TFTs made from graphene oxide reduced back to graphene form to varying extent. It can be seen that the most oxidized samples exhibit the highest on/off ratio at the expense of drive current.

Figure 2.9. a) Band gap as a function of graphene oxidation time. b) I<sub>D</sub>-V<sub>G</sub> characteristics for reduced graphene oxide samples at various times. HG-A/B are samples reduced in aqueous solution of hydrazine. 8m, 15m, 30m, and 16h are samples reduced with hydrazine vapor for amount of time indicated by the label.

# 2.4 Graphene Oxide

Graphene can be oxidized to form GO, which possesses a number of interesting properties that make it pertinent to solution-processed electronics. During oxidation some bonds of a graphene sheet break to form bonds with oxide and other carbon functional groups[48,49]. The various functional groups make an individual sheet very hydrophilic and easily soluble in water (and other polar solvents). Once solubilized, material can be deposited via several techniques such as spin-coating, ink-jet printing, spraying, and others.

## 2.4.1 Fabrication

Separating graphene into individual sheets is commonly achieved by chemical exfoliation, where strong oxidizing agents are used to yield GO. Currently, the exact structure of GO is undetermined, although it is clear that in the oxidized form some of the aromatic rings of the graphene lattice are broken up and decorated with alcohols, epoxides, carboxylic, and other functional groups. This "functionalization" of individual sheets serves two important purposes: one, it breaks up the Van der Waals forces holding the sheets together; and two, it makes the sheets strongly hydrophilic and soluble in water and other polar solvents.

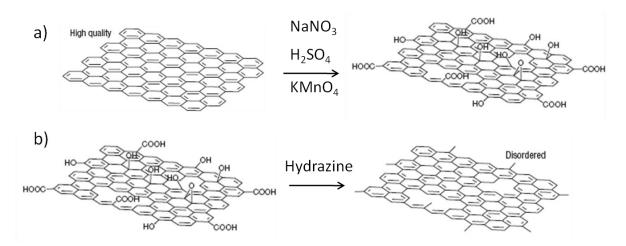

The first demonstration of GO synthesis was performed in 1859[50] by treating graphitic powder with nitric acid and potassium chlorate. However, the most popular route of producing GO is commonly referred to as "Hummers' method", introduced in 1958 by Hummers and Offeman[51]. The process involves mixing graphite powder with sodium nitrate (NaNO $_3$ ) and subsequent addition of sulfuric acid (H $_2$ SO $_4$ ). The solution is then cooled to 0°C to control reaction rate and vigorously stirred. Potassium permanganate (KMnO $_4$ ) is then added to complete the mixture. The solution temperature is allowed to increase to  $\approx$  35C and the reaction proceeds for a desired amount of time. At the end of reaction time, the final GO product is extracted by washing. Figure 2.10(a) shows a schematic of graphene in its pristine and oxidized forms.

Figure 2.10. a) Graphene lattice before and after oxidation via Hummers method. b)

Representation of the graphene oxide lattice and its reduced form.

#### 2.4.2 Reduction

While graphene oxide could be an interesting material in itself, in the context of printed electronics, its most intriguing property is the ability to be converted back to graphene form via chemical reduction. Once converted, reduced graphene oxide (rGO) regains many of the electronic properties that make graphene so attractive, such as low resistivity  $(1x10^{-4} \Omega\text{-cm})[52]$  and high mobility (365 cm<sup>2</sup>/V-s for holes)[53].

Several pathways have been demonstrated for reduction of GO including thermal annealing both in inert atmospheres (vacuum, nitrogen, argon)[48,49,54] and chemically active ambients (hydrogen, forming gas, hydrazine)[47,55,56] and chemical reduction[57]. One of the

most widely used methods, and most promising for ink-jet printing, is reduction in hydrazine ( $N_2H_4$ ) vapor. Hydrazine is a very strong reducing agent and requires very little thermal assistance (as low as 80°C) to convert GO, which is important for plastic substrate compatibility.

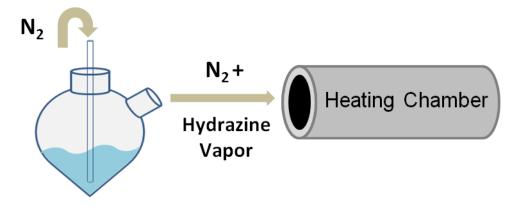

Hydrazine annealing can be performed in various ways. The simplest one is to place a GO sample into a heated enclosure (such as a covered beaker) which also separately contains liquid hydrazine. The atmosphere in the beaker will become saturated with hydrazine vapor which will react with GO and reduce it. Although simple and often utilized, this method is not very precise in temperature control and vapor exposure extent. A more reliable method of introducing hydrazine vapor is through a bubbler system, where an inert gas ( $N_2$  or Ar) is bubbled through a volume of hydrazine solution. The resulting gas mixture with chemical vapor is sourced into a heated chamber containing the samples to be reduced. This method is advantageous as it provides better temperature control through a furnace-like chamber and more precise chemical exposure through gas flow control. Figure 2.11 demonstrates a schematic of a bubbler.

Figure 2.11. Hydrazine bubbler. N2 is bubbled through hydrazine solution and directed into a heated chamber.

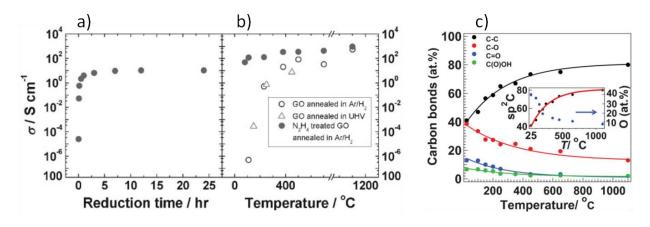

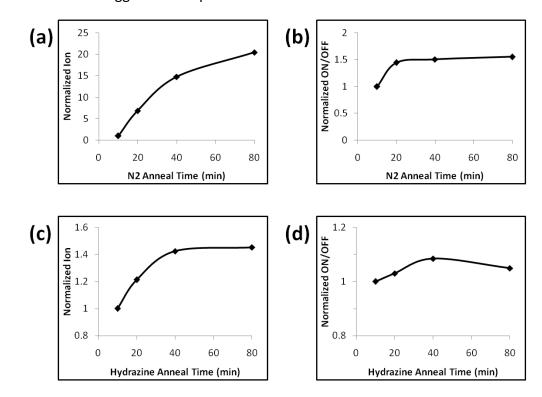

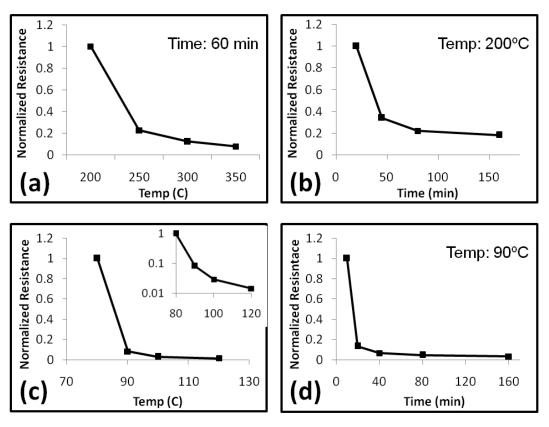

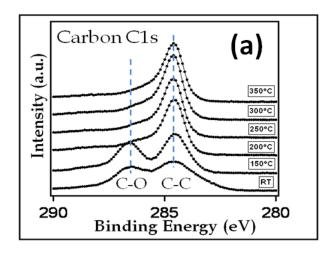

It should be noted that the reduction process is not a perfect reversal of the oxidation process. Although a large portion of the oxidizing groups is removed, some are inevitably left over and the resulting rGO lattice is imperfect. Figure 2.10(b) shows a schematic of a sheet of rGO. Clearly, the imperfections in the lattice will have detrimental effects on electrical characteristics, such as mobility. Furthermore, remaining chemical impurities will result in sp³ hybridization of carbon atoms which reduces the number of delocalized carriers and disrupts their transport through an sp² network, reducing conductivity and mobility. Figure 2.12 shows representative electrical behavior as a function of anneal conditions. Part (a) demonstrates conductivity as a function of reaction time in hydrazine at 80°C; it can be seen that the effects saturate after approximately 2 hours of exposure. Part (c) demonstrates the atomic percentage of different carbon bonds as a function of anneal temperature in UHV (identified by XPS) as well as the percentage of sp² bonds and total oxygen content (inset). It can be seen that the atomic percentage of desired C-C bonds, and associated sp² hybridization, saturates at approximately 80%. This suggests that complete reversal to graphene is not achieved.

Figure 2.12. Conductivity as a function of (a) reduction time and (b) reduction temperature of GO. c) Concentration of various carbon bonds as a function of anneal temperature.

#### 2.4.3 GO Deposition Methods

A number of methods have been demonstrated for depositing solutions of graphene oxide. One of the more direct ways to deposit any material in solution on a flat surface is spin-coating[58]. It has proven invaluable in the development of many solution-processable materials as a quick and effective means for materials prototyping. Generally spin-coating consists of pouring a solution onto a wafer/substrate and spinning the substrate at desired rotation rate (usually on the order of 500 – 5000 RPM). Solution properties, such as viscosity and mass loading, along with the spin speed determine the final thickness of the resulting film. Spin-coating of GO solutions has been demonstrated before for both electronic and nanomechanical devices. Although conceptually simple, is not ideally suited for purely aqueous solutions as the surface tension of the drying water will cause formation of small beads and result in a non-uniform films. To remedy this effect, ethanol, or a similar solvent, could be added to reduce net surface tension and allow for more uniform drying.

One of the earlier methods used for obtaining film of GO with controllable thickness was filtration[59,60]. It has been previously used for deposition of carbon nanotubes[61]. A solution containing a controlled concentration of GO flakes would be passed through a filter which would catch the flakes on the surface of the membrane. The filter/GO assembly is subsequently placed onto a substrate (GO face down) and the membrane is removed via dissolution. By controlling the amount and the concentration of the solution used it is possible to produce films of thicknesses down to single monolayers. Although this method is claimed to produce high-yield films, there is an obvious processing complication involving the transfer and dissolution of the filter membrane.

Techniques such as Langmuir-Blodgett deposition[62], templating[63], and spraying[64] have also been shown to produce GO films with varying degree of success. Some of these and previously mentioned methods promise compatibility with low-cost manufacturing; however, none of those are well suited for true large area integration due to issues with large area coverage uniformity and thickness control. Coverage uniformity is critical for device yield while thickness control is essential for electrical properties of graphene, as discussed earlier.

Furthermore, all of these techniques deposit blanket films thereby necessitating post-deposition patterning to achieve proper designs for most electronic applications. Patterning is usually achieved through conventional lithography or stamping techniques. For lithographic patterning, electron-beam (e-beam) techniques can locate an area of graphene favorable for TFT measurements and expose appropriate areas for electrode deposition. Stamping techniques often utilize polydimethylsiloxane (PDMS) or hybrid structures consisting of silicon, glass, and plastic for transferring graphene films which have been deposited on a temporary dummy substrate, hence introducing an extra step to the fabrication process. While these methods have proven valuable for basic investigations of graphene properties, their low throughput (e-beam) and poor registration control over large area (PDMS) make such techniques poorly suited for low-cost, large-area integration.

# 2.5 Ink-Jet Printed rGO TFTs

Ink-jet printing promises distinct advantages over the previously mentioned solution-processing compatible deposition methods. Firstly, it is ideally suited for low-cost manufacturing due to its all additive, low-waste process. Blanket deposition methods are inherently wasteful as they deposit material everywhere, which subsequently requires removal of some or most of the material to create the desired pattern. In contrast, ink-jet printing is capable of depositing material only where necessary. Furthermore, with simple adjustment of the print program, it is possible to deposit various amounts of material in different locations on the substrate, thereby achieving different film thicknesses. This is useful both for rapid prototyping and, potentially, for manufacturing. None of the blanket deposition techniques offer such flexibility. Additionally, the pattering step itself (usually requiring photolithography) adds additional cost to the fabrication process. Ink-jet printing is also capable of producing uniform micron-sized patterns over large areas and a wide variety of substrates. It can be implemented into roll-to-roll processes for fast throughput manufacturing.

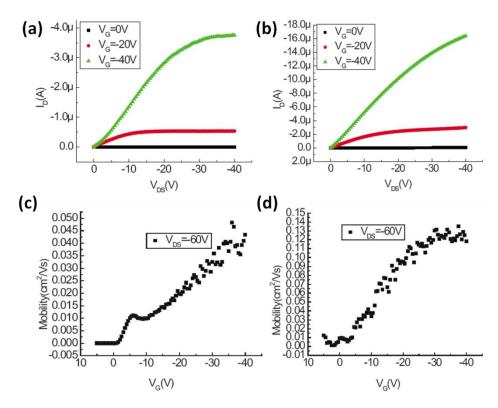

In this section, fabrication and characterization of ink-jet printed rGO TFTs will be presented and their properties will be discussed. For active material prototyping purposes, devices presented here were printed on back-gated  $SiO_2$  substrates. Effects of jetting conditions, substrate temperature, and anneal conditions on device performance will be examined. By controlling printing conditions, uniform films of rGO are achieved. Devices exhibit drive currents up to 1  $\mu$ A, current ON/OFF ratios of up to 10, and field effect mobilities of up to  $0.018 cm^2/V$ -s.

#### 2.5.1 Device Fabrication

#### 2.5.1.1 Print Ink Optimization

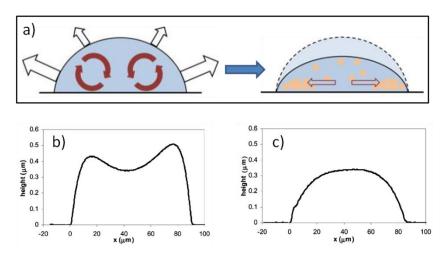

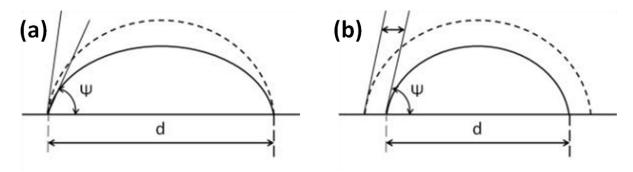

It is often erroneously assumed that "solution" is synonymous with "ink". Unfortunately for the printing community that is rarely the case; a material in solution does not always make an optimal ink compatible with jetting. One of the biggest problems plaguing pattern formation via liquid drop deposition is a "coffee ring" effect, first described by Deegan[65]. He showed that non-uniform drying on the surface of a drop leads to an excess of solute at the edge. Figure 2.13(a) demonstrates this principle. Left side shows the evaporation patterns in a freshly deposited drop. On the edges, evaporation proceeds faster as compared to the center. This

causes flow from the bulk of the drop to the edges. As drying proceeds, more solute is transferred to the edges (right side of Figure 2.13(a)). At the completion of the drying process, most of the material ends up on the periphery of the printed feature. Figure 2.13(b) shows a representative cross section of printed drop exhibiting strong coffee ring effect. Clearly, substrate temperature will have an effect on drying rate and dynamics, and increasing temperature is expected to increase convective flow. In fact, it has been shown that increasing temperature can result in a more pronounced coffee ring[66].

Figure 2.13. a) Schematic of an evaporating liquid drop demonstrating non-uniform drying and resulting convective flow. b) A cross section of a dried drop showing strong CF effect, and c) cross section of a drop without CR effect.

To ameliorate the coffee ring problem a dual solvent system can be introduced. It has been shown that by combining two solvents dissimilar in volatility and surface tension more uniform drops can be obtained. Multi-solvent systems can be used to increase a surface tension enhanced flow inside a drying drop [67,68]. This is often referred to as "Marangoni effect"

Figure 2.14. Top view images of aqueous silver nanoparticle solution drops with (a) 0, (b) 16, and (c) 32 wt% EG. d) Corresponding cross section profiles [68].

which states that mass transfer will occur in a liquid from an area with low surface tension to an area with high surface tension. It has been shows that addition of ethylene glycol (EG) to water eliminates the formation of a coffee ring (Figure 2.14). The proposed mechanism is as follows: in a freshly deposited liquid drop evaporation proceeds faster at the edges, which creates an excess of EG at the edges as it evaporates slower due to higher boiling point. This in turn generates a surface tension gradient in the drop due to a difference in surface tension of EG and water ( $\gamma = 48$  mN/m and 72 mN/m, respectively). Thus, an inward Marangoni flow is induced carrying solute from the edge towards the center of the drop (i.e. low to high surface tension). In the case of water/EG system, this induced Marangoni flow is sufficiently large to offset the convective flow generally responsible for the coffee ring effect.

## 2.5.1.2 Experimental Setup and Sample Preparation

GO flake solutions were prepared via the Hummers method which was described earlier. After oxidation, the GO slurry was ultrasonicated, centrifuged for cleaning, and suspended in water. The loading of the final solution was approximately 0.3 mg/ml of GO flakes in water. The ink was filtered through a 5  $\mu$ m Nylon filter before printing to remove agglomerated particles and prevent clogging of the print head.

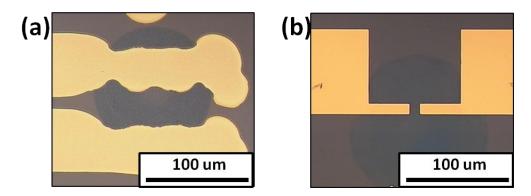

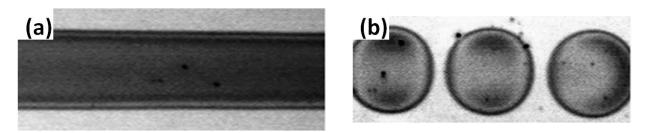

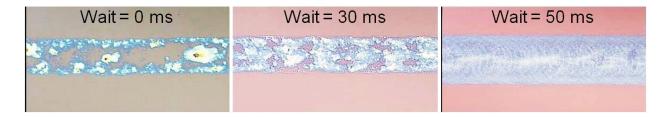

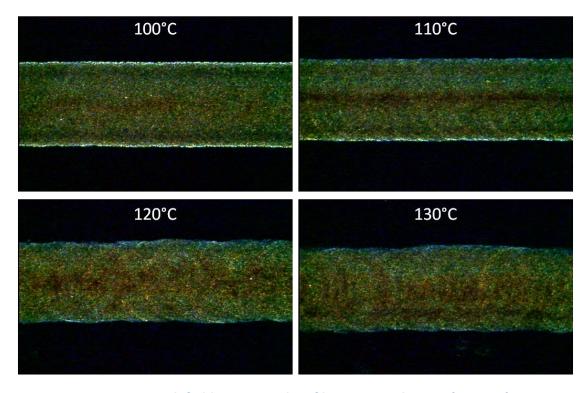

Bottom-gate structures were used for printing and testing. A heavily doped n++ substrate served as the conductive gate and a 100 nm of thermally grown  $SiO_2$  layer served as the gate insulator (as illustrated in Figure 2.1). Both top and bottom contacts structures were used. Bottom contacts consisted of a chrome/gold (Cr/Au) stack of 2.5/50 nm deposited by thermal evaporation. These were defined by standard lithographic step followed by liftoff. Top contacts consisted of printed silver inks annealed at 150 °C in air. GO inks were deposited at various substrate temperatures and drop conditions. After deposition, GO films were subjected to a two step anneal process. An initial "pre-anneal" step was performed in a  $N_2$  ambient at temperatures of 150°C – 250°C to drive off excess solvent and EG. The second step was performed in a hydrazine bubbler chamber (as described earlier) to reduce GO at temperatures of 80°C – 150°C. Figure 2.15 shows optical micrographs of devices with printed and evaporated S/D contacts. The slight variations in the rGO film morphology and the dissimilarity with the  $SiO_2$  substrate result in a variation of the surface energy experienced by the printed silver lines. Consequently, the lines exhibit line edge non-uniformity.

Figure 2.15. Optical micrographs of rGO devices with (a) printed Ag top contacts and (b) evaporated Au bottom contacts.

GO inks were printed with a custom-built ink-jet printer. The printer consists of a substrate holder with lateral and rotational movement (accuracy of approximately  $1\mu m$ ). Ink delivery is performed via a piezoelectric actuated print head manufactured by Microfab Inc. with nominal nozzle size of 60  $\mu m$  and drop volume of 100 pL. The ink is stored in a pressure controlled reservoir and fed to the head via a Teflon tube. Commercially available CCI-300 silver particle ink from Cabot Corporation was used for silver top S/D contacts structures. Metallic ink was printed with a Dimatix DMP 2800 printer. Cr/Au contacts were deposited in a standard thermal evaporator at base pressure of approximately 2e-6 torr.

Electrical measurements were performed with an Agilent 4155/6 parameter analyzer. Atomic force microscopy (AFM) measurements were taken with a Veeco Dimension 3100.

#### 2.5.2 Results and Discussion

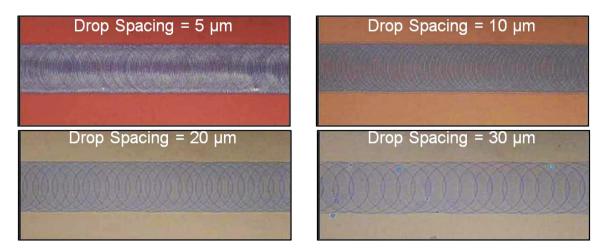

#### 2.5.2.1 Print Conditions

As described earlier, ink composition and substrate temperature play a critical role in determining the final print feature morphology and it is important to optimize both to achieve desired film quality. Three types of inks were evaluated: pure water, water + ethanol, water + EG. As expected, pure water resulted in a pronounced build up of material at the edges, likely due to induced convective flows. Addition of ethanol also resulted in undesirable drop profiles, most likely due to an additional outward Marangoni flow. Ethanol has lower boiling point and surface tension than water ( $T_b = 78$ °C and  $\gamma = 22.4$  mN/m). As a result, the edge of a drying drop will evaporate ethanol faster and result in an excess of water. The water rich region will have higher surface tension and induce an outward Marangoni flow, thus enhancing the undesired transfer of solute to the edge.

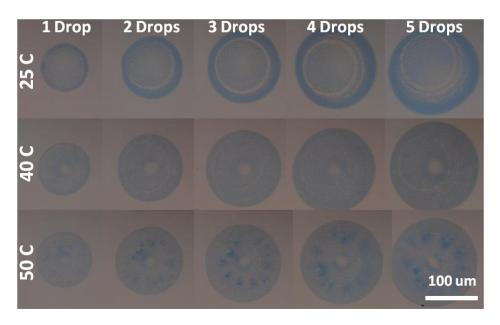

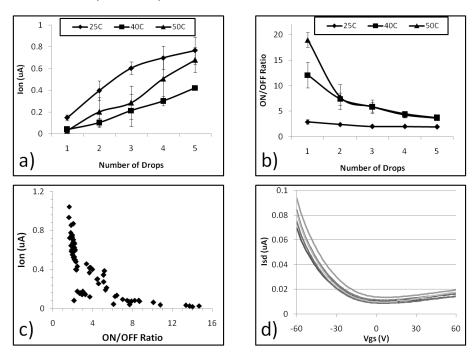

Addition of EG and proper control of temperature was found to give the best results with GO flake inks. Combination of 4 – 5% EG with water produces the desired inward Marangoni flow to counteract the outward convective flow. Figure 2.16 shows optical micrographs of dried drops printed at various temperatures and drop counts. Multi-drop features were printed immediately, i.e. no drying time was implemented in between individual drop depositions. It can be seen that substrate temperature of 40°C produces the most uniform films. At 25°C, coffee rings are clearly present and become more pronounced with increasing drop count. At 50°C, material agglomeration occurs in the middle likely due to the fact that inward Marangoni flow becomes more pronounced at higher temperature.

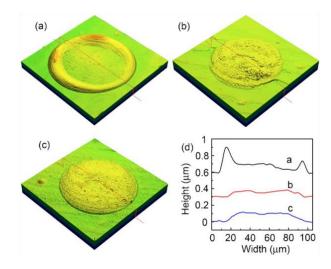

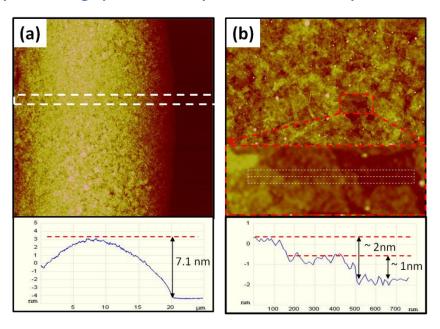

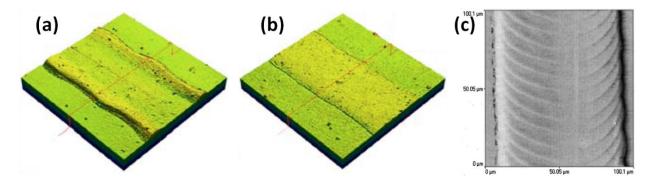

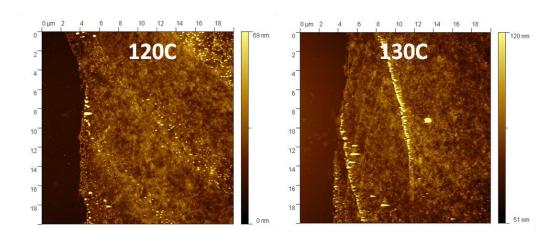

The thickness of the graphene film or, more precisely, the number of individual layers plays a dramatic effect on its electronic properties. As shown in Figure 2.8(b), the bandgap approaches zero as the number of layers is increased past three. To achieve semiconducting behavior, it is important to maintain close-to-single-layer films. Going past three layers will result in a more "metallic" behavior of the film. Consequently, TFTs produced from semiconducting films are likely to show better device characteristics than the metallic films. Figure 2.17 shows AFM images of the features obtained at various print conditions. Part (a) shows an edge of a multi-drop feature printed at substrate temperature of 25°C. It can be seen that the height of the coffee ring is approximately 7.1 nm which corresponds to 7 layers of rGO

Figure 2.16. Optical micrographs of GO inks printed at various temperatures and drop counts.

Figure 2.17. (a) AFM micrograph of the edge of a printed feature resulting in a "metallic" device, showing a relatively thick, multi-layer graphene. (b) AFM micrograph of a printed feature resulting in a "semiconducting" device, showing near single-layer film structure.

(it has been shown that a single layer of rGO is approximately 1 nm, depending on the fabrication/reduction process[55,69]). This type of morphology is expected to result in a more metallic behavior. Figure 2.17(b) shows and AFM image of a feature printed at 40°C. It can be seen that the film consists of 1- to 3-layer rGO, which should result in a more semiconducting behavior and allow much better gate control in a TFT structure. Cross-sectional AFM analysis shows that thickness of an individual sheet is approximately 1 nm.

#### 2.5.2.2 Device Characteristics

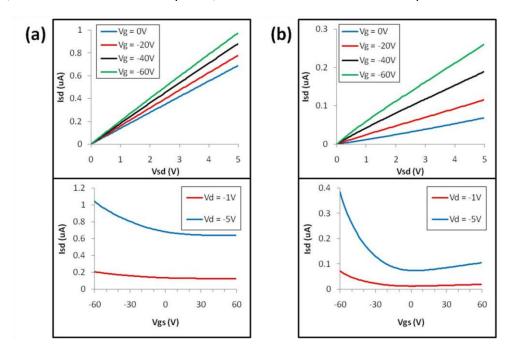

TFT device characteristics corresponding to various print conditions were examined. Figure 2.18 shows representative I-V curves for a metallic (5 drops, 25°C) and a semiconducting (3 drops, 40°C) device. After GO deposition, devices were annealed at 200°C in  $N_2$  and 90°C in hydrazine for 1 hour each. Subsequently, silver S/D contacts were printed and annealed in air at 150°C for 1 hour. It can be seen that a "thick" device (Figure 2.18(a)), with a pronounced coffee ring effect, exhibits more metallic behavior. It has higher drive current of 0.98  $\mu$ A and lower ON/OFF ratio of 1.63 (ON/OFF ratio is defined as maximum to minimum  $I_{DS}$  measured at  $V_G$  = 5V and 0V, respectively). In contrast, a more semiconducting device (Figure 2.18(b)) exhibits a higher ON/OFF ratio of 5.2 at the expense, of lower drive current of 0.26  $\mu$ A.

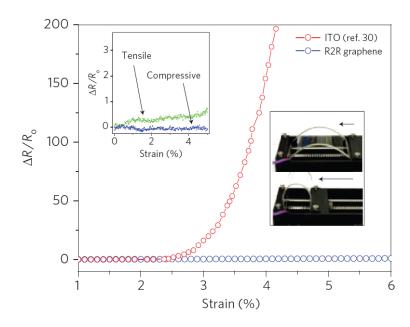

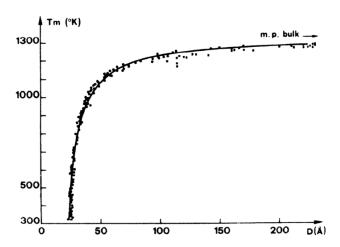

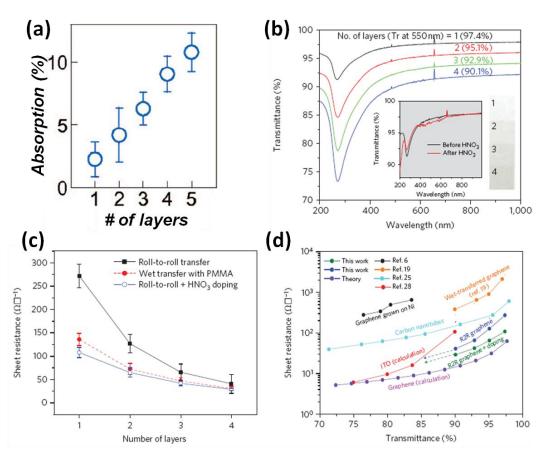

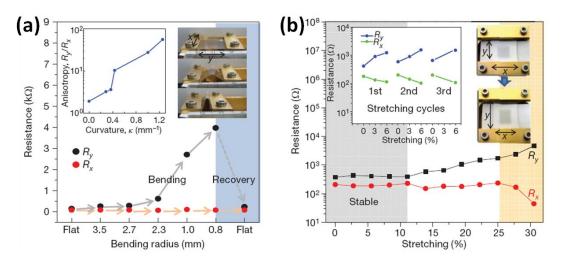

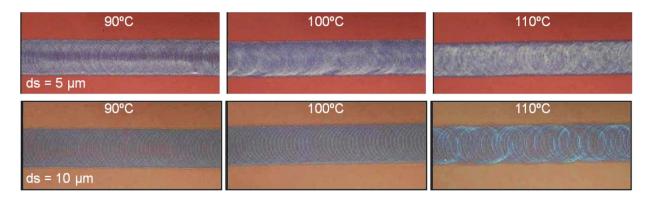

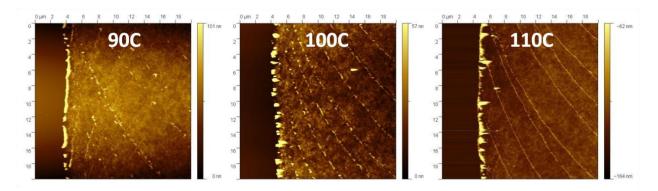

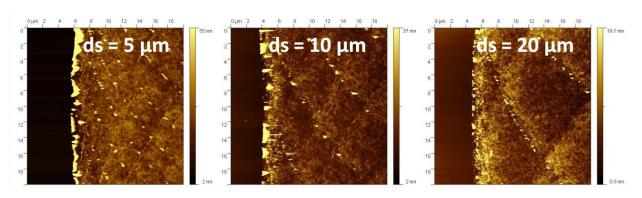

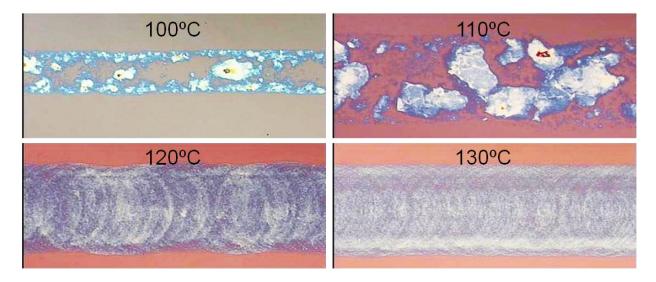

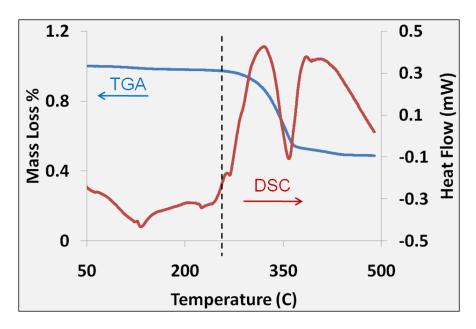

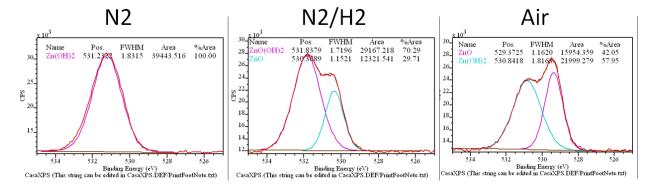

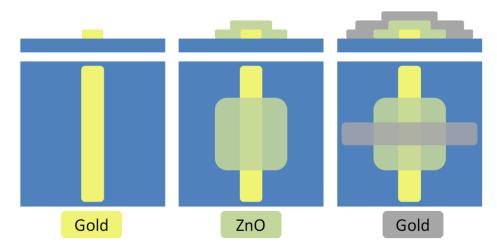

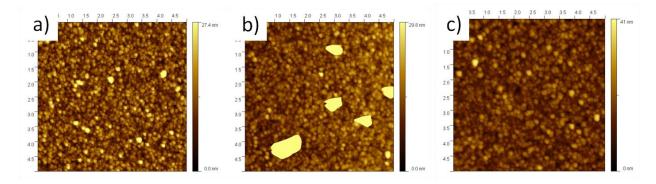

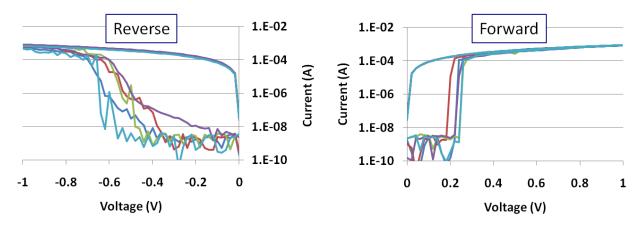

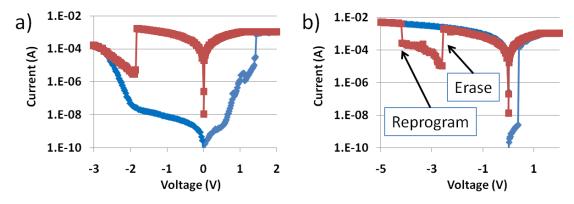

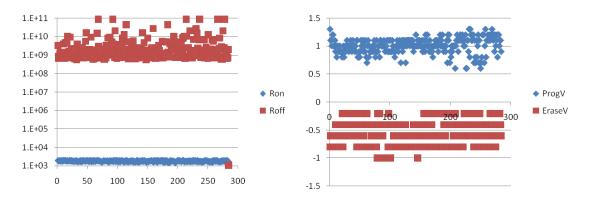

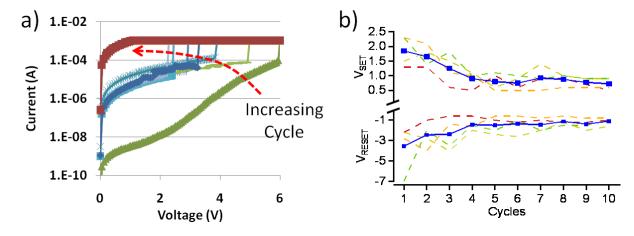

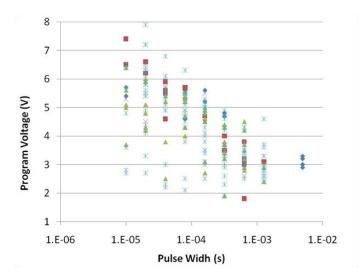

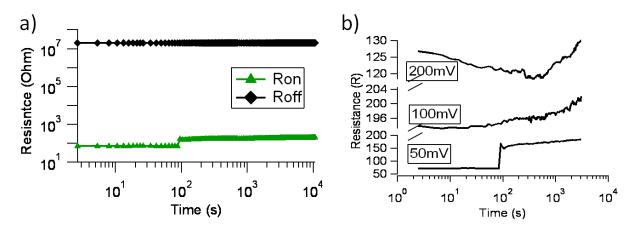

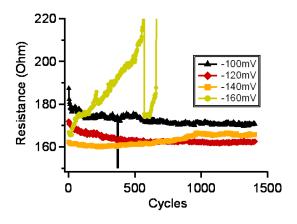

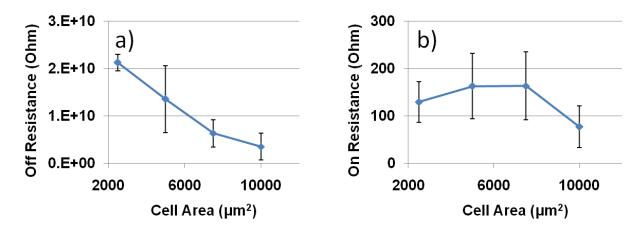

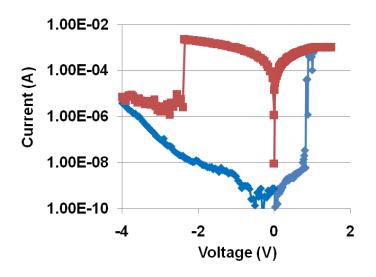

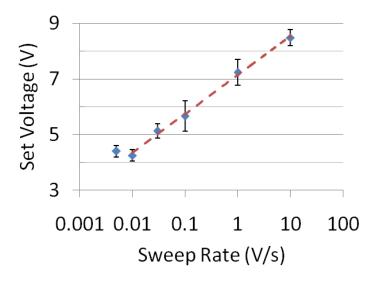

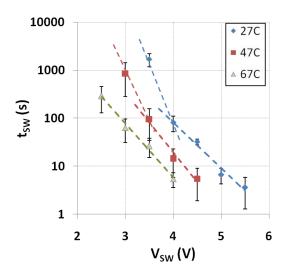

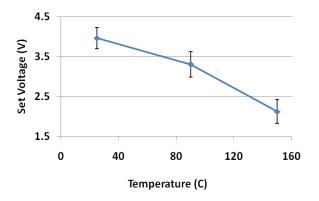

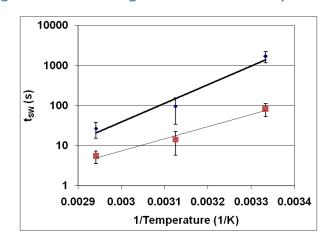

Figure 2.18. I-V characteristics for (a) metallic and (b) semiconducting device.