# UC Irvine UC Irvine Previously Published Works

# Title

Single-mask fabrication of high-G piezoresistive accelerometers with extended temperature range

**Permalink** https://escholarship.org/uc/item/9d2798st

**Journal** Journal of Micromechanics and Microengineering, 17(4)

**ISSN** 0960-1317

**Authors** Eklund, E. Jesper Shkel, Andrei M.

Publication Date

2007-04-01

DOI

10.1088/0960-1317/17/4/009

Peer reviewed

# Single-mask fabrication of high-G piezoresistive accelerometers with extended temperature range

E Jesper Eklund and Andrei M Shkel

Microsystems Laboratory, University of California, Irvine, CA 92697, USA E-mail: eeklund@uci.edu and ashkel@uci.edu

Abstract. This paper presents a fabrication process in which all components of an in-plane piezoresistive accelerometer are fabricated simultaneously using a single mask. By dry-etching a silicon-on-insulator (SOI) wafer that has a specific resistivity, piezoresistors are defined and isolated from each other and from the bulk silicon without the pn-junctions normally required in piezoresistive sensors. In addition to simplifying the fabrication, the temperature range is also extended when compared to conventional piezoresistive accelerometers, due to the absence of pn-junctions. Singleaxis accelerometers, designed for an acceleration range of 1 G to 500 G with a sensitivity of 1 mV/G, were fabricated and tested, and linear output characteristics were demonstrated. The temperature performance was also characterized. The temperature coefficient of sensitivity (TCS) was  $0.3\%/^{\circ}$ C and the temperature coefficient of offset (TCO) was 20 mG/^C.

PACS numbers: 07.07.Df, 42.81.Pa, 85.85+j

Submitted to: J. Micromech. Microeng.

# 1. Introduction

Micromachined piezoresistive accelerometers were first demonstrated in the late 1970s by Roylance and Angell [1]. Their design was based on an anisotropically etched ntype (100) silicon proof mass that deflected out-of-plane. p-type piezoresistors were diffused into a beam that connected the proof mass to the surrounding bulk silicon, and the strain induced by applied acceleration led to a change in resistance which could be detected and related to acceleration. Several design improvements have since been proposed, including mechanical overrange protection [2], in-plane deflection of the proof mass [3], integrated detection circuitry [4, 5], formation of piezoresistors on etched sidewalls [6], temperature compensation [7] and different mass and suspension geometries (for example [3, 6, 8, 9, 10, 11]). However, with the exception of [3], in which (110) silicon is anisotropically etched to achieve vertical sidewalls and the proof mass deflects in-plane, the conceptual design of most commercial piezoresistive accelerometers remains largely unchanged and can be traced back to the original design by Roylance and Angell [1].

In conventional piezoresistive accelerometers the piezoresistors and conductors are defined by doping selected areas of a silicon wafer to achieve reversely biased pnjunctions. At least two doping steps are employed in order to obtain both heavily doped conductors and ohmic contacts, as well as lightly doped piezoresistors. Once the piezoresistors and conductors have been defined, additional fabrication steps are required to etch the suspension system as well as the free-standing proof mass. Thus, at least four photomasks are required during conventional fabrication, although a larger number of masks is often used in commercial processes.

Since reversely biased pn-junctions are used to isolate the sensing elements from each other and from the bulk silicon in most piezoresistive accelerometers, leakage currents limit the operation of these sensors to about 150°C [12]. Furthermore, the piezoresistive coefficients are highly dependent on temperature [13], leading to a change in sensitivity when piezoresistive sensors are operated at fluctuating temperatures. While the temperature coefficient of sensitivity (TCS) can be compensated for [14], the limited temperature range of piezoresistive silicon accelerometers can only be addressed by eliminating the pn-junctions. Silicon-on-insulator (SOI) wafers can be utilized for this purpose. By defining the piezoresistors in the device layer and using the buried oxide to isolate them from the proof mass and support structure in the handle layer, operational temperatures of 400°C have been demonstrated [9].

Another drawback of many piezoresistive accelerometers is the out-of-plane deflection of the proof mass, necessitating cumbersome overrange stops above and below the structure to assure survival when the sensor is subjected to excessive accelerations. This is often accomplished by bonding of glass or silicon wafers to both sides of the device wafer. However, while most commercial piezoresistive accelerometers still deflect out-of-plane, several innovative designs of in-plane accelerometers have been demonstrated [3, 6, 10].

This paper describes a fabrication process for piezoresistive accelerometers that combines the improved temperature performance of SOI sensors with an in-plane design approach. Furthermore, the accelerometers are fabricated with a single photomask, greatly reducing the number of required fabrication steps compared to conventional piezoresistive accelerometers [15].

The fabrication process is based on deep reactive ion etching (DRIE) of the SOI device layer in order to simultaneously define piezoresistors, reference resistors, a proof mass, conductors, overrange stops, and a suspension beam. By choosing wafers with a particulary resistivity, piezoresistors can be achieved without pn-junctions and the doping steps can be eliminated from the fabrication process. Free-standing structures are obtained by selective removal of the buried oxide layer.

The presented accelerometers are designed to measure high G-loads. Some of the possible applications include airbag deployment systems, automotive crash testing, and munitions testing.

# 2. Accelerometer design

#### 2.1. Design overview

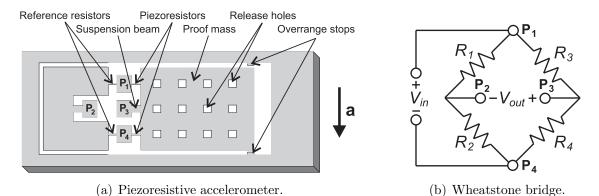

The conceptual design of the single-mask piezoresistive accelerometer is illustrated in figure 1(a). All of the features are defined with one photomask and etched simultaneously in the device layer of a single-crystal SOI wafer with a selected low resistivity, as will be described in section 3. The oxide layer underneath the proof mass is removed through the release holes using hydrofluoric (HF) acid, leading to a mass that is free to deflect in-plane. Areas without release holes, including bonding pads  $P_1$ ,  $P_2$ ,  $P_3$ , and  $P_4$ , define anchor points. A suspension beam attaches the proof mass to pad  $P_3$ and two narrow piezoresistors are defined between the proof mass and pads  $P_1$  and  $P_4$ . During applied acceleration, bending will occur around the centrally located suspension beam, causing one of the piezoresistors to stretch and the other one to compress. This leads to an increased resistance in the stretched piezoresistor and decreased resistance in the compressed piezoresistor. Overrange stops are etched on both sides of the proof mass to prevent breakage when the accelerometer is subjected to excessive accelerations.

Figure 1. Conceptual illustration of a single-mask piezoresistive accelerometer, designed to emulate a Wheatstone bridge.

The piezoresistive accelerometer is designed to emulate a Wheatstone bridge (compare to figure 1(b)). A half-bridge configuration is chosen with the piezoresistors  $(R_3 \text{ and } R_4)$  on the right-hand side of bonding pads  $P_1$  and  $P_4$  and the reference resistors  $(R_1 \text{ and } R_2)$  on the left-hand side.

In order to amplify the output voltage, a signal conditioning circuit can potentially be integrated with the accelerometer on the SOI wafer. Alternatively, a two-chip solution can be used, where the signal conditioning circuit is located on a separate chip and wirebonded to the pads of the accelerometer bridge circuit. Since the only difference between the piezoresistors and reference resistors in figure 1(a) is that the piezoresistors are free to deform when the proof mass deflects, while the reference resistors are anchored, the resistance will change equally with temperature on both sides of the bridge and no significant change in the output voltage due to temperature is expected. There will however be a slight change in sensitivity due to the temperature dependence of the piezoresistive coefficients, discussed in the next section.

Although the suspension beam is preferably much wider than the piezoresistors and reference resistors, it still has a small resistance and a slight voltage drop is therefore expected. In order to maintain a symmetrical and balanced Wheatstone bridge, a similar structure is therefore included on the left-hand side. This structure is anchored on both sides between bonding pad  $P_2$  and a wide conductor. Since the cross-sectional area of this wide conductor and the proof mass is much greater than the width of the piezoresistors and reference resistors, the voltage drop over the conductor and proof mass can be neglected.

The accelerometer is fabricated in a thick (preferably 50  $\mu$ m - 100  $\mu$ m) device layer of an SOI wafer, and the width of the suspension beam is smaller than the thickness. This gives a structure that is stiff in the out-of-plane direction and compliant in the in-plane direction. However, even if the proof mass would deflect out-of-plane during excitation, the change in resistance would be equal for both piezoresistors and the voltage output would be unaffected, due to the half-bridge sensor configuration.

# 2.2. Principle of operation

The piezoresistive effect causes a change in resistivity,  $\rho$ , when a conductive material is subjected to stress. For the piezoresistors described in the previous section, the resistance is given by  $R = \rho L_0 / A$ , where  $L_0$  is the length and A the cross-sectional area. Assuming that the dimensional changes can be neglected and that the stress is applied in the longitudinal direction, the change in resistance,  $\Delta R$ , is given by

$$\frac{\Delta R}{R_0} = \pi_l \sigma_l,\tag{1}$$

where  $R_0$  is the initial resistance,  $\pi_l$  is the longitudinal piezoresistive coefficient and  $\sigma_l$  is the longitudinal stress [13]. The piezoresistive coefficients are dependent on the dopant concentration, crystal orientation, and temperature. At room temperature, the measured piezoresistive coefficients for p-type single-crystal silicon with a resistivity of 7.8  $\Omega$ -cm are  $\pi_{11} = 6.6 \times 10^{-11} \text{ Pa}^{-1}$ ,  $\pi_{12} = -1.1 \times 10^{-11} \text{ Pa}^{-1}$ , and  $\pi_{44} = 138.1 \times 10^{-11} \text{ Pa}^{-1}$  [16]. If the piezoresistors are aligned along the [110] crystal direction of (100) silicon, the piezoresistive coefficient is

$$\pi_{l,[110]} = \frac{1}{2} \left( \pi_{11} + \pi_{12} + \pi_{44} \right). \tag{2}$$

Following [17], the piezoresistive coefficient can be written as a function of dopant concentration, N, and temperature, T, as  $\pi_l(N,T) = P(N,T)\pi_l(300K)$ , where P(N,T) is the piezoresistive factor and  $\pi_l(300K)$  is the piezoresistive coefficient at room

$$\pi_l(T) = P(T) \pi_l(300K).$$

(3)

The piezoresistive coefficient along the [110] direction in single-crystal silicon is  $\pi_{l,[110]}(300K) = 71.8 \times 10^{-11} \text{ Pa}^{-1}$ , calculated from equation (2) using the above values of  $\pi_{11}$ ,  $\pi_{12}$ , and  $\pi_{44}$ , and P(T) is a nonlinear function of temperature with a value of 1.0 at 300 K [17]. Equation (3) is valid as long as the resistivity of the silicon is greater than 0.05  $\Omega$ -cm [18]. For lower resistivities, the piezoresistive coefficient, and in turn the sensitivity of the sensor, is greatly reduced. SOI wafers with a device layer resistivity higher than 0.05  $\Omega$ -cm are therefore chosen for the presented fabrication process.

Output voltage drift in piezoresistive sensors during fluctuating temperatures is primarily due to different temperature dependence of the four resistors in the Wheatstone bridge. The accelerometer in figure 1(a) is designed with identical resistors on both sides of the Wheatstone bridge, fabricated simultaneously using only one photomask. Therefore, no significant temperature dependence of the output voltage is expected. In reality, however, a slight voltage shift will likely occur due to fabrication imperfections and thermal stress [19]. It should also be noted from equations (1) and (3) that the sensitivity of the sensor has a nonlinear temperature dependence that needs to be compensated for. Several methods have been demonstrated for this purpose (for example [14, 20]).

#### 2.3. Design parameters

By expressing the piezoresistive coefficient as  $\pi_l = G/E_l$ , where G is the gage factor and  $E_l$  is Young's modulus in the longitudinal direction of the piezoresistors, and writing the strain as  $\Delta L/L_0 = \sigma_l/E_l$ , equation (1) can be rewritten as

$$\frac{\Delta R}{R_0} = G \frac{\Delta L}{L_0},\tag{4}$$

where  $L_0$  is the initial length of a piezoresistor and  $\Delta L$  is the change in length due to applied acceleration. Young's modulus in the [110] crystal direction of single-crystal silicon is  $E_{l,[110]} = 169$  GPa [21], and  $\pi_{l,[110]} (300K) = 71.8 \times 10^{-11}$  Pa<sup>-1</sup> was calculated in the previous section, yielding a gage factor of G = 121.

As was discussed in section 2.1, the accelerometer is configured as a Wheatstone half-bridge. Assuming all four resistors in figure 1 have equal resistance when no acceleration is applied  $(R_1 = R_2 = R_3 = R_4 = R_0)$ , the relationship between input voltage and detected output voltage is

$$\frac{V_{out}}{V_{in}} = \frac{\Delta R}{2R_0}.$$

(5)

The stiffness of the suspension system can be estimated as

$$k = \frac{E_l h}{L_0 d_{cg}^2} \left( 2w_{pr} d_{pr}^2 + \frac{w_{beam}^3}{4} \right), \tag{6}$$

where  $w_{beam}$  is the width of the suspension beam,  $w_{pr}$  is the width of the piezoresistors,  $d_{pr}$  is the distance between the piezoresistors and the suspension beam,  $d_{cg}$  is the distance to the center of gravity of the proof mass, and h is the thickness of the SOI device layer [3].

For a quasi-static accelerometer, the acceleration is given by  $a = \omega_n^2 x = kx/m$ , where  $\omega_n$  is the natural frequency (in rad/s), m is the mass, and x is the deflection of the center of the proof mass. From geometry considerations, the deflection of the proof mass can be related to the change in length of the piezoresistors as  $x = \Delta L d_{cg}/d_{pr}$ . By combining equations (4), (5), and (6) the sensitivity of the accelerometer,  $S = V_{out}/a$ , can now be calculated as

$$S = \frac{V_{in}Gmd_{pr}d_{cg}}{2E_lh\left(2w_{pr}d_{pr}^2 + w_{beam}^3/4\right)}.$$

(7)

Naturally, the sensitivity increases with gage factor and applied voltage. The sensitivity can also be increased by making the proof mass larger or the piezoresistors and suspension beam thinner. From a sensitivity standpoint, it is desirable to choose SOI wafers with a thin device layer. However, note that the out-of-plane stiffness is reduced when thinner wafers are used.

The product of the sensitivity and the square of the natural frequency,  $Sf_n^2$ , is often used for accelerometers as a figure of merit in order to optimize the design. Although most of the parameters in equation (7) can otherwise be chosen relatively freely, the choice of width of the piezoresistors is somewhat limited. The length of a piezoresistor can be expressed as  $L_0 = R_0 w_{pr} h/\rho$ , and it is preferred to make the piezoresistors as thin as possible to assure bending around the centrally located suspension beam. However, due to the limited aspect ratio of the DRIE (here assumed to be 25:1), the minimum width is approximately  $w_{pr} = h/25$ .

The accelerometer that will be considered in section 4 was fabricated from a 50  $\mu$ m thick SOI device layer with a resistivity of 0.12  $\Omega$ -cm. It was designed for an acceleration range of 1 G to 500 G, with  $w_{pr} = 2 \ \mu$ m,  $d_{pr} = 60 \ \mu$ m,  $w_{beam} = 12 \ \mu$ m, and  $L_0 = 38 \ \mu$ m. The proof mass is 934  $\mu$ m × 3735  $\mu$ m, the etch holes are 15  $\mu$ m × 15  $\mu$ m, and the density of silicon is 2330 kg/m<sup>3</sup>, leading to  $m = 3.5 \times 10^{-7}$  kg and  $d_{cg} = 1906 \ \mu$ m. With a gage factor of G = 121 (estimated earlier in this section) and applied voltage of  $V_{in} = 5 \ V$ , the sensitivity is estimated to be  $S = 1 \ \text{mV/G}$ . The natural frequency can be calculated as  $f_n = 1/2\pi \times \sqrt{k/m} = 8.1 \ \text{kHz}$ .

#### 3. Fabrication process

Multiple photomasks are normally required when fabricating piezoresistive accelerometers in order to define the piezoresistors, conductors, proof mass, and suspension system. By eliminating the need for doping steps, piezoresistive accelerometers are fabricated using only one photomask in the process described in this section.

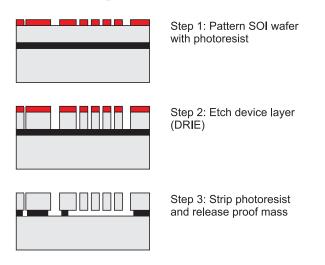

The single-mask fabrication process depicted in figure 2 is based on SOI wafers with a specific resistivity. First, a layer of Shipley 1827 photoresist is spin-coated onto the wafer. The layout of the proof mass, suspension beam, thin piezoresistors, overrange stops, and wide conductors is then patterned using a photomask and the photoresist is exposed and developed. Next, deep reactive ion etching (DRIE) is utilized to etch the device layer of the SOI wafer all the way to the buried silicon oxide. The wafer is then diced and the photoresist is stripped. Finally, selected parts of the silicon oxide layer is removed with hydrofluoric (HF) acid and a free-standing proof mass is obtained. Areas without release holes define anchor points.

Figure 2. Single-mask SOI fabrication process for piezoresistive accelerometers.

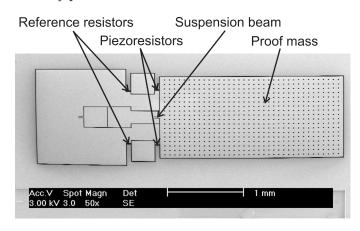

Figure 3 shows a scanning electron microscope (SEM) image of a fabricated singleaxis accelerometer. While the piezoresistors are attached to the proof mass, the reference resistors are anchored. Since the reference resistors are included on the chip and designed to be equal in size to the piezoresistors, all four resistors should have the same temperature properties. On the contrary, in many traditional piezoresistive sensors offchip reference resistors are used, often requiring additional temperature compensation in order to adjust for temperature dependence of the sensitivity and the voltage offset.

It is expected that the proposed fabrication process will allow for higher operational temperatures than sensors where pn-junctions are used to isolate the piezoresistors, due to high leakage currents in pn-junctions above 150°C. Note, however, that while the presented SOI sensors will likely be operational up to about 350°C, temperature compensation of the sensitivity will still be required due to the temperature dependence of the piezoresistive coefficients, discussed in section 2.

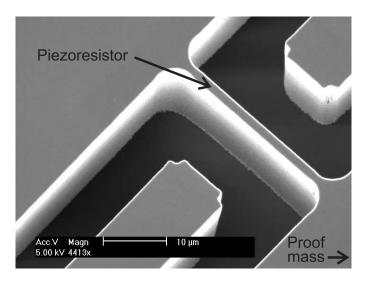

Figure 4 displays a close-up SEM image of one of the 2  $\mu$ m wide piezoresistors from the accelerometer in figure 3. The central suspension beam (see figure 3) is preferably made much wider than this piezoresistor to assure that the bending occurs around the center of the device.

Figure 3. SEM image of single-axis piezoresistive accelerometer.

Figure 4. Close-up of a piezoresistor. The width is approximately 2  $\mu$ m and the height 50  $\mu$ m (SOI device layer).

#### 4. Experimental results

The accelerometers were designed to emulate a Wheatstone bridge, as was illustrated in figure 1. A half-bridge configuration was used with both the piezoresistors and reference resistors included on the chip. Applied acceleration causes bending of the centrally located suspension beam, and stretches one of the piezoresistors (increased resistance) and compresses the other (decreased resistance). This in turn leads to an unbalanced bridge and the output voltage is increased or decreased depending on the direction of the acceleration.

Diced SOI chips containing single-axis accelerometers were placed in dual in-line packages (DIP) and wire-bonded. For proof-of-concept, aluminum wires were bonded straight onto the silicon, without using metal bonding pads, making this truly a singlemask fabrication process. Adequate contacts can be provided in this manner due to the relatively high doping concentration in the p-type silicon. However, a contact resistance of about 50  $\Omega$  is measured in the bonded samples. In order to reduce this contact resistance and improve the ohmic contacts, a heavily doped surface layer and metal bonding pads should preferably be added to the process.

#### 4.1. Sensitivity and time domain response

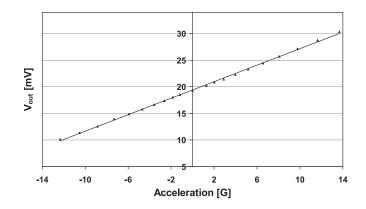

The packaged accelerometers were positioned 26 cm from the center of a rate table, which has a maximum angular velocity of  $1300^{\circ}$ /s.  $V_{in}$  was applied and  $V_{out}$  was measured through the rate table's slip rings. The velocity was increased in  $100^{\circ}$ /s increments from  $400^{\circ}$ /s to  $1300^{\circ}$ /s, corresponding to acceleration from approximately 1 G to 13 G. The same test was repeated with the accelerometer turned  $180^{\circ}$  and positioned 24 cm from the center of the rate table, inducing acceleration from approximately -1 G to -13 G.

Figure 5 shows linear output characteristics between -13 G and +13 G when  $V_{in} = 5$  V was applied. The measured sensitivity was 0.77 mV/G. The voltage offset of 19 mV is due to fabrication imperfections that led to a slightly unbalanced Wheatstone bridge. Several approaches can be considered in order to eliminate this offset, including on-chip tuning resistors, off-chip shunt resistors, laser-trimming of the etched resistors, or using an external voltage-shifting circuit.

Figure 5. Accelerometer sensitivity measurements on rate-table.

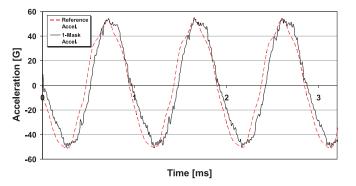

Next, a Dytran 3030A piezoelectric reference accelerometer was mounted in close proximity to the single-axis accelerometer to measure the time domain response, and the mounting platform was placed on a shaker. Figure 6 displays the output from both the reference accelerometer and the single-mask piezoresistive accelerometer at 1 kHz. Both outputs were AC coupled to eliminate the voltage offset. The sensitivity of the reference accelerometer was 10 mV/G and its maximum output during the excitation was 520 mV, yielding a maximum acceleration of 52 G. The single-mask piezoresistive accelerometer outputted approximately 40 mV for this acceleration, which is consistent with the sensitivity of 0.77 mV/G, previously obtained from figure 5.

While no significant phase shift is noted at 1 kHz, several different high-frequency components are sensed by the two accelerometers. This is the main reason for the

Figure 6. Time domain response at 1 kHz for single-mask piezoresistive accelerometer and piezoelectric reference accelerometer.

mismatch between the curves in figure 6. The compliance of the package and the mounting bracket is believed to be the source of this discrepancy.

### 4.2. High-G testing

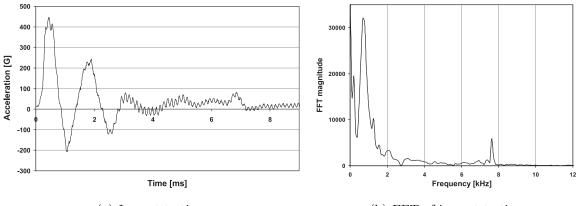

The accelerometers presented in this section were designed for impact testing applications with a maximum acceleration of 500 G. Figure 7(a) shows the time domain results from high-G testing, where an impact hammer was used to excite the piezoresistive accelerometer. The maximum measured impact was approximately 450 G. Note that the measured acceleration signal settles at about 25 G, which corresponds to the permanent offset of 19 mV from figure 5.

The high frequency oscillation of the signal in figure 7(a) is due to the undamped design of the accelerometer. From the fast Fourier transform (FFT) of the acceleration signal in figure 7(b), it can be seen that the frequency of this oscillation is approximately 7.6 kHz, which is consistent with the estimation of the natural frequency from section 2 (8.1 kHz). In future designs, a slight damping coefficient will be introduced by reducing the gap between the proof mass and the sidewalls of the bulk silicon in order to reduce this high-frequency oscillation.

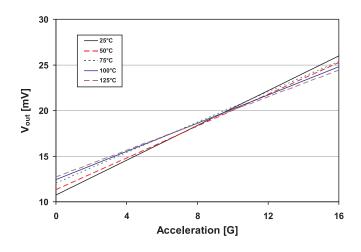

## 4.3. Thermal characterization

A packaged accelerometer was placed inside a small thermal chamber together with a heater and thermocouple. The chamber was then put on a rate table and the sensitivity and voltage offset were measured at different temperatures during applied acceleration between 1 G and 16 G, as shown in figure 8.

The sensitivity of this accelerometer at room temperature was approximately 0.95 mV/G and the permanent voltage offset was 10.8 mV. As predicted from the discussion in section 2, the sensitivity is reduced at higher temperatures. However, while no significant change in voltage offset was expected due to the matching of the bridge resistors, a slight increase was observed in figure 8. This is likely due to fabrication

(a) Impact testing.

(b) FFT of impact testing.

Figure 7. Time and frequency domain response of impact testing of piezoresistive accelerometer.

Figure 8. Thermal testing of piezoresistive accelerometer.

imperfections and thermal stress in the material.

Table 1 summarizes the measured output voltage at zero acceleration and shows the obtained sensitivity at different temperatures. By dividing the sensitivity at an elevated temperature by the sensitivity at room temperature, the piezoresistive factor can be calculated (see section 2). As is shown in the table, the measured piezoresistive factors match the predicted values in [17].

The average temperature coefficient of sensitivity (TCS) is  $0.3\%/^{\circ}$ C and the temperature coefficient of offset (TCO) is 20 mG/°C. While the TCS certainly needs to be compensated for, the TCO is not completely detrimental to the performance considering that the sensor is designed for acceleration between 1 G and 500 G. For example, if not properly compensated at 125°C, the offset will show up as a false 2 G acceleration.

While the current testbed only allows for temperatures up to  $125^{\circ}$ C, it has been demonstrated (for example [9, 12]) that isolation of piezoresistors using the buried oxide

|                              | $25^{\circ}\mathrm{C}$ | $50^{\circ}\mathrm{C}$ | 75°C | 100°C | 125°C |

|------------------------------|------------------------|------------------------|------|-------|-------|

| $V_{out}   [mV]$             | 10.8                   | 11.3                   | 12.0 | 12.5  | 12.8  |

| $\Delta V_{offset} \; [mV]$  | -                      | 0.5                    | 1.2  | 1.7   | 2.0   |

| $S \; [mV/G]$                | 0.95                   | 0.87                   | 0.83 | 0.77  | 0.73  |

| $S/S_{25^{\circ}\mathrm{C}}$ | 1                      | 0.92                   | 0.87 | 0.81  | 0.77  |

| P(N,T) [17]                  | 1                      | 0.92                   | 0.86 | 0.80  | 0.75  |

Table 1. Offset voltage and sensitivity at elevated temperatures

layer in SOI wafers is suitable for temperatures up to about 350°C.

# 5. Conclusion

A single-mask fabrication process for piezoresistive accelerometers was presented. This process significantly reduces the number of required fabrication steps and also extends the operational temperature range, when compared to conventional piezoresistive accelerometers. Single-axis accelerometers were fabricated and characterized at high G-loads and different temperatures.

# Acknowledgments

The authors would like to thank the staff of the UCI Integrated Nanosystems Research Facility, INRF, for fabrication support and the members of the UCI Microsystems Laboratory for useful discussions. This research was partially supported by VIP Sensors grant 442531-19919 and UC Discovery grant 482530-59829.

# References

- Roylance L M and Angell J B 1979 A batch-fabricated silicon accelerometer IEEE T. Electron Dev. 26 1911–1917

- [2] Barth P W, Pourahmadi F, Mayer R, Poydock J and Petersen K 1988 A monolithic silicon accelerometer with integral air damping and overrange protection Tech. Dig. 3rd IEEE Solid-State Sensor and Actuator Workshop (Hilton Head Island, SC) pp 597–600

- [3] Suminto J T 1996 A wide frequency range, rugged silicon micro accelerometer with overrange stops Proc. 9th IEEE Int. Workshop on Micro Electro Mechanical Systems (San Diego, CA) pp 180–185

- [4] Riethmüller W, Benecke W, Schnakenberg U and Wagner B 1992 A smart accelerometer with on-chip electronics fabricated by a commercial CMOS process Sens. Actuat. A 31 121–124

- [5] Seidel H, Fritsch U, Gottinger R and Schalk J 1995 A piezoresistive silicon accelerometer with monolithically integrated CMOS-circuitry Proc. 8th Int. Conf. on Solid-State Sensors and Actuators (Stockholm, Sweden) pp 597–600

- [6] Partridge A, Reynolds J K, Chui B W, Chow E M, Fitzgerald A M, Zhang L, Maluf N I and Kenny T W 2000 A high-performance planar piezoresistive accelerometer J. Microelectromech. Syst. 9 58–66

- [7] Takashima Y, Adachi T, Yoshino T and Yamada T 1997 A temperature compensation method for piezoresistive sensors JSAE Review 19 317–319

- [8] Yamada K, Higuchi K and Tanigawa H 1990 A novel silicon accelerometer with a surrounding mass structure Sens. Actuat. A 21 308–311

- [9] Takao H, Matsumoto Y, Seo H and Tanaka H 1995 Three dimensional vector accelerometer using SOI structure for high temperature Proc. 8th Int. Conf. on Solid-State Sensors and Actuators (Stockholm, Sweden) pp 683–686

- [10] Huang S, Li X, Song Z, Wang Y, Yang H, Che L and Jiao J 2005 A high-performance micromachined piezoresistive accelereometer with axially stressed tiny beams J. Micromech. Microeng. 15 993–1000

- [11] Amarasinghe R, Dao D V, Toriyama T and Sugiyama S 2006 Simulation, fabrication and characterization of a three-axis piezoresistive accelerometer Smart Mater. Struct. 15 1691– 1699

- [12] Kroetz G H, Eickhoff M H and Moeller H 1999 Silicon compatible materials for harsh environment sensors Sens. Actuat. A 74 182–189

- [13] Kanda Y 1991 Piezoresistance effect of silicon Sens. Actuat. A 28 83-91

- [14] Gakkestad J, Ohlckers P and Halbo L 1995 Compensation of sensitivity shift in piezoresistive pressure sensors using linear voltage excitation Sens. Actuat. A 49 11–15

- [15] Eklund E J and Shkel A M 2005 Single-mask SOI fabrication process for linear and angular piezoresistive accelerometers with on-chip reference resistors Proc. 4th IEEE Conf. on Sensors (Irvine, CA) pp 656–659

- [16] Smith C S 1954 Piezoresistance effect in germanium and silicon Phys. Rev. 94 42-49

- [17] Kanda Y 1982 A graphical representation of the piezoresistance coefficients in silicon IEEE T. Electron Dev. 29 64–70

- [18] Thurber W R, Mattis R L, Liu Y M and Filliben J J 1980 Resistivity-dopant density relationship for boron-doped silicon J. Electrochem. Soc. 127 2291–2294

- [19] Kim S and Wise K D 1983 Temperature sensitivity in silicon piezoresistive pressure sensors IEEE T. Electron Dev. 30 802–810

- [20] Tanigawa H, Ishihara T, Hirata M and Suzuki K 1985 MOS integrated silicon pressure sensor IEEE T. Electron Dev. 32 1191–1195

- [21] Wortman J J and Evans R A 1964 Young's modulus, shear modulus, and Poisson's ratio in silicon and germanium J. Appl. Phys. 36 153–156