# UC Riverside UC Riverside Electronic Theses and Dissertations

## Title

Engineer Nanocrystal Floating Gate Memory Scaling

## Permalink

https://escholarship.org/uc/item/9fn949dp

## **Author** Ren, Jingjian

# Publication Date 2012

Peer reviewed|Thesis/dissertation

## UNIVERSITY OF CALIFORNIA RIVERSIDE

Engineer Nanocrystal Floating Gate Memory Scaling

A Dissertation submitted in partial satisfaction of the requirements for the degree of

Doctor of Philosophy

in

**Electrical Engineering**

by

Jingjian Ren

December 2012

Dissertation Committee:

Dr. Jianlin Liu, Chairperson Dr. Roger K. Lake Dr. Sheldon Tan

Copyright by Jingjian Ren 2012 This Dissertation of Jingjian Ren is approved:

Committee Chairperson

University of California Riverside

#### ACKNOWLEDGEMENTS

First and for the most I would like to express my sincerest gratitude to my research advisor, Professor Jianlin Liu for his supervision and advice from the very early stage of this research. Throughout my whole PhD study, he provided me invaluable support and encouragement. His passion for scientific research and his meticulous attitude toward working guided me to grow into a good researcher. Without his persistent help, this dissertation would not have been possible at all.

I would like to thank my committee members, Professor Roger Lake and Professor Sheldon Tan for serving on my qualification examination and as my thesis committee members. They provided precious suggestions for my research.

I am also thankful to Dr. Bei Li, Dr. Mario Olmedo, Dr. Dong Yan and Dr. Dexter Humphrey for their research and technical help throughout my graduate research. They were always the ones that gave me selfless help with a lot of patience.

I would like to thank my lab mates, Dr. Sheng Chu, Dr. Zheng Zuo, Dr. Jianze Zhao, Dr. Jing Qi, Dr. Zheng Yang, Dr. Guoping Wang, Dr. Jieying Kong, Dr. Lin Li, Dr. Huimei Zhou, Dr. Ning Zhan, Mr. Jian Huang, Ms. Zonglin Li, Mr. Monzur Morshed, Mr. Zhongguang Xu for their priceless friendship that I will always cherish,

I would like to give my special thanks to my beloved parents for supporting me and encouraging me with their unconditional love. They are always there for me whenever I need them. I would also like to thank all my friends for who you are to me. This thesis is dedicated to my parents,

to those who love me and those who I love.

v

#### ABSTRACT OF THE DISSERTATION

Engineer Nanocrystal Floating Gate Memory Scaling

by

Jingjian Ren

### Doctor of Philosophy, Graduate Program in Electrical Engineering University of California, Riverside, December 2012 Dr. Jianlin Liu, Chairperson

Flash memory is the dominant nonvolatile memory technology that has been experiencing fastest market growth driven by the booming of portable electronic devices. Since its invention in 1980s, it has been through aggressive scaling. Leading semiconductor memory manufacturers such as Samsung, Intel/Micron and SanDisk/Toshiba have unveiled their 19/20nm NAND flash technology in production. However, how long the fast scaling pace of flash can be maintained remains a question mark since this device using continuous polycrystalline Si floating gate faces increasing challenge brought by poor immunity to charge leakage and process difficulty due to large vertical gate stack dimension. To enable the further scaling of flash technology, change needs to be made at the cell level. Devices using discrete charge storage units have been recognized as potential alternatives to conventional flash cells, including charge trapping type device and nanocrystal floating gate device.

Nanocrystal floating gate memory is considered a promising future nonvolatile memory candidate because of its immunity to weak-point leakage in tunnel oxide and thus its superior scalability in terms of tunnel oxide thickness and power consumption. However, no scaling is easy. Problem of nano-dot density fluctuation has arisen for this type of device as scaling process proceeds. The increasing sensitivity of chiplevel device performance to dot distribution in scaled cells requires that nanocrystal deposition, which is the key step for device fabrication, should be fully understood, and that this device should start evolving to incorporate material and structure innovations. This work is devoted to propelling the scaling process of nanocrystal memory through nanocrystal deposition behavior investigation and device structure engineering. In chapter 2, Si nanocrystal growth on patterned oxide substrate by chemical vapor deposition is studied both experimentally and theoretically and directed self-assembly behavior of Si nanocrystals is identified as due to the effect of substrate morphology. This deepens our understanding on nanocrystal nucleation and growth and provides a general guidance to deposition process for memory applications. Chapter 3 includes the work on a gate stack-engineered nanocrystal MOS capacitor memory device. An  $Al_2O_3$ -SiO<sub>2</sub> double-barrier structure is utilized for dielectric layers and process-induced oxide degradation issue is well solved, resulting in improved memory performance. Chapter 4 and chapter 5 focus on the demonstration of non-planarity concept for nanocrystal memory device. Non-planar

nanocrystal memories with multiple and single triangular-shaped Si nanowire channel are introduced. This new concept of nanocrystal memory device is aimed at alleviating dot density variation issue at the scaled technology nodes and helps extend the scaling limit of planar device.

Based on all the theoretical and experimental work in this dissertation, it is concluded that nanocrystal memory scaling lies in good understanding and control of the key process as well as continued cell architecture engineering. This work serves as a step toward the scaling limit of nanocrystal floating gate device for next generation nonvolatile memory development.

## TABLE OF CONTENTS

| Acknowledgements  | iv   |

|-------------------|------|

| Abstract          | vi   |

| Table of Contents | ix   |

| List of Figures   | xiii |

| List of Tables    | xvi  |

| Chapter 1 | Introduction                                                                         | 1  |

|-----------|--------------------------------------------------------------------------------------|----|

| 1.1       | Semiconductor memory                                                                 | 1  |

| 1.2       | Flash memory                                                                         | 5  |

|           | 1.2.1 Cell structure and working principle                                           | 5  |

|           | 1.2.2 NAND vs. NOR                                                                   | 7  |

|           | 1.2.3 Limitations and alternatives                                                   | 8  |

| 1.3       | Nanocrystal floating gate memory                                                     | 10 |

|           | 1.3.1 Basic device concepts                                                          | 10 |

|           | 1.3.2 Current status                                                                 | 11 |

|           | 1.3.3 Perspective and challenges of scaling                                          | 12 |

| 1.4       | Motivation of this research                                                          | 14 |

| Reference | S                                                                                    | 16 |

| Chapter 2 | Strain-less directed self-assembly of Si nanocrystals on patterned $SiO_2$ substrate | 19 |

| 2.1       | Introduction                                                                         | 19 |

| 2.2       | Motivation                                                                           | 19 |

| 2.3       | Experiments                                                                          | 20 |

|                   | 2.3.1 Substrate preparation                                                                                                                                                                                 | 20                                                                                             |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

|                   | 2.3.2 Si nanocrystal deposition                                                                                                                                                                             | 22                                                                                             |

|                   | 2.3.2.1 Deposition temperature-dependent nucleation                                                                                                                                                         | 22                                                                                             |

|                   | and growth behavior                                                                                                                                                                                         |                                                                                                |

|                   | 2.3.2.2 Deposition time-dependent nucleation and                                                                                                                                                            | 26                                                                                             |

|                   | growth behavior                                                                                                                                                                                             |                                                                                                |

| 2.4               | Modeling                                                                                                                                                                                                    | 28                                                                                             |

| 2.5               | Summary                                                                                                                                                                                                     | 33                                                                                             |

| 2.6               | Acknowledgement                                                                                                                                                                                             | 33                                                                                             |

| References        |                                                                                                                                                                                                             | 35                                                                                             |

| Chapter 3         | High-density NiSi nanocrystals embedded in Al <sub>2</sub> O <sub>3</sub> /SiO <sub>2</sub><br>double-barrier for robust retention of nonvolatile memory                                                    | 38                                                                                             |

|                   |                                                                                                                                                                                                             |                                                                                                |

| 3.1               | Introduction                                                                                                                                                                                                | 38                                                                                             |

| 3.1<br>3.2        | Introduction<br>Motivation                                                                                                                                                                                  | 38<br>38                                                                                       |

|                   |                                                                                                                                                                                                             |                                                                                                |

| 3.2               | Motivation                                                                                                                                                                                                  | 38                                                                                             |

| 3.2<br>3.3        | Motivation<br>Device fabrication                                                                                                                                                                            | 38<br>41                                                                                       |

| 3.2<br>3.3        | Motivation<br>Device fabrication<br>Device characterization                                                                                                                                                 | 38<br>41<br>43                                                                                 |

| 3.2<br>3.3        | Motivation<br>Device fabrication<br>Device characterization<br>3.4.1 Material and device structure characterizations                                                                                        | <ul><li>38</li><li>41</li><li>43</li><li>43</li></ul>                                          |

| 3.2<br>3.3        | Motivation<br>Device fabrication<br>Device characterization<br>3.4.1 Material and device structure characterizations<br>3.4.2 Memory window                                                                 | <ul> <li>38</li> <li>41</li> <li>43</li> <li>43</li> <li>44</li> </ul>                         |

| 3.2<br>3.3        | Motivation<br>Device fabrication<br>Device characterization<br>3.4.1 Material and device structure characterizations<br>3.4.2 Memory window<br>3.4.3 Transient performance                                  | <ul> <li>38</li> <li>41</li> <li>43</li> <li>43</li> <li>44</li> <li>46</li> </ul>             |

| 3.2<br>3.3<br>3.4 | Motivation<br>Device fabrication<br>Device characterization<br>3.4.1 Material and device structure characterizations<br>3.4.2 Memory window<br>3.4.3 Transient performance<br>3.4.4 Retention and Endurance | <ul> <li>38</li> <li>41</li> <li>43</li> <li>43</li> <li>44</li> <li>46</li> <li>48</li> </ul> |

| Chapter 4 | Non-planar NiSi nanocrystal floating gate memory based on a triangular-shaped Si nanowire array                                     | 55 |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.1       | Introduction                                                                                                                        | 55 |

| 4.2       | Motivation                                                                                                                          | 55 |

| 4.3       | Device fabrication                                                                                                                  | 58 |

| 4.4       | Results and discussion                                                                                                              | 60 |

|           | 4.4.1 Output characteristics                                                                                                        | 60 |

|           | 4.4.2 Transfer characteristics                                                                                                      | 61 |

|           | 4.4.3 Transient characteristics                                                                                                     | 62 |

|           | 4.4.4 Retention and Endurance characteristics                                                                                       | 64 |

| 4.5       | Summary                                                                                                                             | 66 |

| 4.6       | Acknowledgement                                                                                                                     | 66 |

| Referen   | ces                                                                                                                                 | 67 |

| Chapter 5 | Non-volatile memory effect of a high-density NiSi nano-<br>dots floating gate transistor memory using single Si<br>nanowire channel | 69 |

| 5.1       | Introduction                                                                                                                        | 69 |

| 5.2       | Motivation                                                                                                                          | 70 |

| 5.3       | Device fabrication                                                                                                                  | 72 |

| 5.4       | Results and discussion                                                                                                              | 74 |

|           | 5.4.1 Material and device structure characterization                                                                                | 74 |

|           | 5.4.2 Electrical characterization                                                                                                   | 75 |

|           | 5.4.2.1 Transfer characteristics                                                                                                    | 75 |

|           | 5.4.2.2 Programming/erasing mechanism: fringing field                                                                               | 77 |

|           | 5.4.2.3 Programming/erasing characteristics                                                                                         | 80 |

|           | 5.4.2.4 Retention           | 81 |

|-----------|-----------------------------|----|

| 5.5       | Summary                     | 82 |

| 5.6       | Acknowledgement             | 83 |

| Reference | · <i>S</i>                  | 84 |

| Chapter 6 | Conclusions and future work | 88 |

#### LIST OF FIGURES

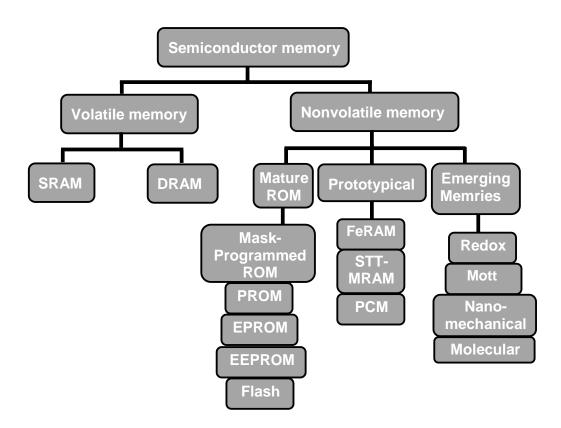

- Figure 1.1 Classification of semiconductor memory.

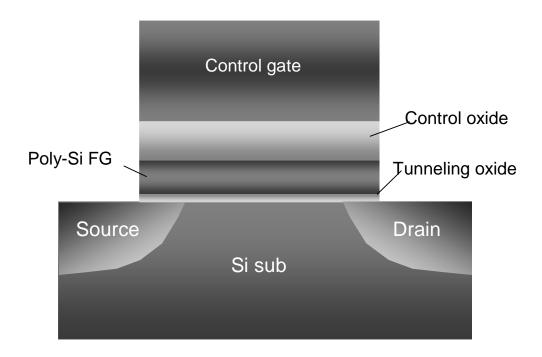

- Figure 1.2 A typical flash memory cell.

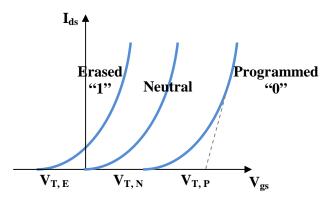

- Figure 1.3  $I_{ds}$ - $V_{gs}$  characteristics and  $V_T$  shift of n-type flash memory at neutral, programmed and erased states.

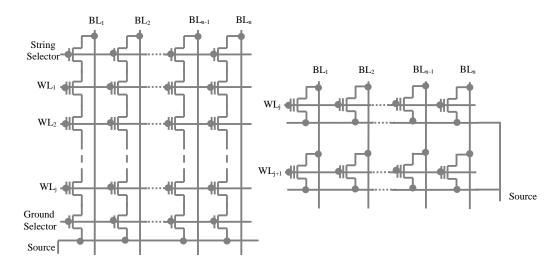

- Figure 1.4 NAND and NOR array architecture.

- **Figure 1.5** Alternatives to poly-Si floating gate memory.

- Figure 1.6 Nanocrsytal floating gate memory cell.

- Figure 1.7 Comparison of immunity to leakage between conventional flash cell and NC memory cell.

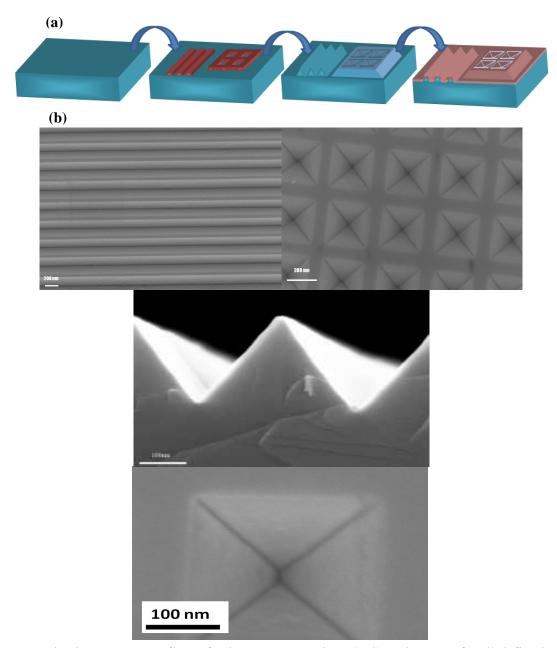

- **Figure 2.1** (a) Process flow of substrate preparation; (b) SEM images of well-defined quasi-triangular- and pit-shaped patterns.

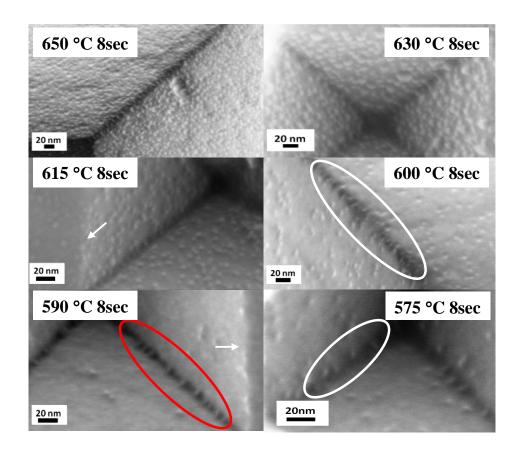

- Figure 2.2 SEM images of temperature-dependent Si NCs nucleation and growth.

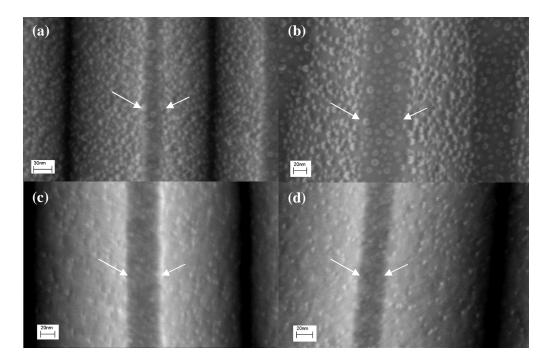

- Figure 2.3 SEM images of Si NC growth on quasi-triangular shaped patterns: (a) 650 °C, 8sec; (b) 600 °C, 30sec; (c) 600 °C, 15sec; (d) 580 °C, 60sec.

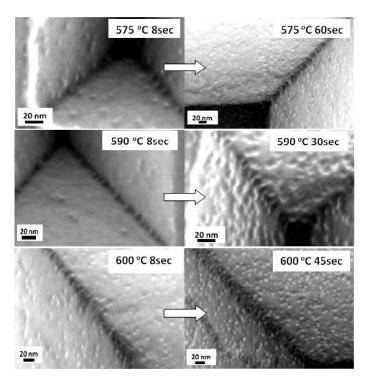

- **Figure 2.4** SEM images of the growth time dependence of Si NCs growth on patterned substrate surface to show the evolvement of NC deposition process at different stages.

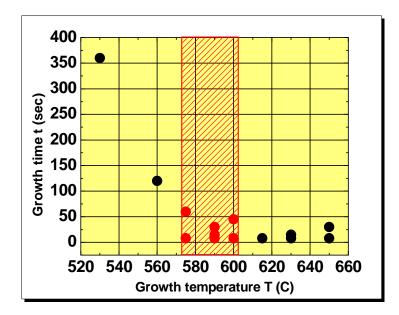

- **Figure 2.5** Summary of growth condition splits and the temperature window for Si NCs preferential growth on concave oxide substrate surface with t<sub>ox</sub>=5nm (temperature window: T=575°C~600°C; gas pressure P=0.5torr, gas flux= SiH<sub>4</sub> 20sccm:N<sub>2</sub> 100sccm)

- **Figure 2.6** (a) Two-dimensional model of NC-patterned oxide substrate system; (b) 3-D plot of total NC formation energy as a function of substrate angle  $\varphi$  and system parameter  $\gamma$ , with the unit of energy  $2 \gamma_{NC} S^{1/2}$ .

(a) Schematic of the patterned substrate surface; (b) Calculated total

- Figure 2.7 NC formation energy for three different types of experimental surface morphologies.

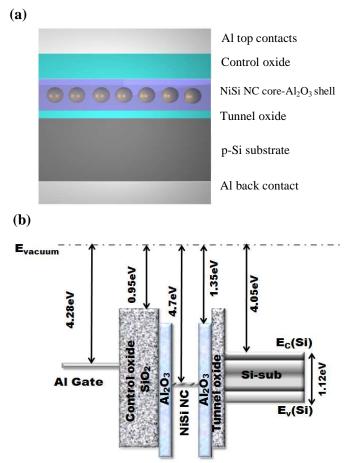

- Figure 3.1 (a) Schematic of device structure; (b) flat energy band diagram of NiSi NC-Al<sub>2</sub>O<sub>3</sub> floating-gate memory.

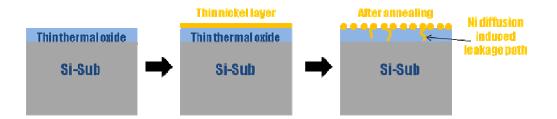

- Figure 3.2 Metal atom diffusion induced leakage paths in VSS process.

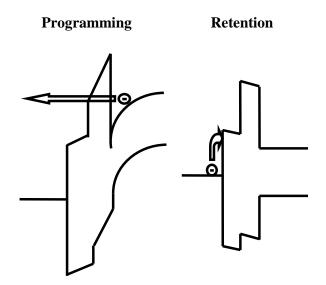

- Figure 3.3 Possible energy band diagram at programming and retention states.

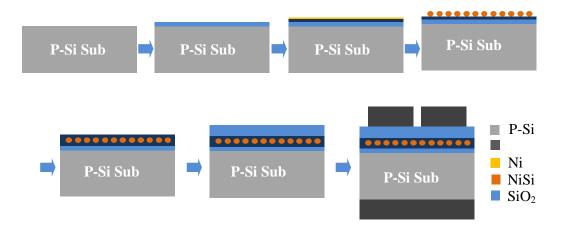

- **Figure 3.4** Double barrier NC capacitor memory fabrication process flow.

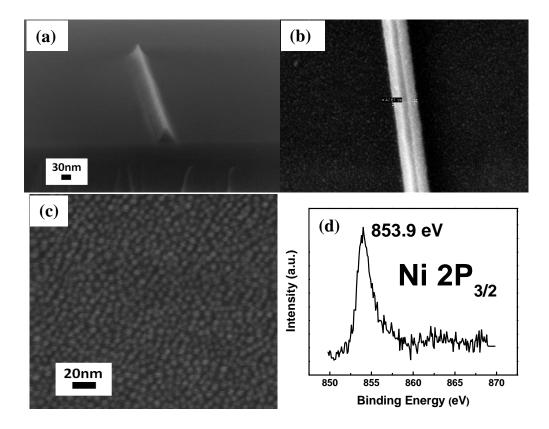

- **Figure 3.5** (a) SEM image of high-density NiSi NCs; (b) XPS spectrum of NiSi NCs on Al<sub>2</sub>O<sub>3</sub>/SiO<sub>2</sub>/Si substrate; (c) cross-sectional TEM image of NiSi NC-Al<sub>2</sub>O<sub>3</sub> floating-gate memory device, (d) cross-sectional TEM image of the control sample.

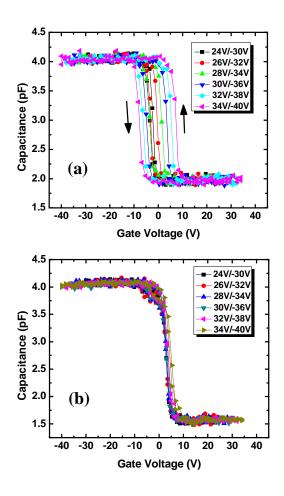

- **Figure 3.6** C-V sweep of (a) NiSi NC-Al<sub>2</sub>O<sub>3</sub> floating-gate memory device and (b) control device under different scanning gate voltages.

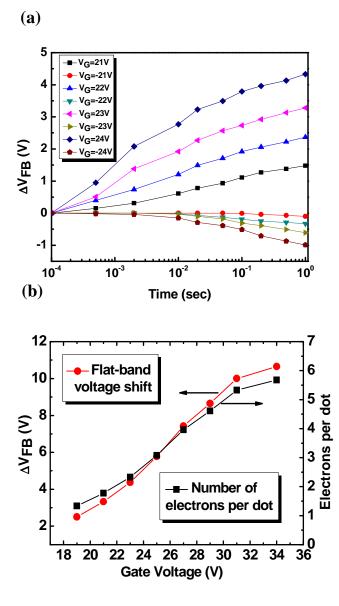

- **Figure 3.7** (a) Transient characteristics of NiSi NC-Al<sub>2</sub>O<sub>3</sub> floating-gate memory under different gate programming /erasing voltages,(b) flat-band voltage shift and number of electrons per dot as a function of gate bias.

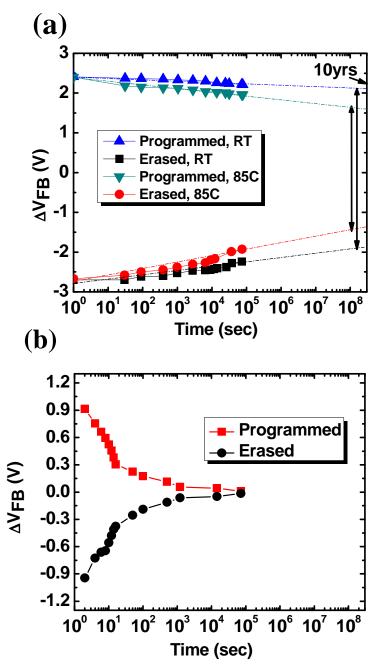

- (a) Retention characteristics of NiSi NC-Al<sub>2</sub>O<sub>3</sub> floating-gate memory

Figure 3.8 at room temperature and 85°C; (b) retention characteristics of NiSi NC memory without Al<sub>2</sub>O<sub>3</sub> barrier layer.

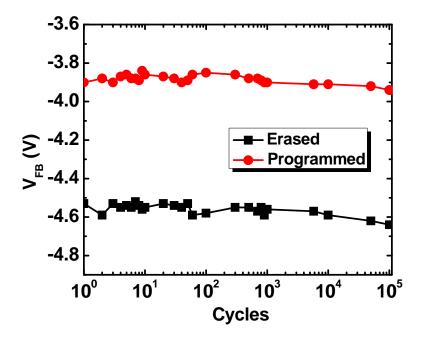

Endurance characteristics of NiSi NC-Al<sub>2</sub>O<sub>3</sub> floating-gate memory up **Figure 3.9** to  $10^5$  cycles.

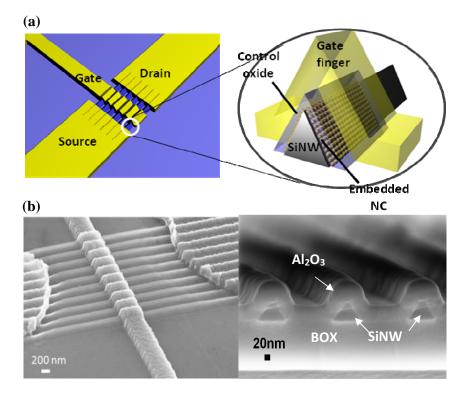

- **Figure 4.1** (a) Schematic and (b) SEM images of triangular-shaped SiNW array based NiSi NC memory.

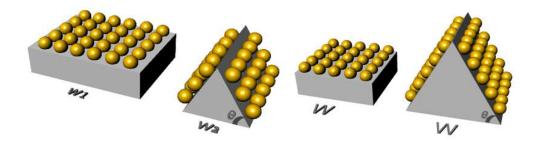

- **Figure 4.2** Comparison between non-planar and planar NC memory cells: (a) cells with the same number of NCs; (b) cells with the same chip floor plan.

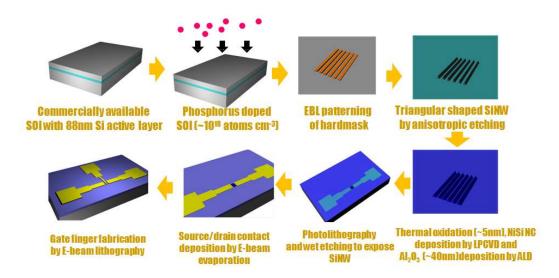

- **Figure 4.3** Fabrication process flow of a SiNW array based non-planar NC memory device.

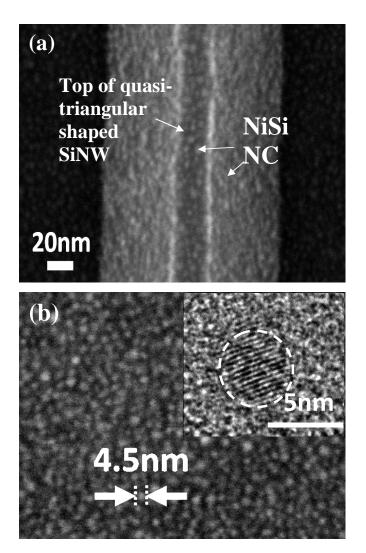

- **Figure 4.4** (a) Top-view SEM image of NiSi NCs on a SiO<sub>2</sub>-covered SiNW; (b) SEM image of NiSi NCs at open area. Inset shows an HRTEM image of single NC.

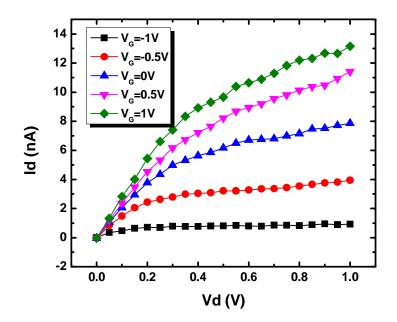

- Figure 4.5 Output characteristics of SiNW array based non-planar NC memory transistor.

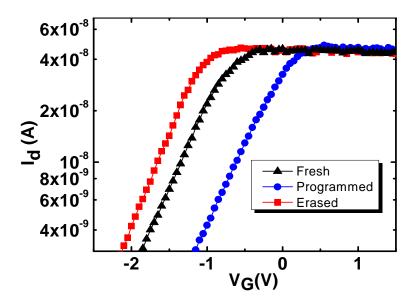

- **Figure 4.6** Transfer characteristics of triangular shaped SiNW array based NiSi NC memory at the neutral, programmed and erased states.

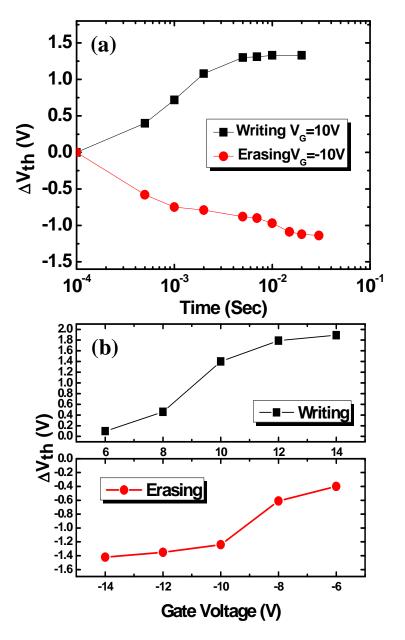

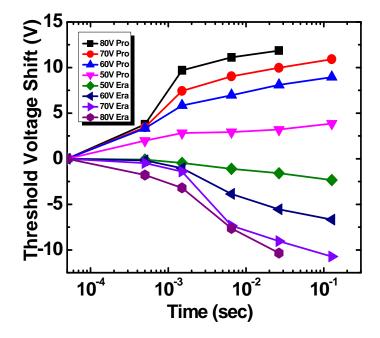

- Figure 4.7 (a) Time and (b) gate bias dependent P/E characteristics.

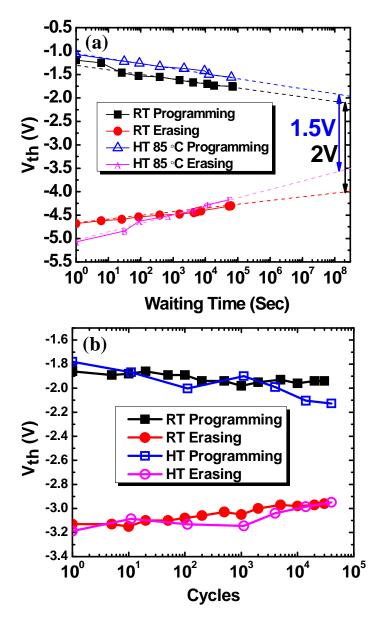

- **Figure 4.8** (a) Retention characteristics and (b) Endurance characteristics of triangular-shaped SiNW array based NiSi NC memory at RT and 85°C.

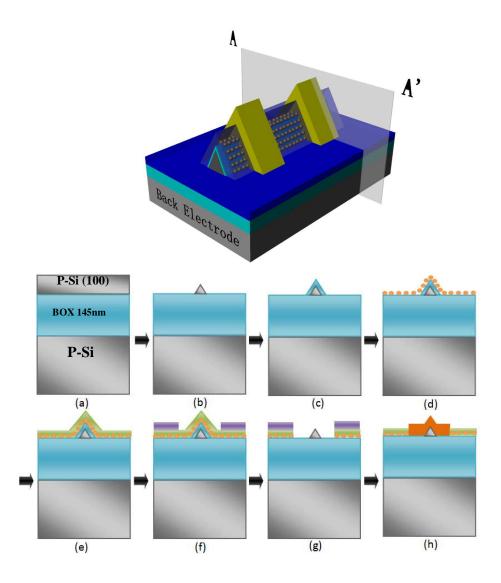

- Figure 5.1 Schematic of back-gated device structure and fabrication process flow:

(a) SOI wafer; (b) SiNW after etching; (c) Tunneling oxide by dry oxidation; (d) Nano-dots deposition; (e) Al<sub>2</sub>O<sub>3</sub> passivation; (f) E-beam lithography patterning of S/D; (g) Wet etching to expose SiNW channel; (h) Contact metal deposition.

- Figure 5.2 (a) Tilted cross-sectional view of stand-alone triangular-shaped SiNW (~40nm); (b) Top view of high-density nano-dots on tunneling oxide-covered SiNW; (c) Evenly distributed nano-dots at open area; (d) XPS result of nano-dots layer.

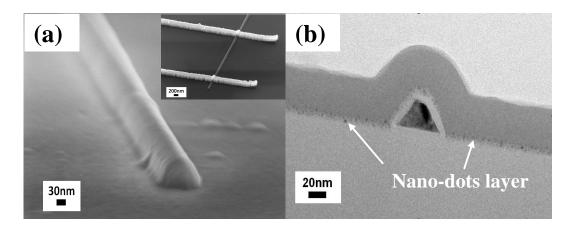

- Figure 5.3 (a) Tilted SEM view of NW covered with Al<sub>2</sub>O<sub>3</sub>; Inset: S/D contacts of as-fabricated device by E-beam lithography; (d) Cross-sectional TEM image of triangular SiNW embedded in Al<sub>2</sub>O<sub>3</sub>.

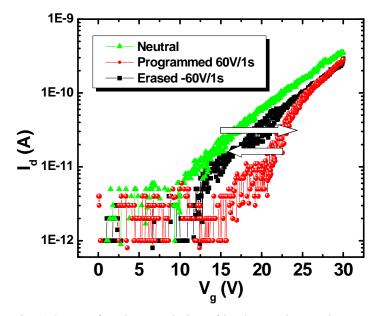

- **Figure 5.4** Transfer characteristics of back-gated non-planar nano-floating gate memory at neutral, programmed and erased states.

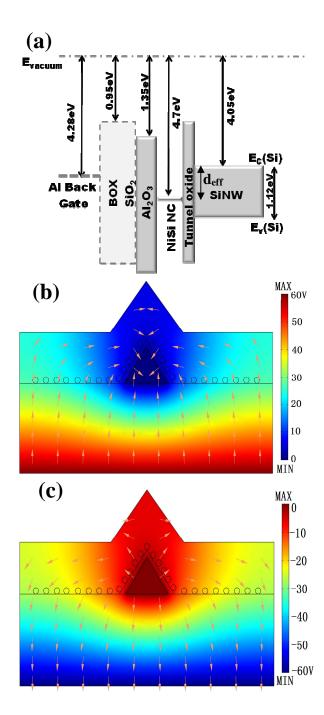

- **Figure 5.5** (a) Equivalent energy band diagram of back-gated non-planar nanofloating gate memory, work function of NiSi~4.7eV; (b) Fringing electrical field direction during programming; (c) Fringing electrical field direction during erasing.

- **Figure 5.6** Programming/Erasing characteristics of back-gated non-planar nano-floating gate memory under varied gate bias.

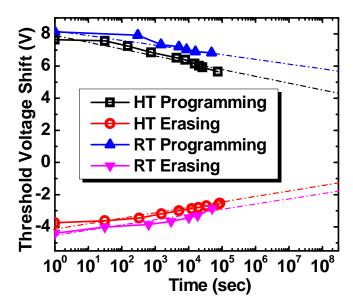

- **Figure 5.7** Room-temperature and high-temperature retention properties of backgated non-planar nano-floating gate memory showing robust hightemperature retention performance.

#### LIST OF TABLES

- **Table 1.1**Potential of Current Prototypical and Emerging Research Memory<br/>Candidates from 2011 ITRS update.

- **Table 1.2**Cell elements of nonvolatile memories.

- **Table 1.3**2D planar NAND flash technology requirements.

- Table 3.1

Comparison of retention performance among different novel NC memory work.

#### **Chapter 1 Introduction**

#### **1.1 Semiconductor memory**

Semiconductor memory is one of the dominant memory technologies in people's daily life today and plays a key role in information storage. It is everywhere from personal computers, global positioning systems, automotives to portable consumer electronics such as cellular phones, digital cameras and tablets. Its applications embrace a variety of computer memories and portable storage devices for massive data storage, system code storage and other embedded solutions.

There are many ways to classify semiconductor memory based on the technology variety and the applications. As shown in Fig. 1.1, in general, it can be categorized as volatile type and nonvolatile type. The word "volatile" here refers to the fact that the stored information cannot be maintained when the power supply is cut off. In contrast, nonvolatile memory is able to keep the memory states information and information storage mechanism.

Among volatile memories are SRAM (Static Random Access Memory) and DRAM (Dynamic Random Access Memory). SRAM offers the fastest write/erase speed among all memories. However, a single SRAM cell consists of 6 transistors, resulting in poor chip density, although 4-transistor SRAM cell has been developed. DRAM consists of one transistor and one capacitor. It is superior to SRAM in terms of its smaller cell size (lower cost per bit) and lower power consumption. But the writing speed is slower in the DRAM than in the SRAM. In addition, DRAM cell needs refreshing frequently to maintain its data, so from this point of view, the power consumption is significant. As far as scaling is concerned, the size of a DRAM cell is large and scaling the DRAM cell size down would be difficult due to the large capacitor required to store data.

Nonvolatile memory is attracting tremendous interest today because of the booming market of portable electronics. Since the very first mask-programmed ROM (Read Only Memory), it has been experiencing significant evolvement from PROM (Programmable Read Only Memory), EPROM (Erasable Programmable Read Only Memory), EEPROM (Electrically Erasable Programmable Read Only Memory) to flash memory [1], with flash memory being the most prevailing technology nowadays. During the past several decades, the family of nonvolatile memory has expanded greatly. Not only have the density, speed, power consumption and cost been improved to an unprecedented level [2, 3], but more emerging memory technologies have gotten on the stage of semiconductor industry. Table 1.1 appeared in the latest update of 2011 International Technology Roadmap for Semiconductors (ITRS) [4]. It provides an overall evaluation and comparison among prototypical and emerging research memory candidates in terms of several most important industrial criteria such as scalability, multi-level cell (MLC), 3D integration, fabrication cost and endurance. The most intriguing prototypical devices demonstrated by leading semiconductor memory companies are FeRAM (Ferroelectric RAM), STT-MRAM (spin-torque transfer magnetic RAM) and PCRAM (Phase change RAM), some of which have already been patented and even utilized in hybrid products. Other emerging memories include Redox memory, which relies on cation/anion migration and reduction/oxidation reaction to realize bistable states (e.g. resistive memory with transition metal oxide), Mott memory based on Mott insulator, nanomechanical

memory with electrically controlled mechanical switch and molecular memory employing polymer molecules for high-density storage. Among all the new technologies, while some of the candidates do show very promising performance either as prototype device (i.e. PCRAM) or in research level (i.e. Redox memory), limitations within each type of memory are also becoming more realized and there yet remains a long way to go for these innovative technologies to be mature enough for the real market.

Fig. 1.1 Classification of semiconductor memory.

Within the scope of this research, scalability is the focus and the comparison of nonvolatile memory cell elements needs to be made in order to give a clear picture of this memory group. The components of one cell for each type are shown in Table 1.2 [4]. While most of the candidates require at least one transistor and one diode/resistor as well as new materials for the cell, flash memory provides supremacy in scalability through its simplified one-transistor cell structure and robust feasibility on present CMOS platform by its Si-based process. These have been the dominating features that make flash technology unmatchable and irreplaceable in the current nonvolatile memory market.

Table 1.1 Potential of Current Prototypical and Emerging Research Memory Candidates from 2011 ITRS update

|                  | Prot  | otypical (Table El | RD3)         | Emerging (Table ERD5)     |                          |              |             |                          |                     |

|------------------|-------|--------------------|--------------|---------------------------|--------------------------|--------------|-------------|--------------------------|---------------------|

| Parameter        | FeRAM | STT-MRAM           | PCRAM        | Emerging<br>ferroelectric | Nanomechanical<br>memory | Redox memory | Mott Memory | Macromolecular<br>memory | Molecular<br>Memory |

| Scalability      | :     |                    | •            |                           |                          | <u>.</u>     | ?           | ?                        | (;)                 |

| MLC              | -     |                    | $\mathbf{C}$ |                           |                          | $\mathbf{C}$ | ?           |                          |                     |

| 3D integration   | : (   |                    |              | -                         |                          |              | ?           |                          |                     |

| Fabrication cost | •••   |                    | :            | ••                        |                          |              | ?           |                          | ?                   |

| Endurance        | :)    | $\overline{}$      | •            | <u>.</u>                  |                          |              | ••          |                          | ?                   |

|           | Scalability      | F <sub>min</sub> >45 nm         |  |  |  |

|-----------|------------------|---------------------------------|--|--|--|

|           | MLC              | difficult                       |  |  |  |

| •••       | 3D integration   | difficult                       |  |  |  |

| -         | Fabrication cost | high                            |  |  |  |

|           | Endurance        | ≤1E5 write cycles demonstrated  |  |  |  |

|           |                  |                                 |  |  |  |

|           | Scalability      | F <sub>min</sub> =10-45 nm      |  |  |  |

|           | MLC              | feasible                        |  |  |  |

|           | 3D integration   | feasible                        |  |  |  |

|           | Fabrication cost | medium                          |  |  |  |

|           | Endurance        | ≤1E10 write cycles demonstrated |  |  |  |

|           |                  |                                 |  |  |  |

|           | Scalability      | F <sub>min</sub> <10 nm         |  |  |  |

| $(\cdot)$ | MLC              | solutions anticipated           |  |  |  |

|           | 3D integration   | difficult                       |  |  |  |

|           | Fabrication cost | potentially low                 |  |  |  |

|           | Endurance        | >1E10 write cycles demonstrated |  |  |  |

|           |                  |                                 |  |  |  |

|      |         |              |                      | Mott                    | Nanomechanical             | moncuum                       |

|------|---------|--------------|----------------------|-------------------------|----------------------------|-------------------------------|

|      |         |              | 1T1R                 | 1T1R                    | 1T1R                       | 1T1R                          |

| 1T1C | 1(2)T1R | 1T(D)1R      | or                   | or                      | or                         | or                            |

|      |         |              | 1D1R                 | 1D1R                    | 1D1R                       | 1D1R                          |

|      | 1T1C    | 1T1C 1(2)T1R | 1T1C 1(2)T1R 1T(D)1R | 1T1C 1(2)T1R 1T(D)1R or | 1T1C 1(2)T1R 1T(D)1R or or | 1T1C 1(2)T1R 1T(D)1R or or or |

Table 1.2 Cell elements of nonvolatile memories

Up to date, both academia and industry have been making every effort to explore maximum possibilities out of each device, trying to bypass those technical and practical constraints and implement those claimed advantages so as to replace all or most of the existing technologies and provide a Universal Semiconductor Memory (USM). The quest for such a USM device has long been an objective for the memory communities and a huge amount of revenue is invested by those semiconductor giants. It can be expected that the reward for achieving such a device would be extremely abundant, gaining an enormous market share from computer applications to consumer electronic products in this highly competitive global memory business.

#### 1.2 Flash memory

#### **1.2.1 Cell structure and working principle**

Flash memory was invented by Dr. Fujio Masuoka at Toshiba in 1980. Over the decades it has been recognized as the most successful nonvolatile memory technology for both massive storage and embedded applications. The 1T cell structure enables ultra-high density integration, which is further enhanced by its MLC capability. Furthermore, the device fabrication process compatibility with current CMOS process is what brings this technology into real application. Fig. 1.2 shows a typical cell of flash memory. Similar to a metal-oxide-semiconductor field effect transistor (MOSFET), flash cell consists of a control gate, oxide and Si substrate, with the exception that a poly-Si floating gate layer is inserted into the oxide layer as the charge storage unit. The insertion of floating gate just requires few additional masks and minor modification of the current MOSFET process flow. Consequently, it becomes an economic and practical way to fulfill this type of memory cell and array based on the already well-developed semiconductor process platform.

Fig. 1.2 A typical flash memory cell.

Fig 1.3 shows how flash memory works by sensing the threshold voltage shift  $(\Delta V_T)$  induced by charge injection in the floating gate. The floating gate is sandwiched between two layers of oxide, namely, control oxide and tunneling oxide which serve as barriers for holding the charge injected from substrate. The stored charge imposes extra electric field on the channel, leading to  $\Delta V_T$  shown by drain current-gate voltage ( $I_{ds}$ - $V_{gs}$ ) curves at neutral, programmed and erased states. The programmed and erased states are defined as logic "0" and "1" as bistable states of this memory, usually read from  $I_{ds}$  at fixed  $V_{gs}$ .  $\Delta V_T$  is determined by the charge stored in the floating gate and also related to the capacitance of control oxide as:  $\Delta V_T$  =  $Q/C_{control}$ .

Fig. 1.3  $I_{ds}$ -V<sub>gs</sub> characteristics and V<sub>T</sub> shift of n-type flash memory at neutral, programmed and erased states.

#### 1.2.2 NAND vs. NOR

Based on how cells are organized as arrays, flash memory in production today can be divided into two dominant variants: NAND flash, in which cells are connected in series as a chain and packed with higher density for data-block storage; common ground NOR flash, which consists of parallel-connected cells and is suited for highspeed read and code storage applications. The architectures of NAND and NOR array are shown in Fig. 1.4. The organization of NAND array allows the elimination of all the contact holes between wordlines (WLs) and thus reduces the occupied area by 40% compared to NOR array [5]. This is the reason the scaling of NAND flash is always ahead of NOR flash in reality.

Fig. 1.4 NAND and NOR array architecture.

#### 1.2.3 Limitations and alternatives

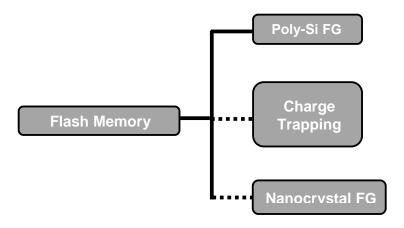

Charge-based nonvolatile memories require a media to hold charge for longterm storage. Hence it is critical that the media should be reliable enough and should also be small in geometries for the perspective of scaling. Conventional flash memory employs a continuous polycrystalline Si film as the floating gate for charge storage. As oxide layer gets thinner with scaling of cell dimensions both horizontally and vertically, the immunity of charge storage in poly-Si floating gate to oxide-defect induced leakage path gets much poorer. This is primarily due to the continuous nature of the floating gate that allows charge to move freely in the film. Hence, a local leakage path (e.g. caused by stress) can drain all the stored charge. Flash device scaling, including dimension and power consumption scaling, is seriously limited by this fact and alternatives to this continuous floating gate needs to be developed to mitigate the issue. Memory cells with discrete charge storage units instead of continuous floating gate were proposed, among which are charge-trapping memory and nanocrystal floating gate memory, as illustrated in Fig. 1.5 by the dashed lines. Charge trapping memory technology was first conceptualized through the invention of the metal-nitride-oxide-semiconductor (MNOS) transistor by H. A. R. Wegener in 1967 [6] and then was developed into silicon-oxide-nitride-oxide-silicon (SONOS). This type of memory utilizes the traps in nitride layer to store charge, alleviating the problem in conventional flash up to a point. Nonetheless, the randomness of traps in nitride becomes the drawback when it comes to the controllability of charge storage. The other type of alternative with discrete charge storage nodes is nanocrystal floating gate memory, which is discussed in detail in the next part.

Fig. 1.5 Alternatives to poly-Si floating gate memory.

#### **1.3 Nanocrystal floating gate memory**

#### **1.3.1 Basic device concepts**

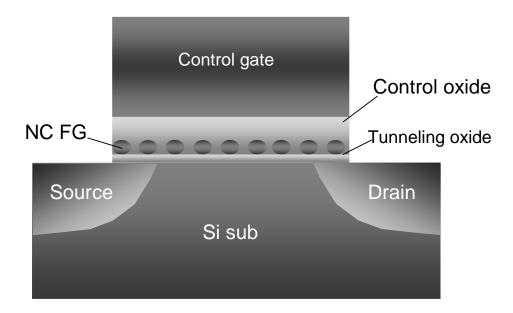

To substitute for continuous poly-Si floating gate, it was proposed that discrete nanocrystals (NCs) could be used as charge storage layer [7], as shown in Fig. 1.6. When control gate is biased, charges tunnel through the thin oxide layer and get trapped in the NCs. In this case, charges are confined within NCs of around several nanometers in size and cannot move horizontally. The amount of charge that NCs can hold is determined by density of states in the NCs as well as coulomb blockade effect [8].

Fig. 1.6 Nanocrsytal floating gate memory cell.

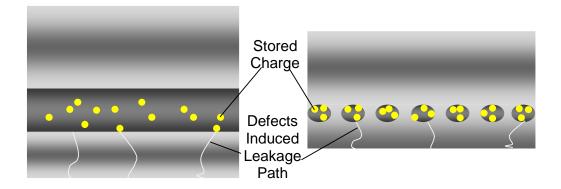

As is mentioned in previous section, the immunity of charge storage to tunnel oxide leakage is severely limited by the continuous nature of poly-Si floating gate in conventional flash memory, which also puts constraints on scalability of the device. In contrast, as shown in Fig. 1.7, localized oxide leakage path caused by process defects or stress may drain the charge kept in single NC that is touching the defects while other NCs in the same cell can still maintain the charge for cell state assurance. In this way, prolonged retention performance can be expected and thinner tunneling oxide can be adopted for this structure, leading to improved scalability and reduced power consumption. Furthermore, compared to charge-trapping type memory, it is feasible to control the ordering of charge storage sites by various NC deposition techniques, enabling further cell size scaling and enhancing reliability of the MLC features.

Fig. 1.7 Comparison of immunity to leakage between conventional flash cell and NC memory cell.

#### 1.3.2 Current status

Si NC floating gate memory has been heavily explored not only in academic research but also for real-market applications by semiconductor companies. Freescale (formerly Motorola Semiconductor) successfully pioneered the use of nanocrystals in memory devices in March 2003, and discussed the demonstration of its first-of-itskind 4-Mbit nanocrystal memory device at the December 2003 IEEE International Electron Devices Meeting (IEDM) [9]. Later on in 2005, it started manufacturing 24-Mbit memory array based on Si NCs using their 90 nm CMOS bulk technology, aimed at automotive market [10]. Continued efforts have been invested for scaling this technology down to 65nm and further.

In the meantime, people are seeking to improve this device through various NC deposition techniques and NC material/structure engineering. NC deposition techniques such as low pressure chemical vapor deposition (LPCVD) [9, 11], molecular beam epitaxy (MBE) [12], ion implantation and subsequent hightemperature annealing [13] have been extended to the synthesis of NC floating gate. Memory devices with high nanocrystal density and good performance have been demonstrated based on these techniques. NCs of different materials such as Ge and other semiconductors [14], metal, metallic silicide and metal-like material [15-20], dielectrics [21, 22] have been adopted for device performance improvement, i.e. larger memory window, higher writing/erasing speed, longer retention and better cycling performance. Band structure engineering has also been conducted by novel NC structure development. For instance, Ge/Si hetero-nanocrystal structure was proposed for good retention while maintaining high writing/erasing efficiency [23]; Core-shell nanocrystals with metal core and high-k dielectric shell and double-layered NCs have been proven as excellent potential solutions to retentionprogramming/erasing trade-off [25, 26].

#### **1.3.3** Perspective and challenges of scaling

Flash technology has been scaling aggressively. In particular, many companies dealing with NAND flash, including Samsung, Micron, Toshiba, have announced 20nm products by 2012. But if one takes a look at the 2D planar NAND flash technology requirements from ITRS 2011 updates (Table 1.3), scaling will not always be so optimistic. The slowing down pace of NAND flash scaling on cell size, tunnel oxide and inter-poly dielectric thickness and the rigorous requirements on device performance imply that this technology is also inevitably approaching the ultimate limit.

| A. 2D Planar NAND Flash (Floating                                       |         |         |         |         |              |              |         |         |

|-------------------------------------------------------------------------|---------|---------|---------|---------|--------------|--------------|---------|---------|

| Gate (FG) or Charge Trapping (CT))                                      |         |         |         |         |              |              |         |         |

| year of production                                                      | 2011    | 2012    | 2013    | 2014    | 2015         | 2016         | 2017    | 2018    |

| Planar (2D) NAND Flash uncontacted                                      | 22      | 20      | 18      | 17      | 15           | 14           | 13      | 12      |

| poly 1/2 Pitch (nm)                                                     | "       | 20      | 10      |         | 15           |              | 19      | 12      |

| Cell size – area factor a in multiples of                               | 4.0/1.3 | 4.0/1.3 | 4.0/1.3 | 4.0/1.3 | 4.0/1.3      | 4.0/1.3      | 4.0/1.3 | 4.0/1.3 |

| F2 SLC/MLC [5]                                                          |         |         |         |         |              |              |         |         |

| Tunnel oxide thickness (nm) [6]                                         | 6-7     | 6-7     | 6-7     | 6-7     | 6-7          | 5-6          | 5-6     | 5-6     |

| Interpoly dielectric material [7]                                       | ONO     | ONO     | ONO     | ONO     | ONO          | ONO          | High-K  | High-K  |

| Interpoly dielectric thickness (nm)                                     | 10-13   | 11      | 11      | 10      | 10           | 9            | 9       | 9       |

| Gate coupling ratio (GCR) [8]                                           | 0.6     | 0.6     | 0.6     | 0.5-0.6 | 0.5-0.6      | 0.5-0.6      | 0.5-0.6 | 0.5-0.6 |

| Control gate material [9]                                               | n-poly  | n-poly  | n-poly  | n-poly  | n-poly/Metal | n-poly/Metal | Metal   | Metal   |

| Highest W/E voltage (V) [10]                                            | 17-19   | 15-17   | 15-17   | 15-17   | 15-17        | 15-17        | 15-17   | 15-17   |

| Endurance (erase/write cycles) [11]                                     | 1.E+04  | 1.E+04  | 1.E+04  | 1.E+04  | 1.E+04       | 1.E+04       | 5.E+03  | 5.E+03  |

| Nonvolatile data retention (years) [12]                                 | 10      | 10      | 10      | 10      | 10           | 10           | 10      | 10      |

| Maximum number of bits per cell<br>(MLC) [13]                           | 3       | 3       | 3       | 3       | 3            | 3            | 3       | 3       |

| A. 2D Planar NAND Flash (Floating<br>Gate (FG) or Charge Trapping (CT)) |         |         |         |         |              |              |         |         |

| year of production                                                      | 2019    | 2020    | 2021    | 2022    | 2023         | 2024         | 2025    | 2026    |

| Planar (2D) NAND Flash uncontacted                                      | 2019    | 2020    | 2021    | 2022    | 2025         | 2024         | 2025    | 2020    |

| poly 1/2 Pitch (nm)                                                     | 11      | 10      | 9       | 8       | 8            | 8            | 8       | 8       |

| Cell size – area factor a in multiples of<br>F2 SLC/MLC [5]             | 4.0/1.3 | 4.0/1.3 | 4.0/1.0 | 4.0/1.0 | 4.0/1.0      | 4.0/1.0      | 4.0/1.0 | 4.0/1.0 |

| Twnnel oxide thickness (nm) [6]                                         | 5-6     | 5-6     | 5-6     | 5-6     | 5-6          | 5-6          | 5-6     | 5-6     |

| Interpoly dielectric material [7]                                       | High-K  | High-K  | High-K  | High-K  | High-K       | High-K       | High-K  | High-K  |

| Interpoly dielectric thickness (nm)                                     | 8       | 8       | 8       | 8       | 8            | 8            | 8       | 8       |

| Gate coupling ratio (GCR) [8]                                           | 0.5-0.6 | 0.5-0.6 | 0.5-0.6 | 0.5-0.6 | 0.5-0.6      | 0.5-0.6      | 0.5-0.6 | 0.5-0.6 |

| Control gate material [9]                                               | Metal   | Metal   | Metal   | Metal   | Metal        | Metal        | Metal   | Metal   |

| Highest W/E voltage (V) [10]                                            | 15-17   | 15-17   | 15-17   | 15-17   | 15-17        | 15-17        | 15-17   | 15-17   |

| Endurance (erase/write cycles) [11]                                     | 5.E+03  | 5.E+03  | 5.E+03  | 5.E+03  | 5.E+03       | 5.E+03       | 5.E+03  | 5.E+03  |

| Nonvolatile data retention (years) [12]                                 | 10      | 10      | 10      | 10      | 10           | 10           | 10      | 10      |

| Maximum number of bits per cell<br>(MLC) [13]                           | 3       | 3       | 4       | 4       | 4            | 4            | 4       | 4       |

|                                                                         |         |         |         |         |              |              |         |         |

Table 1.3 2D planar NAND flash technology requirements

3D non-planar technology is one of the viable ways to extend this technology to further nodes and is currently under intensive research, development and optimization. On the other hand, to explore the possibilities of NC memory as a replacement and realize the so-claimed superiorities of this device becomes more attractive.

In order for successful scaling of NC floating gate memory, the most critical part lies in obtaining NCs of high density and supreme uniformity. This can be intuitive. The device relies on NCs to store charge and fulfill its functionality. As miniaturization of device dimensions proceeds, the erasing/writing performance non-uniformity and variable memory windows of different devices on the same chip arise as an issue due to the increased sensitivity of performance to floating dot density variation. As a result, understanding towards NC growth behaviors needs to be furthered for better control over NC deposition techniques, Moreover, new materials and cell structures are a necessity for future technology nodes promotion.

#### 1.4 Motivation of this research

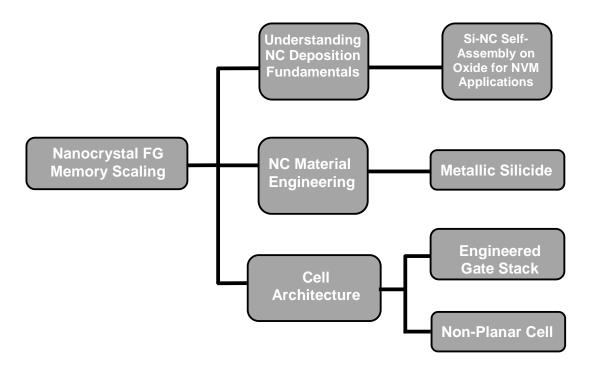

The motivation of this research is to enhance the understanding on NC floating gate memory device from both material and cell point of view through theoretical and experimental efforts. It is also to investigate and demonstrate novel NC memory devices to assist the implementation of future flash candidates.

The main tasks of this research are summarized in Fig. 1.8:

1) To reveal underlying physical fundamentals of Si NCs deposition on patterned oxide substrate and cast light on robust NC layer synthesis. The effect of oxide substrate morphology on NC self-assembly is investigated experimentally. Observation of strain-less directed self-assembly of Si NCs is addressed by building a simplified physical model and performing theoretical calculation.

2) NC layer engineering: metallic silicide NC deposition through varied deposition techniques and processes (i.e. LPCVD, gas source MBE) to achieve high density NC layer with supreme uniformity.

3) Memory cell architecture engineering: perform band structure engineering and introduce novel gate stack by using high-k material to form double-barrier structure for improved memory performance; demonstrate a proof-of-concept non-planar NC memory device by using triangular-shape Si nanowire array and single nanowire as channel for alleviating NC density fluctuation issue and extending NC memory scaling limit.

Fig. 1.8 Engineering NC floating gate memory scaling.

#### References

[1] S. Asai, Proceedings of the IEEE, vol. 74, no. 12, pp. 1623-1635 (1986).

[2] K. Kim, G. Koh, 7th International Conference on Solid-State and Integrated Circuits Technology, vol. 1, pp. 662-667 (2004).

[3] C. H. Lam, IEEE Conference on Electron Devices and Solid-State Circuits, pp. 327-331 (2005).

[4] www.itrs.net.

[5] Palo Pavan, Roberto Bez, Perro Olivo and enrico Zanoni, Proceedings of the IEEE, vol 85, No. 8, (1997).

[6] H.A.R.Wegener, et al. IEDM (International Electron Device Meeting) Technical Digest (1967).

[7] S. Tiwari, F. Rana, K. Chan, H. Hanafi, W. Chan, D. Buchanan, IEDM Technical Digest. p. 521-524 (1995).

[8] Ilgweon Kim, Sangyeon Han, Kwangseok Han, Jongho Lee and Hyungcheol Shin,Jpn. J. Appl. Phys., vol. 40, pp. 447-451 (2001).

[9] R. Muralidhar, et al., IEDM Tech. Dig., pp. 601-604, (2003).

[10] http://media.freescale.com/.

[11] Y. Zhu, B. Li, and J. L. Liu, J. Appl. Phys. 101, 063702 (2007).

[12] A. Nylandsted Larsen, A. Kanjilal, J. Lundsgaard-Hansen, P. Gaiduk, P. Normand, P. Dimitrakis, D. Tsoukalas, N. Cherkashin, A. Claverie, Mater. Res. Soc. Symp. Proc. vol. 830 (2004).

[13] Kaori Masuda, Masahiro Yamamoto, Masatoshi Kanaya and Yoshihiko Kanemitsu, Journal of Non-Crystalline Solids, Vol. 299-302, Part 2, 1079-1083 (2002).

[14] Q. Wan, C. L. Lin, W. L. Liu, and T. H. Wang, Appl. Phys. Lett., vol. 82, pp.4708–4710 (2003).

[15] Z. T. Liu, C. Lee, V. Narayanan, G. Pei, and E. C. Kan, IEEE Trans. Electron Devices, vol. 49, no. 9, pp. 1606–1613, (2002).

[16] C.H. Lee, J. Meteer, V.Narayanan, and E. C. Kan, J. Electron. Mater., vol. 34, pp. 1–11 (2005).

[17] J. J. Lee and D. L. Kwong, IEEE Trans. Electron Devices, vol. 52, no. 4, pp. 507–511 (2005).

[18] Bei Li, and Jianlin Liu, J. Appl. Phys. 105, 084905 (2009).

[19] Bei Li, Jingjian Ren and Jianlin Liu, Appl. Phys. Lett. 96, 172104 (2010).

[20] S. Choi, S. Kim, M. Chang, H. Hwang, S. Jeon, and C. Kim, Appl. Phys. Lett., vol. 86, pp. 123110-1–123110-3 (2005).

[21] J. H. Chen, W. J. Yoo, D. S. H. Chan, and L. J. Tang, Appl. Phys. Lett., vol. 86, pp. 073114-1–073114-3 (2005).

[22] Y. H. Lin, C. Chien, C. Lin, C. Chang, and T. Lei, IEEE Electron Device Lett., vol. 26, no. 3, pp. 154–156, (2005).

[23] Bei Li, Jianlin Liu, G. F. Liu, and J. A. Yormoff, Appl. Phys. Lett. 91, 132107(2007).

[24] Huimei Zhou, James A. Dorman, Ya-Chuan Perng, Stephanie Gachot, Jian-GuoZheng, Jane P. Chang, and Jianlin Liu, Appl. Phys. Lett. 98, 192107 (2011).

[25]R. Ohba, N. Sugiyama, K. Uchida, J. Koga, and A. Toriumi, IEEE Trans. Electron Devices, vol. 49, no. 8, pp. 1392–1398 (2002).

[26] C. Lee, A. Gorur-Seetharam, and E. C. Kan, IEDM Tech. Dig., pp. 557–560, (2003).

## Chapter 2 Strain-less Directed Self-assembly of Si Nanocrystals on Patterned SiO<sub>2</sub> Substrate

#### **2.1 Introduction**

As electronic devices scale down, it becomes more and more technically challenging to continue miniaturization of semiconductor nanostructures relying on lithography only. Alternatively, self-assembly is of significant interest to both academic research and industrial applications due to the potential of getting ordered nanostructures at ultra-scaled regime. Both experimental and theoretical efforts have been invested extensively into study of growth of group III-V and group IV quantum dots (QDs) or islands on single-crystalline substrates[1-5], aiming at exploring predictable and well-controlled QD growth with supreme spatial uniformity and understanding the underlying physical mechanism. Perfect self-alignment of Ge QDs on Si ridge [6-10], SiGe QDs on lithographically patterned Si substrate [11] and InAs QDs on GaAs plateau [12-13] were reported by many groups and different models were built to address the directed nucleation effect of strained islands [10-11, 14,15].

#### 2.2 Motivation

Mediated by a substrate morphology induced strain relaxation mechanism, so far, most practices of directed self-assembly of islands have been towards strained islands on patterned substrates. However, unstrained islands growth on amorphous substrate such as  $SiO_2$  is also of great importance because of modern electronic device demands. Among many applications, one example is metal-oxide-semiconductor structure based nanocrystal floating gate memories [16], which require high-density ultra-uniform metallic or semiconductor NCs on oxide surface to circumvent device performance variability issue. Thus, identifying a growth mechanism that will lead to a "strain-less" directed self-assembly of NCs in V-W mode on oxide substrates is of both scientific interest and technological significance. One intriguing question is how NCs grow on patterned oxide substrate and whether the non-planar surface morphology can direct NCs self-assembly in the absence of strain.

In this work, we present our experimental observations of preferential nucleation and growth of Si NCs on patterned  $SiO_2$  substrate, showing direct evidence of strainless directed self-assembly. The growth condition dependence of this preferential growth effect is studied. A simple two-dimensional (2D) model is developed and calculation is performed in terms of the energetics associated with V-W island growth on the patterned substrate, to explain these interesting experimental findings.

#### **2.3 Experiments**

#### 2.3.1 Substrate preparation

Substrates for Si NCs growth were prepared as shown in the process flow in Fig.2.1 (a). E-beam lithography was employed to pattern the resist on pre-cleaned ptype Si (100) substrates. Cr was evaporated in a high-vacuum e-beam evaporation system. This was followed by a lift-off process to form hard-mask as shown in the schematic for subsequent wet etching step. KOH anisotropic wet etching was performed on the samples and well-defined quasi-triangular- and pit-shaped patterns were achieved. After organic contaminants and metal residue cleaning and native oxide removal, samples were immediately transferred into an oxide furnace for dry oxidation. 5nm thermal oxide on the surface of the pit-shaped substrates was formed

Fig. 2.1 (a) Process flow of substrate preparation; (b) SEM images of well-defined quasi-triangular- and pit-shaped patterns.

at 950°C with clean and flat surface. The large-area and magnified patterns are shown in the scanning electron microscopy (SEM) images in Fig.2.1 (b).

#### 2.3.2 Si nanocrystal deposition

Chemical vapor Si NCs deposition technology has been explored and developed for NC memory applications and silicon crystallites with nanometer size can be reliably obtained by controlling the early stages of Si film growth [16-19]. In our experiments, Si NCs growth was performed on the patterned substrates in a low pressure chemical vapor deposition (LPCVD) system with split growth conditions. During the growth, SiH<sub>4</sub> was used as Si precursor and the flow rate was fixed at SiH<sub>4</sub>:N<sub>2</sub>=20sccm:100sccm and pressure at 0.5torr for all the samples. Growth temperature and growth time were chosen as the parameters to be tuned for condition split study of nucleation and growth behavior of NCs. Temperature is believed to be directly related to the energy gained by adatoms during growth, which is critical in determining the migration behavior and nucleation barrier. Different growth time shows the evolvement of Si dots nucleation and growth and allows one to see a clear picture of NC growth process during different stages.

## 2.3.2.1 Deposition temperature-dependent nucleation and growth behavior

Fig. 2.2 shows SEM images of temperature-dependent Si NCs nucleation and growth behavior on pit-shaped patterns. Samples were grown under six different temperatures from 650°C to 575°C with the same growth time of 8 sec. To monitor temperature effect on the early-stage nucleation and growth behavior of NCs, short

growth time was used and NCs with very small sizes were synthesized. Despite the tiny size of NCs (5-10nm), SEM was able to capture the morphology of NCs after growth and qualitatively show the segregation and NC density variation. From high temperature to low temperature, a clear trend of dot density and size decreasing is observed. Interestingly, while under higher temperatures of 650°C, 630°C and 615°C no obvious dot density variation between the wall (planar area) and the trench (concave area) is found, dot segregation in the trench is observed for lowertemperature samples at 600°C, 590°C and 575°C, with more NCs gathering in this concave part of the substrate than in other parts. This phenomenon is attributed to the preferential nucleation of NCs in the trench due to lower NC formation energy induced primarily by the substrate morphology. The fact of the enhanced stress of oxide substrate in this part making the chemical bonds here more reactive for nucleation also contributes to this effect [19, 20]. In the particular temperature range of 575°C-600°C, adatoms adsorbed to the sample surface move around and find most energy-favorable sites (the concave parts of the substrate) to settle down as nuclei for later NC growth. Afterwards, more adatoms segregate to the nuclei and NCs preferentially form in the trench.

Among the three temperatures, 590°C is the one under which the best preference occurs, with NCs selectively aligned along the trench and almost no dots found on other area outside the trench. This can be considered a consequence of the competition between adatoms surface migration and reaction with substrate atoms (nucleation). At lower temperature of 575°C, some NCs form on the planar surface due to insufficient energy gained by the adatoms at lower temperatures and the limited migration. Similarly, for samples grown at temperatures below 575°C, although low NC formation energy locations (trenches) are available, the energy supplied to adatoms is not enough for them to overcome migration barrier and reach the energy-favorable sites. Therefore, no directed self assembly behavior was found. On the other hand, at higher temperature of 600°C, the nucleation and growth process is accelerated. Si NC deposition rate is so high that later-stage random nucleation starts covering the directed self-assembly effect at earlier stage. This is intuitive because as earlier-formed NCs fill in the trench, low-energy sites for nucleation are occupied and the effect of substrate morphology on the nucleation and growth of NCs becomes weaker and weaker. Preferential nucleation is then replaced by continuous

Fig. 2.2 SEM images of temperature-dependent Si NCs nucleation and growth.

random NCs deposition on the whole sample surface at later stage with no or a small limitation in the number of nucleation sites [21]. This situation is more pronounced for even higher temperatures, as mentioned above, where almost no sign of preference can be observed from the images. In fact, it is expected that even on samples where directed self-assembly is observed, with longer growth time this effect would eventually be covered by subsequent random NC formation. This is confirmed by the growth time-dependent growth experiments in this work.

It should also be mentioned that a series of NCs growth with split conditions was also carried out on substrate with quasi-triangular shaped patterns, with SEM images of selective samples shown in Fig. 2.3. Similar directed self-assembly was not observed at either convex parts (i.e. the intersection of (111) and (100) planes as marked by the white arrows) or planar parts of the substrates in our experiments.

Fig. 2.3 SEM images of Si NC growth on quasi-triangular shaped patterns: (a) 650 °C, 8sec; (b) 600 °C, 30sec; (c) 600 °C, 15sec; (d) 580 °C, 60sec.

#### 2.3.2.2 Deposition time-dependent nucleation and growth behavior

The growth time dependence of Si NCs deposition on patterned concave substrate surface is shown in Fig. 2.4. These SEM images present clear surface evolvement of NC samples with growth time at three temperatures (575°C, 590°C and 600°C). At the initial stage (with growth time of 8sec), three samples show different levels of directed self-assembly. As growth time increases, an increase of dot density and size is noticeable and directed NC formation is covered with dots showing up at locations other than the concave trench. In line with the discussion above, this is because of the occupation of energy-favorable nucleation sites by NCs that offsets the morphology-induced NC formation energy difference among concave, flat and convex areas.

Fig. 2.4 SEM images of the growth time dependence of Si NCs growth on patterned substrate surface to show the evolvement of NC deposition process at different stages.

The growth condition splits for all the samples are summarized in Fig. 2.5, with X-axis standing for growth temperatures and Y-axis representing growth times. As highlighted in red, the temperature range of  $575^{\circ}C\sim600^{\circ}C$  is found to be a temperature window allowing for observation of directed Si NC self-assembly on concave substrate surface, under the given experimental configurations. In other words, samples with oxide thickness of 5nm grown under pressure of 0.5torr and precursor flux of SiH<sub>4</sub>:N<sub>2</sub>=20sccm:100sccm show preferential nucleation behavior at these temperatures using growth duration of 8sec. This window could vary with oxide thickness, pressure and gas source flux. Note that although from an energy point of view, higher temperatures provide adatoms with higher energy to migrate on substrate and promote directed self-assembly, the whole nucleation and growth process occurs

Fig. 2.5 Summary of growth condition splits and the temperature window for Si NCs preferential growth on concave oxide substrate surface with  $t_{ox}$ =5nm (temperature window: T =575°C~600°C; gas pressure P=0.5torr, gas flux= SiH<sub>4</sub> 20sccm:N<sub>2</sub> 100sccm)

much faster, leading to difficulty in capturing the effect of interest at earlier stage. Growth conditions need to be tuned carefully in order to reveal this behavior.

## 2.4 Modeling

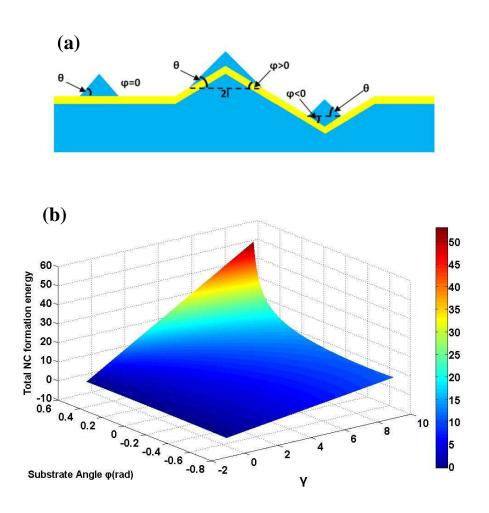

Different from previously reported self-alignment of semiconductor islands (Ge on Si, InAs on GaAs, etc.), in this case of NC growth on amorphous substrate (e.g. Si NC on SiO<sub>2</sub>), another growth mode, i.e. Volmer-Weber (V-W) mode, is involved, in which no wetting of the substrate happens and NC (3D island) nucleation and growth happen from the very beginning. To formulate the theory of NC nucleation on nonplanar substrate in this mode, we first consider a 2D model of the NC-patterned substrate system. As shown in Fig. 2.6 (a), this model consists of saw tooth-shaped substrate (thin thermal  $SiO_2$  layer on top of patterned Si substrate) and NCs with constant size (area). The shape of NC is assumed as surface-faceted for simplicity. Three different types of substrate surface morphology are configured, namely, planar, convex and concave, with substrate angle  $\varphi=0, \varphi>0, \varphi<0$ , respectively.  $\theta$  denotes the surface angle of NC and 2l is the width of the NC covering the substrate. In this model surface and interface energy are considered to be dominant factors in determining NC nucleation and no strain relaxation energy term is introduced in the calculation [23-24]. In addition, since this growth mode normally involves material growth on foreign substrate, an interface energy term is included into the total surface energy change of the system. Consequently, the total NC formation energy can be written as:

$$E_{surf} = E_{surf-NC} + E_{int} - E_{surf-sub} = 2l\gamma_{NC} \left(\sec\theta + \frac{\gamma_{int} - \gamma_{sub}}{\gamma_{NC}} \sec\varphi\right)$$

$$= 2\gamma_{NC} \left(\sec\theta + \frac{\gamma_{int} - \gamma_{sub}}{\gamma_{NC}} \sec\varphi\right) S^{1/2} (\tan\theta - \tan\varphi)^{-1/2} \quad (1)$$

Where  $E_{surf-NC}$  is the surface energy of the NC,  $E_{int}$  is the interface energy of the interface between the two materials, and  $E_{surf-sub}$  is the surface energy of the substrate covered by NC;  $\gamma_{NC}$ ,  $\gamma_{int}$ ,  $\gamma_{sub}$  are the surface energy density of NC, interface and substrate, respectively; *S* is the NC area in 2D model.

From equation (1), it can be seen that for fixed *S* and  $\theta$ , the total NC formation energy is a function of the non-dimensional system parameter  $\gamma = (\gamma_{int} - \gamma_{sub})/\gamma_{NC}$ , and substrate angle  $\varphi$ . To reveal how total NC formation energy varies with different substrate morphologies and  $\gamma$ , we examined the dependence of  $E_{surf}$  on  $\varphi$  and  $\gamma$  with  $\theta$  fixed at 30° as an example, as shown in Fig. 2.6 (b). In general, the surface contact angle of QD ( $\theta$ ) can have a size dependence even in V-W mode due to edge effect as shown by previous theory [22] and experiments [21]. Here the value is chosen as a representative case just to show the overall trend of the effect of substrate morphology on NC nucleation behavior.  $\gamma$  is an intrinsic parameter related to the nature of the two materials in the system and in different growth modes it holds different value ranges. In V-W mode,  $\gamma_{NC} + \gamma_{int} > \gamma_{sub}$  or  $\gamma >-1$  is satisfied. Substrate angle  $\varphi$  is investigated within the range  $-45^\circ < \varphi \le 28^\circ$  to meet the restriction that  $\varphi \le \theta$ . From the 3-D plot it should be noticed that  $E_{surf}$  increases with the value of  $\gamma$ , qualitatively indicating the fact that the larger this system parameter is, the higher NC formation energy is hence the harder it is for NC to form. Under different  $\gamma$ , the changing trend of  $E_{surf}$  with  $\varphi$  varies. In most cases,  $E_{surf}$  decreases monotonously with  $\varphi$  decreasing from positive regime to negative regime, suggesting that lower NC formation energy is needed for negative substrate angle (concave) compared to zero (flat) and positive (convex) substrate angle.

Fig. 2.6 (a) Two-dimensional model of NC-patterned oxide substrate system; (b) 3-D plot of total NC formation energy as a function of substrate angle  $\varphi$  and system parameter  $\gamma$ , with the unit of energy  $2 \gamma_{NC} S^{1/2}$ .

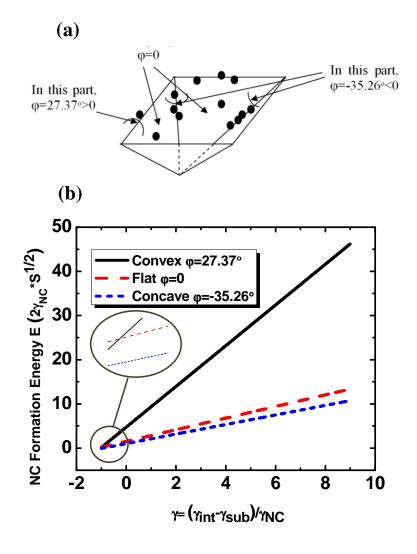

To further address the experimental results observed and illustrate the morphology effect,  $E_{surf}$  as a function of  $\gamma$  is plotted for the three types of substrate angles for comparison. Fig. 2.7 (a) shows a schematic of the patterned substrate surface utilized in the experimental part to study NC growth behavior, with  $\varphi$ =-35.26° at the concave trench of the pit,  $\varphi=0$  on the planar surface and  $\varphi=27.37^{\circ}$  at the convex edge of the pit. It can be clearly seen from Fig. 2.7 (b) that within the whole range of variable  $\gamma$ , concave substrate requires lowest NC formation energy than that for the other two cases. This result implies that concave substrate always favors the nucleation and growth of NC in V-W mode, an effect regardless of what material system is involved  $(\gamma)$  and this is in very good consistency with the experimental findings above. While over a large range of  $\gamma$  lower energy is needed in flat case than that in convex case, the magnified region of the plots in the figure shows that in certain systems the situation could be reversed, indicating a dramatic dependence of NC formation energy on material natures and interface structures. There have been experimental reports showing NC self-alignment on convex oxide surface with very fine alignment condition window [25], a proof of more energy-favored nucleation sites on convex surface over flat surface in some systems. It is worth mentioning that the simplified 2D model developed here is aimed at semi-quantitatively describing and explaining the experimental findings, focusing on the directed self-assembly behavior observed on concave surface. The range of  $\gamma$  shown in Fig. 2.7 (b), (-1, 10), is chosen mainly for illustration of this concave surface effect. Although the specific value of  $\gamma$  could not be obtained due to the amorphous nature of thermal SiO<sub>2</sub> and the unknown interface atomic structure of Si-SiO<sub>2</sub>, these calculation results provide direct

theoretical evidence to well support and address the experimental findings within the scope of this work.

Fig. 2.7 (a) Schematic of the patterned substrate surface; (b) Calculated total NC formation energy for three different types of experimental surface morphologies.

Previous theory analysis [15] has shown that strain relaxation can favor nucleation of "strained" islands at the concave region on patterned substrates in Stranski-Krastanov (S-K) growth mode. In this study, we show that the competition between surface/interface energy without strain relaxation can also favor nucleation of "unstrained" NCs at the concave region on patterned substrates in V-W growth mode. It is also interesting to note that although the "unstrained" V-W islands have no misfit epitaxial strain, they may still experience stress effects due to surface stress discontinuity at island edges as shown before [22,26], an effect deserves further study.

## 2.5 Summary

Preferential growth behavior of Si NCs on patterned SiO<sub>2</sub> substrate is found within certain experimental condition window. Simple modeling and calculation were carried out to depict the possible dominant mechanism underlying the experimental results. Different from common strain energy directed island nucleation on patterned substrate in S-K mode, the surface/interface energy directed NCs growth on amorphous thermal oxide substrate in V-W mode is relatively a weaker effect, which requires the growth parameters to be tuned more strictly for the effect to show up. This work furthers our fundamental understanding of NC growth behavior on amorphous substrate with various morphologies.

## 2.6 Acknowledgement

Most of the results in this chapter were published on Journal of Applied Physics 112, 054311 (2012). This work was sponsored by the Defense Advanced Research Projects Agency (DARPA) /Defense Microelectronics Activity (DMEA) under agreement number H94003-10-2-1003 and the National Science Foundation (NSF) DMR-0807232. The work at Utah was supported by DOE-BES (Grant number DE-FG02-04ER46148).

## References

S. Yu Shiryaev, F. Jensen, J. Lundsgaard Hansen, J. Wulff Petersen, and A. Nylandsted Larsen, Phys. Rev. Lett. 78, 503 (1997).

[2] Yoshiyuki Suda, Shuya Kaechi, Daisuke Kitayama, Taichi Yoshizawa, Thin SolidFilms 464-465, 190 (2004).

[3] Daisuke Kitayama, Taichi Yoshizawa and Yoshiyuki Suda, Jap. J. Appl. Phys. 43,6B, 3822 (2004).

[4] Olivier Guise, John T. Yates, Jeremy Levy, Joachim Ahner, Venugopalan Vaithyanathan, and Darrell G. Schlom, Appl. Phys. Lett. 87, 171902 (2005).

[5] Shyh-Shin Ferng, Tsung-Hsi Yang, Guangli Luo, Kai-Ming Yang, Ming-FengHsieh and Deng-Sung Lin, Nanotechnology 17, 5207 (2006).

[6] T. I. Kamins and R. S. Williams, Appl. Phys. Lett. 71, 1201 (1997).

[7] G. Jin, J. L. Liu, S. G. Thomas, Y. H. Luo, K. L. Wang, and Bich-Yen Nguyen, Appl. Phys. Lett. 75, 2752 (1999).

[8] Z.Y. Zhong, A. Halilovic, T. Fromherz, F. Schäffler, and G. Bauer, Appl. Phys. Lett. 82, 4779 (2003).

[9] Z.Y. Zhong, A. Halilovic, M. Mühlberger, F. Schäffler, and G. Bauer, J. Appl. Phys. 93, 6258 (2003).

[10] B. Yang, F. Liu, and M. G. Lagally, Phys. Rev. Lett. 92, 025502 (2004).

[11] Z.Y. Zhong, W. Schwinger, F. Schäffler, G. Bauer, G. Vastola, F. Montalenti and L. Miglio, Phys. Rev. Lett. 98, 176102 (2007).

[12] R. Zhang, R. Tsui, K. Shiralagi, D. Convey, and H. Goronkin, Appl. Phys. Lett.73, 505 (1998).

[13] H. Lee, J. A. Johnson, M. Y. He, J. S. Speck, and P. M. Petroff, Appl. Phys. Lett., 78, 105 (2001).

[14] G. Katsaros, J. Tersoff, M. Stoffel, A. Rastelli, P. Acosta-Diaz, G. S. Kar, G.

Costantini, O. G. Schmidt, and K. Kern, Phys. Rev. Lett. 101, 096103 (2008).

[15] Hao Hu, H. J Gao, and Feng Liu, Phys. Rev. Lett. 101, 216102 (2008).

[16] S. Tiwari, F. Rana, H. Hanafi, A. Hartstein, E. F. Crabbe, and K. Chan, Appl.Phys. Lett. 68, 1377 (1996).

[17] S. Miyazaki, Y. Hamamoto, E. Yoshida, M. Ikeda, M. Hirose, Thin Solid Films,369, 55-59 (2000).

[18] S. Jacob, B. De Salvo, L. Perniola, G. Festes, S. Bodnar, R. Coppard, J.F. Thiery,T. Pate-Cazal, C. Bongiorno, S. Lombardo, J. Dufourcq, E. Jalaguier, T. Pedron, F.Boulanger, S. Deleonibus, Solid-State Electronics, 52, 1452-1459 (2008).

[19] F. Mazen, T. Baron, G. Brémond, N. Buffet, N. Rochat, P. Mur and M. N.Séméria, Journal of the Electrochemical Society, 150, G203 (2003).

[20] D. B. Kao, J. P. McVittie, W. D. Nix, K. C. Saraswat, IEEE Trans. on Electron Devices, 34, 1008 (1987).

[21] G. Nicotra, R. A. Puglisi, S. Lombardo, C. Spinella, M. Vulpio, G. Ammendola,M. Bileci, and C. Gerardi, J. Appl. Phys. 95, 2049 (2004).

[22] F. Liu, Phys. Rev. Lett. 89, 246105 (2002).

[23] Vladimir M. Kaganer, Bernd Jenichen, Roman Shayduk, Wolfgang Braun and Henning Riechert, Phys. Rev. Lett. 102, 016103 (2009).

[24] Thin Film Materials-Stress, Defect Formation and Surface Evolution, Cambridge University Press, L. B. Freund, S. Suresh, pp. 27-33 (2004). [25] Mario Olmedo, Alfredo A. Martinez-Morales, Gang Liu, Emre Yengel, Cengiz S.Ozkan, Chun Ning Lau, Mihrimah Ozkan, and Jianlin Liu, Appl. Phys. Lett. 94, 123109 (2009).

[26] V. A. Shchukin, N. N. Ledentsov, P. S. Kop'ev and D. Bimberg, Phys. Rev. Lett.75, 2968 (1995).

## Chapter 3 High-density NiSi nanocrystals embedded in Al<sub>2</sub>O<sub>3</sub>/SiO<sub>2</sub> doublebarrier for robust retention of nonvolatile memory

#### **3.1. Introduction**