# UC Santa Cruz

**UC Santa Cruz Electronic Theses and Dissertations**

### Title

Effective Performance Analysis of Modern CPUs

### Permalink

https://escholarship.org/uc/item/00h6g45t

Author Southern, Gabriel

Publication Date 2016

## **Copyright Information**

This work is made available under the terms of a Creative Commons Attribution-NonCommercial-NoDerivatives License, available at <u>https://creativecommons.org/licenses/by-nc-nd/4.0/</u>

Peer reviewed|Thesis/dissertation

### UNIVERSITY OF CALIFORNIA SANTA CRUZ

### EFFECTIVE PERFORMANCE ANALYSIS OF MODERN CPUS

A dissertation submitted in partial satisfaction of the requirements for the degree of

### DOCTOR OF PHILOSOPHY

in

### COMPUTER ENGINEERING

by

### **Gabriel Southern**

December 2016

The Dissertation of Gabriel Southern is approved:

Professor Jose Renau, Chair

Professor Cormac Flanagan

Professor Matthew Guthaus

Professor Jishen Zhao

Tyrus Miller Vice Provost and Dean of Graduate Studies Copyright © by

Gabriel Southern

2016

# **Table of Contents**

| Li                               | st of F          | ligures                                                         | v  |

|----------------------------------|------------------|-----------------------------------------------------------------|----|

| Li                               | st of T          | Sables   vi                                                     | ii |

| Ab                               | ostrac           | t vi                                                            | ii |

| Ac                               | know             | ledgments i                                                     | X  |

| 1                                | Intro            | oduction                                                        | 1  |

| 2                                | Live             | Sim: Enabling Interactive Microarchitectural Simulation         | 7  |

|                                  | 2.1              | Introduction                                                    | 8  |

|                                  | 2.2              | Background                                                      | 2  |

|                                  | 2.3              | LiveSim Methodology                                             | 4  |

|                                  |                  | 2.3.1 Sampling Setup                                            |    |

|                                  |                  | 2.3.2 Calibration                                               | -  |

|                                  |                  | 2.3.3 LiveSample                                                | -  |

|                                  |                  | 2.3.4 LiveCI                                                    |    |

|                                  | 2.4              | Measurement Setup                                               |    |

|                                  | 2.5              | Evaluation                                                      |    |

|                                  | 2.0              | 2.5.1 Speed                                                     |    |

|                                  |                  | 2.5.2 Accuracy                                                  | -  |

|                                  |                  | 2.5.2       Accuracy       2         2.5.3       Warmup       3 |    |

|                                  |                  | 2.5.5       Walmup                                              |    |

|                                  | 2.6              | Related Work                                                    | -  |

|                                  | 2.0              | Summary                                                         |    |

|                                  | 2.1              | Summary 4                                                       | U  |

| 3 Analysis of PARSEC Scalability |                  | lysis of PARSEC Scalability 4                                   | 1  |

|                                  | 3.1 Introduction |                                                                 |    |

|                                  | 3.2              | Background                                                      | 4  |

|                                  | 3.3              | Experiment Setup                                                | 7  |

|                                  | 3.4              | Results                                                         |    |

|   |     | 3.4.1    | ROI Percentage                                      | 50 |

|---|-----|----------|-----------------------------------------------------|----|

|   |     | 3.4.2    | Maximum Speedup                                     | 52 |

|   |     | 3.4.3    | Quantifying Similarity                              | 54 |

|   |     | 3.4.4    | Measured Scalability                                |    |

|   | 3.5 | Related  | d Work                                              | 66 |

|   | 3.6 |          | ary                                                 | 68 |

| 4 | Ove | rhead of | f Deoptimization Checks in the V8 JavaScript Engine | 69 |

|   | 4.1 | Introdu  | action                                              | 70 |

|   | 4.2 | Backgi   | round                                               | 73 |

|   |     | 4.2.1    | Dynamic Languages                                   | 73 |

|   |     | 4.2.2    | V8 JavaScript Engine                                |    |

|   |     | 4.2.3    | Octane Benchmarks                                   | 77 |

|   | 4.3 | Checks   | s Categorization                                    | 78 |

|   |     | 4.3.1    | Type Checks                                         | 80 |

|   |     | 4.3.2    | Small Integer (Smi) Checks                          | 81 |

|   |     | 4.3.3    | Bounds Checks                                       | 81 |

|   |     | 4.3.4    | Overflow Checks                                     | 82 |

|   | 4.4 | Perform  | mance Evaluation                                    | 82 |

|   |     | 4.4.1    | Experiment Methodology                              | 83 |

|   |     | 4.4.2    | Experiment Setup                                    |    |

|   |     | 4.4.3    | Relative Performance                                | 87 |

|   |     | 4.4.4    | IPC                                                 | 88 |

|   |     | 4.4.5    | Branch Prediction                                   | 91 |

|   | 4.5 | Related  | d Work                                              | 93 |

|   | 4.6 | Summa    | ary                                                 | 96 |

| 5 | Con | clusion  | and Future Work                                     | 99 |

### Bibliography

103

# **List of Figures**

| 2.1  | LiveSim Timeline                     | 10 |

|------|--------------------------------------|----|

| 2.2  | Checkpoint Creation                  | 16 |

| 2.3  | CPI trace of Astar                   | 19 |

| 2.4  | LiveSim CPI error                    | 26 |

| 2.5  | Average simulation time              | 27 |

| 2.6  | CPI error distribution               | 29 |

| 2.7  | LiveCI CPI of LP architecture        | 31 |

| 2.8  | LiveCI CPI of MP architecture        | 31 |

| 2.9  | LiveCI CPI of HP architecture        | 32 |

| 2.10 | AMAT error for LiveCache             | 33 |

| 2.11 | Average error of branch prediction   | 34 |

| 2.12 | Number of samples needed             | 35 |

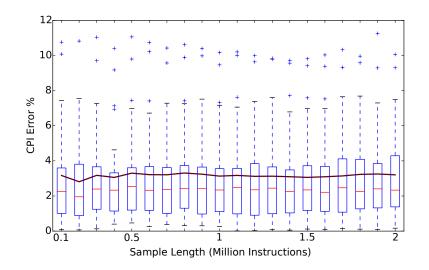

| 2.13 | Effect of sample size on CPI error   | 36 |

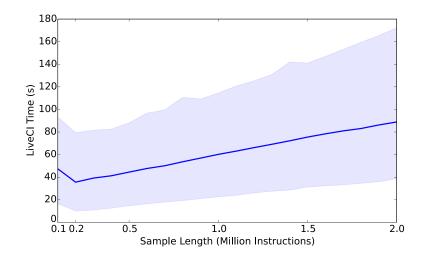

| 2.14 | Effect of sample size on LiveCI time | 37 |

| 3.1  | Blackscholes speedup comparison      | 43 |

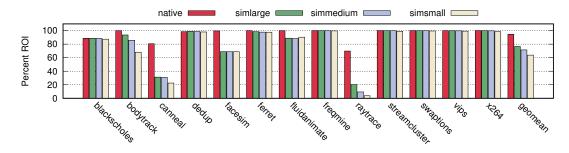

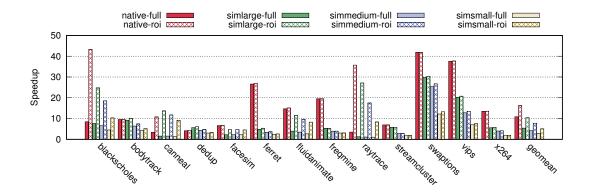

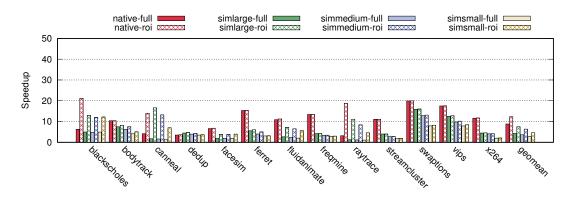

| 3.2 | Percentage of execution time in ROI                 | 49 |

|-----|-----------------------------------------------------|----|

| 3.3 | Maximum speedup on M48                              | 53 |

| 3.4 | Maximum speedup on M32                              | 53 |

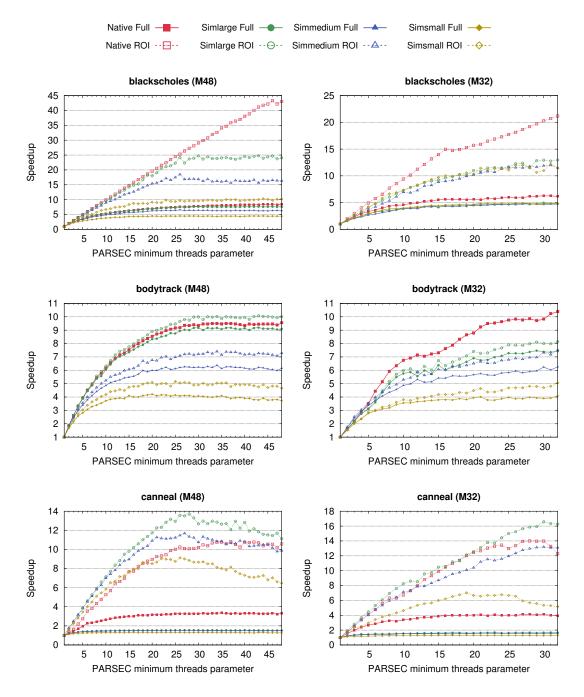

| 3.5 | Scalability of blackscholes, bodytrack, and canneal | 58 |

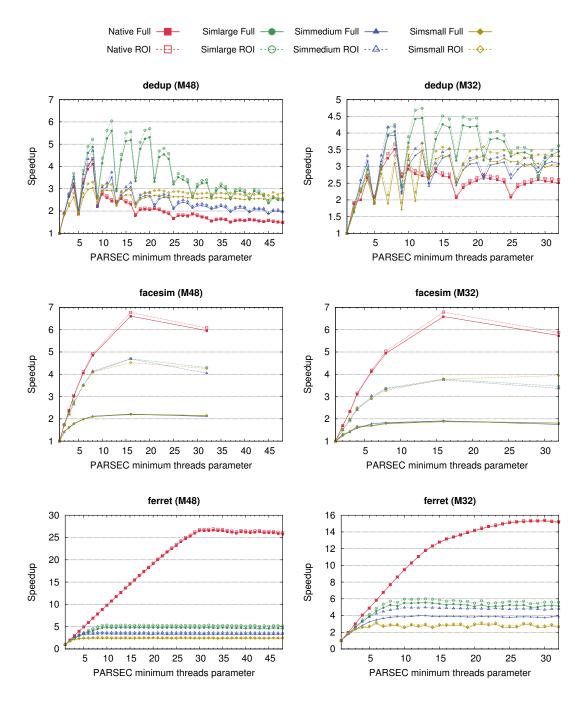

| 3.6 | Scalability of dedup, facesim, and ferret           | 60 |

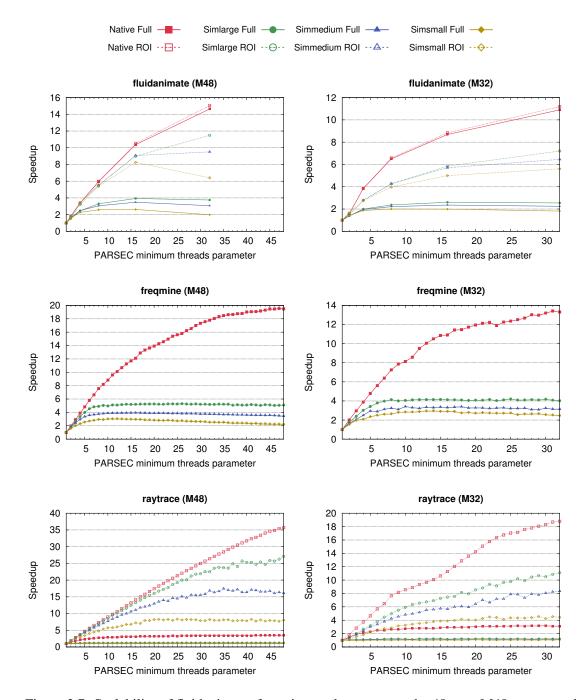

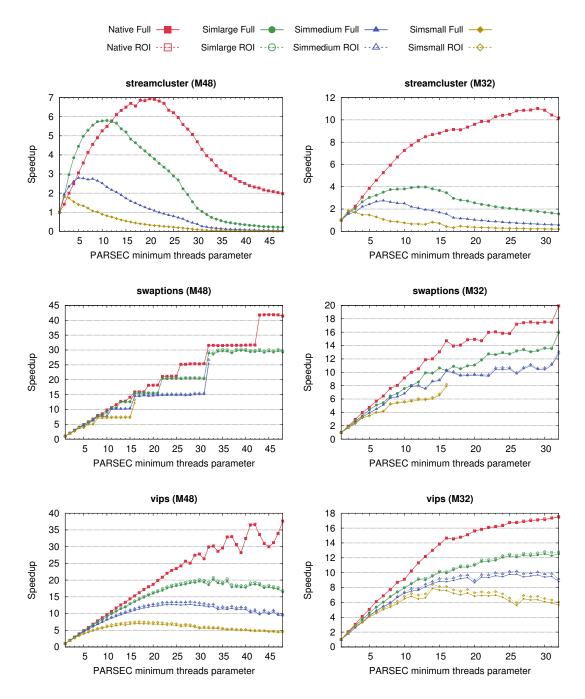

| 3.7 | Scalability of fluidanimate, freqmine, and raytrace | 63 |

| 3.8 | Scalability of streamcluster, swaptions, and vips   | 64 |

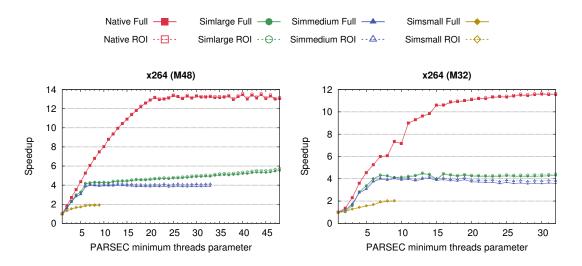

| 3.9 | Scalability of x264                                 | 66 |

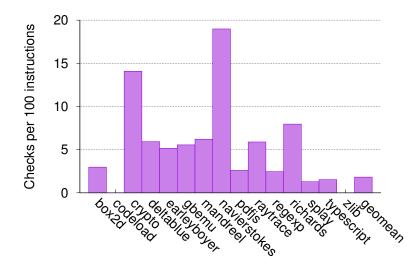

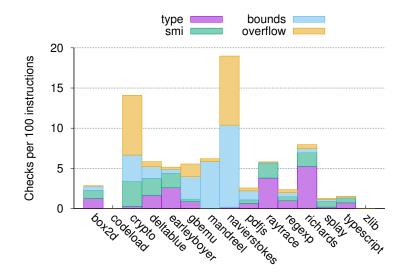

| 4.1 | Frequency of deoptimization checks                  | 72 |

| 4.2 | Frequency of deoptimization checks by category      | 80 |

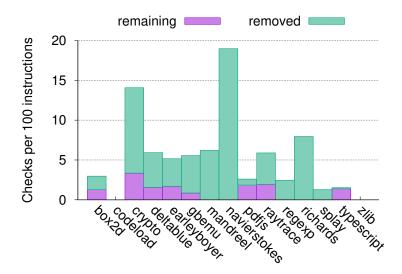

| 4.3 | Frequency of removed deoptimization checks          | 85 |

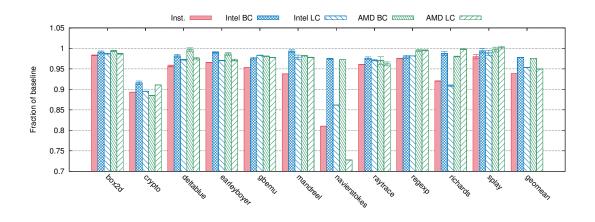

| 4.4 | Relative instruction count and execution time       | 87 |

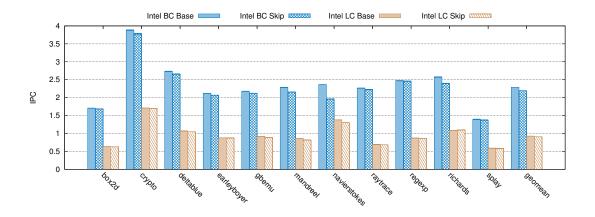

| 4.5 | Absolute IPC of Intel cores                         | 89 |

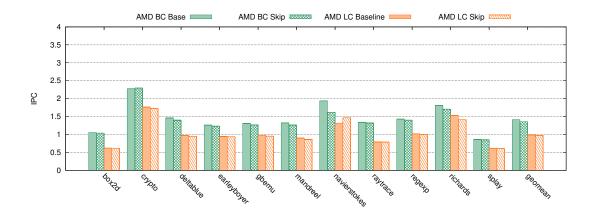

| 4.6 | Absolute IPC of AMD cores                           | 90 |

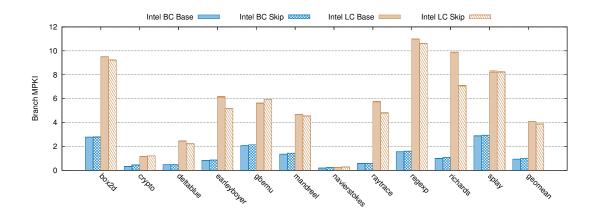

| 4.7 | Branch MPKI of Intel cores                          | 91 |

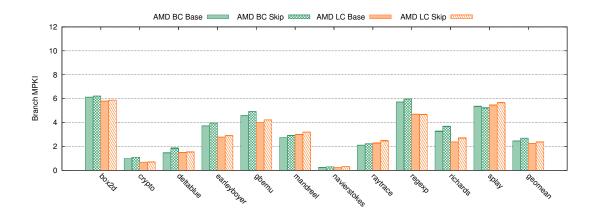

| 4.8 | Branch MPKI of AMD cores                            | 92 |

# **List of Tables**

| 2.1 | Architectures used to evaluate LiveSim         | 25 |

|-----|------------------------------------------------|----|

| 2.2 | Number of checkpoints                          | 28 |

| 3.1 | Benchmarks and threads in PARSEC               | 46 |

| 3.2 | Specifications of systems used for experiments | 48 |

| 3.3 | ROI percentage and maximum theoretical speedup | 50 |

| 3.4 | Speedup % difference: ROI and full             | 54 |

| 3.5 | Speedup % difference: Native and Simulation    | 55 |

| 4.1 | CPU Specifications                             | 86 |

#### Abstract

#### Effective Performance Analysis of Modern CPUs

by

#### Gabriel Southern

Performance analysis is a critical aspect of CPU design, but it has become more difficult during the past decade as physical constraints limit improvements in single-threaded performance. This dissertation analyzes three interrelated problems associated with effective performance analysis. First, high-level microarchitecture simulation is orders of magnitude slower than native execution. I propose a novel statistical sampling technique called LiveSim that dramatically reduces simulation time. Second, multithreaded benchmarks may use input sets that produce misleading results. I demonstrate, for the first time, the true scalability of the PARSEC benchmark suite using real multiprocessor systems, and show how to accurately evaluate the performance of simulated multiprocessor systems. Third, modern software is often written in dynamic languages, and the interaction of a JIT compiler and different CPU microarchitectures can be difficult to analyze using simulation. I modified the V8 JavaScript engine and ran benchmarks using real systems to attain statistically sound novel insights that would be difficult to attain using simulation alone. These three solutions demonstrate ways to perform effective and statistically valid microarchitectural performance analysis.

#### Acknowledgments

The pursuit of a Ph.D. is a lengthy process that provides many opportunities for professional and personal growth and I benefited greatly from my experience as a Ph.D. student. I have been fortunate to interact with and learn from numerous people while working on my dissertation and I cannot possibly thank them all, but there are a few I want to mention by name.

First and foremost I want to thank my adviser, Professor Jose Renau, for his support and mentorship over the years. Jose possess a wealth of knowledge about computer architecture and I learned an incredible amount from him about the functionality and design of microprocessors. He allowed me to explore many topics and guided me to discover my interest in performance analysis of practical systems. Jose also directed and approved the research papers published in peer-reviewed venues.

I am fortunate to have three other active researchers—Professor Cormac Flanagan, Professor Matthew Guthaus, and Professor Jishen Zhao—who agreed to serve on my dissertation committee and provided valuable feedback. I thank each of them both for their assistance with my dissertation and for the interactions I had with them in classes and seminars during my time as a Ph.D. student.

A Ph.D. dissertation focuses on the research contribution of its author, but most research in computer architecture is a collaborative effort. I was fortunate to participate in several joint research projects that resulted in peer reviewed publications.

Sina Hassani and I worked together on developing a statistical sampling technique for

fast simulation, and along with our adviser Jose Renau, we published our results at the IEEE International Symposium on High Performance Computer Architecture (HPCA) in March 2016. Sina used part of the HPCA paper as the basis of his M.S. thesis, and I have included part of it in Chapter 2 of this dissertation.

I also worked closely with Dr. Madan Das to apply static analysis techniques to reduce instrumentation overhead of dynamic analysis of multithreaded applications. We published our work in the ACM Transactions on Architecture and Code Optimizations (TACO), and Madan used much of our TACO paper as part of his own dissertation. I also worked closely with Dr. Ehsan Ardestani and Elnaz Ebrahimi in applying statistical sampling techniques to thermal simulation. We published our work at the International Symposium on Low Power Electronics and Design and in the IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems. Going through the process of having peer reviewed research papers published was invaluable for my growth as a researcher, and I thank my co-authors for the opportunity to collaborate in their research efforts.

I am grateful for my interaction with members of the Micro Architecture Santa Cruz (MASC) lab over the years including: Ehsan, Elnaz, David, Rafael, Sina, Madan, Javi, Sangeetha, Alamelu, Rigo, Daphne, Ian, Blake, Ethan, Jason, Meeta, Akash, Ramesh, Tom, and Michael.

I appreciate the support I received from my parents over the years. My father's experience as a newspaper editor, and willingness to help with proofreading, was especially helpful. Last, but not least, I appreciate my friend Sophie's support, companionship, and patience during the years I spent working on my dissertation.

# **Chapter 1**

# Introduction

Performance analysis has long been an important part of the development of CPUs. One of the earliest ways of measuring CPU performance was to simply count the number of instructions it could execute per unit time. This led to a popular performance metric of millions of instructions per second (MIPS). However, researchers discovered that this simple measurement was insufficient to give an accurate characterization of actual processor performance [37]. MIPS was insufficient because it failed to measure the complexity associated with running actual applications. It also failed to capture the relationship between instruction count, clock frequency, and time to execute an instruction.

$$\frac{time}{program} = \frac{instructions}{program} \times \frac{cycle}{instruction} \times \frac{time}{cycle}$$

(1.1)

The Iron Law—shown in Equation 1.1—did capture that relationship, and for many years it served as the most important way to evaluate proposals to improve processor perfor-

mance. Computer architects would carefully balance cycle time and the number of instructions executed per cycle (IPC) when evaluating proposed changes to architecture and microarchitecture. For many years CPU performance for single threaded applications increased at a rate similar to the rate of increase of transistors in a CPU. Much of the performance improvement was driven by the ability of computer architects to extract instruction level parallelism (ILP) from a serial instruction sequence.

However, by 2005 the physical constraints of device level physics caused clock frequency growth to stall, and increases in IPC also slowed. CPU architects determined that using all the transistors on a die for a single monolithic CPU was no longer feasible or effective.

Architects responded to constraints on ILP by integrating multiple processing elements on the same processor die. Modern CPUs are developed as a system-on-chip (SOC) with multiple CPU cores as well as GPUs and other hardware accelerators depending on the system requirements. As a result, modern CPU design requires close collaboration between software and hardware developers to maximize performance. One way to improve performance of applications running on multicore processors is by running multithreaded applications.

Today, general purpose CPUs still are designed to attain the highest possible performance within the power, thermal, and cost constraints associated with their intended use case. Designing a CPU is typically a multi-year effort, and the applications that the CPUs are designed to run might not even exist during early stages of the CPU development. However, early design decisions are often difficult or impossible to change later on. CPU architects typically develop models early in the design process to estimate expected performance of the system under development and to tune design parameters. The complex interaction between hardware and software makes this a challenging process for a variety of reasons, including:

- Applications that the CPU is designed to run may not be developed until after the CPU is designed and manufactured.

- The interaction between CPU design parameters and performance is often too complex to model analytically.

- Simulation models of CPU microarchitecture require approximation of elements of system behavior in order to make development of the simulator feasible.

- Software simulation of CPUs is orders of magnitude slower than native execution on a real system.

- Behavior of the simulated CPU may differ from the actual CPU in ways that have a significant impact on the true performance.

While modern CPUs are designed as an SOC that can execute many independent threads in parallel, single threaded performance still remains critically important. Parallel programs are more difficult to develop than single threaded applications, some algorithms are not well suited to parallelism, and existing programs need to run on new CPUs. And even in parallel application, performance of sequential sections of code can be critically important for overall application performance.

In this dissertation I analyze three related aspects of CPU performance evaluation: microarchitectural simulation time, multithreaded benchmark fidelity, and the overhead of software runtime system for dynamic languages. The analysis of simulation time considers a problem that faces architects early in the design cycle, and it proposes a novel way to speed up simulation and improve designer productivity by using statistical sampling. The other analysis of multithreaded benchmarks and dynamic languages was done using real systems to allow for measurements that considered benchmark performance without the possibility of modeling error.

Chapter 2 first surveys existing research to reduce simulation time by using statistical sampling with microarchitectural simulation. Then it presents a novel statistical sampling technique called LiveSim that reduces high-level microarchitectural simulation time from hours to seconds. The main contributions of this chapter are:

- A new architectural simulation methodology called LiveSim that enables interactive microarchitectural design space exploration.

- A demonstration of how LiveSim provides accurate results within 5 seconds.

- A demonstration of how LiveSim is able to bound simulation error within 41 seconds on average.

Chapter 3 presents an analysis of the scalability of a popular multithreaded benchmark suite named PARSEC. It carefully considers how much speedup the components of the benchmark suite attain when increasing the number of CPU cores available in a system under test. PARSEC provides features to separate the parallel portion of each benchmark from the sequential regions, which is called the region of interest (ROI). In this chapter I also analyze the impact of measuring only the ROI. The main contributions of this chapter are:

• A systematic analysis of the runtime scalability of each of the PARSEC input sets.

• A systematic analysis of the runtime scalability of the full benchmark execution compared to the ROI only.

Chapter 4 presents an analysis of the performance overhead associated with deoptimization checks used by the V8 JavaScript runtime. Its analysis is performed using four different systems with different microarchitectures. It considers how a possible optimization to reduce the overhead of dynamic languages can have a different impact depending on the CPU microarchitecture. This is increasingly relevant as modern SOCs integrate different cores in the same heterogeneous multiprocessor. The main contributions of the chapter are:

- Characterization of the performance overhead of deoptimization checks for the V8 JavaScript engine.

- Showing that performance overhead does not always correlate with instruction count, and that the specific overhead can vary dramatically depending on the CPU core microarchitecture.

- Categorizing the types and frequency of deoptimization checks and their execution frequency when executing optimized code.

Chapter 5 concludes by noting how the end of exponential increases in clock frequency has changed the types of performance analysis that computer architects need to perform. It ties together elements from the previous three chapters to illustrate the need for architects to carefully consider which parts of the software stack to model, and how to effectively use performance models early in the design cycle. It also considers how emerging trends such as heterogeneous compute, reconfigurable compute, and persistent memory will provide new challenges and opportunities for effective performance analysis.

# **Chapter 2**

# LiveSim: Enabling Interactive Microarchitectural Simulation

The first problem with effective CPU performance analysis that this dissertation considers is that of slow simulation time. Software simulation models are widely used for design space exploration and development of CPUs. Architects want to determine what the expected performance of a proposed design is before investing the immense amount of time and effort needed to design and fabricate the CPU in silicon. In this chapter I survey some of the techniques used to reduce simulation time, with a focus on applying statistical sampling to microarchitectural simulation. This chapter is based largely on the paper *LiveSim: Going Live with Microarchitecture Simulation*, which was published in the proceedings of the IEEE International Symposium on High Performance Computer Architecture in March 2016. I collaborated closely with Sina Hassani in developing and tuning the LiveSim prototype system, and in jointly writing the text of the published paper. The research was supervised and directed by our adviser Jose Renau.

### 2.1 Introduction

Computer architects are constrained by the fact that system design is a slow, expensive, and time-consuming process. To ameliorate this architects use a variety of techniques to prototype ideas and perform design space exploration. One of the most important techniques is architectural simulation, where a software model of the simulated system is developed to evaluate its performance using realistic benchmarks. Unfortunately, software simulation is many orders of magnitude slower than the real systems being designed. This limits the length of the benchmarks that can be executed, and also forces architects to wait for long periods (from minutes to days) until new simulation results are ready.

Many techniques have been developed to reduce simulation time, including benchmarks size reduction [47], specialized hardware [77], phase-based sampling [72], and statistical sampling [80]. Of these techniques, the sampling-based approaches typically provide the best trade-off between simulation fidelity, speed, and flexibility.

The state of the art simulation techniques have reduced simulation time from weeks to days or hours, but in many ways microarchitectural simulation still uses the methodology of the era of punched cards and batch queues. An architect typically first develops and configures the simulation parameters. Then the simulation is submitted to a batch queue and runs for hours or days while the architect works on something else. After the simulation finishes execution the architect must recall what she was working on, interpret the results, and then repeat the cycle with new experiments.

This methodology contrasts with the rapid development techniques popular in many types of software engineering. We expect the productivity of computer architects to improve with an interactive development environment. To support this development model we propose LiveSim, a simulation framework that provides simulation results in near real-time. In this chapter we define our near real-time goal as within 5 seconds and we use the terms live and interactive<sup>1</sup> interchangeably. LiveSim provides initial results as soon as the first sample finishes simulation, and it provides a confidence interval to bound the expected error after a minimum number of samples have executed (typically within 5 seconds on our system). If necessary, LiveSim continues simulating more samples until reaching a user-defined threshold for the confidence interval. We call the results that are updated in real-time LiveSample, and the result that is within the desired confidence interval LiveCI.

LiveSim first runs a setup phase that executes the applications in emulation only mode and creates in-memory checkpoints with architectural state. This step is completely independent of simulated microarchitecture. Next the microarchitecture simulator is loaded as a dynamic library, which allows it to be easily modified without rerunning the costly setup phase. Then a calibration phase runs which executes a sample from each checkpoint using the current simulator configuration. The samples are used to characterize the checkpoint and allow for clustering. Although the measured performance depends somewhat on the simulated microarchitecture, in practice the clustering tends to be associated with program phases, and the calibration phase tends not to need to be repeated even if the simulated microarchitecture has radical changes. At

<sup>&</sup>lt;sup>1</sup>The simulator is used interactively, not the benchmark that is simulated.

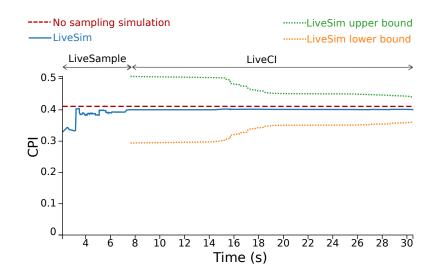

Figure 2.1: LiveSim timeline showing how the user is presented with LiveSample results from the beginning, how accurate the results get within a few seconds, and how the simulation continues running until the confidence interval reaches the threshold for the LiveCI results.

this point LiveSim is ready for interactive use allowing the user to experiment with changes to the simulated microarchitecture. After making a change to the simulator the user requests new simulation results. LiveSim randomly selects the minimum number of checkpoints and begins simulating samples from the selected checkpoints in parallel and reporting the LiveSample results to the user. After meeting the cutoff for the LiveCI results the simulation halts and reports the final results.

Figure 2.1 illustrates how LiveSim works by showing the simulation result of running namd benchmark from SPEC2006 for approximately 10 seconds in a Haswell CPU and simulating a similar CPU with LiveSim. Unlike traditional simulators, LiveSim starts to produce results as each simulation sample finishes (LiveSample). As the evaluation will show, after 5 seconds it is able to provide results within 4% of the correct result. The correct result is a full simulation of the 10 seconds without sampling shown as No Sampling Simulation. Once enough samples are gathered, it is possible to start reporting the confidence interval for the simulation. As more samples are added, the confidence interval decreases and stops the simulation when enough samples are processed. While LiveSample provides accurate results in a very short time, it cannot guarantee them. Live Confidence Interval (LiveCI) bounds the error according to the user requested acceptable error.

This chapter describes the following novel contributions:

- Introduces LiveSim, a new architectural simulation methodology that enables interactive microarchitecture design space exploration.

- Demonstrates that LiveSim is able to provide very accurate LiveSample simulation results within 5 seconds. These results are independent of the length of the simulated benchmark, and simulating more instructions does not increase the time it takes for LiveSim to provide the LiveSample results.

- Demonstrates that LiveSim is able to produce LiveCI results that bound the simulation error within 10% within 41 seconds on average.

The rest of this chapter is organized as follows: Section 2.2 provides background about existing techniques to speed up simulation; Section 2.3 explains how LiveSim works; Section 2.4 details the setup of our evaluation framework; Section 2.5 describes our results; Section 2.6 provides a comparison with related work; and Section 2.7 summarizes the contributions of this chapter.

### 2.2 Background

Most architectural simulators are implemented as discrete event simulators where the simulator models the changes to microarchitectural state that occur each clock cycle while the simulated processor executes an instruction. Simulating a single instruction can require the host to execute thousands of instructions to update all of the simulated microarchitectural state for an advanced out-of-order processor, and even fast simulators are thousands of times slower than native execution.

There are a variety of ways to cope with the slow simulation speed. One is to simulate benchmarks that execute very small numbers of instructions; however, it is difficult to ensure that these results are comparable to those obtained with standard benchmark inputs [45, 47]. Another approach is to accelerate the timing simulation using FPGAs [77, 24, 23], but this requires custom hardware, increases simulator development complexity, and is not widely used in practice. The most popular approach is to use sampling to reduce the number of instructions that need to be simulated, and this is the technique we use for LiveSim.

Many simulators have a variety of levels of simulation detail ranging from the most detailed mode which models all microarchitectural details, to modes that only simulate structures with long lived state (such as caches or branch predictor), to emulation-only mode, or even to modes that run parts of the simulated benchmark directly on the host system [81]. As the level of detail decreases, the speed of the simulation increases. Most sampling techniques take advantage of this difference in simulation speed by executing the majority of instructions in a faster simulation mode and extrapolating statistics collected from a small percentage of instructions executed using full detailed simulation mode. The two main sampling techniques are profile based sampling and statistical sampling.

Profile based sampling attempts to identify a few regions of a benchmark that are representative of the behavior of the full benchmark execution. Sherwood et al. [72] developed SimPoint, which works by profiling a benchmark and collecting information about the distribution of basic blocks executed during benchmark execution. This information is used to find phases in program execution and then select representative samples for each phase. The statistics that are collected from these samples can be used to extrapolate results that tend to be very close to those from full benchmark execution. The effectiveness of the original SimPoint proposal was purely heuristic based, but Perelman et al. [62] extended SimPoint to provide statistical confidence measures.

Wunderlich, et al. [80] developed the SMARTS framework, which applies statistical sampling theory to computer architecture simulation. The main drawback with SMARTS is that it requires continuous updates to the simulated cache and branch predictor microarchitectural state between sampling units. The simulation mode that updates this state is called functional warming, and while it is faster than detailed simulation, it is still much slower than native execution. Although SMARTS is the de facto reference for applying statistical sampling to microarchitecture simulation, earlier work from Conte et al. [27, 26] also explored using statistical sampling with microarchitecture simulation.

Since functional warming of the cache dominates simulation time, there have been a variety of proposals to reduce the amount of warmup needed and to speed up the emulation mode. One technique is to save some of the simulation state in a checkpoint and then load this checkpoint during future simulation runs [79, 78]. Another technique is to forego detailed cache modeling during the functional warmup phase and simply record the sequence of memory operations. This information can then be used to quickly rebuild the cache state prior to detailed simulation of a sampling unit [7].

LiveSim builds on existing work that uses sampling to accelerate microarchitecture simulation, but rather than simply trying to make the simulation faster, it is designed to be suitable for interactive use. LiveSim uses statistical sampling, in-memory checkpoints, checkpoint clustering, parallel checkpoint execution, and a fast cache warmup technique in order to support interactive simulation.

### 2.3 LiveSim Methodology

The previous section provided background about the sampling techniques that LiveSim leverages to enable interactive or Live simulation. In this section we explain in detail exactly how we implemented LiveSim. The basic outline for how LiveSim works is as follows:

- Setup: Run simulated benchmark in emulation only mode and periodically create inmemory checkpoints that contain architecturally visible state. Information about the sequence of memory accesses is also recorded during checkpoint creation and used later for cache warmup. The state contained in the checkpoints is independent of the simulated microarchitecture.

- **Calibration**: Execute a sample from each of the checkpoints and use the recorded statistics to group the checkpoints into clusters.

- LiveSample: When the user requests new simulation results LiveSim begins executing a number of checkpoints in parallel. As soon as simulation results are ready they are reported visually to the user.

- LiveCI: After a minimum number of checkpoints complete execution LiveSim monitors the calculated confidence interval. If it is not within the user specified limit then LiveSim randomly selects more checkpoints to run. Eventually the confidence interval reaches the selected limit and the simulation halts.

In LiveSim *checkpoints* contain all of the architecturally visible state necessary to start simulation from a specific point in the benchmark and can be reused multiple times with many different simulator configurations, whereas *samples* represent the result of simulating a specific microarchitecture for a specific checkpoint. Samples are created by first copying the checkpoint state, next loading the simulator library and configuration for the microarchitecture that is being simulated, next warming up the microarchitecture state, and finally collecting statistics for the sample.

In the rest of this section we explain in detail how each of the steps in LiveSim works.

### 2.3.1 Sampling Setup

The field of inferential statistics provides well known techniques for inferring statistics about a population given a sample of that population. SMARTS [80] demonstrated that systematic sampling can be used to approximate random sampling when used with microarchitectural simulation. LiveSim also uses systematic sampling to approximate random sampling

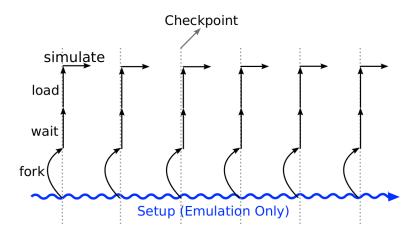

Figure 2.2: During setup the benchmark is emulated and checkpoints are created by periodically forking new processes. Each checkpoint process enters a waiting mode. Once LiveSim starts, each checkpoint loads the simulation dynamic library and configurations; then it starts simulation.

during the setup phase.

During the setup phase LiveSim runs a fast emulation-only process that periodically forks copies of itself to create an in-memory set of checkpoints that contain all the architecturally visible state necessary to continue benchmark execution. Figure 2.2 illustrates how these newly created checkpoints enter a wait mode listening for commands to start microarchitectural simulation. Since forking a process uses copy-on-write, the checkpoint creation step is relatively cheap during the setup phase. However, in our implementation each checkpoint uses tens of megabytes which makes its memory consumption worthy of study. In Section 2.5.4 we evaluate checkpoint size and how to determine the optimal number of them.

In addition to the architecturally visible state, a checkpoint also needs a way to warm up the microarchitectural state before collecting statistics from a sample. In our experiments we found LiveSim was able to warm up most of the microarchitectural state, including an advanced O-GHEL branch predictor, with only 1 million instructions of warmup. However, effectively warming up the cache required more than 50 million instructions on average, and research indicates larger caches may require even more warmup [59]. Executing this many instructions to warm up a sample would make the simulation too slow to meet the 5 second near real-time targets for LiveSim.

To solve the cache warmup problem we adapted the memory timestamp record (MTR) technique proposed by Barr et al. [7], and we call our adapted cache warmup technique Live-Cache. LiveCache is implemented as a very large and highly associative cache that is larger than the largest cache that will ever be simulated. Each cache line in LiveCache has a counter field which stores a timestamp of the most recent access to this line. Each memory operation increases this timestamp and stores it in the counter field of the cache line it is accessing. These counters provide an ordering of all locations that could possibly be in the cache. Maintaining this state has a low overhead and does not slow down the LiveSim setup process much. It will automatically be made available to forked checkpoints and it is independent of the microarchitecture that will be simulated later.

When LiveSim starts simulating a sample from a checkpoint, it first loads the simulator's dynamic libraries and configuration information. Next LiveSim executes all memory operations saved in the checkpoint's LiveCache in least recently used order without advancing the clock or collecting any statistics. This warms up the sample's microarchitectural cache state. Once all LiveCache memory operations are executed, the real simulation starts. This is similar to the technique proposed by Barr et al. [7] with some slight changes to simplify the integration with the LiveSim simulation infrastructure.

#### 2.3.2 Calibration

The central limit theorem is the underlying foundation for the statistics theory that allows us to approximate the distribution of sample averages as though it were normally distributed. A typical rule of thumb is that 30 samples are enough to apply the central limit theorem when the sampled population is not highly skewed. But if the population is highly skewed, more samples are required.

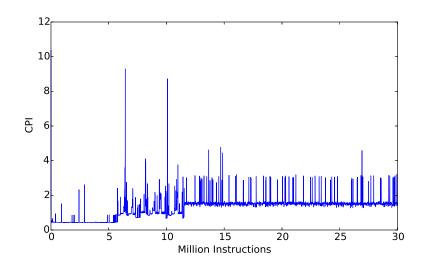

Figure 2.3 shows a trace of CPI values for the Astar benchmark plotted over time for the first 30 billion instructions of the benchmark execution. This distribution is highly skewed for two reasons. First, the minimum CPI in the simulated 4-wide system is 0.25, but the maximum CPI is effectively unbounded and we can see spikes as high as 10 for this benchmark. Second, the spikes are relatively rare and most of the samples have a CPI much closer to 1. Simply using random sampling can require hundreds of samples for a distribution this highly skewed. Furthermore, while we can calculate the number of samples needed if we are given the population distribution, this information is not known a priori. Thus random sampling alone is unable to meet the execution time constraints of LiveSim.

However, LiveSim is able to take advantage of the correlation between code signatures and performance [48] and use this information to group the checkpoints into clusters. When results are calculated, LiveSim ensures that each cluster has at least 1 sample that is selected, and it also weights the results from each cluster based on the cluster size. This technique has some similarities to what Perelman et al. [62] do to statistically bound the error for results obtained using SimPoint.

Figure 2.3: The CPI trace of Astar benchmark in SPEC 2006. The infrequent but extremely large spikes will have a considerable effect on the average CPI. Missing these spikes in random sampling will result in an unreliable sample mean.

LiveSim groups the checkpoints based on the performance statistics obtained with the baseline simulator configuration. Since performance statistics correlate with code signatures, this grouping tends to cluster the checkpoints together such that even radical changes in the simulated microarchitecture still cause the checkpoints to be clustered in a similar way. The clustering does not need to be exactly the same for different simulated microarchitectures, just close enough to avoid problems with extreme outliers that may otherwise skew the results.

After all the checkpoints are spawned during setup, LiveSim begins calibration. For each checkpoint, LiveSim loads the baseline simulator configuration and simulates a sample. After all the checkpoint samples are collected, LiveSim uses a clustering algorithm to group the checkpoints into clusters.

For clustering, LiveSim uses a K-means algorithm where K ranges from K = 1 to K = numcheck points/2 and LiveSim attempts to find the value of K that provides the optimal

trade-off between the variation of samples in clusters and the number of clusters (with the goal of minimizing both of these values). For each iteration of K LiveSim finds the best possible grouping of checkpoints to minimize the total variation of the metric of interest (typically CPI) across all K clusters. As LiveSim iterates through different values of K it keeps track of the value of K (and the associated configuration) seen thus far that minimizes total variation. When the algorithm finishes, LiveSim uses the value of K that minimized total variation as the selected configuration for clustering checkpoints.

The final step in calibration is to assign weights to each cluster. This is done based on the number of checkpoints assigned to each cluster. For example, if there were 2 clusters, and the first cluster had 900 checkpoints while the second had 100 checkpoints, the first cluster would have a weight of 0.9 and the second cluster would have a weight of 0.1. These weights are used for averaging results obtained from simulated samples and reporting LiveSample results.

#### 2.3.3 LiveSample

Once the setup and calibration phases are complete LiveSim is ready for interactive use. The usage scenarios that we envision is that the setup and calibration phases can be completed when the architect is not actively using the simulator (similar to how simulation batch jobs are run today). The LiveSample and LiveCI results are what the architect would be interested in seeing while using LiveSim for Live simulation. An architect may make a configuration change and then request results from LiveSim.

At this point LiveSim randomly selects the first batch of checkpoints to simulate. The selection algorithm depends on the number of clusters and the computation resources of the system used for running the simulation and is shown in Algorithm 1. The reason that we spawn at least twice as many checkpoints as cores in the host system is that it provided the highest sample execution throughput on our system. Too many running samples will overload the computation resources of the system, while too few limit opportunities for overlapping computation with I/O. This part of the initial checkpoint selection algorithm could be tuned differently for different systems, but it is important to ensure that at least one checkpoint is executed from each cluster, regardless of the amount of samples that the system can execute in parallel.

The selected checkpoints are contacted by the LiveSim controller process and each selected checkpoint forks another copy of itself to run the simulation, while the parent checkpoint process goes back to its waiting mode. Each child process, which will execute a sample, loads the simulator library, initializes the cache state using the LiveCache data, warms up the rest of the microarchitectural state using detailed warmup, collects statistics for its sample, and reports them to the LiveSim controller process.

LiveSim begins reporting simulation statistics to the user as soon as the first checkpoint finishes execution. These statistics are calculated by computing the arithmetic mean of the sample values after weighting each sample by its cluster weight. In our experiments these LiveSample results typically reached a steady state value within 5 seconds of starting the simulation.

#### 2.3.4 LiveCI

Figure 2.1 shows an example of how LiveSim produces LiveSample and LiveCI results for a user. The LiveSample result is provided as soon as the first checkpoint is simulated, and it usually reaches a steady state value very quickly (typically within 5 seconds). However, the initial LiveCI results take slightly longer and the simulation continues running until the LiveCI result reaches the user's specified threshold.

When LiveSim selects checkpoints to use for LiveSample results it ensures that at least 1 sample is selected from each cluster. Afterwards it begins selecting checkpoints completely randomly. However, for calculating the confidence interval, the samples that were initially selected from clusters cannot be used. The reason is that the confidence interval calculation requires samples to be chosen randomly from the population, and the clustering violates that requirement.

Consequently, when LiveSim selects checkpoints for the LiveCI results it starts by selecting 30 completely random checkpoints to take samples from. If any of the checkpoints happen to have already been simulated then the earlier sample results can be used directly. Otherwise the LiveCI results have to wait until at least 30 completely random samples have been simulated. LiveSim requires a minimum of 30 samples before calculating the confidence interval because 30 is a heuristic generally accepted as the minimum cutoff value for using the central limit theorem to approximate the sample mean distribution as normally distributed; and

a normal distribution is required for calculating the confidence interval.

However, the minimum value of 30 is simply a heuristic, and in a highly skewed distribution it may not be enough. In some of our initial experiments we observed that this could result in the confidence interval being reported as more precise than it really was. This happened in cases with a population that was mostly homogeneous, but had a few large spikes (such as the Astar example shown in Figure 2.3). If the initial set of samples did not contain one of the spikes, the samples variance could be very small which would lead to a very tight confidence interval being calculated for a sample mean that did not match the true sample mean of the population. On the other hand if the initial set of samples did contain a spike the confidence interval would be very large and outside of the user defined range. In this case the simulation would continue running and eventually enough samples would be collected so that an accurate sample mean and confidence interval was calculated.

The problem with the 30 sample minimum heuristic was that sometimes the simulation could end earlier than it should have because LiveSim missed one of the infrequent spikes. To solve this problem we developed a heuristic that inserted a synthetic sample in the sample set when calculating the confidence interval. The synthetic sample was created by computing the average of the samples collected thus far and multiplying by 10. Then the confidence interval was calculated using the true samples as well as the synthetic one. This heuristic solved the problem of ending the simulation too early due to missing extreme outlier values and it works well in practice for the SPEC CPU 2006 benchmarks that we simulated. In the event that a user was simulating a workload with even more extreme variation in sample metric, a different heuristic might be required, but we expect that adding a synthetic point 10 times the sample average should suffice for most workloads that computer architects simulate.

### 2.4 Measurement Setup

We evaluated LiveSim using 24 of the 29 SPEC CPU 2006 benchmarks that we were able to run with our simulator. Our simulation infrastructure used the MIPS64r6 ISA, which was missing support for some Fortran libraries, preventing us from running 5 of the CPU 2006 benchmarks (bwaves, gamess, cactusADM, leslie3d, wrf).

We ran all of the benchmarks on an x86 system with Haswell microarchitecture for 10 seconds using the first reference input set and used performance counters to determine how many instructions the benchmark executed during this time. We then rounded this up to the nearest 5 billion instructions and used this as the number of instructions to simulate during our evaluation. This ranged from 15 billion to 90 billion instructions depending on the benchmark.

We implemented LiveSim using a modified version of ESESC [5] as the timing simulator and a modified version of QEMU [9] as the emulation engine.

We compared 3 different simulated microarchitectures: a high performance (HP) configuration that was modeled on Intel's Haswell microarchitecture, a medium performance (MP) configuration modeled on the ARM A72 microarchitecture, and a low performance (LP) configuration modeled after MIPS Apache microarchitecture. Table 2.1 provides details about the simulated microarchitecture configurations. The confidence level for all evaluations was set to 95% and the target confidence interval was 10% of the reported values.

Our host system had 2 Intel Xeon CPU E5-2689 CPUs and 192 GB of main memory.

| Parameter   | HP             | MP             | LP            |

|-------------|----------------|----------------|---------------|

| Freq        | 3.5 GHz        | 2.5 GHz        | 1.7 GHz       |

| I\$         | 32KB 8w 2cyc   | 32KB 2w 2cyc   | 32KB 4w 2cyc  |

| D\$         | 32KB 8w 4cyc   | 32KB 4w 4cyc   | 32KB 4w 4cyc  |

| L2          | 256KB 8w 11cyc | 2 MB 16w 16cyc | 1MB 8w 26cyc  |

| L3 (shared) | 8MB 16w 20cyc  | N/A            | 2MB 32w 14cyc |

| Mem.        | 110 cyc        | 100 cyc        | 60 cyc        |

| BPred.      | ogehl 10*2K    | Hybrid 16K     | 2level 2K     |

| Issue       | 4              | 3              | 2             |

| ROB         | 192            | 128            | 64            |

| IWin.       | 60             | 72             | 64            |

| LSQ         | 72/42          | 32/32          | 24/24         |

| Reg(I/F)    | 168/168        | 128/128        | 40/40         |

Table 2.1: The three different architectures used to evaluate LiveSim

Each CPU had 8 cores with 2 SMT threads per core, giving a total of 32 OS visible logical processors. We executed the benchmarks one at a time on the host system, allowing the host to use all its resources to run a single benchmark. In all our evaluations, the simulated architecture is single-core and only one single threaded benchmark is running at a time.

# 2.5 Evaluation

Our evaluation of LiveSim is focused on four areas: speed, accuracy, warmup, and sample characterization. For speed and accuracy we compared LiveSim with no sampling simulation and with a sampling mode very similar to SMARTS [80].

### 2.5.1 Speed

Our primary goal for LiveSim was to enable interactive design space exploration using a microarchitectural simulator. To evaluate this we ran all 24 benchmarks for each of the 3

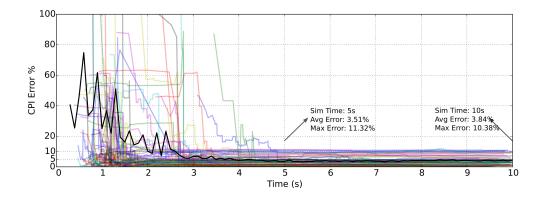

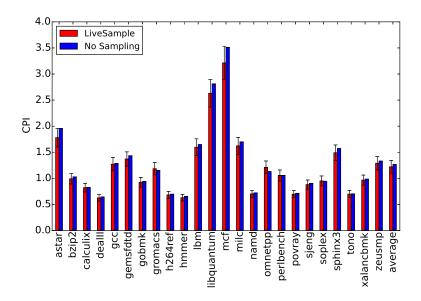

Figure 2.4: LiveSim CPI error for all 3 configurations and all 24 benchmarks (black line shows average error). LiveSim achieves an average of 3.51% CPI error within 5 seconds.

configurations using both sampling and no sampling, and we recorded a time varying trace of the LiveSim results. We calculated the time varying CPI error percentage for each benchmark by comparing the benchmark CPI reported by LiveSim with the CPI simulated without sampling. Figure 2.4 shows a graphical representation of this data. The important thing to note is that although many of the initially reported values have a large CPI error, this quickly stabilizes and within 5 seconds the average error drops to 3.51%. Furthermore this error stays roughly the same over the next 5 seconds. We believe that the LiveSample results reported after 5 seconds of simulation make LiveSim suitable for interactive microarchitectural simulation. This is even more impressive considering that the portion of the benchmark simulated is equivalent to 10 seconds of execution on a high performance system with a Haswell microarchitecture. This means that LiveSim enables simulation that is even faster than native execution.

With LiveSim we define LiveSample as the initial results that are produced using a weighted average of samples from the checkpoint clusters created during the calibration step. The results in Figure 2.4 indicate that the LiveSample results are usable within 5 seconds.

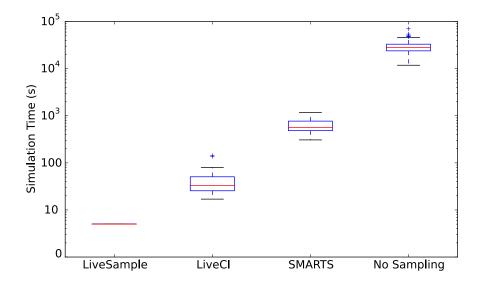

Figure 2.5: Average simulation time of all benchmarks and configurations. LiveSample results are ready within 5 seconds, LiveCI takes tens of seconds, SMARTS takes tens of minutes, and running without sampling takes many hours.

LiveCI results take longer because they require true random selection of a larger number of samples. Figure 2.5 shows a comparison of runtime for all of the different configurations for LiveSample, LiveCI, SMARTS, and running the simulation without sampling. It is important to note that the execution time of SMARTS and no sampling is proportional to the length of the benchmark, while the execution time for LiveSample is nearly constant and for LiveCI it is proportional to the variability of the samples. Hence, simulating a longer benchmark won't necessarily increase the simulation time for either LiveSample or LiveCI.

Table 2.2 provides additional insight about the speed of LiveSample and LiveCI and how it varies per benchmark using the HP configuration. The execution time of LiveCI is proportional to the number of samples that need to be simulated, and this is typically proportional to the variability of the benchmarks. For LiveSample we don't show a specific time since it is not determined algorithmically. But as illustrated earlier it is typically stable within 5 seconds. The

| Benchmark  | LiveSample | LiveCI | LiveCI Time (s) |  |  |

|------------|------------|--------|-----------------|--|--|

| astar      | 10         | 433    | 67.163          |  |  |

| bzip2      | 10         | 496    | 64.021          |  |  |

| calculix   | 6          | 398    | 48.227          |  |  |

| dealII     | 1          | 178    | 17.937          |  |  |

| gcc        | 14         | 490    | 80.032          |  |  |

| gemsfdtd   | 6          | 328    | 45.724          |  |  |

| gobmk      | 4          | 360    | 56.750          |  |  |

| gromacs    | 2          | 246    | 30.327          |  |  |

| h264ref    | 1          | 178    | 24.756          |  |  |

| hmmer      | 1          | 177    | 21.247          |  |  |

| lbm        | 3          | 239    | 32.679          |  |  |

| libquantum | 1          | 194    | 33.360          |  |  |

| mcf        | 13         | 321    | 64.381          |  |  |

| milc       | 13         | 500    | 74.741          |  |  |

| namd       | 1          | 180    | 22.842          |  |  |

| omnetpp    | 4          | 185    | 33.932          |  |  |

| perlbench  | 6          | 183    | 33.197          |  |  |

| povray     | 1          | 177    | 21.083          |  |  |

| sjeng      | 2          | 899    | 137.470         |  |  |

| soplex     | 9          | 427    | 61.676          |  |  |

| sphinx3    | 8          | 213    | 27.493          |  |  |

| tono       | 4          | 190    | 21.105          |  |  |

| xalancbmk  | 1          | 177    | 31.461          |  |  |

| zeusmp     | 8          | 412    | 54.872          |  |  |

| Average    | 5.4        | 315.9  | 54.8            |  |  |

Table 2.2: Number of checkpoints needed for LiveSample, and LiveCI as well as LiveCI execution time for each benchmark

execution time of LiveCI is determined algorithmically and it varies quite a bit from one benchmark to another. However, for most benchmarks it finishes within a minute or less. The MP and LP configurations typically finish running more quickly than the HP configuration, which is why the overall average execution time for LiveCI of all benchmarks and all configurations is 41 seconds.

Setup and calibration only need to be performed once for each benchmark even when

there are big changes in configurations (e.g. LP to HP) or even code changes in simulator. In our experiments the average setup time was 18 minutes and the average calibration time was 3 minutes. The only steps taken in every simulation are LiveCache reload which takes 0.6 seconds on average, branch predictor warmup which takes 1 second, LiveSample timing which takes 3.4 seconds and LiveCI which can add 16 to 132 additional seconds to the simulation time.

#### 2.5.2 Accuracy

Figure 2.6: CPI error distribution across benchmarks in LiveSim. Each box label shows calibration and live simulation configurations respectively.

In the previous section we demonstrated that LiveSim is fast enough to be used for interactive simulator use. However, fast results are only useful if they are reasonably accurate. When evaluating accuracy there are two things to consider: how close is the point estimate to the true value, and how often is the true value within the confidence interval. For our evaluation we selected a confidence interval of 10% and a confidence level of 95%. This means that we

expect at most 5% of the simulation results to vary by more than 10% from the true value.

To evaluate this we ran 9 different experiments for each of the 24 benchmarks. In each experiment, we first ran calibration with one configuration (HP, MP, or LP) and then ran LiveCI with another configuration (we tested all possible combinations). Of the total 216 experiments, there were 9 instances where the true CPI value was outside of the range reported by LiveCI. This is 4.16% of the time, which is within the expected range for a 95% confidence level. Figure 2.6 shows the distribution of CPI error for this set of experiments. Although the target confidence interval was set to 10%, in most cases the actual CPI error was much less, and the overall average error was 3.39%. These results also support our contention that the calibration step is microarchitecture independent. The overall error is roughly the same regardless of whether calibration is done with the same configuration as LiveCI or if the configuration used for LiveCI is very different from that used for calibration.

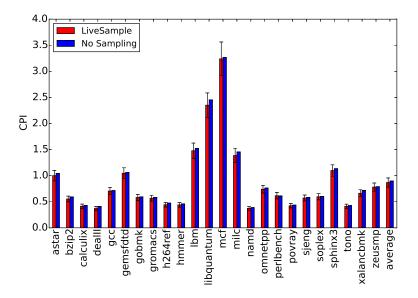

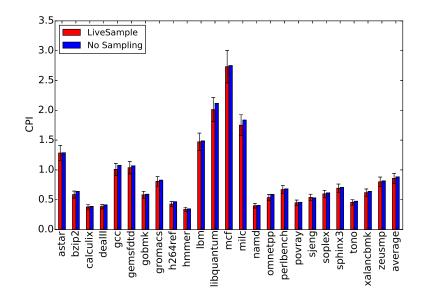

Figures 2.7, 2.8, and 2.9 compare the CPI from LiveCI and full simulation when using the same configuration for calibration and LiveCI. In this case all of the benchmarks are within the configured confidence interval.

#### 2.5.3 Warmup

Earlier we described how architectural state warmup is a critical part of sampling. In this section we evaluate the effectiveness of LiveCache as well as the amount of detailed warmup for other parts of the simulated microarchitecture. All of these experiments were performed using the HP configuration since it has the largest and most complex microarchitectural structure and will need the most warmup.

Figure 2.7: LiveCI results of SPEC benchmarks simulating the LP architecture compared to no-sampling simulation. The reported CPI results have 3.32% error and CI estimation is 100% accurate.

Figure 2.8: LiveCI results of SPEC benchmarks simulating the MP architecture compared to no-sampling simulation. The reported CPI results have 3.32% error and CI estimation is 100% accurate.

Figure 2.9: LiveCI results of SPEC benchmarks simulating the HP architecture compared to nosampling simulation. The reported CPI results have 3.33% error in average and CI estimation is 100% accurate.

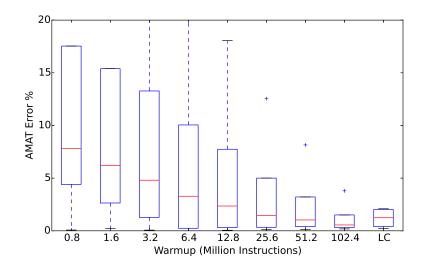

LiveCache eliminates the need for traditional cache warmup for millions of instructions. To see how it compares, we ran a set of experiments with warmup varying from 0 to 102.4 million instructions. In each experiment we measured and recorded the AMAT error for all benchmarks. Figure 2.10 shows the results comparing them to an experiment in which LiveCache was enabled and no other warmup was done. The evaluation demonstrates that LiveCache results in less AMAT error on average than 50 million instructions of warmup and less maximum AMAT error than 102 million instructions of warmup. The overhead associated with LiveCache per checkpoint was less than 0.6 seconds on average. This is a relatively small overhead compared to the sample execution time, and is less significant because samples are executed in parallel.

Although LiveCache eliminates the need for cache warmup, there are other microar-

Figure 2.10: Comparison of AMAT error for LiveCache (LC) and traditional cache warmup.

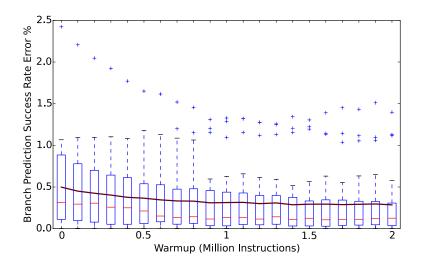

chitectural components that need to be warmed up, especially the branch predictor. Figure 2.11 shows how branch prediction accuracy error rate decreases as the amount of warmup increases. It hits a plateau around 900K instructions, and we found that in practice 1 million instructions was a good value for warmup.

In our evaluations, we used ESESC [5], which has a typical timing simulation speed of 1 MIPS. Since ESESC is fast, it does not need additional functional warmup for the branch predictor. However, a slower simulator may need functional warmup for the branch predictor and a shorter detailed warmup phase.

#### 2.5.4 Checkpoint Characterization

Although the number of samples that LiveSim uses is determined on-the-fly, the maximum value is limited by the number of available checkpoints. We needed to ensure that enough checkpoints were created for any possible combination of configuration and benchmark that

Figure 2.11: Average error of branch prediction statistics based on amount of detailed warmup at the start of a checkpoint.

might be simulated. However, we also needed to limit the number of checkpoints for two reasons: First, since each checkpoint needs to be run during the calibration phase, additional checkpoints makes calibration take longer. (However, if LiveSim were used in practice we expect that calibration would be done infrequently relative to how often the user collected LiveSim and LiveSample results, and longer calibration times would not be a problem.) Second our current implementation potentially uses a large amount of memory for each checkpoint, and if LiveSim uses swap, performance drops dramatically. We think these problems are more significant in simulator development than if LiveSim were used in practice. We also believe that this is mostly an implementation issue rather than something intrinsic to the LiveSim system, and that memory use per checkpoint could be reduced if more time were spent optimizing this bottleneck.

LiveSim uses copy-on-write when creating checkpoints so the memory utilization depends on how many pages the application writes to. We have measured the memory usage

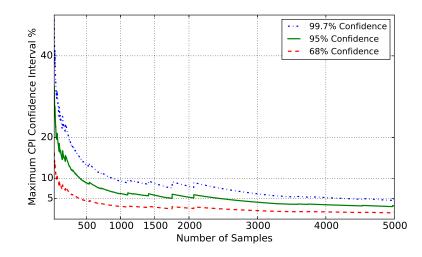

Figure 2.12: Maximum number of samples needed for a given confidence interval and confidence level in LiveSim, estimated using Monte Carlo simulation.

per checkpoint for SPEC benchmarks, and on average, a new checkpoint adds 45 MB memory occupancy. The maximum checkpoint size belongs to MCF, which is 165 MB.

To determine the maximum number of checkpoints that might be needed for various confidence interval and confidence level targets we ran the simulations without sampling and collected samples for every possible checkpoint candidate. This gave us a pool of tens of thousands of potential samples. Next we ran a Monte Carlo simulation to randomly select from the pool of samples. For each benchmark and configuration pair, we calculated the confidence interval from the set of samples, and saved the maximum confidence interval calculated for that number of samples. Figure 2.12 shows a plot of the results for the three most common confidence levels. The plot indicates that for our target of 10% confidence interval at a 95% confidence level we need roughly 500 checkpoints. Since this is simply a heuristic, to be safe we recommend doubling the number shown here when picking how many checkpoints to actually use, because if LiveSim does not have enough checkpoints it may be unable to meet the

Figure 2.13: The effect of sample size on CPI error. Each box shows the error rate distribution for SPEC benchmarks and the line shows the average error across benchmarks.

confidence interval target for LiveCI results.

We also evaluated how many instructions each sample should contain and the impact of sample size on simulation error and runtime. In general, larger samples tend to improve accuracy but decrease simulation speed. We found a a sweet spot where increasing sample size does not improve accuracy but does decrease speed. Furthermore, in our implementation we did not get any speedup for samples smaller than 100,000 instructions because of communication overhead between the simulation server and the worker nodes. We experimented with sample sizes ranging from 100,000 instructions to 20 times that amount. Figure 2.13 shows that the average error does not decrease with larger sample sizes.

Although Figure 2.13 indicates that the minimum sample size is best in terms of speed and accuracy trade-off, this is not necessarily the case, because smaller samples can have more variation, and more variation across samples increases the number of samples needed for LiveCI. Figure 2.14 shows the effect of sample size on simulation time (LiveCI). This figure

Figure 2.14: The effect of sample size on LiveCI time. The line shows the average LiveCI time across benchmarks and the area is where the actual distribution lies.

shows that 200K instruction samples result in the minimum simulation time. Since the error rate is nearly the same for all samples sizes, this is the sample size we used for LiveSim.

## 2.6 Related Work

Researchers have been working on ways to speed up simulation for decades and we surveyed some of the seminal work related to profile based sampling [72, 62] and statistical sampling [80, 27, 26] for microarchitecture simulation in Section 2.2. LiveSim achieves fast simulation by combining three main techniques: random sampling of checkpoints, parallel simulation of checkpoints, and fast warmup of checkpoint state using LiveCache. There is a variety of related work in these various areas, but none of them attempt to achieve the goals of LiveSim.

The most closely related work to LiveSim is from Sandberg et al. [70, 71]. Like us, they use copy-on-write to fork multiple checkpoints and execute the checkpoints in parallel to

speed up simulation. However, their proposal focuses on accelerating a single simulation run and only executes at 25% of native execution speed when simulating a system with an 8MB L2 cache. While this is an impressive result, our LiveSim system is able to execute at faster than native speed. After the initial setup step, LiveSim is able to provide simulation results in 5 seconds or less, even though we simulated 10 seconds of native execution. Sandberg et al. essentially use the SMARTS methodology, while using virtualization and parallel checkpoint execution to accelerate the function warming (which is the most time-consuming part of SMARTS). In contrast we randomly select checkpoints in LiveSim and are able to report initial results within 5 seconds, and we choose how many total checkpoints to execute based on characteristics of the benchmark that we are simulating, whereas Sandberg et al. simulate all checkpoints as SMARTS would. Parallel execution of forked copies of an application has also been used by others to speed up analysis performed using dynamic binary instrumentation [76, 56].

SMARTS is effective at minimizing the number of instructions that need detailed simulation; however, its conservative always-on warmup of caches and branch predictor makes warmup the simulation bottleneck (over 99% of simulation time). Many researchers have observed that always-on warmup of caches may be unnecessary and have looked for ways to accelerate warmup. For LiveSim we developed LiveCache by adapting a technique developed by Barr et al. [7] which keeps track of the sequence of memory operations during functional warmup and uses this information to rebuild the cache state before beginning detailed simulation of a sampling unit. We found that LiveCache technique works very well with LiveSim and helps us meet our goal of getting accurate simulation results in 5 seconds or less. However, there are a variety of other techniques that have been proposed for accelerating warmup.

Haskins and Skadron [41, 42] demonstrated that continuous cache and branch predictor warmup was unnecessary, and they proposed ways to determine when to begin warmup prior to simulating a sample. Eeckhout et al. [34] proposed a similar technique that further reduced the amount of warmup required. Luo [51] proposed a method to monitor when a cache was warmed up and used that information to decide when to switch to full simulation. Recent work from Nikoleris et al. [59] shows that some workloads may require up to 100 million instructions of warmup for caches larger than 64 MB. They propose a technique that uses native execution to capture a sample of memory accesses and use this technique to reduce the amount of warmup for large caches. All of these techniques are effective for the types of simulation they evaluate, but they would not help with LiveSim because we still need to execute the application once during the setup phase. LiveCache is easily integrated with LiveSim's setup phase as a low overhead and relatively simple way to do cache warmup.

For LiveSim we have focused on developing a simulator that supports interactive use when evaluating new architecture proposals. Our work focuses on fast performance simulation for a single thread of execution because this is the baseline for microarchitecture simulation, and it must work correctly before considering more complex scenarios. Other researchers have looked for ways to speed up thermal simulation [28, 4], multithreaded simulation [5, 19, 20], and simulation of soft-errors in caches [74]. As future work we may extend LiveSim to support these additional simulation modes, but first we want to establish the usefulness of LiveSim using performance simulation only.

There are also proposals to accelerate simulation by varying the level of simulation detail depending on the region of code being simulated [36, 18, 40]. While these techniques

work well for accelerating simulation they fall short of our goal of supporting simulation speeds suitable for interactive use.

## 2.7 Summary

This chapter presents LiveSim, a novel simulation methodology that can be used for interactive microarchitectural design space exploration. Although analytical modeling can also be used for early design space exploration, eventually architects typically use simulation based methods to evaluate the usefulness of proposed ideas. LiveSim makes simulation fast enough for interactive use and allows architects to quickly change parameters and get immediate feedback using real benchmarks. LiveSim leverages many advances of the past two decades in applying statistical sampling to microarchitectural simulation. However, previous work on sampling has simply tried to make simulation faster. LiveSim is the first to demonstrate how sampling can be used to support interactive microarchitectural simulation.

The prototype demonstrates the feasibility of LiveSim and obtains accurate results within 5 seconds and bounds the possible error within 41 seconds on average for the benchmarks we evaluated. It is available as an open source project at https://github.com/masc-ucsc/liveos. Although the LiveSim methodology was evaluated using this prototype, the concepts are general and can be adopted for use with other simulators.

## **Chapter 3**

# **Analysis of PARSEC Scalability**

The previous chapter examined the problem of slow simulation speed and demonstrated how to use statistical sampling to dramatically reduce simulation time for single threaded applications. Statistical sampling has also been used to reduce simulation time for multithreaded applications [5, 19]. However, despite this promising research, it is still relatively difficult to use statistical sampling correctly when simulating multithreaded applications.

Multithreaded applications are also difficult for computer architects to analyze during early design space exploration because there are fewer multithreaded applications in widespread use, making it difficult to design benchmark suites. Despite this challenge there have been efforts to create multithreaded benchmarks, and one of the most widely used multithreaded benchmark suites is PARSEC. I used PARSEC extensively while studying ways to improve parallel programming. During this research I discovered that some of the features PARSEC included to simplify simulation of multithreaded applications could potentially result in misleading conclusions. In this chapter I present a detailed analysis of the scalability of the PARSEC benchmarks that is, how much faster the benchmarks complete execution when adding additional parallel computing resources. The research presented in this chapter was also published in the IEEE International Symposium on Performance Analysis of Systems and Software (ISPASS) in April 2016.

#### **3.1 Introduction**

The PARSEC benchmark suite is "designed to provide parallel programs for the study [of] CMPs" [14]. It was introduced in 2008 and has been widely used for computer architecture research since then. Developed with the needs of researchers in mind, it has features that make it easier to use with architectural simulators. Each benchmark has multiple input sets, including three that are intended to run with simulators (*simsmall, simmedium, simlarge*), and one that is intended to be representative of a real application (*native*).<sup>1</sup> This allows users to simulate a smaller workload but obtain results representative of a real workload. Each benchmark also defines a *Region of Interest* (ROI) indicating which part of the benchmark executes in parallel. By simulating only the ROI, PARSEC users can reduce simulation time. The ROI is also important for ensuring that results obtained using simulation inputs are representative of real program behavior [12].

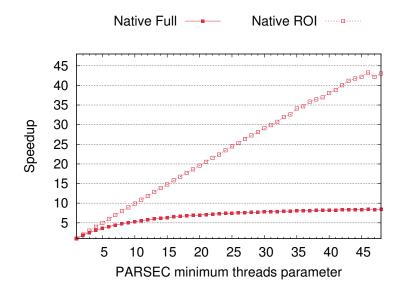

Choices in input set size and whether to model the whole program, or only the ROI, can lead to different interpretations when analyzing benchmark results. For instance, Figure 3.1

<sup>&</sup>lt;sup>1</sup>Two additional input sets (*test* and *simdev*) are included for simulator testing and are not appropriate for scientific studies.

Figure 3.1: Speedup for the full execution of Blackscholes is much less than ROI, when using the native input set and running on a 48-core system.

shows the scalability of ROI only and full benchmark execution for blackscholes running on a 48-core system and using the native input set. The ROI achieves a maximum speedup of 43 times, while the maximum speedup of the full benchmark is less than 9 times.

Prior research characterized the behavior of the PARSEC benchmark suite [8, 10, 13, 12, 14, 15, 16, 21, 65] but none of them compare the runtime scalability of the native input sets with that of the simulation input sets, nor do they compare the runtime scalability of the ROI to that of the full program. This chapter provides this missing characterization and highlights the importance of PARSEC users reporting data about what input set was used in their own papers.

In this chapter I measure the runtime scalability of the four main PARSEC input sets, and I compare the scalability of the ROI with that of the whole program. I do so by running the benchmarks on real multicore systems, varying the number of threads, and measuring the *runtime* of the ROI and the full program for the four different input sets. My contributions are as follows:

- Systematic analysis of the runtime scalability of all PARSEC input sets. I found that in many cases different inputs to the same benchmark have very different scalability characteristics.

- Systematic analysis of the runtime scalability of the ROI compared with full-program execution for all input sets. I identify 6 benchmarks where the scalability of ROI and full program execution has significantly different behavior, while for the other 7 benchmarks ROI and full program execution have very similar behavior.

The rest of this chapter is organized as follows: Section 3.2 provides background about PARSEC; Section 3.3 describes the experiment setup; Section 3.4 provides detailed results; Section 3.5 surveys related work; and Section 3.6 concludes.

#### 3.2 Background