#### UNIVERSITY OF CALIFORNIA SAN DIEGO

#### SAN DIEGO STATE UNIVERSITY

# Towards Autonomous Brain-Computer Interfaces: Approaches, Design, and Implementation

A Dissertation submitted in partial satisfaction of the requirements for the degree Doctor of Philosophy

in

Engineering Science (Electrical and Computer Engineering)

by

Daniel Valencia

Committee in charge:

University of California San Diego

Professor Patrick Mercier, Co-Chair Professor Gert Cauwenberghs Professor Drew Hall

San Diego State University

Professor Amir Alimohammad, Co-Chair Professor Hakan Toreyin

Copyright

Daniel Valencia, 2024

All rights reserved.

| The dissertation of Daniel Valencia is approved, and it is acceptable in quality |

|----------------------------------------------------------------------------------|

| and form for publication on microfilm and electronically.                        |

|                                                                                  |

|                                                                                  |

|                                                                                  |

|                                                                                  |

|                                                                                  |

|                                                                                  |

|                                                                                  |

|                                                                                  |

|                                                                                  |

| Co-chair                                                                         |

|                                                                                  |

| Co-chair                                                                         |

University of California San Diego San Diego State University 2024

# **DEDICATION**

To my family.

### **EPIGRAPH**

No one can tell what goes on in between the person you were and the person you become.

There are no maps of the change. You just come out the other side.

Stephen King

# TABLE OF CONTENTS

| Disserta              | ation Approval Page                                                    | iii         |

|-----------------------|------------------------------------------------------------------------|-------------|

| Dedicat               | ion                                                                    | iv          |

| Epigrap               | h                                                                      | v           |

| Table of              | f Contents                                                             | vi          |

| List of F             | Figures                                                                | ix          |

| List of T             | Tables                                                                 | xvi         |

| Acknow                | vledgements                                                            | xviii       |

| Vita                  |                                                                        | xxi         |

| Abstrac               | t of the Dissertation                                                  | xxii        |

| Chapter<br>1.1<br>1.2 | 1 Introduction                                                         | 1<br>2<br>2 |

| Chapter               | 2 In Vivo Neural Spike Detection with Adaptive Noise Estimation        | 7           |

| 2.1                   | Introduction                                                           | 8           |

| 2.2                   | Filtering, Pre-processing, and Noise Estimation Algorithms             | 10          |

| 2.3                   | Performance of In Vivo Potential Spike Detection Techniques            | 15          |

| 2.4                   | Hardware Realization of the Candidate Detector                         | 19          |

| 2.5                   | Spike Detection Performance Analysis                                   | 25          |

|                       | 2.5.1 Spike Detection Performance Analysis Over Real Neural Recordings | 26          |

|                       | 2.5.2 The Impact of Spike Detection on Neural Decoding Applications    | 28          |

| 2.6                   | Conclusion                                                             | 30          |

| 2.7                   | Publications                                                           | 30          |

| Chapter               | Neural Spike Sorting using Binarized Neural Networks                   | 31          |

| 3.1                   | Introduction                                                           | 32          |

| 3.2                   | Spike Sorting                                                          | 34          |

| 3.3                   | Binarized Neural Networks for Spike Sorting                            | 36          |

| 3.4                   | BNN Hardware Architecture                                              | 42          |

| 3.5                   | Conclusion                                                             | 51          |

| 3.6                   | Publications                                                           | 51          |

| Chapter               | Partially Binarized Neural Networks for Efficient Spike Sorting        | 52          |

| 4.1                   | Introduction                                                           | 53          |

| 4.2                   | Efficiency of the Feature Extraction Methods                           | 55          |

| 4.3        | Partially Binarized Neural Networks                                           | 57  |

|------------|-------------------------------------------------------------------------------|-----|

|            | 4.3.1 Evaluation of BNN and PBNN for Feature Vector Classification            | 59  |

|            | 4.3.2 Evaluation of BNN and PBNN-based Sorting Over Real Datasets             | 62  |

| 4.4        | Hardware Architecture and Implementation of the PBNN-based Classifier         | 64  |

| 4.5        | Conclusion                                                                    | 71  |

| 4.6        | Publications                                                                  | 71  |

| Chapter    | 5 Efficient In Vivo Neural Signal Compression Using an Autoencoder-based      |     |

| 1          | Neural Network                                                                | 72  |

| 5.1        | Introduction                                                                  | 73  |

| 5.2        | Local Field Potential-based BCIs                                              | 75  |

| 5.3        | Autoencoder-based Compression                                                 | 78  |

| 5.4        | In Vivo Encoder Optimizations                                                 | 84  |

| 5.5        | Hardware Architecture and Implementation Results                              | 89  |

| 5.6        | Conclusion                                                                    | 96  |

| 5.7        | Publications                                                                  | 97  |

| Chapter    | 6 Towards In Vivo Neural Decoding                                             | 98  |

| 6.1        | Introduction                                                                  | 99  |

| 6.2        |                                                                               | 102 |

|            | Estimating Information in Neural Spike Trains                                 | 102 |

| 6.3        | Neural Decoding and Spike Sorting                                             | 100 |

|            | 6.3.1 Investigating Sorted and Unsorted Decoding Paradigms                    |     |

| <i>C</i> 1 | 6.3.2 Training and Calibration                                                | 111 |

| 6.4        | Towards an Implantable Decoding Processor                                     | 112 |

| 6.5        | Conclusion                                                                    | 118 |

| 6.6        | Publications                                                                  | 118 |

| Chapter    | 1 9                                                                           |     |

|            | works                                                                         | 119 |

| 7.1        | Introduction                                                                  | 120 |

| 7.2        | A Computationally-Efficient SNN Model                                         |     |

| 7.3        | A Generalized Reconfigurable Hardware Architecture for SNNs                   | 126 |

|            | 7.3.1 SNN Core Memory                                                         | 127 |

|            | 7.3.2 Neuron Input Accumulation                                               | 128 |

|            | 7.3.3 Neuron State Computation                                                | 129 |

| 7.4        | SNN Emulation and Implementation Results                                      | 132 |

|            | 7.4.1 Real-time SNN Emulation                                                 | 132 |

|            | 7.4.2 Hardware Implementation Results                                         | 134 |

|            | 7.4.3 Design Verification                                                     | 136 |

|            | 7.4.4 Comparison                                                              | 141 |

| 7.5        | Conclusion                                                                    | 147 |

| 7.6        | Publications                                                                  | 148 |

| Chapter    | 8 Power-Efficient In Vivo Brain-Machine Interfaces via Brain-State Estimation | 149 |

| 8.1      | Introduction                                                 | 150 |

|----------|--------------------------------------------------------------|-----|

| 8.2      | Neural Signals and Brain-Switches                            | 155 |

|          | 8.2.1 Brain-switch Algorithms                                | 158 |

| 8.3      |                                                              | 161 |

| 8.4      | Intention-Aware Decoding                                     | 169 |

| 8.5      | Conclusion                                                   | 172 |

| 8.6      | Publications                                                 |     |

| Chapter  | 9 An Efficient Brain-Switch for                              |     |

|          | J                                                            | 174 |

| 9.1      |                                                              | 175 |

| 9.2      | Feasibility of Employing Local Field Potentials              | 177 |

| 9.3      | Design of LFP-based RNN Brain Switches                       | 181 |

|          | 9.3.1 LFP Feature Extraction Unit                            | 182 |

|          |                                                              | 183 |

|          | 9.3.3 MEA Channel Selection                                  | 185 |

|          | 9.3.4 CAR and Filter Considerations                          | 189 |

| 9.4      | Hardware Architecture of the Designed LFP-based Brain Switch | 192 |

| 9.5      | Conclusion                                                   | 199 |

| 9.6      | Publications                                                 | 199 |

| Chapter  | · · · · · · · · · · · · · · · · · · ·                        |     |

|          | Decoding                                                     | 200 |

|          | Introduction                                                 |     |

|          | Neural Signal Features                                       |     |

|          | Asynchronous BCIs using Intention Estimation                 | 208 |

| 10.4     | 1                                                            | 210 |

|          | 10.4.1 LFP Domain                                            |     |

|          | 10.4.2 Spike Domain                                          |     |

|          | 10.4.3 ASIC Implementation and Comparison                    |     |

|          | FPGA-based BCI System Prototype                              |     |

| 10.6     | Conclusion                                                   | 224 |

| 10.7     | Publications                                                 | 224 |

| Chapter  | 11 Conclusion                                                | 225 |

| Chapter  | 12 Future Work                                               | 230 |

| Bibliogr | anhy                                                         | 235 |

# LIST OF FIGURES

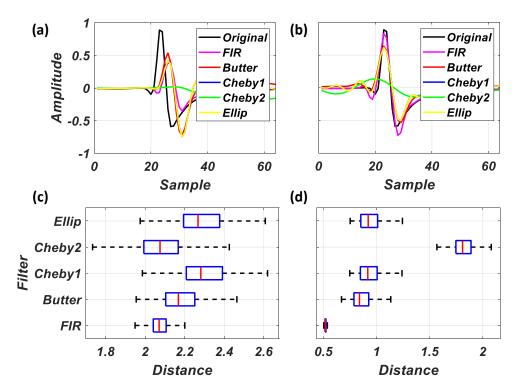

| Figure 2.1.  | The impact of (a) causal filtering and (b) non-causal filtering on the spike waveform shapes. The boxplots (c) and (d) show the variations of the Euclidean dsitance between actual spike waveforms and the filtered spikes employing causal and non-causal filtering, respectively  | 11 |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

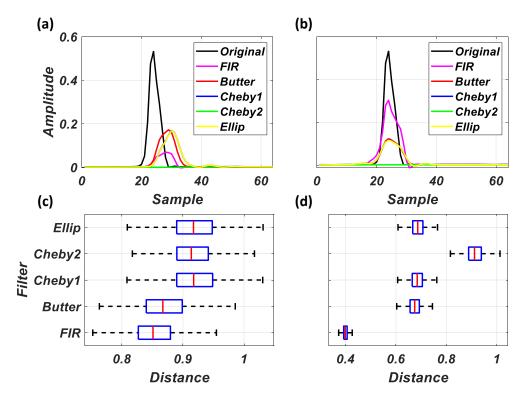

| Figure 2.2.  | The impact of (a) causal filtering and (b) non-causal filtering on the spike energy waveform shapes. The boxplots (c) and (d) show the variations of the Euclidean distance between actual and the filtered energy waveforms employing causal and non-causal filtering, respectively | 12 |

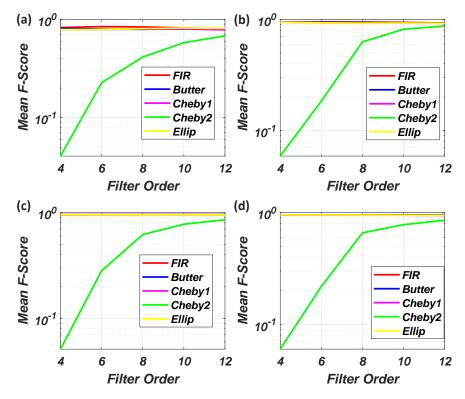

| Figure 2.3.  | The F-scores of the NEO and RMS detection with various filters for the (a) Easy1, (b) Easy2, (c) Difficult1, and (d) Difficult2 datasets, respectively                                                                                                                               | 18 |

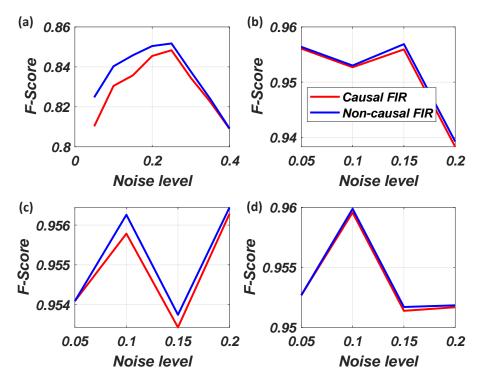

| Figure 2.4.  | The F-Scores of the fourth-order causal and non-causal Equiripple FIR filter over the (a) Easy1, (b) Easy2, (c) Difficult1, and (d) Difficult2 datasets.                                                                                                                             | 19 |

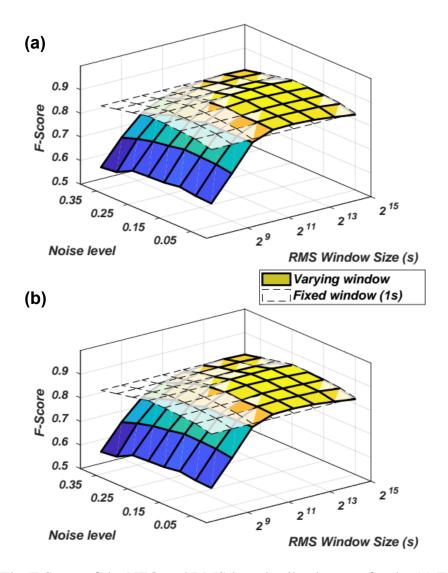

| Figure 2.5.  | The F-Score of the NEO and RMS-based spike detector for the (a) Easy1 and (b) Difficult1 datasets over various noise levels and varying RMS window sizes using the simplified Equation (2.4)                                                                                         | 21 |

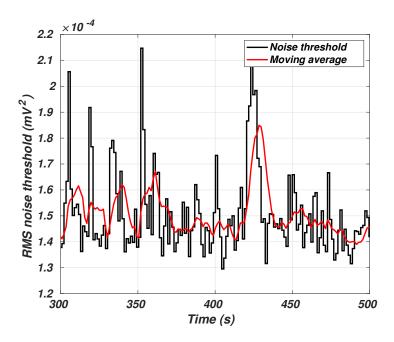

| Figure 2.6.  | Adaptive noise threshold estimation                                                                                                                                                                                                                                                  | 22 |

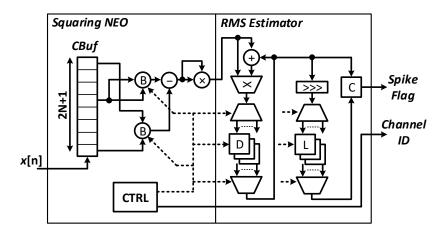

| Figure 2.7.  | The datapath of the multi-channel NEO and RMS-based spike detector                                                                                                                                                                                                                   | 22 |

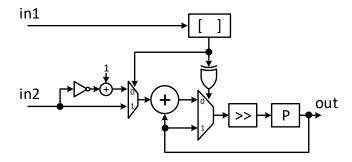

| Figure 2.8.  | The datapath of the sequential radix-2 booth multiplier                                                                                                                                                                                                                              | 22 |

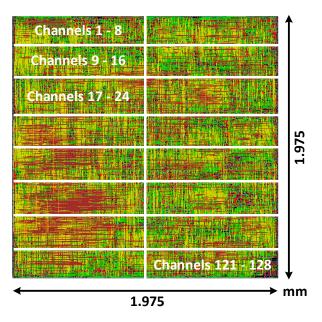

| Figure 2.9.  | The ASIC layout of the designed 128-channel NEO and RMS-based spike detector.                                                                                                                                                                                                        | 24 |

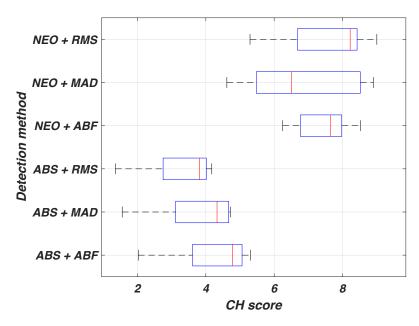

| Figure 2.10. | The CH score boxplots of the projected spike trains using various spike detection methods for the macaque monkey's reaching tasks                                                                                                                                                    | 28 |

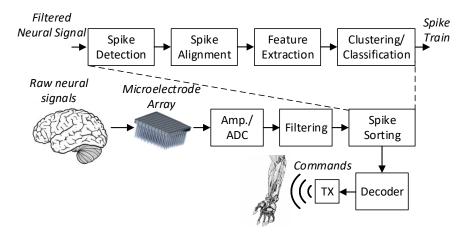

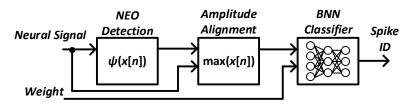

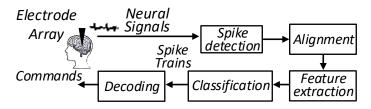

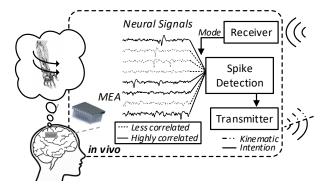

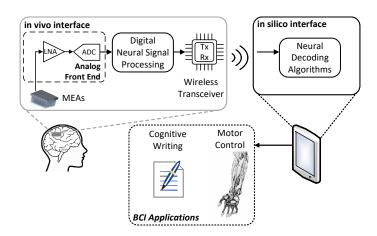

| Figure 3.1.  | The system-level diagram of a BCI.                                                                                                                                                                                                                                                   | 34 |

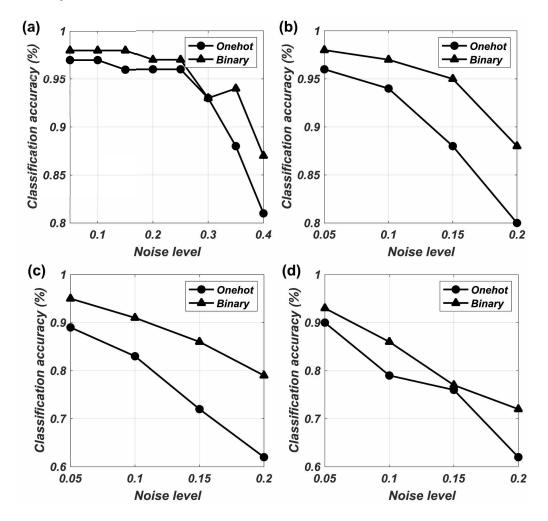

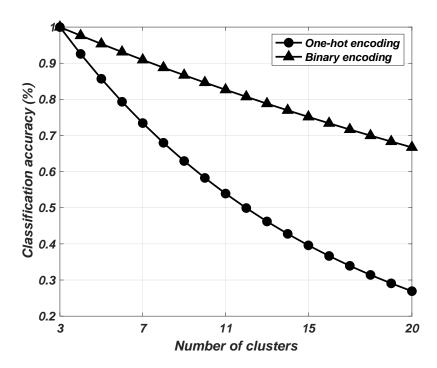

| Figure 3.2.  | Classification accuracy of the BNN for the (a) Easy1, (b) Easy2, (c) Difficult1, and (d) Difficult2 datasets using the one-hot and binary encoding schemes.                                                                                                                          | 38 |

| Figure 3.3.  | The top-level block diagram of the BNN-based spike sorting hardware                                                                                                                                                                                                                  | 42 |

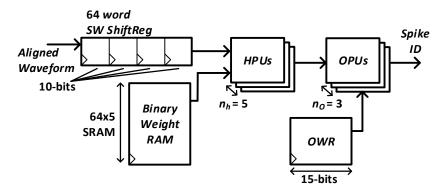

| Figure 3.4.  | The block diagram of the designed BNN-based spike classification module.                                                                                                                                                                                                             | 43 |

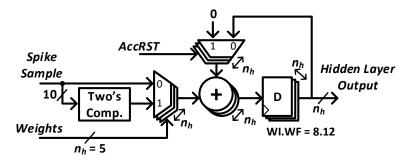

| Figure 3.5.  | The block diagram of the hidden layer processing units                                                                                                                                                                                                                               | 44 |

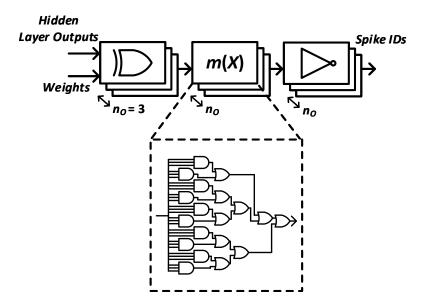

| Figure 3.6. | The block diagram of the output layer processing units (OPUs)                                                                                                        | 45 |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 3.7. | Classification accuracy of the BNN utilizing the one-hot and binary encoding schemes for varying numbers of clusters                                                 | 45 |

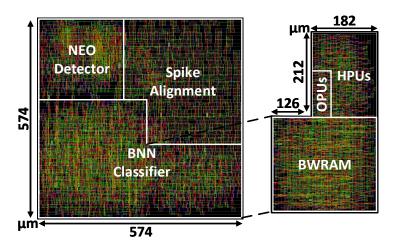

| Figure 3.8. | The chip layout of the designed BNN-based spike sorting system                                                                                                       | 46 |

| Figure 4.1. | The block diagram of a BMI system employing spike sorting                                                                                                            | 53 |

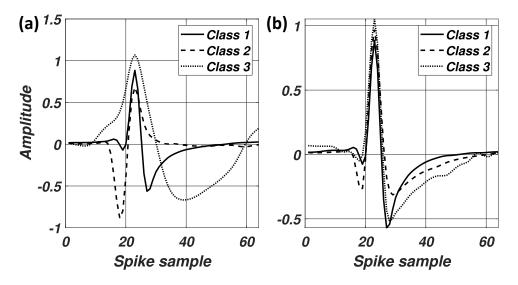

| Figure 4.2. | The mean spike waveforms for the (a) Easy1 and (b) Difficult1 WaveClus datasets                                                                                      | 59 |

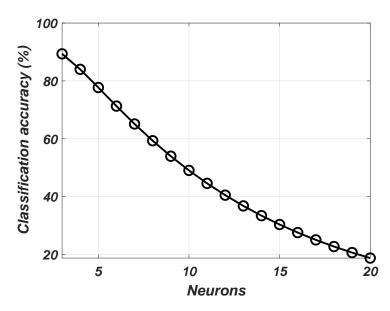

| Figure 4.3. | The classification accuracy of the PBNN over varying number of neurons.                                                                                              | 62 |

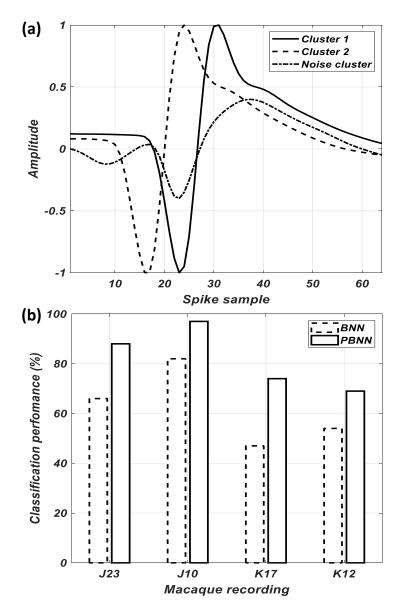

| Figure 4.4. | (a) Example cluster waveforms of the J23 macaque recording and (b) the classification performance of the BNN and PBNN-based clustering over four macaque recordings. | 63 |

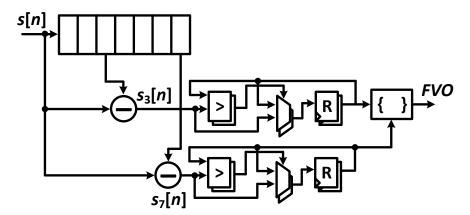

| Figure 4.5. | The block diagram of the DD-2Ex-based FE module                                                                                                                      | 64 |

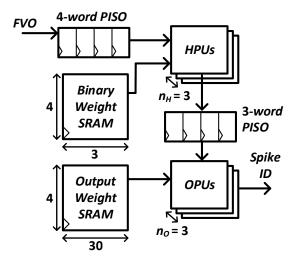

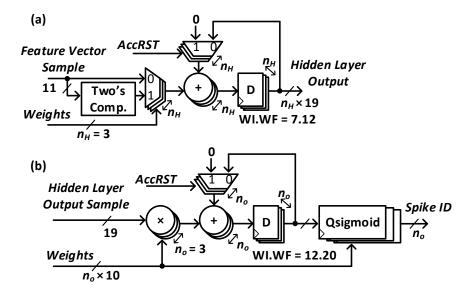

| Figure 4.6. | The block diagram of the PBNN                                                                                                                                        | 66 |

| Figure 4.7. | The block diagram of (a) the hidden layer processing units ( <i>HPUs</i> ) and (b) the output layer processing units ( <i>OPUs</i> )                                 | 66 |

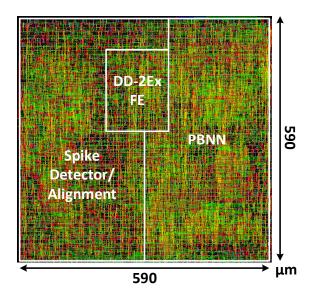

| Figure 4.8. | The layout of the designed PBNN-based spike sorting system                                                                                                           | 67 |

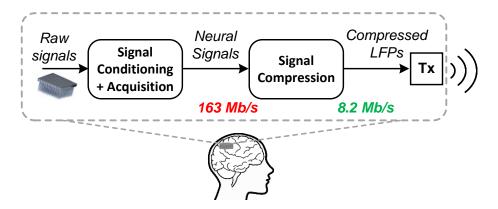

| Figure 5.1. | Intracortical recording and wireless transmission of compressed neural signals, employing 1000 recording channels                                                    | 74 |

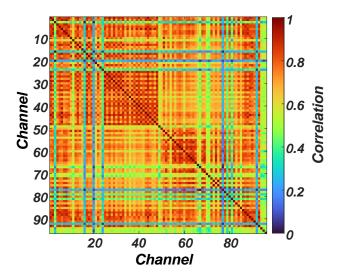

| Figure 5.2. | The inter-channel correlation over 30 seconds of a neural recording                                                                                                  | 79 |

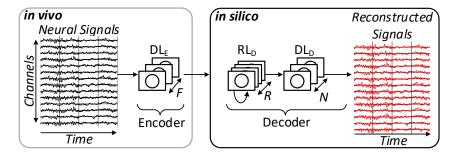

| Figure 5.3. | The block diagram of the designed autoencoder-based compression scheme.                                                                                              | 80 |

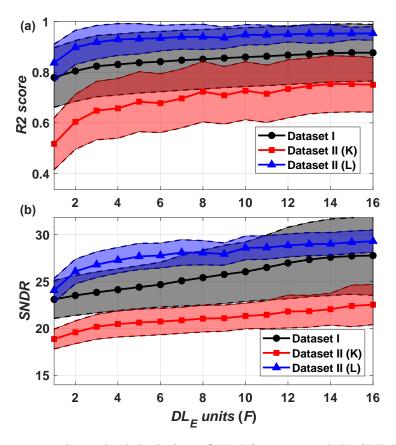

| Figure 5.4. | The mean and standard deviation of (a) R2 scores and (b) SNDRs for the reconstructed LFP signals analyzed over various numbers of $DL_E$ units $F$ .                 | 81 |

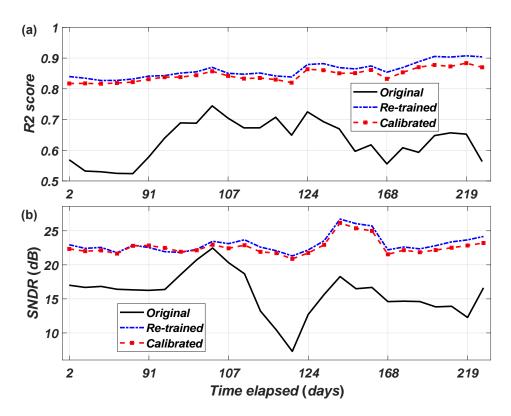

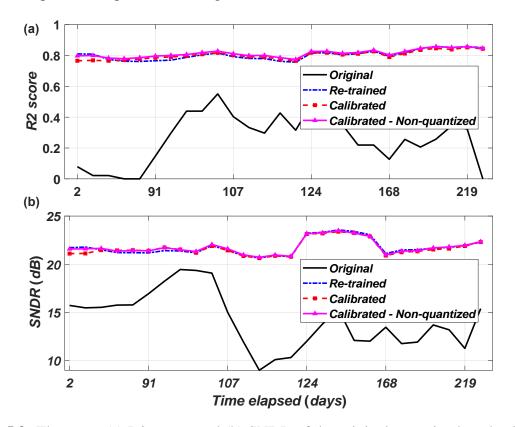

| Figure 5.5. | The mean of the (a) R2 scores and (b) SNDRs of the original, re-trained, and calibrated models over all recordings of Dataset I, respectively                        | 82 |

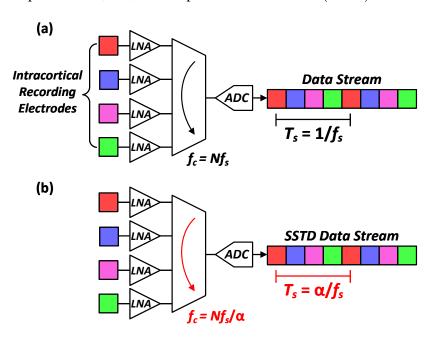

| Figure 5.6. | The analog front-end configuration for realizing staggered spatio-temporal downsampling (SSTD).                                                                      | 85 |

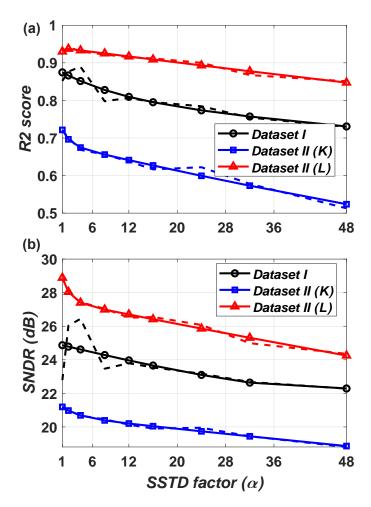

| Figure 5.7.  | The variations of (a) R2 scores and (b) SNDR for the first recording of Dataset I, the Monkey K recording of Dataset II, and the Monkey L recording of Dataset II, over various SSTD factors. The dashed lines show the metrics for raw data, while the marked-up lines depict the trend | 87  |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

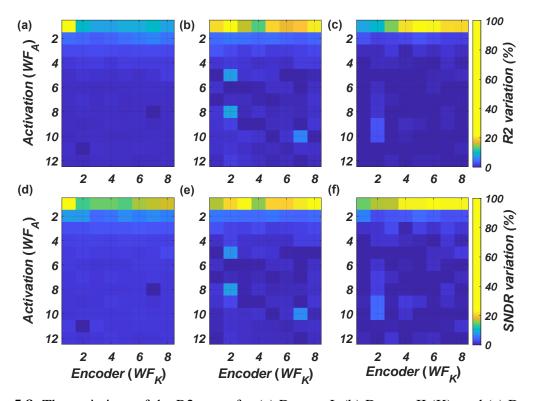

| Figure 5.8.  | The variations of the R2 score for (a) Dataset I, (b) Dataset II (K), and (c) Dataset II (L), along with the variations of the SNDR for (d) Dataset I, (e) Dataset II (K), and (f) Dataset II (L) over different encoder resolutions $WF_K$ and HardTanh output resolutions $WF_A$       | 88  |

| Figure 5.9.  | The mean (a) R2 scores and (b) SNDR of the original, re-trained, and calibrated models using encoder quantization and SSTD over all recordings of Dataset I, respectively. The performance of the calibrated SSTD configuration without quantization is also shown.                      | 89  |

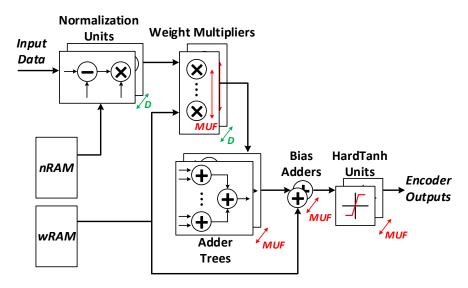

| Figure 5.10. | The top-level block diagram of the designed encoder network                                                                                                                                                                                                                              | 90  |

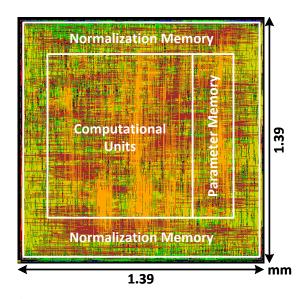

| Figure 5.11. | The 1.94 mm <sup>2</sup> ASIC layout of the synthesized in vivo encoder in a standard 180-nm CMOS process                                                                                                                                                                                | 91  |

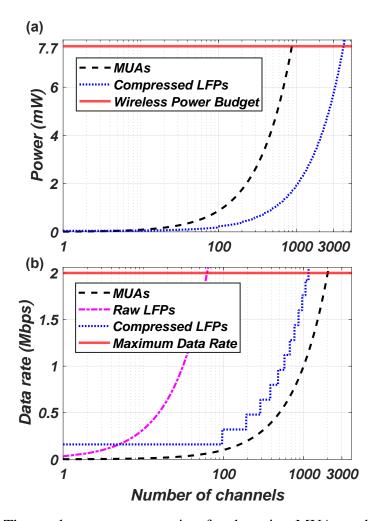

| Figure 5.12. | (a) The total power consumption for detecting MUAs and compressed LFPs (including that of the AFE and wireless transmission) and (b) the supported data rate for MUAs, raw LFPs, and compressed LFPs over various number of channels.                                                    | 96  |

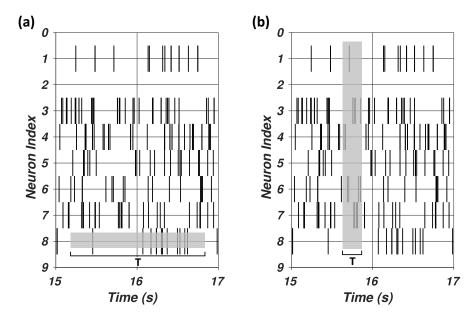

| Figure 6.1.  | (a) Neuron rate coding and (b) ensemble rate coding                                                                                                                                                                                                                                      | 103 |

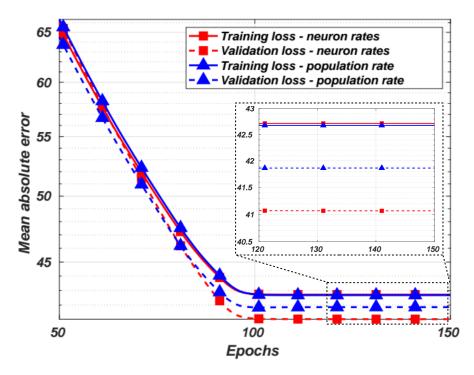

| Figure 6.2.  | The training and validation loss for neuron rate coding and ensemble rate coding over various training epochs                                                                                                                                                                            | 106 |

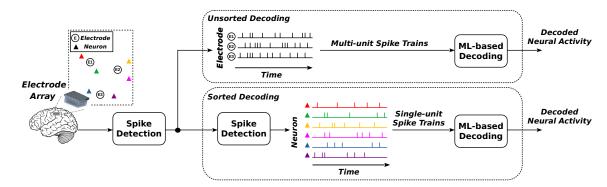

| Figure 6.3.  | The in vivo neural decoding paradigms                                                                                                                                                                                                                                                    | 106 |

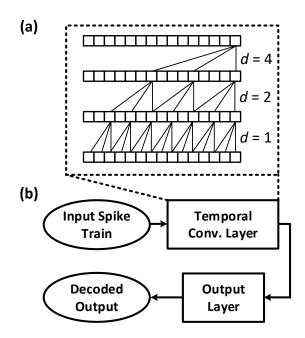

| Figure 6.4.  | (a) The block diagram of a TCN layer and (b) the TCN-based decoder                                                                                                                                                                                                                       | 108 |

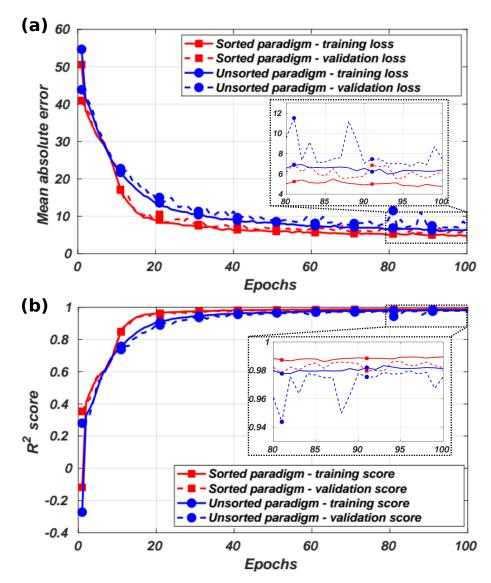

| Figure 6.5.  | (a) The training performance and (b) the $R^2$ score of the TCN-based decoder for both decoding paradigms                                                                                                                                                                                | 110 |

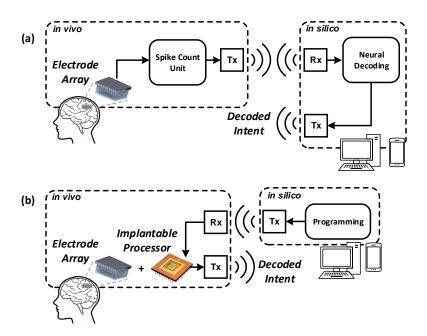

| Figure 6.6.  | The system-level diagrams of (a) conventional and (b) the fully-implantable wireless BMIs                                                                                                                                                                                                | 113 |

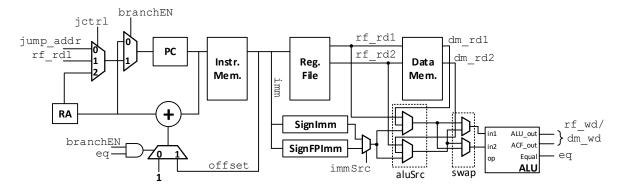

| Figure 6.7.  | The top-level block diagram of the designed and implemented neural network processor.                                                                                                                                                                                                    | 113 |

| Figure 6.8.  | The program snippet for computing the dilated convolution                                                                                                                                                                                                                                | 116 |

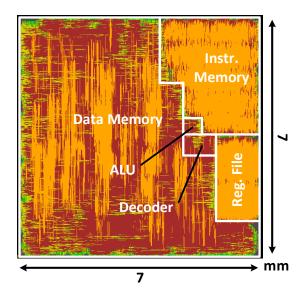

| Figure 6.9.  | The ASIC layout of the designed and implemented neural network processor.                                                                                                                                                                                                                | 117 |

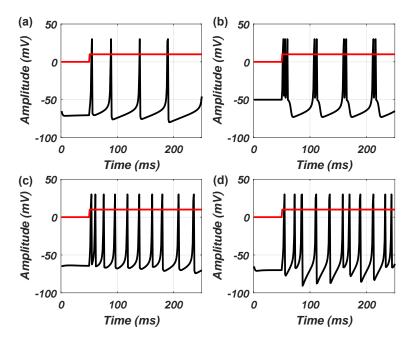

| Figure 7.1.  | Membrane potential waveforms for (a) regular spiking, (b) chattering, (c) low-threshold spiking, and (d) fast-spiking neurons                                                                                     | 124 |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

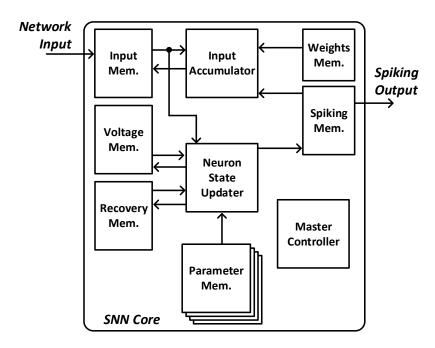

| Figure 7.2.  | The top-level block diagram of the designed and implemented SNN core                                                                                                                                              | 127 |

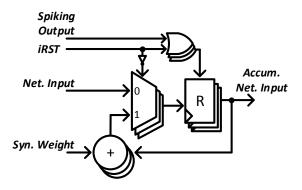

| Figure 7.3.  | The datapath of the input accumulator module                                                                                                                                                                      | 129 |

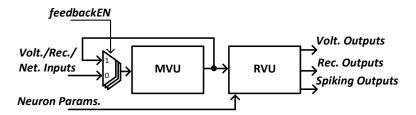

| Figure 7.4.  | The block diagram of the neuron state updater                                                                                                                                                                     | 129 |

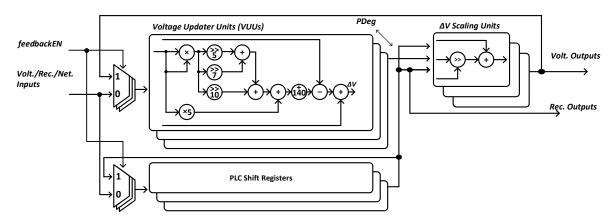

| Figure 7.5.  | The block diagram of the membrane voltage updater (MVU)                                                                                                                                                           | 129 |

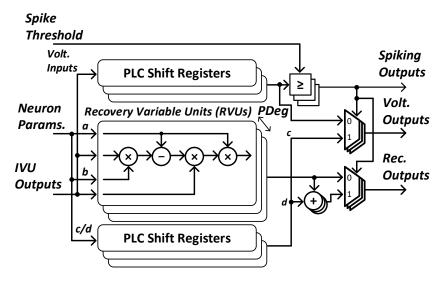

| Figure 7.6.  | The block diagram of the Recovery Variable Updater (RVU)                                                                                                                                                          | 131 |

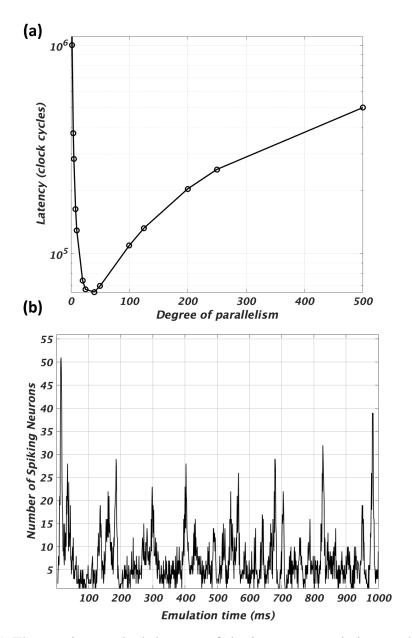

| Figure 7.7.  | (a) The maximum clock latency of the input accumulation module for varying degrees of parallelism, and (b) the number of spiking neurons for a SNN with 1000 fully-connected neurons over one second of emulation | 133 |

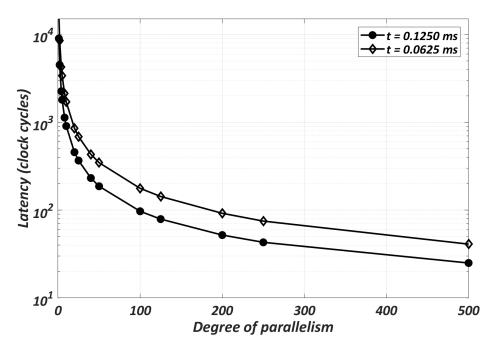

| Figure 7.8.  | The clock cycle budget for computing the neuron state equations with varying degrees of parallelism for a network with $N = 1000$ neurons over 1000 emulation time steps.                                         | 135 |

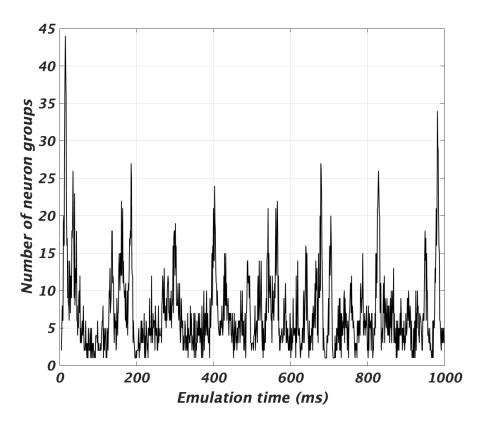

| Figure 7.9.  | The number of SN groups for $N = 1000$ neurons, $PDeg = 10$ , over 1000 emulation time steps                                                                                                                      | 136 |

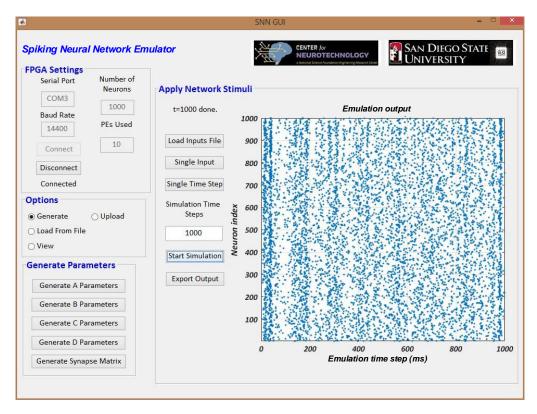

| Figure 7.10. | The developed graphical user interface for emulating and testing SNNs on FPGAs                                                                                                                                    | 138 |

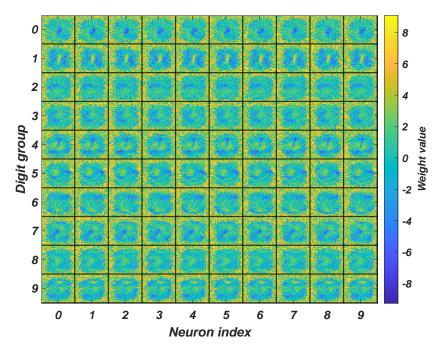

| Figure 7.11. | Weight matrices of the trained Izhikevich SNN                                                                                                                                                                     | 140 |

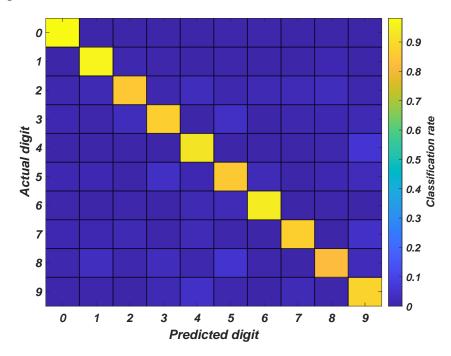

| Figure 7.12. | Confusion matrix for the SNN-based MNIST digit recognition task                                                                                                                                                   | 141 |

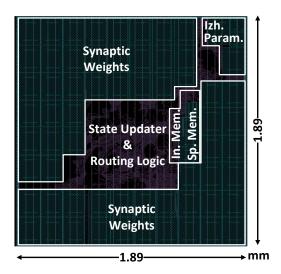

| Figure 7.13. | Layout of the implemented SNN hardware architecture in a standard 32-nm CMOS process.                                                                                                                             | 144 |

| Figure 8.1.  | The block diagram of the designed intention-aware in vivo BMI                                                                                                                                                     | 155 |

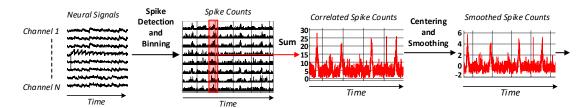

| Figure 8.3.  | Generating an estimate of the correlated channel's spike density. Binned spike counts are added per time step for a subset of correlated channels, followed by centering and smoothing                            | 156 |

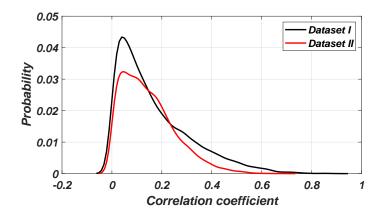

| Figure 8.2.  | The probability distributions of correlation coefficients between recording channels and the state transitions over the trials in Datasets I and II                                                               | 156 |

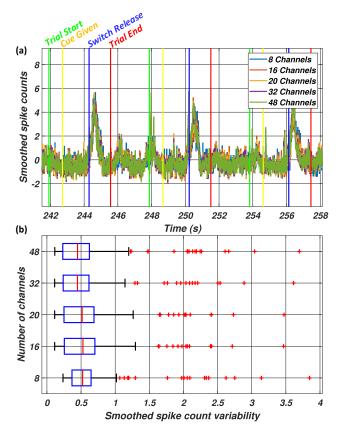

| Figure 8.4.  | (a) A sample from Dataset I of the smoothed spike counts during the trials and (b) the smoothed spike count variability during the non-BMI periods over both datasets.                                            | 159 |

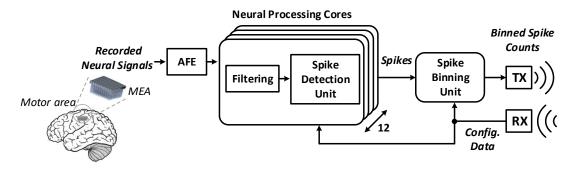

| Figure 8.6.  | The top-level block diagram of the designed intention-aware in vivo BMI.                                                                                                                                                                                                           | 162 |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

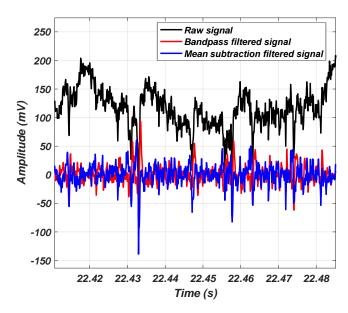

| Figure 8.5.  | The raw neural signal, the bandpass filtered signal, and the mean subtraction filter outputs                                                                                                                                                                                       | 162 |

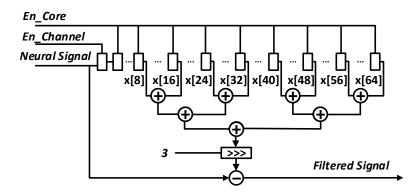

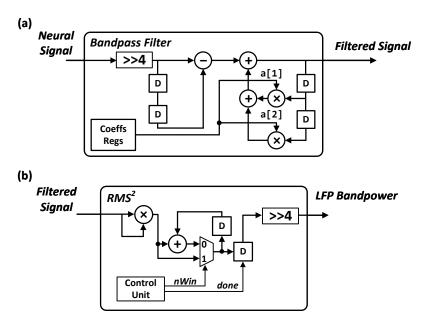

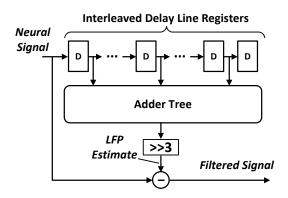

| Figure 8.7.  | The datapath of the LFP-removal moving average filter                                                                                                                                                                                                                              | 164 |

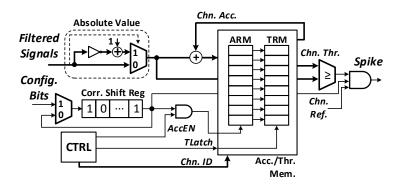

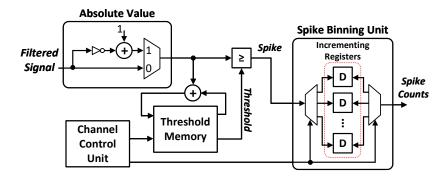

| Figure 8.8.  | The datapath of the spike detection unit                                                                                                                                                                                                                                           | 165 |

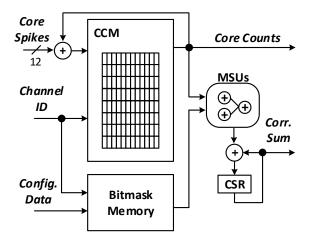

| Figure 8.9.  | The datapath of the spike binning unit                                                                                                                                                                                                                                             | 166 |

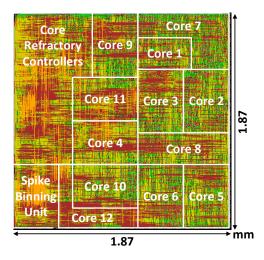

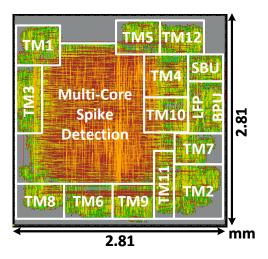

| Figure 8.10. | The ASIC layout of the designed intention-aware BMI system employing a 96-electrode Utah Array with 12 spike detection cores                                                                                                                                                       | 167 |

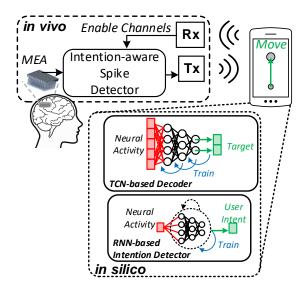

| Figure 8.11. | The system-level block diagram of our designed wireless BMI system for neural decoding applications                                                                                                                                                                                | 170 |

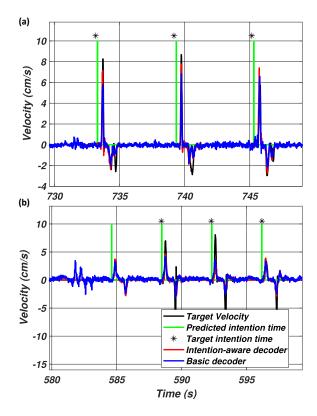

| Figure 8.12. | The outputs of the basic and intention-aware TCN-based decoders and the estimated intention times using the RNN-based intention estimator over the testing subset of (a) Dataset I and (b) Dataset II                                                                              | 171 |

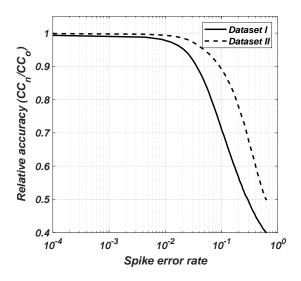

| Figure 8.13. | The relative accuracy of the TCN-based decoder over increasing values of SER                                                                                                                                                                                                       | 172 |

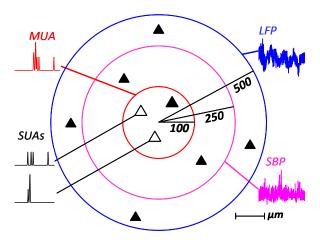

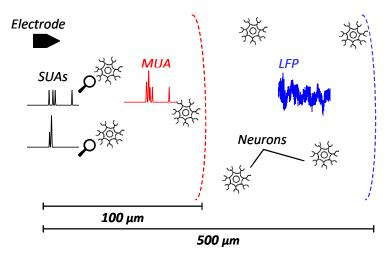

| Figure 9.1.  | The different signal modalities of intracortical recording electrodes                                                                                                                                                                                                              | 178 |

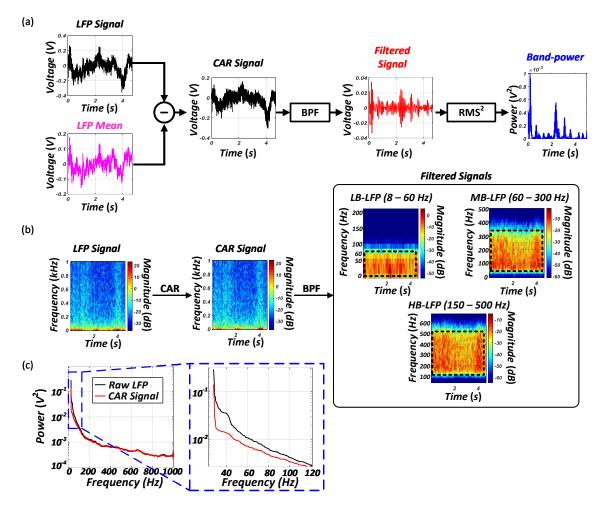

| Figure 9.2.  | (a) The block diagram of the in vivo LFP-based feature extraction pre-<br>processing. (b) The time-frequency power spectrum of the neural signals<br>during different phases of the feature extraction pre-processing. (c) The<br>spectral power of the raw LFP and the CAR signal | 180 |

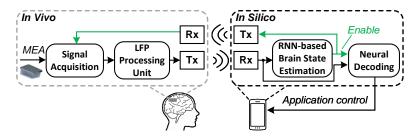

| Figure 9.3.  | The system-level block diagram of the designed brain-switch consisting of the in vivo LFP processing unit and in silico brain-state estimation                                                                                                                                     | 183 |

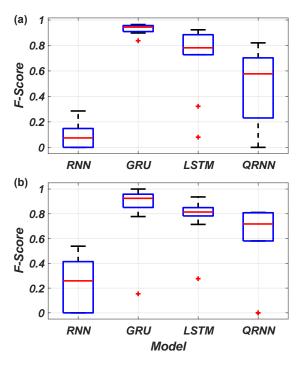

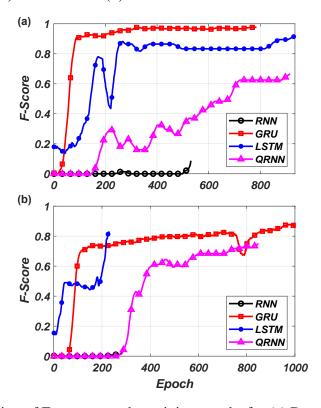

| Figure 9.4.  | The boxplots of the F-score of the four alternative RNN-based models over the first recording channel of (a) Dataset I and (b) Dataset II                                                                                                                                          | 186 |

| Figure 9.5.  | The variation of F-score over the training epochs for (a) Dataset I and (b) Dataset II.                                                                                                                                                                                            | 186 |

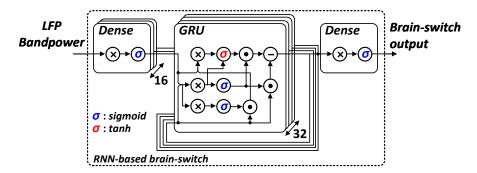

| Figure 9.6.  | The block diagram of the designed GRU-based LFP brain-switch                                                                                                                                                                                                                       | 187 |

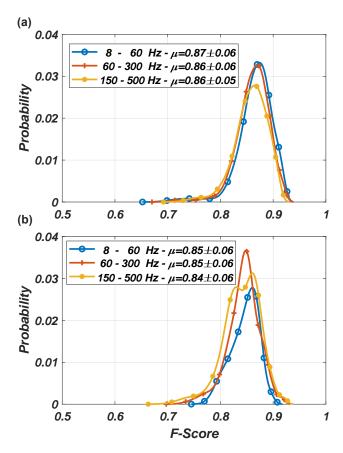

| Figure 9.7.  | The F-score probability distributions for (a) Dataset I and (b) Dataset II over the three frequency bands and all recording channels                                                                                                                                               | 188 |

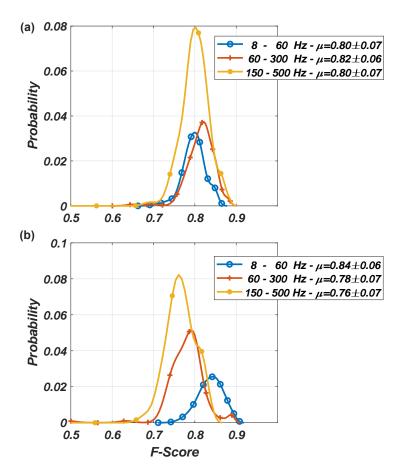

| Figure 9.8.  | The F-score probability distributions for (a) Dataset I and (b) Dataset II over the three frequency bands and all recording channels when removing CAR                               | 190 |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

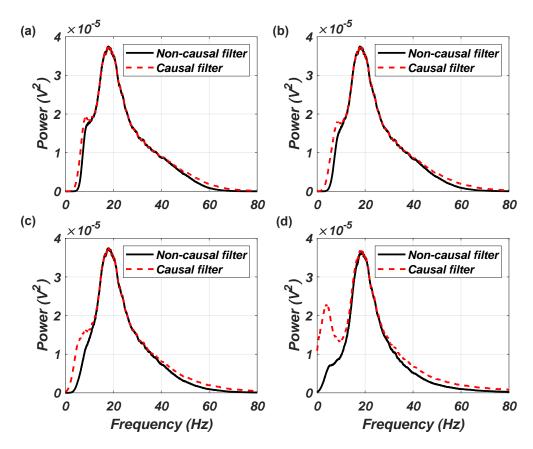

| Figure 9.9.  | The spectral power of the LB-LFP of non-causal and causal filters with filter order (a) $8$ , (b) $6$ , (c) $4$ , and (d) $2$ over the first channel of Dataset I                    | 191 |

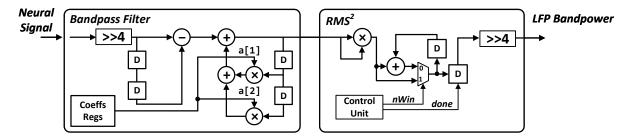

| Figure 9.11. | The block diagram of the in vivo signal processing for estimating LFP bandpower.                                                                                                     | 191 |

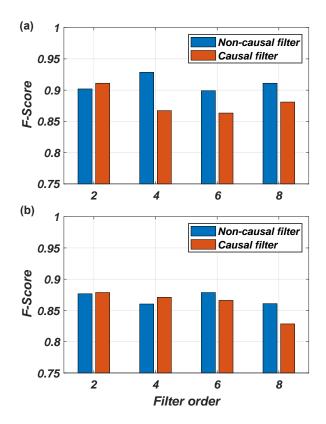

| Figure 9.10. | The F-score of the LFP-based RNN brain-switch model using various filter orders and filter causalities for the LB-LFP and the first channel of (a) Dataset I and (b) Dataset II      | 192 |

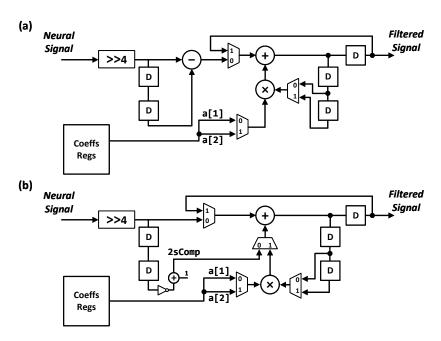

| Figure 9.12. | The block diagram of the designed band-pass filter with the folding factors of (a) two and (b) three                                                                                 | 193 |

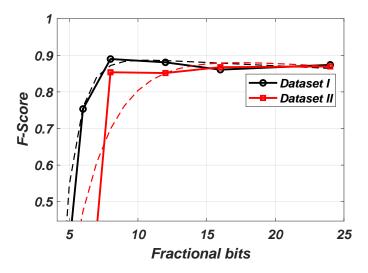

| Figure 9.13. | The variation of the F-Score of the designed RNN brain-switch over various number of fractional bits used for representing the bandpower, with the dashed lines indicating the trend | 194 |

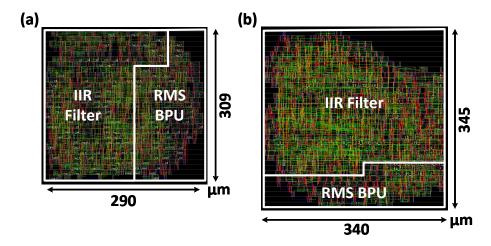

| Figure 9.14. | The ASIC layouts of the synthesized in vivo LFP-based feature extraction units for (a) the LB-LFP and (b) the programmable frequency band in a standard 180-nm CMOS process          | 196 |

| Figure 10.1. | The system configuration of a conventional wireless intracortical BCI                                                                                                                | 202 |

| Figure 10.2. | The various scales of neural signals using intracortical recording electrodes.                                                                                                       | 204 |

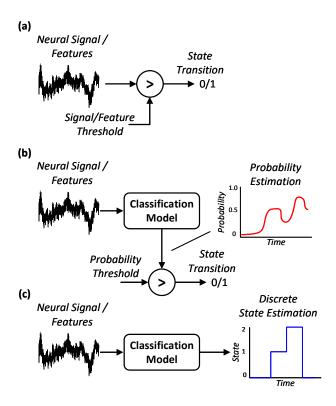

| Figure 10.3. | The block diagrams of (a) threshold-based, (b) classifier-based, and (c) discrete state classifier-based intention estimation                                                        | 209 |

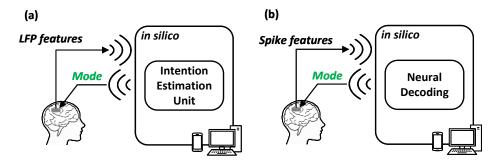

| Figure 10.4. | The block diagram of the designed hybrid BCI in the (a) inactive mode, and the (b) active mode                                                                                       | 210 |

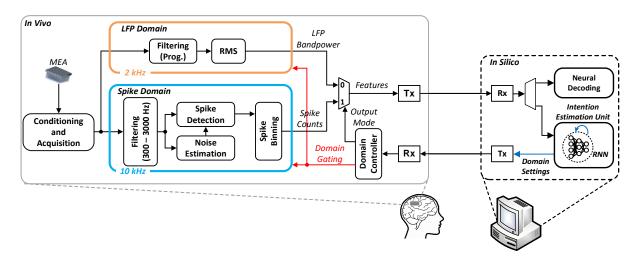

| Figure 10.5. | The top-level block diagram of the proposed hybrid asynchronous BCI                                                                                                                  | 210 |

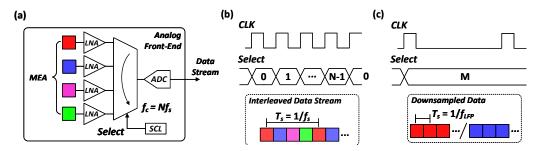

| Figure 10.6. | The block diagram of (a) the AFE configuration, (b) the interleaved sampling, and (c) the channel-configurable LFP downsampling                                                      | 211 |

| Figure 10.7. | The block diagram of (a) the second-order band-pass filter and (b) the RMS estimation unit                                                                                           | 212 |

| Figure 10.8. | The block diagram of the approximate LFP-removal filter                                                                                                                              | 213 |

| Figure 10.9.  | The block diagram of the absolute value-based spike detection and binning units.                                                     | 214 |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 10.10. | The ASIC layout of the designed and implemented hybrid BCI                                                                           | 215 |

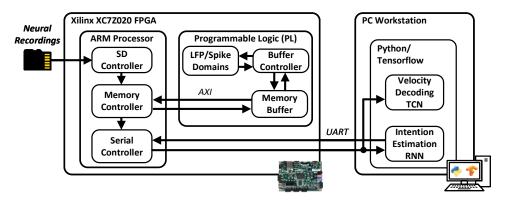

| Figure 10.11. | The block diagram of the implemented FPGA-based prototype system for functional verification of the designed hybrid asynchronous BCI | 218 |

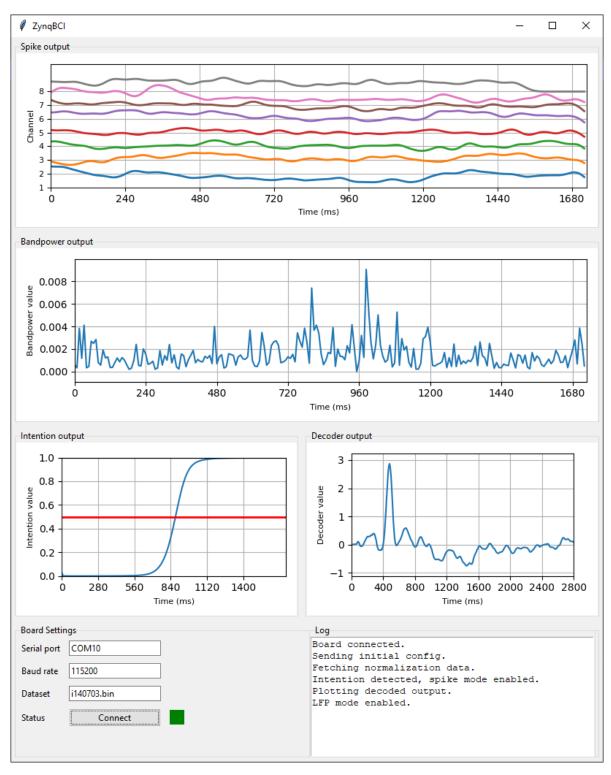

| Figure 10.12. | The custom-developed graphical user interface for functional verification of the designed and implemented hybrid asynchronous BCI    | 223 |

# LIST OF TABLES

| Table 2.1. | The computational complexity of various noise estimation methods over a one second window                                           | 15  |

|------------|-------------------------------------------------------------------------------------------------------------------------------------|-----|

| Table 2.2. | The mean F-scores of the candidate detection methods over the WaveClus datasets                                                     | 17  |

| Table 2.3. | The characteristics and implementation results of various spike detection ASICs                                                     | 23  |

| Table 2.4. | The validation and testing performance of the GRU-based RNN decoder using various potential in vivo spike detection methods         | 29  |

| Table 3.1. | The average classification accuracy of the BNN employing two encoding schemes over four different datasets and various noise levels | 40  |

| Table 3.2. | The ASIC characteristics and implementation results of various spike sorting systems                                                | 46  |

| Table 3.3. | The characteristics and implementation results of various spike sorting systems on FPGAs                                            | 48  |

| Table 4.1. | The classification accuracy of the PBNN over various datasets and quantization modes                                                | 59  |

| Table 4.2. | The power consumption of each ASIC module                                                                                           | 67  |

| Table 4.3. | The ASIC characteristics and implementation results of various spike sorting systems                                                | 69  |

| Table 5.1. | The ASIC characteristics of the designed and synthesized in vivo encoder over various values of MUF                                 | 91  |

| Table 5.2. | The characteristics and implementation results of in vivo neural signal compression ASICs                                           | 92  |

| Table 5.3. | The power consumption of the in vivo neural signal processing ASICs employing MUA, SUA, and LFP neural signals                      | 94  |

| Table 6.1. | The entropy rates for different neurons                                                                                             | 104 |

| Table 6.2. | The instruction set of the designed neural network processor                                                                        | 115 |

| Table 6.3. | The estimated number of instructions for various network operations                                                                 | 118 |

| Table 7.1.  | The neuron model and learning parameters for Izhikevich-based SNN digit recognition                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 139 |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Table 7.2.  | The characteristics and FPGA implementation results for various SNN realizations                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 141 |

| Table 7.3.  | The characteristics and ASIC implementation results for various SNN realizations                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 145 |

| Table 8.2.  | The energy dissipation of three alternative wireless BMI configurations. Configuration I constantly detects and transmits MUAs for all recording channels; Configuration II.a transmits and detects MUAs for a subset of channels for realizing a brain-switch algorithm on an external device; Configuration II.b detects MUAs for a subset of channels and realizes a brain-switch algorithm in vivo. Configurations II.a and II.b enable processing on all channels when the brain-switch algorithm denotes an "active" mental state. | 152 |

| Table 8.1.  | The in vivo BMI states and the in silico signal processing of the designed brain-switch scheme                                                                                                                                                                                                                                                                                                                                                                                                                                           | 152 |

| Table 8.3.  | The performance of alternative brain-state estimation methods over two datasets.                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 161 |

| Table 8.5.  | The ASIC characteristics and implementation results of the state-of-the-art spike detection circuits                                                                                                                                                                                                                                                                                                                                                                                                                                     | 167 |

| Table 8.4.  | The ASIC characteristics and implementation results of the intention-aware spike detection circuitry over various numerical formats                                                                                                                                                                                                                                                                                                                                                                                                      | 167 |

| Table 9.2.  | The characteristics and implementation results of various feature extraction ASICs.                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 195 |

| Table 9.1.  | The area utilization and power consumption of the designed and implemented LFP-based feature extraction unit                                                                                                                                                                                                                                                                                                                                                                                                                             | 195 |

| Table 10.1. | The estimated power consumption of the hybrid BCI for three different operating phases                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 216 |

| Table 10.2. | The characteristics and implementation results of various neural signal processing ASICs.                                                                                                                                                                                                                                                                                                                                                                                                                                                | 216 |

| Table 10.3. | The resource utilization of the implemented hybrid asynchronous BCI on a Zynq XC7Z020CLG400-1 FPGA.                                                                                                                                                                                                                                                                                                                                                                                                                                      | 218 |

| Table 10.4. | The AXI control and status registers of the developed BCI Wrapper                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 219 |

#### **ACKNOWLEDGEMENTS**

Starting out the Ph.D. five years ago I knew this would be a big undertaking. Completing the Ph.D. would not have been possible without the support group I had from various parts of my life. I'd like to thank my advisor Professor Amir Alimohammad for his constant guidance, not only during the Ph.D., but also during the end of my Bachelor's and throughout my Master's studies. Professor Alimohammad gave me an opportunity to get involved in research in the VLSI Lab at SDSU, and had I not taken up the offer I would not have grown as much as I have as both a scholar and a person. In truth, being the first of my family to attend University, I wasn't truly aware about higher levels of education and would not have believed it to be something I could achieve if it had not been for Professor Alimohammad's encouragement. I'd also like to thank Professor Patrick Mercier for accepting to be my co-advisor during the PhD and providing key insights for my publications, particularly on the analog circuit side of things. Special thanks go to the rest of my doctoral committee: Professor Gert Cauwenberghs, Professor Drew Hall, and Professor Hakan Toreyin. I appreciate the valuable questions and suggestions you have made toward my research and this final dissertation.

Part of my support group includes my friends, who helped keep me sane during stressful times, such as preparing for exams and making constant paper revisions late into the nights. In no particular order, Ezra, Jake, Jesus Leon, Jesus Fematt, Andrew, Abe, Carter, Nutdanai, Kristian, those games of Caverna and Terra Mystica (and the rare Agricola) meant more to me than you could know, I thank you for indulging me all those times. I certainly cannot forget those friend trips to the Grand Canyon, Sedona, and Yosemite, which seemed to come at just the right times to avoid burnout and get out a for a while. Former VLSI lab-mates and fellow students, your companionship was invaluable during my studies, special thanks go to Rushabh, Vishnu, Michael, Mauro, Mitchell, Xinqiao, Nick, Jose, Omar, and Raghu. I will always remember the illuminating discussions regarding Verilog and MATLAB programming, as well as our philosophical discussions over freshly brewed pour-over coffee.

Of course, none of this would have been possible without the support and encouragement

of my family. I appreciate all of the family trips, meals, and constant support as I worked toward not only the Ph.D., but other goals in my life. During rough times, I am sure my family believed in me more than I believed in myself. This dissertation, the publications, and the degree are not mine alone, but a mutual accomplishment we share.

This work was supported, in part, by the Center for Neurotechnology, a *National Science Foundation* (NSF) *Engineering Research Center* (EEC-1028725), the NSF Award #2007131, and the *San Diego State University Graduate Fellowship*.

This dissertation is based on various articles that have been published in or submitted to peer-reviewed journals, all of which are first-authored by the author of this dissertation.

Chapter 2 is primarily based on the paper by D. Valencia, P. P. Mercier, and A. Alimohammad, titled "In vivo neural spike detection with adaptive noise estimation," published in the *Journal of Neural Engineering*, vol. 19, 046018, July 2022. The author of this dissertation is the lead investigator and primary author of this paper.

Chapter 3 is primarily based on the paper by D. Valencia and A. Alimohammad, titled "Neural spike sorting using binarized neural networks," published in the *IEEE Transactions on Neural Systems and Rehabilitation Engineering*, vol. 29, pp. 206 – 214, December 2020. The author of this dissertation is the lead investigator and primary author of this paper.

Chapter 4 is primarily based on the paper by D. Valencia and A. Alimohammad, titled "Partially binarized neural networks for efficient spike sorting," published in the *Biomedical Engineering Letters*, vol. 13, pp. 73 – 83, February 2023. The author of this dissertation is the lead investigator and primary author of this paper.

Chapter 5 is primarily based on the paper by D. Valencia, P. P. Mercier, and A. Alimohammad, titled "Efficient In Vivo Neural Signal Compression Using an Autoencoder-based Neural Network," published in the *IEEE Transactions on Biomedical Circuits and Systems*, vol. 18, pp. 691 – 701, January 2024. The author of this dissertation is the lead investigator and primary author of this paper.

Chapter 6 is primarily based on the paper by D. Valencia and A. Alimohammad, titled

"Towards in vivo neural decoding," published in the *Biomedical Engineering Letters*, vol. 12, pp. 185 – 195, May 2022. The author of this dissertation is the lead investigator and primary author of this paper.

Chapter 7 is primarily based on the paper by D. Valencia and A. Alimohammad, titled "A generalized hardware architecture for real-time spiking neural networks," published in *Neural Computing and Applications*, vol. 35, pp. 17821 – 17835, August 2023. The author of this dissertation is the lead investigator and primary author of this paper.

Chapter 8 is primarily based on the paper by D. Valencia, G. Leone, N. Keller, P. P. Mercier, and A. Alimohammad, titled "Power-efficient in vivo brain-machine interfaces via brain-state estimation," published in the *Journal of Neural Engineering*, vol. 20, 016032. The author of this dissertation is the lead investigator and primary author of this paper.

Chapter 9 is primarily based on the paper by D. Valencia, P. P. Mercier, and A. Alimohammad, titled "An efficient brain-switch for asynchronous brain-computer interfaces," published in the *IEEE Transactions on Biomedical Circuits and Systems*, May 2024. The author of this dissertation is the lead investigator and primary author of this paper.

Chapter 10 is primarily based on the paper by D. Valencia, P. P. Mercier, and A. Alimohammad, titled "A hybrid brain-computer interface for low-power and efficient neural decoding," submitted to the *IEEE Transactions on Biomedical Circuits and Systems*. The author of this dissertation is the lead investigator and primary author of this paper.

Daniel Valencia

December 2024

San Diego, CA

# VITA

| 2016      | Bachelor of Science, San Diego State University, San Diego                                                     |

|-----------|----------------------------------------------------------------------------------------------------------------|

| 2018–2024 | Instructional Student Assistant, Department of Electrical and Computer Engineering, San Diego State University |

| 2018–2024 | Research Assistant, VLSI Design and Test Lab<br>San Diego State University, San Diego                          |

| 2019      | Masters of Science, San Diego State University, San Diego                                                      |

| 2024      | Doctor of Philosophy, University of California San Diego and San Diego State University, San Diego             |

#### ABSTRACT OF THE DISSERTATION

Towards Autonomous Brain-Computer Interfaces: Approaches, Design, and Implementation

by

#### Daniel Valencia

Doctor of Philosophy in Engineering Science (Electrical and Computer Engineering)

University of California San Diego, 2024

Professor Patrick Mercier, Co-Chair Professor Amir Alimohammad, Co-Chair

Autonomous brain-computer interfaces (BCIs) are devices designed to record, process, and interpret neural activity, enabling individuals with neurodegenerative diseases or spinal cord injuries to regain their ability to interact with their environment without assistance. Over the past two decades, BCI technology has advanced remarkably, largely due to improvements in neural recording interfaces, such as high-density micro-electrode arrays (MEAs). These innovations allow researchers to collect more comprehensive neural data, enhancing our understanding of neural dynamics and their interaction with human physiology. However, BCI technology still faces three major challenges that hinder its progression toward practical applications.

- 1. **Data overload**: Modern MEAs, with their increased number of recording channels, generate vast amounts of data. Consequently, the power consumption required to acquire, process, and transmit this data becomes a significant barrier, especially given tissue-safe design constraints. This dissertation investigates three effective approaches to reduce data rates, and thus power consumption: spike detection, spike sorting, and neural signal compression, all of which leverage relevant signal features for specific applications.

- 2. **Neural decoding versatility**: No single neural decoding algorithm suits all applications or users. Therefore, a versatile BCI system must be capable of executing a range of neural decoding algorithms. This dissertation examines the efficient design and implementation of two processor architectures supporting various neural decoding schemes. One processor uses fine-grained sequential processing to implement arbitrary machine-learning-based neural decoding models, while the other employs biologically plausible neuron models to realize a spiking neural network.

- 3. **Autonomous user engagement**: Traditional BCIs require users to engage with the system during predefined time periods. This dissertation explores two methods for estimating a user's intention to engage with a BCI application: one using high-frequency neural spikes and the other using low-frequency local field potentials. A hybrid (multi-signal) asynchronous BCI is designed, implemented, and verified, combining both neural signal types to optimize intention estimation and improve neural decoding performance.

The approaches discussed in this dissertation present practical strategies to advance BCI technology by reducing power consumption, enabling flexible and robust neural decoding, and incorporating various neural signal features for efficient user intention estimation.

# **Chapter 1**

# Introduction

# 1.1 Introduction

The human brain is a remarkable product of human evolution. Within the brain, billions of cells, called neurons, interact with one another to enable a myriad of human behaviors, both autonomic- such as our ability to breathe without conscious effort- and voluntary, such as controlling our hands and feet to operate a vehicle. Neurons convey information to one another by firing action potentials through connections known as synapses [1]. The mechanism underlying the generation of action potentials relies on ionic current flow during the operation of the neuron. This shifting ionic balance causes variations in the voltage potential in the regions between neurons [2]. This voltage potential can be recorded by using penetrating electrodes, which initiates the process of interpreting neural activity. The concept of relating neural activity to physiological control began in the 1980s, with the pioneering work by Fetz et al. which studied how the activity of cortical motor neurons modulated muscle movement [3, 4]. These studies unlocked the idea of neural decoding, whereby brain activity can be mapped to a known variable or representation. For example, seminal work by Georgopoulos et al. proposed population vector coding, a concept suggesting that the direction of movement is represented as the weighted average of the preferred direction of a population of neurons [5]. Brain-computer interfaces (BCIs) have the potential to become foundational tools for aiding people suffering from spinal cord injury or other neuro-degenerative diseases. Studies have shown that, although a person may lose a limb due to an accident, the underlying neural circuitry that controls motor activity remains functional and active [6].

# 1.2 The State of the Art and Challenges of BCI

BCI technology has made significant progress over the past two decades. In particular, advances in neural recording technology now allow for simultaneous recording from thousands of sites [7, 8, 9]. This progress has enabled neuroscientists to deepen their understanding of the mechanisms underpinning various neurophysiological processes. Additionally, the rapid

growth of machine learning algorithms has allowed researchers to develop relatively robust neural decoding models. By employing a data-driven approach, decoding performance has surpassed that of the hand-tuned models of the past [10]. For example, combining computer-aided assistance, such as typing auto-correction, with neural decoding has been shown to vastly improve communication speed in recent studies [11]. Similarly, artificial intelligence has been shown to enhance BCI control by improving movement-related tasks [12].

BCI applications have also extended beyond traditional kinematic decoding, including recent studies demonstrating the ability to decode speech from neural activity [13, 14]. It should be noted that the majority of these BCI studies focus on either non-invasive recording modalities, such as electroencephalography (EEG), or are limited to clinical or lab-based settings. In such settings, data transmission is typically performed through wired connections to ensure highfidelity neural recordings. However, these wired connections pose challenges for long-term use, as they may not be safe or hygienic. As a result, there is significant ongoing research aimed at developing implantable BCIs with low-power wireless telemetry, such as backscatter communication [15] or near-field communication (NFC) for both wireless power and data transmission [16]. A key challenge in realizing wireless implantable BCIs is minimizing overall power consumption and energy dissipation, as increased in vivo processing can cause neural tissue temperatures to raise by more than 1° C, potentially leading to tissue damage [17]. To address this, extensive research efforts have focused on designing efficient implementations of various in vivo digital neural signal processing algorithms [18, 19, 20, 21, 22, 23, 24, 25]. However, even with all of these advancements, BCI technology remains in its early stages of development for practical daily use. This is due to three main challenges in BCI technology. First, the amount of data generated by modern recording circuitry is staggering. This can be partly attributed to two conflicting objectives in the development of modern neural recording interfaces. On one hand, increasing the total number of recording sites can be extremely useful for scientific inquiry. For example, recording electrodes employing high-density configurations are essential for resolving the activities of individual neurons over long periods of time [26]. However, using

such electrodes not only increases the amount of data generated but also heightens operational demands. For instance, more recording sites require greater power for signal acquisition and conditioning. Additionally, the wireless transmission circuitry would require high-bandwidth telemetry to handle the increased data rate. On the other hand, studies have shown that for practical neural decoding purposes, such fine-grained high-density neural recordings are not required to achieve acceptable performance. For example, a recent study demonstrated how a state-of-the-art "thought-to-text" BCI was realized using a relatively simple 10x10 microelectrode array (MEA) [11]. This dissertation thus covers three approaches to reduce the overall amount of data generated and transmitted for neural decoding, effectively lowering overall system power consumption to meet tissue-safe design constraints. The foundational approach for two of these methods is to focus neural recording on the activity of individual neurons, representing neural activity as a discrete sequence of action potential (spike) events. The first method involves performing spike detection, where the recorded neural activity is limited to that of nearby neurons instead of recording and transmitting the entire signal. The second method builds upon spike detection by providing finer granularity through spike sorting. In this approach, after spikes are detected, the activities of individual neurons are distinguished from one another. By targeting specific types of neurons, spike sorting further reduces the output data rate compared to spike detection. Both methods convert the continuous neural signals into discrete event-based signals, such that periods without spiking activity do not require wireless transmission. In certain applications, however, it may be beneficial to transmit continuous neural activity rather than reducing it to spike events, which might limit the recorded information due to the spatial selectivity of neurons [27, 28]. For example, the local field potential (LFP) represents the activities of entire neuron populations, extending beyond those near the recording electrode. The LFP has been shown to encode information in various forms, such as the power at different frequencies or specific variations in the continuous voltage waveforms [29]. A notable advantage of these signals is that their information exists at relatively low frequencies, typically up to 500 Hz. For these types of signals, signal compression can be employed. Rather than using

conventional compression schemes such as rate coding or difference encoding, this dissertation explores a machine-learning-based compression scheme that leverages the nature of neural signals and the characteristics of multi-channel recording arrays.

Secondly, the large amount of inter-subject variability poses significant challenges in developing robust neural decoding algorithms. For example, a neural decoding algorithm tailored to one person may not be applicable to another. Additionally, due to the non-stationary nature of neural activity, a decoding algorithm designed for a specific individual may require periodic calibration or updates to maintain acceptable performance over extended periods of time. To tackle these challenges, this dissertation presents the efficient design and implementation of two processor architectures capable of executing a wide range of neural decoding algorithms. The first processor employs fine-grained sequential processing to implement various machine-learning-based decoding models, including convolutional neural networks and recurrent neural networks. The second processor utilizes biologically-plausible neuron models to realize a generalized spiking neural network.

Thirdly, traditional BCIs require users to engage with the application during predefined time periods. One vital step toward transitioning BCI technology to practical implementations is enabling a mechanism by which the user can control the BCI engagement. Not only would this reduce unnecessary processing, but it would also restore user autonomy to individuals who currently require the assistance of a caregiver or clinician. Thus, a critical step toward realizing autonomous BCI systems is estimating the user's intention to engage with the BCI application. This is also referred to as the asynchronous processing paradigm, where the user controls when the BCI application is active or inactive. However, the process of intention estimation necessitates constant monitoring of the neural activity for specific biomarkers that indicate user intention. This dissertation explores two methods for efficient and low-power user intention estimation. The first method employs spikes to detect user intention, while the second relies on the LFP. Specifically, this dissertation details the algorithms for intention estimation and the digital circuit optimizations required to achieve constant monitoring with minimal overhead.

Finally, a hybrid asynchronous BCI is proposed that combines both spikes and LFPs to optimize intention estimation while maintaining neural decoding performance.

Overall, the approaches and implementations discussed in this dissertation provide a foundation for enabling low-power, autonomous BCI systems. By optimizing the design of brain-computer interfaces to meet practical use constraints, these advancements serve to extend device lifespan and enhance the overall user experience.

# **Chapter 2**

# In Vivo Neural Spike Detection with Adaptive Noise Estimation

# 2.1 Introduction

Damage to the spinal cord can disrupt the pathway of signals sent between the brain and the body and may result in partial or complete loss of both motor and sensory functions. The loss of these functions can have devastating implications on the quality of one's life. Currently, most patients living with paralysis require around-the-clock assistance to fulfill their daily tasks, which can be cost-intensive and deprive their sense of independence. Extraction of motor intent directly from the brain using brain-machine interfaces (BMIs) have shown to be promising in generating control signals for external assistive devices. However, complex brain processes are reflected by the activity of large neural populations and that the study of a few neurons provide relatively limited information [30].

Biological neurons communicate information among each other via electrical pulses, called action potentials or spikes. Conventional micro-electrode arrays (MEAs), such as Utah Array, are able to record from hundreds of electrodes [31]. Each electrode records spikes from multiple neurons close to the electrode's tip. In fact, the neural signal on a recording electrode is the cumulative electrical activity of various nearby neurons contaminated with noise, which is referred to as multi-unit activity (MUA), offering an extracellular recording. In general the background noise is a non-Gaussian random process due to various issues including electrode drift during operation, tissue-electrode interface noise, electronics noise, variation in the spike shape, the presence of overlapping spikes, and correlations between spikes and local field potentials. Using conventional MEAs, it is not possible to precisely place electrodes to individually record from a single neuron. Extracellular electrodes detect changes in electrical potentials from a vicinity of a neuron (about 140 micrometers) where generally tens of neurons are present [32]. Researchers, however, often require single-neuron activity for the study of how neurons are correlated with each other for specific stimulus [33, 34]. Also, the algorithms employed for accurate neural decoding typically process spike trains, which represent the action potentials of individual neurons over time [35].

For detecting the spiking activity of neurons, the continuous recorded analog signal by the MEA is first amplified and then converted into a digital signal. The digitized signal is then passed through a band-pass filter typically between 300 Hz and 3000 Hz. Frequencies below 300 Hz are filtered to remove low-frequency activity and the upper cutoff frequency is set to diminish the noisy appearance of the spike shapes [36]. After filtering, spike detection attempts to separate the high amplitude spike signals from the low amplitude neural background noise. The background noise can be either fixed to a specific value or it can be estimated dynamically. The noise threshold is often set to a scaled version of the background noise. Detecting neural spikes is performed in two phases, the pre-processing to emphasize the spikes from the background noise and then applying the estimated threshold to the pre-emphasized signal. Spikes are interpreted as occurring when the pre-emphasized signal crosses the noise threshold. The spike detection process can thus return the spike waveform itself in addition to the time an action potential occurs.

This chapter focuses on the development of an accurate spike detection module toward implantable in vivo operation that can adapt to changes in channel statistics autonomously. The rest of this chapter is organized as follows. Section 2.2 presents the impact of various filtering methods on the performance of spike detection as well as the commonly employed signal pre-emphasis algorithms and alternative techniques for noise estimation. The computational complexity and feasibility of the pre-emphasis and noise estimation techniques for in vivo spike detection are discussed and compared. Section 2.3 quantifies the performance of various combinations of the pre-emphasis and noise estimation methods for spike detection using the widely-employed WaveClus synthetic datasets [37]. Section 2.4 presents the design and hardware implementation of our designed detection technique with adaptive noise estimation. Section 2.5 quantifies the reliability of our designed and implemented spike detection module and its application in neural decoding. Finally, Section 2.6 makes some concluding remarks.

# 2.2 Filtering, Pre-processing, and Noise Estimation Algorithms

After the amplification and analog-to-digital conversion of the recorded neural signals, spike detection, which consists of filtering, pre-emphasis, noise estimation, and thresholding, is applied. Filtering is used to remove unwanted frequency components from the recorded neural signals. For example, low frequency local field potential (LFP), with the frequency of about 250 Hz, are removed. Pre-emphasis involves processing of the filtered neural signals to discern the neural activity from ambient background noise. The ambient background noise is estimated dynamically, which is used to derive a threshold value that the pre-emphasized neural signal must exceed in order to be detected as spikes.

From the perspective of in vivo signal processing, low-order filters are preferable due to their lower computational complexity and memory requirements. Using Matlab's FilterDesigner toolbox, we designed five candidate band-pass causal filters, Equiripple FIR, Butterworth IIR, Chebyshev Types I and II IIR, and Elliptical IIR filters. Each of the filters had the following characteristics: Sampling rate of 24 kHz, high-pass frequency of 300 Hz, low-pass frequency of 3000 Hz, 60 dB of attenuation in both stop bands, unity gain and 1 dB of ripple in the pass band, and the filter orders between 4 and 10.

Figs. 2.1 (a) and (b) illustrate the impact of causal and non-causal filtering, respectively, on the spike waveforms with various sixth-order filters. Non-causal filtering was realized using MATLAB's filtfilt function. It can be seen that the causal filter realizations reduce the spike amplitude and more importantly, impose a phase delay to the signal. In the case of the Cheby2 realization, the signal is severely attenuated when using a relatively low order of six. Fig. 2.1 (b) shows the benefit of utilizing non-causal filtering, which ensures zero phase shift. Also, the amplitudes and shapes of the spike waveforms are better preserved compared to the causal filtering. Figs. 2.1 (c) and (d) show the bloxplots of the Euclidean distance between actual spike waveforms and the filtered spikes employing causal and non-causal filtering, respectively.

**Figure 2.1.** The impact of (a) causal filtering and (b) non-causal filtering on the spike waveform shapes. The boxplots (c) and (d) show the variations of the Euclidean dsitance between actual spike waveforms and the filtered spikes employing causal and non-causal filtering, respectively.

It is shown that the Equiripple FIR filter provides the least Euclidean distance among the various filter realizations.

In this work we consider two of the most commonly employed pre-emphasis methods, Non-linear energy operator (NEO) [38], and Absolute value (ABS) [37]. Energy-based signal pre-emphasis methods such as NEO accentuate the spikes by computing the energy of the signal. NEO is given as

$$\psi[n] = x[n]^2 - x[n-1] \times x[n+1], \tag{2.1}$$