#### Quadratic and linear optimization with analog circuits

by

Sergey Vichik

A dissertation submitted in partial satisfaction of the requirements for the degree of Doctor of Philosophy

in

Engineering - Mechanical Engineering

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Professor Francesco Borrelli, Chair Professor Roberto Horowitz Professor Ilan Adler

Fall 2015

## Quadratic and linear optimization with analog circuits

Copyright 2015 by Sergey Vichik

#### Abstract

Quadratic and linear optimization with analog circuits

by

Sergey Vichik

#### Doctor of Philosophy in Engineering - Mechanical Engineering

University of California, Berkeley

Professor Francesco Borrelli, Chair

In this work we propose and investigate a new method of solving quadratic and linear optimization problems using analog electrical circuits instead of digital computation.

We present the design of an analog circuit which solves Quadratic Programming (QP) or Linear Programming (LP) problems. In particular, the steady-state circuit voltages are the components of the QP (LP) optimal solution. The thesis shows how to construct the circuit and provides a proof of equivalence between the circuit and the QP (LP) problem.

We study the stability of the analog optimization circuit. The circuit dynamics are modeled as a switched affine system. A piece-wise quadratic Lyapunov function and the KYP lemma are used to derive the stability criterion. The stability criterion characterizes the range of critical circuit parameters for which the QP circuit is globally asymptotically stable.

The proposed method is used to build a printed circuit board (PCB) using programmable components to allow solution of various QP problems. The board supports implementation of an MPC controller for buck DC-DC converter. We conduct an experimental study to evaluate the performance of the analog optimization circuit.

We study the feasibility of very high speed implementation of the optimization circuit using Analog Very Large Scale Integration (AVLSI) technology. In AVLSI, all the required circuit components are built on top of a silicon substrate using advanced photo-lithographic technologies. AVLSI circuits are fast, small and cheap. Thus, AVLSI implementation is paramount to make the proposed technology commercially competitive.

We discuss the possible usage of the proposed method to make fast MPC controllers, image processors, communication decoders and analog co-processors. In fact, any application that requires a repeating solution of related optimization problems can benefit from this technology. Besides being faster than the digital computers, analog computers are more power efficient, may occupy smaller area on silicon and may be more resilient in harsh environments. This dissertation is dedicated to my wife that bravely followed and supported me during those years, to my children — Adam and Eitan who may one day be inspired by this experience, and to my father whose ideas sowed a seed that started this work.

# Contents

| Co | ntents                                                                                                                                                                                                                                    | ii              |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| Li | t of Figures                                                                                                                                                                                                                              | $\mathbf{iv}$   |

| Li | t of Tables                                                                                                                                                                                                                               | viii            |

| 1  | Introduction         1.1       Motivation                                                                                                                                                                                                 | $\frac{3}{4}$   |

| 2  | Literature Review         2.1 "Classical" Analog Computers         2.2 Previous Work on Analog Optimization         2.3 Applications of analog optimization                                                                               | 8               |

| 3  | The novel QP/LP optimization circuit3.1 Problem statement3.2 Analog QP Circuit3.3 Analog LP circuit                                                                                                                                       | 13              |

| 4  | Steady state analysis of the QP/LP circuit4.1Steady state solution of the QP circuit4.2Equivalence of the QP optimization problem and the electric circuit4.3Designing quadratic cost objective4.4Steady state solution of the LP circuit | 24<br>26        |

| 5  | Dynamical analysis         5.1       Dynamic Model         5.2       Compact Form – Hybrid Model         5.3       Global Asymptotic Stability         5.4       Practical implications of the circuit stability criterion                | $\frac{38}{42}$ |

iii

| 6  | Implementation of QP solver on a PCB         6.1       Introduction                                                                                          | <b>48</b><br>48<br>48<br>50<br>59<br>70 |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|

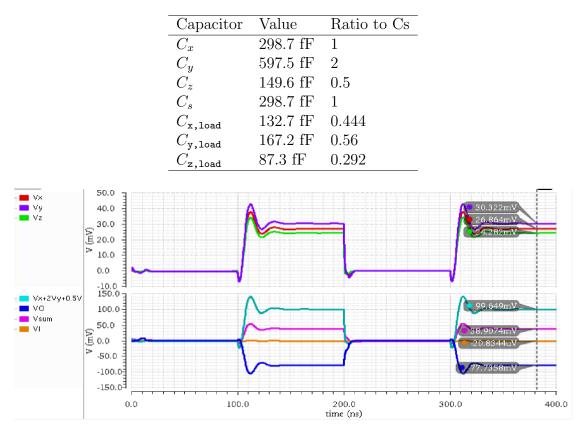

| 7  | Analog VLSI chip implementation7.1 Resistor based VLSI design7.2 Capacitor variant of the optimization circuit7.3 Capacitor based VLSI design                | <b>72</b><br>72<br>86<br>92             |

| 8  | Applications of analog optimization8.1Solution of a linear system of equalities.8.2Error correcting decoding of linear codes8.3Image processing8.4Conclusion | <b>99</b><br>99<br>101<br>107<br>110    |

| Bi | ibliography                                                                                                                                                  | 111                                     |

| Α  | Optimization problems for PCB board                                                                                                                          | 119                                     |

# List of Figures

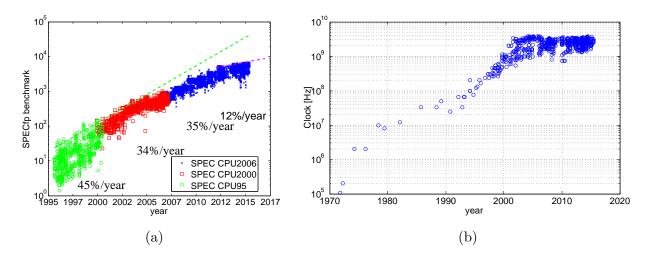

| 1.1 | <ul> <li>(a) CPU floating point benchmarks from SPEC CPU95, CPU2000 and CPU2006 [86].</li> <li>(b)Clock speed of Intel processors [67, 85].</li> </ul>                                                                                                                 | 2  |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.1 | <ul> <li>(a) A planispheric astrolabe from the workshop of Jean Fusoris in Paris circa 1400, on display at the Putnam Gallery in the Harvard Science Center. Sage Ross, Wikimedia Commons.</li> <li>(b) Exploded computer reconstruction of the Antikythera</li> </ul> |    |

| 2.2 | Mechanism, from [31]                                                                                                                                                                                                                                                   | 7  |

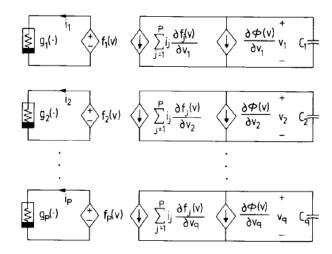

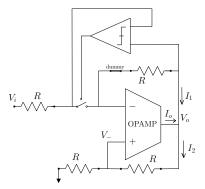

|     | implement Lagrangian for KKT optimality conditions.                                                                                                                                                                                                                    | 9  |

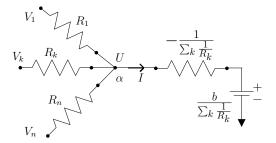

| 3.1 | Equality enforcing circuit consisting of $n$ resistors $(R_1 \ldots R_n)$ , a negative resistance, and a reference voltage.                                                                                                                                            | 15 |

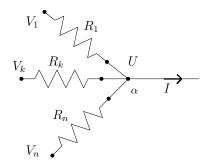

| 3.2 | A node with $n$ connected wires                                                                                                                                                                                                                                        | 15 |

| 3.3 | Inequality enforcing circuit.                                                                                                                                                                                                                                          | 16 |

| 3.4 | Quadratic cost circuit.                                                                                                                                                                                                                                                | 17 |

| 3.5 | Analog circuit solving a QP. Vertical wires are variable nodes with potentials $V_1 \ldots V_n$ . Black dots represent resistances that connects vertical and horizontal                                                                                               |    |

|     | wires. Horizontal wires are cost or constraint nodes. Some of the horizontal                                                                                                                                                                                           |    |

|     | wires are connected to a ground via a negative resistance $R_i = -\left(\sum_j \frac{1}{R_{ij}}\right)^{-1}$ , a                                                                                                                                                       |    |

|     | constant voltage source and a diode for inequality nodes.                                                                                                                                                                                                              | 19 |

| 3.6 | Compact representation of a resistor.                                                                                                                                                                                                                                  | 19 |

| 3.7 | Linear cost circuit.                                                                                                                                                                                                                                                   | 20 |

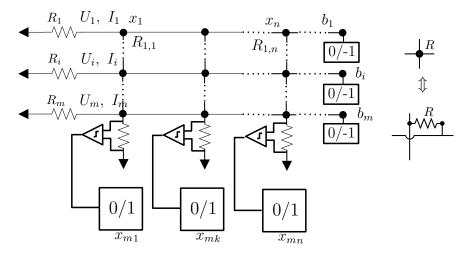

| 3.8 | Electric circuit solving an LP. Vertical wires are variable nodes with potentials                                                                                                                                                                                      |    |

|     | $V_1 \ldots V_n$ . Black dots represent resistances that connects vertical and horizontal                                                                                                                                                                              |    |

|     | wires. Horizontal wires are cost or constraint nodes. Each horizontal wire is                                                                                                                                                                                          |    |

|     | connected to a ground via a negative resistance, a constant voltage source and a                                                                                                                                                                                       |    |

|     | diode for inequalities nodes. The topmost horizontal wire is the linear cost circuit                                                                                                                                                                                   |    |

|     | which is connected to a constant voltage source $U_{\text{cost}}$ .                                                                                                                                                                                                    | 20 |

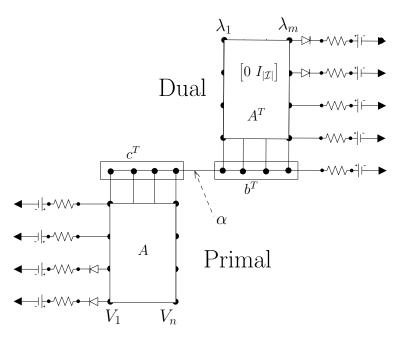

| 4.1<br>4.2          | Circuit implementing the primal-dual feasibility problem (4.42). Primal and dual parts are connected via the zero duality gap constraint. For compactness, $b_+$ and $b$ are represented as $b$ , and $\lambda$ is part of $\lambda$ | 33                                      |

|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|

|                     | are assumed to be zero.                                                                                                                                                                                                              | 34                                      |

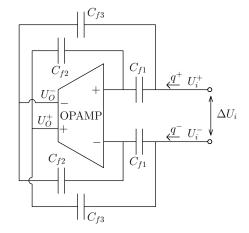

| $5.1 \\ 5.2 \\ 5.3$ | Realization of negative resistance using operational amplifier                                                                                                                                                                       | 37<br>37                                |

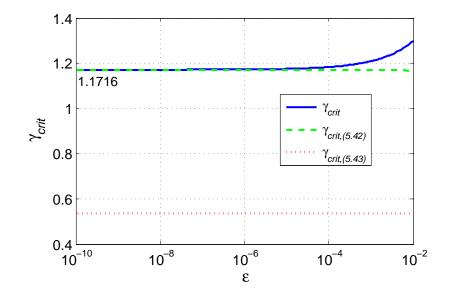

| 5.4                 | is the current $\overline{I}$ The tight bound $\gamma_{\text{crit}}$ , and the conservative bounds $\gamma_{\text{crit},(5.42)}$ and $\gamma_{\text{crit},(5.43)}$ vs $\varepsilon$ as in Lemma 9.                                   | 40<br>47                                |

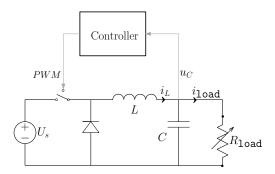

| 6.1                 | Buck DC-DC converter                                                                                                                                                                                                                 | 49                                      |

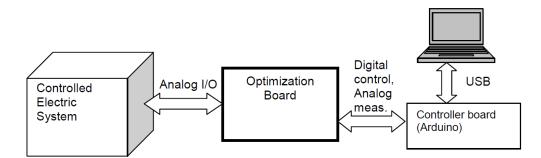

| 6.2                 | Block diagram of a system that includes an optimization board                                                                                                                                                                        | 50                                      |

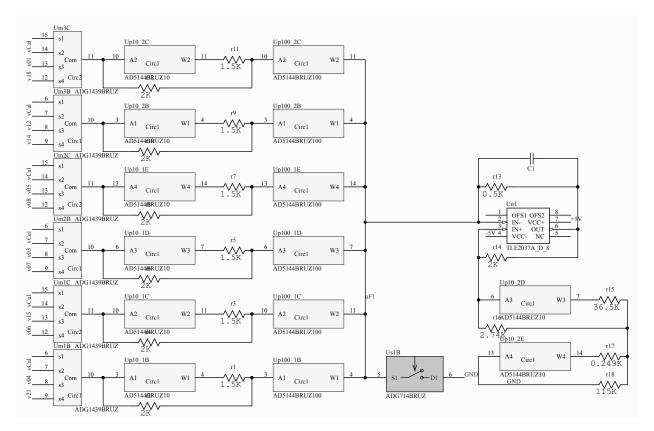

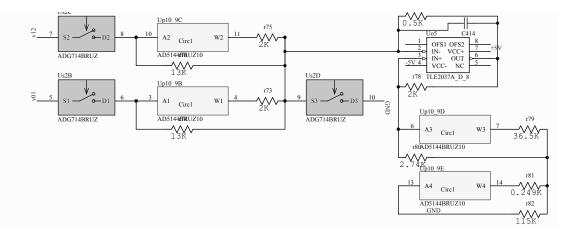

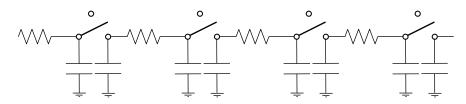

| 6.3                 | Schematics of a 6-variable equality constraint.                                                                                                                                                                                      | 52                                      |

| 6.4                 | Schematics of a 2-variable equality constraint.                                                                                                                                                                                      | 53                                      |

| 6.5                 | Conceptual schematics of an inequality constraint.                                                                                                                                                                                   | 54                                      |

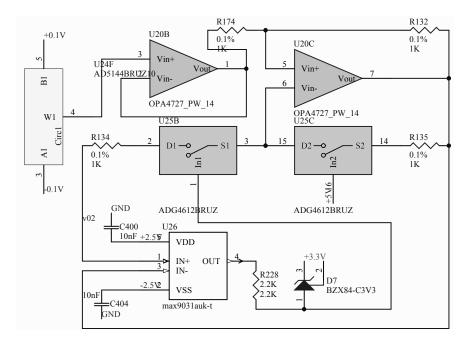

| 6.6                 | Schematics of an inequality constraint.                                                                                                                                                                                              | 54                                      |

| 6.7                 | Schematics of a cost circuit.                                                                                                                                                                                                        | 55                                      |

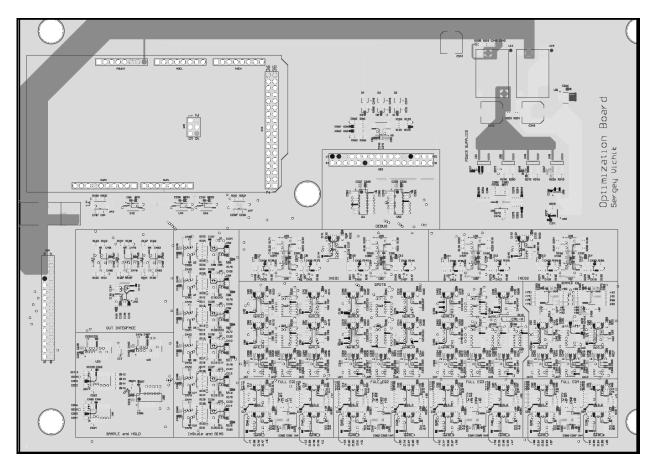

| 6.8                 | PCB layout                                                                                                                                                                                                                           | 55                                      |

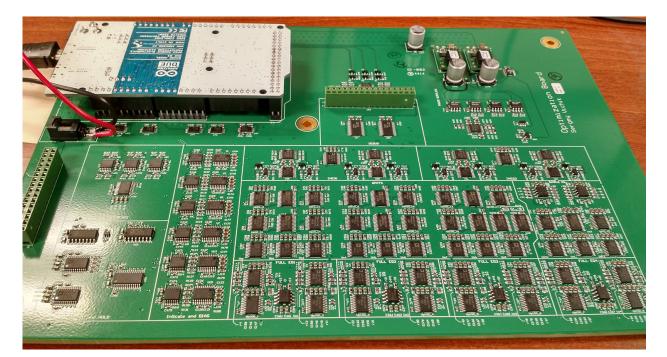

| 6.9                 | The QP board.                                                                                                                                                                                                                        | 56                                      |

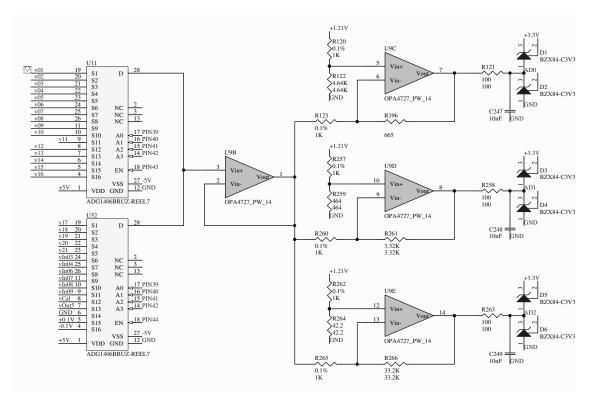

| 6.10                | Schematics of the measurement function.                                                                                                                                                                                              | 59                                      |

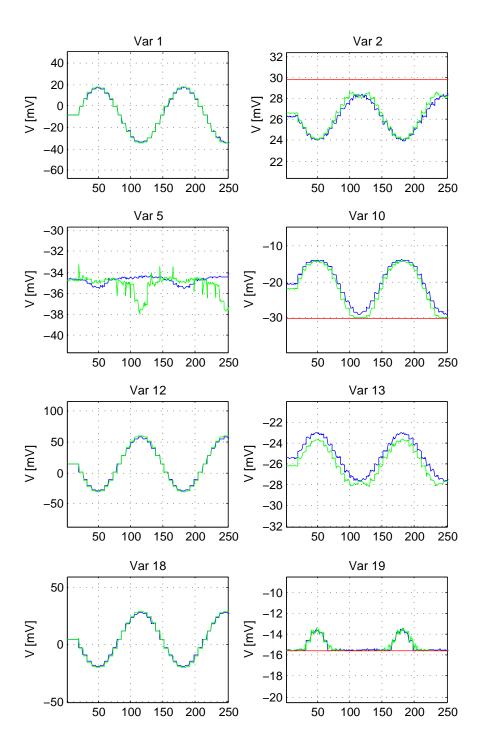

| 6.11                | · 0 0                                                                                                                                                                                                                                |                                         |

|                     | analog. Red line shows constraints.                                                                                                                                                                                                  | 61                                      |

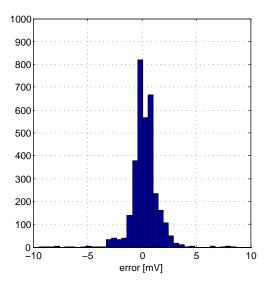

|                     | Histogram of the difference between analog and digital solutions                                                                                                                                                                     | 62                                      |

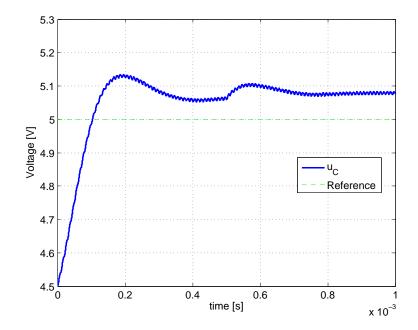

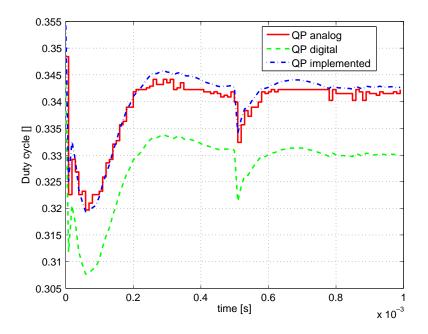

| 0.14                | mization board.                                                                                                                                                                                                                      | 64                                      |

| 6.14                | Duty cycle command as computed by the analog optimization board, by an exact                                                                                                                                                         | C 4                                     |

| C 15                | digital solver and by a digital solver using the implemented resistance values                                                                                                                                                       | 64                                      |

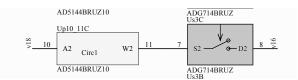

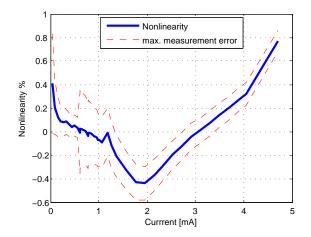

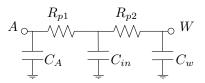

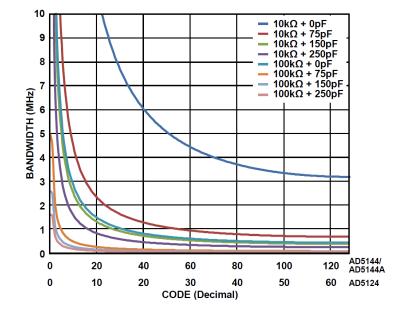

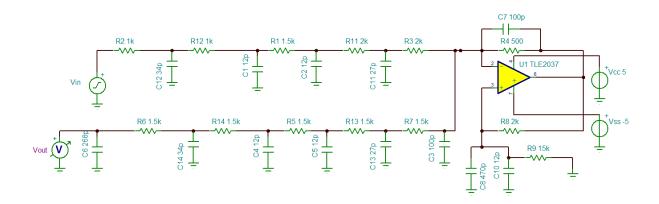

|                     | Schematics of a digital potentiometer.                                                                                                                                                                                               | 65<br>66                                |

|                     | Nonlinearity of AD5144 potentiometer                                                                                                                                                                                                 | 66<br>66                                |

|                     | (a) Circuit for the non-linearity experiment. (b) Negative resistance non-linearity.                                                                                                                                                 | 66<br>68                                |

|                     | PotModel                                                                                                                                                                                                                             | $\begin{array}{c} 68 \\ 68 \end{array}$ |

|                     | Simplified dynamical model of full equality constaint using TINA-TI.                                                                                                                                                                 | 69                                      |

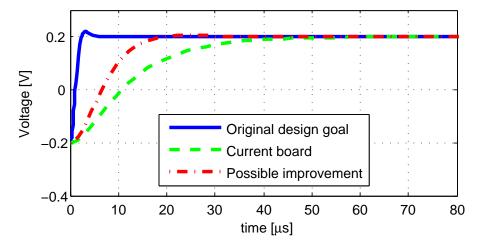

|                     | Simulation of step response of the model 6.20.                                                                                                                                                                                       | 09<br>70                                |

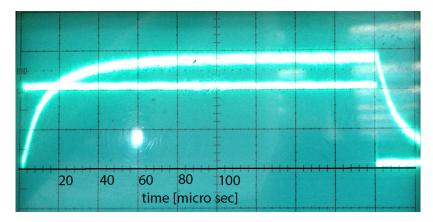

|                     | Step response of the board as captured with an oscilloscope                                                                                                                                                                          | 70<br>70                                |

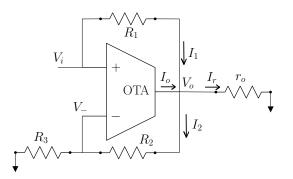

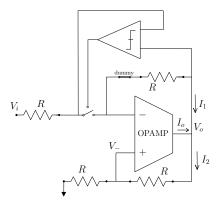

| 7.1                 | Negative resistance implementation with OTA.                                                                                                                                                                                         | 73                                      |

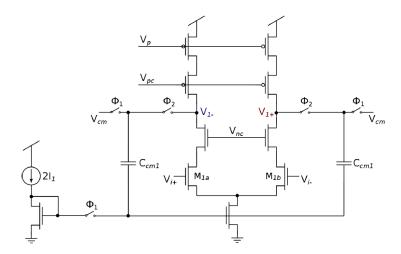

| 7.2                 | Two stage differential amplifier                                                                                                                                                                                                     | 75                                      |

| 7.3  | Dual stage amplifier.                                                                               | 76           |

|------|-----------------------------------------------------------------------------------------------------|--------------|

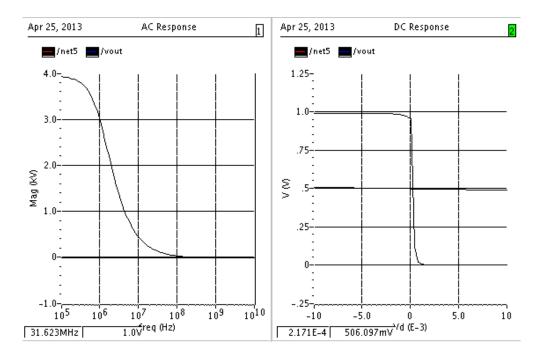

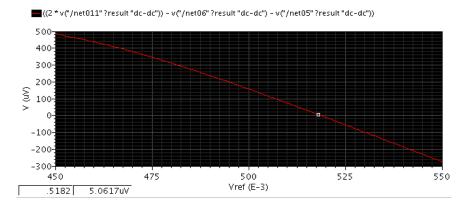

| 7.4  | AC and DC response of the amplifier                                                                 | 77           |

| 7.5  | The negative resistance AC and DC response                                                          | 77           |

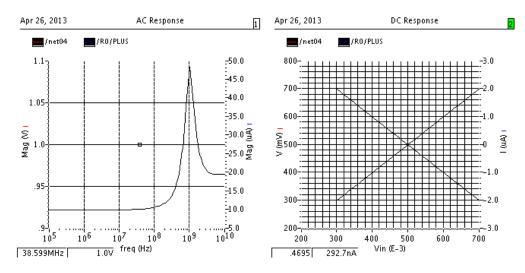

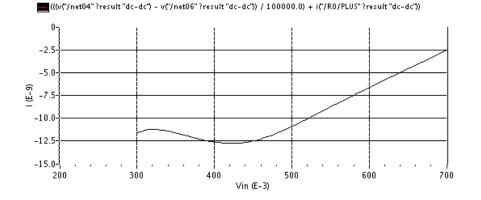

| 7.6  | Error of negative resistant current. The error is less then 15 nA                                   | 78           |

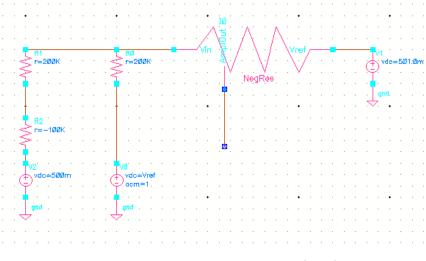

| 7.7  | The circuit for LP $(7.12)$                                                                         | 79           |

| 7.8  | Error of $x_2$ computation in LP (7.12).                                                            | 79           |

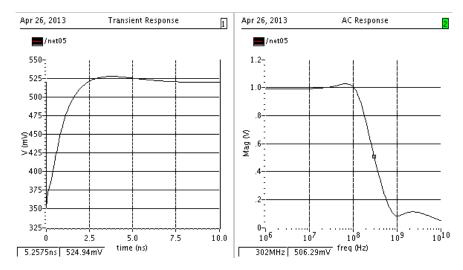

| 7.9  | Step response and AC response of the LP circuit.                                                    | 80           |

| 7.10 | Negative resistance circuit with the diode model in feedback                                        | 81           |

| 7.11 | Active Diode                                                                                        | 82           |

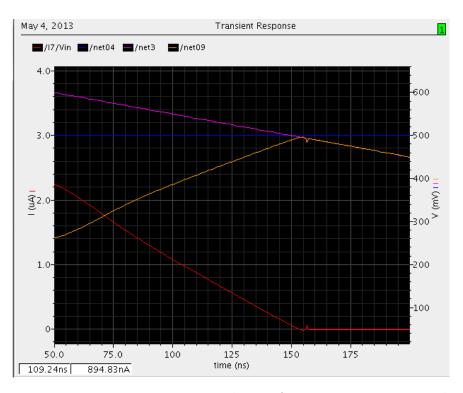

| 7.12 | Transient response to a ramp voltage of negative resistance with active diode .                     | 83           |

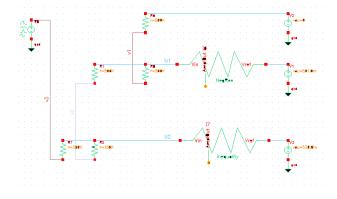

|      | Schematics of LP $(7.13)$                                                                           | 84           |

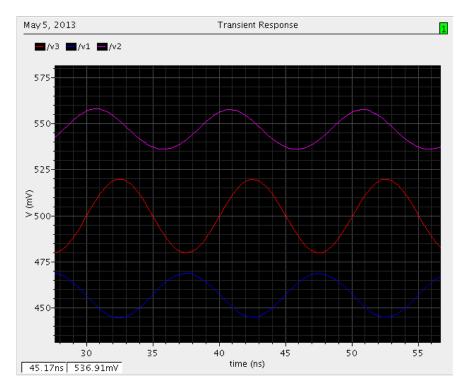

|      | Simulation results of $LP$ (7.13). 100 MHz input.                                                   | 84           |

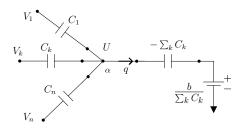

|      | Equality enforcing circuit consisting of $n$ capacitors $(C_1 \ldots C_n)$ , a negative capac-      | 01           |

|      | itance, and a reference voltage.                                                                    | 86           |

| 7 16 | A node with $n$ connected wires                                                                     | 87           |

|      | Inequality enforcing circuit.                                                                       | 88           |

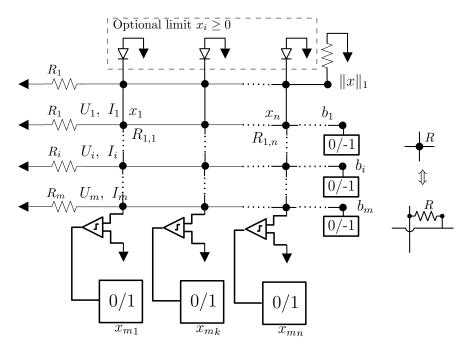

|      | Electric circuit solving an LP. Vertical wires are variable nodes with potentials                   | 00           |

| 1.10 | $V_1 \dots V_n$ . Black dots represent capacitances that connects vertical and horizontal           |              |

|      | wires. Horizontal wires are cost or constraint nodes. Each horizontal wire is                       |              |

|      | connected to a ground via a negative capacitance, a constant voltage source and                     |              |

|      | a diode for inequalities nodes. The topmost horizontal wire is the cost circuit                     |              |

|      |                                                                                                     | 89           |

| 7 10 | which is connected to a constant voltage source                                                     | - 89<br>- 90 |

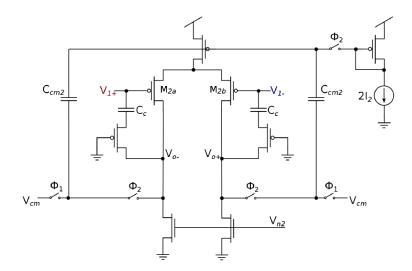

|      | Compact representation of a capacitor.                                                              | 90<br>92     |

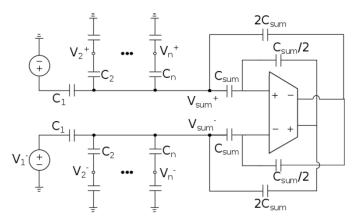

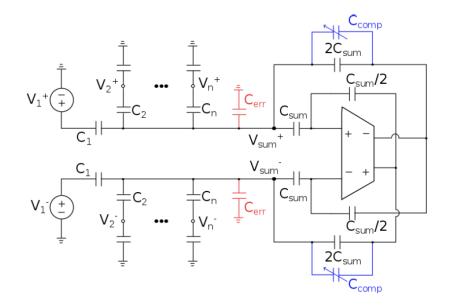

|      | Differential negative capacitor. $\dots$                                                            |              |

|      | Fully differential equality constraint with capacitor values, where $C_{\text{sum}} = \sum_i C_i$ . | 93           |

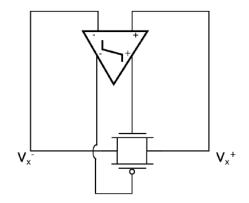

| 7.22 | Inequality enforcing $V_x \leq 0$ . The comparator includes an SR latch to hold the                 | 0.4          |

| - 00 | outputs constant during the comparator reset phase.                                                 | 94           |

| 7.23 | Diagram showing addition of compensation capacitor $C_{\text{comp}}$ to correct for error           | ۰ <b>۲</b>   |

|      | due to summing node parasitic capacitance $C_{\text{err}}$ .                                        | 95           |

| 7.24 | First stage of fully differential two stage telescopic cascode amplifier with common                | ~            |

|      | mode feedback.                                                                                      | 95           |

| 7.25 | Second stage of fully differential two stage telescopic cascode amplifier with com-                 |              |

|      | mon mode feedback.                                                                                  | 96           |

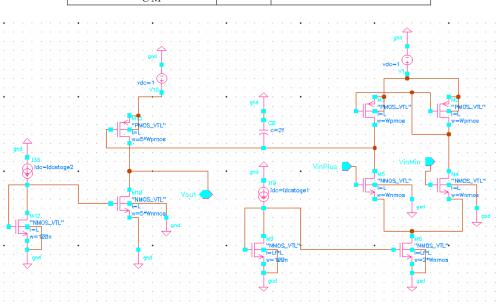

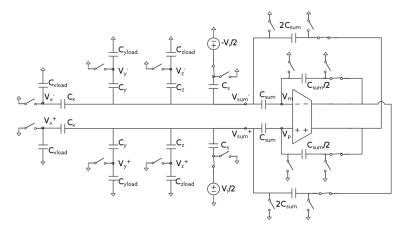

|      | Schematics for the QP $(7.36)$                                                                      | 97           |

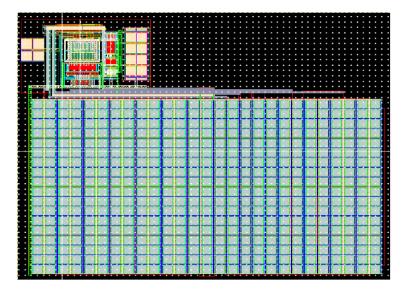

| 7.27 | Layout for the QP (7.36) implemented in TSMC 65nm. Total size is $240 \mu m \times$                 |              |

|      | $300\mu m$ . The bottom part are the capacitors and the upper left part is the OTA.                 | 97           |

| 7.28 | Extracted results showing settling time of $50ns$ for the QP (7.36) with a switching                |              |

|      | period of 200 <i>ns</i> . The differential values of the summing node and amplifier input           |              |

|      | and output are also shown                                                                           | 98           |

| 01   | Commention of divital and analysis in the size of solutions (AV D                                   | 100          |

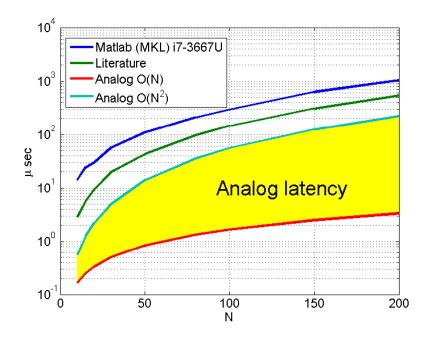

| 8.1  | Comparison of digital and analog latencies of solution to $AX = B$                                  | 100          |

| 8.2  | Circuit that decodes a linear code using norm-2 (quadratic program)                                 | 103          |

| 8.3 | Circuit that decodes a linear code using norm-1 (linear program).                         | 104 |

|-----|-------------------------------------------------------------------------------------------|-----|

| 8.4 | Legal correcting transitions for a single MLC flashes implemented by a <i>generalized</i> |     |

|     | comparator                                                                                | 105 |

| 8.5 | Performance of the proposed analog LDPC decoding compared to digital imple-               |     |

|     | mentation in Matlab toolbox and [80]                                                      | 106 |

| 8.6 | Image acquisition and processing pipeline with the proposed analog processing             |     |

|     | stage at the CCD level. The image is captured as voltage levels by a CCD sensor,          |     |

|     | those voltages are the input to an analog processor, and its output is sampled by         |     |

|     | the A/D block and transferred to a processor for further processing                       | 107 |

| 8.7 | Single cell of an optical flow array.                                                     | 109 |

| A.1 | Input and constant variables of the circuit.                                              | 123 |

|     |                                                                                           |     |

# List of Tables

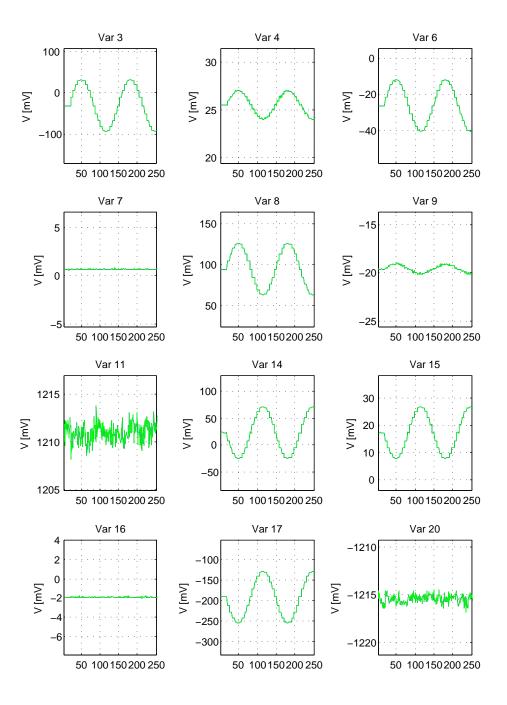

| 6.1 | Variables in the QP board                |

|-----|------------------------------------------|

| 6.2 | Capacitances of AD5144 potentiometer     |

| 6.3 | Input capacitances                       |

| 7.1 | Requirements from the amplifier          |

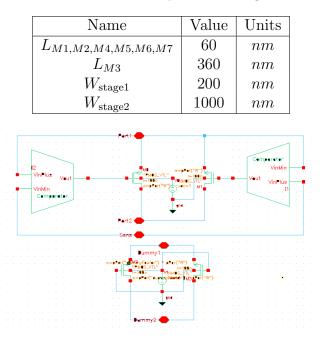

| 7.2 | Amplifier sizing    76                   |

| 7.3 | Comparator sizing                        |

| 7.4 | Absolute and Normalized Capacitor Values |

#### Acknowledgments

Foremost, I would like to express my sincere gratitude to my advisor Prof. Francesco Borrelli for the continuous support of my Ph.D research, for his genuine interest, enthusiasm, and immense knowledge. His meticulous approach and guidance were paramount in shaping a rough idea into a coherent research work. I could not have imagined having a better advisor and mentor for my Ph.D study.

I want to thank all the Professors who shared their knowledge and experience with me, especially, Prof. Ilan Adler and Prof. Arcak Murat for valuable discussions and great ideas!

I want to thank Dr. Tibor Kozak from Imagize LLC for his enthusiastic assistance in design of the PCB prototype, and to Saman Fahandezhsaadi and Roya Firoozi for writing software for the prototype.

I want to express my most sincere thanks to Kristel Deems for designing the analog VLSI prototype and to Prof. Elad Alon for advising and assisting the VLSI design.

A special acknowledgement goes to my lab mates in those years: Sarah Koehler, Ashwin Carvalho and Tony Kelman. We spent long time discussing various topics, exchanging ideas and negotiating difference in culinary preferences.

# Chapter 1

# Introduction

## 1.1 Motivation

The digital revolution has fundamentally changed technology, science and the everyday life. Our society got used to a steady and fast pace of improvement of the digital technology, embodied by the famous "Moore's law". However, there are multiple indications that this trend begins to level off. Novel and unconventional approaches will be needed to sustain the expected progress.

Standard benchmarks show the progress in computation speed. For instance, Fig. 1.1a presents the results of a floating point benchmark SPECfp from the last 20 years as published by Standard Performance Evaluation Corporation (SPEC) [86]. SPEC maintains historic and current performance results as reported by computer manufacturers. The benchmark result is the ratio between execution time of a baseline CPU to a tested CPU. Thus, benchmark result of 100 means that a tested CPU is 100 times faster then the baseline CPU. The benchmark had evolved through three versions (CPU1995, CPU2000 and CPU2006) with different baselines. In order to have smooth transition between the versions, we have scaled the results of CPU2000 and CPU2006 to match the baseline of CPU1995.

Fig. 1.1a shows a major slowdown in an improvement rate. The performance used to improve by annual 45% in 90's, but it is only 12% annually since 2012. The slowdown may be partially contributed to a stall in modern CPU clock frequency. Fig. 1.1b plots the CPU clock frequency of Intel processors from 1970 to 2015 [67, 85]. The figure clearly shows that the maximum clock speed (about 4 GHz) was reached in 2002 and remains constant ever since. Faster clock frequencies are unfeasible in practice because of an excessive heat that it produces. Therefore, the performance gain since 2002 as shown in Fig. 1.1a originates from other improvements in computer design, especially memory access optimization (cache, memory bandwidth) and deep instruction pipelines with branch prediction.

Nowadays, when the low-hanging fruits of digital computation appear to be picked, it is time to evaluate the alternatives, such as analog computation. Analog computers have radically better performance then digital computers for a certain class of computational

Figure 1.1: (a) CPU floating point benchmarks from SPEC CPU95, CPU2000 and CPU2006 [86]. (b)Clock speed of Intel processors [67, 85].

problems. We demonstrate that when the analog computation is applied wisely, utilizing the progress in microelectronics, we can radically reduce computation latency comparing to digital processors. Moreover, analog computation yields lower power consumption and a smaller physical size.

The analog computers had been a formidable competitor to the digital computers at the beginning of the computer era, but were outpaced due to the rapid development of the digital computers. However, today thanks to the gigantic investment and progress made in microelectronics, we can build analog computers with the same tools utilized for the production of digital electronics. Therefore, analog computers can successfully compete in speed, price, power requirements and robustness with the digital computers.

Straightforward computation tasks can be done quickly with digital hardware, but as the complexity builds up, certain tasks demand long computing time. Digital computers are based on a sequential computation paradigm, which assumes that every computation is a sequence of operations. The sequential computation paradigm leads to iterative algorithms, which are major contributors to high latency and power consumption. Analog computers do not necessarily follow the sequential computation paradigm. For example, the optimization circuit proposed in this thesis reaches an equilibrium using a simultaneous bidirectional interaction between all parts of the problem and the solution is obtained in a single "iteration", unlike digital computers that require multiple iterations.

Analog circuits for solving optimization problems have been extensively studied in the past [26, 91, 48]. Our renewed interest in analog optimization stems from Model Predictive Control (MPC) [33, 65]. In MPC at each sampling time, starting at the current state, an open-loop optimal control problem is solved over a finite horizon. The optimal command signal is applied to the process only during the following sampling interval. At the next time

step, a new optimal control problem based on new measurements of the state is solved over a shifted horizon. The optimal solution relies on a dynamic model of the process, respects input and output constraints, and minimizes a performance index. When the model is linear and the performance index is based on two-norm, one-norm or  $\infty$ -norm, the resulting optimization problem can be cast as a linear program (LP) or a quadratic program (QP), where the state enters the right hand side (rhs) of the constraints.

This thesis proposes an analog circuit which can solve MPC problems faster and using less power then any digital method. The proposed circuit can be applied to a wide range of problems. Everything that requires repeated low-latency solution of similar problems is a potential application for analog optimization technology. Examples of possible application are (1) a MIMO receiver for mobile network, where the analog circuit recovers source signal from multiple antenna measurements; (2) image processing (e.g. edge detection, optical flow) implemented on the focal plane of CMOS sensor, where the processing is performed in an analog domain prior to image sampling; (3) error correcting decoder that recovers a valid code word from a corrupted one.

## **1.2** Outline and Contribution

This thesis presents an analog circuit which can solve LP or QP problems with varying r.h.s. (right hand side). In particular, the steady state voltages are the LP/QP optimizers. This thesis presents the circuit design, studies the steady state and the dynamical properties of the circuit, and demonstrates the method with hardware prototypes and simulations.

The thesis is structured as follows.

Previous work in analog optimization is reviewed in Chapter 2. One of the earliest attempts to use analog circuits for solving optimization problems was made by J. Dennis in his Ph.D. work published in 1959 [26]. More recent works by L. Chua [48] and J. Hopfield [91] proposed to build an analog solver that solves the optimization problem. The chapter discusses similarities and differences between the new circuit and the circuits proposed in previous works.

In Chapter 3 we present the design of the optimization circuit. The circuit proposed in this work is built out of resistors and diodes. A novel way of combining positive and negative resistances yields a linear equality constraint on voltage of the connected nodes. By introducing a diode, an inequality constraint is created. Resistors and a voltage source make linear and quadratic cost functions. Chapter 3 details the basic elements and their interconnection that creates an analog optimization circuit.

In Chapter 4 we show that the steady state of the optimization circuit is equivalent to a solution of the associated optimization problem. We use Karush-Kuhn-Tucker (KKT) conditions and properties of the dual optimization problem to prove the equivalence. This analysis reveals the role of voltages as the primal variables, currents as the dual variables, and the diodes as the enforcers of the complimentary slackness. Chapter 5 studies the dynamical properties of the circuit when ideal components are replaced by devices with real properties, such as parasitic capacitances and finite gain and feedback of operational amplifiers. In particular, we study the circuit stability and find bounds on circuit critical parameters that guarantee stability of the circuit.

The theory developed in the Chapters 3 through 5 is put to the test with a hardware prototype described in Chapter 6. The prototype is a programmable printed circuit board (PCB) that can be calibrated to solve a QP as required. The PCB is based on digital potentiometers (programmable resistors). Thus, the QP problem to solve is set by a software which calibrates the potentiometers to the required values. After the board is calibrated, it receives analog input and after a transient time of few microseconds it returns an analog output that is a solution to the required QP. The PCB yields good solution accuracy and demonstrates the feasibility of the method. Simultaneously, this works highlights the challenges of building high speed analog optimization devices such as parasitic capacitance and non-linear effects.

We demonstrate the feasibility of nano-second soluion latency by carrying out a high speed design of an analog Very Large Scale Integration (VLSI) chip in Chapter 7. The first section of Chapter 7 shows how an LP/QP optimization circuit can be made out of capacitors instead of resistors. When the optimizing circuit is built using a modern 65nm CMOS technology the transient latency is as low as few nano-seconds. For the VLSI design a new formulation of the circuit using capacitors instead of resistors is developed. A variant of the proofs of Chapter 4 is used to show equivalence between the new circuit with capacitance technology and the LP/QP problem. We create a detailed layout of a solver for a QP problem using switched-capacitors technology. This design occupies just  $0.08mm^2$  and yields a solution in 50ns.

Even though the original motivation for this work stems from MPC applications, the proposed method has a much bigger potential. Chapter 8 is a speculates on additional applications. The analog optimization circuit can be used as a co-processor for fast solution of linear systems, it can decode error correcting codes faster than any digital circuit, it can be used in highly parallel image processing device.

## 1.3 Outlook

In this thesis we highlight the benefits of using analog optimization circuits over the digital computers. Those include radically lower latency, lower power consumption and smaller physical size. The experiments demonstrate that the developed theory correctly predicts performance of the analog optimization circuit and it is possible to design to a very short latency, in the order of nanoseconds.

However, the experimental part of the work has also illuminates the challenges that should be overcome before the analog circuits can be successfully used in real life applications. Perhaps expectedly, those challenges include the common issues with analog designs including non-linearity of components, manufacturing tolerances, and oscillatory or unstable behavior. The required accuracy is achievable using current technology, as shown using the PCB and VLSI designs. Yet, the design process requires an effort that is substantially larger than the one required for modern digital design. This larger effort is translated to longer design cycles and a higher design cost, that is an important limiting factor in today's very competitive technology market.

We believe that a combination of two factors will remove the obstacles for wider adoption of a modern analog computation. The first factor is an increasing demand for advanced low latency computation that digital computers would not be able to meet. The second factor is an advanced design methodology and tools that should lower the barrier for introducing analog computing elements to products. While the former factor is inevitable, since it stems from the inherent limitation of digital computers, the later factor totally depends on the will of the scientific and the engineering communities to invest in an analog computing research.

## **1.4** Publications

Large parts of this thesis build on results that were previously published in collaboration with colleagues and faculty advisors. These publications are listed below.

Chapters 3 and 4 are partially based on the following two publications

- Sergey Vichik and Francesco Borrelli, "Solving linear and quadratic programs with an analog circuit", Computers & Chemical Engineering, 2014.

- Sergey Vichik and Francesco Borrelli, *"Fast solution of linear and Quadratic Programs with an analog circuit"* in American Control Conference (ACC), 2014, pp. 2954-2959.

Chapter 5 is based on an

• Sergey Vichik, Murat Arcak, Francesco Borrelli, "Stability of an Analog Optimization Circuit for Quadratic Programming", Systems & Control Letters, 2015 (accepted).

The section 7.3 in Chapter 7 is based on Master thesis by Kristel Deems where I have guided and collaborated

• Kristel Deems, "High Speed Analog Circuit for Solving Optimization Problems". M.Sc. thesis. University of California in Berkeley, 2015.

# Chapter 2

# Literature Review

This thesis can be viewed as an old and recently rediscovered effort to move beyond the digital computation [82, 84, 50, 27]. In this chapter we present the historical perspective of analog computation/optimization and the recent advances in this area.

# 2.1 "Classical" Analog Computers

Analog computers are an ancient idea and they preceded digital computers by millennia. Any physical system that converts continuous input information to continuous output information is an analog computer.

One of the earliest known analog computers is the *astrolabe* shown in Fig. 2.1a, which is an astronomical device used to compute the position of celestial objects on the sphere as function of time. The first astrolabes are mentioned in the Ptolemey's books *Almagest* and *Geography* from 150 AD, but is thought by some to date back to Hipparchus around 130 BC [55]. Another prominent example is a similar device shown in Fig. 2.1b — the *Antikythera Mechanism* dated to 150-100 BC that can predict, for many years ahead, not only eclipses but also a remarkable array of their characteristics, such as directions of obscuration, magnitude, colour, angular diameter of the Moon, relationship with the Moon's node and eclipse time [30, 31].

Fast forward to two millennia later and we find an array of conceptually similar mechanical analog computers up to the middle of the twentieth century. Those include a tide-predicting machine from 1872 and the Norden bombsight used in World War II.

Starting from the 1950s, electronic analog computers began to dominate due to a faster speed, smaller size and simpler reconfiguration. A traditional electronic analog computer is built out of resistors, capacitors, inductions and operational amplifiers. Most standard mathematical functions, including polynomials, exponents, logarithm and divisions can be implemented using the basic electronic elements [44]. Capacitors are used to store the state of a system, therefore, an analog computer can integrate linear and non-linear ordinary

Figure 2.1: (a) A planispheric astrolabe from the workshop of Jean Fusoris in Paris circa 1400, on display at the Putnam Gallery in the Harvard Science Center. Sage Ross, Wikimedia Commons. (b) Exploded computer reconstruction of the Antikythera Mechanism, from [31].

differential equations. Even partial differential equations can be solved using analog computers [47].

Electronic analog computers have been used with great success for scientific, industrial and military needs. Non-linear dynamical systems, such as bridge under aerodynamic load, nuclear reactions, problems in astronomy and trajectory tracking and flight control can be studied with analog computers [51]. In fact, the veteran PID controller is a special case of an analog computer since it used to be implemented using analog electronics.

The aforementioned analog computers perform computation by sequential evaluation of mathematical functions, like a chain of linked dials (in Astrolabe, Antikythera, bombsight) or a serial connection of electronic basic blocks. For this reason, this type of analog computers are no match for the digital computers that can perform the same operations faster and with greater precision. However, analog computers can perform operations based on simultaneous interaction between all parts of the problem. One example is mathematical optimization, where the goal is to minimize a function subject to constraints. When sequential computers, digital or analog, solve an optimization problem, they need to use an iterative process to converge to the solution. However, a certain class of analog computers can achieve this goal with no iterations required. In the next section we review iterative and non-iterative analog optimization circuits from the literature.

## 2.2 Previous Work on Analog Optimization

#### 2.2.1 Mathematically exact analog circuit

Analog circuits for solving optimization problems have been extensively studied in the past [26, 91, 48].

The monograph by J. Dennis [26] presents an analog electrical network for solving an QP

г. ¬

$$\min_{i_V, i_D, i_R} \frac{1}{2} i_R^T Q i_R + c^T i_V \tag{2.1a}$$

s.t.

$$\begin{bmatrix} N_V & N_D & N_R \end{bmatrix} \begin{bmatrix} i_V \\ i_D \\ i_R \end{bmatrix} = N_C i_C$$

(2.1b)

$$i_D \ge 0 \tag{2.1c}$$

where  $i_V, i_D, i_R$  are the optimization variables,  $N_V$ ,  $N_D$ ,  $N_R$ ,  $N_C$  are directed graph incidence matrices,  $Q \succ 0$  is a diagonal matrix, and c and  $i_C$  are column vectors. The equality and inequality operators are element-wise operators. In Dennis's work, the primal and dual optimization variables are represented by the circuit currents and voltages, respectively. A basic version of Dennis's circuit consists of resistors, current sources, voltage sources, and diodes. In this circuit each element value of matrices  $N_V$ ,  $N_D$ ,  $N_R$ ,  $N_C$  is equal to 1, 0 or -1, since those are directed graph incidence matrices. Therefore, this circuit is limited to problems where the coefficients are in  $\{1, 0, -1\}$ . An extended version of the circuit includes a multiport DC-DC transformer and can represent arbitrary matrix. Current distribution laws in electrical networks (also known as minimum dissipation of energy principle or Kirchhoff's laws) are used to prove that the circuit equilibrium is governed by the same equations as the Lagrangian Problem that yields the optimizer of the problem [26].

The circuit of Dennis does not implement an iterative algorithm that solves an optimization problem, rather he design the circuit so that the circuit currents and voltages at steady state are the optimizer of the original problem. This is also the approach we took in this thesis. Moreover, nor Denis's circuit neither the circuit proposed in this thesis include, by design, dynamical elements that yield a transient response. Ideally, the circuits reach instantly the equilibrium state. A similar more recent work explores the behavior of resistor-transformer-diode networks as a projection operator [69].

Denis's intention was to use the circuit analogy to develop optimization algorithms. Indeed, while widely cited, this work had limited practical impact due to difficulties in implementing the actual circuit, and especially in implementing the multiport DC-DC transformer.

In later work, Chua [16] showed a different and more practical way to realize the multiport DC-DC transformer using operational amplifiers. In subsequent works, Chua [48, 15] and

Figure 2.2: Canonical nonlinear programming circuit-dynamic model, from [48]. The circuits on the left generate currents  $i_j$  that represent dual variables, circuits on the right implement Lagrangian for KKT optimality conditions.

Hopfield [91] proposed circuits to solve non-linear optimization problems of the form

$$\min_{x} \Phi(x)$$

s.t.  $f_j(x) \le 0, \ j = 1 \dots m,$  (2.2)

where  $x \in \mathbb{R}^n$  is the vector of optimization variables,  $\Phi(x)$  is the cost function, and  $f_j(x)$  are the *m* constraint functions.

The circuits proposed by Chua, Hopfield, and coauthors model the Karush-Kuhn-Tucker (KKT) conditions by representing primal variables as capacitor voltages and dual variables as currents. The dual variables are driven by the inequality constraint violations using high gain amplifiers. The circuit proposed in [48] is shown in Fig. 2.2. The circuit comprises of controlled current sources, each implementing partial derivative  $\frac{\partial \Phi(x)}{\partial x_i}$  or  $\frac{\partial f_i(x)}{\partial x_i}$ , voltage sources implementing  $f_j(x)$  and variable nonlinear resistors  $g_j(\cdot)$  used to impose the constraints in the circuit realization. The circuit capacitors are charged with a current proportional to the gradient of the Lagrangian of problem (2.2)

$$\frac{\partial x_i}{\partial t} = -\left[\frac{\partial \Phi(x)}{\partial x_i} + \sum_{j=1}^m I_j \frac{\partial f_j(x)}{\partial x_i}\right],\tag{2.3}$$

where  $\frac{\partial x_i}{\partial t}$  is the capacitor voltage derivative and  $I_j$  is the current corresponding to the *j*th dual variable. The derivatives  $\frac{\partial f}{\partial x_i}$  and  $\frac{\partial g_j}{\partial x_i}$  are implemented by using combinations of analog electrical devices [44]. When the circuit reaches an equilibrium, the capacitor charge is constant ( $\frac{\partial x_i}{\partial t} = 0$ ) and Eq. (2.3) becomes one of the KKT conditions.

The circuit in Fig. 2.2 computes violations of the KKT conditions (currents in the right hand circuits) and a feedback loop alters the state variables until an equilibrium is reached.

Therefore, it exhibits the features of an iterative type of analog computers that implement a known mathematical functions and require iterations to converge. The authors prove that their circuit always reaches an equilibrium point that satisfies the KKT conditions. This is an elegant approach since the circuit can be intuitively mapped to the KKT equations. However, the time required for the capacitors to reach an equilibrium is non-negligible. This might be the reason for the relatively large settling time reported to be "tens of milliseconds" for those circuits in [48] for QP and LP problems implemented as a special case of problem (2.2).

#### 2.2.2 Artificial neural network for optimization

Artificial neural network (ANN) are a powerful tool and are applied to various tasks. ANN can be implemented as analog computers [96, 66, 90, 52], or more commonly the networks are digitally simulated.

ANN can be designed and trained to solve linear and nonlinear optimization problems [19, 89]. J. Hopfield proposed a new class of ANN (called later Hopfield Neural Network) that is used to solve the traveling salesman problem [42], LP [91] and more.

The digital simulation of ANN is very computationally intensive and cannot compete with dedicated optimization algorithms and the analog implementations although demonstrate a steady progress over the last two decades but not yet competitive with digital implementations either due to scale or speed [68, 97, 74].

We believe that the analog optimization method proposed in this thesis is simpler, faster and easier to build than the one based on ANN.

## 2.3 Applications of analog optimization

#### 2.3.1 Image processing

Image processing traditionally requires substantial computing power. Many of the image processing algorithms can be formulated as an optimization problem and solved using an analog circuit. There are many published results in this field [12].

Stocker has successfully used an analog optimization circuit in an analog optical flow sensor [88]. Stocker solves a QP that represents an optical flow problem using analog electronic circuit integrated in a CMOS image sensor. The approach is based on a circuit constructed of transistor and resistors originally proposed by Poggio and Koch [76, 75]. In addition, Poggio and Koch propose to perform edge detection operation using a similar circuit. Harris built an analog VLSI chip to perform Gaussian smoothing, or interpolation and optical flow estimation [37, 38]. A more recent work [18] presents an analog image processing in the focal-plane that is able to compute image convolution with predefined kernels to implement algorithms such as edge detection, smoothing and motion detection.

In 2012 DARPA driven by the realization that "The digital processors used for ISR data analysis are limited by power requirements, potentially limiting the speed and type of data analysis that can be done. A new, ultra-low power processing method may enable faster, mission critical analysis of ISR data" announced the Unconventional Processing of Signals for Intelligent Data Exploitation (UPSIDE) program to "break the status quo of digital processing with methods of video and imagery analysis based on the physics of nanoscale devices" [95].

#### 2.3.2 Applying analog circuits to MPC problems

The analog computing era declined before the widespread use of Model Predictive Control. Quero, Camacho and Franquelo [77] have been the first to study the implementation of analog MPC. They use the Hopfield circuit proposed in [91] to implement an MPC controller. The approach they propose is validated with an experimental circuit which reaches the equilibrium after a transient of 1.8 msec.

More recently in [71], fast analog PI controllers are implemented on an Anadigm's Field Programmable Analog Array (FPAA) device [5] for an application involving a fast chemical microreactor. An FPAA is an integrated device containing configurable analog blocks and configurable block interconnections. The analog circuit designed in [71] has a computation time that is faster than that of a digital controller implementing the PI controller. The article briefly proposes to use an FPAA for MPC without specifying details. To the best of the authors knowledge, no further work has been published in this direction.

#### 2.3.3 Analog optimization co-processors

Multiple works have studied an offloading of computing tasks to an analog co-processor. There seems to be a growing consensus in the research community that an analog computation is capable to provide the much needed speed and power efficiency gains. In this thesis we propose to use the analog LP/QP circuit for this purpose, whereas an overwhelming majority of publications studies analog neural networks as an analog co-processor.

S. Koziol studied path planning [53], that is a special case of optimization, with resistive grid or neural network using a family of Field Programmable Analog Arrays (FPAAs) [7, 81, 11]. Those analog devices require tens of microseconds to find a solution, that was shown to be faster than a software solution and comparable to a digital hardware, FPGA, solution. The same family of FPAA devices was used to solve an optimal Bayesian inference and least squares problems using a programmable analog network of 18 neurons with speed 1000 times faster then the digital [83].

A general purpose analog VLSI accelerator and a complete tool chain was developed using hardware neural processing units (NPUs) in a large effort by multiple institutions [87]. In [22], G. Cowan studied solution of ODE,PDE and SDE (stochastic differential equations) using an analog VLSI co-processor and reported computation speed and power consumption substantially better than the digital computers.

The emerging memristor technology [17] may support the analog computation trend, since it provides the way to make compact and configurable resistors. In [79] a configurable memristor network is proposed to accelerate the solution of linear equations to achieve  $1500 \times$

reduction in time and  $8.5 \times$  reduction in energy consumption. An analog neural network configurable using memristors is proposed in [56].

# Chapter 3

# The novel QP/LP optimization circuit

## 3.1 Problem statement

This thesis deals with a solution of a quadratic programming (QP) problem

$$\min_{V=[V_1,\dots,V_n]^T} V^T Q V + c V \tag{3.1a}$$

s.t.

$$A_{\rm eq}V = b_{\rm eq}$$

(3.1b)

$$A_{\text{ineq}}V \le b_{\text{ineq}},$$

(3.1c)

where  $V_1, \ldots, V_n$  are the optimization variables,  $b_{eq}$  and  $b_{ineq}$  are column vectors, c is a row vector  $Q \succ 0$ , and  $A_{ineq}$  and  $A_{eq}$  are matrices. We assume that the matrix Q is positive definite, but will explain also the case where positive semi-definite Q is allowed. A linear programming (LP) problem and solution of a linear system are treated as a special case of the QP problem.

In this chapter we present the basic building blocks which will be later combined to create a circuit that solves problem (3.1). The first basic block enforces equality constraints of the form (3.1b). The second building block enforces inequality constraints of the form (3.1c). Two more basic blocks implement the linear and quadratic cost functions.

## 3.2 Analog QP Circuit

**Proposition 1.** Any QP (3.1) can be written in a QP form where all the coefficients of the constraint matrices  $A_{eq}$ ,  $A_{ineq}$  are non-negative.

Proof. We prove it by constructing a QP with non-negative matrices. Consider the QP

$$\min_{\tilde{V}=[\tilde{V}_1,\dots,\tilde{V}_n]^T} \tilde{V}^T \tilde{Q} \tilde{V}$$

(3.2a)

s.t.

$$\tilde{A}_{eq}\tilde{V} = \tilde{b}_{eq}$$

(3.2b)

$$\hat{A}_{\text{ineq}}\hat{V} \le b_{\text{ineq}}$$

(3.2c)

where  $\tilde{A}_{eq}$  and  $\tilde{A}_{ineq}$  are not necessarily non-negative. We introduce an auxiliary vector

$$V \triangleq \begin{bmatrix} V^+ \\ V^- \end{bmatrix} \tag{3.3}$$

and rewrite the QP (3.2) as

$$\min_{V} \quad V^{T}QV \tag{3.4a}$$

s.t.

$$A_{eq}^+ V^+ + A_{eq}^- V^- = \tilde{b}_{eq}, \ A_{ineq}^+ V^+ + A_{ineq}^- V^- \le \tilde{b}_{ineq}$$

(3.4b)

$$V^{+} + V^{-} = 0, (3.4c)$$

where  $A_{\text{ineq}}$  and  $A_{\text{eq}}$  are split into positive and negative parts  $(A_{\text{ineq}} = A_{\text{ineq}}^+ - A_{\text{ineq}}^-)$  and  $A_{\text{eq}} = A_{\text{eq}}^+ - A_{\text{eq}}^-)$ . The cost matrix Q in (3.4) satisfies  $M^T Q M = \tilde{Q}$ , where the matrix M is the transformation from  $\tilde{V}$  to V

$$V = M\tilde{V} \tag{3.5}$$

$$M = \begin{bmatrix} \mathbb{I} \\ -\mathbb{I} \end{bmatrix}, \tag{3.6}$$

and  $\mathbb I$  is the identity matrix.

The QP (3.4) can be written in the same form as the original problem (3.1).

$$\min_{V=[V_1,\dots,V_n]^T} V^T Q V \tag{3.7a}$$

s.t.

$$A_{\rm eq}V = b_{\rm eq}$$

(3.7b)

$$A_{\rm ineq}V \le b_{\rm ineq} \tag{3.7c}$$

where

$$A_{\rm eq} = \begin{bmatrix} A_{\rm eq}^+ & A_{\rm eq}^- \\ \mathbb{I} & \mathbb{I} \end{bmatrix}$$

(3.8)

$$A_{\text{ineq}} = \begin{bmatrix} A_{\text{ineq}}^+ & A_{\text{ineq}}^- \end{bmatrix}$$

(3.9)

$$b_{\rm eq} = \begin{bmatrix} b_{\rm eq} \\ 0 \end{bmatrix} \tag{3.10}$$

$$b_{\text{ineq}} = \hat{b}_{\text{ineq}},\tag{3.11}$$

with  $A_{eq}$  and  $A_{ineq}$  non-negative by construction.

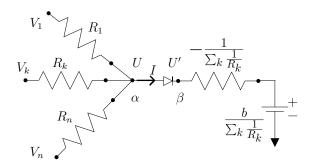

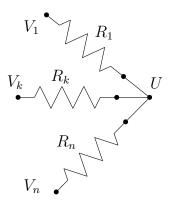

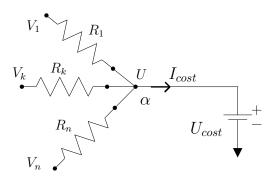

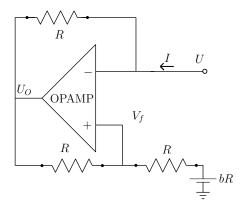

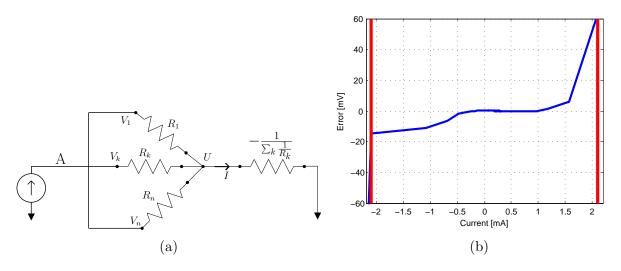

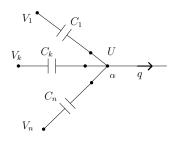

#### 3.2.1 Equality constraint

Consider the circuit depicted in Fig. 3.1.  $V_k$  is the potential of node k,  $R_k$  is the resistance between node k and the common node  $\alpha$  with potential U,  $-\frac{1}{\sum_k \frac{1}{R_k}}$  is a negative resistance,

and  $\frac{b}{\sum_k \frac{1}{R_k}}$  is a constant voltage source.

**Proposition 2** (Equality constraint circuit). The circuit in Fig. 3.1 enforces the equality constraint

$$\begin{bmatrix} \frac{1}{R_1} & \dots & \frac{1}{R_n} \end{bmatrix} \begin{bmatrix} V_1 \\ \vdots \\ V_n \end{bmatrix} = b.$$

(3.12)

*Proof.* Consider the circuit depicted in Fig. 3.2. In this circuit, n wires are connected to a common node. We call this common node  $\alpha$ , its potential U, and the current that exits this node I. Kirchhoff's current law (KCL) implies

$$\sum_{k=1}^{n} I_k = \sum_{k=1}^{n} \frac{V_k - U}{R_k} = I,$$

(3.13)

Figure 3.1: Equality enforcing circuit consisting of n resistors  $(R_1 \ldots R_n)$ , a negative resistance, and a reference voltage.

Figure 3.2: A node with n connected wires.

Figure 3.3: Inequality enforcing circuit.

where  $I_k$  is the current through branch k, and  $R_k$  is the resistance between node k and node  $\alpha$ . Eq. (3.13) can be written as an equality constraint on potentials  $V_k$ ,

$$\sum_{k=1}^{n} \frac{V_k}{R_k} = I + U \sum_{k=1}^{n} \frac{1}{R_k}.$$

(3.14)

If the right hand side (rhs) of (3.14) is set to any desired value b, then (3.14) enforces an equality constraint on a linear combination of  $V_k$ . The voltage U is set to

$$U = -\frac{I}{\sum_{k=1}^{n} \frac{1}{R_k}} + \frac{b}{\sum_{k=1}^{n} \frac{1}{R_k}}.$$

(3.15)

The rhs in (3.15) is implemented by a negative resistance of  $-\frac{1}{\sum_{k=1}^{n} \frac{1}{R_k}}$  and a constant voltage source of  $\frac{b}{\sum_{k=1}^{n} \frac{1}{R_k}}$ . Eq. (3.15) together with (3.14) yield the desired (3.12). Therefore, the circuit shown in Fig. 3.1 enforces (3.12).

Note that the negative resistance  $-\frac{1}{\sum_k \frac{1}{R_k}}$  in the circuit in Fig. 3.1 can be realized by using an operational amplifier [13, pp. 395-397].

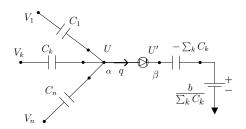

#### 3.2.2 Inequality constraint

Consider the circuit shown in Fig. 3.3. Similarly to the equality constraint circuit, n wires are connected to a common node  $\alpha$ .  $\alpha$ 's potential is U and the current exiting this node is I. An ideal diode connects node  $\alpha$  to node  $\beta$ . The potential of node  $\beta$  is U'.

**Proposition 3** (Inequality constraint circuit). The circuit in Fig. 3.3 enforces the inequality constraint

$$\begin{bmatrix} \frac{1}{R_1} & \dots & \frac{1}{R_n} \end{bmatrix} \begin{bmatrix} V_1 \\ \vdots \\ V_n \end{bmatrix} \le b.$$

(3.16)

Figure 3.4: Quadratic cost circuit.

*Proof.* Kirchhoff's current law (KCL) implies (3.13) as in the previous case. The diode enforces  $U' \ge U$ . In Fig. 3.3, the voltage U' can be computed as follows

$$U' = \frac{b - I}{\sum_{k=1}^{n} \frac{1}{R_k}} \ge U.$$

(3.17)

Eq. (3.13) and  $U \leq U'$  yield

$$\sum_{k=1}^{n} \frac{V_k}{R_k} = I + U \sum_{k=1}^{n} \frac{1}{R_k} \le I + U' \sum_{k=1}^{n} \frac{1}{R_k} = b,$$

(3.18)

which can be compactly rewritten as (3.16). Therefore, the circuit shown in Fig. 3.3 enforces (3.16).

The diode in Fig. 3.3 enforces

$$I \ge 0, \tag{3.19a}$$

$$I(U - U') = 0. (3.19b)$$

By using (3.17) and rearranging its terms, (3.19b) can be rewritten as:

$$I\left(\left(\sum_{k=1}^{n}\frac{1}{R_k}\right)U - b + I\right) = 0.$$

(3.20)

Eq. (3.20) will be used later in Section 4.1 to characterize the QP circuit.

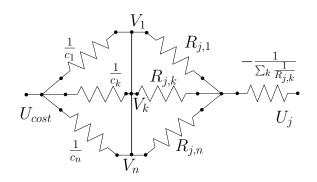

#### 3.2.3 Quadratic cost function

Let  $A = \begin{bmatrix} A_{eq} \\ A_{ineq} \end{bmatrix}$  be the matrix of constraint coefficients. By composing the elementary circuits of the previous sections we can design an analog circuit which implements the constraints  $A_{eq} V = b_{eq}$  and  $A_{ineq} V \leq b_{ineq}$ . In section 4.2 it will be shown that such circuit

would minimize a cost function  $V^T Q_A V$  where

$$Q_A = \operatorname{diag}(\mathbf{1}^T A) - A^T \operatorname{diag}(\mathbf{1}^T A^T)^{-1} A.$$

(3.21)

In general, this cost function is different from the desired cost Q. However, it is possible to add redundant constraints of the form  $A_{\text{augm}}V < \infty$ , which are always inactive and have no effect on a feasible set of the problem (3.1). By doing so the cost matrix can be shaped in a way that  $Q_{A'} = kQ$ , where  $A' = \begin{bmatrix} A \\ A_{\text{augm}} \end{bmatrix}$ , k > 0 is a scalar, and  $Q_{A'} =$  $\operatorname{diag}(\mathbf{1}^T A') - A'^T \operatorname{diag}(\mathbf{1}^T A'^T)^{-1} A'$  (see section 4.2 for additional details). The redundant constraints are implemented using a simple circuit depicted in Fig. 3.4, i.e, a special case of the inequality circuit, without the diode and the negative resistor.

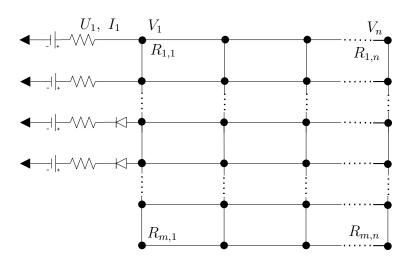

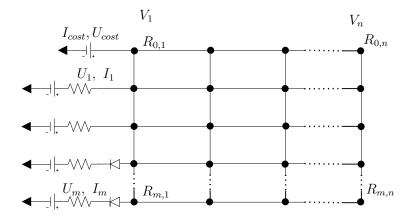

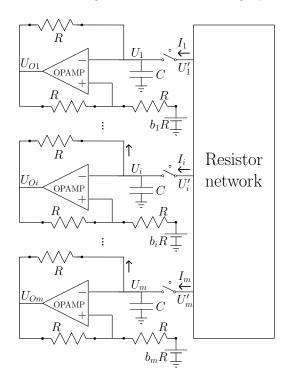

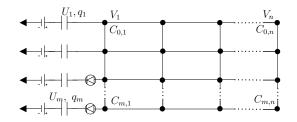

#### 3.2.4 Connecting the basic circuits to form a QP circuit

This section presents how to construct the circuit that solves a general QP. We construct the conductance matrix  $A \in \mathbb{R}^{m \times n}$  as

$$A \triangleq \begin{bmatrix} A_{\rm eq} \\ A_{\rm ineq} \end{bmatrix}$$

(3.22)

and denote  $A_{ij}$  the *i*, *j* element of *A*. For a given QP (3.1) the  $R_{ij}$  resistor is defined as

$$R_{ij} = \frac{1}{A_{ij}}, \ i = 1, \dots m, \ j = 1, \dots, n.$$

(3.23)

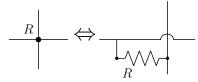

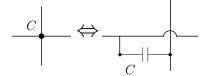

Consider the circuit shown in Fig. 3.5. The circuit is shown using a compact notation where each resistor  $R_{ij}$  is represented by a dot, vertical wires represent variable nodes with potentials  $V_1 \ldots V_n$  and horizontal wires represent *constraint nodes*. The compact representation of a resistor through the dot symbol is clarified in Fig. 3.6. If  $A_{ij} = 0$  then no resistor is present in the corresponding dot.

The QP circuit is constructed by connecting the nodes associated with the variables  $V_1 \ldots V_n$  to three types of the basic circuits: equality, inequality and quadratic cost. We will refer to such nodes as *variable nodes*. Each row of the circuit in Fig. 3.5 is one of the basic circuits presented in Sections 3.2.1, 3.2.2 and 3.2.3.

## 3.3 Analog LP circuit

The LP circuit includes the same equality and inequality circuits as in Sections 3.2.1 and 3.2.2 and a linear cost circuit described in the next section.

Figure 3.5: Analog circuit solving a QP. Vertical wires are variable nodes with potentials  $V_1 \ldots V_n$ . Black dots represent resistances that connects vertical and horizontal wires. Horizontal wires are cost or constraint nodes. Some of the horizontal wires are connected to a ground via a negative resistance  $R_i = -\left(\sum_j \frac{1}{R_{ij}}\right)^{-1}$ , a constant voltage source and a diode for inequality nodes.

Figure 3.6: Compact representation of a resistor.

#### 3.3.1 Linear cost function

Although the linear cost is a special case of the quadratic cost (see section 4.4.1), we define a special circuit for linear cost since it promotes understanding of the analog optimization circuit and this form is useful for practical purposes.

Consider the circuit in Fig. 3.7. In this circuit the potential of node  $\alpha$  is equal to  $U_{\text{cost}}$ and the current that exits the node is  $I_{\text{cost}}$ . From (3.14) we have

$$c^{T}V = I_{\text{cost}} + U_{\text{cost}} \sum_{k=1}^{n} \frac{1}{R_{k}} \triangleq J.$$

(3.24)

where  $c = [1/R_1 \dots 1/R_n]^T$ ,  $V = [V_1 \dots V_n]^T$  and J is the cost function. This part of the circuit implements the minimization of the linear cost function. A thorough explanation of the cost circuit requires the equations of the whole LP circuit which will be presented in Section 4.4. Here we present a brief intuitive interpretation.

When  $U_{\text{cost}}$  is set to a low value, the voltages  $V_k$  are driven in a direction that minimizes the current  $I_{\text{cost}}$ . Consequently, the cost J is decreased by decreasing  $U_{\text{cost}}$ .

Figure 3.7: Linear cost circuit.

Figure 3.8: Electric circuit solving an LP. Vertical wires are variable nodes with potentials  $V_1 \ldots V_n$ . Black dots represent resistances that connects vertical and horizontal wires. Horizontal wires are cost or constraint nodes. Each horizontal wire is connected to a ground via a negative resistance, a constant voltage source and a diode for inequalities nodes. The topmost horizontal wire is the linear cost circuit which is connected to a constant voltage source  $U_{\text{cost}}$ .

Note that we can obtain the circuit in Fig. 3.7 from Fig. 3.4 simply by setting one of the variables to a constant voltage  $U_{\text{cost}}$ .

#### 3.3.2 Connecting the basic circuits to form an LP circuit

This section presents how to construct the circuit that solves a general LP. A similar circuit to the QP circuit in Fig. 3.5 for solving LP is shown in Fig. 3.8. The circuit includes a linear cost circuit instead of quadratic cost circuits. Each row of the circuit in Fig. 3.8 is one of the basic circuits presented in Sections 3.2.1, 3.2.2 and 3.3.1. The LP circuit in Fig. 3.8 is a special case of the QP circuit Fig. 3.5 as will be shown in section 4.4.

**Remark 1.** Note that one can easily change the rhs of equality constraints (3.12) or/and inequality constraints (3.16) to a different value b by simply using a voltage source equal to

$b/\sum_{k=1}^{n} \frac{1}{R_k}$ . This allows one to solve parametric problems by simply changing the value of the external voltage sources.

The circuit as shown in Fig. 3.5 contains no dynamic elements such as capacitors or inductors. Therefore, the time required to reach steady-state is governed by the parasitic effects (e.g. wires inductance and capacitance) and by the properties of the elements used to realize negative resistance (usually opamp) and diode. Hence, a good electronic design can achieve solution times on the order of these parasitic effects as shown in Chapters 5 and 7.

# Chapter 4

# Steady state analysis of the QP/LP circuit

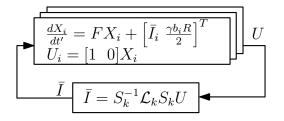

Consider the QP circuit in Fig. 3.5 with  $R_{ij}$  defined by Eqs. (3.22)-(3.23). In this chapter we show that the QP circuit in Fig. 3.5 solves the optimization problem (3.1). In particular, the steady-state circuit voltages are the components of an QP optimal solution. First, we derive the steady state equations of the electric circuit and then we show the equivalence.

## 4.1 Steady state solution of the QP circuit

Consider the circuit in Fig. 3.5. Let  $U = [U_1, \ldots, U_m]^T$  be the voltages of the constraint nodes as shown on Fig. 3.5. By applying the KCL (Kirchhoff's current law) to every variable node with potential  $V_1, \ldots, V_n$ , we obtain

$$\sum_{i=1}^{m} A_{i,j}(U_i - V_j) = 0, \ j = 1, \dots, n$$

(4.1)

which can be rewritten in the matrix form

$$\begin{bmatrix} A_{11} & A_{1n} \\ \vdots & \vdots \\ A_{m1} & A_{mn} \end{bmatrix}^T \begin{bmatrix} U_1 \\ \vdots \\ U_m \end{bmatrix} = \begin{bmatrix} (\sum_{i=1}^m A_{i,1})V_1 \\ \vdots \\ (\sum_{i=1}^m A_{i,n})V_n \end{bmatrix}.$$

(4.2)

Eq. (4.2) can be compactly written as

$$A^T U = \operatorname{diag}(\mathbf{1}^T A) V, \tag{4.3}$$

where m is the number of equality and inequality constraints, **1** is a vector of ones, and diag(x) is a diagonal matrix with x on its diagonal.

Next, we apply KCL on all nodes with potentials  $[U_1, \ldots, U_m]$  to obtain

$$\sum_{j=1}^{n} A_{i,j}(U_i - V_j) = I_i, \quad i = 1, \dots, m,$$

(4.4)

which can be written in the matrix form

$$\begin{bmatrix} A_{11} & . & A_{1n} \\ \vdots & . & \vdots \\ A_{m1} & . & A_{mn} \end{bmatrix} \begin{bmatrix} V_1 \\ \vdots \\ V_n \end{bmatrix}$$

$$= \begin{bmatrix} U_1 \sum_{j=1}^n A_{1,j} \\ \vdots \\ U_m \sum_{j=1}^n A_{m,j} \end{bmatrix} + I, \qquad (4.5)$$

where  $I = [I_1 \dots I_n]$ . Eq. (4.5) can be compactly rewritten as

$$AV = \operatorname{diag}\left(\mathbf{1}^{T}A^{T}\right)U + I.$$

(4.6)

The equality voltage regulator law (3.15) and the inequality law (3.17) can be compactly written as

$$\operatorname{diag}\left(\mathbf{1}^{T} A_{\operatorname{eq}}^{T}\right) U_{\operatorname{eq}} = b_{\operatorname{eq}} - I_{\operatorname{eq}} \tag{4.7a}$$

diag

$$(\mathbf{1}^T A_{\text{ineq}}^T) U_{\text{ineq}} \le b_{\text{ineq}} - I_{\text{ineq}}.$$

(4.7b)

By substituting (4.7) into (4.6), we obtain

$$A_{\rm eq}V = b_{\rm eq} \tag{4.8a}$$

$$A_{\text{ineq}}V \le b_{\text{ineq}}.$$

(4.8b)

Substitution of (4.6) for inequalities to the diode constraint (3.20) yields

$$[A_{\text{ineq}}V - b_{\text{ineq}}]_i [I_{\text{ineq}}]_i = 0, \ \forall i \in \mathcal{I},$$

(4.9)

where  $\mathcal{I}$  is the set of all inequality constraints.

We collect (4.3), (4.1), (4.8), and (3.19a) into one set of equations which characterize the circuit

$$AV = \operatorname{diag}\left(\mathbf{1}^{T}A^{T}\right)U + I \tag{4.10a}$$

$$A^{T}U = \operatorname{diag}(\mathbf{1}^{T}A)V \tag{4.10b}$$

$$A_{\rm eq}V = b_{\rm eq} \tag{4.10c}$$

$$A_{\text{ineq}}V \le b_{\text{ineq}} \tag{4.10d}$$

$$I_{\text{ineq}} \ge 0 \tag{4.10e}$$

$$\left[A_{\text{ineq}}V - b_{\text{ineq}}\right]_i \left[I_{\text{ineq}}\right]_i = 0, \forall i \in \mathcal{I}$$

(4.10f)

where U, I and V are the unknowns. The equations (4.10a) and (4.10b) are derived by appling KCL for all V nodes and U nodes respectively, equation (4.10c) originates from voltage control law for the equality nodes, equations (4.10e), (4.10d), (4.10f) describe ideal diode model and voltage control law for the inequality nodes

# 4.2 Equivalence of the QP optimization problem and the electric circuit

Assumption 1. The QP (3.1) is feasible and the feasible set is bounded.

Assumption 2. The matrices  $A_{eq}$  and  $A_{ineq}$  in the QP (3.1) are non-negative,  $\mathbf{1}^T A > 0$  and  $\mathbf{1}^T A^T > 0$ .

**Assumption 3.** The matrix Q in the QP(3.1) is positive definite and strictly diagonally dominant.

The Assumption 2 is almost trivial, since  $A_{eq}$  and  $A_{ineq}$  can be made non-negative as follows from Proposition 1,  $\mathbf{1}^T A > 0$  holds if there are no zero columns (unused variables), and  $\mathbf{1}^T A^T > 0$  holds if there are no zero rows (empty constraints).

The Assumption 3 is not very restrictive, since any positive definite matrix can be transformed to a strictly diagonal dominant form by coordinate transformation, e.g. by an eigenvalue decomposition.

**Theorem 1** (Steady state of the circuit is a solution to a QP). Let Assumptions 1 and 2 hold. Then, the Eqs. (4.10) have a solution, and the solution is the optimizer of the QP (3.1) with

$$Q = Q_A = \operatorname{diag}\left(\boldsymbol{1}^T A\right) - A^T \operatorname{diag}\left(\boldsymbol{1}^T A^T\right)^{-1} A.$$

(4.11)

*Proof.* First we rearrange (4.10). Eq. (4.10a) can be split into equality and inequality parts

$$A_{\rm eq} = \operatorname{diag}\left(\mathbf{1}^T A_{\rm eq}^T\right) U_{\rm eq} + I_{\rm eq} \tag{4.12}$$

$$A_{\text{ineq}} = \text{diag}\left(\mathbf{1}^T A_{\text{ineq}}^T\right) U_{\text{ineq}} + I_{\text{ineq}}.$$

(4.13)

Eq. (4.10b) can be rewritten as

$$A_{\rm eq}^T U_{\rm eq} + A_{\rm ineq}^T U_{\rm ineq} = {\rm diag} \left( \mathbf{1}^T A \right) V. \tag{4.14}$$

Therefore, (4.10) can be written as

$$A_{\rm eq}V = {\rm diag}\left(\mathbf{1}^T A_{\rm eq}^T\right) U_{\rm eq} + I_{\rm eq} \tag{4.15a}$$

$$A_{\text{ineq}}V = \text{diag}\left(\mathbf{1}^{T}A_{\text{ineq}}^{T}\right)U_{\text{ineq}} + I_{\text{ineq}}$$

(4.15b)

$$A_{\rm eq}^T U_{\rm eq} + A_{\rm ineq}^T U_{\rm ineq} = {\rm diag} \left( \mathbf{1}^T A \right) V \tag{4.15c}$$

$$A_{\rm eq}V = b_{\rm eq} \tag{4.15d}$$

$$A_{\text{ineq}}V \le b_{\text{ineq}}$$

(4.15e)

$$I_{\text{ineq}} \ge 0 \tag{4.15f}$$

$$(A_{\text{ineq}}V - b_{\text{ineq}})_i I_{\text{ineq}_i} = 0, \ \forall i \in \mathcal{I}.$$

$$(4.15g)$$

Next, consider the following quadratic program (QP)

$$\min_{V} \frac{1}{2} V^{T} Q_{A} V$$

s.t.  $A_{eq} V = b_{eq}$

(4.16a)

$$A_{\text{ineq}}V \le b_{\text{ineq}},\tag{4.16b}$$

From Assumption 1, Problem (4.16) has a finite solution for any  $Q_A$  because the feasibility domain is bounded and not empty. The value of  $Q_A$  will be selected later. We use this problem to find a solution to (4.10). The KKT conditions are necessary optimality conditions for problems with linear constraints [8, Theorem 5.1.3]. Therefore, there exist  $V^*$ ,  $\mu^*$ ,  $\lambda^*$ which satisfy the KKT conditions

$$A_{\rm eq}^T \mu^\star + A_{\rm ineq}^T \lambda^\star + Q_A V^\star = 0 \tag{4.17a}$$

$$A_{\rm eq}V^{\star} = b_{\rm eq} \tag{4.17b}$$

$$A_{\rm ineq}V^{\star} \le b_{\rm ineq} \tag{4.17c}$$

$$\lambda^{\star} \ge 0 \tag{4.17d}$$

$$(A_{\text{ineq}}V^{\star} - b_{\text{ineq}})_i \lambda_i^{\star} = 0, \ i \in \mathcal{I},$$

(4.17e)

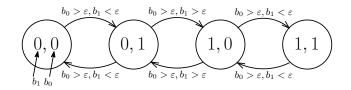

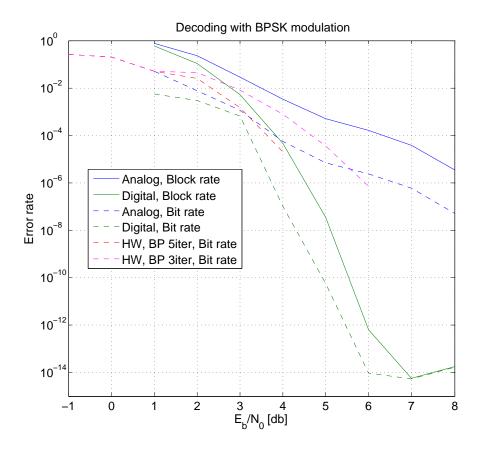

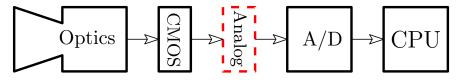

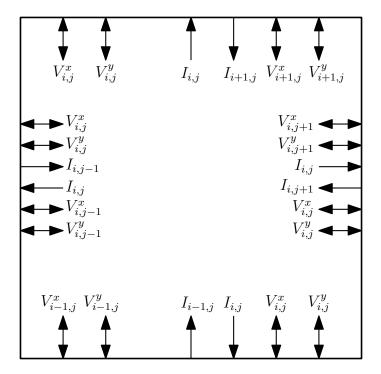

where  $\mu^*$  and  $\lambda^*$  are the dual variables of the QP (4.16).