### **UC Davis**

### **UC Davis Electronic Theses and Dissertations**

### **Title**

Re-imagining the Security of the Hardware using Lookup Table based Obfuscation

### **Permalink**

https://escholarship.org/uc/item/0257r2q3

### **Author**

Kolhe, Gaurav

### **Publication Date**

2022

Peer reviewed|Thesis/dissertation

# Re-imagining the Security of the Hardware using Lookup Table based Obfuscation

By

# GAURAV KOLHE DISSERTATION

Submitted in partial satisfaction of the requirements for the degree of

### DOCTOR OF PHILOSOPHY

in

**Electrical and Computer Engineering**

in the

OFFICE OF GRADUATE STUDIES

of the

UNIVERSITY OF CALIFORNIA

**DAVIS**

Approved:

Houman Homayoun, Chair

Bevan Bass

Vivek Menon

Committee in Charge

2022

### Abstract

The increasing cost of manufacturing the complex Integrated Circuits (ICs) and ever-rising competition to shorten time-to-market have given rise to the trend of fabless manufacturing. Moreover, the addition of various players in the product manufacturing lifecycle has endangered the security of Intellectual Properties (IPs). "Logic locking" and "IC camouflaging" are amongst the most prevalent protection schemes that can thwart various hardware security threats. However, the state-of-the-art attacks such as Boolean Satisfiability Attack (SAT-attack) and approximation-based attacks, question the efficacy of the existing defense schemes.

Recent solutions to protect hardware designs from various hardware security threats have employed a myriad of obfuscation techniques. However, these solutions have mostly focused on specific design elements such as "SAT-hardness". Despite meeting the focused criterion such as "SAT-hardness" for maximizing security, obfuscated designs are still vulnerable to the newly evolving attack vectors. To mitigate this problem and provide a better solution for thwarting SAT-attack and evolving attack vectors, Look-Up Table (LUT)-based obfuscation is studied. This work provides an extensive analysis of LUT-based obfuscation by exploring several factors such as LUT technology, size, number of LUTs, and replacement strategy as they have a substantial influence on the Power-Performance-Area (PPA) and security of the design.

For making the reconfigurable logic obfuscation efficient in terms of design overheads, this work further proposes a novel architecture using LUT. Additionally, a study is conducted with different threat models and attack vectors to show that the security provided by the proposed primitive is superior to that of the traditional ways of LUT-based obfuscation.

While many existing works have focused on mitigating the well-known SAT-attack and its derivatives, there hasn't been much research on preventing Power Side-Channel Attacks (P-SCAs), which have the capability to retrieve the sensitive contents of the IP in a non-invasive manner. Using P-SCA for unlocking the obfuscated circuit, does not require the laborious task of simulating powerful SAT attacks. For maximizing the security, and curbing P-SCA, the work proposes a "defense-indepth obfuscation" which builds on our existing LUT-based solution. The proposed obfuscation is tailored such that LUT-based obfuscation incurs minimal overheads while providing a full-scale robust solution to secure the hardware.

Additionally, this work invents a security-driven design flow, which uses off-the-shelf industrial Electronic Design Automation (EDA) tools for easier obfuscation of the design. This proposed flow is meticulously crafted in a way such that it is non-disruptive to the current industrial physical design flow. To enable this flow one must overcome some obstacles; as there is a lack of frameworks and unified methods that can validate the security and functionality of obfuscated designs. This work has discussed the challenges of validating the security and functionality of obfuscated designs and further presents the methodology for verifying the functionality of the LUT-based obfuscated IP (pre and post-fabrication). Additionally, Security Evaluation Platform for Hardware Logic Obfuscation using Intelligent Artificial Neural Net (SEPIANN) is proposed to validate the security of the design. This system-level framework instantaneously estimates the obfuscation strength in terms of attack resiliency time eliminating the need to simulate de-obfuscation using the SAT-attack.

Finally, the work shows the application and scalability of the proposed work by fabricating various security and computing cores by obfuscating them with the LUT-based obfuscation.

### Acknowledgment

With a heart full of gratitude I would like to thank my advisor, Professor Houman Homayoun, who supported me throughout the entire journey of my Ph.D., He provided me the opportunity to conduct groundbreaking research and helped me unlock my true potential. His insightful feedback pushed me to sharpen my thinking and brought my work to a higher level.

I want to extend my gratitude to Defense Advanced Research Projects Agency (DARPA), Air Force Research Laboratory (AFRL), and the National Science Foundation Center for Hardware and Embedded Systems Security and Trust (CHEST) as the various parts of the research were primarily funded by them.

Moreover, I would also like to acknowledge my mentor, Dr. Vivek Menon, from the Department of Defense, and Dr. Sai Manoj from George Mason University for always guiding me and I would also like to thank Prof. Bevan Baas, Prof. Setareh Rafatirad, and Prof. Soheil Ghiasi who served on my dissertation and qualification exam committee. Your valuable comments and feedback were very significant.

In addition, I would like to express my gratitude to my loving parents for their unconditional trust, timely encouragement, and emotional and financial support. It was their love that raised me when I got weary. I am grateful to my sister Ankita. You're a beautiful sister who has always shown deep and unwavering care for me all of my life.

"Where we love is home, home that our feet may leave, but not our hearts."

I could not have completed this dissertation without the support of my friends, who provided stimulating discussions and happy distractions to rest my mind outside of my research. You made me feel at home while being away from home.

Finally, I am also thankful to the University of California, George Mason University, and all of its wonderful staff who helped me with various aspects of clerical work.

# Contents

| 1 | Spec | cific Aims of the Research                                                         | 1  |

|---|------|------------------------------------------------------------------------------------|----|

|   | 1.1  | Aim I - Breaking the trade-off between design overheads and security for LUT-based |    |

|   |      | obfuscation.                                                                       | 1  |

|   | 1.2  | Aim II - Providing multi-layer defense mechanism.                                  | 1  |

|   | 1.3  | Aim III - Validating the security of an obfuscated IP.                             | 2  |

| 2 | Intr | oduction                                                                           | 4  |

|   | 2.1  | Hardware Security                                                                  | 4  |

| 3 | Back | kground                                                                            | 8  |

|   | 3.1  | Logic Locking                                                                      | 8  |

|   | 3.2  | Overview of the SAT-Attack                                                         | 9  |

|   | 3.3  | Working of the SAT-Attack                                                          | 10 |

|   | 3.4  | Resisting SAT-Attack                                                               | 14 |

| 4 | Loo  | kup Table Obfuscation                                                              | 15 |

|   | 4.1  | Lookup Table-based obfuscation                                                     | 15 |

|   | 4.2  | Impact of LUT Technology                                                           | 16 |

|   |      | 4.2.1 Design and Integration of Spin Transfer Torque-based Look-up Table           | 17 |

|   |      | 4.2.2 STT-Based LUT versus CMOS-based LUT                                          | 19 |

|   | 4.3  | Effect of Replacement Strategies                                                   | 20 |

|   |      | 4.3.1 Random Selection (RND)                                                       | 21 |

|   |      | 4.3.2 Low Output Corruptibility (LC)                                               | 21 |

|   |      | 4.3.3    | Avoiding Unintentionally Correct Key Generation (LC_NoGen)         | 22 |

|---|------|----------|--------------------------------------------------------------------|----|

|   | 4.4  | LUT S    | Size versus Number of LUTs                                         | 25 |

| 5 | Brea | aking tl | ne design and security trade-off of Lookup Table-based Obfuscation | 29 |

|   | 5.1  | SAT-A    | Attack and Lookup Table-based Obfuscation                          | 29 |

|   | 5.2  | Creati   | ing SAT-hard instances using Lookup Table                          | 31 |

|   | 5.3  | Exper    | imental Evaluation                                                 | 33 |

|   |      | 5.3.1    | Experimental Setup                                                 | 33 |

|   |      | 5.3.2    | Security Analysis against SAT-based Attack                         | 35 |

|   |      | 5.3.3    | Comparison with other Obfuscation Methodologies                    | 39 |

|   |      | 5.3.4    | Exploration of Large Benchmark                                     | 40 |

| 6 | Rob  | ust "De  | efense-in-depth" solution using LUT-based Obfuscation              | 42 |

|   | 6.1  | Power    | Side-Channel Attacks (P-SCA)                                       | 43 |

|   | 6.2  | P-SCA    | A resilient LUT-based Obfuscation                                  | 44 |

|   |      | 6.2.1    | Symmetrical MRAM-LUT (SyM-LUT)                                     | 44 |

|   |      | 6.2.2    | SyM-LUT's Resiliency against P-SCA                                 | 47 |

|   | 6.3  | Propo    | sed LOCK & ROLL                                                    | 50 |

|   |      | 6.3.1    | Scan-Enable Obfuscation Mechanism                                  | 50 |

|   |      | 6.3.2    | Elimination of SAT Attack and It's Derivatives!                    | 52 |

|   |      | 6.3.3    | Security Coverage of LOCK & ROLL                                   | 53 |

| 7 | Secu | ırity Va | alidation of an Obfuscated IP                                      | 55 |

|   | 7.1  | Quant    | sifying Security                                                   | 55 |

|   |      | 7.1.1    | SAT Resiliency Pit-Fallacies                                       | 58 |

|   |      | 7.1.2    | Graph Neural Networks                                              | 59 |

|   | 7.2  | SEPIA    | ANN: CNF-NET and De-obfuscation Time Prediction                    | 63 |

|   |      | 7.2.1    | CNF Bipartite Graph Representation                                 | 63 |

|   |      | 7.2.2    | Energy-based Operators for CNF Graph                               | 66 |

|    | 7.3  | Summarizing the SEPIANN                                 | 69 |

|----|------|---------------------------------------------------------|----|

|    | 7.4  | Evaluation of SEPIANN                                   | 72 |

| 8  | Inte | gration of Tool Flow                                    | 76 |

|    | 8.1  | ASIC Iterative Security-driven Design Flow              | 77 |

|    | 8.2  | Configuring the LUT Unit Obfuscation Cell               | 79 |

|    | 8.3  | Validating Obfuscated Designs                           | 80 |

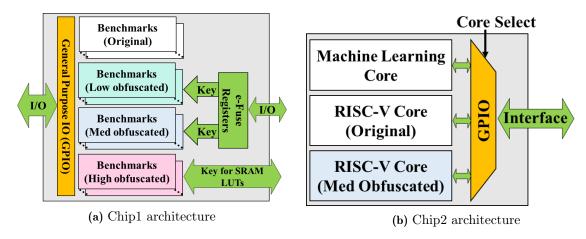

|    | 8.4  | Design and Implementation of Test Chip                  | 81 |

|    | 8.5  | Post-Silicon Validation of LUT-based Logic-Locked Cores | 83 |

|    |      | 8.5.1 Post-silicon Test Fixture                         | 83 |

|    |      | 8.5.2 Post-silicon validation results                   | 84 |

| 9  | Con  | clusion & Future Work                                   | 86 |

|    | 9.1  | Conclusion                                              | 86 |

|    | 9.2  | Contribution                                            | 88 |

|    | 9.3  | Future Work                                             | 90 |

| 10 | Ack  | nowledgments                                            | 91 |

| 11 | Refe | erences                                                 | 92 |

| Ap | pend | lix                                                     | 98 |

# List of Tables

| Table 3.1 | Tseytin Transformation of Basic Logic Gates [1]             | 10 |

|-----------|-------------------------------------------------------------|----|

| Table 5.1 | Benchmarks used for Experimentation with their gate counts. | 34 |

| Table 5.2 | Overhead comparison of various obfuscation techniques.      | 39 |

| Table 6.1 | Parameters of 2-terminal STT-MTJ device.                    | 46 |

| Table 6.2 | Performance of ML-assisted P-SCAs on SyM-LUT                | 49 |

| Table 6.3 | Performance of ML-assisted P-SCAs on SyM-LUT with SOM       | 52 |

| Table 7.1 | Performance of Design Security Analyzer                     | 72 |

| Table 8.1 | Benchmarks included in test chip                            | 82 |

# List of Figures

| Figure 2.1 | Various hardware security threats involved in Fabless manufacturing process.                                                      | 6  |

|------------|-----------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 3.1 | Strong Logic Locking [2]. The attacker can not sensitize either K1 or K2 to a                                                     |    |

|            | primary output O1 or O2.                                                                                                          | 9  |

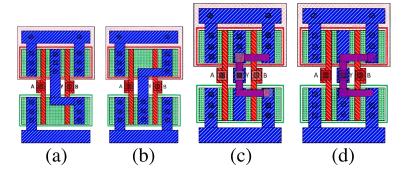

| Figure 3.2 | Standard Cell Versus Camouflaged Cell [3] (a) NAND Cell (b) NOR Cell (c)                                                          |    |

|            | Camouflaged NAND Cell (d) Camouflaged NOR Cell                                                                                    | 9  |

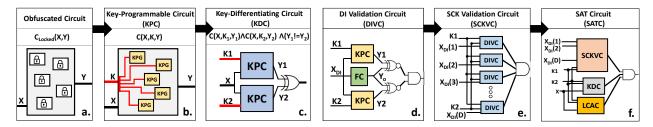

| Figure 3.3 | (a) Transforming an obfuscated circuit to (b) Key-Programmable Circuit and                                                        |    |

|            | (c) Key Differentiating Circuit. (d) DIVC circuit for validating that two input                                                   |    |

|            | keys produce the correct output with respect to a previously discovered DIP. (e)                                                  |    |

|            | SCKVC circuit for validating that both input keys are in SCK set and produce                                                      |    |

|            | the correct output for all previously discovered DIPs. (f) SAT circuit for finding                                                |    |

|            | a new DIP.                                                                                                                        | 11 |

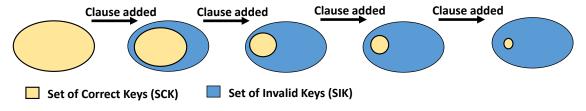

| Figure 3.4 | SCK set reduces in each pass through the while loop in Algorithm 1 as a new DI                                                    |    |

|            | is discovered and is added to SATC circuit.                                                                                       | 13 |

| Figure 4.1 | (a) Sample circuit used for obfuscation with gates G <sub>4</sub> , G <sub>6</sub> , G <sub>7</sub> , G <sub>9</sub> selected for |    |

|            | obfuscation (b) Obfuscation with LUT with representation of the LUT for SAT-                                                      |    |

|            | attack simulation.                                                                                                                | 16 |

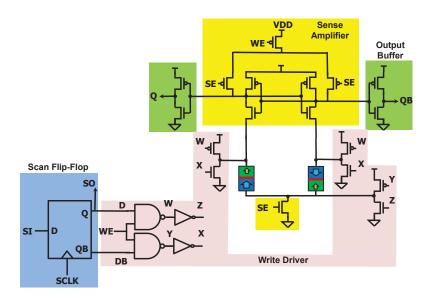

| Figure 4.2 | MTJ latch with Scan Chain Programming.                                                                                            | 18 |

| Figure 4.3 | (a) Proposed STT-LUT with Scan Chain Programming (b) Full custom layout of                                                        |    |

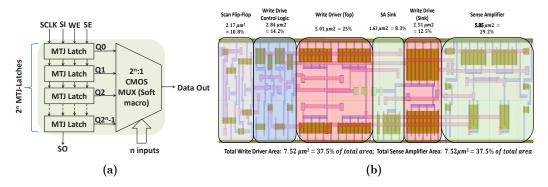

|            | MTJ latch in standard cell format and area breakdown between different blocks                                                     | 19 |

| Figure 4.4 | Comparison of (a) Power, (b) Delay, and Area of STT-LUT and Standard Cells                                                        |    |

|            | in 28nm                                                                                                                           | 20 |

| Figure 4.5 | De-obfuscation time using SAT-attack for Different (1) Replacement Strategy, (2)                                                  |    |

|            | LUT Size (scale up), and (3) Number of LUTs (scale out) in ISCAS-85 c7552 [4]                                                     | 24 |

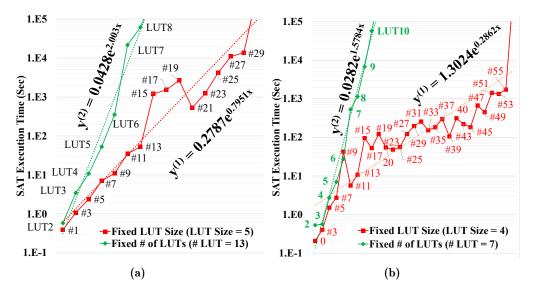

| Figure 4.6 | re 4.6 De-obfuscation time of C7552 benchmark with different number of LUTs and      |    |  |

|------------|--------------------------------------------------------------------------------------|----|--|

|            | different sizes of LUT using SAT-attack [4].                                         | 25 |  |

| Figure 4.7 | LUT scale up vs. scale out: Comparison between the Impact of LUT size and            |    |  |

|            | Number of LUTs on SAT Execution Time [4].                                            | 26 |  |

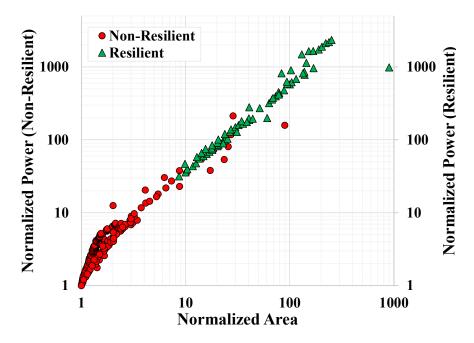

| Figure 4.8 | Normalized area and power overhead of LUT-based obfuscation. Points that result      |    |  |

|            | in SAT execution time out are marked as SAT-resilient configuration [4].             | 27 |  |

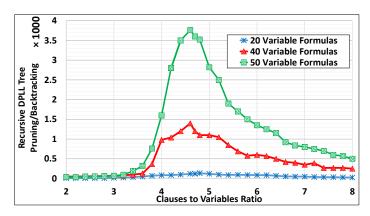

| Figure 5.1 | Median Number of Recursive DPLL Tree Pruning/Backtracking for Random 3-              |    |  |

|            | SAT Formulas, based-on the Ratio of Clauses to Variables [1, 5].                     | 30 |  |

| Figure 5.2 | (a) Proposed novel (LUT $_n$ +n:LUT $_2$ ) (b) SAT-representation of proposed obfus- |    |  |

|            | cation with size 4 (LUT <sub>4</sub> +4:LUT <sub>2</sub> )                           | 33 |  |

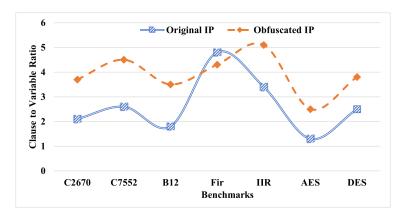

| Figure 5.3 | Effect of obfuscation on the Clause to Variable Ratio.                               | 34 |  |

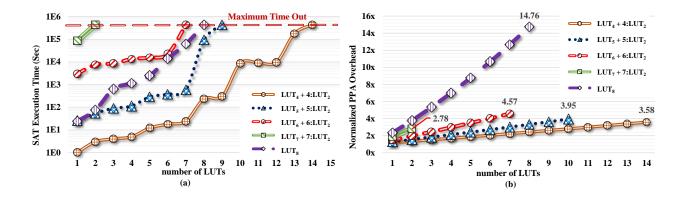

| Figure 5.4 | Comparison of the proposed primitive where the size of the LUT is varied from        |    |  |

|            | 4 to 7 with the traditional LUT-based obfuscation. Figure (a) shows the de-          |    |  |

|            | obfuscation time of various obfuscated samples using SMT-solver and Figure (b)       |    |  |

|            | shows the PPA incurred by the proposed primitive [4].                                | 36 |  |

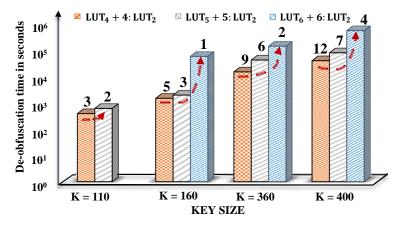

| Figure 5.5 | SMT-solver execution time to find the unlocking key when the benchmark is            |    |  |

|            | obfuscated with different size and number of LUTs. The number and size of the        |    |  |

|            | LUTs to be replaced are determined by the key size which is constrained in this      |    |  |

|            | experiment and denoted by the number above each individual bar [4].                  | 37 |  |

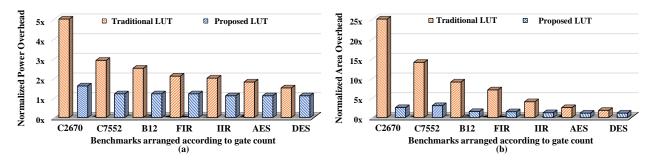

| Figure 5.6 | Comparison of Proposed LUT obfuscation with the traditional LUT-based obfus-         |    |  |

|            | cation in terms<br>of (a) Design Area overhead (b) Design power overheads            | 38 |  |

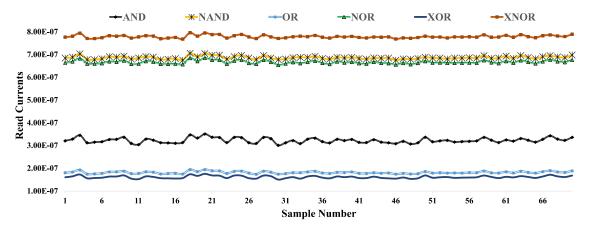

| Figure 6.1 | Read current traces of a 2-input MRAM-LUT in [6]. (Y-axis: Read Current in           |    |  |

|            | Amps; X-axis samples in collected data)                                              | 44 |  |

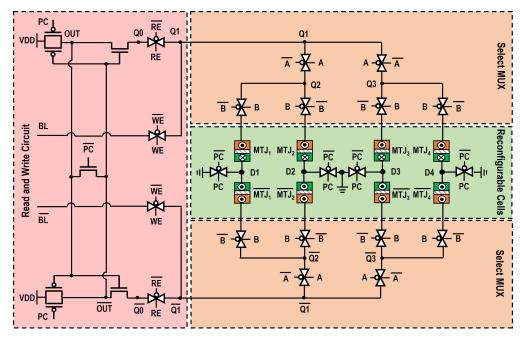

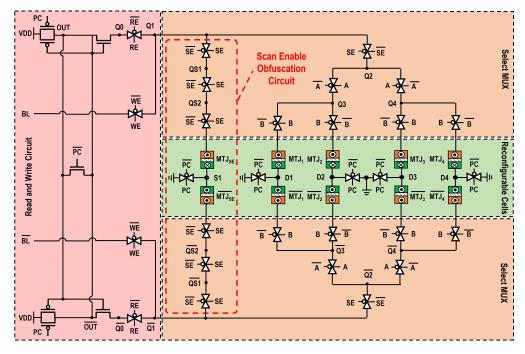

| Figure 6.2 | The circuit-level diagram of the proposed 2-input SyM-LUT using STT-MTJ              |    |  |

|            | devices.                                                                             | 45 |  |

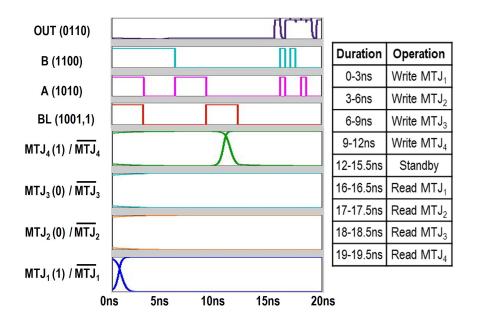

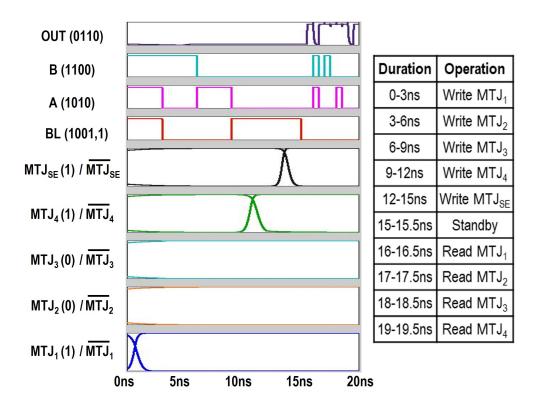

| Figure 6.3 | Simulation waveform for implementation of a 2-input XOR gate using SyM-LUT.          | 47 |  |

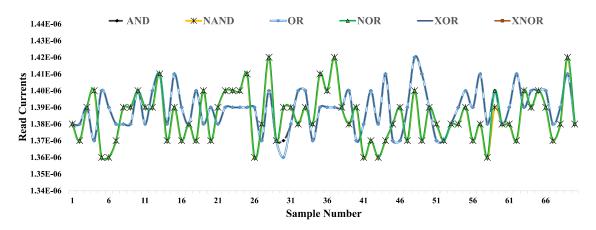

| Figure 6.4 | Read current trace samples of 2-input SyM-LUT implementing various functions         |    |  |

|            | using Monte Carlo instances.                                                         | 48 |  |

| Figure 6.5 | The circuit-level diagram of the proposed 2-input SyM-LUT with SOM using                                                            |    |

|------------|-------------------------------------------------------------------------------------------------------------------------------------|----|

|            | STT-MTJ devices.                                                                                                                    | 51 |

| Figure 6.6 | Simulation waveform for implementation of a 2-input XOR gate using SyM-LUT                                                          |    |

|            | with $\mathbf{MTJ}_{SE}$ being set to value of "0".                                                                                 | 52 |

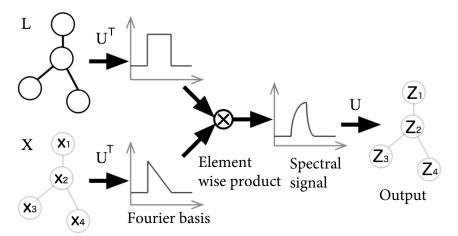

| Figure 7.1 | Graph Convolutional Network workflow.                                                                                               | 60 |

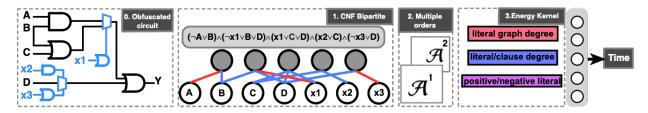

| Figure 7.2 | Architecture of CNF-NET: 1) extract CNF graph from obfuscated circuit; 2)                                                           |    |

|            | derive multiple order information from graph representation (section 7.2.1); 3)                                                     |    |

|            | apply energy kernel to aggregate intermediate features (section 7.2.2); 4) utilize                                                  |    |

|            | distribution layer on graph properties to sample runtime.                                                                           | 64 |

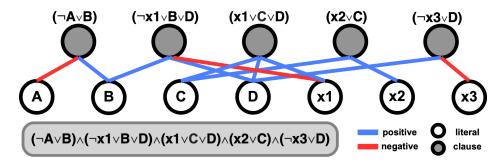

| Figure 7.3 | An example showing the conversion from CNF to $1^{st}$ order graph.                                                                 | 65 |

| Figure 7.4 | A simple example showing (left): adjacency matrix of $1^{st}$ order graph: $\mathcal{A}$ , which                                    |    |

|            | models the example in Figure 7.3; and (right): adjacency matrix of $2^{nd}$ order                                                   |    |

|            | graph: $\mathcal{A}^2$ . There are 5 clauses: clause $\mathcal{C}_1 = \{\neg A, B\}$ , clause $\mathcal{C}_2 = \{\neg x1, B, D\}$ , |    |

|            | clause $C_3 = \{x1, C, D\}$ , clause $C_4 = \{x2, C\}$ , clause $C_5 = \{\neg x3, D\}$ .                                            | 65 |

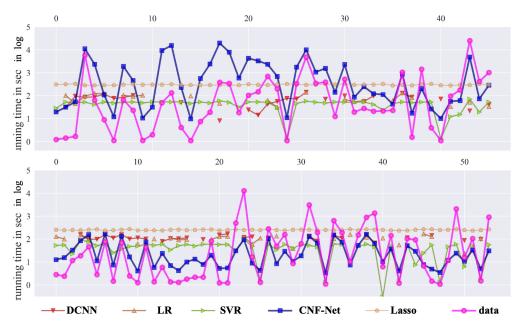

| Figure 7.5 | Prediction performance on B04 and B12 benchmarks: x-axis is various obfuscated                                                      |    |

|            | instances and y-axis denotes the predicted runtime compared with real runtime                                                       |    |

|            | (label of $data$ ).                                                                                                                 | 73 |

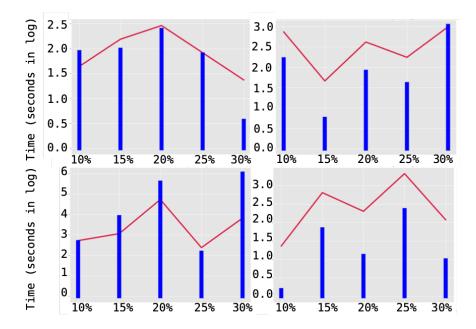

| Figure 7.6 | Prediction performance on samples from benchmark under different obfuscation                                                        |    |

|            | policies ( $LC\_NoGen$ and Random), here X-axis denotes obfuscation percentages                                                     |    |

|            | while Y-axis demonstrate the de-obfuscation time in seconds.                                                                        | 74 |

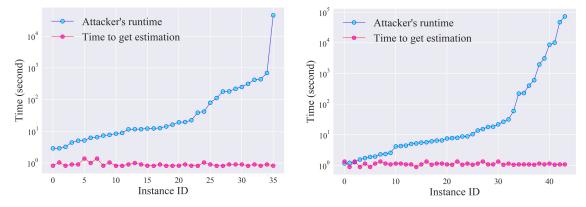

| Figure 7.7 | Real runtime compared with prediction time on y-axis and different obfuscated                                                       |    |

|            | instances on x-axis for benchmarks B04 and B12 respectively.                                                                        | 74 |

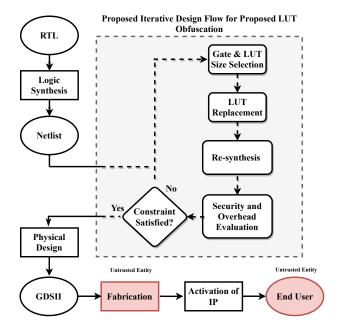

| Figure 8.1 | Iterative-based Security-driven Design Flow for PPA optimization with optimal                                                       |    |

|            | security solution.                                                                                                                  | 77 |

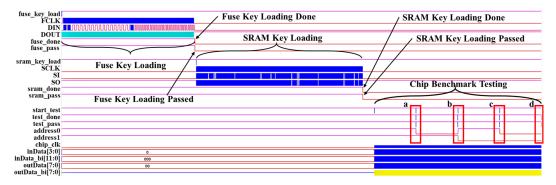

| Figure 8.2 | Synopsys VCS pre-silicon simulation for verification of obfuscated IP. The simulations                                              |    |

|            | include validation of a) original design, b) low, c) medium, and d) high obfuscated versions.                                       | 80 |

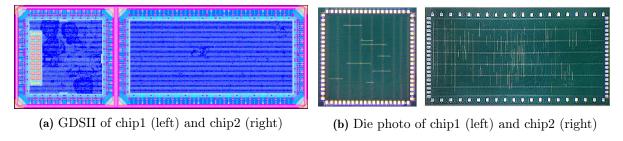

| Figure 8.3 | (a) GDSII and (b) Die of chip1 and chip2                                                                                            | 81 |

| Figure 8.4 | Overall Architecture for chip1 (a) and chip2 in (b)                                                                                 | 82 |

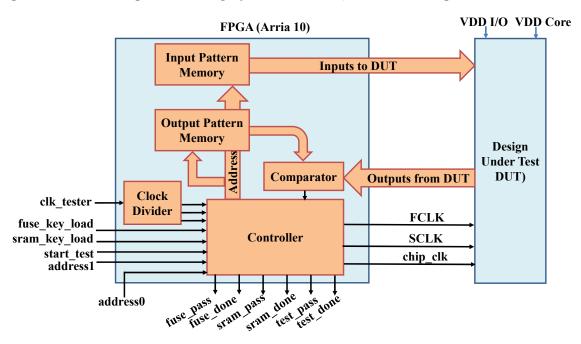

| Figure 8.5  | Diagram of FPGA-based Silicon validation setup for validating the functionality of ob-          |     |  |

|-------------|-------------------------------------------------------------------------------------------------|-----|--|

|             | fuscated IP post fabrication.                                                                   | 83  |  |

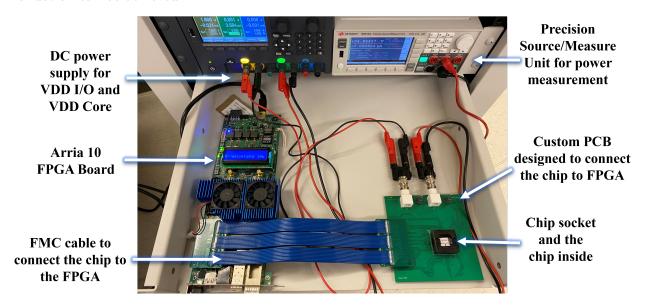

| Figure 8.6  | Figure 8.6 Test setup using the Intel Aria 10 development kit.                                  |     |  |

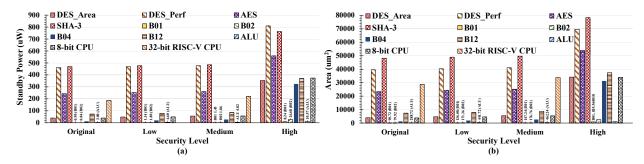

| Figure 8.7  | Figure 8.7 Study of (a) Standby power and (b) area for various obfuscation levels and benchmark |     |  |

|             | for LUT-based obfuscation.                                                                      | 85  |  |

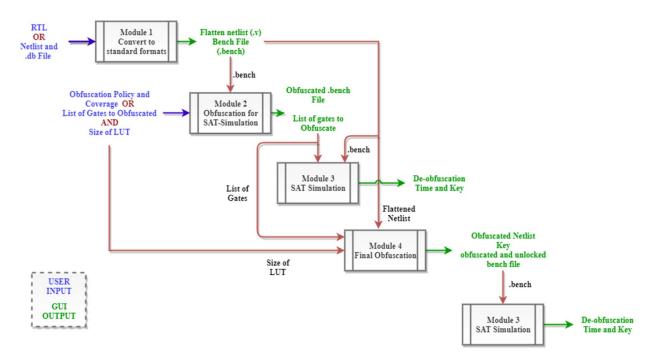

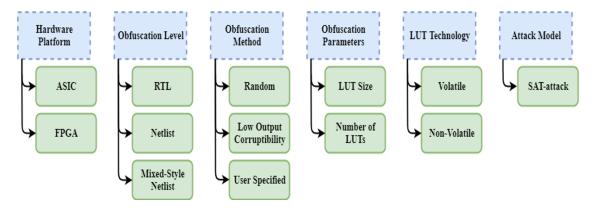

| Figure 11.1 | Automated LUT-based Obfuscation Flow                                                            | 99  |  |

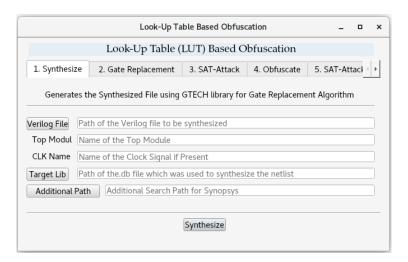

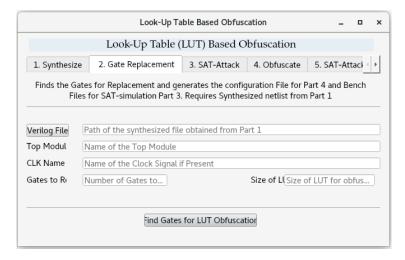

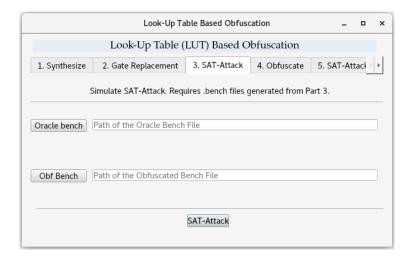

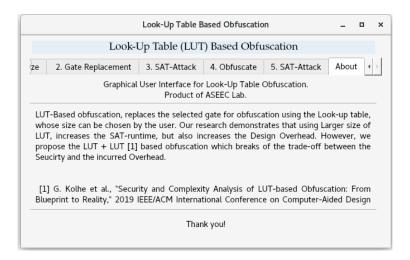

| Figure 11.2 | Flexibility and Functionality offered by the Customized LUT-obfuscation GUI                     |     |  |

|             | Tool                                                                                            | 101 |  |

| Figure 11.3 | Synthesize Module (Module 1)                                                                    | 101 |  |

| Figure 11.4 | Gate Replacement Module (Module 2)                                                              | 102 |  |

| Figure 11.5 | SAT-Attack Module (Module 3)                                                                    | 102 |  |

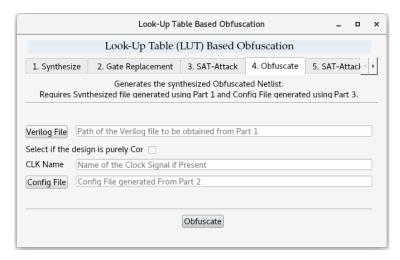

| Figure 11.6 | Final Obfuscation Module (Module 4)                                                             | 102 |  |

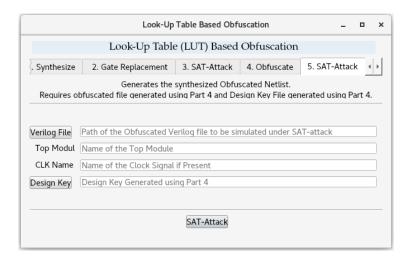

| Figure 11.7 | SAT-attack post obfuscation (Module 5)                                                          | 103 |  |

| Figure 11.8 | About Page                                                                                      | 103 |  |

## Chapter 1

## Specific Aims of the Research

# 1.1. Aim I - Breaking the trade-off between design overheads and security for LUT-based obfuscation.

Maximizing profits while minimizing the risk in a technologically advanced silicon industry has motivated the globalization of the fabrication and electronic hardware supply chains. However, with the increasing magnitude of successful hardware attacks, the security of hardware IPs has been compromised. Many existing security works have focused on resolving a single vulnerability such as SAT-attack while neglecting the possibility other threats. The lack of the obfuscation method that can provide security against various threat has motivated us to propose a novel approach for securing hardware IPs during the fabrication process and supply chain via logic obfuscation by utilizing LUT-based obfuscation. The first part of this research aims to study and deploy the LUT-based obfuscation that protects against most of the hardware security attacks while breaking the trade-off between security and imposed overheads. Moreover, the work establishes a standard security-driven flow for deploying LUT-based obfuscation, which is non-disruptive to standard Application-Specific Integrated Circuit (ASIC)-design flow.

### 1.2. Aim II - Providing multi-layer defense mechanism.

While LUT-based obfuscation can thwart most attacks, a successful security scheme usually uses a defense-in-depth mechanism. With the constant evaluation of the attack vectors, reliance on single security primitive is not recommended, and thus in this part, the aim is to realize the "defense-

in-depth" obfuscation using LUT. Moreover, the logic obfuscation community uses a threat model, which assumes the key for restoring the functionality of the obfuscated IP is stored in the tamper-proof memory, where an attacker can't access its content. However, in reality, due to the surge of P-SCA, it is possible to retrieve the content of the tamperproof memory without simulating SAT-attack, and thus, the work focuses on making the obfuscation resilient to P-SCA. The work proposes a multi-layer defense mechanism called Deep-Learning Power Side-Channel Attack Mitigation using Emerging Reconfigurable Devices and Logic Locking (LOCK & ROLL). LOCK & ROLL utilizes Magnetoresistive Random-Access Memory (MRAM)-based LUT called Symmetric Magnetoresistive Random-Access Memory-based Look-up Table (SyM-LUT) with Scan-Enable Obfuscation Mechanism (SOM), which is the key element that provides "defense-in-depth" solutions for restoring the trust in Silicon.

### 1.3. Aim III - Validating the security of an obfuscated IP.

Finally, numerous defense mechanisms exist for an IP owner who wants to protect his IP against various hardware security threats. As the defense mechanisms' success depends on the underlying characteristics of the IP being secured, evaluating and validating the security of the IP after the integration of obfuscation logic against various attacks is a highly crucial step. However, the security evaluation against SAT-attack can take a few days to months using a contemporary method of simulating the attack. A mechanism that can instantaneously assess the strength of different obfuscation schemes against SAT-attack is the need of the hour. This work proposes the methodology for validating the security and the functionality of the LUT-based Logic-Locked IP Cores.

#### Outline

The research proposes a full-fledged solution to mitigate hardware security threats. The following chapter introduces the concept of hardware obfuscation, security, and attack vectors/threats. Lookup table-based obfuscation and its empirical evaluation against SAT-attack is covered in Chapter 4. Further, this section introduces a novel architecture that breaks the trade-off in chapter 5 to make LUT-based obfuscation a more viable means of obfuscation. To render maximum security against various threat vectors, chapter 6 uses LUT-based obfuscation to deploy a defense-in-depth

solution in the hardware security domain. Finally, Chapter 7 discusses the methodology to verify the security of the obfuscation instantaneously using neural networks, and Chapter 8 introduces obfuscation flow and the results from the fabricated version of the IPs obfuscated with LUT. The conclusion of the work is drawn in Chapter 9.

## Chapter 2

## Introduction

### 2.1. Hardware Security

With the rapid advancement in semiconductor technology due to "technology scaling," the dimensions of the ICs have been reducing which has led to the increasing transistor density on a die. Today, the device integration density has continued to double every two years, following "Moore's Law." This trend has led to a rapid increase in the computational power of IC from its advent into manufacturing in the 1960s. However, this growth has not been cheap. The complexity in design increases the time-to-market, manufacturing costs, and recurring and non-recurring test costs at different levels of abstraction. The IP production house has to account for these by-products of Moore's Law to sustain itself in today's competing market. This need has led to heavy reliance on the:

- 1. Third-party fabrication services for cheaper manufacturing and testing

- 2. Third-party soft/hard IP core vendors to reduce design time, increase reliability with preverification, and hence time-to-market.

Today, the design, manufacturing, and assembly of modern ICs consisting of millions and billions of transistors with intricate fabrication processes are backed by a complex network of global suppliers. For example, one of the United States (US)-based semiconductor companies has 7,300 suppliers spread over 46 states in the US, and more than 8,500 suppliers that are geographically located outside of the US. [7]. The globalization of the fabrication process and hardware supply chain

benefits mainly from the diverse and varied skills of human resources and geographical advantages of suppliers.

In the fabless model, the IP is made available to Contract Manufacturers (CM) responsible for mass production. The ICs are then tested, with the good ones being sent to the next stage of the supply chain, whereas the rest is either recycled or dumped as an e-waste. The next phase of the supply chain consists of the Authorized Sellers/Distributors supplying the semiconductor chips to Original Equipment Manufacturers (OEM).

Consumers heavily rely on the company's reputation for providing the end product, which depends on the Original Chip Manufacturer (OCM) reputation. The end applications can range from simple day-to-day hand-held gadgets to critical ones potentially dealing with health, safety, and security. Any vulnerability introduced in the IC supply chain ripples back and forth through the chain regarding economic damages, reputation, and consumer health and safety.

Monitoring the flow of the final products becomes a daunting, impossible task once the IP leaves the design house through brokers, sub-contractors, OEM, and their CM. In recent years, thousands of independent distributors and brokers have set up shop outside the traditional supply chain consisting of simply OCMs and their Authorized Distributors with the help of e-commerce. Consumers are offered products with better availability and possibly lower costs, so they often fall prey to spurious brokers. One of the reasons for such spurious products being present in the market is e-waste recycling. Environmental awareness has resulted in electronics waste (e-waste) no longer ending up in landfills; instead, they have been known to be recycled by removing electronic components from scrap circuit boards sent for "recycling." These used components can then be refurbished and remarked to indicate new and/or higher-performing parts. Some component buyers might also end up buying out-of-production chips with lower performance. The OCM, OEM, and CM remain oblivious to these forged products in the supply chain until/unless they register huge failure rates or warranty claims. At this point, the damages can be irreparable.

An inference to the above discussion is with the dissolution of control over the IC supply chain where most of the security challenges are introduced, such as overproduction, trojan insertion, Reverse Engineering (RE), IP theft, and counterfeiting [8] to name a few. Figure 2.1 shows the various hardware security threats during multiple stages of IP manufacturing.

To curb various threats involved during IP manufacturing, Hardware Obfuscation was intro-

Figure 2.1. Various hardware security threats involved in Fabless manufacturing process.

duced. Hardware Obfuscation is a technique that makes understanding or RE of a design difficult. To protect hardware IP from these threats, the design must be unintelligible, even in decrypted form. Hardware obfuscation provides the option to effectively hide and disable the design while facilitating structural testing and static/dynamic parameter analysis during manufacturing. This convenience makes obfuscation a desirable method for security and an active field of research.

Numerous obfuscation techniques, namely logic locking and camouflaging, have been proposed to thwart existing hardware security threats. Increased interest within the logic locking and IC camouflaging research community has persuaded Mentor Graphics, a major Computer-aided design (CAD) tool provider, to release TrustChain, which is a CAD framework that supports logic locking and camouflaging as a means of curbing various hardware security threats [9]. However, recently introduced attacks have exploited vulnerabilities in various available logic obfuscation schemes. SAT-attack is one of the most effective de-obfuscation/de-camouflaging techniques. Such attacks vectors can RE a target design even when state-of-the-art logic locking and camouflaging protection mechanisms [10, 11] are used.

For the working of SAT-attack, it requires a reverse-engineered netlist along with an oracle copy. An oracle copy is the activated, working copy of the obfuscated design. Although IC RE for netlist extraction is a slow and expensive process, it has become more practical today with the advent of advanced imaging and probing techniques such as focused ion beam (FIB) and scanning electron microscopy (SEM). To RE the design, an attacker needs to perform delayering, high-resolution imaging or X-raying, and image processing to retrieve the netlist from a fabricated IC. If the adversary is a foreign government or competitive ill-intended organization, acquiring this expensive imaging equipment is possible. Therefore, sensitive designs, like military-grade ICs, need to be kept secure from such threats.

To curb the SAT-attack, recent works in the domain of reconfigurable obfuscation make use of

diverse approaches like increasing the number of reconfigurable blocks [12] to reinforce the security against the SAT-attack. However, on closer study, it is observed that security can be compromised despite considering all substantial and compelling factors for reconfigurable logic obfuscation.

Many studies try to mitigate SAT-attack using different techniques/methods. Yet, the redteaming efforts in the hardware security community have continued to find the vulnerability in the proposed techniques. Some techniques are impractical due to their overheads, while others are vulnerable to evolving attacks in the community. This study aims to develop a full-scale solution that can prevent existing attacks while providing maximum security in case of zero-day attacks. Moreover, this work discusses the methods to verify functionality and security in case of obfuscated design.

The work discusses the background, basic terminology in the hardware security community, and the current problem in the following chapter.

## Chapter 3

## Background

### 3.1. Logic Locking

Logic Locking is a type of hardware obfuscation that aims to conceal the functionality of the design by inserting additional logic gates. These gates can be key-programmable (KPG) XOR/XNOR gates or KPG MUXes for interconnection. The ambiguity is created in the circuit due to the newly added gates. The programmable key for restoring the original functionality of the IP is stored in the tamper-proof memory. The strength of the logic obfuscation depends on the number of gates inserted, and the location of the gate insertion [13–15]. Logic obfuscation is weak when the inserted key gates are isolated, or their effect can be muted. If mutable gates are employed, the attacker can determine the key bits within a second. However, it can be strengthened by inserting key gates such that their effects are not mutable. One of the logic locking techniques, Strong Logic Locking, insert gates at the position where input cannot be easily sensitized to output. Figure 3.1 shows Strong Logic Locking.

Another obfuscation technique thwarts the RE attempt using camouflaging, which doesn't require extra KPG gates. This technique blocks the RE attempt by replacing existing gates in the design with camouflaged gates. In one embodiment of IC camouflaging, the layouts of logic gates are designed to look identical, resulting in an incorrect extraction. For example, in Figure 3.2 Standard Cell Versus Camouflaged Cell, the layout of regular NAND cell and NOR cell look different and are hence easy to RE. However, the layout of camouflaged NAND cell and NOR cell look identical and difficult to differentiate. When deceived into incorrectly interpreting the functionality of the

**Figure 3.1.** Strong Logic Locking [2]. The attacker can not sensitize either K1 or K2 to a primary output O1 or O2.

camouflaged gate, the attacker may obtain a reverse-engineered netlist that is different from the original.

Figure 3.2. Standard Cell Versus Camouflaged Cell [3] (a) NAND Cell (b) NOR Cell (c) Camouflaged NAND Cell (d) Camouflaged NOR Cell

After proposing various techniques for hardware security, attacks such as justification or sensitization [16] were developed to RE the design using heuristic techniques; however, with more advanced logic obfuscation, the community has shown success in extracting the keys using Automatic Test Generation Pattern (ATPG) and SAT-attack [11]. The novel SAT-attack is discussed in the following section.

#### 3.2. Overview of the SAT-Attack

Boolean Satisfiability Attack (SAT-attack) [11] is used for determining the correct key of the obfuscated or logic-locked circuit. The SAT-attack is an "oracle-guided attack" where the threat model assumes that an attacker has access to the activated IC and the locked netlist, which can be retrieved through invasive RE [17]. The SAT solver input is a Boolean formula in conjunctive normal

form (CNF) obtained from the transformation of the obfuscated netlist. The CNF representations of various logic gates are represented in Table 3.1.

**Table 3.1.** Tseytin Transformation of Basic Logic Gates [1]

| Gate                            | Operation                   | CNF (sub-expression)                                                                                                                                             |

|---------------------------------|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $\overline{C} = 	ext{AND}(A,B)$ | C = A.B                     | $(\overline{A} \vee \overline{B} \vee C) \wedge (A \vee \overline{C}) \wedge (B \vee \overline{C})$                                                              |

| $C = \operatorname{NAND}(A,B)$  | $C = \overline{A.B}$        | $(\overline{A} \vee \overline{B} \vee \overline{C}) \wedge (A \vee C) \wedge (B \vee C)$                                                                         |

| C = OR(A,B)                     | C = A + B                   | $(A \lor B \lor \overline{C}) \land (\overline{A} \lor C) \land (\overline{B} \lor C)$                                                                           |

| C = NOR(A,B)                    | $C = \overline{A + B}$      | $(A \lor B \lor C) \land (\overline{A} \lor \overline{C}) \land (\overline{B} \lor \overline{C})$                                                                |

| $C = \mathrm{BUFF}(A,\!B)$      | C = A                       | $(A \vee \overline{C}) \wedge (\overline{A} \vee C)$                                                                                                             |

| C = NOT(A,B)                    | $C = \overline{A}$          | $(\overline{A} \vee \overline{C}) \wedge (A \vee C)$                                                                                                             |

| C = XOR(A,B)                    | $C = A \oplus B$            | $(\overline{A} \vee \overline{B} \vee \overline{C}) \wedge (A \vee B \vee \overline{C}) \wedge (A \vee \overline{B} \vee C) \wedge (\overline{A} \vee B \vee C)$ |

| C = XNOR(A,B)                   | $C = \overline{A \oplus B}$ | $(\overline{A} \vee \overline{B} \vee C) \wedge (A \vee B \vee C) \wedge (A \vee \overline{B} \vee \overline{C}) \wedge (\overline{A} \vee B \vee \overline{C})$ |

| $C = \mathrm{MUX}(S,A,B)$       | $C = A.\overline{S} + B.S$  | $(S \vee \overline{A} \vee C) \wedge (S \vee A \vee \overline{C}) \wedge (\overline{S} \vee \overline{B} \vee C) \wedge (\overline{S} \vee B \vee \overline{C})$ |

SAT attack iteratively eliminates the incorrect keys based on specific input patterns, called Distinguishing Inputs (DIP) [11]. DIPs are found using a miter circuit, which was initially used to check the two hardware designs' equivalence. The miter circuit is built using two copies of the locked netlist obtained after invasive RE efforts, with their outputs XORed together. The input is common to both instances of the locked netlists, which are part of the miter circuit, but each locked netlist is programmed with a different key. The DIP is found when the output of the two circuits differs, making the XOR gate or miter circuit "1" output. These two different outputs indicate that one of the keys is wrong, and the input that helped us distinguish between the keys is termed distinguishing input. The DIP is applied to the oracle circuit to identify the correct output. The SAT-attack in every iteration tries to find a new DIP until no new DIP exists. This algorithm reduces the search space for finding the correct key with fewer queries (iteration) that need to be done with the oracle circuit. The following section discusses the process of SAT-attack in further details.

#### 3.3. Working of the SAT-Attack

Every key input combination is considered a candidate key before invoking the SAT solver to find the key. Let's denote the Set of Candidate Keys (SCK). If one can find an input  $x_d$ , and two distinct key values  $K_1$  and  $K_2$  in SCK such that  $C(x_d, K_1, Y_1) \neq C(x_d, K_2, Y_2)$ , the input  $x_d$  would be a DIP [11]. This is because the selected input can prune the SCK and find at least one incorrect key which can be removed from SCK. In addition, each time a new DIP is found, the SCK search space for function  $F_{DI}$  should be updated. This could be achieved by forcing the  $F_{DI}$  to check each pair of new keys,  $K_1$  and  $K_2$ , against all DIPs. A Complete- DIP-set is a set of DIP inputs that reduce the SCK to the Set of Valid Keys (SVK). SCK reduces to SVK when one no longer can find a DIP using the updated  $F_{DI}$ . At this point, if a key is valid across the complete-DIP-set, it is the correct key for all other inputs [11].

Figure 3.3. (a) Transforming an obfuscated circuit to (b) Key-Programmable Circuit and (c) Key Differentiating Circuit. (d) DIVC circuit for validating that two input keys produce the correct output with respect to a previously discovered DIP. (e) SCKVC circuit for validating that both input keys are in SCK set and produce the correct output for all previously discovered DIPs. (f) SAT circuit for finding a new DIP.

Figure 3.3 (b) shows a reverse-engineered netlist, where all obfuscated cells or camouflaged cells from Figure 3.3 (a) are replaced with KPG cells. KPC denotes this circuit). To build the  $F_{DIP}$ , two copies of the KPC are used, their non-key inputs (X) are tied together, and their outputs are XORed. This circuit produces logic 1 when the output of two instantiated KPCs for the same input X, but different keys  $K_1$  and  $K_2$  are different. As suggested in Figure 3.3 (c), this circuit is denoted as KDC or miter circuit.

The candidate keys in the SCK can produce the correct output for all DIPs that have previously been discovered and tested on the KPC circuit. To test the keys for one DIP, the circuit in Figure 3.3 (d) is instantiated. In this figure, FC is the working copy of the chip, and its output is used for testing the correctness of both KPCs for a given DIP and two key values. This circuit is denoted as Distinguishing Input Validation Circuit (DIVC). To test the keys for all DIPs, as illustrated in Figure 3.3 (e), the DIVC circuit is duplicated D times, with D being the number of current DIPs tested and the output of all DIVC circuits ANDed together. The resulting circuit is a validation circuit for SCK the set denoted as Validation Circuit for Set of Candidate Keys (SCKVC).

If two keys,  $K_1$  and  $K_2$ , produce the correct output for all previously tested DIPs (SCKVC evaluates to true) but produce different results for a new input  $X_{test}$ , then  $X_{test}$  is a DIP that

further prunes the SCK. This, as illustrated in Figure 3.3 (f), could be tested by using an AND gate at the output of SCKVC and KDC circuits. The resulting circuit forms a SAT solvable circuit denoted by SATC. When SATC evaluates to true, the KDC has tested a pair of keys,  $K_1$  and  $K_2$ , that produce two different results for an input  $X_{test}$ , and the SCKVC circuit has confirmed that both  $K_1$  and  $K_2$  belong to the SCK set. Hence, the input  $X_{test}$  is yet another DIP. Each time a new DIP is found, the SCKVC should be updated by adding another DIVC circuit to test the newly discovered DIP. This process is continued until SAT solver no longer finds a solution to the final SAT circuit. In this case, any key remaining in the SCK set is the correct key for the circuit. Every time the SAT solver is executed on the SAT solver side, it learns a new set of conflict clauses. It is essential to store the learned clauses and use them in the following invocation of the SAT solver to prevent SAT solver from re-learning these clauses. Hence, as illustrated in Figure 3.3 (f), a Learned-Clause Avoidance Circuit (LCAC) is added to the SATC to check for learned conflict clauses.

As illustrated in Algorithm 1, the SAT-attack follows the SATC construction process explained in Figure 3.3. The SCKVC circuit does not contain any logic in the first iteration since there is no previously tested DIP. Hence, it is set to 1 (true). The KDC circuit is built based on its definition using the equation in Figure 3.3.c. ANDing the KDC and SCKVC circuits builds the SATC circuit.  $SAT_F$  function is a call to SAT solver. Considering the to-be-assigned variables in the SATC circuit are X,  $K_1$ , and  $K_2$ , the SAT solvers return an assignment to these variables and a list of conflict clauses (CC) learned during SAT execution.  $SAT_F$  returns UNSAT if no such assignment exists. The while loop is controlled by the return status of the SAT solver. In every pass through the while loop, a new DIP is found. Hence, the SATC circuit should be modified (lines 7-10). The parts of the SATC circuit that are updated are the SCKVC and LCAC. After finding each DIP, an additional DIVC is added to SCKVC to validate the keys generated in the following invocation of SAT solver for the newly found DIP. In addition, the freshly learned CCs are added to LCAC. The  $C_F$  is a call to the functional circuit that returns the correct output for each newly found DIP. Finally, the SATC circuit is formulated at line 10 for the following invocation of SAT solver.

The while loop is executed until no other DIP is found. At this point, any key in the SCK set is the correct key. To obtain a correct key, the DIVC circuit is modified to take a single key denoted as KeyGenCircuit. Hence, KeyGenCircuit has input K, and its output is valid if K satisfies all previous

### Algorithm 1: SAT-based Attack Algorithm [11]

```

1 SAT_Attack (Circuit C_{obf}, Circuit C_{org});

Input: Obfuscated Circuit, Oracle Circuit

Output: Key to unlock the functionality of the obfuscated circuit

2 i \leftarrow 0;

3 F_1 \leftarrow C(X, K_1, Y_1) \wedge C(X, K_2, Y_2);

4 while SAT (F_i \wedge (Y_1 \neq Y_2)) do

5 X_d[i] \leftarrow \text{sat}_a \text{ssignment} (F_i \wedge (Y_1 \neq Y_2));

6 Y_d[i] \leftarrow \text{eval}(X_d[i]);

7 F_{i+1} \leftarrow F_i \wedge C(X_d[i], K_1, Y_d[i]) \wedge C(X_d[i], K_2, Y_d[i]);

8 i \leftarrow i+1;

9 end

10 Correct_Key \leftarrow \text{sat}_a \text{ssignment}(F_i \mid K_1);

```

constraints imposed by previously found DIPs. A simple call to a SAT solver at this point returns a correct key assignment. If the SAT solver does not produce a valid key, the obfuscation, locking, or camouflaging technique is invalid. Note that the SAT-attack in each iteration, as explained in Algorithm 1 and illustrated in Figure 3.4, reduces the SCK by constraining the SATC with new clauses added to the SCKVC and LCAC. But it does not explicitly check to find the keys in SCK.

**Figure 3.4.** SCK set reduces in each pass through the while loop in Algorithm 1 as a new DI is discovered and is added to SATC circuit.

The discussion above shows how the logic locking obfuscation can be broken using SAT-attack. However, an additional pre-processing step is required for the camouflaged gate, where the reverse-engineered netlist with camouflaged gates is replaced with a MUX. The input to the MUX is the choice of gates that a camouflaged gate can implement, and the select input to MUX is treated as a key input. For example, to represent a camouflaged gate from Figure 3.2, one can use 2:1 MUX, with the input of MUX being NAND gate and NOR gate, and the select line can choose between the correct functionality implemented by the camouflaged gate.

#### 3.4. Resisting SAT-Attack

Many works in the area of hardware security seek to increase the number of iterations required to retrieve the correct key for unlocking the circuit to thwart the SAT-attack. Stripped Functionality Logic Locking (SFLL) is the state-of-the-art method requiring exponential SAT iterations to find the correct key. However, the continued success of red-teaming efforts led by the hardware security community, work in [18], and [19] exploits the vulnerability in the SFLL method implementation and shows that the obfuscation key can be found within several minutes. Moreover, obfuscation similar to SFLL [20], such as SAR-Lock [21] and Anti-SAT [22], obfuscations fall into categories of one-point function, which evaluates to correct output upon applying a specific input pattern. The one-point obfuscation-based techniques require SAT-attack to apply many inputs to find the correct key. However, the output corruptibility offered by such techniques is very low, which means that the circuit works almost identical to the oracle circuit even when the wrong key is used [23].

In the quest to resist the SAT-attack, the community also formulated obfuscation techniques that resisted the obfuscated netlist's transformation to SAT problems. Delay-based locking or cyclic obfuscation are among a few of the examples that defy the SAT-attacks. However, shortly after introducing these obfuscation techniques, the attacks such as cycSAT and Satisfiability Module Theories (SMT) attacks were able to model the cyclic or behavioral locking into an SAT or SAT+theory solvable logic problems [24].

The solution to resist SAT-attack involves using reconfigurable blocks such as the LUT, where using large LUT sizes provides us with increased key size and number of functions that LUT can render. In LUT-based obfuscation, the combination of gates is replaced with LUT instead of adding key gates. The key in a LUT-based obfuscation is the memory element that configures/realizes the functionality of the LUT. The following section first illustrates the LUT-based obfuscation and its effect on security and design overheads.

## Chapter 4

## Lookup Table Obfuscation

This chapter expands upon the idea of LUT-based obfuscation and it is organized as follows: Section 4.1 describes the idea of leveraging LUT for securing IPs against SAT-attack. Section 4.2, Section 4.3 and Section 4.4 discusses the effect of various factors that can directly impact security and design overhead of an IP obfuscated using LUT-based obfuscation. As an outcome of the research covered in this chapter, this work has contributed to [4, 25, 26].

### 4.1. Lookup Table-based obfuscation

In obfuscation using LUT, the gates are selected from the design and are mapped to the LUTs. For example, to obfuscate a 2-input AND gate with LUT, one can replace the AND gate in the IP with the LUT whose configuration bits are set to  $\{0,0,0,1\}$  (Based on the truth table of AND gate). Obfuscation using LUT thus results in a netlist as a hybrid mixture of ASIC and programmable Field-Programmable Gate Array (FPGA) styles. In the LUT-based obfuscation, the keys that denote the logical function of the LUT can be stored in a tamper-proof (Secure) non-volatile memory. Without prior knowledge of the content of the non-volatile memory contents, the attacker doesn't have access to the IP's intended functionality and thus refrains the attacker from RE the IP. Figure 4.1 shows the LUT-based obfuscation, where part of the circuit is mapped to the LUT.

While storing the LUT configuration bits in tamperproof memory thwarts the attacker from understanding the content and functionality of the LUT, the attacker can still use SAT-attack to restore the content of the LUT. The attack on the LUT-based obfuscation using SAT-attack is

**Figure 4.1.** (a) Sample circuit used for obfuscation with gates  $G_4$ ,  $G_6$ ,  $G_7$ ,  $G_9$  selected for obfuscation (b) Obfuscation with LUT with representation of the LUT for SAT-attack simulation.

described here. The SAT-attack simulation does not offer the ability to model the LUT directly. Hence, LUT-based obfuscation is modeled using the MUXes, where each LUT is replaced with a (2+)-level MUX. Figure 4.1 (b) shows the representation of the LUT of size 2 for SAT simulation. The LUT of size 2 is built using 2:1 MUX. Since the attacker is interested in finding the LUT's configuration bits' content, which represents the functionality imparted by the LUT, the memory cells of the LUT are treated as the key inputs. The SAT-solver tries to find the value of these key inputs during the de-obfuscation process. After replacing all the LUT with their equivalent representation using MUXes, one can perform the SAT-attack.

Having shown the ways to attack LUT-based obfuscation using SAT-attack, one obvious way to hinder SAT-attack would be to use the larger sizes of the LUT in large quantities. However, it would also result in increased design overheads. Therefore, in LUT-based obfuscation, the question to address is (1) whether to use a few numbers of large LUTs or (2) use more numbers of small LUT sizes to defend against the SAT-attack. To answer this question, the work performs an extensive design-for-security space exploration for LUT-based obfuscation using four critical factors, namely (1) LUT technology, (2) LUT size, (3) number of LUTs, and (4) replacement strategy to find the impact of each on SAT-resiliency in the following section.

### 4.2. Impact of LUT Technology

This section discusses the design implementation of the MTJ-based LUT, followed by the impact of the SRAM and MTJ-based LUT on the design overheads.

#### 4.2.1 Design and Integration of Spin Transfer Torque-based Look-up Table

As Spin Transfer Torque-based Look-up Table (STT-LUT) has shown higher efficiency in terms of design overheads [12], this work considers STT-LUT in this work. STT technology can provide incredible features like (1) higher integration density than Static Random Access Memory (SRAM), (2) high endurance and retention time, (3) near-zero leakage, and (4) soft error resilience [4]. Additionally, STT-LUT has shown to be highly integrative in the Complementary Metal-Oxide Semiconductor (CMOS) fabrication process [12]. Thus, STT-LUT, due to its virtue of on-die reconfigurability, enables us to achieve high performance and security against various hardware RE threats.

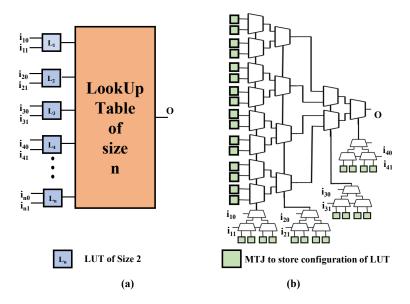

Additionally, for STT-LUT, reconfigurable bits can be stored in a Magnetic Tunnel Junction (MTJ) inserted between metal layers. MTJs are constructed of two ferromagnetic layers: a free layer and a fixed layer, and a thin oxide layer [6]. In the STT switching approach used in Spin Transfer Torque Magnetoresistive Random Access Memory (STT-MRAM), applying a bidirectional charge current through the terminals of the MTJ using a Metal-Oxide Semiconductor (MOS)-based circuit will result in the generation of a spin current. The spin current is used to change the magnetic polarity of the free layer to represent: 1) a high resistance or **Anti-Parallel** (AP) state and 2) a low resistance or parallel (P) state. The content stored in the MTJs is vulnerable to the de-layering process involved in the RE of the IP. The MTJ, in this manner, serves as the tamperproof memory to store the configuration of the LUT. The custom part of the design is implemented using the standard cell-based ASIC design flow. The resulting designs are static since the ASIC standard cells are implemented in the static logic style. This limits the LUT design to have a static type interface for connection with the static ASIC standard cells. Also, in the existing STT-LUT design styles, a dynamic circuit such as a dynamic sense amplifier resides in between the LUT's input and the output. However, this type of setting is not suitable for the obfuscation in static style [27]. In contrast, this work proposes STT-LUT with a design concept in which the path from the LUT inputs to the LUT output is a MUX, as shown in Figure 4.3 (a). The MUX of the LUT is a  $2^n$ to 1  $(2^n:1)$  CMOS MUX implemented in static style, which can be written as a synthesizable Register-Transfer Level (RTL) code for automatic implementation and optimization by the logic synthesizer tool in the process of design compilation.

Figure 4.2. MTJ latch with Scan Chain Programming.

Each configuration bit is stored by a MTJ latch with scan chain programmability, as shown in Figure 4.2. The MTJ latch uses a pair of differentially programmed MTJs for non-volatile storage, a pre-charge sense amplifier for sensing the state of the MTJs, and three write driver schemes for parallel writing both MTJs simultaneously with each MTJ receiving full voltage swing, offering more write current. The Sense Enable (SE) signal must be low during the write operation, and the Write Enable (WE) signal must be low during the sensing operation. To avoid conflict of state between the pre-charge state of the sense amplifier (when SE=0) and the state of the write driver outputs in the write mode, the pre-charge path to  $V_{DD}$  is disconnected via the PMOS driven by the WE signal. The MTJ latch uses a dynamic latched sense amplifier that needs to be fired (SE) low to high pulse) once on every power-up to convert the resistive state of the MTJs into the volatile voltage states at the outputs (Q and QB). In this configuration, the MTJs are read-only once, and for the remaining time in the active mode, the LUT read power and delay are determined by the static MUX. Moreover, by not reading from the MTJs repetitively in the active mode as in the dynamic STT-LUT styles, the stress is removed from the MTJs, enhancing their lifetime. Another critical thing to note here is that the scan chain used to program the LUT is separate from the one used in the design for testing and thus does not require critical MUX to switch from functional mode to test mode.

The MTJ latch is designed in a full-custom manner and needs to be optimized for sensing

Figure 4.3. (a) Proposed STT-LUT with Scan Chain Programming (b) Full custom layout of MTJ latch in standard cell format and area breakdown between different blocks

reliability and area. The custom-designed MTJ latch is delivered as a standard cell for integration into the ASIC design flow. The full-custom design and optimization of the one-bit MTJ latch cell are performed in the Synopsys generic 28nm process [28]. The write drivers tend to require large transistors to produce sufficient current needed for MTJ write. The write transistors need to be optimized so that the write operation can succeed under Process Variation (PV). This experiment performed statistical transistor sizing optimization on the write driver for achieving a near-zero (less than 0.1%) write failure rate under process variation. After the write driver sizing optimization, the read path (i.e., the sense amplifier) transistor sizes are statistically optimized for achieving less than 0.1% sensing failure rate at the smallest possible area. Moreover, a minimum-sized scan flip-flop is inserted in front of the MTJ latch to store the data written to the MTJ latch. These scan flip-flops will form a scan chain for loading the configuration bits to the MTJ latches in a design. Figure 4.3 (b) shows the full-custom layout of the one-bit MTJ latch designed in a standard cell layout format (fixed height). The write drivers occupy most of the layout area (37.5%) since the MTJ write current is still significant. Notice that the MTJ devices are stacked on top of this layout between two metal layers (assuming M3 and M4) and do not occupy the 2D area. M3 pins are placed for connection to the MTJ layers.

### 4.2.2 STT-Based LUT versus CMOS-based LUT

Figure 4.4 shows the comparison of the area of the MTJ latch and STT-LUTs, along with the areas of other standard cells in 28nm. The MTJ latch area is  $6 \times$  to  $15 \times$  that of basic logic gates and  $3 \times$  larger than rhe SRAM-based D flip-flop. The MTJ latch, however, shows much less leakage

power. It has  $7 \times$  to  $11 \times$  less leakage power than basic CMOS logic gates and is  $20 \times$  smaller than SRAM-based D-FF.

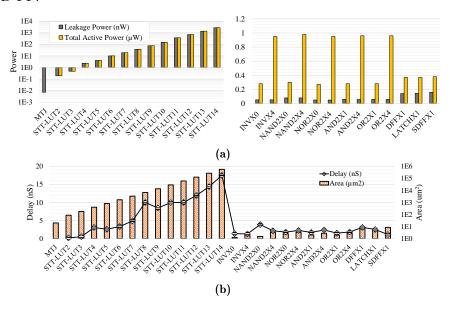

Figure 4.4. Comparison of (a) Power, (b) Delay, and Area of STT-LUT and Standard Cells in 28nm

The delay and active mode power of the STT-LUT are determined by the multiplexer part of the LUT, which is optimizable by the logic synthesizer. Figure 4.4 compares delay and active mode power for various fan-in STT-LUTs with standard cells. LUT<sub>2</sub> to LUT<sub>7</sub> have delays comparable to the standard cell delays. Due to the large MTJ latch area, LUTs are noticeably larger than the standard cells, and their area increases exponentially with fan-in. The power of STT-LUTs is significantly less than the standard cells due to low leakage MTJ latches. Therefore, relying on STT-LUT will render a lower overhead footprint.

#### 4.3. Effect of Replacement Strategies

The location of the gate(s) selected for the obfuscation is one of the critical factors that define the strength of the obfuscation [11]. The replacement strategy finds the gate for obfuscation based on heuristics. LUT-based obfuscation needs to select the gates for replacement; however, an effective replacement strategy needs to meet several conditions to provide resiliency against the SAT-attacks. The two most essential requirements are (1) low corruptibility and (2) avoiding unintentionally correct key generation. By considering these conditions, this section introduces a replacement strategy and compares it with the random placement strategy [13]. To better evaluate the impact

of each condition, three different strategies are compared in this work as follows.

### 4.3.1 Random Selection (RND)

In the random selection algorithm, the gates are selected for obfuscation randomly. This method works as a baseline for comparison as opposed to the *independent selection* in [12].

#### 4.3.2 Low Output Corruptibility (LC)

The state-of-the-art SAT-solvers use the Conflict Driven Clause Learning (CDCL) algorithm to find the solution. The CDCL works by searching for the conflicting clauses to learn clauses effectively and comparing the two outputs of the same netlist upon applying the input pattern with different keys helps find the conflicting clause. If the Hamming Distance (HD) between the two obtained outputs is high, finding the conflicting clause and distinguishing input is easy. An obfuscation strategy that influences more than one primary output (PO) of a circuit on the application of a wrong key input will result in a higher hamming distance, and the probability of hamming distance > 1 will be significant; (more than one primary output differs from the Oracle). This phenomenon is also known as the property of the obfuscation strategy to have high *output corruptibility*. High corruptibility leads to higher hamming distances, which provides the SAT-solver with an opportunity to find the conflict clauses much faster, resulting in lower de-obfuscation time. Due to this phenomenon, the maximum of one output must be different when a wrong key is applied to increase SAT execution time. This is called having low output corruptibility; if fewer (the best is 1) outputs are different after applying different keys and input. This phenomenon can also be thought of as reducing the observability in the presence of obfuscation, such that the effect of the wrong key can only be observed at fewer primary outputs. Due to this, sensitizing the key input to the primary output becomes intricate.

For the IP to exhibit the low output corruptibility, Breadth-first-search is employed on the circuit graph, where gates are treated as a node and edges are the connection between the logical gates. While traversing from Logical Cone Output (LCO) toward the inputs, a dictionary with all the gates and their corruptibility will be created, which allows us to pick the combination of the gates with the lowest output corruptibility. After traversing, based on the number of gates targeted for obfuscation, multi-objective optimization is performed to maximize the number of gates selected

for obfuscation while minimizing the output corruptibility.

### 4.3.3 Avoiding Unintentionally Correct Key Generation (LC NoGen)

As the LUT is a reconfigurable unit, it can implement  $2^{2^n}$  possibilities where n is the size of the LUT. Obfuscating two gates back to back with LUTs can generate additional correct keys. When the number of correct keys is increased, the SAT solver's search space to find the working key reduces the de-obfuscation time. Consider an example where two "NOT" gates are replaced with LUTs. In this scenario, if the LUTs are configured as buffers instead of "NOT," the circuit will still be equivalent to the oracle, and thus there exist 2 correct keys instead of 1. This means the probability of finding a key is doubled instantaneously. Therefore, obfuscating the gates with LUTs directly connected in a back-to-back fashion significantly decreases the SAT solver's search space. Due to the virtue of the reconfigurability in the LUTs, the number of correct keys must be reduced, and thus extra care should be taken to avoid this condition.

Considering the above case of avoiding the obfuscation of two directly connected gates, this work proposes a  $LC\_NoGen$  replacement strategy. The pseudocode for the  $LC\_NoGen$  replacement strategy is illustrated in Algorithm 2.

The algorithm involves traversing the graph followed by dictionary creation. The dictionary is filtered to eliminate the back-to-back gates and gates that contribute to the critical path. Further, an optimizer maximizes the gate coverage while reducing output corruption. The complexity of traversing the graph with V vertices and E edges is given as  $\mathcal{O}(V+E)$ . With fewer modifications, the dictionary creation and filtering can be done while traversing the graph, and thus, the overall complexity for traversing the graph and dictionary creation is given as  $\mathcal{O}(V+E)$ . The optimization problem, on the other hand, is a combinatorial optimization problem. While finding the optimal set of gates for obfuscation is an NP-hard problem. Thus off-the-shelf Integer Linear Programming (ILP) solvers are leveraged to get the sub-optimal solution using an approximation algorithm. The problem of gate selection with minimum output corruptibility is treated as a variant of a classical problem of minimum vertex cover. The task is to choose a minimum number of nodes that maximize the cover. The gates selected by the optimizer are replaced with the LUT, and the work illustrates that by considering the  $LC_NoGen$ , the Security per PPA overhead footprint is improved. The proposed algorithm can also be scaled to other obfuscation techniques for inserting the obfuscation

```

Algorithm 2: Avoiding Unintentionally Correct Key Generation (LC_NoGen)

```

```

1 LC NoGen (Circuit C_{org});

Input: Original Circuit

Output: Obfuscated Circuit

2 foreach LCO in Logic cones do

// LCO: Logic Cone Output

gate\ list = BFS(LCO);

// Get all gates in the logic cone;

foreach gate in gate list do

// Find all the Output gates of Logic Cone, which are affected by each

gate.;

gate.listLCOs = find affected LCOs(gate);

\mathbf{5}

end

6

7 end

8 foreach (gate in circuit) do

foreach (LCO in gate.listLCOs) do

tag key(LCO);

10

if isExist(tag \ key(LCO)) then

11

dictionary.add(qate);

12

13

end

else

14

dictionary.add(gate);

15

dictionary.addtag((tag key(LCO));

16

17

end

end

18

19 end

20 CriticalPath = PrimeTime(Get Critical Path);

// Get List of gates that are on Critical Path using Synopsys PrimeTime.

Afterwards also remove gates that are adjacent to each other to avoid

back-to-back LUT replacement. Remove gates on critical path list;

21 foreach (tag in dictionary) do

foreach (gate in tag) do

22

if isExist(Parent(qate) in taq)

23

or isExist(gate in CriticalPath) then

24

dictionary/tag/.delete(gate);

25

end

26

end

27

28 end

// find tag_key which have maximum gate coverage with lowest Output

Corruption;

29 tag key = Optimize ();

30 foreach (gate in tag key) do

Replace LUT(gates, target no);

// Replace gates with LUT;

32 end

```

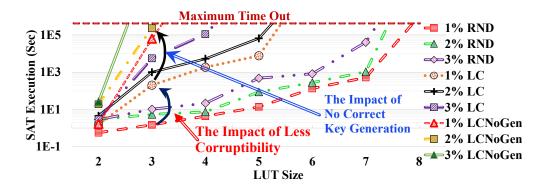

**Figure 4.5.** De-obfuscation time using SAT-attack for Different (1) Replacement Strategy, (2) LUT Size (scale up), and (3) Number of LUTs (scale out) in ISCAS-85 c7552 [4]

as this algorithm finds the optimal place for inserting a gate that minimizes the output corruptibility.

After developing replacement strategies tailored for LUT-based obfuscation, they are evaluated against the SAT-attack. Benchmark C7552 from ISCAS-85 is obfuscated with the different discussed obfuscation strategies for the experiment. Figure 4.5 illustrates the performance of the discussed obfuscation strategies against the SAT-attack. With the improved obfuscation strategies, the de-obfuscation time of the SAT solver is increased, and in most cases, obfuscation using the  $LC_{-}NoGen$ , strategy outweighs the Random and LC obfuscation, which shows that high security can be obtained with a lower number of gates obfuscated. The lower number of gates used for obfuscation results in lower PPA overhead. However, while providing higher security at the cost of lower PPA overheads, these obfuscation schemes tend to have low output corruptibility.

While on the other hand, it can be observed that for the LUT with size 8 and above, obfuscating  $\sim 1\%$  of overall gates with any obfuscation strategy also renders the timeout states for the SAT solver. Moreover, one can get the security against the SAT-attack and the increased output corruptibility for a random obfuscation scheme using a large LUT size. Therefore, by scaling up the size of the LUT for obfuscation, the LUT-based obfuscation can break the trade-off of SAT-resiliency with output corruptibility. Increasing the size of the LUTs increases the resiliency of the IP regardless of the replacement strategy.

The experiment also shows that using a larger LUT size overweighs the benefits of using a better gate replacement policy at the expense of increased design overheads. Another observation from the experiment is that a change in the obfuscation coverage from 1% to 3% (i.e., changing the number of LUTs inserted in the circuit) also increases the runtime of the SAT-solver. Thus, in the

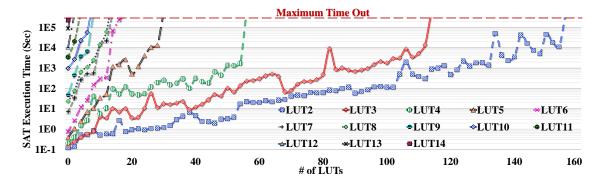

**Figure 4.6.** De-obfuscation time of C7552 benchmark with different number of LUTs and different sizes of LUT using SAT-attack [4].

next section, the effect of the size of LUT vs. the number of gates obfuscated (obfuscation coverage) on the circuit resiliency is discussed in more detail.

#### 4.4. LUT Size versus Number of LUTs

To get the best security results using LUT-based obfuscation, it is wise to leverage the large size of the LUT because increasing the LUT's size can thwart the SAT-attack and increase the output corruptibility. This advantage of using larger LUT sizes is that LUTs are modeled using the  $\log_2(n)$ -level MUX-based structure, and with the increasing size of LUT, the SAT-attack will replace them with the deep MUX trees. The SAT-attack leverages the CDCL algorithm to find the distinguish input. However, when the symmetrical structure of the MUX tree is used for the obfuscation, there is no shortleaf in finding the conflict clause while running the SAT-attack. The increasing size of LUT grows the MUX tree deep, and consequently, the search space and the efforts for finding the conflicting clause are increased, making the resulting instance an SAT-hard. The following example shows how the de-obfuscation time rises exponentially, with larger LUTs to find the keys' value.

For larger LUT sizes, combinations of gates are replaced using large LUT. Figure 4.1 (a) shows an example of the large-sized LUTs used for the obfuscation. The 2-input gates (G<sub>4</sub>, G<sub>6</sub>, G<sub>7</sub>, G<sub>9</sub>) are replaced using LUT of size 4. The LUTs are represented using MUX-tree as shows in Figure 4.1 (b) for SAT-attack simulation. To evaluate the effect of LUT size vs. the number of LUTs, multiple gates with varying LUT sizes and various gates with a varying count of LUT are used.

Figure 4.6 shows SAT execution time with more details on the ISCAS-85 C7552 benchmark for different sizes of LUTs used for obfuscation. This experiment shows a similar trend of leveraging