# $\begin{array}{c} {\rm UNIVERSITY\ OF\ CALIFORNIA,} \\ {\rm IRVINE} \end{array}$

# Root-of-Trust Architectures for Low-end Embedded Systems ${\bf DISSERTATION}$

submitted in partial satisfaction of the requirements for the degree of

### DOCTOR OF PHILOSOPHY

in Computer Science

by

Sashidhar Jakkamsetti

Dissertation Committee: Professor Gene Tsudik, Chair Professor Alfred Chen Professor Ardalan Amiri Sani

# **DEDICATION**

To my beloved family – my parents, Padmasree and Someswara Rao, my wife, Apoorva, and my brother, Venkatesh.

# TABLE OF CONTENTS

| LIST OF FIGURES LIST OF TABLES ACKNOWLEDGMENTS                                   | viii ix x xiii xv |

|----------------------------------------------------------------------------------|-------------------|

|                                                                                  | x<br>xii<br>xv    |

| ACKNOWLEDGMENTS                                                                  | xii<br>xv         |

|                                                                                  | xv                |

| VITA                                                                             |                   |

| ABSTRACT OF THE DISSERTATION                                                     | 1                 |

| 1 Introduction                                                                   | 1                 |

| 1.1 Contributions                                                                | 5                 |

| 1.2 Scope and Limitations                                                        | 6                 |

| 1.3 Dissertation Structure                                                       | 7                 |

| 2 Background                                                                     | 8                 |

| 2.1 Targeted Devices                                                             | 10                |

| 2.2 Remote Attestation ( $\mathcal{R}A$ )                                        | 12                |

| 2.2.1 <i>VRASED</i>                                                              | 13                |

| 2.3 Proofs of Execution $(PoX)$                                                  | 15                |

| $2.3.1  APEX  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $   | 15                |

| 3 Tiny-CFA: A Minimalistic Control-Flow Attestation Using Verified Proof         | s                 |

| of Execution                                                                     | <b>17</b>         |

| 3.1 Introduction                                                                 | 19                |

| 3.1.1 Contributions                                                              | 20                |

| 3.2 Background                                                                   | 21                |

| $3.2.1$ Control-Flow Attestation ( $\mathcal{C}FA$ )                             | 21                |

| $3.3  Tiny-CFA  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $ | 22                |

| 3.3.1 Design Rationale & Security                                                | 23                |

| 3.3.2 Optimizations                                                              | 27                |

| 3.3.3 Implementing Tiny-CFA                                                      | 29                |

| 3.4 Case Study & Evaluation                                                      | 31<br>31          |

| 3.4.1 Case Study: Control-Flow Attacks in Low-End MCO-s                          |                   |

|   | 3.5        | Conclusions                                                        |

|---|------------|--------------------------------------------------------------------|

| 4 | DIA        | LED: Data Integrity Attestation for Low-end Embedded Devices 38    |

|   | 4.1        | Introduction                                                       |

|   |            | 4.1.1 Contributions                                                |

|   | 4.2        | Background                                                         |

|   |            | 4.2.1 Control-Flow vs. Data-Only Attacks                           |

|   | 4.3        | DIALED Design                                                      |

|   |            | 4.3.1 Overview                                                     |

|   |            | 4.3.2 Adversary Model                                              |

|   |            | 4.3.3 Design Rationale                                             |

|   |            | 4.3.4 Security Analysis                                            |

|   | 4.4        | DIALED Implementation                                              |

|   | 4.5        | Evaluation                                                         |

|   |            | 4.5.1 Hardware Overhead                                            |

|   |            | 4.5.2 Experimental Analysis on Real-world Applications             |

|   | 4.6        | Conclusions                                                        |

|   | 1.0        | Conclusions                                                        |

| 5 | Priv       | acy-from-Birth: Protecting Sensed Data from Malicious Sensors with |

|   | VEI        | SSA                                                                |

|   | 5.1        | Introduction                                                       |

|   |            | 5.1.1 Contributions                                                |

|   | 5.2        | Preliminaries                                                      |

|   |            | 5.2.1 <b>GPIO</b> & MCU Sensing                                    |

|   |            | 5.2.2 LTL, Model Checking, & Verification                          |

|   | 5.3        | VERSA Overview                                                     |

|   | 5.4        | MCU Machine Model                                                  |

|   |            | 5.4.1 Execution Model                                              |

|   |            | 5.4.2 Hardware Signals                                             |

|   | 5.5        | <i>PfB</i> Definitions                                             |

|   |            | 5.5.1 <i>PfB</i> Syntax                                            |

|   |            | 5.5.2 Assumptions & Adversarial Model                              |

|   |            | 5.5.3 PfB Game-based Definition                                    |

|   | 5.6        | VERSA: Realizing $PfB$                                             |

|   | 0.0        | 5.6.1 VERSA: Construction                                          |

|   |            | 5.6.2 Encryption & Integrity of $ER$ Output                        |

|   | 5.7        | Verified Implementation & Security Analysis                        |

|   | 0.1        | 5.7.1 Sub-module Implementation & Verification                     |

|   |            | 5.7.2 Sub-module Composition and VERSA End-To-End Security 80      |

|   | 5.8        | VERSA Composition Proof                                            |

|   | 5.8<br>5.9 | <u>.</u>                                                           |

|   | 5.9        |                                                                    |

|   |            | 5.9.1 Toolchain & Prototype Details                                |

|   |            | 5.9.2 Hardware Overhead                                            |

|   |            | 5.9.3 Verification Costs                                           |

|   |            | 5.9.4 Runtime Overhead                                             |

|   |                                                                   | 5.9.5 Comparison with Other Low-End Architectures: |  |  |  |  |  |

|---|-------------------------------------------------------------------|----------------------------------------------------|--|--|--|--|--|

|   | 5.10                                                              | Discussion                                         |  |  |  |  |  |

|   |                                                                   | 5.10.1 Clean-up after Program Termination          |  |  |  |  |  |

|   |                                                                   | 5.10.2 Data Erasure on Reset/Boot                  |  |  |  |  |  |

|   | 5.11                                                              | Limitations:                                       |  |  |  |  |  |

|   |                                                                   | 5.11.1 Shared Libraries                            |  |  |  |  |  |

|   |                                                                   | 5.11.2 Atomic Execution & Interrupts               |  |  |  |  |  |

|   |                                                                   | 5.11.3 Possible Side-channel Attacks               |  |  |  |  |  |

|   |                                                                   | 5.11.4 Flash Wear-Out                              |  |  |  |  |  |

|   |                                                                   | 5.11.5 VERSA Alternative Use-Case                  |  |  |  |  |  |

|   | 5.12                                                              | Conclusions                                        |  |  |  |  |  |

| 6 | CASU: Compromise Avoidance via Secure Update for Low-end Embedded |                                                    |  |  |  |  |  |

|   | Syst                                                              | tems 104                                           |  |  |  |  |  |

|   | 6.1                                                               | Introduction                                       |  |  |  |  |  |

|   |                                                                   | 6.1.1 Contributions                                |  |  |  |  |  |

|   | 6.2                                                               | Background                                         |  |  |  |  |  |

|   |                                                                   | 6.2.1 TOCTOU Attacks & <i>RATA</i>                 |  |  |  |  |  |

|   | 6.3                                                               | CASU Scheme & Assumptions                          |  |  |  |  |  |

|   |                                                                   | 6.3.1 Basics                                       |  |  |  |  |  |

|   |                                                                   | 6.3.2 Secure Update Overview                       |  |  |  |  |  |

|   |                                                                   | 6.3.3 Adversary Model                              |  |  |  |  |  |

|   | 6.4                                                               | <i>CASU</i> Design                                 |  |  |  |  |  |

|   |                                                                   | 6.4.1 <i>CASU-HW</i> : Hardware Security Monitor   |  |  |  |  |  |

|   |                                                                   | 6.4.2 <i>CASU</i> Secure Update                    |  |  |  |  |  |

|   |                                                                   | 6.4.3 (Optional) $CASU$ Secure Boot                |  |  |  |  |  |

|   | 6.5                                                               | Implementation                                     |  |  |  |  |  |

|   |                                                                   | 6.5.1 CASU-HW Verified Hardware Module             |  |  |  |  |  |

|   |                                                                   | 6.5.2 CASU-SW Secure Update Routine                |  |  |  |  |  |

|   | 6.6                                                               | Evaluation                                         |  |  |  |  |  |

|   |                                                                   | 6.6.1 Hardware Overhead                            |  |  |  |  |  |

|   |                                                                   | 6.6.2 Runtime for Secure Updates                   |  |  |  |  |  |

|   | 6.7                                                               | Conclusions                                        |  |  |  |  |  |

| 7 | Rela                                                              | ated Work                                          |  |  |  |  |  |

|   | 7.1                                                               | Prior Work on $\mathcal{R}A$ and $PoX$             |  |  |  |  |  |

|   |                                                                   | 7.1.1 Software-based $RA$                          |  |  |  |  |  |

|   |                                                                   | 7.1.2 Hardware-based $\mathcal{R}A$                |  |  |  |  |  |

|   |                                                                   | 7.1.3 Hybrid $\mathcal{R}A$                        |  |  |  |  |  |

|   |                                                                   | 7.1.4 Temporal Aspects of $\mathcal{R}A$           |  |  |  |  |  |

|   |                                                                   | 7.1.5 <i>PoX</i> Related Work                      |  |  |  |  |  |

|   | 7.2                                                               | Mitigation of Control-flow Attacks                 |  |  |  |  |  |

|   |                                                                   | 7.2.1 Control-Flow Integrity (CFI)                 |  |  |  |  |  |

|   |                                                                   | 7.2.2 Control-Flow Attestation ( $\mathcal{C}FA$ ) |  |  |  |  |  |

|   | 7.3                                                               | Mitigation of Data-only Attacks                    |  |  |  |  |  |

| $\mathbf{B}^{\mathbf{i}}$ | Bibliography |                                                 |                   |  |  |

|---------------------------|--------------|-------------------------------------------------|-------------------|--|--|

|                           |              | Future Work                                     | <b>141</b><br>142 |  |  |

|                           | 7.6          | Remote Updates                                  | 140               |  |  |

|                           | 7.5          | Formally Verified Systems                       | 139               |  |  |

|                           | 7.4          | Other Active RoTs                               | 138               |  |  |

|                           |              | 7.3.2 Data-Flow Attestation ( $\mathcal{D}FA$ ) | 138               |  |  |

|                           |              | 7.3.1 Data-Flow Integrity (DFI)                 | 137               |  |  |

# LIST OF FIGURES

|            |                                                                                 | Page     |

|------------|---------------------------------------------------------------------------------|----------|

| 2.1<br>2.2 | System Architecture of an MCU-based IoT Device                                  | 11<br>13 |

| 3.1<br>3.2 | OR region used to store regular program outputs and CF-Log                      | 23<br>29 |

| 3.3        | Instrumentation example: indirect write instructions                            | 30       |

| 3.4        | Instrumentation example: $\mathcal{R}$ initialization check                     | 30       |

| 3.5        | Instrumentation example: conditional branches                                   | 30       |

| 3.6<br>3.7 | Safety critical application exploitable by control-flow attacks                 |          |

| 3.8        | lines represent the total hardware cost of MSP430 core itself                   | 34       |

|            | represent the total hardware cost of MSP430 core itself                         | 35       |

| 4.1        | Embedded application vulnerable to a data-flow attack                           | 42       |

| 4.2        | DIALED Architectural Components                                                 | 45       |

| 4.3        | Instrumentation example: Logging $\mathcal{P}$ 's arguments                     | 50       |

| 4.4        | Instrumentation example: Logging runtime data inputs                            | 51       |

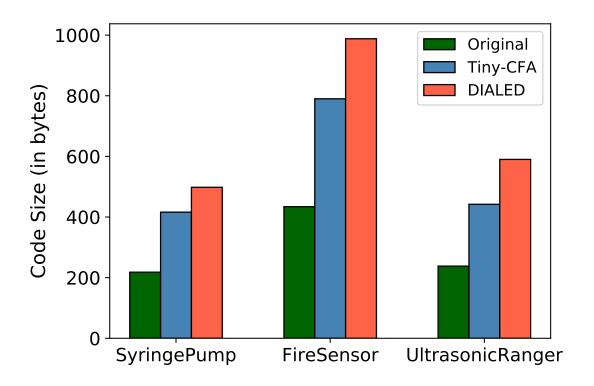

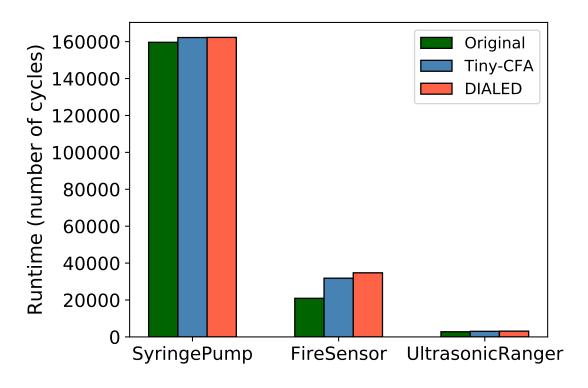

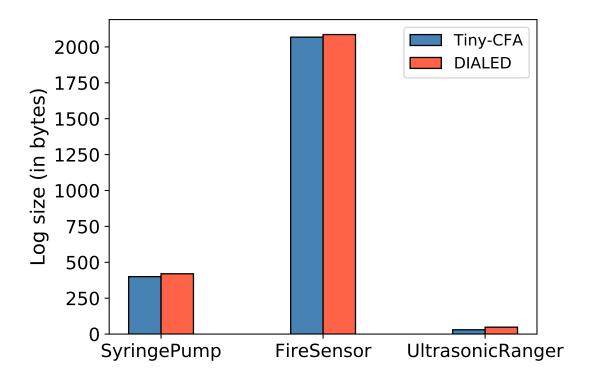

| 4.5        | Total code size comparison                                                      | 54       |

| 4.6        | Runtime comparison                                                              | 54       |

| 4.7        | Log size comparison                                                             | 55       |

| 5.1        | LTL Quantifiers                                                                 | 63       |

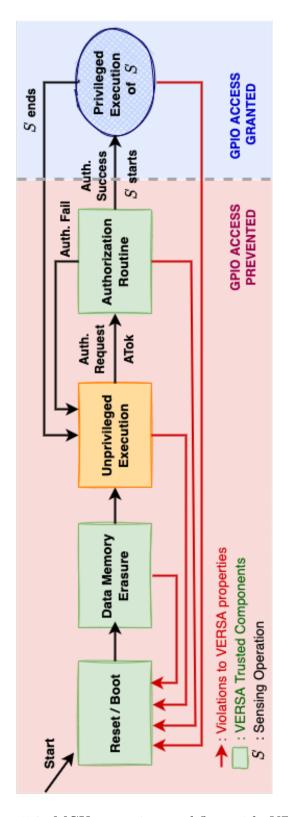

| 5.2        | MCU execution workflow with VERSA                                               | 67       |

| 5.3        | MCU Execution Model                                                             | 69       |

| 5.4        | MCU Hardware Model                                                              | 70       |

| 5.5        | Syntax of the PfB Scheme                                                        | 72       |

| 5.6        | PfB Security Game                                                               | 73       |

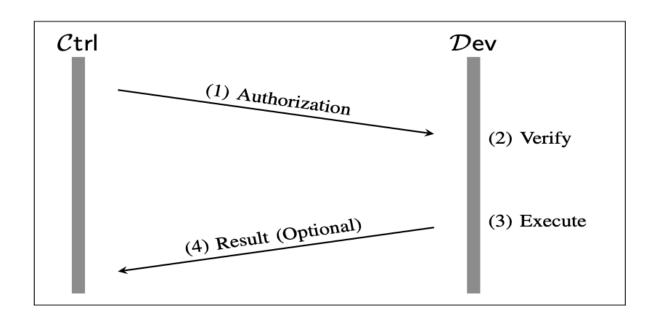

| 5.7        | PfB interaction between $Ctrl$ and $Dev$                                        | 75       |

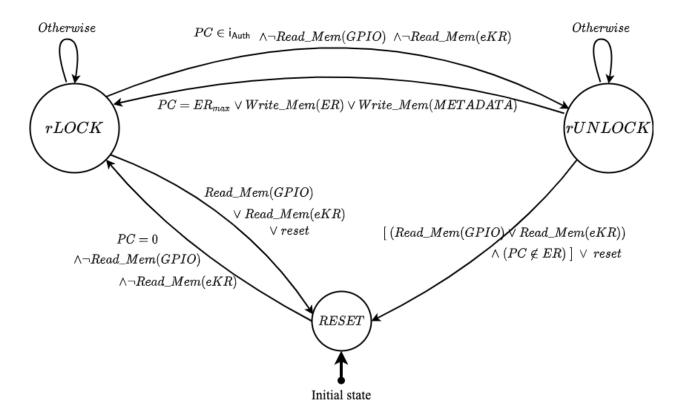

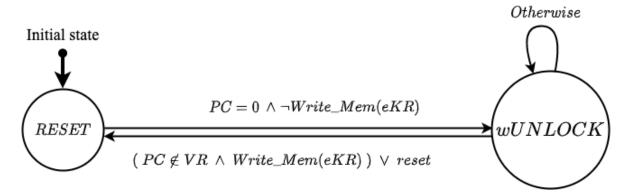

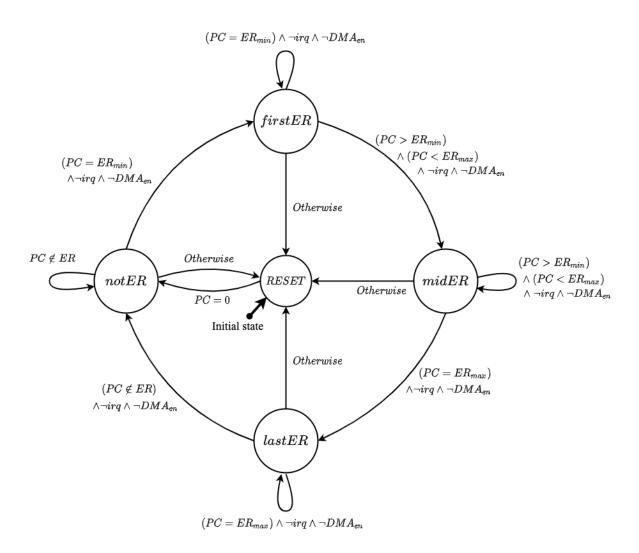

| 5.8        | VERSA Architecture                                                              | 77       |

| 5.9        | Verified Remote Sensing Authorization (VERSA) Scheme                            | 80       |

| 5.10       | VERSA HardwareMonitor Specifications                                            | 81       |

| 5.11       | Verified FSM for <b>GPI0</b> and $eKR$ Read-Access Control (LTL (5.10)-(5.14) & |          |

|            | LTL (5.18)-(5.19))                                                              | 86       |

| 5.12       | Verified FSM for $eKR$ Write-Access Control (LTL $(5.20)$ )                     | 86       |

| 5.13 | ER Atomicity and Controlled Invocation FSM (LTL $(5.15)$ - $(5.17)$ )        | 87  |

|------|------------------------------------------------------------------------------|-----|

| 5.14 | VERSA End-To-End Security Properties in LTL                                  | 88  |

| 5.15 | VERSA Theorems for proving end-to-end security                               | 89  |

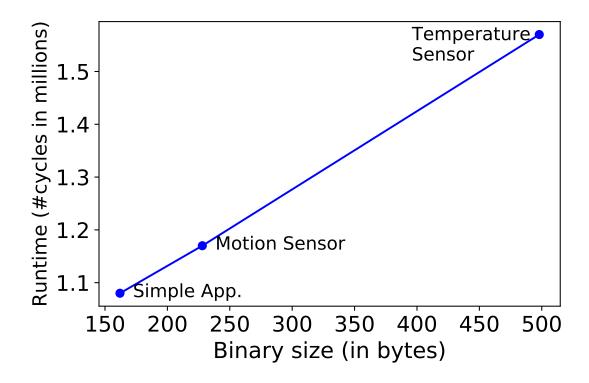

| 5.16 | Runtime overhead of VERSA due to Verify                                      | 95  |

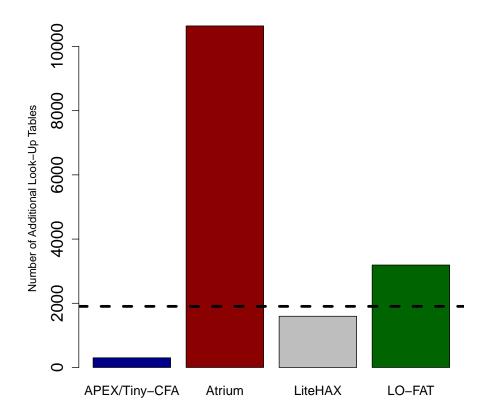

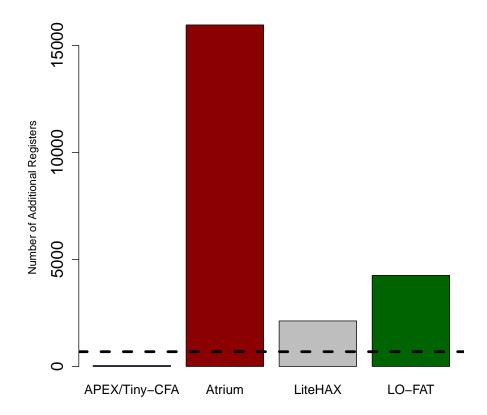

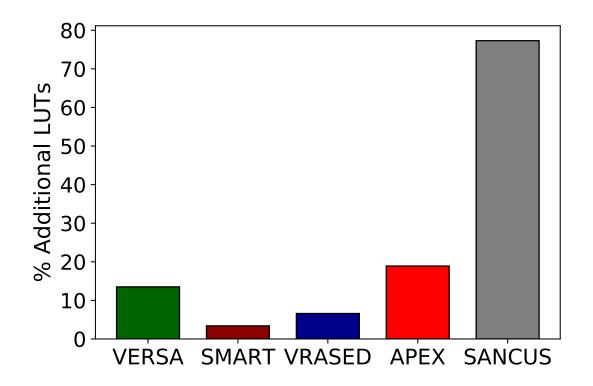

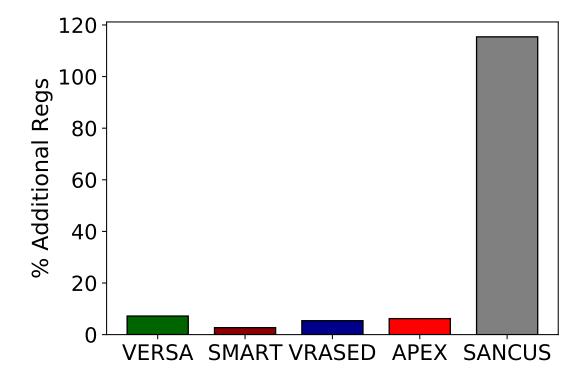

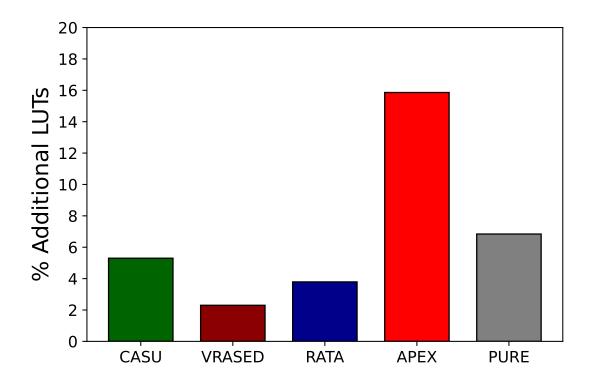

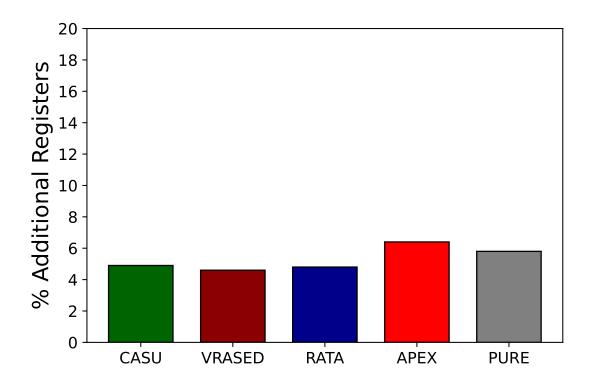

| 5.17 | VERSA Additional HW overhead (%) in Number of Look-Up Tables                 | 97  |

| 5.18 | VERSA Additional HW overhead (%) in Number of Registers                      | 97  |

| 5.19 | Sample sensing operation that reads GPIO input, encrypts it, and cleans up   |     |

|      | its stack after execution                                                    | 99  |

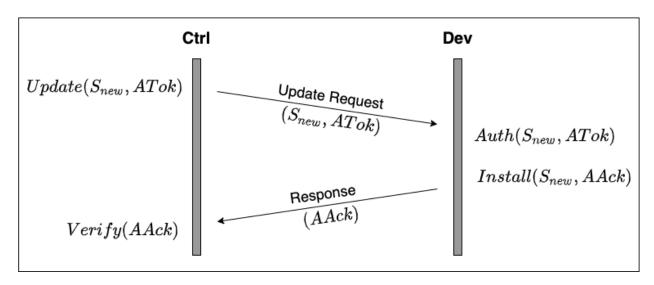

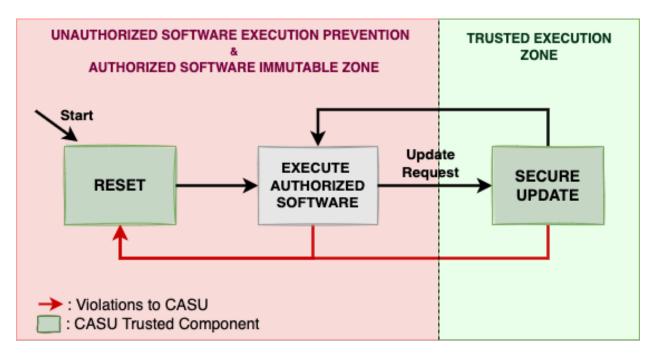

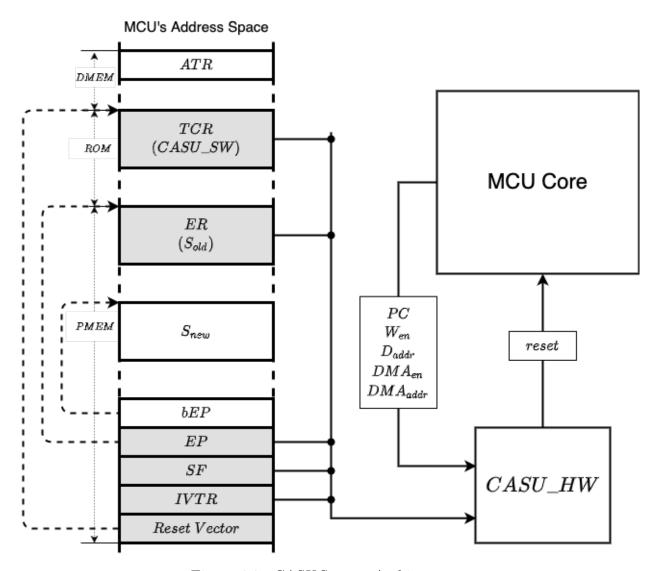

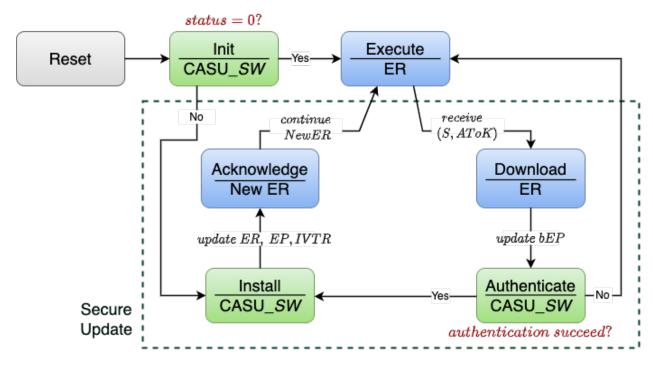

| 6.1  | CASU Secure Update Protocol                                                  | 110 |

| 6.2  | CASU Software Execution Flow                                                 | 113 |

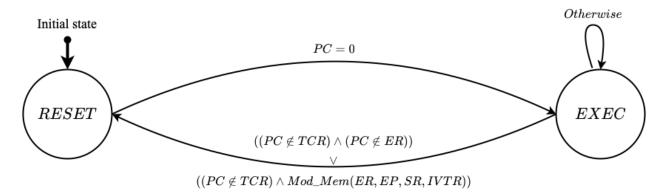

| 6.3  | CASU System Architecture                                                     | 114 |

| 6.4  | CASU-HW Security Properties                                                  | 117 |

| 6.5  | CASU Secure Update                                                           | 119 |

| 6.6  | Secure Update Workflow: blue and green boxes indicate authorized and trusted |     |

|      | execution routines, respectively                                             | 123 |

| 6.7  | FSM of CASU-HW Verified Hardware Module                                      | 125 |

| 6.8  | CASU Additional HW overhead (%) in Number of Look-Up Tables                  | 128 |

| 6.9  | CASU Additional HW overhead (%) in Number of Registers                       | 129 |

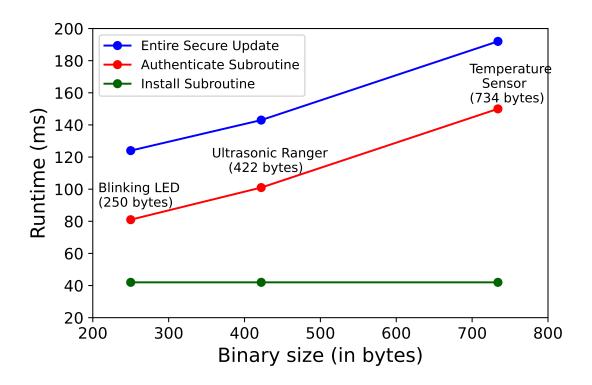

| 6.10 | Runtime of CASU-SW Secure Update                                             | 130 |

# LIST OF TABLES

|     |                                                                                               | Page |

|-----|-----------------------------------------------------------------------------------------------|------|

|     | Original application costs                                                                    |      |

| 4.1 | Functionality and hardware overhead comparison of existing run-time attestation architectures |      |

|     | Notation Summary                                                                              |      |

|     | Notation Summary                                                                              |      |

### ACKNOWLEDGMENTS

Such a wonderful five years of my life! Ph.D. was indeed a monumental learning experience. It taught me patience and diligence and helped me evolve into a better and more mature person. I am truly happy that I pursued this journey, and I am deeply grateful to everyone who played a role, whether knowingly or unknowingly, in making it remarkable.

Above all, I am incredibly thankful to my amazing advisor, Gene Tsudik, for providing me with the opportunity to pursue this Ph.D. with his generous support and guidance. He taught me how to conduct proper research and, especially, how to write scientific papers. His simple and unique style of writing and presenting research makes things easy to understand, and I am glad that I could take at least some of it with me.

I extend my sincere thanks to my committee members, Ardalan Amiri Sani and Alfred Chen, for their interest in my research and their valuable feedback and expertise. Having such exceptional researchers on my Ph.D. committee was truly a privilege.

I also owe my gratitude to my early mentors without whom this journey wouldn't have started. First of all, I would like to convey my sincere thanks to Jean-Pierre Seifert, my mentor during my first internship while pursuing Bachelor's degree. He is one of the reasons for my early interest in security. I would also like to thank my Bachelor's advisors – Debashis Ghosh and Vinod Pankajakshan – who were the very first to introduce me to research.

In addition to the mentors who helped me career-wise, I would also like to express my immense respect and gratitude towards my early teachers, Krishnan Pagalthivarthi and Ankush Mittal, who inspired me to pursue a Ph.D. and taught me how to lead a happy life.

Coming to my extraordinary collaborators during my Ph.D., I want to extend my heart-felt thanks to all whom I have worked with, am currently working with, and/or continue to work with: Ivan De Oliveira Nunes, Benjamin Terner, Seoyeon Hwang, Norrathep Rattanavipanon, Youngil Kim, Karim Eldefrawy, Moti Yung, Zeyu Liu, and Varun Madathil. Some of them were also my fellow labmates at UCI who were directly involved in some parts of this dissertation. I especially want to mention Ivan De Oliveira Nunes, my close mentor, with whom I had a lot of fun working, discussing, sharing ideas, and writing papers together. I have learned a lot from him. I also want to specifically thank Benjamin Terner and Karim Eldefrawy for introducing me to other interesting topics (apart from this dissertation) during one of my internships, which I would like to further explore. This list of collaborators is never-ending... thank you all so so much!

It would be incomplete without mentioning my dear friends that I made at UCI. I am very thankful to all my labmates who were there for me throughout my journey: Norrathep Rattanavipanon, Ivan De Oliveira Nunes, Ercan Ozturk, Yoshimichi Nataksuka, Seoyeon Hwang, Andrew Searles, Youngil Kim, Renascence Tarafder Prapty, Elina Van Kempen, and Gene Tsudik. Here's to all the fun times!

Last but not least, my delightful family and friends. This phase of my life wouldn't have

been this great if it weren't for all of you. First and foremost, I want to express my deep gratitude to my loving, understanding, and caring wife, Apoorva Muthineni. She was the reason I made it this far. I can't thank my parents, Padmasree and Someswara Rao Jakkamsetti, and my brother, Venkatesh Jakkamsetti, enough. You guys have been my strongest supporters throughout my life; this dissertation belongs to you! I would also like to thank my grandparents, uncles, aunts, and cousins in my family. Additionally, I am very grateful to all my friends in the US and India for their love, laughter, and support.

Portion of Chapter 3 is a reprint of the material as it appears in the Proceedings of 24th Design, Automation and Test in Europe Conference (DATE 2021) [53], used with permission from the Institute of Electrical and Electronics Engineers.

Portion of Chapter 4 is a reprint of the material as it appears in the Proceedings of the 58th Design Automation Conference (DAC 2021) [52], used with permission from the Institute of Electrical and Electronics Engineers.

Portion of Chapter 5 is a reprint of the material as it appears in the Proceedings of 43rd IEEE Symposium on Security and Privacy (S&P 2022) [104], used with permission from the Institute of Electrical and Electronics Engineers.

Portion of Chapter 6 is a reprint of the material as it appears in the Proceedings of the 41st International Conference on Computer-Aided Design (ICCAD 2022) [50], used with permission from the Association for Computing Machinery.

Financial support was provided by Gene Tsudik (via Graduate Student Researcher position), University of California, Irvine, UCI School of ICS (via Teaching Assistant position); and other grants and funding sources (via Gene): Army Research Office under contract W911NF-16-1-0536, Semiconductor Research Corporation under contract 2019-TS-2907, NSF Awards 1956393-SATC and 1840197-CICI, DARPA subcontract from Peraton Labs.

### VITA

### Sashidhar Jakkamsetti

#### **EDUCATION**

Doctor of Philosophy in Computer Science 2023 University of California, Irvine Irvine, California

Bachelor of Technology in Electronics & Communications Eng. 2016

Indian Institute of Technology, Roorkee Roorkee, India

#### PROFESSIONAL EXPERIENCE

Research Scientist

Bosch Research

Sunnyvale, California

Research Engineer Intern

Meta Research

Menlo Park, California

Ph.D. Research Intern

Visa Research

Menlo Park, California

Security Research Intern

SRI International

Summer 2019 & 2020

Menlo Park, California

Software Development Engineer 2016 - 2018 Microsoft Hyderabad, India

Research Intern & DAAD Scholar

Deutsche Telekom & Technical University of Berlin

Berlin, Germany

#### TEACHING EXPERIENCE

Teaching Assistant

University of California, Irvine

2018 – 2019

Irvine, California

#### PAPERS IN SUBMISSION OR UNDER REVIEW\*

Ivan De Oliveira Nunes, Seoyeon Hwang, Sashidhar Jakkamsetti, Norrathep Rattanavipanon, and Gene Tsudik. **PARseL: Towards a Verified Root-of-Trust over seL4.** In submission at *International Conference on Computer-Aided Design (ICCAD)*, 2023.

Sashidhar Jakkamsetti, Youngil Kim, and Gene Tsudik. Caveat (IoT) Emptor: Towards Transparency of IoT Device Presence. In submission at ACM Conference on Computer and Communications Security (CCS), 2023.

Sashidhar Jakkamsetti, Zeyu Liu, and Varun Madathil. Scalable Private Signaling. In submission at IEEE Symposium on Security and Privacy (S&P), 2023.

Karim Eldefrawy, Sashidhar Jakkamsetti, Ben Terner, and Moti Yung. **Standard Model Time-Lock Puzzles: Defining Security and Constructing via Composition.** In *IACR Cryptology ePrint Archive*, 2023.

#### REFERRED CONFERENCE PUBLICATIONS\*

Ivan De Oliveira Nunes, Sashidhar Jakkamsetti, Youngil Kim, and Gene Tsudik. CASU: Compromise Avoidance via Secure Updates for Low-end Embedded Systems. Appeared at *International Conference on Computer-Aided Design (ICCAD)*, 2022.

Ivan De Oliveira Nunes, Seoyeon Hwang, Sashidhar Jakkamsetti, and Gene Tsudik. Privacy-from-Birth: Protecting Sensed Data from Malicious Sensors with VERSA. Appeared at *IEEE Symposium on Security and Privacy (S&P)*, 2022.

Ivan De Oliveira Nunes, Sashidhar Jakkamsetti, Norrathep Rattanavipanon, and Gene Tsudik. On the TOCTOU Problem in Remote Attestation. Appeared at ACM Conference on Computer and Communications Security (CCS), 2021.

Ivan De Oliveira Nunes, Sashidhar Jakkamsetti, and Gene Tsudik. **DIALED: Data Integrity Attestation for Low-end Embedded Devices.** Appeared at *Design Automation Conference (DAC)*, 2021.

Ivan De Oliveira Nunes, Sashidhar Jakkamsetti, and Gene Tsudik. **Tiny-CFA: A Minimalistic Control-Flow Attestation Using Verified Proofs of Execution.** Appeared at *Design, Automation & Test in Europe (DATE)*, 2021.

<sup>\*</sup>Authors in the listed publications are arranged in alphabetical order of their last name.

#### OTHER PUBLICATIONS

Sugareddy, Sai Rohith, Sashidhar Jakkamsetti, Ramesh Goud, Yashaswini K.V. **Digi Analysis: Static And Dynamic Evaluation Of Facial Asymmetry & Mandibular Deviation**. Appeared at *International Journal of Current Advanced Research*, 2021. (*Runner-up in Competitive Table Clinic (Research*), Indian Orthodontic Society, 2021.)

#### OPEN-SOURCE CONTRIBUTIONS

Scalable Private Signaling https://github.com/sashidhar-jakkamsetti/sgx-ps  $Implementation\ of\ Scalable\ Private\ Signaling\ using\ Intel\ SGX\ SDK\ and\ Drivers,\ and\ OpenSSL\ written\ in\ C++.$

${\bf CASU} \\ Implementation\ of\ CASU\ using\ Xilinx\ Vivado,\ Diligent\ Basys3\ FGPA,\ OpenMSP430,\\ and\ HACL^*\ written\ in\ Verilog\ and\ C.$

VERSA https://github.com/sprout-uci/pfb Implementation of VERSA using Xilinx Vivado, Diligent Basys3 FGPA, OpenMSP430, and HACL\* written in Verilog and C.

VRASED+ https://github.com/sprout-uci/vrased-plus Implementation of VRASED+ (VRASED with Verifier Authentication) using Xilinx Vivado, Diligent Basys3 FGPA, OpenMSP430, and HACL\* written in Verilog and C.

RATA https://github.com/sprout-uci/RATA Implementation of RATA using Xilinx Vivado, Diligent Basys3 FGPA, OpenMSP430, and  $HACL^*$  written in Verilog and C.

## ABSTRACT OF THE DISSERTATION

Root-of-Trust Architectures for Low-end Embedded Systems

By

Sashidhar Jakkamsetti

Doctor of Philosophy in Computer Science

University of California, Irvine, 2023

Professor Gene Tsudik, Chair

Internet-of-Things (IoT), "smart", and Cyber-Physical Systems (CPS) devices have become increasingly popular and commonplace over the past two decades. Some of them perform safety-critical tasks and collect sensitive information, e.g., smoke detectors, temperature sensors, heart rate monitors, and fitness trackers. However, due to their stringent cost, size, and energy constraints, they are equipped with few (or no) security features. This makes them vulnerable to attacks. Some prior work proposed security architectures (such as remote attestation, proof of execution, and secure reset/erasure) to detect and mitigate malware on them. However, these approaches either partially mitigate the problem and/or require new hardware that is unrealistic for low-end devices.

This dissertation presents four hybrid (hardware/software co-design) root-of-trust (RoT) architectures that mitigate various attacks with small hardware modifications: TinyCFA, DIALED, VERSA, and CASU. TinyCFA and DIALED are passive RoTs that detect runtime (control-flow and data-only) attacks by proposing new control-flow and data-flow attestation architectures respectively. Whereas, VERSA and CASU are active RoTs that prevent sensor data privacy leakage and code-injection attacks based on hardware-enforced access control mechanisms. We implement and evaluate these architectures on low-end microcontrollers (e.g., TI MSP430) and show that they are suitable for resource-constrained IoT. We also

formally verify the hardware implementation of VERSA and CASU, thus showing that they meet all stated security requirements.

# Chapter 1

# Introduction

Internet-of-Things (IoT) and Cyber-Physical Systems (CPS) refer to (inter)connected embedded devices equipped with sensors, actuators, control units, and network connectivity that enable them to collect, process, and exchange data. Such special-purpose computing devices have become increasingly ubiquitous and widely adopted in many everyday settings, including both private (e.g., homes, offices, and factories) and public (e.g., cultural, entertainment, and transportation) spaces; they are also frequently used in farming, industrial, and vehicular automation. This enables the creation of "smart" environments that improve efficiency, productivity, and convenience in various aspects of modern society. It is expected that the number of IoT devices will exceed 29 billion by 2030 [122], indicating their continued growth and important role in shaping the future of industries, societies, and economies.

In contrast with general-purpose computers, IoT devices are purpose-built for specific tasks that involve sensing and/or actuation. Some of these devices have safety-critical functions, such as smoke/fire detectors, smart door locks, surveillance cameras, and other safety sensors used in industrial and automobile settings. On the other hand, there are IoT devices that gather and process sensitive personal information, including wearables like fitness trackers,

smartwatches, and health monitors such as pacemakers, connected inhalers, and syringe pumps.

IoT device manufacturers understandably prioritize the development of novel functionality, external aesthetics, user-friendliness, and other factors. Unfortunately, security is often considered a secondary concern or an afterthought. This is partly due to various constraints such as physical space, energy consumption, and cost considerations.

Unsurprisingly, IoT devices have been easy and attractive attack targets over the past few years, e.g., [121, 94, 58, 42]. In 2010, Stuxnet Worm [121] targeted industrial control systems (specifically, programmable logic controllers) used in Iran's nuclear facilities. By exploiting vulnerabilities in their firmware, Stuxnet disrupted centrifuge operations, causing physical damage to the equipment and sabotaging the nuclear enrichment process. In 2016, Mirai Botnet [94] launched a large-scale Distributed Denial-of-Service (DDoS) attack that infected a vast number of poorly secured IoT devices, including cameras and routers. Mirai also zombified Dyn, a major DNS provider in the US, causing widespread service disruptions and making them inaccessible for several hours. There are also many Mirai-inspried Botnets (e.g. Bashlite [7] and Hajime [8]) that search for, and infect, vulnerable IoT devices in order to later take advantage of them. In 2017, Triton (or Trisis) malware [58] attacked industrial safety systems used in oil and gas related infrastructures, leading to physical accidents and disruptions. There are also numerous attacks targeting IoT user privacy [63, 64, 130, 113, 16]. Notably, [130, 16] attacked smart home devices and eavesdropped on users to obtain sensitive private information.

A lot of research effort was invested in mitigating security and privacy issues in the IoT ecosystem. Many proposed techniques (e.g., [132, 78, 91]) use end-to-end encryption, authentication, and other cryptographic constructs to secure IoT devices and their communication with cloud servers. Another research direction focused on protecting sensitive data from passive in-network adversaries, (e.g. [127, 22, 23]) and performing analysis based on traffic

metadata, e.g., packet header fields, size, and frequency. However, most of the prior work assumes that these devices execute expected benign software and thus perform their expected functionality, including cryptographic operations upon which their security generally relies.

Aforementioned techniques are suitable for high-end computing devices, such as smartphones and laptops, because they are, by default, equipped with protective hardware such as Memory Protection Units (MPUs), Memory Management Units (MMUs), or Trusted Execution Environments (TEEs). Such devices also support operating systems or microkernels to provide virtualization and isolate security-sensitive functions. However, the situation becomes more challenging with low-power and budget-constrained embedded devices.

Low-end embedded devices are typically equipped with one or more resource-constrained micro-controller unit(s) (MCUs) (for example, TI MSP430 [74] and AVR AtMega32 [5]), which cannot run complex software or host expensive hardware. They often run simple software on "bare metal" with minimal (or no) security mechanisms in place. Consequently, it is impractical to assume that these MCUs, by themselves, can mitigate attacks, unlike their higher-end counterparts.

A naive approach to protect these MCUs is by making all software to be read and execute only. While this idea prevents malware from tampering with the software, it also sacrifices flexibility by precluding any software updates.

Motivated by the aforementioned concerns, several small Root-of-Trusts (RoTs) were recently proposed to provide rudimentary security services such as remote attestation [62, 47, 119, 21, 81, 117], proof of remote software execution [49, 118], proof of secure reset, erase, and update [27, 115, 48] on low-end devices. These tiny RoTs are usually implemented as hardware/software (hybrid) co-designs, aiming to achieve similar security levels as more costly hardware-based architectures, albeit, at much lower hardware cost. See Chapter 2 for more details on low-end MCUs and hybrid RoTs.

Nonetheless, current state-of-the-art can only measure software integrity, which although useful, is not sufficient for a comprehensive security design. Their key limitations are:

- 1. Techniques such as remote attestation and proofs of software execution measure software integrity during runtime. However, this does not capture the control-flow path taken by the software. For example, a buffer overflow attack can corrupt the stack or heap, potentially leading to a *control-flow attack*, i.e., where the software takes an unexpected (or unintended) execution path. In that case, despite measuring software integrity, the result of the execution is incorrect.

- 2. Data-only attacks target and corrupt the critical data variables while allowing the software to follow expected control-flow path, thus remaining undetected. Techniques that mitigate such attacks in sophisticated devices are not applicable to low-end MCUs since they require much additional hardware.

- 3. Most prior results are reactive in nature, meaning they can detect and report software compromises after the fact. However, they cannot prevent such compromises. Merely detecting software compromises is not very useful in privacy-sensitive or safety-critical applications. For example, consider a smoke detector. If the malware launches a code injection attack, it can prevent the alarm from sounding even in the presence of smoke. In such a scenario, despite attestation detecting the compromise, the consequences could be catastrophic. Moreover, attestation during such real-time applications is a hindrance because of its runtime overhead.

This dissertation explores new techniques in order to fill the gap in securing low-end resourceconstrained MCUs.

## 1.1 Contributions

We present four RoT architectures for low-end MCUs:

- 1. Tiny-CFA a control-flow attestation architecture that detects control-flow attacks by measuring the control-flow path taken by the software during runtime.

- 2. DIALED a data-flow attestation architecture that detects both control-flow and data-only attacks by measuring data-flow taken by the software during runtime.

- 3. VERSA a privacy architecture that prevents sensor data leakage by enabling a hardware-enforced access control mechanism.

- 4. CASU a security architecture that prevents code-injection attacks by enforcing benign software immutability and enabling secure authorized software updates.

The first two are *passive* architectures that detect and report runtime software exploits in low-end IoT devices. Whereas, the second two are *active* architectures that prevent privacy leakage and code modification attacks. They are specifically targeted toward personal or safety-critical devices.

The focus of this dissertation is on designing, implementing, and evaluating these RoTs. Another contribution of this dissertation is it implements formally verified hardware to derive its security properties. For the first two RoTs, we use verified hardware to extend runtime execution integrity, while for the other two, we implement new hardware, and verify it, to enforce the stated security properties.

Additional hardware used in the proposed architectures is kept minimal, accounting for less than 10-15% of the unmodified MCU core, making it suitable for low-end devices. Furthermore, all source code (including verification proofs) of VERSA and CASU are open-sourced.

# 1.2 Scope and Limitations

As usual with most new techniques, those proposed in this dissertation have limitations with respect to applicability, deployability, and security:

- 1. In terms of scope, they only apply to very low-end MCUs that perform simple tasks. Hence, they are probably not suitable for complex devices that run sophisticated software, as they may incur noticeable overhead when the software size increases. However, in our experiments (see the following Chapters), the overhead incurred by proposed RoTs is tolerable.

- 2. With regard to deployability, proposed techniques are not applicable to off-the-shelf MCUs, due to reliance on custom hardware support. However, all proposed techniques can be extended to MCUs equipped with hardware support, such as a TEE (e.g. ARM TrustZone [26]) with minor modifications.

- 3. In terms of security level, proposed techniques offer protection against software-compromised MCUs including those that are physically re-programmed. However, physical invasive attacks (e.g., inducing hardware faults, snooping on the memory bus, or retrieving MCU secrets via physical side-channels) are out of scope. There are standard techniques that address such attacks [110].

This dissertation further discusses these and other specific limitations inline in the corresponding chapters.

## 1.3 Dissertation Structure

Next, Chapter 2 provides some background relevant to the dissertation as a whole, including its scope and required fundamental security services: Remote Attestation and Proof-of-Execution (PoX). Chapters 3 and 4 present, respectively, Tiny-CFA and DIALED, the runtime attestation architectures for detecting control-flow and data-only attacks in low-end MCUs. These two architectures are built atop PoX to support basic runtime attestation mechanisms. DIALED is directly built atop Tiny-CFA to further reduce hardware overhead. Chapter 5 focuses on sensor data privacy problem stated earlier. It defines sensor data privacy, Privacy-from-Birth, and presents a provable RoT – VERSA – that realizes Privacy-from-Birth with formally verified hardware. Next, Chapter 6 introduces CASU, a proactive RoT that prevents code modification attacks. CASU includes an efficient secure over-the-air update protocol suitable for low-end devices. Finally, Chapter 7 discusses directions for future work.

We note that Chapter 2 only includes background on topics relevant to the dissertation as a whole. Background specific to a particular chapter is provided within that chapter. Similarly, system and adversary models are defined on a per-chapter basis. For the most part, notation is consistent across chapters.

Chapter 2

Background

#### Abstract

This chapter overviews background material. Section 2.1 sets the scope of targeted devices. We motivate this choice and discuss some intended contributions (specific contributions are outlined in subsequent chapters). Next, Section 2.2 overviews Remote Attestation ( $\mathcal{R}A$ ): a security service that enables verification of the software state of a potentially compromised remote device – a prover ( $\mathcal{P}rv$ ) – by a trusted verifier ( $\mathcal{V}rf$ ). We also overview of  $\mathit{VRASED}$ , a formally verified  $\mathcal{R}A$  architecture for low-end MCUs. Lastly, Section 2.3, describes Proof-of-Execution ( $\mathit{PoX}$ ): an attestation service that provides proof that software executed properly, besides measuring its integrity. Following this, we overview  $\mathit{APEX}$ , a formally verified  $\mathit{PoX}$  architecture for low-end MCUs.

# 2.1 Targeted Devices

We focus on low-end CPS/IoT/smart devices with low computing power and meager resources. These are some of the smallest and weakest devices based on low-power single-core MCUs with only a few kilobytes (KB) of program and data memory. Two prominent examples of such MCUs are Atmel AVR ATmega [5] and TI MSP430 [74]: 8- and 16-bit CPUs, respectively, typically running at 1-16MHz clock frequencies, with  $\approx 64$ KB of addressable memory.

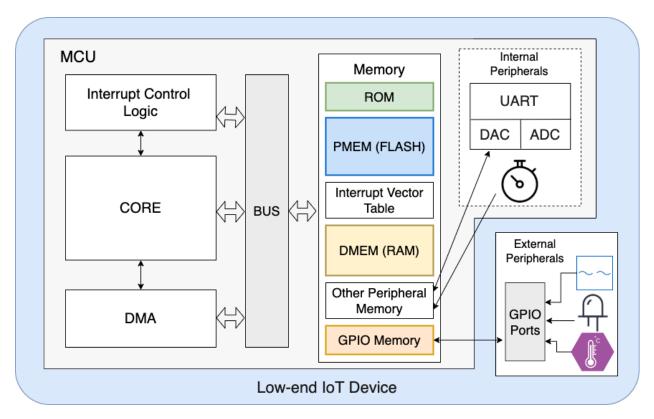

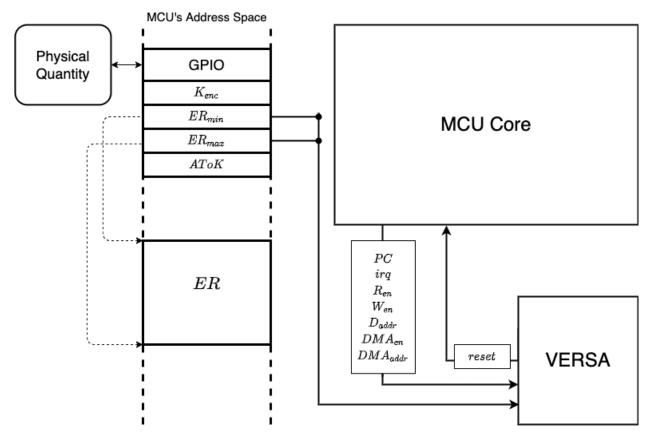

Figure 2.1 illustrates a generic architecture of such MCUs. It includes a CPU core, a Direct Memory Access (DMA) controller, and an interrupt control logic connected to the main memory via a bus, on a single System-on-a-Chip (SoC). DMA is a hardware controller that can read/write from/to memory in parallel with the core. Main memory contains several logical regions: read-only memory (ROM), program memory (PMEM or flash), Interrupt Vector Table (IVT), data memory (DMEM or RAM), and peripheral memory. IVT stores pointers to the Interrupt Service Routines (ISRs), where the execution jumps when an interrupt occurs; it also contains the Reset Vector pointer from where the core starts to execute, after a reboot. Application software is installed in PMEM, which is non-volatile memory realized as flash, and it uses DMEM, which is volatile memory made up of DRAM, for its stack and heap. ROM contains the bootloader and/or any immutable software hardcoded at manufacturing time, which is not modifiable thereafter. Peripheral memory region (also in DRAM and often considered as a part of DMEM), contains memory-mapped I/O and other communication interfaces, i.e., addresses in the memory layout that are mapped to hardware components, e.g., timers, General-Purpose Input/Output (GPIO), Universal Asynchronous Receiver/Transmitter (UART), Analog-to-Digital Converter (ADC) and vice versa, Inter-Integrated Circuit (I2C), and Serial Peripheral Interface (SPI). In particular, GPIO is peripheral memory addresses hardwired to physical ports that interface with external circuits, e.g., analog sensors/circuits.

Figure 2.1: System Architecture of an MCU-based IoT Device

We note that small MCUs usually come in one of two memory architectures: Harvard and von Neumann. The former isolates PMEM and DMEM by maintaining two different buses and address spaces, while the latter keeps both PMEM and DMEM in the same address space and accessible via a single bus.

These MCUs execute instructions in place, i.e., directly from flash memory. They have neither memory management units (MMUs) to support virtualization/isolation, nor memory protection units (MPUs). Therefore, privilege levels and isolation used in higher-end devices and generic enclaved execution systems (e.g., Intel SGX [75] or ARM TrustZone-A [26]) are not applicable.

The prototype implementation of all the proposed RoTs in this dissertation is based on MSP430 MCU, a common platform for low-end embedded devices. One important factor in this choice is public availability of an open-source MSP430 MCU design – OpenMSP430

[68]. Nonetheless, we note that our generic machine model and methodology can be readily applicable to other low-end MCUs of the same class, such as Atmel AVR ATmega. Additionally, we hope that the lessons and insights gained from this work can be valuable for designing and proving the security of similar services targeting higher-end devices.

# 2.2 Remote Attestation (RA)

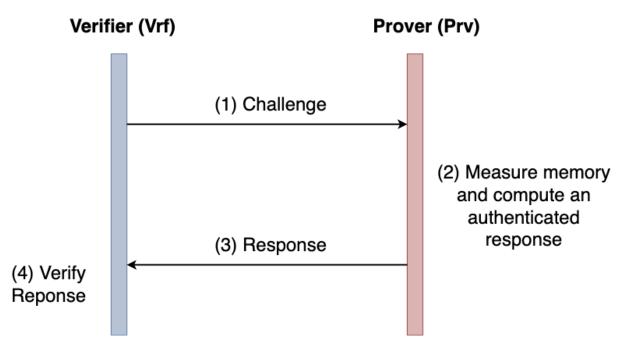

Remote Attestation ( $\mathcal{R}A$ ) allows a trusted entity (verifier =  $\mathcal{V}rf$ ) to remotely measure current memory contents (e.g., software binaries) of an untrusted embedded device (prover =  $\mathcal{P}rv$ ). As shown in Figure 2.2,  $\mathcal{R}A$  is usually realized as a challenge-response protocol:

- 1. Vrf sends an attestation request containing a challenge ( $\mathcal{C}$ hal) to  $\mathcal{P}$ rv.

- Prv receives the request and computes an authenticated integrity check over its memory and Chal. The memory region can be either pre-defined or explicitly specified in the attestation request.

- 3.  $\mathcal{P}$ rv returns the result to  $\mathcal{V}$ rf.

- 4. Vrf verifies the result and decides if it corresponds to a valid  $\mathcal{P}$ rv state.

The authenticated integrity check is accomplished by first measuring the  $\mathcal{P}rv$  software memory using a suitable cryptographic hash function (e.g., SHA-256). Then, the result, i.e. the digest, is authenticated using a Message Authentication Code (e.g., HMAC) or a digital signature (e.g., ECDSA). While computing a MAC requires  $\mathcal{P}rv$  to have a symmetric key shared with  $\mathcal{V}rf$ , computing a signature does not need any shared secrets, since  $\mathcal{V}rf$  uses  $\mathcal{P}rv$ 's public key for verification. Both MAC and signature require secure storage to store the symmetric/private key that is not accessible to software running on  $\mathcal{P}rv$  memory, except for trusted and typically immutable attestation code (or attestation hardware engine, when

Figure 2.2:  $\mathcal{R}A$  Protocol

present). Since we are dealing with low-end MCUs, we assume the symmetric key setting with MAC implementation, however, we note that using a public key with signatures is not very different. Since most  $\mathcal{R}A$  threat models assume that  $\mathcal{P}rv$ 's software is compromised, secure key storage implies some level of hardware support.

### **2.2.1** *VRASED*

VRASED [47] is a verified hybrid (hardware/software)  $\mathcal{R}A$  architecture for low-end MCUs. It comprises a set of (individually) verified hardware and software sub-modules; their composition provably satisfies formal definitions of  $\mathcal{R}A$  soundness and security. VRASED software component, which is immutable (stored in ROM), implements the authenticated integrity function computed over a given "Attested Region" (AR) of  $\mathcal{P}rv$ 's memory. Meanwhile, its hardware component assures that its software counterpart executes securely and that no function of the secret key is ever leaked. In short,  $\mathcal{R}A$  soundness states that the integrity measurement must accurately reflect a snapshot of  $\mathcal{P}rv$ 's memory in AR, disal-

lowing any modifications to AR during the actual measurement.  $\mathcal{R}A$  security defines that the measurement must be unforgeable, implying protection of secret key  $\mathcal{K}$  used for the measurement.

In order to prevent DoS attacks on  $\mathcal{P}rv$ , the RA protocol may involve authentication of the attestation request, before  $\mathcal{P}rv$  performs attestation. If this feature is used, an authentication token must accompany every attestation request. (By saying "this feature is used", we mean that its usage, or lack thereof, is fixed at the granularity of a  $\mathcal{V}rf$ - $\mathcal{P}rv$  setting, and not per single  $\mathcal{R}A$  instance.). In  $\mathcal{V}RASED$ ,  $\mathcal{V}rf$  computes this token as an HMAC over  $\mathcal{C}hal$ , using  $\mathcal{K}$ . Since  $\mathcal{K}$  is only known to  $\mathcal{P}rv$  and  $\mathcal{V}rf$ , this token is unforgeable. To prevent replays,  $\mathcal{C}hal$  is a monotonically increasing counter, and the latest  $\mathcal{C}hal$  used to successfully authenticate  $\mathcal{V}rf$  is stored by  $\mathcal{P}rv$  in persistent and protected memory. In each attestation request, incoming  $\mathcal{C}hal$  must be greater than the stored value. Once an attestation request is successfully authenticated, the stored value is updated accordingly.

VRASED software component is based on a formally verified HMAC implementation from the HACL\* cryptographic library [139], which is used to compute:

$$H = HMAC(KDF(\mathcal{K}, \mathcal{C}hal), AR)$$

(2.1)

where  $KDF(\mathcal{K}, \mathcal{C}hal)$  is a one-time key derived from the received  $\mathcal{C}hal$  and  $\mathcal{K}$  using a key derivation function.

All techniques proposed in this dissertation use VRASED for some form of attestation or HMAC computation on Prv memory. Details of each instance of VRASED usage are in each chapter.

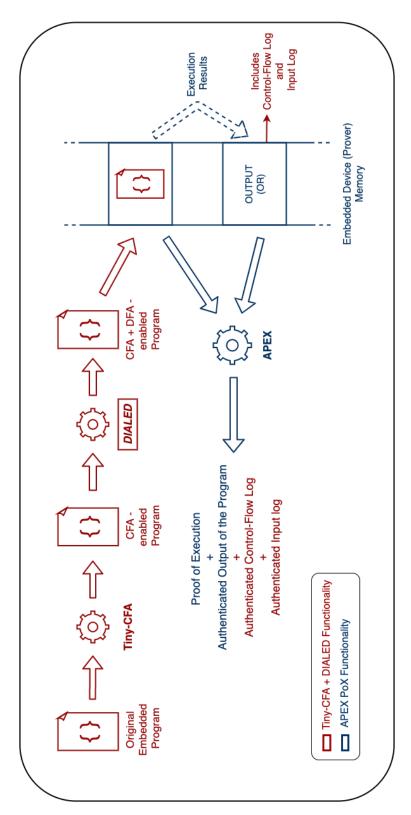

# 2.3 Proofs of Execution (PoX)

PoX augments RA capability by proving to Vrf that: (a) the expected software is stored in Prv memory, and (b) this code executed, and any outputs were produced by its timely and authentic execution. In short, PoX cryptographically binds and authenticates the executed software and the outputs it generated during runtime, with the help of RA.

### **2.3.1** *APEX*

The first PoX architecture for low-end MCU-s is in APEX [49]. It includes a hardware module controlling the value of a 1-bit flag called EXEC, that cannot be written by any software. A value EXEC = 1 indicates to Vrf that attested code was executed successfully, between the time when the Chal was received from Vrf and the time when the RA measurement occurs (via HMAC). Similarly, when it receives an attestation reply with EXEC = 0, Vrf concludes that execution of said code did not occur, or the code terminated due to an error, or that execution (or its output) was tampered with. In APEX, the RA measurement covers: (a) the EXEC flag itself; (b) the region where this execution's output is saved (output region -OR); and (c) the executable itself (stored in the executable region -ER). Thus, security of the underlying RA architecture guarantees that the contents of these memory regions cannot be forged/spoofed to something different from their values at the time of the attestation computation.

APEX considers that a code executed properly (and sets EXEC = 1) if and only if:

- 1. Execution is atomic (i.e., uninterrupted), from the executable's first instruction (legal entry  $ER_{min}$ ), to its last instruction (legal exit  $ER_{max}$ );

- 2. Neither the executable (ER), nor its outputs OR are modified in between the execution

and subsequent RA computation;

3. During execution, data-memory (including OR) cannot be modified, by means other than the executable in ER itself, e.g., no modifications by other software or DMA controllers.

These conditions mean that EXEC = 1 assures that memory contents (of ER and OR) are consistent between ER's code execution and respective attestation, and that execution itself is untampered, e.g. via interrupts, or modification of intermediate results in data memory. ER and OR locations and sizes are configurable, allowing for PoX of arbitrary code and output sizes. APEX implementation is built atop VRASED. Moreover, APEX hardware module is itself formally verified to adhere to a set of formal logic specifications, similar to VRASED. These properties, along with VRASED verified guarantees, are proven sufficient to imply a security definition (stated using the cryptographic security game framework [92]) for unforgeable proofs of execution. For a detailed description of APEX proofs, we refer the interested reader to [49].

As discussed in [49], similar to Trusted Execution Environments (TEEs) targeting higherend platforms (e.g., Intel SGX [75] and ARM TrustZone[26]), APEX assumes executable correctness, i.e., the code to be executed on  $\mathcal{P}rv$  is assumed to be bug-free and memorysafe code. Hence, APEX does not protect against runtime (aka control-flow and data-only) attacks. In Tiny-CFA and DIALED, we bridge this gap by introducing an automated code instrumentation technique that uses APEX to implement Control-Flow Attestation ( $\mathcal{C}FA$ ) and Data-Flow Attestation ( $\mathcal{D}FA$ ), respectively. In other words, we show that  $\mathcal{C}FA$  on top of APEX (or any PoX), without any additional hardware requirement, is both possible and affordable.

# Chapter 3

Tiny-CFA: A Minimalistic Control-Flow

Attestation Using Verified Proofs of

Execution

#### Abstract

This chapter fills the gap in prior work by detecting control-flow attacks in low-end MCUs. Control-flow attacks refer to manipulation of software execution flow during runtime, which can lead to incorrect and potentially malicious behavior. While a few techniques have been proposed, they require a lot of additional hardware that might cost more than the underlying MCU.

To this end, we construct Tiny-CFA, a Control-Flow Attestation (CFA) technique that requires only a single hardware capability: the ability to generate proofs of remote software execution (PoX). This results in the lowest hardware overhead among all CFA techniques. Furthermore, in terms of runtime overhead, Tiny-CFA incurs lower performance compared to previous CFA techniques. We implement and evaluate Tiny-CFA, analyze its security, and demonstrate its practicality using real-world publicly available applications.

Material in this chapter appeared in the Proceedings of 24th Design, Automation and Test in Europe Conference (DATE 2021) [53].

## 3.1 Introduction

Runtime/data-oriented attacks [125] tamper with execution state on the program's stack or heap to arbitrarily divert the program's execution flow. Such attacks need not modify the executable itself, but only the order in which its instructions are executed. Thus, they are not detectable by  $\mathcal{R}A$ . Control-flow attacks can be launched by a variety of means. For instance, in languages such as  $\mathsf{C}$ ,  $\mathsf{C++}$ , and Assembly (which are widely used to program MCU-s), buffer overflows [45] can overwrite functions' return addresses, hijacking the program's control-flow and launching well-known Return-Oriented Programming (ROP) attacks [120]. These attacks are especially dangerous for low-end MCU-s that can not avail themselves of more sophisticated OS-based mitigations, e.g., canaries, Address Space Layout Randomization (ASLR), and Control-Flow Integrity techniques, available in high-end platforms. We discuss a concrete example of such an attack in low-end MCU-s (and how it is detected by Tiny-CFA) in Section 3.4.1.

Control-Flow Attestation (CFA) [15, 55, 54, 135] augments conventional RA capability to enable detection of control-flow attacks. CFA techniques provide Vrf with a report that conveys whether the expected code is loaded on Prv, as well as which particular instruction path was taken during each execution of this program. In other words, CFA provides an authentic and unforgeable report that allows Vrf to learn if instructions of a given program were executed in a particular expected/legal order. This is typically achieved by securely logging information associated with the destination of each control-flow altering instruction, e.g., jumps, branches, returns.

CFA techniques have been implemented on medium- to high-end embedded devices (e.g., Raspberry Pi, and RISC-V based processors), by leveraging trusted hardware support, such as ARM TrustZone, hardware branch monitors, and hardware hash engines. However, for resource constrained MCU-s, these requirements are too costly, since their hardware overhead

is often higher than that of the MCU's core itself, in terms of size, energy, and monetary cost. To bridge this gap, our work uses PoX [49] (see Section 2.3 for details) – along with automatic code instrumentation, to derive a new CFA technique. Since PoX can be implemented efficiently even on most resource-constrained MCU-s, our CFA technique has considerably lower hardware overhead than that of prior work.

#### 3.1.1 Contributions

This chapter makes the following contributions:

- 1. Design of Tiny-CFA— a CFA technique based on automated software instrumentation where the only hardware requirement is that already provided (at relatively low-cost) by PoX architectures.

- 2. Implementation of *Tiny-CFA* based on *APEX* as a result, its hardware cost is about 1 to 2 orders of magnitude lower than prior *CFA* techniques. Hence, it is suitable for the low-end and ultra-low-energy MCU-s, such as MSP430 and AVR ATmega32. We also show a case study of a control-flow attack and how *Tiny-CFA* detects it.

We note that because Tiny-CFA implementation relies on a formally verified PoX architecture as the sole architectural component on Prv, it is also the first CFA technique to offer the high-level assurance provided by a verified hardware Trusted Computing Base (TCB).

## 3.2 Background

### 3.2.1 Control-Flow Attestation (CFA)

Runtime attacks exploit program vulnerabilities to cause malicious and unauthorized program actions. The most prominent example is a buffer overflow, allowing the attacker to corrupt memory adjacent to a buffer. The main target of these attacks is the manipulation of control-flow information stored on the program's stack and heap, causing the program to deviate from its intended behavior. In addition to detection of code modification via  $\mathcal{R}A$ ,  $\mathcal{C}FA$  detects such runtime attacks that hijack the program's control-flow by reporting the path the program took to  $\mathcal{V}rf$ .

A typical CFA scheme works by first instrumenting the existing software to record every control-flow transfer it takes at runtime. After the program terminates, this log is then sent to the Vrf for investigation of potential control-flow attacks. The instrumentation ensures that at each control-flow altering instruction (e.g., jumps, branches, returns), execution is trapped into a secure region to log the destination address. Only logging each control-flow transfer is not sufficient, since one flavor of control-flow attacks involves hijacking the loops to iterate more or fewer times than expected. Therefore, CFA also logs the condition on which such control-flow transfer occurs.

C-FLAT [15] is the earliest CFA architecture. It uses ARM TrustZone-M [90] secure world to implement CFA. By instrumenting the executable, at its every control-flow transfer, with context switches between TrustZone's normal and secure worlds, the control-flow path is logged into protected memory. C-FLAT targets higher-end embedded devices (e.g., Raspberry Pi), and its dependence on TrustZone (plus, numerous context switches) makes it unsuitable for low-end MCU-s.

## **3.3** *Tiny-CFA*

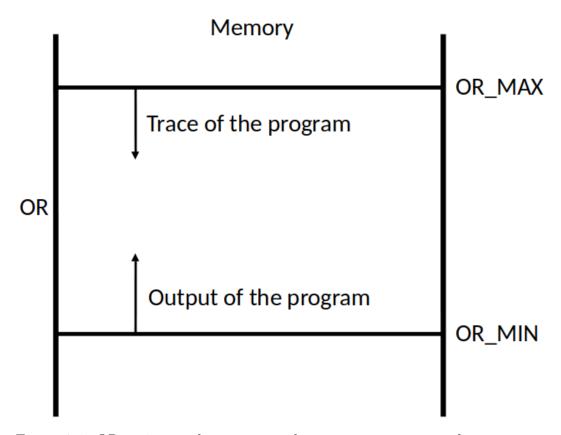

Tiny-CFA uses APEXPoX that ties the executed code to its output, stored in a data-memory range of configurable size, called OR. The basic idea is to instrument the code to produce a log of the program control-flow path and make it a part of the output. The program instrumentation writes the destination address of each control-flow altering instruction into OR. We denote this control-flow log as CF-Log.

As shown in Figure 3.1, both regular program outputs and CF-Log are written to OR. Recall from Section 2.3 that OR size/location is configurable. Hence, Vrf can choose OR to be large enough to fit both the regular program output and its expected CF-Log. Note that, in any CFA scheme, Vrf must have a priori knowledge of the expected/benign control-flows and their sizes. Therefore, the appropriate OR size is trivially obtained by adding the regular output and CF-Log sizes. The regular program output is written to OR normally, bottom-to-top of OR, as in APEX. Whereas, Tiny-CFA instrumentation writes CF-Log to OR from top to bottom. This strategy is similar to how stack and heap are handled in RAM and it assures that the program output and CF-Log do not interfere or overlap with each other, as long as OR is appropriately sized.

We believe that this general idea is both intuitive and sensible; it guides Tiny-CFA's design. However, ensuring that Tiny-CFA results in a  $secure\ CFA$  design is more challenging. To see why, note that **the executable to be attested**, (i.e., security-critical code stored in ER) is itself subject to control-flow attacks. Thus, any values logged to CF-Log by the instrumented executable can, in principle, be modified as part of a control-flow attack. In other words, Tiny-CFA's approach secure only if CF-Log is an **append-only log**. Otherwise, upon completion of its nefarious tasks, a control-flow attack can overwrite CF-Log to reflect a benign or expected control-flow, erasing any trace of the compromised control-flow and thus fool  $\mathcal{V}$ rf. In higher-end  $\mathcal{C}$ FA architectures (e.g., C-FLAT [15]), this property is ob-

Figure 3.1: OR region used to store regular program outputs and CF-Log.

tained by logging the control-flow to dedicated secure memory, which is never accessible to untrusted/application code. However, as discussed in Sections 3.1 and 3.2, low-end MCU-s cannot afford such expensive security features. Below, we detail how Tiny-CFA can be made secure by relying exclusively on PoX and instrumentation.

## 3.3.1 Design Rationale & Security

We now discuss *Tiny-CFA* design rationale and security properties at a high-level. Implementation details of *Tiny-CFA* on MSP430 are specified in Section 3.3.3. We postulate the properties that ensure that control-flow attacks are always detected under the following comprehensive adversarial model:

#### 3.3.1.1 Adversarial Model

We assume that the adversary controls  $\mathcal{P}rv$ 's entire software state, including code and data.  $\mathcal{A}dv$  can modify any writable memory and read any memory that is not explicitly protected by hardware-enforced access control rules (e.g., APEX rules). Program memory modifications can be performed to change instructions, while data memory modifications may trigger control-flow attacks. Adversarial modifications are allowed before, during, or after the execution of the program.

#### 3.3.1.2 Security Properties

The following security properties are adhered to by Tiny-CFA for achieving guaranteed CFA.

#### (P1) Integrity of Code, Instrumentation, and Output

Clearly, any instrumentation-based approach is only sound if unauthorized modifications to the instrumented code itself (e.g., to remove instrumentation) are detectable. Detection of modifications is offered by the underlying  $\mathcal{R}A$  and PoX architectures (see Section 3.2). In particular, these architectures guarantee that any unauthorized code modification is detected by Vrf. They also guarantee that modifications to attested executable's output (OR – which includes CF-Log) are only possible if done by the attested executable itself, during its execution.

#### (P2) Secure logging of control-flow instructions

The first step in *Tiny-CFA*, is to instrument all control-flow altering instructions to log their destinations to CF-Log, in OR. CF-Log is implemented as a stack, from the highest value in

OR  $(OR_{max})$  growing downwards, as shown in Figure 3.1. The pointer to the top of this stack is stored in a dedicated register  $\mathcal{R}$ . Each control-flow instruction is then instrumented with additional instructions to push its destination address to this stack, i.e.: (a) write the destination of address to the memory location pointed to by  $\mathcal{R}$ ; and (b) decrement  $\mathcal{R}$ . At instrumentation time, the assembly code of the executable is inspected to assure that no other instructions utilize the MCU register  $\mathcal{R}$ . In all practical examples considered in this work, executables have at least one free register available. If no such register exists by default, the code can be recompiled to free up one register.

#### (P3) Secure logging of conditional branches

Conditional branches determine control-flow at runtime, depending on a result of a conditional statement, e.g., a comparison or equality test. These instructions are used to implement loops and if-then-else statements used in high-level languages. Conditional branches are instrumented by pushing to CF-Log's stack (using the same method as in P2) the possible destinations as well as the result of the conditional statement. This way, by inspecting CF-Log,  $\mathcal{V}$ rf can determine the exact path taken by the conditional branch.

#### (P4) CF-Log Write safety

Write operations (e.g. mov) are risky because they can be used to overwrite CF-Log, thus hiding the compromised control-flow from Vrf. Direct writes (which modify constant addresses) are easy to deal with because they can be statically inspected for safety at instrumentation time. In particular, the instrumenter can check that no direct writes modify CF-Log reserved addresses in OR. Indirect writes modify memory addresses determined at runtime. Consequently, they require instrumentation to check at runtime. After each indirect write, Tiny-CFA instrumentation inserts instructions to check whether the write destination

is within CF-Log by checking if the write destination is within the range  $[\mathcal{R}, OR_{max}]$  – the memory range currently in use to store CF-Log. Upon detection of an illegal write, execution is terminated, implying an invalid control-flow.

#### (P5) Wrap-around attack protection

Another way for a control-flow attack to go undetected is to keep executing the program until  $\mathcal{R}$  value overflows and wraps-around, and overwriting of CF-Log. To protect against such attacks, modifications to  $\mathcal{R}$  have an additional check, ensuring that whenever  $\mathcal{R}$  points to an instruction outside OR range, execution is terminated.

#### (P6) $\mathcal{R}$ initialization verification

Previous properties rely on  $\mathcal{R}$ , which is initialized to  $OR_{max}$  at the start of execution, to assure that CF-Log is indeed stored in OR. However, performing this initialization inside the executable being attested allows for control-flow attacks that jump back to the  $\mathcal{R}$  initialization code to reset  $\mathcal{R}$  in the middle of the execution. To prevent this, Tiny-CFA instruments the executable to check if  $\mathcal{R}$  has been previously properly initialized to  $\mathcal{R} = OR_{max}$ . The caller application becomes responsible for initializing  $\mathcal{R}$  appropriately, making control-flow attacks that re-initialize  $\mathcal{R}$  to reset CF-Log impossible, since they require jumping outside of the executable range -ER — which is detected by APEX as a violation.

#### 3.3.1.3 Security Argument

Below we argue the security of Tiny-CFA based on the aforementioned properties (P1 - P6).

Let  $\mathcal{P}$  denote a function/code-segment for which execution and control-flow need to be attested. Properties  $\mathbf{P2}$  &  $\mathbf{P3}$  assure that all changes to the control-flow of  $\mathcal{P}$  are logged to CF-Log at runtime. Then, by inspecting an authentic (untampered) CF-Log,  $\mathcal{V}$ rf can determine the exact control-flow taken by that particular  $\mathcal{P}$  execution. Meanwhile, properties  $\mathbf{P5}$  &  $\mathbf{P6}$  guarantee that CF-Log is stored inside OR, within  $[\mathcal{R}, OR_{max}]$  range. Property  $\mathbf{P4}$  detects any illegal writes during execution that attempt to modify CF-Log, i.e., writes to  $[\mathcal{R}, OR_{max}]$  range. Hence, for a given execution of  $\mathcal{P}$ , the combination of  $\mathbf{P4}$ ,  $\mathbf{P5}$  &  $\mathbf{P6}$  guarantees that each written value can never be overwritten or deleted from CF-Log. Finally,  $\mathbf{P1}$ , inherited from the underlying PoX architecture, assures that neither  $\mathcal{P}$  instructions (including instrumentation), nor its output (including CF-Log) can be modified by other means (e.g., other software on  $\mathcal{P}rv$ , interrupts, DMA) before, during, or after execution. Any such attempt is detectable by  $\mathcal{V}rf$ , because it causes APEX to set EXEC = 0; recall the EXEC flag behavior described in Section 2.3. Therefore, Tiny-CFA properties  $\mathbf{P1}$ - $\mathbf{P6}$  suffice to implement secure  $\mathcal{CFA}$ , under the aforementioned adversarial model.

## 3.3.2 Optimizations

CF-Log size determines the practicality of *Tiny-CFA* due to the resource-constrained nature of low-end MCU-s, especially, with respect to memory size. Any log of control flow transitions bloats rapidly for control-flow intensive code segments, e.g., loops with many iterations. In this section, we discuss two simple optimizations (O1 & O2) that significantly reduce CF-Log size without sacrificing overall security.

### (O1) Static Control-Flow Instructions

Control-flow instructions with constant destination addresses (determined statically in the code) need not be logged to CF-Log, as their effect on the program control-flow can not

change at runtime. This removes the need to log operations, such as usual function calls (with exception of callbacks), fixed-address **go-to-s**, and similar.

#### (O1) Loops Optimization

Loops are challenging to log efficiently due to their high number of control-flow operations. For instance, consider a delay function based on *busy-wait*, commonly used in MCU code. It essentially consists of a loop that increments a counter up to a certain constant. The higher the delay, the higher the number of iterations, implying the higher the number of control-flow instructions to be logged. Even a 1-second delay loop, would require millions of iterations (assuming typical clock frequencies on the order of MHz) resulting in millions of symbols logged to CF-Log. To deal with such cases, we introduce an optimization for loops for which the number of iterations can be determined, at instrumentation time.

memset, and memcpy.

### **3.3.3** Implementing Tiny-CFA

We now describe how properties **P1-P6** are securely implemented via automatic assembly instrumentation on the MSP430 MCU. Our instrumenter is implemented in **Python** with approximately 300 lines of code. It replaces relevant code segments in order to securely enforce properties **P1-P6**.

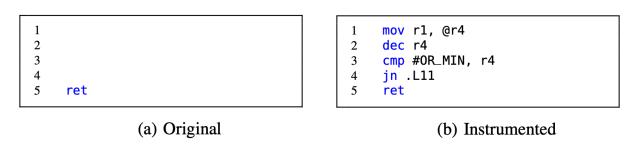

Figure 3.2: Instrumentation example: indirect control-flow instructions.

Figure 3.2 shows the instrumentation of indirect control-flow instructions: return in this particular example. It writes the return address, which in MSP430 assembly must be loaded to register r1 before ret is called, to CF-Log. In our implementation  $\mathcal{R} = r4$ . Hence, the content of r1 (destination address) is copied to the address pointed to by  $\mathcal{R}$  in OR, as required by P2. To also enforce P5, upon writing to the address of  $\mathcal{R}$ , and moving  $\mathcal{R}$  to point to the next address, the comparison at line 3 checks if  $\mathcal{R}$  is still inside OR, otherwise exiting the program, by jumping to an exit instruction at line 4.

Figure 3.3 depicts the instrumentation of indirect write instructions to enforce **P4**. Upon writing to a given memory location (address pointed to by r14, in this example), checks are performed to determine if this write operation did not modify CF-Log memory range:  $[\mathcal{R}, OR_{max}]$ . If an illegal write occurs, program execution is terminated (at line 5) and a control-flow attack attempt is detected.

```

mov.b r15, @r14

mov.b r15, @r14

2

2

cmp r4, r14

3

3

ilo .L12

4

4

cmp #OR_MAX, r14

5

5

jlo .L11

6

6

.L12:

(a) Original

(b) Instrumented

```

Figure 3.3: Instrumentation example: indirect write instructions.

```

1 application:

1 application:

2 cmp #0R_MAX, r4

3 jne .L11

4 ...

4 ...

(a) Original

(b) Instrumented

```

Figure 3.4: Instrumentation example:  $\mathcal{R}$  initialization check.

Figure 3.4 shows the instrumentation, required by  $\mathbf{P6}$ , at the beginning of the code segment. It ensures that  $\mathcal{R}$  is properly initialized, otherwise halting execution at line 3.

Finally, Figure 3.5 depicts the instrumentation required by **P3**. It logs to CF-Log the results of conditional statements. Note that, after a conditional statement (e.g., at line 1) evaluation, the result is stored in the status register r2. Hence, the content of r2 is written to CF-Log (line 2), since it is sufficient to determine the destination of the conditional branch. The

```

cmp.b #64, r15

cmp.b #64, r15

2

mov r2, @r4

3

dec r4

3

4

4

cmp #OR_MIN r4

5

5

.L11

6

6

mov l(r4), r2

7

jne .L2

jne .L2

7

8

(a) Original

(b) Instrumented

```

Figure 3.5: Instrumentation example: conditional branches.

same check to enforce P5 in Figure 3.2, is also performed in this case, because information is being written to CF-Log. Since this check itself overwrites r2, the original value of r2 needs to be retrieved (at line 6) before the actual branch instruction at line 7. A more memory-optimized implementation of P3 could be to rather find out which status bit in the status register decides the jump to the destination address and write only that bit into OR instead of the whole 16-bit register value. Essentially saving 15-bits of the CF-log for every conditional jump.

**Remark:** Tiny-CFA can not be abused by control-flow attacks that jump in the middle of the instrumentation instructions. Such an illegal jump is logged to CF-Log and is thus detectable by Vrf. Since R never retracts (within a given execution), write checks (see Figure 3.3) make it impossible to delete any information logged to CF-Log, including jumps into the middle of instrumented code instructions.

## 3.4 Case Study & Evaluation

## 3.4.1 Case Study: Control-Flow Attacks in Low-End MCU-s