## **UC Davis**

## **UC Davis Previously Published Works**

#### **Title**

Ultra-Steep-Slope High-Gain MoS2 Transistors with Atomic Threshold-Switching Gate

### **Permalink**

https://escholarship.org/uc/item/07n1k06f

### **Journal**

Advanced Science, 9(8)

#### **ISSN**

2198-3844

#### **Authors**

Lin, Jun Chen, Xiaozhang Duan, Xinpei <u>et al.</u>

### **Publication Date**

2022-03-01

#### DOI

10.1002/advs.202104439

Peer reviewed

www.advancedscience.com

# **Ultra-Steep-Slope High-Gain MoS<sub>2</sub> Transistors with Atomic Threshold-Switching Gate**

Jun Lin, Xiaozhang Chen, Xinpei Duan, Zhiming Yu, Wencheng Niu, Mingliang Zhang, Chang Liu, Guoli Li, Yuan Liu, Xingqiang Liu,\* Peng Zhou,\* and Lei Liao\*

The fundamental Boltzmann limitation dictates the ultimate limit of subthreshold swing (SS) to be 60 mV dec $^{-1}$ , which prevents the continued scaling of supply voltage. With atomically thin body, 2D semiconductors provide new possibilities for advanced low-power electronics. Herein, ultra-steep-slope  $\text{MoS}_2$  resistive-gate field-effect transistors (RG-FETs) by integrating atomic-scale-resistive filamentary with conventional  $\text{MoS}_2$  transistors, demonstrating an ultra-low SS below 1 mV dec $^{-1}$  at room temperature are reported. The abrupt resistance transition of the nanoscale-resistive filamentary ensures dramatic change in gate potential, and switches the device on and off, leading to ultra-steep SS. Simultaneously, RG-FETs demonstrate a high on/off ratio of 2.76  $\times$  10 $^7$  with superior reproducibility and reliability. With the ultra-steep SS, the RG-FETs can be readily employed to construct logic inverter with an ultra-high gain  $\approx$ 2000, indicating exciting potential for future low-power electronics and monolithic integration.

J. Lin, X. Duan, Z. Yu, W. Niu, M. Zhang, C. Liu, G. Li, Y. Liu, X. Liu, L. Liao Key Laboratory for Micro/Nano Optoelectronic Devices of Ministry of Education& Hunan Provincial Key Laboratory of Low-Dimensional Structural Physics and Devices School of Physics and Electronics Hunan University Changsha 410082, China E-mail: liuxq@hnu.edu.cn; liaolei@whu.edu.cn

X. Chen, P. Zhou State Key Laboratory of ASIC and System Department of Microelectronics Fudan University Shanghai 200433, P. R. China E-mail: pengzhou@fudan.edu.cn

L. Liao College of Semiconductors (College of Integrated Circuits)

Changsha 410082, China

Hunan University

The ORCID identification number(s) for the author(s) of this article can be found under https://doi.org/10.1002/advs.202104439

© 2022 The Authors. Advanced Science published by Wiley-VCH GmbH. This is an open access article under the terms of the Creative Commons Attribution License, which permits use, distribution and reproduction in any medium, provided the original work is properly cited.

DOI: 10.1002/advs.202104439

#### 1. Introduction

Continuous miniaturization of traditional silicon-based metal-oxide-semiconductor field-effect transistors (MOSFETs) has facilitated aggressive high-performance integrated circuits with ever-increasing speed, integration density, and low power consumption. Improved MOSFETs performance requires to reduce the supply voltage  $(V_{DD})$  and the threshold voltage  $(V_{TH})$  to maintain high overdrive factor  $(V_{\rm DD} - V_{\rm TH})^{[1,2]}$  However, subthreshold swing (SS) is fundamentally limited to above 60 mV dec-1 at room temperature, because of Boltzmann distribution of carrier, which leads to exponential growth of leakage current and static power consumption.[3] Therefore, reducing SS has become one of the critical challenges for large-scale high-performance integrated circuit development.[4] Several steep-slope

devices based on innovative structure or transport mechanisms, such as tunnel FETs (TFETs)[5,6] and negative capacitance FETs (NCFETs),<sup>[7]</sup> have been proposed to combat the "Boltzmann tyranny," which have SS below 60 mV dec-1 at room temperature. However, in TFETs, because carriers are injected into the channel through band-to-band tunneling, drive current is greatly reduced.[8] While in NCFETs, ferroelectric materials are prone to fatigue in the electric field, so the applications are affected by long-term stability.<sup>[9]</sup> Therefore, fabricating FETs with ultrahigh on-off ratio and ultra-low SS is an urgent issue for lowpower circuits. Collective interactions in functional materials potentially enable augment current of state-of-the-art transistors, which provides unique routes to overcome conventional limits for high-performance devices. Insulator-to-metal transition threshold switch (TS) with connection with FET was previously reported, and realized abrupt resistivity switching for steep-slope operation and demonstrates SS below 60 mV dec<sup>-1</sup> at room temperature. However, due to the series connection of the memristor and transistor, high drive voltage and low on-state output current are needed.[10-12]

Herein, black phosphorus (BP)-based filamentary TS resistive gate (RG) is integrated on top of a top-gated MoS<sub>2</sub> FETs, in which atomic-scale filament formation/dissolution (in the gate region) can be induced by a low triggering voltage. Therefore, RG-FETs exhibit ultra-steep slope and demonstrate SS below 1 mV dec<sup>-1</sup> at room temperature. By rationally designing threshold voltage

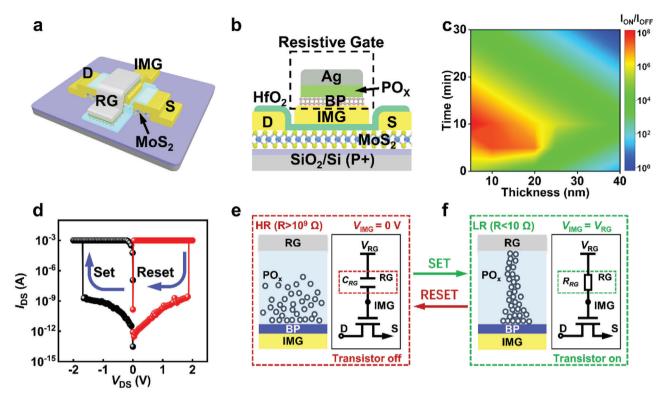

**Figure 1.** Schematic image and mechanism illustration of the ultra-steep-slope MoS<sub>2</sub> RG-FETs. a) Schematic image of the MoS<sub>2</sub> RG-FETs. b) Cross-sectional illustration of MoS<sub>2</sub> RG-FETs. c) 2D plot of the relationship between TS versus ozone treatment time (*Y*-axis) and the thickness of BP (*X*-axis) that influence on/off ratio of MoS<sub>2</sub> RG-FETs. d) Typical *I–V* characteristics of BP memristor. e) Operation principle of the RG-FETs.

$(V_{\rm TH})$  of common MoS $_2$  transistors with HfO $_2$  dielectric layer, gate potential from RG can readily exceed  $V_{\rm TH}$ . Although the conduction current of RG-FETs is still dominated by carrier injection over potential barrier like MOSFET, abrupt resistance transition of the TS leads to obvious change of the internal metal gate (IMG) voltage, leading to ultra-low SS. Therefore, it could overcome fundamental thermionic limitation and maintain competitive on-current with that of MoS $_2$  MOSFETs.

#### 2. Results and Discussion

#### 2.1. RG-FETs Fabrication

Figure 1a schematically presents the device structure of MoS<sub>2</sub> RG-FETs. Mechanical-exfoliated MoS<sub>2</sub> flakes with thickness of three to five layers are selected as the channel to ensure high carrier mobility and low contact resistance.<sup>[13,14]</sup> Figure 1b exhibits the cross-sectional view of MoS<sub>2</sub> RG-FETs, and fabrication processes are detailed in the Supporting Information (Figure S1, Supporting Information). The BP/PO<sub>x</sub> TS is formed by oxidation of 10 nm BP flake via ozone treatment.<sup>[15]</sup> Large on—off ratio and low transition voltage of TS are essential for abruptly changing IMG potential. Figure 1c illustrates the dependence of ozone treatment time and BP thickness on the on/off ratio of the TS, and 10 nm BP with 10 min ozone treatment is selected as the TS layer. The resistive characteristics of BP TS are shown in Figure 1d. And the retention and endurance characteristics are present in the Supporting Information (Figure S2, Supporting

Information), indicating high reliability and reproducibility. To illustrate the formation principle of two current states, Figure 1e plots formation/rupture of conductive filament and corresponding equivalent circuit diagram. Briefly, at low external voltage below the transition voltage of BP memristor, there is no current path formed in the BP oxide or the TS has been ruptured. The memristor is in high resistance state (HRS) and presents a high resistance over  $10^9\,\Omega$ , and thus the IMG is insulated from the external gate. Therefore, the transistor is in off-state. When a high voltage above the transition voltage of BP-based memristor, the formation of TS makes the BP oxide to have a low resistance below  $10\,\Omega$  at low resistance state (LRS). At this time, the IMG potential is nearly equivalent to the external gate voltage, and thus the transistor is on, as shown in Figure 1f.

#### 2.2. Mechanism and Electrical Performance of the RG-FETs

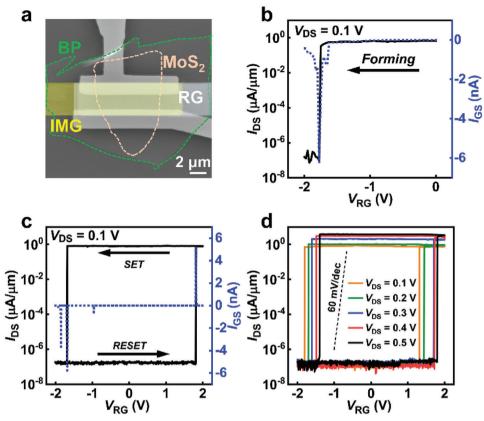

Typical scanning electron microscope (SEM) image of MoS $_2$  RG-FETs is shown in **Figure 2a**. The resistive switching effect of the TS is caused by redox reactions, which leads to the formation and rupture of a few nanometers thin conductive filament connecting RG and IMG electrodes, and the oxygen vacancies play a critical role. As shown in Figure 2b, the source—drain bias ( $V_{\rm DS}$ ) is kept at 0.1 V and the voltage applied on RG ( $V_{\rm RG}$ ) sweeps from 0 to –2.0 V. At beginning, the initial channel current ( $I_{\rm DS}$ ) is 1  $\mu$ A  $\mu$ m $^{-1}$  when  $V_{\rm RG}=0$  V and sharply decreases to  $10^{-7}~\mu$ A  $\mu$ m $^{-1}$  when  $V_{\rm RG}=-1.75$  V. At the same time, the gate current ( $I_{\rm GS}$ ) has the

www.advancedsciencenews.com

**Figure 2.** Electrical performance of the MoS<sub>2</sub> RG-FETs. a) Scanning electron microscope (SEM) image of the MoS<sub>2</sub> RG-FETs, and the scale bar is 2  $\mu$ m. b) The transfer characteristic of the MoS<sub>2</sub> RG-FETs during the forming process of TS. The blue dash dots present the gate current of the transistor. c) The transfer characteristic of the MoS<sub>2</sub> RG-FETs as the TS transits from "SET" to "RESET," and the blue dash dots are the gate current of the transistor. d) The transfer characteristic of the MoS<sub>2</sub> RG-FETs with different source–drain voltage ( $V_{DS}$ ).

same trend as  $I_{\mathrm{DS}}$ , which proves that ultra-steep slope is achieved by conductive filament formation and rupture, as shown in Figure 2b. Forward and backward sweep is applied on device in the range between -2 and 2 V, as shown in Figure 2c. When resistance state of the TS transforms from LRS to HRS, corresponding to the "RESET" process of the TS,  $I_{\rm DS}$  is rapidly drawn back to high level. When resistance state of the TS transforms from HRS back to LRS, corresponding to the "SET" process of the TS,  $I_{DS}$ abruptly drops down to low level. That is because oxygen vacancies accumulation induces conductive filament formation, and the IMG voltage approaches to the external RG voltage. By using ultra-thin HfO<sub>2</sub> as dielectric layer, the  $V_{TH}$  of the MoS<sub>2</sub> FETs is -0.7 V (Figure S3, Supporting Information), which can afford IMG voltage suddenly transitions between high and low voltage level. Figure 2d shows the transfer characteristics of MoS2 RG-FETs with different  $V_{DS}$ . Both  $V_{TH}$  and on/off ratio increase with  $V_{\rm DS}$ , which is induced by disproportionate increment of the IMG voltage from the external RG.

## 2.3. Statistical Analysis of ${\rm MoS_2}$ RG-FET and Performance Comparison

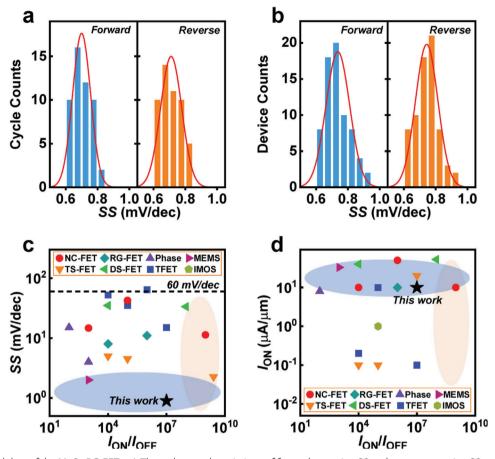

Statistical analysis can illustrate the reliability and reproducibility of MoS<sub>2</sub> RG-FETs. The statistical analysis for the forward and

reverse SS is conducted in cycle-to-cycle (50 cycles) and deviceto-device (70 devices) at  $V_{DS} = 0.1$  V, as shown in Figure 3a,b, respectively. The extracted SS is concentrated on a very small region, from 0.6 to 1.0 mV dec<sup>-1</sup>, which means that abrupt switching behavior of RG-FETs has minimized cycle-to-cycle variations and device-to-device deviations, indicating high stability and uniformity. The Gaussian distributions of forward and reverse SS in Figure 3a,b show the average SS values of 0.7 and 0.71 mV dec<sup>-1</sup> in cycle-to-cycle test and 0.73 and 0.74 mV dec<sup>-1</sup> in device-to-device deviation. Figure S4a in the Supporting Information shows cycle-to-cycle variation of channel current with consecutive "RESET" operations. Figure S4b in the Supporting Information is the dependence of  $I_{ON}$  (y-axis) and  $V_{TH}$  (x-axis) on  $V_{\rm DS}.$  Figure S4c in the Supporting Information shows relationship between  $V_{\rm RG}$  and on/off ratio. All of these indicate the RG-FETs obtain robust stability and reliability. The performance comparison among the steep-slope transistors is shown in Figure 3c,d. Compared with other classical low SS prototype devices, including TFETs,[16-20] impact-ionization FETs (IMOS-FETs),[21] Dirac-source FETs (DS-FET),[8,9] phase-transition FET (phase-FETs),[22,23] resistive-switching FETs (TS-FETs),[10,24,25] NC-FETs,[26-28] nano-electro-mechanical FETs (NEM-FETs),[29] RG-FETs,[11,12] this work presents extremely steep SS below 1 mV  $dec^{-1}$  and high switching ratio of 2.76  $\times$  10<sup>7</sup>, indicating MoS<sub>2</sub> RG-FETs are promising for high-performance low-power electronics.

www.advancedsciencenews.com

Open Access

**Figure 3.** Statistical data of the MoS<sub>2</sub> RG-FETs. a) The cycle-to-cycle variations of forward sweeping SS and reverse sweeping SS at  $V_{DS} = 0.1 \text{ V. b}$ ) The device-to-device deviations of forward sweeping SS and reverse sweeping SS at  $V_{DS} = 0.1 \text{ V. c,d}$ ) SS and  $I_{ON}$  comparisons of various steep-slope FETs, respectively, including TFETs, [16–20] impact-ionization FETs (IMOS-FETs), [21] Dirac-source FETs (DS-FET), [8,9] phase-transition FET (phase-FETs), resistive-switching FETs (TS-FETs), 10,24,25] NC-FETs, 126–28] nano-electro-mechanical FETs (NEM-FETs), 129 RG-FETs, 111,121 and this work.

#### 2.4. Ultra-High Gain Inverter

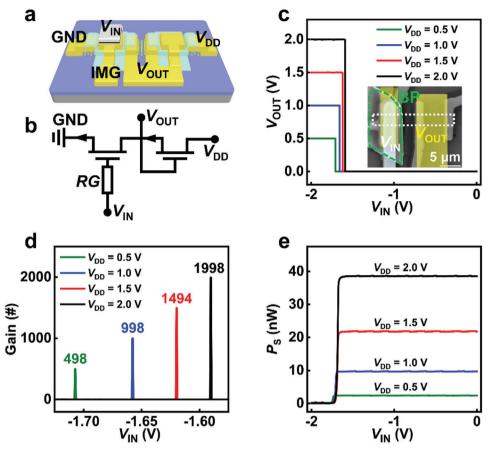

Direct-coupled FET logic technology is alternative architecture for constructing low-power circuit.[30] Based on the ultra-high and super-steep on/off ratio, an ultra-high gain inverter is fabricated. As shown in Figure 4a, MoS<sub>2</sub> RG-FET with channel length of 0.5 µm serves as the switch of inverter, and the load is realized by common MoS<sub>2</sub> FETs working at saturation state. This inverter is completed by connecting the load transistor (connected to  $V_{\rm DD}$ ) and switch transistor in series. The connection between switch transistor and load transistor gate acts as the output terminal, as shown in Figure 4b. Figure 4c shows electrical performance of the inverter at different  $V_{\rm DD}$ , the input voltage  $(V_{\rm IN})$ sweeps from 0 to -2 V (100 step s<sup>-1</sup> with a voltage span of 0.5 mV per step), and the inset is corresponding SEM image. With ultra-steep-slope characteristic of MoS2 RG-FETs, abruptly turn on of the switch MoS2 RG-FETs leads to ultra-sharp transition between high and low level of the inverter. Figure 4d indicates voltage gain of the inverter, and an ultra-high gain of 1998 at  $V_{\rm DD}$ = 2.0 V is obtained, representing a highest value among the previously reported 2D materials-based inverters.<sup>[2]</sup> Besides high voltage gain, Figure 4d shows that the inverter has ultra-low dynamic power consumption ( $P_{\rm S} = V_{\rm DD} \times I_{\rm DD}$ ) and its power consumption

is less than 40 nW at  $V_{\rm DD}=2.0$  V. The static power consumption is calculated by  $P_{\rm s}=V_{\rm s}^{~2}/(R_{\rm L}+R_{\rm on}),^{[31]}$  where  $R_{\rm L}$  and  $R_{\rm on}$  are load resistance and resistance of RG-FETs, respectively. At high input level, the static power consumption is equal to  $P_{\rm s}=V_{\rm s}^{~2}/R_{\rm L}$ , so its maximum static power consumption is about 0.2 nW at  $V_{\rm DD}=2.0$  V. While at low input level, there is only leakage current in the inverter, so the static power consumption is equal to 0 W. Moreover, by thinning the dielectric layer thickness and reducing the transition voltage of TS, the hysteresis and  $V_{\rm TH}$  of the RG-FETs can be further optimized. All of these indicate the fabricated RG-FETs are promising for high-performance low-power electronics.

#### 3. Conclusions

In summary, ultra-steep-slope MoS<sub>2</sub> RG-FETs are constructed by introducing atomic resistive gate that is connected with the IMG. The devices exhibit an ultra-low SS value below 1 mV dec<sup>-1</sup> at room temperature, indicating superior reliability and reproducibility. Based on abruptly switching characteristic of MoS<sub>2</sub> RG-FETs, high-performance inverters with 1998 voltage gain are obtained. Because the proposed strategy still relies on carrier injection mechanism, fabrication processes are compatible with

**Figure 4.** Ultra-high gain inverter based on MoS<sub>2</sub> RG-FETs. a) Schematic image of the inverter. b) Circuit diagram of the inverter based on MoS<sub>2</sub> RG-FETs. c) Electrical performance of the inverter at different applied voltage ( $V_{\rm DD}$ ). The inset is the corresponding SEM image. d) Voltage gain of the inverter at different  $V_{\rm DD}$ . e) Dynamic power consumption ( $P_{\rm d}$ ) as a function of the input voltage  $V_{\rm IN}$  under different  $V_{\rm DD}$ .

traditional planner processes. Therefore,  $MoS_2$  RG-FETs show the potential of promising candidate for future monolithic integration and advanced low-power electronics.

ments of the transistors were performed on a probe station equipped with Agilent B1500A semiconductor parameter analyzer under a vacuum environment.

#### 4. Experimental Section

Device Fabrication: 5 nm thick MoS<sub>2</sub> nanoflakes were exfoliated mechanically with Scotch tape and transferred on silicon (Si) substrates with a thermally grown 300 nm thick SiO<sub>2</sub> layer. And copolymer was spin-coated at a speed of 3000 rpm and was baked on a hot plate at 150 °C for 1 min, and then polymethyl methacrylate 495k was spin-coated at 3000 rpm and baked at 150  $^{\circ}\text{C}$  for 5 min. Subsequently, the source and drain contact regions of MoS<sub>2</sub> RG-FETs were defined by a standard electron-beam lithography (EBL), followed by thermal evaporation of Cr/Au (10/30 nm), and lift-off process. Then, 5 nm thick dielectric HfO2 layer was prepared via atomic layer deposition. The IMG electrodes of the MoS2 FETs were fabricated by a second EBL process, metallization of Au (30 nm), and lift-off process. After that, 10 nm thick BP was transferred onto the IMG electrode by a physical dry transfer process, followed by 5 min ozone treatment to form an ultra-thin resistive oxide onto the surface. Finally, the resistive gate electrodes of MoS<sub>2</sub> RG-FETs were defined at the desired position by a third EBL process, metallization of Ag (100 nm), and lift-off process.

Materials Characterization and Electrical Measurements: SEM images were conducted on JOEL IT300 operated at 20 kV, and the EBL was carried out on a Raith pattern generator SEM combination. Electrical measure-

#### **Supporting Information**

Supporting Information is available from the Wiley Online Library or from the author.

#### **Acknowledgements**

J.L. and X.C. contributed equally to this work. This work was supported by the National Key Research and Development Program of Ministry of Science and Technology (no. 2018YFA0703700), China National Funds for Distinguished Young Scientists Grant 61925403, the National Natural Science Foundation of China (grant nos. 61851403, 51872084, and 61704051), Natural Science Foundation of Hunan Province (grant nos. 2021JJ20028, 2020JJ1002), and in partly by the Key Research and Development Plan of Hunan Province under Grant (nos. 2022WK2001, 2018GK2064).

#### **Conflict of Interest**

The authors declare no conflict of interest.

www.advancedsciencenews.com

www.advancedscience.com

#### **Data Availability Statement**

Research data are not shared.

#### **Keywords**

high gain, inverter, resistive gate, steep slope, threshold swing

Received: October 6, 2021 Revised: December 1, 2021 Published online: January 17, 2022

- [1] A. M. Ionescu, H. Riel, Nature 2011, 479, 329.

- [2] J. Lin, B. Wang, Z. Yang, G. Li, X. Zou, Y. Chai, X. Liu, L. Liao, Sci. Bull. 2021, 66, 777.

- [3] W. Li, H. Ning, Z. Yu, Y. Shi, X. Wang, J. Semicond. 2019, 40, 091002.

- [4] M. Chhowalla, D. Jena, H. Zhang, Nat. Rev. Mater. 2016, 1, 16052.

- [5] A. Saeidi, T. Rosca, E. Memisevic, I. Stolichnov, M. Cavalieri, L.-E. Wernersson, A. M. Ionescu, Nano Lett. 2020, 20, 3255.

- [6] S. Kim, G. Myeong, J. Park, K. Watanabe, T. Taniguchi, S. Cho, Nano Lett. 2020, 20, 3963.

- [7] M. Si, C.-J. Su, C. Jiang, N. J. Conrad, H. Zhou, K. D. Maize, G. Qiu, C.-T. Wu, A. Shakouri, M. A. Alam, P. D. Ye, Nat. Nanotechnol. 2018, 13. 24.

- [8] C. Qiu, F. Liu, L. Xu, B. Deng, M. Xiao, J. Si, L. Lin, Z. Zhang, J. Wang, H. Guo, H. Peng, L.-M. Peng, Science 2018, 361, 387.

- [9] Z. Tang, C. Liu, X. Huang, S. Zeng, L. Liu, J. Li, Y.-G. Jiang, D. W. Zhang, P. Zhou, Nano Lett. 2021, 21, 1758.

- [10] Q. Hua, G. Gao, C. Jiang, J. Yu, J. Sun, T. Zhang, B. Gao, W. Cheng, R. Liang, H. Qian, W. Hu, Q. Sun, Z. L. Wang, H. Wu, Nat. Commun. 2020, 11, 6207.

- [11] Q. Huang, R. Huang, Y. Pan, S. Tan, Y. Wang, IEEE Electron Device Lett. 2014, 35, 877.

- [12] S.-G. Kim, S.-H. Kim, G.-S. Kim, H. Jeon, T. Kim, H.-Y. Yu, Adv. Sci. **2021**, 8, 2100208.

- [13] G. Wu, S. Wu, X. Wang, Y. Chen, T. Lin, H. Shen, W. Hu, X. Meng, J. Wang, J. A. Chu, J. Semicond. 2019, 40, 092002.

- [14] J. Tan, S. Li, B. Liu, H.-M. Cheng, Small Struct. 2021, 2, 2000093.

- [15] Y. Wang, F. Wu, X. Liu, J. Lin, J.-Y. Chen, W.-W. Wu, J. Wei, Y. Liu, Q. Liu, L. Liao, Appl. Phys. Lett. 2019, 115, 193503.

- [16] T. Krishnamohan, D. Kim, S. Raghunathan, K. Saraswat, presented at IEEE Int. Electron Devices Meeting, San Francisco, CA, USA

- [17] M. Noguchi, S. Kim, M. Yokoyama, S. Ji, O. Ichikawa, T. Osada, M. Hata, M. Takenaka, S. Takagi, presented at IEEE Int. Electron Devices Meeting, Washington, DC, USA 2013.

- [18] G. H. Shin, B. Koo, H. Park, Y. Woo, J. E. Lee, S.-Y. Choi, ACS Appl. Mater. Interfaces 2018, 10, 40212.

- [19] D. Sarkar, X. Xie, W. Liu, W. Cao, J. Kang, Y. Gong, S. Kraemer, P. M. Ajayan, K. Banerjee, Nature 2015, 526, 91.

- [20] N. Oliva, J. Backman, L. Capua, M. Cavalieri, M. Luisier, A. M. Ionescu, npj 2D Mater. Appl. 2020, 4, 5.

- [21] A. Gao, Z. Zhang, L. Li, B. Zheng, C. Wang, Y. Wang, T. Cao, Y. Wang, S.-J. Liang, F. Miao, Y. Shi, X. Wang, ACS Nano 2020, 14, 434.

- [22] N. Shukla, A. V. Thathachary, A. Agrawal, H. Paik, A. Aziz, D. G. Schlom, S. K. Gupta, R. Engel-Herbert, S. A. Datta, Nat. Commun. 2015, 6, 7812.

- [23] W. A. Vitale, E. A. Casu, A. Biswas, T. Rosca, C. Alper, A. Krammer, G. V. Luong, Q.-T. Zhao, S. Mantl, A. Schüler, A. M. Ionescu, Sci. Rep. **2017**, 7, 355.

- [24] S. Lim, J. Yoo, J. Song, J. Woo, J. Park, H. Hwang, presented at IEEE Int. Electron Devices Meeting, San Francisco, CA, USA 2016.

- [25] X.-F. Wang, H. Tian, Y. Liu, S. Shen, Z. Yan, N. Deng, Y. Yang, T.-L. Ren, ACS Nano 2019, 13, 2205.

- [26] W. Song, Y. Li, K. Zhang, X. Zou, J. Wang, Y. Kong, T. Chen, C. Jiang, C. Liu, L Liao, X. Liu, IEEE Trans. Electron Devices 2019, 66, 4148

- [27] F. Wang, J. Liu, W. Huang, R. Cheng, L. Yin, J. Wang, M. Getaye, Y. Zhang, X. Zhan, C. Shan, Z. Wang, J. He, Sci. Bull. 2020, 65, 1444.

- [28] X. Liu, R. Liang, G. Gao, C. Pan, C. Jiang, Q. Xu, J. Luo, X. Zou, Z. Yang, L. Liao, Z. L. Wang, Adv. Mater. 2018, 30, 1800932.

- [29] N. Abele, R. Fritschi, K. Boucart, F. Casset, P. Ancey, A. M. Ionescu, presented at IEEE Int. Electron Devices Meeting, Washington, DC, USA 2005

- [30] W. J. Yu, . Z. Li, H. Zhou, Y. Chen, Y. Wang, Y. Huang, X. Duan, Nat. Mater. 2013, 12, 246.

- [31] A. Pezeshki, S. H. Hosseini Shokouh, P. J. Jeon, I. Shackery, J. S. Kim, I.-K. Oh, S. C. Jun, H. Kim, S. Im, ACS Nano 2016, 10, 1118.