# **UC Santa Barbara**

## **UC Santa Barbara Electronic Theses and Dissertations**

### **Title**

Self-Aligned InGaAs Channel MOS-HEMTs for High Frequency Applications

## **Permalink**

https://escholarship.org/uc/item/08t24458

#### **Author**

WHITAKER, LOGAN

#### **Publication Date**

2023

Peer reviewed|Thesis/dissertation

## UNIVERSITY OF CALIFORNIA

#### Santa Barbara

Self-Aligned InGaAs Channel MOS-HEMTs for High Frequency Applications

A dissertation submitted in partial satisfaction of the requirements for the degree Doctor of Philosophy

in

**Electrical and Computer Engineering**

by

Logan Whitaker

Committee in charge:

Professor Mark J. W. Rodwell, Chair

Professor Umesh K. Mishra

Professor Jonathan Klamkin

Professor Jim Buckwalter

December 2023

| The dissertation of Logan Whitaker is approved. |

|-------------------------------------------------|

| Professor Umesh K. Mishra                       |

| Professor Jonathan Klamkin                      |

| Professor Jim Buckwalter                        |

|                                                 |

Professor Mark J. W. Rodwell, Committee Chair

September 2023

Self-Aligned InGaAs Channel MOS-HEMTs for High Frequency Applications

Copyright © 2023

by

Logan Whitaker

#### **ACKNOWLEDGEMENTS**

My four years at UCSB were the most rewarding years of my life thus far and they could not have been possible without the countless people who have touched my life. Here I will attempt (and fail) to give them the immense amount credit they deserve.

First, I'd like to thank my committee chair Mark Rodwell for this incredible opportunity. Mark's unique background of circuits and devices provides invaluable insight into the world of electronics. More importantly, Mark's support through the rough times of the project kept me sane. I would also like to thank the rest of my committee Professor Umesh Mishra, Professor Jonathan Klamkin, and Professor Jim Buckwalter for taking the time to listen and provide feedback throughout this process.

As the last in a long line of talented transistor designers in the Rodwell group, I was only able to get this project to work with the accumulated knowledge of previous students. First, thank you to the developers of the digital III-V MOSFET process: Uttam Singisetti, Andy Carter, Sanghoon Lee, and Cheng-Ying Huang. Second, thank you to the developer of the first generation of III-V MOS-HEMTs: Brian Markman. Brians original plan to hand over process modules during the summer of 2020 was thrown out due to covid. While he could have simply said "oh well", Brian volunteered hours of

his time to chat with me. This project never would have gotten off the ground without his help. Additionally, Hsin-Ying and Yihao Fang took the time to advise me on my early processing issues even though they were on completely different projects than me. Finally, thank you to the circuits team: Ahmed Ahmed, Ali Farid, Utku Soylu, Amir Alizadeh,

Seungchan Lee, and Ceylin Bormali for teaching me about circuits in our weekly group meetings.

So many thanks are owed to the UCSB electronics community. First, the army of staff in the cleanroom that keep our world class facilities running are the lifeblood of electronics at UCSB. Thank you to Brian Thibeault for working so hard to get us back in the lab during covid. Thank you to Don Freeborn, Demis John, Biljana Stamenic, and Bill Mitchell for your help with various tools and process development.

Next, thank you to the incredible MOCVD staff: Mike Iza, Brian Carralejo, and David Whitlatch for keeping the MOCVD lab up and running. Also, a huge thank you to Simoné Tommaso Šuran Brunelli and Bei Shi from the Klamkin group for teaching me the ways of semiconductor growth.

I'd also like to thank Matt Guidry and Christopher Clymore from the Mishra Group for helping me with device testing. The vast majority of the results presented in this work were on their test set-ups with their training and guidance.

Last, I'd like to thank my girlfriend Reema. You convinced me to get on my first plane and fly across the country to follow my dream of making really small stuff; you took care of the other love of my life (my cat Lana) while I was away; and eventually you came out to California to join me on this adventure. I can never thank you enough for the emotional support you provided during my late nights and long weekends in the cleanroom.

## VITA OF Logan Whitaker September 2023

#### **EDUCATION**

| 2019 | Bachelor of Science in Electrical Engineer, The Ohio State   |

|------|--------------------------------------------------------------|

|      | University                                                   |

| 2021 | Master of Science in Electrical and Computer Engineering,    |

|      | University of California, Santa Barbara                      |

| 0.00 |                                                              |

| 2023 | Doctor of Philosophy in Electrical and Computer Engineering, |

|      | University of California, Santa Barbara                      |

#### **PUBLICATIONS**

- [1] **Logan Whitaker**, Brian Markman, Mark JW Rodwell, "Self-Aligned InGaAs Channel MOS-HEMTs for High Frequency Applications," *DRC*, 2023.

- [2] M. Rodwell, B. Markman, Y. Fang, L. Whitaker, H.-Y. Tseng and A. S. H. Ahmed, "Transistors for 100-300GHz Wireless," *DRC*, 2021.

- [3] B. Markman, S. T. Š. Brunelli, M. Guidry, L. Whitaker and M. J. Rodwell, "Lg = 40nm Composite Channel MOS-HEMT Exhibiting f $\tau$  = 420 GHz, fmax = 562 GHz," DRC, 2021.

- [4] Tyler A Growden, DF Storm, EM Cornuelle, **LM Whitaker**, Brian P Downey, WD Zhang, JW Daulton, R Molnar, ER Brown, Paul R Berger, David J Meyer, "Pulsed characteristics for high current, large area GaN/Ain resonant tunneling diodes, 2019.

- [5] Tyler A Growden, Evan M Cornuelle, David F Storm, Weidong Zhang, Elliott R Brown, **Logan M Whitaker**, Jeffrey W Daulton, Richard Molnar, David J Meyer, Paul R Berger, "930 kA/cm2 peak tunneling current density in GaN/AlN resonant tunneling diodes grown on MOCVD GaN-on-sapphire template," *Applied Physics Letters*, vol. 114, no. 20, 2019.

#### ABSTRACT

Self-Aligned InGaAs Channel MOS-HEMTs for High Frequency Applications

by

#### Logan Whitaker

This work presents the efforts pursued to improve InGaAs/InP FET technologies for high frequency applications. Self-Aligned MOS-HEMTs were developed using a sacrificial InP layer and a diluted HCl sacrificial etch. The new process removes the previous issue of misalignment in MOS-HEMT technology. In addition, the self-aligned process results in a new "V-gate" as opposed to the tradition "T-gate". This new gate technology no longer requires the bi-layer resist used in traditional HEMT technology and allowed for gate footprint scaling from 50 nm to 20 nm.

To improve processability and high frequency performance, a theory on the effects of topside link thickness on resistance, capacitance, and cut off frequency was proposed. Traditionally, HEMTs have thick link regions to keep the donor ions far from the mobile charge in the channel. This keeps scattering and resistance in the source low; however, this places more material in between the source and the gate and increases capacitance. Simply, the theory states that as transistors continue to scale, the mobility of the link becomes less dominant than the extrinsic source gate capacitance when considering optimal link thickness.

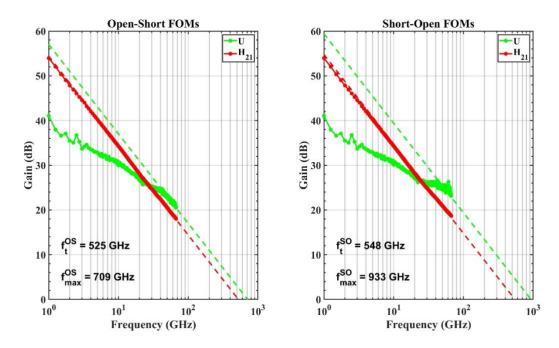

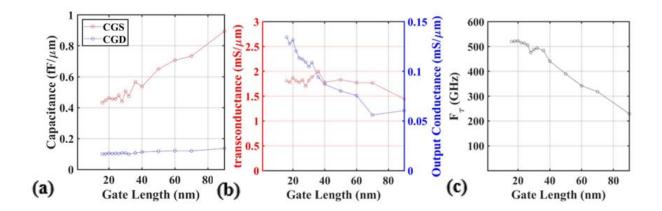

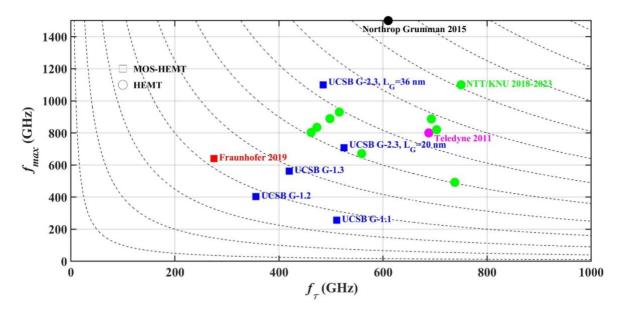

In the new process,  $C_{GS}+C_{GD}$  was reduced by a total of 40% compared to previous MOS-HEMTs. With these improvements, a  $L_g=20$  nm device, exhibiting  $f_\tau=525$  GHz,  $f_{max}=709$  GHz, and a  $L_g=36$  nm device, exhibiting  $f_\tau=479$  GHz,  $f_{max}>1$  THz were demonstrated.

# **TABLE OF CONTENTS**

|       |                                                                                                    | .ix                    |

|-------|----------------------------------------------------------------------------------------------------|------------------------|

| FIGUE | RES                                                                                                | xii                    |

| ΓABL  | ESx                                                                                                | vii                    |

| Intro | duction                                                                                            | 1                      |

| Fet T | heory and Design                                                                                   | 6                      |

| A.    | Drift-Diffusion FET Theory                                                                         | 6                      |

| B.    | Ballistic Transport                                                                                | 8                      |

| C.    | Gate Capacitance                                                                                   | 10                     |

| D.    | Gate Design                                                                                        | .12                    |

| E.    | Link Design                                                                                        | 18                     |

| RF T  | esting and Small Signal Modeling                                                                   | .24                    |

| A.    | DC-67 GHz OSLT                                                                                     | .24                    |

| B.    | Model Extraction                                                                                   | .25                    |

| Proce | essing                                                                                             | .27                    |

| A.    | Overview                                                                                           | .27                    |

| B.    | Alignment Marks                                                                                    | .27                    |

| C.    | Lithography                                                                                        | .30                    |

| D.    | First Regrowth (N+ InGaAs Contacts)                                                                | .33                    |

| E.    | Second Regrowth (Link and Sacrificial layer)                                                       | .34                    |

| F.    | Link Etching                                                                                       | 36                     |

| G.    | High-k Deposition                                                                                  | .37                    |

|       | FCOD<br>FIGURE<br>FIGURE<br>FET TA.  B.  C.  D.  E.  RF TA.  B.  Procee  A.  C.  D.  E.  Froce  F. | B. Ballistic Transport |

|    | H.   | V-Gate Deposition38                                           |

|----|------|---------------------------------------------------------------|

|    | I.   | Gate Side Walling40                                           |

|    | J.   | Sacrificial Etch                                              |

|    | K.   | Pad to Gate Finger Metal Breaks                               |

|    | L.   | Mesa Isolation45                                              |

|    | M.   | Source Drain Ohmics                                           |

|    | N.   | Passivation52                                                 |

|    | O.   | Pad Metal54                                                   |

| 5. | Gene | eration 2.155                                                 |

|    | A.   | Fabrication55                                                 |

|    | B.   | DC Results58                                                  |

|    | C.   | RF Results (Lot)60                                            |

|    | D.   | RF results, Off Wafer Calibration, DC to 67 GHz, Lg = 10 nm61 |

|    | E.   | Conclusions62                                                 |

| 6. | Gene | eration 2.264                                                 |

|    | A.   | Fabrication64                                                 |

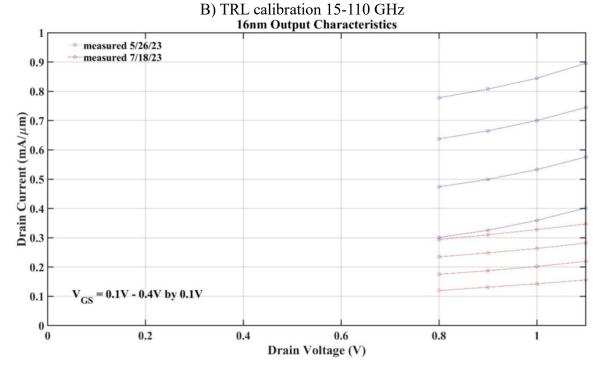

|    | B.   | DC Results67                                                  |

|    | C.   | RF Results (lot)68                                            |

|    | D.   | RF Results, Off Wafer Calibration, DC to 67 GHz, Lg = 26 nm69 |

|    | E.   | Conclusions71                                                 |

| 7. | Gene | eration 2.372                                                 |

|    | A.   | Fabrication72                                                 |

|    | B.   | DC Results                                                    |

|           | C.      | RF Results (Lot)                                             | 76 |

|-----------|---------|--------------------------------------------------------------|----|

|           | D.      | RF Results, Off Wafer Calibration, DC to 67 GHz, Lg = 20 nm? | 78 |

|           | E.      | RF Results, Off Wafer Calibration, DC to 67 GHz, Lg = 36 nm8 | 80 |

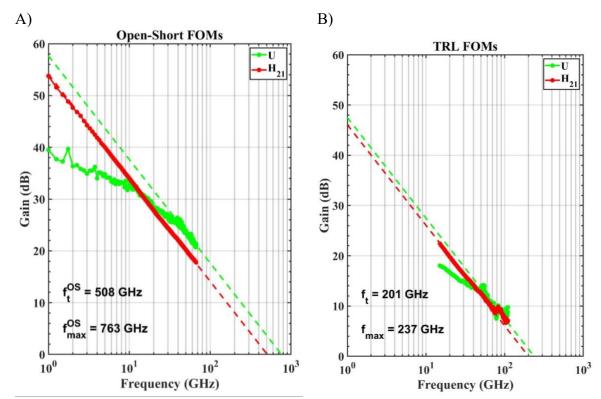

|           | F.      | RF Results, On Wafer TRL Calibration 15 to 110 GHz           | 83 |

|           | G.      | Conclusions                                                  | 86 |

| 8.        | Conc    | lusion                                                       | 88 |

|           | A.      | Summary                                                      | 88 |

|           | B.      | Future Work                                                  | 89 |

| Reference | s       |                                                              | 91 |

| Appendix  | 1 – G   | eneration 2.1 Process flow                                   | 98 |

| Appendix  | 2-Ge    | eneration 2.2 Process flow                                   | 04 |

| Appendix  | $3-G_0$ | eneration 2.3 Process flow                                   | 10 |

# **LIST OF FIGURES**

| Figure 1.1: Illustration of typical HEMT cross section                                                                      |

|-----------------------------------------------------------------------------------------------------------------------------|

| Figure 1.2: Illustration of MOS-HEMT cross section by Markmen et al                                                         |

| Figure 1.3: Illustration of self-align MOS-HEMT cross section proposed in this work4                                        |

| Figure 2.1: Transmission line model for gate resistance                                                                     |

| Figure 2.2: Geometric illustration of T-gate                                                                                |

| Figure 2.3: Geometric illustration of V-gate cross section                                                                  |

| Figure 2.4: Vertical gate resistance component vs gate length for different gate stem angles                                |

|                                                                                                                             |

| Figure 2.5: Vertical, lateral, and total gate resistance vs gate width for a) $L_{gate} = 25$ nm, $\theta =$                |

| 90° b) $L_{gate} = 25$ nm, $\theta = 45$ ° c) $L_{gate} = 10$ nm, $\theta = 90$ ° d) $L_{gate} = 10$ nm, $\theta = 45$ °.17 |

| Figure 2.6: Illustration of previous MOS-HEMT link design and approximate band diagram                                      |

|                                                                                                                             |

|                                                                                                                             |

| Figure 2.7: Illustration of non-self aligned MOS-HEMT gate-link overlap                                                     |

|                                                                                                                             |

| Figure 2.7: Illustration of non-self aligned MOS-HEMT gate-link overlap19                                                   |

| Figure 2.7: Illustration of non-self aligned MOS-HEMT gate-link overlap                                                     |

| Figure 2.7: Illustration of non-self aligned MOS-HEMT gate-link overlap                                                     |

| Figure 2.7: Illustration of non-self aligned MOS-HEMT gate-link overlap                                                     |

| Figure 2.7: Illustration of non-self aligned MOS-HEMT gate-link overlap                                                     |

| Figure 2.7: Illustration of non-self aligned MOS-HEMT gate-link overlap                                                     |

| Figure 2.7: Illustration of non-self aligned MOS-HEMT gate-link overlap                                                     |

| Figure 4.5: N+ contact vs link TLM structures and results                         | 35            |

|-----------------------------------------------------------------------------------|---------------|

| Figure 4.6: Cross sectional illustration of sacrificial layer (blue) regrowth     | 35            |

| Figure 4.7: Sacrificial InP regrowth angle from RRMH-24                           | 36            |

| Figure 4.8: Illustration of gate formation cross section                          | 39            |

| Figure 4.9: FIB/SEM cross section of device with Nickel gate etching              | 40            |

| Figure 4.10: Process flow for self-aligned DC FETs by Egard et al [31]Error!      | Bookmark      |

| not defined.                                                                      |               |

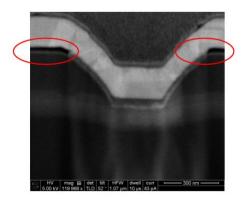

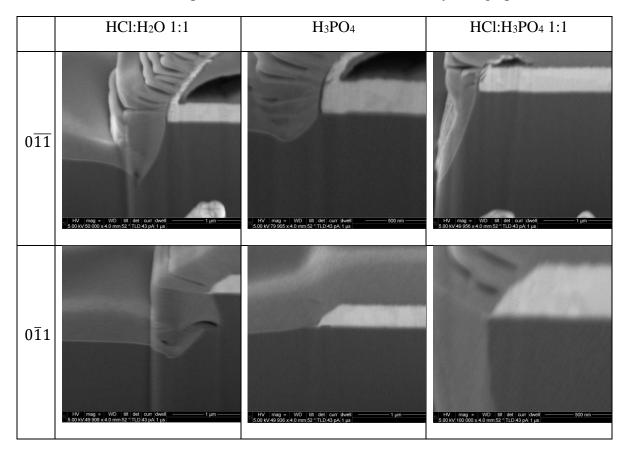

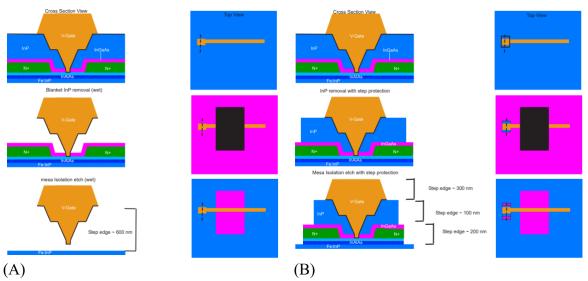

| Figure 4.11: Undercut etch profile for HCl:H2O 1:1 chemistry in the 010 direction | on .44        |

| Figure 4.12: Angled SEM of gate finger to pad metal connection void               | 44            |

| Figure 4.13: illustration of gate cross section outside of mesa (A) without       | photoresist   |

| protection (B) with photoresist protection                                        | 45            |

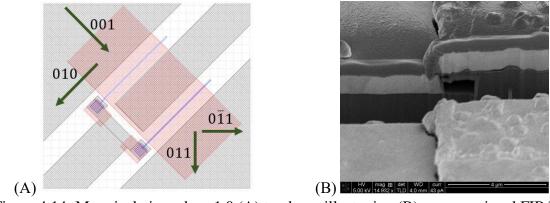

| Figure 4.14: mesa undercut A) before adhesion layer B) after adhesion layer       | 48            |

| Figure 4.15: Mesa isolation edges 1.0 (A) topdown illustration (B) cross section  | al FIB/SEM    |

|                                                                                   | 48            |

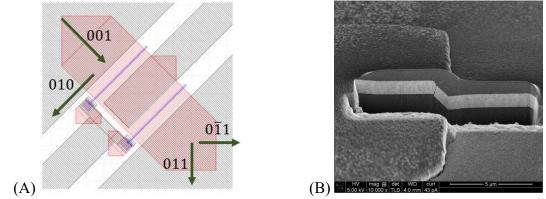

| Figure 4.16: Mesa isolation edges 2.0 (A) topdown illustration (B) cross section  | al FIB/SEM    |

|                                                                                   | 49            |

| Figure 4.17: Mesa isolation edges 2.0 angled SEM                                  | 49            |

| Figure 4.18: InP etch using photomask step edges (A) 010 oriented gate (B) 011 or | riented gates |

|                                                                                   | 50            |

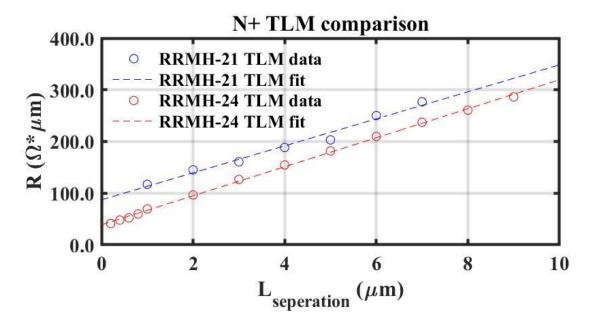

| Figure 4.19: Raw N+ TLM data for RRMH-21 (before) and RRMH-24 (after)             | 52            |

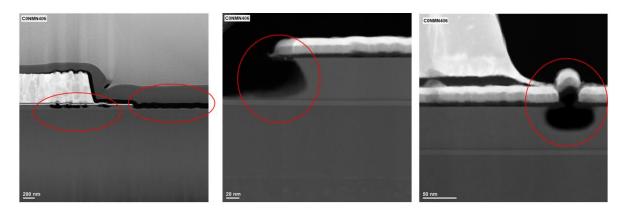

| Figure 4.20: Cross sectional TEMs of paracistic etching of N+ InGaAs              | 53            |

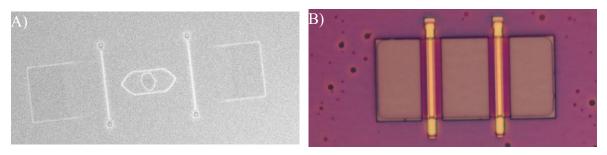

| Figure 5.1: Illustration of generation 2.1 process flow.                          | 55            |

| Figure 5.2: 3D island growth from regrowth                                        | 56            |

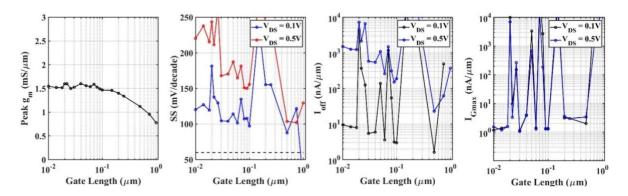

| Figure 5.3: Lot DC results for RRMH-11-Die-2-Wg-20um                                              |

|---------------------------------------------------------------------------------------------------|

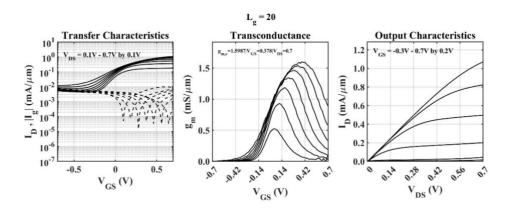

| Figure 5.4: DC characteristics for generation 2.1, $L_g$ = 20 nm, $W_g$ = 20 $\mu$ m, Die = 2.58  |

| Figure 5.5: Lot DC characteristics for generation 2.1 devices, $W_g$ = 20 $\mu$ m, Die = 2 (leaky |

| devices removed)59                                                                                |

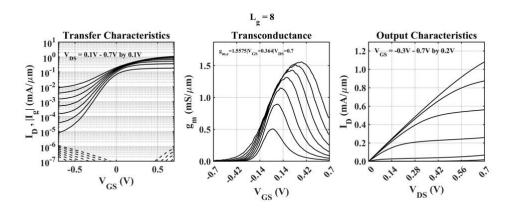

| Figure 5.6: DC characteristics for generation 2.1, $L_g = 8$ nm, $W_g = 20$ $\mu m$ , Die = 259   |

| Figure 5.7: RF FOM extraction for RRMH-11-Die-2, $W_g$ =2x20um, $Lg$ = 10 nm, $V_{GS}$ = 0.2 V,   |

| $V_{DS} = 0.7 \text{ V}60$                                                                        |

| Figure 5.8: Gate length series of extracted common-source SSEC elements for RRMH-11-              |

| Die-2, $W_g = 2x20 \text{ um}$ 61                                                                 |

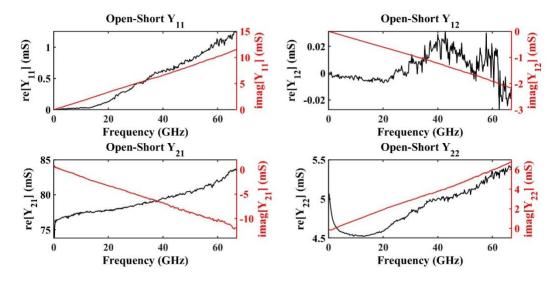

| Figure 5.9: DC to 67 GHz Y-parameters with open-short de-embedding for RRMH-11-Die-               |

| 2, $W_g$ =2x20 um, $Lg$ = 10 nm, $V_{GS}$ = 0.2 V, $V_{DS}$ = 0.7 V61                             |

| Figure 5.10: DC to 67 GHz Y-parameters with short-open de-embedding for RRMH-11-Die-              |

| 2, $W_g=2x20um$ , $Lg=10$ nm, $V_{GS}=0.2$ V, $V_{DS}=0.7$ V62                                    |

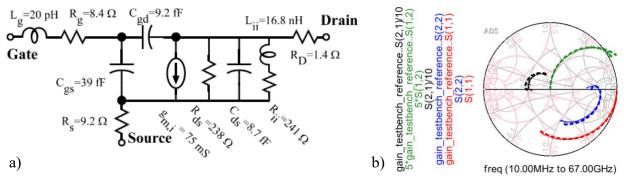

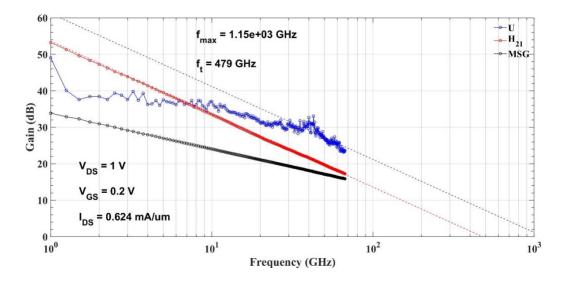

| Figure 5.11: RRMH-11-Die-2, $W_g=2x20um$ , $Lg=10$ nm, $V_{GS}=0.2$ V, $V_{DS}=0.7$ V (a)         |

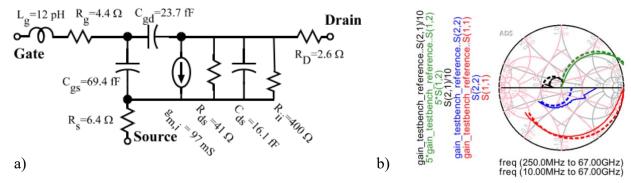

| equivalent circuit model (b) S-parameter DC to 67 GHz62                                           |

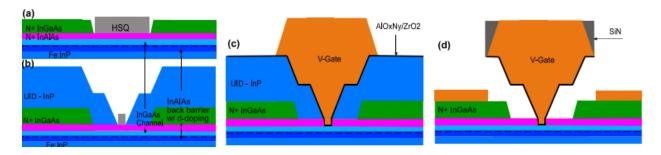

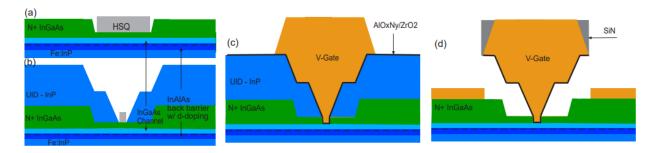

| Figure 6.1: process flow (a) Epi, dummy link, contact regrowth (b) dummy gate, sacrificial        |

| regrowth (c) etch N+ link, high-k deposition, gate metal deposition (d) high-k etch, SiN          |

| sidewall, InP removal, ohmic contact deposition64                                                 |

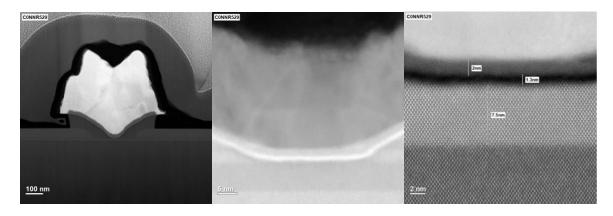

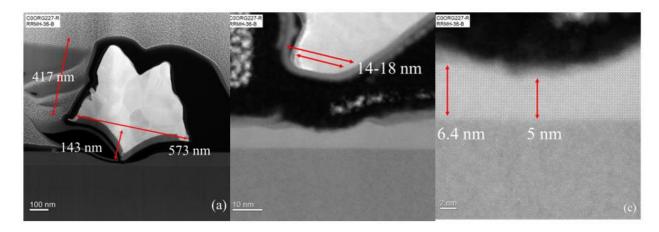

| Figure 6.2: 26 nm Lg TEM cross section. (a) full device (b) gate length (c) channel + oxide       |

| thickness65                                                                                       |

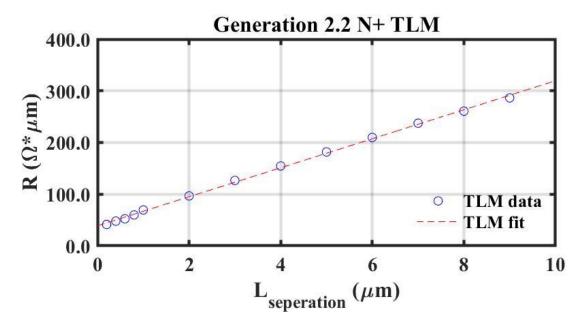

| Figure 6.3: RRMH-24 TLMs for 50 nm thick N+ InGaAs65                                              |

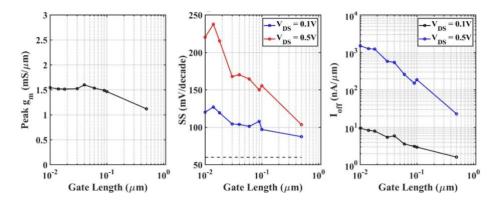

| Figure 6.4: Lot DC results for RRMH-24-Die-2-Wg-20um                                              |

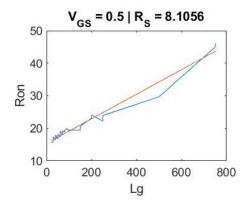

| Figure 6.5: Ron vs gate length for RRMH-24, Die 2                                                 |

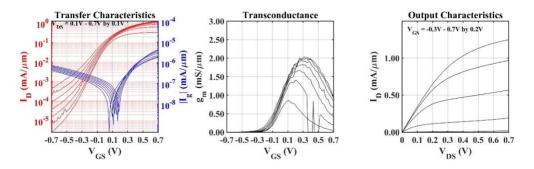

| Figure 6.6: DC results for RRMH-24-Die-2, $W_g$ =20um, $L_g$ = 42 nm68                          |

|-------------------------------------------------------------------------------------------------|

| Figure 6.7: RF FOM extraction for RRMH-24-Die-2, $W_g$ =2x10um, $Lg$ = 26 nm, $V_{GS}$ = 0.3 V, |

| $V_{DS} = 0.8 \text{ V}68$                                                                      |

| Figure 6.8: Gate length series of extracted common-source SSEC elements for RRMH-24-            |

| Die-2, $W_g = 2x10 \text{ um}$ 69                                                               |

| Figure 6.9: DC to 67 GHz Y-parameters with open-short de-embedding for RRMH-24-Die-             |

| 2, $W_g=2x10um$ , $Lg=26$ nm, $V_{GS}=0.3$ V, $V_{DS}=0.8$ V70                                  |

| Figure 6.10: DC to 67 GHz Y-parameters with open-short de-embedding for RRMH-24-Die-            |

| $2,W_g = 2x10um,Lg = 26nm,V_{GS} = 0.3V,V_{DS} = 0.8V70$                                        |

| Figure 6.11: RRMH-24-Die-2, $W_g=2x10um$ , $Lg=26$ nm, $V_{GS}=0.3$ V, $V_{DS}=0.8$ V (a)       |

| equivalent circuit model (b) S-parameter DC to 67 GHz71                                         |

| Figure 7.1: process flow (a) Epi, dummy link, contact regrowth (b) dummy gate, sacrificial      |

| regrowth (c) etch N+ link, high-k deposition, gate metal deposition (d) high-k etch, SiN        |

| sidewall, InP removal, ohmic contact deposition                                                 |

| Figure 7.2: 18 nm Lg TEM cross section. Note: the gate was dislodged from channel during        |

| FIB. (a) full device (b) gate length (c) channel thickness                                      |

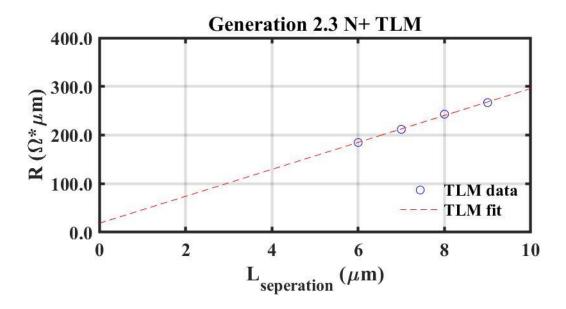

| Figure 7.3: RRMH-36 TLMs for 50 nm thick N+ InGaAs73                                            |

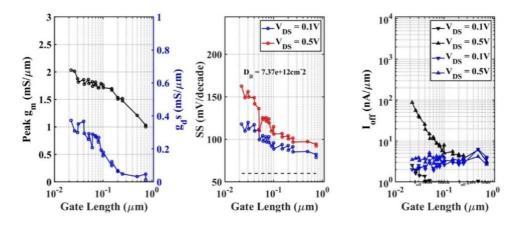

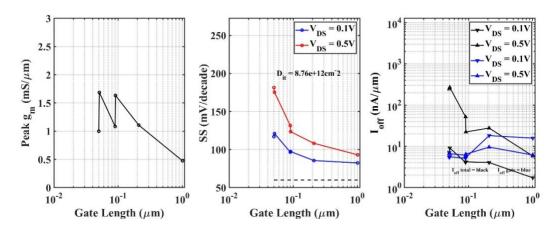

| Figure 7.4: Lot DC results for RRMH-36-Die-5-Wg-20um75                                          |

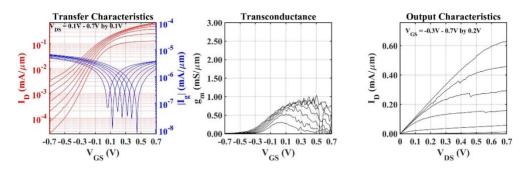

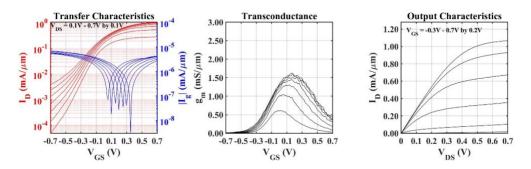

| Figure 7.5: DC results for RRMH-36-Die-5, $W_g$ =20um, $L_g$ = 30 nm (left)76                   |

| Figure 7.6: DC results for RRMH-36-Die-5, $W_g$ =20um, $Lg$ = 30 nm (right)76                   |

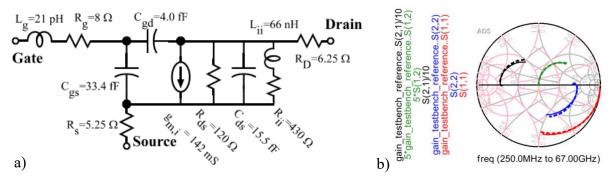

| Figure 7.7: RF FOM extraction for RRMH-36-Die-5, $W_g$ =2x20um, $Lg$ = 20 nm, $V_{GS}$ = 0.2 V, |

| $V_{DS} = 1.0 \text{ V}$                                                                        |

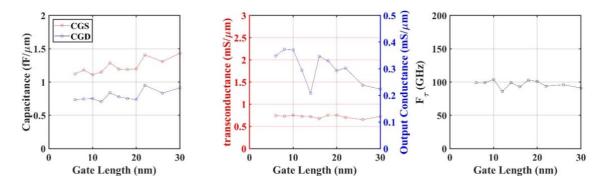

| Figure 7.8: Gate length series of extracted common-source SSEC elements for RRMH-36-             |

|--------------------------------------------------------------------------------------------------|

| Die-5, W <sub>g</sub> =2x20um78                                                                  |

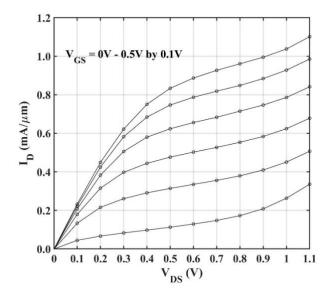

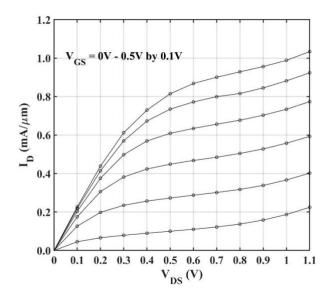

| Figure 7.9: Output characteristics for RRMH-36-Die-5, $W_g$ =2x20um, $Lg$ = 20 nm78              |

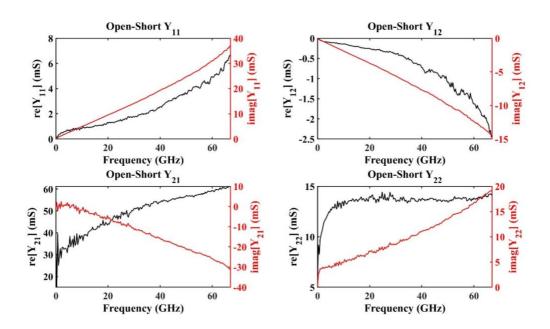

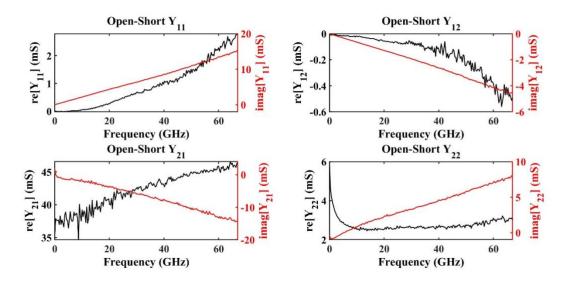

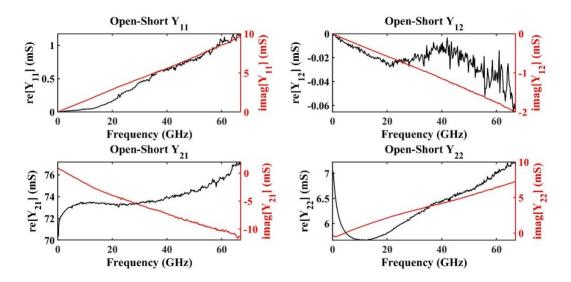

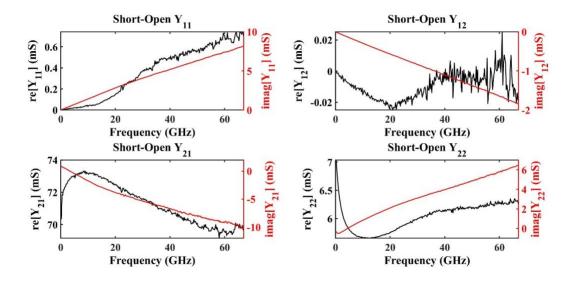

| Figure 7.10: DC to 67 GHz Y-parameters with open-short de-embedding for RRMH-36-Die-             |

| 5, $W_g=2x20um$ , $Lg=20$ nm, $V_{GS}=0.2$ V, $V_{DS}=1.0$ V                                     |

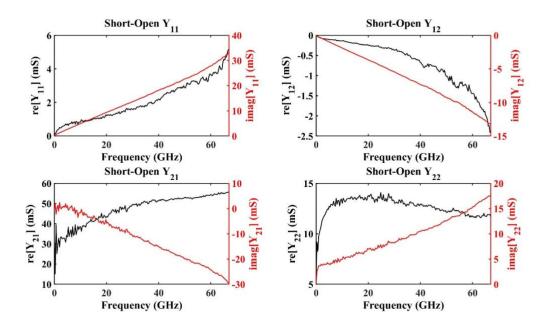

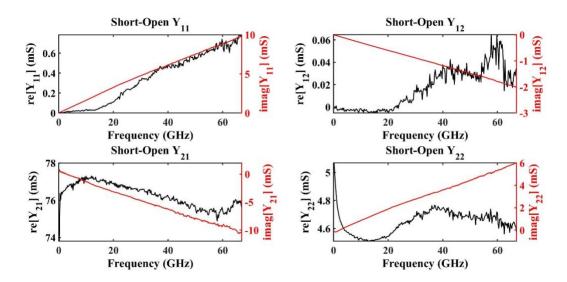

| Figure 7.11: DC to 67 GHz Y-parameters with short-open de-embedding for RRMH-36-Die-             |

| 5, $W_g=2x20um$ , $Lg=20$ nm, $V_{GS}=0.2$ V, $V_{DS}=1.0$ V                                     |

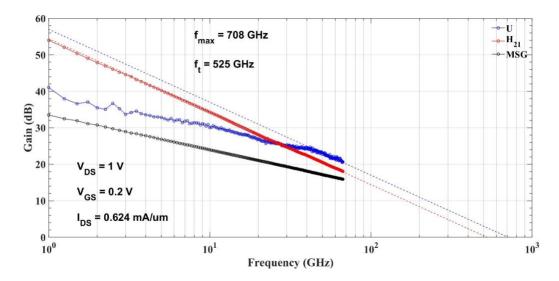

| Figure 7.12: U, $H_{21}$ , and MSG at DC to 67 GHz for RRMH-36-Die-5, $W_g$ =20um, $Lg$ = 20 nm, |

| $V_{GS} = 0.2 \text{ V}, V_{DS} = 1.0 \text{ V}$ 80                                              |

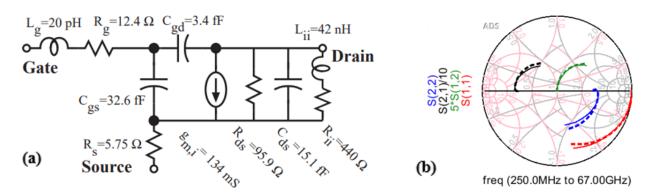

| Figure 7.13: RRMH-36-Die-5, $W_g=2x20um$ , $Lg=20$ nm, $V_{GS}=0.2$ V, $V_{DS}=1.0$ V (a)        |

| equivalent circuit model (b) S-parameter DC to 67 GHz80                                          |

| Figure 7.14: Output characteristics for RRMH-36-Die-5, $W_g$ =2x20um, $Lg$ = 36 nm 81            |

| Figure 7.15: DC to 67 GHz Y-parameters with open-short de-embedding for RRMH-36-Die-             |

| 5, $W_g$ =2x20um, $Lg$ = 36 nm, $V_{GS}$ = 0.2 V, $V_{DS}$ = 0.9 V81                             |

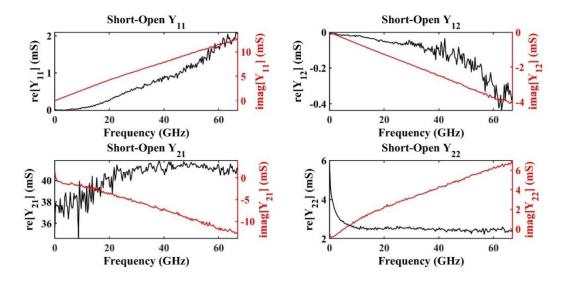

| Figure 7.16: DC to 67 GHz Y-parameters with short-open de-embedding for RRMH-36-Die-             |

| 5, $W_g$ =2x20um, $Lg$ = 36 nm, $V_{GS}$ = 0.2 V, $V_{DS}$ = 0.9 V82                             |

| Figure 7.17: U, $H_{21}$ , and MSG at DC to 67 GHz for RRMH-36-Die-5, $W_g$ =2x20um, $Lg$ = 36   |

| nm, $V_{GS} = 0.2 \text{ V}$ , $V_{DS} = 0.9 \text{ V}$ 82                                       |

| Figure 7.18: RRMH-36-Die-5, $W_g$ =40um, $Lg = 36$ nm, $V_{GS} = 0.2$ V, $V_{DS} = 0.9$ V (a)    |

| equivalent circuit model (b) S-parameter DC to 67 GHz83                                          |

| Figure 8.1: High Frequency Figures of Merit for state of the art MOS-HEMTs and                   |

| HEMTs88                                                                                          |

# **LIST OF TABLES**

| Table 2.1: Predicted change in total capacitance for a 4 nm thick link                | 21        |

|---------------------------------------------------------------------------------------|-----------|

| Table 2.2: Predicted change for total source resistance and its effect on             | extrinsic |

| transconductance                                                                      | 23        |

| Table 4.1: Undercut etch profiles for different chemistries and crystallographic dire | ections43 |

| Table 4.2: N+ TLM results for RRMH-21 (before) and RRMH-24 (after)                    | 52        |

| Table 5.1: TLM data for generation 2.1                                                | 57        |

| Table 6.1: RRMH-24 TLM results for 50 nm thick N+ InGaAs                              | 66        |

| Table 7.1: RRMH-36 TLM results for 50 nm thick N+ InGaAs                              | 74        |

## 1. Introduction

As consumers demand higher bandwidth and higher data rates, industry is rolling out 5G communication in the 20-80 GHz regime. While industry works to meet the demand of consumers today, researchers must explore design challenges to expand to >100 GHz communication for the future [1]. Communication at higher frequencies requires amplifiers that exhibit gain at these high frequencies. Because transistor gain rolls off at 20 dB/decade at high frequencies, it is advantageous to build amplifiers with cutoff frequencies ( $f_{\tau}$ ,  $f_{max}$ ) much greater than the operating frequency of the system.

This work is specifically focused on developing transistors with low noise characteristics for Low Noise Amplifiers (LNAs), for which Field Effect Transistors (FETs) are the preferred device. FETs outperform Heterojunction Bipolar Transistors (HBTs) in noise performance because of their lower parasitic resistances ([R<sub>S</sub>+R<sub>G</sub>]\*g<sub>m</sub><R<sub>bb</sub>\*g<sub>m</sub>). Current state of the art LNAs utilize a High Mobility Electron Transistor (HEMT) using an InGaAs channel on an InP substrate [2, 3]. The low effective mass InGaAs channel allows high injection velocity ( $v_{inj}$ ) and therefore high transconductance ( $g_m$ ) [4]. State of the art HEMTs optimized for  $f_{\tau}$  exhibit  $f_{\tau}$  = 750 GHz,  $f_{max}$  = 1.1 THz, and HEMTs optimized for  $f_{max}$  exhibit  $f_{\tau}$  = 610 GHz,  $f_{max}$  = 1.5 THz [2, 3].

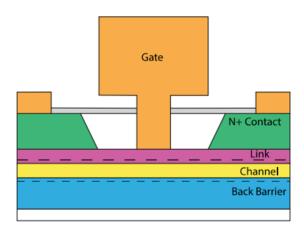

Figure 1.1: Illustration of typical HEMT cross section

Previous improvements in RF performance were attained by scaling transistor gate lengths (L<sub>g</sub>). Scaling the transistor gate length improves performance by minimizing the intrinsic transit time but has the unintended effect of reducing the gate to channel capacitance  $\left(C_{G-ch} = L_g \left[\frac{t_b}{\epsilon_b} + \frac{t_{ch}}{2\epsilon_{ch}}\right]^{-1}\right)$ . Output conductance (g<sub>ds</sub>) is roughly proportional to the ratio of the gate to channel capacitance and drain to channel capacitance ( $C_{G-ch}/C_{D-ch}$ ) at short gate lengths. Because C<sub>G-ch</sub> does not scale with gate length, decreasing gate length by itself can dramatically increase output conductance.

Intelligent designers developed and followed scaling laws to maintain good output conductance as gate lengths scaled [5]. These scaling laws state that if the gate length is cut in half the gate insulator must also be cut in half to maintain channel capacitance and therefore output conductance. Unfortunately, state of the art HEMTs use an InAlAs barrier that has already been aggressively scaled to sub 5 nm thickness. Further scaling of the barrier would result in unacceptable amounts of gate leakage [6]. To address this problem, a new barrier with a larger bandgap and/or a larger dielectric constant would be advantageous.

Work in the Rodwell group from 2009 to 2015 utilized insulators with higher dielectric constants known as "high-k" materials such as Hafnium oxide (HfO<sub>2</sub>) and Zirconium oxide (ZrO<sub>2</sub>) to build highly scaled transistors for digital applications. These materials provided bandgaps greater than 5.0 eV that allowed sub 3 nm insulator scaling. Additionally, dielectric constants greater than 20 resulted in even high gate to channel capacitances. Because these devices were optimized for digital circuits, die area was of upmost importance [7, 8, 9, 10]. Large gate-contact overlap capacitances prevent these devices from overtaking the state-of-the-art HEMTs for high frequency applications.

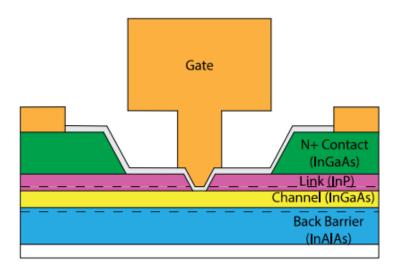

To combine the benefits of the high-k with the low capacitance of a HEMT, a MOS-HEMT design was created like illustrated in Figure 1.2 [11]. Markman *et al* reported extrinsic transconductance on par with the state of the art ( $g_{me} \sim 3$  mS/ $\mu$ m) and output conductance roughly 1/3 of the state of the art ( $g_{ds} \sim 0.25$  mS/ $\mu$ m) showing the potential benefit of a MOS-HEMT. Unfortunately, large overlap capacitances resulted from the gate-link overlap limited this design to  $f_{\tau} = 400$  GHz,  $f_{max} = 600$  GHz [12].

Figure 1.2: Illustration of MOS-HEMT cross section by Markmen et al

Overlap in this design was a result of the T-gate footprint being larger than the gate opening. Because T-gate stems shorter than 50 nm could not be filled with the thermal evaporator set up available, all gate openings shorter than 50 nm needed at least a 50 nm stem attached. Additionally, stems had to be aligned to the gate opening, and to allow for ~25 nm of misalignment in either direction, the gate stems had to be 50 nm larger than the gate openings to ensure complete gating of the channel.

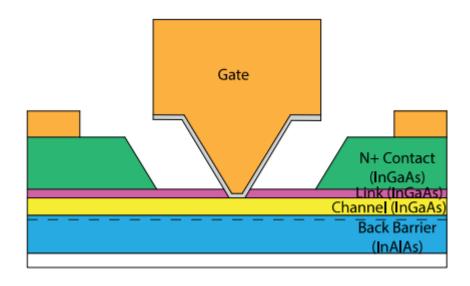

To minimize the overlap capacitance of the previous MOS-HEMT design, this thesis outlines the work to develop a self-aligned process flow and a structure that is easier to fill with metal like seen in Figure 1.3.

Figure 1.3: Illustration of self-align MOS-HEMT cross section proposed in this work

Chapter 2 (Fet Theory and Design) begins with overviews of basic FET, ballistic FET, and MOS operation. Chapter 2 also includes sections on Gate Design and Link Design within the new device structure. Chapter 3 (RF Testing and Small Signal Modeling) focuses on device testing, characterization, and modeling. Chapter 4 (Processing) overviews the process modules used to build the devices as well as various processing decisions and tradeoffs.

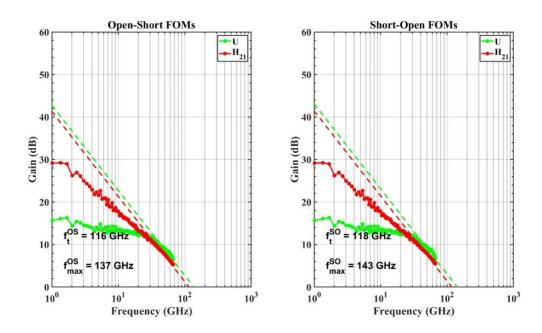

Chapter 5 (Generation 2.1) outlines efforts for the first generation of self-aligned MOS-HEMTs with a  $L_g=10$  nm device, exhibiting  $f_\tau=116$  GHz,  $f_{max}=137$  GHz. Results in these devices were extremely limited in part due to high source resistance attributed to poor link end resistance. Additionally, gate-source and gate drain capacitance was limited by incomplete remove of the InP sacrificial layer.

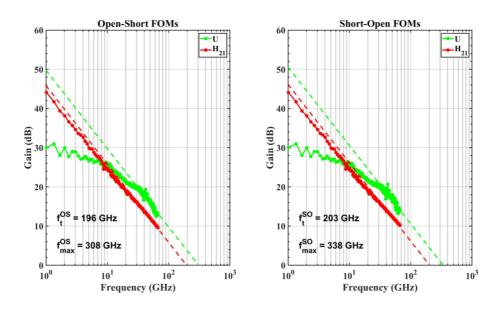

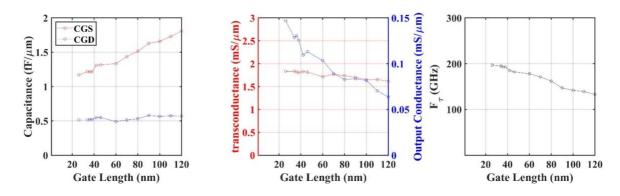

Chapter 6 (Generation 2.2) outlines the second generation of self-aligned MOS-HEMTs with a  $L_g = 26$  nm device, exhibiting  $f_\tau = 196$  GHz,  $f_{max} = 308$  GHz. The InGaAs link regrowth was replaced with an InAlAs topside barrier as a part of the epi. This reduced link end resistance by removing the nonplanar regrowth and reduced link sheet resistance by increasing charge confinement. Removal of the InP sacrificial layer proved difficult in this design because the InAlAs link etched in the HCl chemistry.

Chapter 7 (Generation 2.3) outlines the third generation of self-aligned MOS-HEMTs with a  $L_g = 20$  nm device, exhibiting  $f_\tau = 525$  GHz,  $f_{max} = 709$  GHz, and a  $L_g = 36$  nm device, exhibiting  $f_\tau = 479$  GHz,  $f_{max} > 1$  THz. The InAlAs link was switched back to InGaAs to improve etch selectivity (as in Generation 2.1), but the deposition method was kept the same as Generation 2.2. Additionally, gates were rotated 45 degrees to increase InP undercut etching. Complete removal of the InP resulted in significant improvements in C<sub>GS</sub> and C<sub>GD</sub>.

Chapter 8 (Conclusion) summarizes the theoretical and experimental work outlined in this thesis. It also compares results to other work on MOS-HEMTs and HEMTs and gives an avenue for future performance improvements within this technology.

## 2. Fet Theory and Design

In this chapter, FET theory and design will be discussed. FET theory will start with traditional long gate length theory and then build into the ballistic limit. Next, individual design parameters, specifically the gate and link, will be discussed along with their relation to relevant equivalent circuit parameters and their effect on total RF performance.

## A. Drift-Diffusion FET Theory

Field effect transistors (FETs) are variable resistors whose conductance from source to drain is controlled by applying voltage at the gate electrode. Applying a gate voltage increases charge on the surface of the metal gate which then induces opposite charge in the channel.

For the sake of clarity, an nMOS device will be discussed; therefore, a positive bias is applied to positively charge the gate and induce negative charge in the channel. Current in a FET is dominated by the drift of majority carriers due to an electric field between the source and drain, and in general, is equal to the charge times its velocity.

$$I_D(x) = Q_n(x) * v_n(x)$$

(2.1)

The velocity and charge are easiest to determine in the "ohmic" or "linear" region of operation, when  $V_{GS} > V_{th}$ , and  $V_{DS}$  is positive but less than  $V_{GS} - V_{th}$ . The charge at any point under the channel is equal to the capacitance times the voltage at that point.

$$Q_n(x) = q * C_{gs} (V_{gs} - V_{th} - V(x))$$

(2.2)

For a long gate length device, the velocity can be estimated using the mobility of the channel and the electric field at that given point.

$$v_n(x) = \mu_n \frac{dV(x)}{dx} \tag{2.3}$$

Plugging in equations (2.2) and (2.3) into (2.1), multiplying by dx, and taking the integral from x=0 to x=Lg, we can find the relationship between current density and applied biases in the linear region.

$$\int_{x=0}^{x=L} J_n = \int_{V(x=0)=0}^{V(x=L)=V_{DS}} qC_{gs} \left(V_{gs} - V_{th} - V(x)\right) \mu_n dV$$

(2.4)

$$J_n = \frac{q C_{gs} \mu_n}{L} \left[ (V_{gs} - V_{th}) V_{DS} - \frac{V_{DS}^2}{2} \right]$$

(2.5)

Current will continue to increase with increasing  $V_{DS}$  until the channel is pinched off. After pinch off, the device is in the "saturation" region. To first order, the drain current does not increase as  $V_{DS}$  is increased past  $V_{GS}$ - $V_{th}$ . Replacing  $V_{DS}$  with  $V_{GS}$ - $V_{th}$  results in the equation below.

$$J_n = \frac{qC_{gs}\mu_n}{L} \left[ \frac{\left(V_{gs} - V_{th}\right)^2}{2} \right] \tag{2.6}$$

To the second order, the drain current increases with increasing  $V_{DS}$  because of the shrinking of the effective gate length. This can be handled with the addition of another term as seen in the equation below.

$$J_{n} = \frac{qC_{gs}\mu_{n}}{L} \left[ \frac{(V_{gs} - V_{th})^{2}}{2} \right] [1 + \lambda V_{ds}]$$

(2.7)

If the gate bias is less than the threshold voltage, the device is in the "Subthreshold" region. In this region, the previous charge equation no longer applies, and the charge is now determined by thermal physics. Also, because V<sub>GS</sub> is less than V<sub>th</sub>, the channel has very few electrons and is now limited by diffusion current, not drift.

$$J_n = -q * D_n * \frac{dn}{dx}$$

(2.8)

If all current is assumed to be due to diffusion of electrons (a good approximation), then the gradient of electrons is constant and can therefore be written simply as:

$$-\frac{dn}{dx} = \frac{\Delta n(0) - \Delta n(L)}{L} = \frac{\Delta n(0)}{L} \left(1 - \exp\left(\frac{qV_{DS}}{kT}\right)\right) \tag{2.9}$$

Charge at the source edge can be related to the background doping  $(np_0)$  and the band bending  $(\psi_s)$ . Additionally, the band bending can be related to  $V_{GS}$  and  $V_{th}$  by using a constant  $\eta$  derived from the voltage divider between oxide and depletion capacitance.

$$\Delta n(0) = n_{p0} * \exp\left(\frac{\psi_s}{kT}\right) = n_{p0} * \exp\left(\frac{q(V_{GS} - V_T)}{\eta kT}\right)$$

(2.10)

Finally, combining equations (2.9) and (2.10) into equation (2.8) results in equation (2.11) below, showing how subthreshold current varies as  $V_{GS}$  and  $V_{DS}$  change.

$$J_n = \frac{n_{p0}}{L} \exp\left(\frac{q(V_{GS} - V_T)}{\eta kT}\right) \left(1 - \exp\left(\frac{qV_{DS}}{kT}\right)\right)$$

(2.11)

#### B. Ballistic Transport

State of the art transistors no longer fit into the previous assumptions, most glaringly, the mobility model used to predict velocity. As transistor gate lengths continue to shrink, the time it takes for an electron to traverse the channel decreases. As this time approaches the mean scattering time  $\tau$ , the likelihood of a scattering event taking place decreases, and the validity of the mobility model diminishes. The "Ballistic FET Model" uses the E(k) diagram to predict the injection velocity of the electron from first principles.

At peak bias conditions,  $V_{DS}$  is sufficiently large such that the fermi level at the drain is below the eigen state energy in the channel. This means that only positive k states are

populated in the direction of the electron travel. Assuming parabolic bands, the fermi energy can be related to the crystal momentum:

$$q(E_f - E_1) = \frac{\hbar^2 k_f^2}{2m^*}; k_f = \frac{\sqrt{2m^* q(E_f - E_1)}}{\hbar}$$

(2.12)

From here, the fermi velocity is by definition related to the derivative of the energy, and therefore is readily known. Additionally, the average velocity of all positively moving electrons can be estimated.

$$v_f = \frac{1}{\hbar} \frac{\partial E_f}{\partial k_f} = \frac{\hbar k_f}{m^*} \tag{2.13}$$

$$\langle v \rangle \approx \frac{4}{3\pi} * v_f = \frac{4\hbar k_f}{3\pi m^*} \tag{2.14}$$

$$\langle v \rangle \approx \sqrt{\frac{32q(E_f - E_1)}{9\pi^2 m^*}} \quad \left(\frac{meters}{second}\right)$$

(2.15)

The channel is assumed to be a one-sided infinite quantum well. The charge density in such a well is estimated by using the 2-D density of states and the zero-order Fermi-Dirac integral. The 2-D density of states is divided by 2 because only the positive k state electrons are considered.

$$n_s = \frac{N_{2D}}{2} * F_0 = \frac{N_{2D}}{2} \ln \left[ 1 + \exp\left(\frac{q(E_F - E_1)}{k_B T}\right) \right]$$

(2.16)

$$if E_f - E_1 > 3k_B T, F_0 \approx \frac{q(E_F - E_1)}{k_B T}$$

(2.17)

$$n_{s} \approx \frac{N_{2D}}{2} * \frac{q(E_f - E_1)}{k_{B}T} \tag{2.18}$$

$$N_{2D} = \frac{g_v m^* k_B T}{\pi \hbar^2}; g_v = 1 \text{ for InGaAs } \Gamma - valley$$

(2.19)

$$n_s \approx \frac{m^* q \left( E_f - E_1 \right)}{2\pi \hbar^2} \quad (meters^{-2})$$

(2.20)

Because peak bias conditions are being considered, the fermi level should be sufficiently above the first eigen state energy to apply a degenerate approximation as seen in equation (2.17). When the 2-D density of states from equation (2.19) is plugged into equation (2.18), the resulting charge density formula in equation (2.20) is a function of fermi level and material parameters. Using the drift equation from the previous section, along with the charge density and average electron velocity, the current density as a function of fermi level can be written as:

$$J = q\langle v \rangle n_s = \frac{q}{\hbar^2 \pi^2} \sqrt{\frac{8m^*}{9} \left( q(E_f - E_1) \right)^3} \left( \frac{Amperes}{meter} \right)$$

(2.21)

The current in this equation is limited by the effective mass in the quantum well as well as the maximum allowable gate overdrive  $(E_f - E_1)$  before:

- The fermi-level reaches the top of the back barrier and populates a parallel 2-DEG.

or

- 2. Intervalley scattering.

### C. Gate Capacitance

To relate the fermi level in the channel to the gate voltage, the gate to source capacitance must first be understood. The gate to source capacitance in these devices can be understood as three capacitors in series: insulator capacitance, quantum well capacitance, and density of states capacitance. The insulator capacitance is the parallel plate capacitance from the gate insulator, and in this work, it is the series capacitance of two different oxides.

$$C_{ins} = \frac{\epsilon_{ins}}{t_{or}} \tag{2.22}$$

The quantum well capacitance, also commonly known as the wave function capacitance, accounts for the distance between the edge of the insulator and the center of the charge distribution in the channel. The center of the charge distribution is assumed to be at the center of the channel for simplicity. The quantum well capacitance is effectively another oxide capacitance where the dielectric is half of the channel semiconductor.

$$C_{QW} = \frac{\epsilon_{ch}}{t_{ch}/2} \tag{2.23}$$

The density of states capacitance accounts for the moving of the fermi level as additional charge is provided to the channel. At peak bias conditions, the previous assumptions about channel charge are still valid here.

$$C_{DOS} = \frac{\partial (-qn_s)}{\partial (E_f - E_1)} = \frac{\partial}{\partial (E_f - E_1)} \left[ \frac{m^* q^2 (E_f - E_1)}{2\pi \hbar^2} \right] = \frac{m^* q^2}{2\pi \hbar^2} \left( \frac{F}{m^2} \right)$$

(2.24)

Now the gate overdrive can be related to the applied gate bias as a function of C<sub>DOS</sub> and C<sub>EET</sub> (the remaining series capacitors) and plugged back into equation (2.21) to find ballistic current as a function of gate voltage.

$$E_f - E_1 = \frac{C_{EET}}{C_{EET} + C_{DOS}} * (V_{GS} - V_{th})$$

(2.25)

$$C_{EET} = \frac{C_{ox}C_{depth}}{C_{ox} + C_{depth}}$$

(2.26)

$$J = q \langle v \rangle n_s = \frac{q}{\hbar^2 \pi^2} \sqrt{\frac{8m^*}{9} \left( q \left( \frac{C_{EET}}{C_{EET} + C_{DOS}} * (V_{GS} - V_{th}) \right) \right)^3} \left( \frac{Amperes}{meter} \right)}$$

(2.27)

From here transconductance can be found by taking the derivative of the current with respect to gate voltage:

$$g_{m} = \frac{\partial J}{\partial V_{GS}} = \frac{q}{\hbar^{2} \pi^{2}} \sqrt{2m^{*} \left(\frac{qC_{EET}}{C_{EET} + C_{DOS}}\right)^{3} (V_{GS} - V_{th})} \left(\frac{Siemens}{meter}\right)$$

(2.28)

## D. Gate Design

Gate design is of vital importance because of its effect on gate resistance. F<sub>max</sub> is the maximum frequency a transistor still displays power gain and is often expressed as equation (2.29) below [13]. This equation can be rearranged to equation (2.30) to highlight the significance of gate resistance.

$$f_{max} \approx \frac{f_{\tau}}{2\sqrt{G_{DS}(R_G + R_i + R_s) + 2\pi R_G C_{GD} * f_{\tau}}}$$

(2.29)

$$f_{max} \approx \frac{f_{\tau}}{2\sqrt{R_G(G_{DS} + 2\pi C_{GD}f_{\tau}) + G_{DS}(R_S + R_i)}}$$

(2.30)

Traditional HEMT technology uses a T-gate like the one seen in Figure 2.1 below. The stem is tall and skinny to minimize the fringe capacitance, and the head of the 'T' is wide and tall to minimize the lateral resistance.

Figure 2.1: Geometric illustration of T-gate

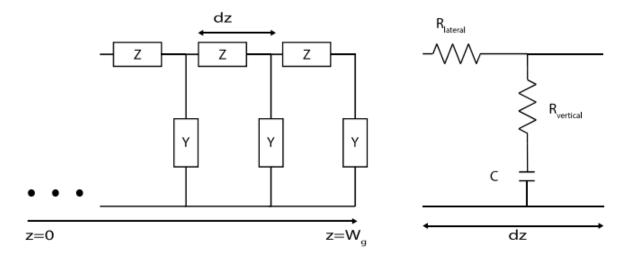

The T-gate is commonly approximated as a series of lateral resistances and vertical admittances to create a transmission line model like seen in Figure 2.2 below [14]. R<sub>lateral</sub> and R<sub>vertical</sub> can be approximated by looking at the geometry of a T-gate in Figure 2.1.

Figure 2.2: Transmission line model for gate resistance

$R_{lateral}$  is approximated using the area of the gate head and the resistivity of the material, usually gold. Technically, the effective lateral area should include some fraction of the stem area as well, but for a highly scaled and well-designed T-gate,  $A_{stem}$  should be much less than  $A_{head}$ .

$$R_{lateral} = \frac{\rho}{(A_{head} + \gamma A_{stem})} \approx \frac{\rho}{A_{head}} = \frac{\rho}{H_{head} L_{head}}$$

(2.31)

$$R_{lateral} = R_{end \ to \ end} / W_g \tag{2.32}$$

R<sub>vertical</sub> is approximated using the stem length and the stem height. Once again, the effective vertical conductance should include some fraction of the vertical resistance through the gate head, but for a highly scaled and well-designed T-gate, the vertical resistance through the head should be much smaller than through the stem.

$$R_{vertical} = \rho \left( \frac{H_{head}}{L_{head}} + \frac{H_{stem}}{L_{stem}} \right) \approx \frac{\rho H_{stem}}{L_{stem}}$$

(2.33)

From generalized transmission line theory, the telegraphers' equations can be written as functions of lateral resistance and vertical conductance. Assuming a one-sided gate connection,  $I(W_g) = 0$  is the valid boundary condition. Simplifying the gate resistance expression results in a hyperbolic cotangent that can be estimated using the first 2 components of the Laurent series that results in the familiar expression seen in equation (2.43).

$$V(z) = V_0^+ e^{-\gamma z} + V_0^- e^{\gamma z}$$

(2.34)

$$I(z) = \frac{V_0^+ e^{-\gamma z} - V_0^- e^{\gamma z}}{Z_0}$$

(2.35)

$$Z_0 = \sqrt{Z/Y} \tag{2.36}$$

$$\gamma = \sqrt{Y * Z} \tag{2.37}$$

$$Z = R_{lateral} = \rho H_{head} * L_{head}$$

(2.38)

$$Y = \frac{j\omega C * L_{stem}}{1 + j\omega C * L_{stem} * R_{vertical}}$$

(2.39)

$$I(W_g) = 0 = \frac{V_0^+ e^{-\gamma W_g} - V_0^- e^{\gamma W_g}}{Z_0} \to V_0^+ = V_0^- e^{2\gamma W_g}$$

(2.40)

$$Z_g = \frac{V(0)}{I(0)} = Z_0 \frac{V_0^+ + V_0^-}{V_0^+ - V_0^-} = Z_0 \frac{e^{2\gamma W_g} + 1}{e^{2\gamma W_g} - 1} = Z_0 \coth(\gamma W_g) \approx Z_0 \left(\frac{1}{\gamma W_g} + \frac{\gamma W_g}{3}\right)$$

(2.41)

$$Z_{0}\left(\frac{1}{\gamma W_{g}} + \frac{\gamma W_{g}}{3}\right) = \sqrt{\frac{Z}{Y}}\left(\frac{1}{W_{g}\sqrt{Y*Z}} + \frac{W_{g}\sqrt{Y*Z}}{3}\right) = \frac{1}{W_{g}*Y} + \frac{W_{g}*Z}{3}$$

(2.42)

$$R_g = Re\{Z_g\} \approx \frac{R_v}{W_g} + \frac{W_g R_L}{3} = \frac{\rho H_{stem}}{W_g L_{stem}} + W_g * \frac{\rho}{3H_{head} L_{head}}$$

(2.43)

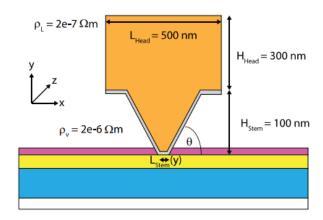

This shows that vertical gate resistance is inversely proportional to gate width, while lateral gate resistance is proportional to gate width. Current state of the art InP-HEMTs aggressively scale gate lengths to 25 nm to minimize  $C_{GS,i}$  and gate widths to 4  $\mu$ m to minimize the lateral gate resistance component [2]. By making reasonable assumptions about the gate geometry and the bulk resistivity, the gate resistance can be estimated. Assuming  $H_{head} = 300$

nm,  $H_{stem}=100$  nm,  $L_{head}=500$  nm,  $L_{stem}=25$  nm,  $\rho_{lateral}=2e\text{-}7~\Omega^*m$ ,  $\rho_{vertical}=2e\text{-}6~\Omega^*m$ , and  $W_g=4~\mu m$ , the vertical gate resistance component is about 50% of the entire gate resistance.

Bulk resistivity here is estimated by using known gate resistance values. Additionally, the vertical resistivity is assumed to be an order of magnitude greater than the lateral resistivity based on experimental work on the relationship between thin film and thick film resistances [15].

As HEMTs continue to scale more aggressively, shorter gate lengths will increase the vertical component of the gate resistance. If the gate length is shrunk to 10 nm while the width is left at 4  $\mu$ m, the vertical component is now about 70% of the total gate resistance. Further scaling of the gate length or the gate width would continue to exacerbate this issue. To continue scaling gate resistance, vertical resistance will need to be minimized.

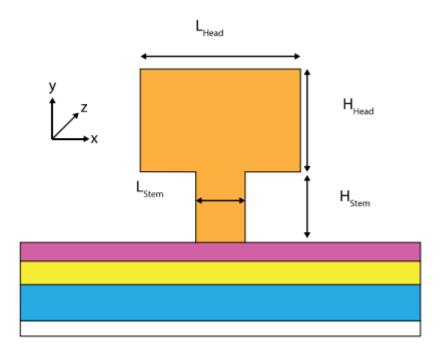

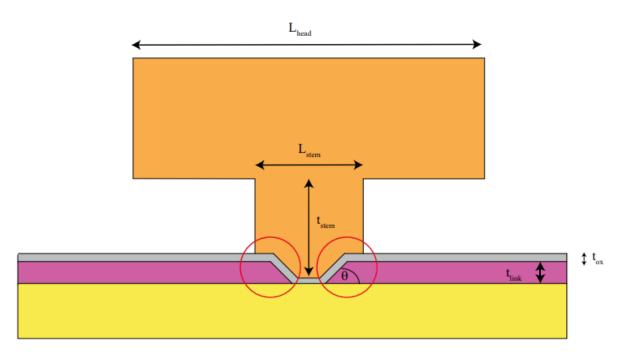

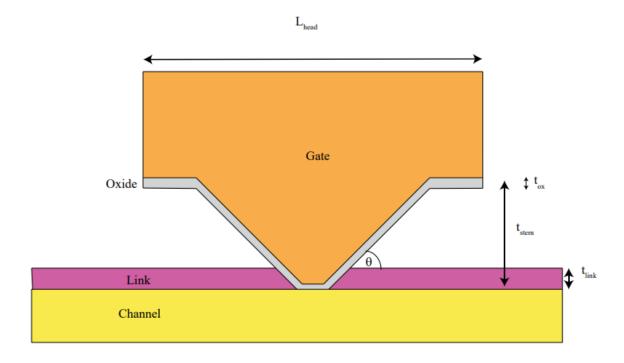

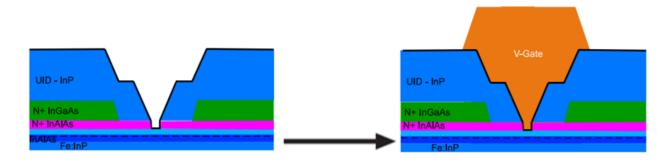

A possible solution is the V-gate technology proposed in this work and illustrated in Figure 2.3. Because the differential resistance is inversely proportional to the stem length, and the stem is no longer a constant thickness, the differential resistance can be rewritten as:

$$dR_v = \rho \frac{dy}{L_{stem}(y)}; \quad L_{stem}(y) = L_{gate} + 2y \cot(\theta)$$

(2.44)

By taking the integral the vertical resistance can be written as:

$$R_{v} = \rho \int_{y=0}^{y=H_{stem}} \frac{1}{L_{gate} + 2y \cot(\theta)} dy = \frac{\rho \tan(\theta)}{2} * \ln\left[\frac{L_{gate} + 2H_{stem} \cot \theta}{L_{gate}}\right]$$

$$for \ 0 < \theta < 90$$

$$(2.45)$$

As  $\theta$  approaches 90 degrees,  $R_v$  simplifies back to its previous formula, and as  $\theta$  approaches 0 degrees,  $R_v$  approaches zero because the effective stem width approaches

infinity. Current V-gate technology has a  $\theta$  of about 45 degrees which results in the convenient simplification:

$$R_v = \frac{\rho}{2} \ln \left[ \frac{L_{gate} + 2H_{stem}}{L_{gate}} \right] \tag{2.46}$$

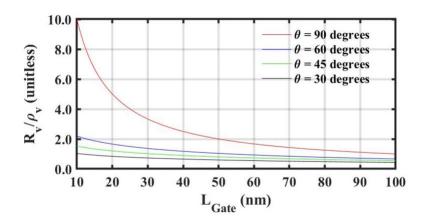

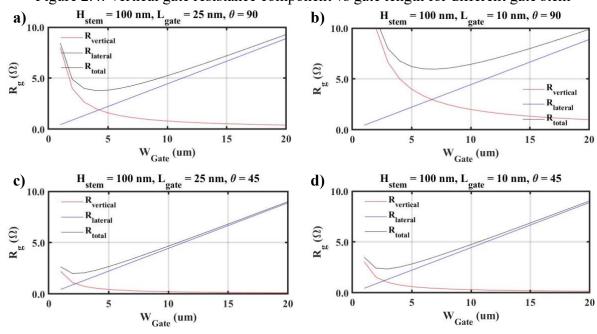

Figure 2.3 below shows the model used to compare gate resistance for different gate lengths, gate widths, and V-gate stem angles. Figure 2.4 shows the vertical resistance divided by the bulk resistivity. This shows that as gate lengths continue to scale, the vertical resistance will increase for all V-gate angles, but angles less than 90 degrees have significantly less vertical resistance.

Lastly, Figure 2.5 shows how the  $R_v/W_g$  and  $W_g*R_L/3$  terms vary as the gate width,  $W_g$ , varies. This shows that current state of the art T-gate ( $W_g=4~\mu m$ ,  $L_g=25~nm$ ,  $\theta=90^\circ$ ) could potentially reduce total gate resistance by almost 50% by switching to a 45° V-gate. Additionally, future  $L_g=10~nm$  devices could reduce total gate resistance by approximately 70%.

Figure 2.3: Geometric illustration of V-gate cross section

Figure 2.4: Vertical gate resistance component vs gate length for different gate stem

Figure 2.5: Vertical, lateral, and total gate resistance vs gate width for a)  $L_{gate}=25$  nm,  $\theta=90^{o}$  b)  $L_{gate}=25$  nm,  $\theta=45^{o}$  c)  $L_{gate}=10$  nm,  $\theta=90^{o}$  d)  $L_{gate}=10$  nm,  $\theta=45^{o}$

### E. Link Design

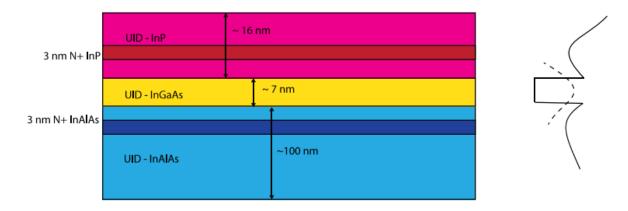

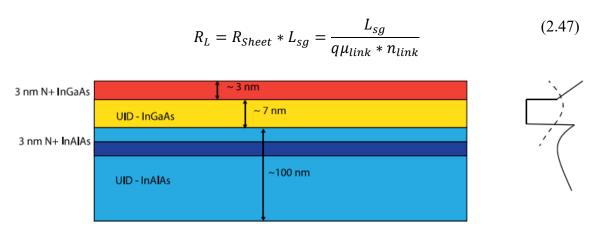

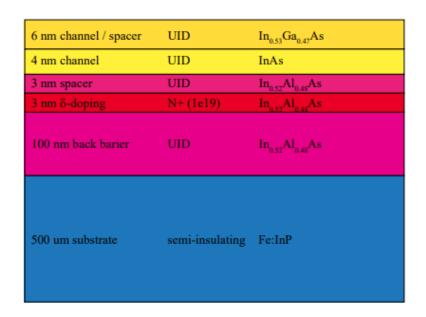

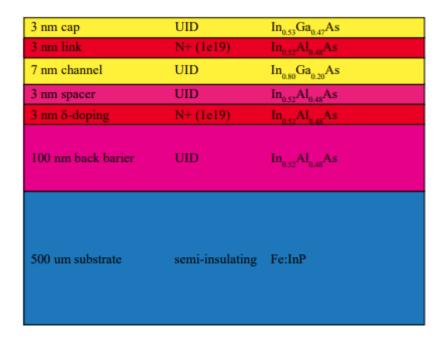

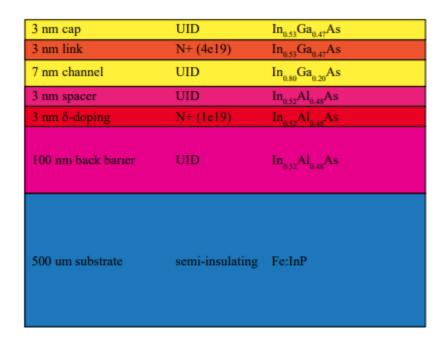

The link, often referred to as the access region in other works, is the region between the thick source / drain contact regions and the gated channel. In previous generations of MOS-HEMTs, the link region consisted of an InGaAs channel with a 106 nm InAlAs bottom barrier and a 16 nm InP top barrier like in Figure 2.6. Both the top and bottom barriers have thin layers of highly doped material offset from the channel by about 3 nm.

Figure 2.6: Illustration of previous MOS-HEMT link design and approximate band diagram

This type of link design keeps the donor ions far from the mobile charge in the channel and therefore minimizing impurity scattering. This results in the HEMTs signature "High Electron Mobility", generally in the 10,000-15,000 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> range [16]. High link mobility minimizes link resistance and therefore total source resistance.

Previous work on MOS-HEMTs had limited high frequency performance in large part due to high capacitance [11]. It was hypothesized that this high capacitance was a result of the gate-link overlap circled in red in Figure 2.7.

Figure 2.7: Illustration of non-self aligned MOS-HEMT gate-link overlap

To minimize the gate-link overlap, the self-aligned process outlined in this work was developed; however, a thick link still results in substantial gate-link overlap as seen in Figure 2.8.

Figure 2.8: Illustration of self-aligned MOS-HEMT gate-link overlap

To further minimize capacitance, it would be advantageous to thin the topside link layer; however, aggressive scaling of the link region would require shrinking, or removing, the topside spacer. As previously mentioned, this would increase the total source resistance. Because  $f_{\tau}$  is dependent on both gate-source capacitance and extrinsic transconductance, and by extension source resistance, both must be considered when designing the optimal link thickness.

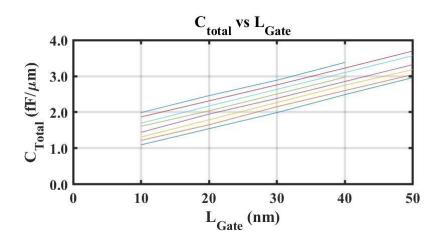

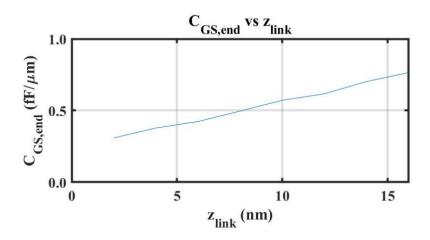

First, the link thickness's effect on end capacitance was explored by using an HFSS model. Because HFSS is an electrostatic simulator and not a quantum simulator, band diagrams have no effect on the charge distribution in the materials. The channel (yellow) and gate (orange) are treated as metals because they are populated with mobile charge, and the oxide (grey) and link (purple) are treated as insulators because they should be depleted of charge.

The model simulated the total capacitance of the structure for a certain gate length and link thickness. To find the end capacitance, the gate length is varied from 10 nm to 50 nm and the total capacitance is plotted as seen in Figure 2.9 below.

Figure 2.9: Total capacitance vs gate length for different link thicknesses

From here, the y-intercept of each line was estimated to be the total end capacitance and when divided by two, estimated to be the end capacitance for the source side. When plotted vs gate length, as in Figure 2.10, a strong linear relationship between link thickness and end capacitance is exhibited.

Figure 2.10: End capacitance vs link thickness graph

While  $C_{GD,end}$  is also expected to shrink as  $C_{GS,end}$  does, a conservative estimate of total gate-source and gate-drain capacitance can be made by simply subtracting the total benefit in  $C_{GS,end}$  from the previous total capacitance.

Table 2.1: Predicted change in total capacitance for a 4 nm thick link

|                                       | Gen 1.3 MOS-HEMTS<br>Thick link (~16 nm) | Gen 2 MOS-HEMTS<br>Thin link (~4 nm) |  |  |

|---------------------------------------|------------------------------------------|--------------------------------------|--|--|

| $C_{GS,i}$ (fF/ $\mu$ m)              | 0.3                                      | 0.3                                  |  |  |

| C <sub>GS,end</sub> (fF/µm)           | 0.7                                      | 0.3                                  |  |  |

| $C_{GD}$ (fF/ $\mu$ m)                | 0.3                                      | 0.3                                  |  |  |

| C <sub>Total</sub> (fF/µm)            | 1.3                                      | 0.9                                  |  |  |

| $\Delta  \mathrm{C}_{\mathrm{Total}}$ |                                          | -31%                                 |  |  |

Next, the dependence of source resistance on link thickness was explored experimentally. The source resistance can be broken down into components and be added up

piecewise. For simplicity, these will be combined into terms that vary with link thickness and those that do not. Terms that don't vary with link thickness come from resistance in the metal, the N+ contact layer, and any contact resistance and can be written as a constant  $R_C$ . The only term that will vary with link thickness is  $R_L$ .

Figure 2.11: Illustration of proposed link design and approximate band diagram

The proposed 3 nm N+ InGaAs topside link, seen in Figure 2.11, was compared to previous work in the group that utilized a 16.5 nm delta-doped InP topside link. Total sheet resistance fell dramatically, in part due to the reduction in mobility. More significant was the drop in charge due to the smaller band offset between InGaAs and InAs than InP and InAs. Additionally, the InP link utilized a thick undoped layer above the delta doping to induce additional charge in the channel via the lever rule.

Table 2.2: Predicted change for total source resistance and its effect on extrinsic transconductance

| Link                                         | 16.5 nm thick InP | 3 nm thick InGaAs |  |  |

|----------------------------------------------|-------------------|-------------------|--|--|

| Sheet resistance ( $\Omega$ /sq)             | 173               | 654               |  |  |

| $R_L (\Omega * \mu m)$                       | 8.65              | 32.7              |  |  |

| $R_{C}(\Omega * \mu m)$                      | 90                | 90                |  |  |

| $R_{_{\mathrm{S}}}(\Omega * \mu \mathrm{m})$ | 98.65             | 122.7             |  |  |

| $g_{mi}$ (mS/ $\mu$ m)                       | 4                 | 4                 |  |  |

| $g_{me} (mS/\mu m)$                          | 2.87              | 2.68              |  |  |

| g <sub>me</sub> % change                     | 0%                | <mark>-7%</mark>  |  |  |

Assuming the source resistance components not dependent on link thickness stay the same, total Rs increases from about  $100~\Omega^*\mu m$  to  $120~\Omega^*\mu m$  based on this design change. By utilizing the known intrinsic transconductance from previous MOS-HEMTs, the extrinsic transconductance can be estimated as well as its total degradation.

By examining percent change in capacitance and transconductance based on link thickness, a rise in  $f_{\tau}$  is predicted for a thinner link region.

$$f_{\tau} \approx \frac{g_{m,e}}{2\pi (C_{gs} + C_{gd})} * \frac{\downarrow 7\%}{\downarrow 31\%} = \uparrow 34\%$$

(2.48)

# 3. RF Testing and Small Signal Modeling

In this chapter, RF calibration, testing, de-embedding, and modeling will be discussed. For devices that showed promising DC characteristics, DC-67 GHz S-parameter testing was performed as described in section A (DC-67 GHz OSLT). A simple circuit model was then extracted as described in section B (Model Extraction). For device results presented in this work, more complex circuit models were used in Keysight Advanced Design Systems (ADS) and presented in their respective results section.

#### A. DC-67 GHz OSLT

For the DC-67GHz testing, a 2-port VNA (Keysight N5227B) was used along with a Keithley 2602A source for biasing the gate and drain. The probes used were cascade infinity probe by form factor with a 75 µm pitch and connected to the system using 24" 67 GHz semi-rigid cables. The VNA was connected to a computer via ethernet to control the testing setup. The setup was controlled via WinCal during calibration and setup and by a python script during device measurement. IF Bandwidth used was 300 Hz, power was -25dBm, averaging was 3, and frequency range was 500 MHz to 67 GHz with 250 MHz steps.

Devices that showed promise during DC testing would initially be tested from DC-67 GHz using off wafer calibration standards. A 104-783 W-band Impedance Standard Substrate is used with Open-Short-Load-Thru (OSLT) calibration to move the testing reference plane to the tip of the probes.

Once the reference plane is at the probe tip, open and short structures are tested. First, the "Open" is used to remove the capacitance from the device under test (DUT) and from the "Short".

$$Y'_{DUT} = Y_{DUT} - Y_{Onen} \tag{3.1}$$

$$Y'_{Short} = Y_{Short} - Y_{Open} \tag{3.2}$$

Next, the inductance can be removed from the DUT after converting from Y parameters to Z parameters.

$$Z''_{DUT} = Z'_{DUT} - Z'_{Short}$$

(3.3)

The resulting  $Z''_{DUT}$  are the device characteristics with pad effects removed. Short-Open de-embedding is also used in this work, but results in higher FOM and noisier data, and is therefore ignored.

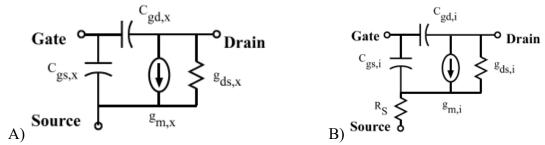

#### B. Model Extraction

For simple automated extraction of small signal circuit parameters, a simple FET model is used [17]. This model removes several important FET parameters, most notably source resistance. Without the inclusion of source resistance,  $g_m$ ,  $g_{ds}$ ,  $C_{gs}$ , and  $C_{gd}$  take on a new meaning referred to in this work as "extrinsic" usually denoted with a subscript 'e' or 'x'. Extrinsic small signal characteristics are used because they are a direct linear fit of real and imaginary parts of admittance parameters at peak bias conditions. This allows for easy and repeatable model extraction for plotting data against gate length.

Figure 3.1 Equivilent circuit for A) extrinsic model B) intrinsic model

$$Y = \begin{bmatrix} j\omega[C_{gs,x} + C_{gd,x}] & -j\omega C_{gd,x} \\ g_{m,x} - j\omega C_{gd,x} & g_{ds,x} + j\omega C_{gd,x} \end{bmatrix}$$

(3.4)

$$C_{gd,x} = -\frac{Im[Y_{12}]}{\omega} {(3.5)}$$

$$C_{gs,x} = \frac{Im[Y_{11}]}{\omega} - C_{gd,x}$$

(3.6)

$$g_{m,x} = Re[Y_{21}]|_{\omega=0} (3.7)$$

$$g_{ds,x} = Re[Y_{22}]|_{\omega=0} (3.8)$$

To estimate intrinsic parameters, first Z-parameters must be used to estimate  $R_S$  and  $R_G$  at 0 Volts  $V_{DS}$  and a large enough  $V_{GS}$  to invert the channel. From here intrinsic parameters can be estimated.

$$R_{s} = Re(Z_{22})|_{\omega=0} - Re(Z_{11})|_{\omega=0}$$

(3.9)

$$R_{G} = Re(Z_{11})|_{\omega=0} - \frac{Re(Z_{12})|_{\omega=0}}{2} - \frac{R_{S}}{2}$$

(3.10)

$$C_{as,i} \approx C_{as,x} (1 + R_s * g_{m,i}) \tag{3.11}$$

$$C_{ad.i} \approx C_{ad.x}$$

(3.12)

$$g_{m,i} \approx \frac{g_{m,x}}{1 - R_c g_{m,x}} \tag{3.13}$$

$$g_{ds,i} \approx g_{ds,x} (1 + R_s * g_{m,i})$$

(3.14)

From here, figures of merit,  $f_{\tau}$  and  $f_{max}$ , can be estimated using the extrinsic model.

$$f_{\tau} = \frac{\omega(H_{21} = 1)}{2\pi} \approx \frac{g_{m,x}}{2\pi(C_{GS,x} + C_{GD,x})}$$

(3.15)

$$f_{max} = \frac{\omega(U=1)}{2\pi} \approx \sqrt{\frac{f_{\tau}}{8\pi R_G C_{gd} + 4g_{ds}(R_G + R_S)}}$$

(3.16)

# 4. Processing

In this chapter process modules and their interactions will be discussed. Entire process flows can be found in the Appendices.

#### A. Overview

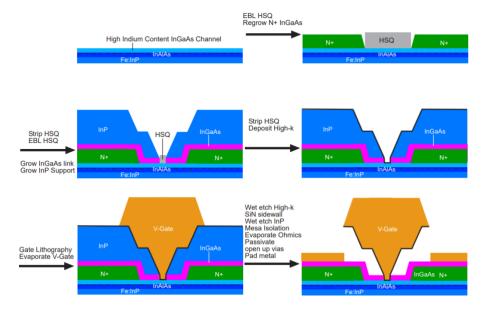

The meat of this thesis work was spent on process development. The goal of the project was to develop a completely self-aligned process to minimize capacitance. To achieve this, the novel double regrowth design previously developed at UCSB was reversed to implement the InP sacrificial regrowth developed at Lund university [11, 18]. To achieve minimal capacitance, the link region was thinned to the acceptable extremes of less than 5 nm. In addition, a gate last process was developed to allow for pad metal connection over mesa edges. Specific implementations of the process modules will be discussed in the chapters for each specific device.

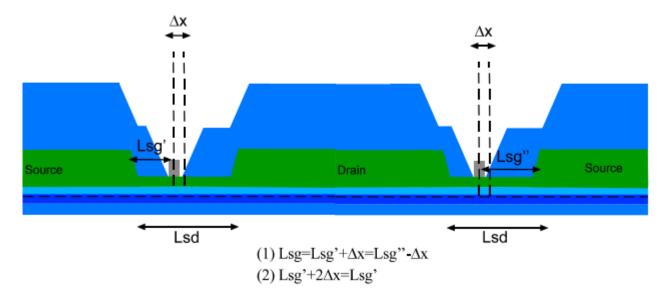

### B. Alignment Marks

The self-aligned process for MOS-HEMTs eliminates the need for gate to link alignment; however, tight alignment tolerances are still required when aligning the second regrowth to the first regrowth. This work used 100 nm gate to source and gate to drain spacing. This required aligning a "Dummy Gate" hard mask of length  $L_g$  to the middle of a "Dummy link" hard mask of length  $L_g + 200$  nm.

It is also important to note that the devices are built in a GSG structure. This means misalignment also creates asymmetric source to gate and gate to drain spacing between the left and right devices. This can be seen in Figure 4.1 below. Variations in the spacing can

cause performance variations, most notably, source resistance and output conductance. With these two things in mind, it is imperative to minimize misalignment, preferably below 20 nm.

Figure 4.1: Cross-sectional illustration of device asymmetry caused by misalignment.

Good alignment marks are an important part of good alignment resolution. To make the alignment marks easier to "see" in an E-beam Lithography system, the amount of detected scattered electrons (SE) and back scattered electrons (BSE) should vary as sharply as possible at the edges of the alignment mark. This will result in a large signal to noise ratio (SNR). The level of electron scattering, and therefore SNR is most highly influenced by atomic number and step edge. Wet or dry etched alignment marks rely on step edge detection, while metal deposited alignment marks can also have the benefit of Z-contrast.

Variance in atomic number, also known as Z-contrast, is easily obtained by depositing metal alignment marks with large atomic numbers such as Tungsten, Molybdenum, Gold, Ruthenium, or Platinum [19]. Unfortunately, later regrowths in the MOCVD system limit these down to refractory metals that have high evaporation temperatures and can only be deposited via high energy processes such as sputtering or E-beam evaporation. At this point in the process, the surface is very sensitive to damage that would result in high Dit [20]. There

are also concerns about galvanic etching issues that come along with exposed metal during processing [21]. For these reasons metal alignment marks were avoided for this work.

A step edge resulting in a variation in scattered electrons can be achieved with an etched trench in material. To maximize SNR, the trench should be as deep as allowable, and the sidewalls should be as steep as possible [19]. To get steep walls, using a dry etch is preferred, and an anisotropic profile is easily achieved by adjusting the gas flows [22]. Unfortunately, ion bombardment damaging the surface is a concern and is avoided in this work.

This work used wet etched alignment marks to remove the concerns about damage, but this has its own drawbacks. Wet etched marks have the lowest SNR of the three options because it provides no Z-contrast, and the sidewalls are sloped. To account for this, it is best to make the trench as deep as possible [19]. In this work the trenches are 1  $\mu$ m deep but could be made deeper if alignment tolerance was an issue.

The second issue with wet etched Alignment marks is resist adhesion. If the resist does not adhere well to the surface, the wet etch can undercut the resist as seen in varying degrees in Figure 4.2 below. This resulting edge roughness can hurt realignment [19]. To avoid this a hard mask is used. Exact details on etch chemistries and times can be seen in the Appendices.

Figure 4.2: Wet etched alignment marks with poor photoresist adhesion

### C. Lithography

### **Optical Lithography**

Previous work in the group utilized an AutoStep 200. This is an i-line step and repeat exposure tool that can achieve high resolution (≥500 nm) and/or critical alignment (≥150nm) according to its specifications. The 1000-Watt Mercury arc lamp source results in very consistent exposures and requires minimal recalibration. Under normal circumstances, this would be the preferred tool for Alignment marks, mesa isolation, metal deposition, and vias.

Due to the highly fluid nature of creating a new process, constant mask changes were desired and impractical using a masked writing system like a stepper. Because of this, the optical lithography in this process was transitioned to a Heidelberg MLA150, a direct write lithography system, early in this work. The Heidelberg has longer write times, lower resolution (≥1000 nm), worse alignment (≥500nm), and shows more variation across a single wafer and different process runs.

#### **Positive Optical Lithography**

The preferred positive resist for this work is SPR-955-0.9. When spun at 3000 rpm the resist thickness is approximately 0.9 um. A prebake of 95 °C for 90 seconds and a post bake of 110 °C for 90 seconds are used. A 405 nm laser, dose of 105 mJ/cm2, and defocus of -3 are used for alignment marks. A 405 nm laser, dose of 240 mJ/cm2, and defocus of -6 are used for mesa isolation and InP sacrificial removal. Samples are developed in 300-MIF for 60 seconds and rinsed in DI water for 60 seconds.

### **Negative Optical Lithography**

For negative optical lithography, HMDS and Nlof-2020 are used. Both the HMDS and nlof are spun on at 4000 rpm resulting in a thickness of approximately 1.7 um. A prebake of 110 °C for 60 seconds and a post bake of 110 °C for 60 seconds are used. A 375 nm laser, dose of 340 mJ/cm2, and defocus of -3 are used for vias, ohmics, and pad metal. Samples are developed in 300-MIF for 90 seconds and rinsed in DI water for 60 seconds.

### **Positive Electron-Beam Lithography**

For positive E-beam lithography, Surpass 4000 and UV-6 are used. Surpass 4000 is dropped onto the sample surface and left to soak for 60 seconds before rinsing the sample for 30 seconds and blow drying the sample dry using N<sub>2</sub>. This is to increase photoresist adhesion. Next, UV 6-0.8 is spun on the sample at 3000 rpm and baked at 115C for 90 seconds. Consistent baking is especially important for UV-6 because it is chemically amplified. This allows for a single layer liftoff with relatively high small features, thick resist, and low doses. The UV-6 is then over-exposed in the EBL to get the desired undercut profile for liftoff. Finally, the sample is post baked at 135C for 2 minutes and developed in AZ-300MIF for 60 seconds.

### **Negative Electron-Beam Lithography**

For negative E-beam lithography, HSQ is used. The Hydrogen Silsesquioxane (HSQ) hard masks define both the minimum achievable gate length and the gate to contact spacing. Prior to HSQ, 10 cycles of TMA+H2O-300C (~1 nm Al<sub>2</sub>O<sub>3</sub>) are deposited on the surface to protect the channel from contamination.

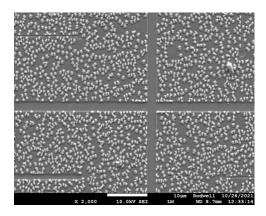

Next, the HSQ in its liquid form is diluted to 2% by volume in MIBK to reduce viscosity and therefore reduce thickness when spun on a wafer to maximize resolution [22]. The HSQ is then spun at 5000 rpm to a thickness of about 40 nm (verified by ellipsometry). Then, the HSQ is cured at 200 degrees Celsius for 2 minutes.

The E-beam dose needed is highly dependent on the resolution needed and by extension, the developer used. TMAH and TMAH containing developers can be used to decrease dose and limit exposure time but have lower sensitivity and therefore minimum feature size [22]. To achieve minimum feature size less than 10 nm a "salty" developer and a base dose of 5000  $\mu$ C/cm<sup>2</sup> is used. The salty developer is 1% NaCl and 4% NaOH by weight in water.

The NaOH can take a long time to completely dissolve and can have an undesirable effect on development if impatient. It's recommended to stir the solution every 5 minutes until it appears dissolved and then wait an additional 5 minutes before developing. The beaker is also covered with a watch glass to avoid evaporation and maintain constant concentration.

The sample is developed for 1 minute before being carefully placed in deionized water. Agitation should be avoided at all times because the HSQ can easily delaminate. After 1 minute the water is replaced and the sample is left in water for another 5 minutes. What is left is essentially a porous SiO2 mask [23].

Dark field optical microscopy is used to verify the HSQ didn't delaminate and is roughly where it should be. It is difficult to see these patterns in an SEM because of the small size and low contrast, so it is not performed. Exact instructions can be found in the Appendices.

### D. First Regrowth (N+ InGaAs Contacts)

Contacts are regrown via MOCVD using the HSQ as a hard mask and using a high V/III ratio gives excellent growth selectivity between the InGaAs channel and HSQ mask. To maximize device performance the resistance of this region should be minimized.

$$R_{sheet} = (q\mu_n t N_d)^{-1} \tag{4.1}$$

Because the mobility is impurity scattering limited by the large amounts of dopants, not much attention is paid to it. The critical variables are thickness and activated doping concentrations. To keep doping concentrations high it is best to keep a high V/III ratio and high temperature [24]. The channel is strained in these devices, so the maximum allowable temperature is 600 degrees Celsius. 4e19 cm-3 is the target doping concentration for this work and is verified by a 4-point probe while assuming a constant mobility of 1000 cm/(V\*s).

High doping concentration is also important for contact resistance. Contact resistance is highly dependent on the tunneling probability through the Schottky barrier at the N+ to ohmic contact interface. Higher levels of doping shrink the depletion region at this interface and improves tunneling probability.

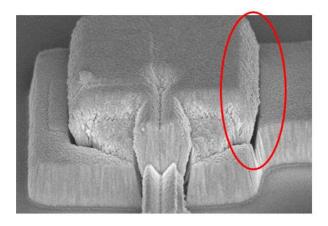

Thickness is limited by later processing and not what is limited by MOCVD regrowth. 50 nm regrown contacts are most commonly used in this work. Increasing the thickness of the regrowth makes the sample less planar and raises concerns about the second regrowth. During run RRMH-33 the contacts were increased to 100 nm and the second regrowth showed defects that appeared to affect the V-gate yield and overall device performance as seen in Figure 4.3 below.

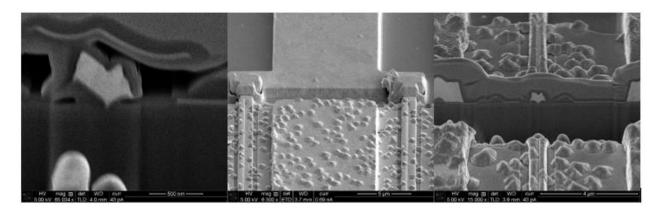

Figure 4.3: RRMH-33 angled and cross-sectional SEMs showing island regrowth.

# E. Second Regrowth (Link and Sacrificial layer)

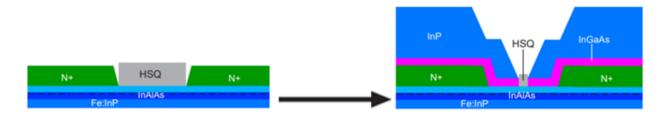

Once again, the regrowth is done via MOCVD using HSQ as a hard mask. The original idea was to regrowth both the link and the InP like in Figure 4.4 below.

Figure 4.4: Cross sectional illustration of link (pink) and sacrificial layer (blue) regrowth

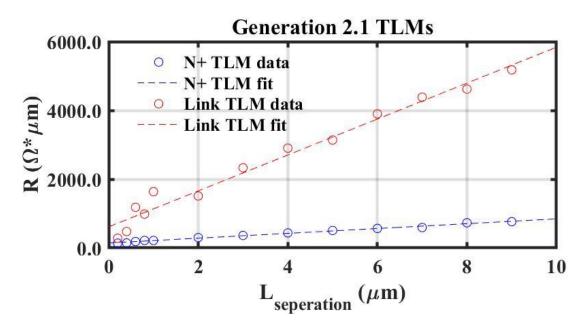

Unfortunately, the TLMs showed poor end resistance for the link TLMs. Sheet link resistance ruled out concerns about doping and thickness of the link region, and good N+ contact resistance ruled out concerns about surface contamination or damage.

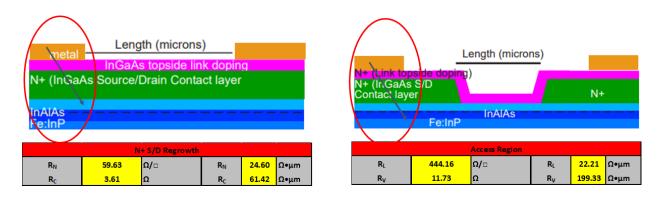

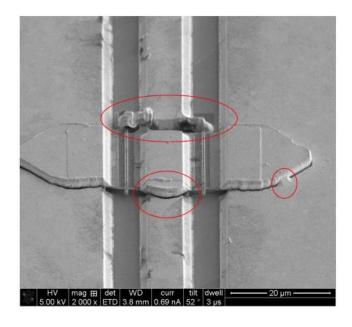

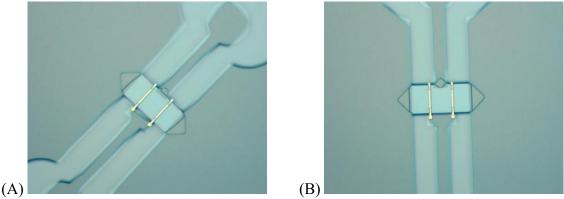

It is hypothesized that the non-planar nature of the sample led to the poor end resistance. The theory is the regrowth isn't perfectly conformal and there is either a lack of link doping or a lack of link material entirely in the corners near the contact region. Figure 4.5 shows the differences between the link and contact TLM structures and results.

Figure 4.5: N+ contact vs link TLM structures and results

In either scenario, the election supply in these corners would be lower than intended and create a barrier to electrons that would increase the end resistance of these structures.

A specific growth experiment including SIMS and TEMs would be necessary to verify this theory and falls out of the scope of this work. To avoid this issue, the link was grown as part of the epi structure. The final design of the process still utilizes a UID-InGaAs regrowth prior to the InP regrowth to ensure the channel is fully protected during the sacrificial etch. Figure 4.6 shows the final design of the first regrowth (a) and second regrowth (b).

Figure 4.6: Cross sectional illustration of sacrificial layer (blue) regrowth

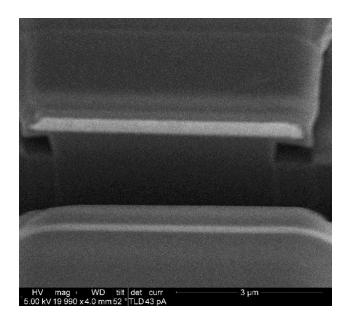

The thickness of the InP regrowth was 80 nm for all experiments in this work. Increasing the InP regrowth thickness is equivalent to increasing the T-gate height in a traditional RF-HEMT. Traditionally, increasing the stem height for a RF FET has been desired to minimize fringe capacitance from the gate; however, increasing stem height over 80 nm was shown to have diminishing gains. Therefore, increasing the stem height only serves to decrease the stability of the gate in this work.

The angle of the InP regrowth is dependent on the growth facets. These can be controlled by the V/III ratio [25]. The high V/III ratio used to achieve good selectivity between the semiconductor and HSQ dielectric mask results in roughly a 45-degree angle like seen in Figure 4.7 below. Making the regrowth at a sharper angle could improve fringe capacitance by maximizing the distance between the gate and a channel but falls out of the scope of this work.

Figure 4.7: Sacrificial InP regrowth angle from RRMH-24

## F. Link Etching

When the process shifted to an epitaxial link instead of a regrown link, controlled etching through the link became imperative for precise channel thickness control. In traditional InP HEMTs, the link recess etch is controlled by an etch stop [26]. This wasn't possible in this work because this would add to the thickness of thickness of the link and add complexity to the material selective etches.