# UC Irvine ICS Technical Reports

# Title

TTL implementation of a CAMB tree network switch

# Permalink

https://escholarship.org/uc/item/09c510d1

# Authors

Huang, Hung Khei Godbille, Kenneth A. Suda, Tatsuya

# **Publication Date** 1991

1991

Peer reviewed

LIBRARY University of California IRVINE Z 699 C3 No. 91-25

Notice: This Material may be protected by Copyright Law (Title 17 U.S.C.)

> TTL Implementation of a CAMB Tree Network Switch<sup>1</sup> Technical Report 91-25

Hung Khei Huang, Kenneth A. Godbille, Tatsuya Suda Department of Information and Computer Science University of California, Irvine Irvine, CA 92717

<sup>&</sup>lt;sup>1</sup>This material is based upon work supported by the National Science Foundation under Grant No. NCR-8907909. This research is also in part supported by University of California MICRO program.

Brinder Monten en ander Belouken, so yne WEL Inpinyos Gor C.D.B.G.S. Onfej

#### Abstract

Packet collisions and their resolution create a performance bottleneck in random-access LANs. A hardware solution to this problem is to use a collision avoidance switch. These switches allow the implementation of random access protocols without the penalty of collisions among packets. An architecture based on collision avoidance is the CAMB (Collision Avoidance Multiple Broadcast) Tree network, where concurrent broadcasts are possible.

The purpose of this paper is to present two implementations for a CAMB Tree switch<sup>\*</sup>. First, a general outline of the CAMB switch is provided. Then, a description of the two implementations is given.

# 1. A CAMB Network.

To fully understand the operation of the tree network switch proposed, this section attempts to briefly describe the principle behind a CAMB Tree Network.

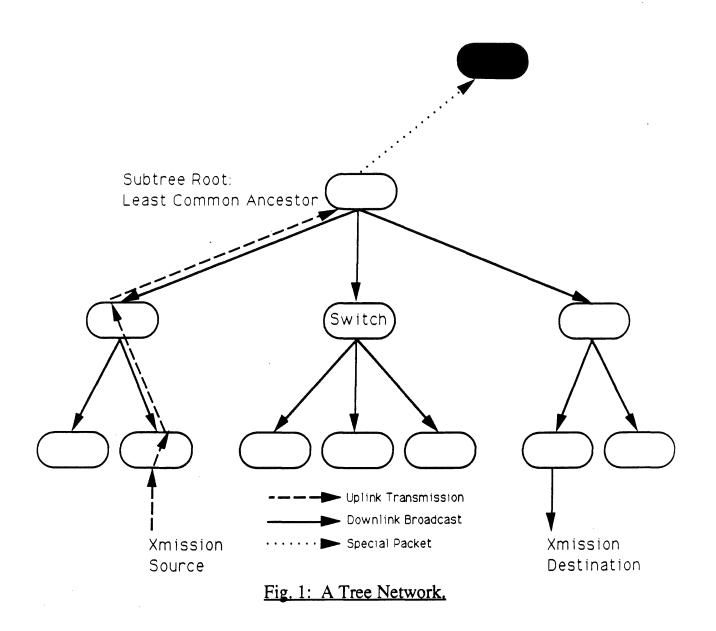

As its name implies, a CAMB Tree Network consists of a set of switches arranged in a tree topology (Fig. 1). Data packets enter and exit the network at the leaf switches. (Each leaf switch is connected to a number of network stations or devices.) The packets are routed up the tree until they reach a switch that is the root of the smallest subtree which contains both the source and destination stations. This switch is know as the *least common ancestor* of the source and destination stations. Packets are then broadcast to every station in this subtree. The receiving stations recognize when a packet is meant for them by a destination address which starts each packet.

\* A short summary of a CAMB Tree network is given here, but for more information, I suggest the reader consult "Tree LANs with Collision Avoidance: Station and Switch Protocols" by Dr. Tatsuya Suda and Steve Morris [Computer Networks and ISDN Systems. Elsevier Science Publishers B.V., North-Holland, 1989, vol. 17, pp. 101-110].

## 1.1 The CAMB Tree Switch.

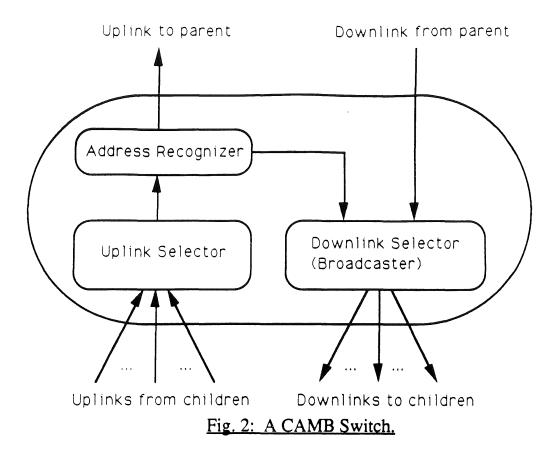

The CAMB Tree Switch can be understood in terms of three smaller modules (shown in Fig. 2):

- The Uplink Selector selects a packet at random from the set of incoming packets.

- The Address Recognizer determines if the switch is the least common ancestor of the source and destination stations.

- -If the switch is not the least common ancestor, the Address Recognizer routes the incoming packet up the tree to the parent switch.

- -Otherwise, the incoming packet is sent to the Downlink Selector, described below. In addition, the Address Recognizer sends the packet up the tree. The reason for sending this packet will be revealed later.

- The *Downlink Selector* broadcasts a packet from either the Address Recognizer, or from the parent switch's downlink. The Downlink Selector gives priority to the parent downlink. Furthermore, if a packet from the parent downlink arrives during a packet transmission from the Address Recognizer, the Downlink Selector will abort the packet transmission from the Address Recognizer in favor of the packet on the parent downlink line. Also, any packets coming from the Address Recognizer during a parent downlink transmission are blocked.

In the description of the Address Recognizer, it was stated that during a packet broadcast the switch will also send the packet up the network tree. The reason for doing this is the protocol which drives the Downlink Selector. When an incoming packet is accepted for broadcast, the Downlink Selector allows the packet to be aborted by a transmission from the parent switch. As a result, it is possible for a switch to be continually forced to abort broadcasts due to other packets accepted by another switch higher in the tree. To resolve this problem, a way must be found to block switches higher in the tree from acquiring new packets during a broadcast.

The solution adopted by the CAMB Network presented here is to insure that the switch has the following properties: 1) the selected packet is always transmitted up the tree, and 2) the packet busies switches higher in the tree so no new packets are accepted by the network.

# 2. Implementing the Switch.

This section gives a high level description of a specific implementation of the CAMB switch. Below, a list is given which describes the specific attributes of the proposed switch.

# 2.1. Switch Interfaces.

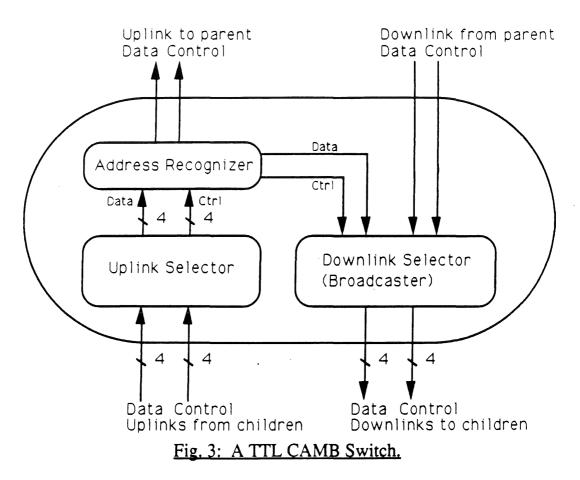

Following is a list which describes a specific implementation of the CAMB switch in relation to the general description given earlier (refer to Fig. 3):

• Each switch in this design has four uplinks and four downlinks. This means leaf switches can interface with four devices (stations)-- the entire tree structure is a 4-ary tree.

- Each uplink or downlink can be thought of as having a *control path* and a *data path*. The control path signals the beginning and end of each packet. The data path is responsible for both packet routing and conveying packet information.

- Each switch is connected to its parent switch with one uplink and one downlink.

# 3. A Hardware Implementation.

This section describes two implementations of a CAMB Tree Switch at the hardware level. Full schematics of the TTL tree switch are provided.

#### 3.1. Switch Implementation # 1.

This section gives a description of one of the switch implementation presented in this paper. First we give a description of the packet format and the addressing scheme assumed in this implementation. Then we present the block diagram of each one of the sections of the CAMB switch. Finally we describe the signals and the circuit schematic.

#### 3.1.1 Packet Format.

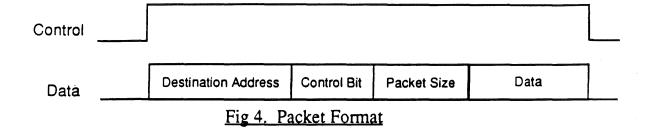

This implementation of the CAMB Tree Network has a packet format with four fields: a Destination Address Field, Control Bit Field, Packet Size Field and Data Field (Fig. 4).

The Destination Address field (8 bits long) indicates the destination address. The next field is the Control Bit (1 bit long). This bit is used to indicate if the packet has reached its proper ancestor. This bit is initially set to 1 by the sending station. It remains 1 until the packet reaches the proper ancestor. When a packet reaches its proper ancestor, this switch resets this bit to 0.

The Packet Size field indicates the number of bits contained in the data field. This information is used by the stations (not by the switches) to determine whether the packet has been aborted. If the Packet Size field is equal to the size of the data field, the packet is successfully transmitted, otherwise, abortion happened. Note that, depending on higher layer protocols, other overhead information such as source address and CRC may be necessary in the packet.

The Control line is high whenever there is a valid packet transmission in the Data line. Otherwise it is low.

#### 3.1.2. Addressing Scheme.

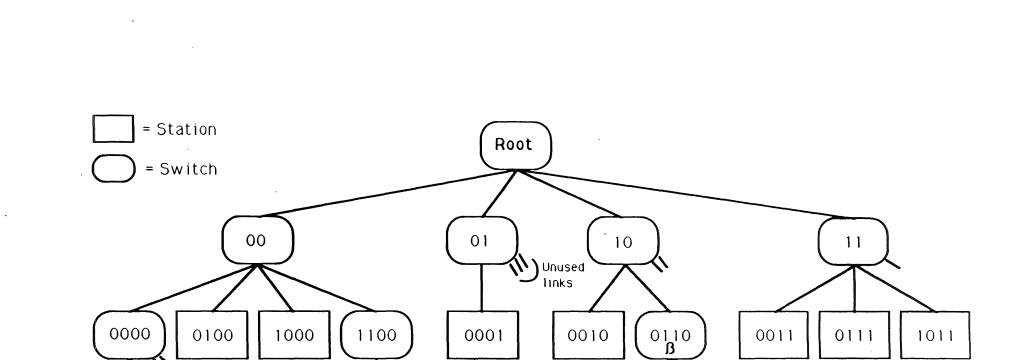

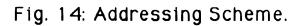

The addressing scheme assumed in this switch design is shown in Fig 5. Stations are ordered in ascending order from left to the right of the tree. Each station has a 2x(M - 1) bit long address, where M is the height of the tree. Address are assigned to the switches in the following way. The level i switches have a 2x(i - 1) bit long address. The address of a switch on level i matches with the first 2x(i - 1) bits of the addresses of all the stations in the subtree.

The above numbering of stations and switches makes it easy for a switch to know whether it is the proper ancestor of a packet. A switch on level i checks the 2x(i - 1) leftmost bit of the address field of a packet. If it is equal to its own address, then it is the proper ancestor of the packet. In this case, the packet is sent to both the parent switch and the downlink switches. Otherwise, the packet is only sent to the parent switch.

Fig 5 shows a transmission of a packet from station A (address 0000000) to station B (address 00000100) as an example. Station A's immeadiate parent switch, Z (address 000000), checks the destination address of the packet. As the six leftmost bits of the destination address in the packet header is different from the switch address, it sends the packet only to its parent switch (Y). Switch Y (address 0000) then checks the four leftmost bits of the destination address of the packet. This time, as they match with the switch's address, switch Y knows that it is the proper ancestor of the packet. Thus, the packet is broadcast to its children. The packet is also sent to the parent switch (X).

Now, the switch X (address 00) checks the two leftmost bits of the destination address field. They agree with the switch address. Therefore, the switch X knows that it is the proper ancestor of the packet and becomes ready to broadcast the packet to its children. However, if the switch X actually broadcasts the packet, it is broadcast twice (once by switch Y and once by switch X). To avoid this undesirable situation where the same packet is broadcast more than once by different switches, a control bit has been added in the packet header (fig 4). First, a switch checks the control bit in the packet header. If it is 0, a switch knows that the packet has already been broadcast by its proper ancestor, so it will transmit the packet only to the parent switch. Otherwise, it will check the address field to see if it is the proper ancestor of the packet. In the example shown above, the switch X first checks the control bit. As it is 0, the switch does not broadcast the packet.

## 3.1.3. Switch Structure.

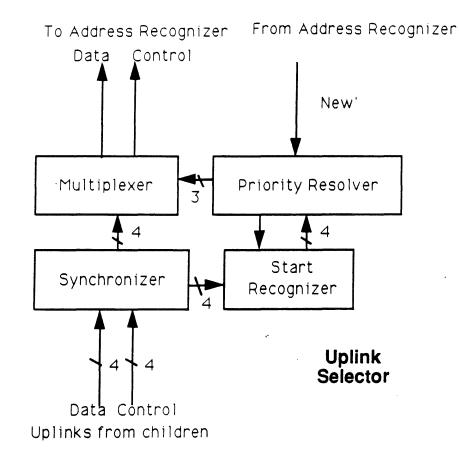

To better understand how the TTL implementation works, the switch has been broken down even further. In Figure 6, the Uplink Selector has been broken down into four parts.

• The Synchronizer - which aligns an incoming packet with the switch's internal clock. One important observation: if several switches in the network share the same clock signal, this unit is not required between interconnected switch nodes. Removal of the unit in this case will speed up packet transmission.

9

- The Start Recognizer which detects the start of a new packet. This unit also allows the Uplink Selector to block all other uplinks while a selected packet is being transmitted.

- The *Priority Resolver* which selects one packet at random from the set of new packets.

- The *Multiplexer* which acts as a gatekeeper, allowing only the packet which the Priority Resolver selects through to the Address Recognizer.

Notice that the Start Recognizer and the Priority Resolver are exclusively control path units, i.e., they do not connect to the data path.

Fig 6. CAMB Switch Uplink Selector

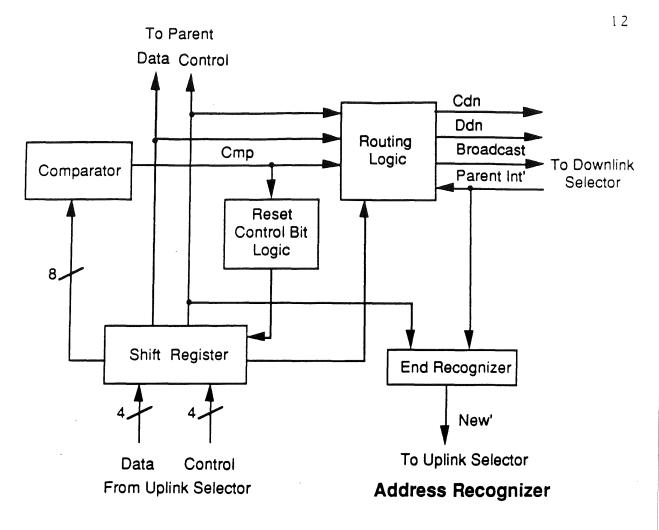

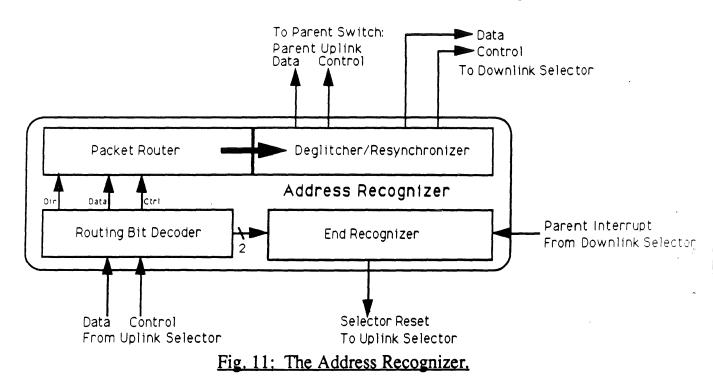

Likewise, the Address Recognizer (fig. 7) can be reduced to its component parts.

- The Shift Register stores the destination address, so it can be checked by the comparator. Note that the shift register always sends the incoming packet to the parent switch.

- The *Comparator* generates a signal (Cmp) which indicates whether the incoming packet destination address matches with the switch address.

- The Routing Logic generates a signal (Broadcast) which indicates whether the incoming packet will be sent to the Downlink Selector to be broadcast or not. This signal is generated based on three signals: Cmp, Control Bit, Parent Int'.

- The Reset Control Bit Logic resets the control bit in the incoming packet whenever the switch recognizes the it is the proper ancestor of the packet. This indicates that the packet has already been broadcast.

- The *End Recognizer* which detects the end of a transmitting packet or a transmission interrupt from the parent downlink line. When one of these events happens, the End Recognizer sends a reset signal (New') to the Uplink Selector.

Fig 7. CAMB Switch Address Recognizer

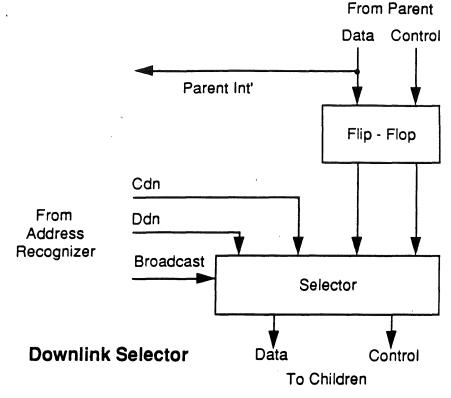

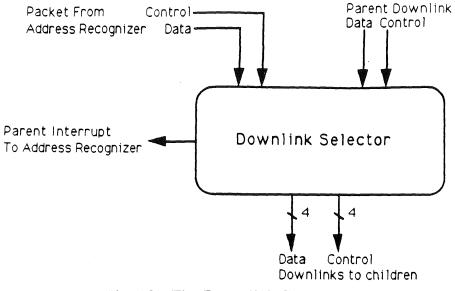

The Downlink Selector (fig. 8) can be reduced to its component parts.

- The Selector selects a packet either from the parent downlink or from the Address Recognizer to be broadcast to all the children switches. Priority is given to the parent downlink. So, if a packet from the parent downlink arrives during a packet transmission from the Address Recognizer, the selector will abort the packet transmission from the Address Recognizer. In addition, any packet from the Address Recognizer will be blocked during a parent downlink transmission.

- The *Flip-flop* is used to force the control line to go low when abortion happens. So if abortion occurs the control line will go to low,

indicating the end of the transmission of the packet from Address Recognizer. A station detects an abortion by checking the packet size indicated in the packet header and the actual size of the packet received.

Fig 8. CAMB Switch Downlink Selector

## 3.1.4. TTL Implementation - The Signals

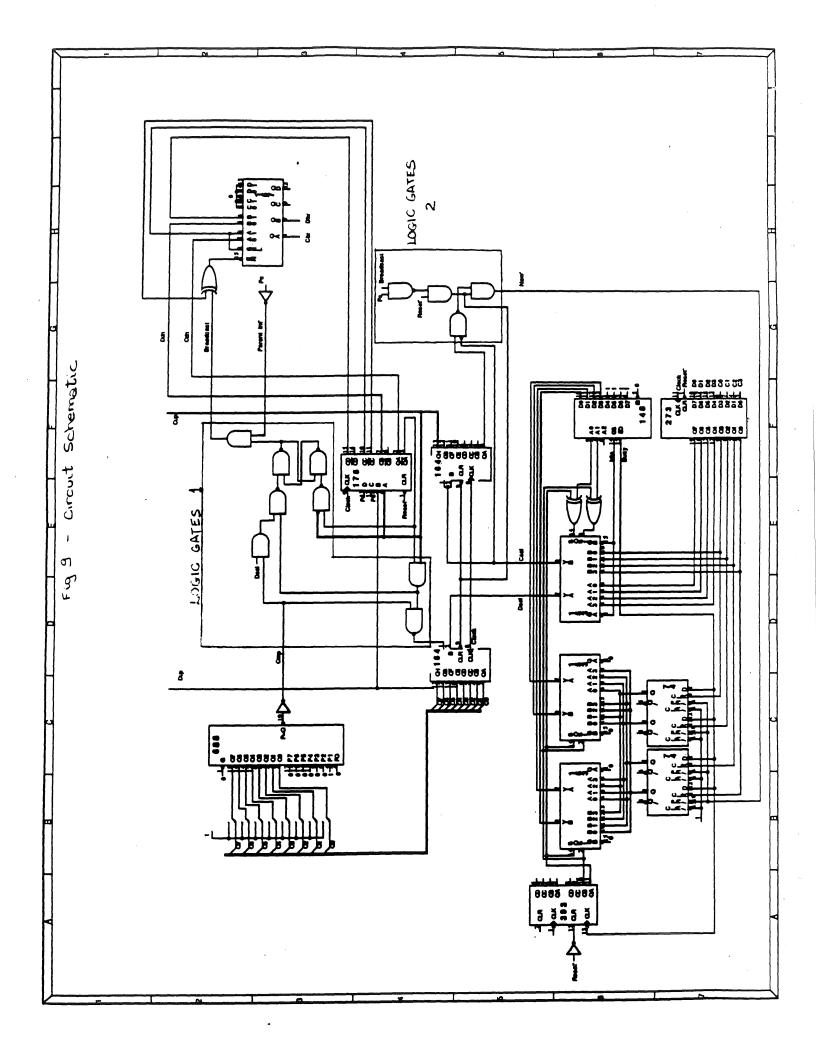

The next sections describes the implementation of the CAMB Tree Switch at the hardware level. A full schematic of the TTL tree switch is given in Figure 9. An explanation of the the signals shown is given below.

| Signal             | Purpose                                                    |  |  |

|--------------------|------------------------------------------------------------|--|--|

| (Inputs)           |                                                            |  |  |

| 10                 | Ground.                                                    |  |  |

| 1                  | Positive power lead.                                       |  |  |

| Clock              | A periodic clock signal.                                   |  |  |

| Reset'             | Master Reset: it activates the New' signal, aborting       |  |  |

|                    | any ongoing transmission, and readying the                 |  |  |

|                    | switch to receive a new packet.                            |  |  |

| D0D3               | Data inputs. An uplink or downlink line consists of        |  |  |

|                    | one data input, Dx, and one control input, Cx              |  |  |

|                    | $(1 \le x \le 3).$                                         |  |  |

| C0C3               | Control inputs.                                            |  |  |

| Pd                 | Parent downlink data line.                                 |  |  |

| Pc                 | Parent downlink control line.                              |  |  |

| (Internal signals) |                                                            |  |  |

| New'               | Resets the switch to receive a new packet. This signal     |  |  |

|                    | is complimented, i.e., the switch is reset when            |  |  |

|                    | New' is 0.                                                 |  |  |

| 1                  | New' resets the switch if one of the following events      |  |  |

|                    | occurs: 1) end of packet, 2) the parent                    |  |  |

|                    | downlink interrupts or blocks a packet from                |  |  |

|                    | the Address Recognizer, or 3) a Reset signal is            |  |  |

|                    | given.                                                     |  |  |

| Idle               | This signal is high when no packet is selected.            |  |  |

| Busy               | This signal is high when a packet is selected.             |  |  |

| Dsel               | Data line of the packet selected.                          |  |  |

| Csel               | Control line of the packet selected.                       |  |  |

| Стр                | It is 1 if the switch is the proper ancestor of the packet |  |  |

| <b>F</b>           | (destination address is equal to the switch                |  |  |

|                    | address and control bit is equal to 1).                    |  |  |

|                    | Otherwise is equal to 0.                                   |  |  |

| Broadcast          | This is equal to 1 when a packet from the Address          |  |  |

|                    | Recognizer is being broadcast.                             |  |  |

| Parent Int'        | Indicates that a packet from the parent downlink is        |  |  |

|                    | being broadcast.                                           |  |  |

| Ddn, Cdn           | These two signals carry packets to the Downlink            |  |  |

| , •••••            | Selector.                                                  |  |  |

|                    |                                                            |  |  |

| (Outputs)          |                                                            |  |  |

| Dup                | This signal is the parent switch data uplink. It will      |  |  |

| -                  | become some Dx on the input to the parent of               |  |  |

|                    | this switch.                                               |  |  |

| Cup                | This signal is the parent switch control uplink.           |  |  |

| Dbr                | This is the data downlink of the switch which carries a    |  |  |

|                    | broadcasted packet to 1-4 children switches or             |  |  |

|                    | devices.                                                   |  |  |

| Cbr                | This is the control downlink of the switch.                |  |  |

|                    |                                                            |  |  |

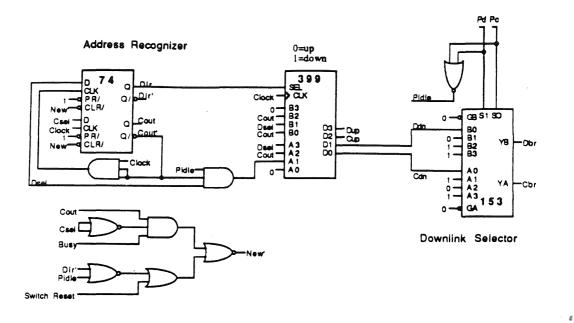

In figure 9, the entire tree switch node is drawn. This section will give a brief rundown of the different parts of the implementation.

On the lower half of the page is the Uplink Selector:

- The 273 at the bottom of the page is an eight-bit latch, and it receives the input from the switch uplinks. The latch functions as the Synchronizer in the Uplink Selector. The resister array just before the latch pulls down to zero (the idle state) any unconnected inputs.

- The two 74 chips (D flip-flops) directly above the 273 function as the Start Detector. They detect the rising edge of each control line at the start of a packet transmission.

- The Priority Encoder 148, the XOR gates, the two Multiplexers 153 and the Counter 393 function as the Priority Resolver. The XOR gates, the two Multiplexers 153 and the Counter 393 provide a rotating priority by shifting which line has priority at any given time. The 148 outputs the number of the selected input. This line is converted by the XOR gates to select the appropriate active incoming uplink.

- The upper half of the page contains the Address Recognizer and the Downlink Selector:

- The Comparator 688 compares the destination address with the switch address. The switch address is determined by a set of DPDT switches.

- The Shift Registers 164 store the destination address.

- The 175's flip-flops A and B are used to store the packet for one cycle while the address recognizer is being analyzed by the 688.

- The group of logic gates 1 form the Routing Logic and the Reset Control Bit Logic.

- The group of logic 2 forms the End Recognizer.

- The Multiplexer 157 acts as a selector.

- The Deglitcher/Resynchronizer realigns the outgoing signal with the clock.

- The End Recognizer detects the end of a transmitting packet and resets the Uplink Selector. The End Recognizer is also responsible for detecting an interrupting transmission from the parent downlink line. (Again: a transmission on the parent downlink will block or abort a broadcast transmission from the Address Recognizer.)

It is not necessary to fragment the last switch component, the Downlink Selector, into smaller pieces (fig. 12). The Downlink Selector's main function is to choose a packet from either the Address Recognizer or from the parent downlink, and broadcast that packet to all child switches. If a packet from the parent downlink arrives during a packet transmission from the Address Recognizer, the Downlink Selector will abort the packet transmission from the Address Recognizer. In addition, any packets from the Address Recognizer will be blocked during a parent downlink transmission.

Fig. 12: The Downlink Selector.

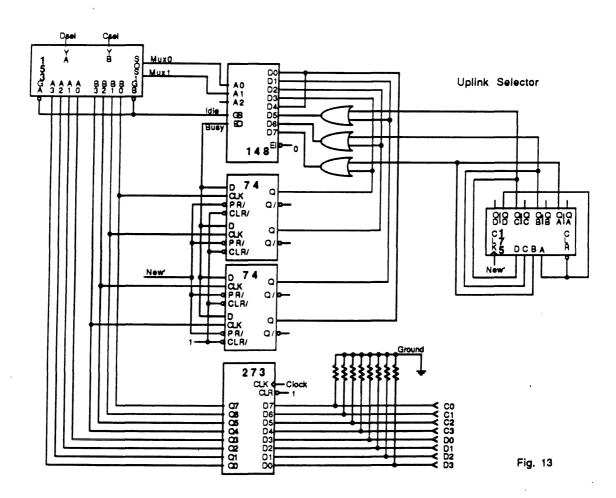

#### 3.2.2. TTL implementation.

This section describes an implementation of a CAMB Tree Switch at the hardware level. A full schematic of the TTL tree switch is given in Figure 13. An explanation of the signals shown is given below.

One of the main philosophies behind this TTL implementation of a CAMB Tree Switch, is to increase the throughput of the network by minimizing the time each transmission takes in the network. To accomplish this, each packet undergoes a short pre-processing step at its source station. How this processing takes place-- weather the processing occurs at the hardware interface, or at the software level-- will determine the final form of the addressing scheme and pre-processing algorithm used. For completeness, one possible addressing scheme and pre-processing algorithm is presented below.

| (Inputs)   Ground.     0   Ground.     1   Positive power lead.     Clock   A periodic clock signal.     Switch Reset   Switch Reset: it activates the New' signal, aborting any ongoing transmission, and readying the switch to receive a new packet.     D0D3   Data inputs. An uplink line consists of one data input, Dx, and one control input, Cx (0 ≤ x ≤ 3).     C0C3   Parent downlink data line.     Pc   Parent downlink control line.     (Internal signals)   This signal, generated by the End Recognizer, resets the switch to receive a new packet. The signal is complimented, i.e., the switch is reset when New' is 0.     New' resets the switch if one of the following events occurs: 1) end of packet, 2) the parent downlink interrupts or blocks a packet from the Address Recognizer, or 3) a Switch Reset signal is given.     Idle   This signal is high when no packet is selected.     Busy   This signal is high when a packet is selected by the Uplink Selector. Mux0 is the LSB.     Dsel   Data line of the packet selected.     Dir   Goes high when the switch is the least common ancestor of both the source and destination device, and low otherwise.     Cout   This is the new control signal for a packet exiting the switch.     Dir   Goes high when the parent downlink line is not transmitting a packet.     Diff   Goe                                                                                                                                                                                                                                                                               | Signal             | Purpose                                              |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|------------------------------------------------------|--|--|

| 0   Ground.     1   Positive power lead.     Clock   A periodic clock signal.     Switch Reset   Switch Reset: it activates the New' signal, aborting any ongoing transmission, and readying the switch to receive a new packet.     D0D3   Data inputs. An uplink line consists of one data input, Dx, and one control input, Cx (0 ≤ x ≤ 3).     C0C3   Control inputs.     Pd   Parent downlink data line.     Pc   Parent downlink control line.     (Internal signals)   This signal, generated by the End Recognizer, resets the switch to receive a new packet. The signal is complimented, i.e., the switch is reset when New' is 0.     New'   This signal is new control of packet, 2) the parent downlink interrupts or blocks a packet from the Address Recognizer, or 3) a Switch Reset signal is given.     Idle   This signal is high when a packet is selected.     Mux0, Mux1   These bits describe the uplink currently selected by the Uplink Selector. Mux0 is the LSB.     Dsel   Data line of the packet selected.     Cout   This is the new control signal for a packet exiting the switch.     Pidle   Goes high when the parent downlink line is not transmitting a packet.     Dup   This signal is the parent switch data uplink. It will become some Dx on the input to the parent of this switch (0 ≤ x ≤ 3).     Cout   This                                                                                                                                                                                                                                                                                             |                    |                                                      |  |  |

| 1   Positive power lead.     Clock   A periodic clock signal.     Switch Reset   Switch Reset: i activates the New' signal, aborting any ongoing transmission, and readying the switch to receive a new packet.     D0D3   Data inputs. An uplink line consists of one data input, Dx, and one control input, Cx (0 ≤ x ≤ 3).     C0C3   Parent downlink data line.     Pc   Parent downlink control line.     (Internal signals)   This signal, generated by the End Recognizer, resets the switch to receive a new packet. The signal is complimented, i.e., the switch is reset when New' is 0.     New'   This signal, generated by the End Recognizer, resets coccurs: 1) end of packet, 2) the parent downlink interrupts or blocks a packet from the Address Recognizer, or 3) a Switch Reset signal is given.     Idle   This signal is high when no packet is selected.     Busy   This signal is high when a packet is selected by the Uplink Selector. MuxO is the LSB.     Dsel   Data line of the packet selected.     Dir   Goes high when the switch is the least common ancestor of both the source and destination device, and low otherwise.     Cout   This signal is the parent downlink line is not transmitting a packet.     Dif   Goes high when the parent downlink line is not transmitting a packet.     Didn, Cdn   These two signals carry packets from the Address Recognizer to the Downlink Selector. </td <td></td> <td>Ground.</td>                                                                                                                                                                                   |                    | Ground.                                              |  |  |

| Clock   A periodic clock signal.     Switch Reset   Switch Reset: it activates the New' signal, aborting any ongoing transmission, and readying the switch to receive a new packet.     D0D3   Data inputs. An uplink line consists of one data input, Dx, and one control input, Cx (0 ≤ x ≤ 3).     C0C3   Parent downlink data line.     Pc   Parent downlink data line.     New'   This signal, generated by the End Recognizer, resets the switch to receive a new packet. The signal is complimented, i.e., the switch is reset when New' is 0.     New'   This signal, generated by the End Recognizer, resets the switch if one of the following events occurs: 1) end of packet, 2) the parent downlink interrupts or blocks a packet from the Address Recognizer, or 3) a Switch Reset signal is given.     Idle   This signal is high when no packet is selected.     Mux0, Mux1   These bits describe the uplink currently selected by the Uplink Selector. Mux0 is the LSB.     Dsel   Data line of the packet selected.     Csel   Control line of the packet selected.     Dir   Goes high when the switch is the least common ancestor of both the source and destination device, and low otherwise.     Cout   This signal is the parent downlink line is not transmitting a packet.     Dir   Goes high when the parent downlink line is not transmitting a packet.     Ddn, Cdn   These two signals carry packets from the Add                                                                                                                                                                                                       | 1                  |                                                      |  |  |

| Switch Reset   Switch Reset: it activates the New' signal, aborting<br>any ongoing transmission, and readying the<br>switch to receive a new packet.     D0D3   Data inputs. An uplink line consists of one data input,<br>Dx, and one control input, Cx (0 ≤ x ≤ 3).     C0C3   Parent downlink data line.     Pc   Parent downlink control line.     (Internal signals)   This signal, generated by the End Recognizer, resets<br>the switch to receive a new packet. The signal<br>is complimented, i.e., the switch is reset when<br>New' is 0.     New'   New' resets the switch if one of the following events<br>occurs: 1) end of packet, 2) the parent<br>downlink interrupts or blocks a packet from<br>the Address Recognizer, or 3) a Switch Reset<br>signal is given.     Idle   This signal is high when no packet is selected.     Mux0, Mux1   These bits describe the uplink currently selected by<br>the Uplink Selector. Mux0 is the LSB.     Dsel   Data line of the packet selected.     Dir   Goes high when the switch is the least common<br>ancestor of both the source and destination<br>device, and low otherwise.     Cout   This signal is the parent downlink line is not<br>transmitting a packet.     Didn, Cdn   These two signals carry packets from the Address<br>Recognizer to the Downlink Selector.     Oup   This signal is the parent switch data uplink. It will<br>become some Dx on the input to the parent of<br>this switch (0 ≤ x ≤ 3).     Dup   This signal is the parent switch control upli                                                                                                         | Clock              |                                                      |  |  |

| any ongoing transmission, and readying the switch to receive a new packet.     D0D3   Data inputs. An uplink line consists of one data input, Dx, and one control input, Cx (0 ≤ x ≤ 3).     C0C3   Parent downlink data line.     Pc   Parent downlink control line.     (Internal signals)   This signal, generated by the End Recognizer, resets the switch to receive a new packet. The signal is complimented, i.e., the switch is reset when New' is 0.     New'   This signal, generated by the following events occurs: 1) end of packet, 2) the parent downlink interrupts or blocks a packet from the Address Recognizer, or 3) a Switch Reset signal is high when no packet is selected.     Busy   This signal is high when no packet is selected.     Mux0, Mux1   These bits describe the uplink currently selected by the Uplink Selector. Mux0 is the LSB.     Dsel   Data line of the packet selected.     Dir   Goes high when the switch is the least common ancestor of both the source and destination device, and low otherwise.     Cout   This signal is the parent downlink line is not transmitting a packet.     Dif   Goes high when the parent downlink Selector.     Out   These two signals carry packets from the Address Recognizer to the Downlink Selector.     Out   This signal is the parent switch data uplink. It will become some Dx on the input to the parent of this switch (0 ≤ x ≤ 3).     Cout   This signal is                                                                                                                                                                                          | Switch Reset       | Switch Reset: it activates the New' signal, aborting |  |  |

| D0D3Data inputs. An uplink line consists of one data input,<br>Dx, and one control input, $Cx (0 \le x \le 3)$ .C0C3Control inputs.<br>Parent downlink data line.<br>Parent downlink control line.PcParent downlink control line.(Internal signals)<br>New'This signal, generated by the End Recognizer, resets<br>the switch to receive a new packet. The signal<br>is complimented, i.e., the switch is reset when<br>New' is 0.<br>New' resets the switch if one of the following events<br>occurs: 1) end of packet, 2) the parent<br>downlink interrupts or blocks a packet from<br>the Address Recognizer, or 3) a Switch Reset<br>signal is given.IdleThis signal is high when no packet is selected.BusyThis signal is high when a packet is selected.Mux0, Mux1These bits describe the uplink currently selected by<br>the Uplink Selector. Mux0 is the LSB.DselData line of the packet selected.CoutControl line of the packet selected.DirGoes high when the switch is the least common<br>ancestor of both the source and destination<br>device, and low otherwise.CoutThis signal is the new control signal for a packet exiting the<br>switch.PidleGoes high when the parent downlink line is not<br>transmitting a packet.OutThis signal is the parent switch data uplink. It will<br>become some Dx on the input to the parent of<br>this switch ( $0 \le x \le 3$ ).CupThis signal is the parent switch control uplink.DirCourse some Dx on the input to the parent of<br>this switch ( $0 \le x \le 3$ ).CourtThis signal is the parent switch control uplink.DifThis signal is the parent switch control uplink. <td></td> <td></td> |                    |                                                      |  |  |

| Dx, and one control input, Cx $(0 \le x \le 3)$ .<br>Control inputs.<br>Parent downlink data line.<br>Parent downlink control line.(Internal signals)<br>New'This signal, generated by the End Recognizer, resets<br>the switch to receive a new packet. The signal<br>is complimented, i.e., the switch is reset when<br>New' is 0.New'This signal, generated by the End Recognizer, resets<br>the switch to receive a new packet. The signal<br>is complimented, i.e., the switch is reset when<br>New' is 0.IdleThis signal is complimented, i.e., the switch is reset when<br>the Address Recognizer, or 3) a Switch Reset<br>signal is given.IdleThis signal is high when no packet is selected.Mux0, Mux1These bits describe the uplink currently selected by<br>the Uplink Selector. Mux0 is the LSB.DselData line of the packet selected.DirGoes high when the switch is the least common<br>ancestor of both the source and destination<br>device, and low otherwise.CoutThis signal is the parent downlink line is not<br>transmitting a packet.Ddn, CdnThese two signals carry packets from the Address<br>Recognizer to the Downlink Selector.Outputs)This signal is the parent switch data uplink. It will<br>become some Dx on the input to the parent of<br>this switch (0 $\le x \le 3$ ).CupThis signal is the parent switch control uplink.DbrThis signal is the parent switch control uplink.                                                                                                                                                                                                                                        |                    |                                                      |  |  |

| Pd   Parent downlink data line.     Pc   Parent downlink control line.     (Internal signals)   This signal, generated by the End Recognizer, resets the switch to receive a new packet. The signal is complimented, i.e., the switch is reset when New' is 0.     New'   This signal, generated by the End Recognizer, resets the switch if one of the following events occurs: 1) end of packet, 2) the parent downlink interrupts or blocks a packet from the Address Recognizer, or 3) a Switch Reset signal is given.     Idle   This signal is high when a packet is selected.     Busy   This signal is high when a packet is selected.     Mux0, Mux1   These bits describe the uplink currently selected by the Uplink Selector. Mux0 is the LSB.     Dsel   Data line of the packet selected.     Cisel   Control line of the packet selected.     Dir   Goes high when the switch is the least common ancestor of both the source and destination device, and low otherwise.     Cout   This is the new control signal for a packet exiting the switch.     Pidle   Goes high when the parent downlink line is not transmitting a packet.     Ddn, Cdn   These two signals carry packets from the Address Recognizer to the Downlink Selector.     Outputs)   This signal is the parent switch data uplink. It will become some Dx on the input to the parent of this switch (0 ≤ x ≤ 3).     Cup   This signal is the parent switch control                                                                                                                                                                                                 | D0D3               |                                                      |  |  |

| Pc   Parent downlink control line.     (Internal signals)   This signal, generated by the End Recognizer, resets the switch to receive a new packet. The signal is complimented, i.e., the switch is reset when New' is 0.     New' resets the switch if one of the following events occurs: 1) end of packet, 2) the parent downlink interrupts or blocks a packet from the Address Recognizer, or 3) a Switch Reset signal is given.     Idle   This signal is high when no packet is selected.     Busy   This signal is high when a packet is selected.     Mux0, Mux1   These bits describe the uplink currently selected by the Uplink Selector. Mux0 is the LSB.     Dsel   Data line of the packet selected.     Cosel   Control line of the packet selected.     Dir   Goes high when the switch is the least common ancestor of both the source and destination device, and low otherwise.     Cout   This signal is the parent downlink line is not transmitting a packet.     Ddn, Cdn   These two signals carry packets from the Address Recognizer to the Downlink Selector.     Cup   This signal is the parent switch data uplink. It will become some Dx on the input to the parent of this switch (0 ≤ x ≤ 3).     Cup   This signal is the parent switch control uplink.     Dbr   This signal is the parent switch control uplink.                                                                                                                                                                                                                                                                                                  | C0C3               | Control inputs.                                      |  |  |

| (Internal signals)   This signal, generated by the End Recognizer, resets the switch to receive a new packet. The signal is complimented, i.e., the switch is reset when New' is 0.     New' resets the switch if one of the following events occurs: 1) end of packet, 2) the parent downlink interrupts or blocks a packet from the Address Recognizer, or 3) a Switch Reset signal is given.     Idle   This signal is high when no packet is selected.     Busy   This signal is high when a packet is selected.     Mux0, Mux1   These bits describe the uplink currently selected by the Uplink Selector. Mux0 is the LSB.     Dsel   Data line of the packet selected.     Cisel   Control line of the switch is the least common ancestor of both the source and destination device, and low otherwise.     Cout   This signal is the parent downlink line is not transmitting a packet.     Ddn, Cdn   These two signals carry packets from the Address Recognizer to the Downlink Selector.     Coup   This signal is the parent switch data uplink. It will become some Dx on the input to the parent of this switch (0 ≤ x ≤ 3).     Cup   This signal is the parent switch control uplink.     Dbr   This signal is the parent switch control uplink.                                                                                                                                                                                                                                                                                                                                                                                      | 1                  | Parent downlink data line.                           |  |  |

| New'This signal, generated by the End Recognizer, resets<br>the switch to receive a new packet. The signal<br>is complimented, i.e., the switch is reset when<br>New' is 0.New' resets the switch if one of the following events<br>occurs: 1) end of packet, 2) the parent<br>downlink interrupts or blocks a packet from<br>the Address Recognizer, or 3) a Switch Reset<br>signal is given.IdleThis signal is high when no packet is selected.BusyThis signal is high when no packet is selected.Mux0, Mux1These bits describe the uplink currently selected by<br>the Uplink Selector. Mux0 is the LSB.DselData line of the packet selected.CiselControl line of the packet selected.DirGoes high when the switch is the least common<br>ancestor of both the source and destination<br>device, and low otherwise.CoutThis is the new control signal for a packet exiting the<br>switch.PidleGoes high when the parent downlink line is not<br>transmitting a packet.Ddn, CdnThese two signals carry packets from the Address<br>Recognizer to the Downlink Selector.CupThis signal is the parent switch data uplink. It will<br>become some Dx on the input to the parent of<br>this switch ( $0 \le x \le 3$ ).CupThis signal is the parent switch control uplink.DbrThis signal is the parent switch control uplink.                                                                                                                                                                                                                                                                                                                             | Pc                 | Parent downlink control line.                        |  |  |

| the switch to receive a new packet. The signal<br>is complimented, i.e., the switch is reset when<br>New' is 0.New' resets the switch if one of the following events<br>occurs: 1) end of packet, 2) the parent<br>downlink interrupts or blocks a packet from<br>the Address Recognizer, or 3) a Switch Reset<br>signal is given.IdleThis signal is high when no packet is selected.BusyThis signal is high when a packet is selected.Mux0, Mux1These bits describe the uplink currently selected by<br>the Uplink Selector. Mux0 is the LSB.DselData line of the packet selected.CoselControl line of the packet selected.DirGoes high when the switch is the least common<br>ancestor of both the source and destination<br>device, and low otherwise.CoutThis is the new control signal for a packet exiting the<br>switch.PidleGoes high when the parent downlink line is not<br>transmitting a packet.DupThis signal is the parent switch data uplink. It will<br>become some Dx on the input to the parent of<br>this switch ( $0 \le x \le 3$ ).CupThis signal is the parent switch control uplink.DbrThis signal is the parent switch control uplink.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | (Internal signals) |                                                      |  |  |

| is complimented, i.e., the switch is reset when<br>New' is 0.     New' resets the switch if one of the following events<br>occurs: 1) end of packet, 2) the parent<br>downlink interrupts or blocks a packet from<br>the Address Recognizer, or 3) a Switch Reset<br>signal is given.     Idle   This signal is high when no packet is selected.     Busy   This signal is high when a packet is selected.     Mux0, Mux1   These bits describe the uplink currently selected by<br>the Uplink Selector. Mux0 is the LSB.     Dsel   Data line of the packet selected.     Cisel   Control line of the packet selected.     Dir   Goes high when the switch is the least common<br>ancestor of both the source and destination<br>device, and low otherwise.     Cout   This is the new control signal for a packet exiting the<br>switch.     Pidle   Goes high when the parent downlink line is not<br>transmitting a packet.     Ddn, Cdn   These two signals carry packets from the Address<br>Recognizer to the Downlink Selector.     Outputs)   This signal is the parent switch data uplink. It will<br>become some Dx on the input to the parent of<br>this switch (0 ≤ x ≤ 3).     Cup   This signal is the parent switch control uplink.     Dbr   This is the data downlink of the switch which<br>broadcasts a packet to 1-4 children switches or<br>devices (stations).                                                                                                                                                                                                                                                                   | New'               | This signal, generated by the End Recognizer, resets |  |  |

| New' is 0.New' resets the switch if one of the following events<br>occurs: 1) end of packet, 2) the parent<br>downlink interrupts or blocks a packet from<br>the Address Recognizer, or 3) a Switch Reset<br>signal is given.IdleThis signal is high when no packet is selected.BusyThis signal is high when a packet is selected.Mux0, Mux1These bits describe the uplink currently selected by<br>the Uplink Selector. Mux0 is the LSB.DselData line of the packet selected.CselControl line of the packet selected.DirGoes high when the switch is the least common<br>ancestor of both the source and destination<br>device, and low otherwise.CoutThis is the new control signal for a packet exiting the<br>switch.PidleGoes high when the parent downlink line is not<br>transmitting a packet.Ddn, CdnThese two signals carry packets from the Address<br>Recognizer to the Downlink Selector.Outputs)This signal is the parent switch data uplink. It will<br>become some Dx on the input to the parent of<br>this switch ( $0 \le x \le 3$ ).CupThis signal is the parent switch control uplink.DbrThis is the data downlink of the switch which<br>broadcasts a packet to 1-4 children switches or<br>devices (stations).                                                                                                                                                                                                                                                                                                                                                                                                                    |                    |                                                      |  |  |

| occurs: 1) end of packet, 2) the parent<br>downlink interrupts or blocks a packet from<br>the Address Recognizer, or 3) a Switch Reset<br>signal is given.IdleThis signal is high when no packet is selected.BusyThis signal is high when a packet is selected.Mux0, Mux1These bits describe the uplink currently selected by<br>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                    |                                                      |  |  |

| downlink interrupis or blocks a packet from<br>the Address Recognizer, or 3) a Switch Reset<br>signal is given.IdleThis signal is high when no packet is selected.BusyThis signal is high when a packet is selected.Mux0, Mux1These bits describe the uplink currently selected by<br>the Uplink Selector. Mux0 is the LSB.DselData line of the packet selected.CselControl line of the packet selected.DirGoes high when the switch is the least common<br>ancestor of both the source and destination<br>device, and low otherwise.CoutThis is the new control signal for a packet exiting the<br>switch.PidleGoes high when the parent downlink line is not<br>transmitting a packet.Ddn, CdnThese two signals carry packets from the Address<br>Recognizer to the Downlink Selector.Outputs)This signal is the parent switch data uplink. It will<br>become some Dx on the input to the parent of<br>this switch ( $0 \le x \le 3$ ).CupThis is the data downlink of the switch which<br>broadcasts a packet to 1-4 children switches or<br>devices (stations).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                    |                                                      |  |  |

| the Address Recognizer, or 3) a Switch Reset<br>signal is given.IdleThis signal is high when no packet is selected.BusyThis signal is high when a packet is selected.Mux0, Mux1These bits describe the uplink currently selected by<br>the Uplink Selector. Mux0 is the LSB.DselData line of the packet selected.CselControl line of the packet selected.DirGoes high when the switch is the least common<br>ancestor of both the source and destination<br>device, and low otherwise.CoutThis is the new control signal for a packet exiting the<br>switch.PidleGoes high when the parent downlink line is not<br>transmitting a packet.Ddn, CdnThese two signals carry packets from the Address<br>Recognizer to the Downlink Selector.CuppThis signal is the parent switch data uplink. It will<br>become some Dx on the input to the parent of<br>this switch ( $0 \le x \le 3$ ).CupThis is the data downlink of the switch which<br>broadcasts a packet to 1-4 children switches or<br>devices (stations).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                    | occurs: 1) end of packet, 2) the parent              |  |  |

| signal is given.IdleThis signal is high when no packet is selected.BusyThis signal is high when a packet is selected.Mux0, Mux1These bits describe the uplink currently selected by<br>the Uplink Selector. Mux0 is the LSB.DselData line of the packet selected.CselControl line of the packet selected.DirGoes high when the switch is the least common<br>ancestor of both the source and destination<br>device, and low otherwise.CoutThis is the new control signal for a packet exiting the<br>switch.PidleGoes high when the parent downlink line is not<br>transmitting a packet.Ddn, CdnThese two signals carry packets from the Address<br>Recognizer to the Downlink Selector.Coutputs)This signal is the parent switch data uplink. It will<br>become some Dx on the input to the parent of<br>this switch ( $0 \le x \le 3$ ).CupThis signal is the parent switch control uplink.DbrThis signal is the parent switch control uplink.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                    |                                                      |  |  |

| IdleThis signal is high when no packet is selected.BusyThis signal is high when a packet is selected.Mux0, Mux1These bits describe the uplink currently selected by<br>the Uplink Selector. Mux0 is the LSB.DselData line of the packet selected.CselControl line of the packet selected.DirGoes high when the switch is the least common<br>ancestor of both the source and destination<br>device, and low otherwise.CoutThis is the new control signal for a packet exiting the<br>switch.PidleGoes high when the parent downlink line is not<br>transmitting a packet.Ddn, CdnThese two signals carry packets from the Address<br>Recognizer to the Downlink Selector.Outputs)This signal is the parent switch data uplink. It will<br>become some Dx on the input to the parent of<br>this switch ( $0 \le x \le 3$ ).CupThis signal is the data downlink of the switch which<br>broadcasts a packet to 1-4 children switches or<br>devices (stations).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                    |                                                      |  |  |

| BusyThis signal is high when a packet is selected.Mux0, Mux1These bits describe the uplink currently selected by<br>the Uplink Selector. Mux0 is the LSB.DselData line of the packet selected.CselControl line of the packet selected.DirGoes high when the switch is the least common<br>ancestor of both the source and destination<br>device, and low otherwise.CoutThis is the new control signal for a packet exiting the<br>switch.PidleGoes high when the parent downlink line is not<br>transmitting a packet.Ddn, CdnThese two signals carry packets from the Address<br>Recognizer to the Downlink Selector.Outputs)This signal is the parent switch data uplink. It will<br>become some Dx on the input to the parent of<br>this switch ( $0 \le x \le 3$ ).CupThis signal is the parent switch control uplink.DbrThis is the data downlink of the switch which<br>broadcasts a packet to 1-4 children switches or<br>devices (stations).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                    |                                                      |  |  |

| Mux0, Mux1These bits describe the uplink currently selected by<br>the Uplink Selector. Mux0 is the LSB.DselData line of the packet selected.CselControl line of the packet selected.DirGoes high when the switch is the least common<br>ancestor of both the source and destination<br>device, and low otherwise.CoutThis is the new control signal for a packet exiting the<br>switch.PidleGoes high when the parent downlink line is not<br>transmitting a packet.Ddn, CdnThese two signals carry packets from the Address<br>Recognizer to the Downlink Selector.Coutputs)This signal is the parent switch data uplink. It will<br>become some Dx on the input to the parent of<br>this switch ( $0 \le x \le 3$ ).CupThis signal is the parent switch control uplink.DbrThis is the data downlink of the switch which<br>broadcasts a packet to 1-4 children switches or<br>devices (stations).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                    |                                                      |  |  |

| the Uplink Selector. Mux0 is the LSB.DselData line of the packet selected.CselControl line of the packet selected.DirGoes high when the switch is the least common<br>ancestor of both the source and destination<br>device, and low otherwise.CoutThis is the new control signal for a packet exiting the<br>switch.PidleGoes high when the parent downlink line is not<br>transmitting a packet.Ddn, CdnThese two signals carry packets from the Address<br>Recognizer to the Downlink Selector.Coutputs)This signal is the parent switch data uplink. It will<br>become some Dx on the input to the parent of<br>this switch (0 ≤ x ≤ 3).CupThis signal is the parent switch control uplink.DbrThis is the data downlink of the switch which<br>broadcasts a packet to 1-4 children switches or<br>devices (stations).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                    |                                                      |  |  |

| DselData line of the packet selected.CselControl line of the packet selected.DirGoes high when the switch is the least common<br>ancestor of both the source and destination<br>device, and low otherwise.CoutThis is the new control signal for a packet exiting the<br>switch.PidleGoes high when the parent downlink line is not<br>transmitting a packet.Ddn, CdnThese two signals carry packets from the Address<br>Recognizer to the Downlink Selector.Outputs)This signal is the parent switch data uplink. It will<br>become some Dx on the input to the parent of<br>this switch ( $0 \le x \le 3$ ).CupThis signal is the parent switch control uplink.DbrThis is the data downlink of the switch which<br>broadcasts a packet to 1-4 children switches or<br>devices (stations).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Mux0, Mux1         |                                                      |  |  |

| CselControl line of the packet selected.DirGoes high when the switch is the least common<br>ancestor of both the source and destination<br>device, and low otherwise.CoutThis is the new control signal for a packet exiting the<br>switch.PidleGoes high when the parent downlink line is not<br>transmitting a packet.Ddn, CdnThese two signals carry packets from the Address<br>Recognizer to the Downlink Selector.(Outputs)This signal is the parent switch data uplink. It will<br>become some Dx on the input to the parent of<br>this switch (0 $\leq x \leq 3$ ).CupThis signal is the parent switch control uplink.DbrThis is the data downlink of the switch which<br>broadcasts a packet to 1-4 children switches or<br>devices (stations).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Dsel               |                                                      |  |  |

| DirGoes high when the switch is the least common<br>ancestor of both the source and destination<br>device, and low otherwise.CoutThis is the new control signal for a packet exiting the<br>switch.PidleGoes high when the parent downlink line is not<br>transmitting a packet.Ddn, CdnThese two signals carry packets from the Address<br>Recognizer to the Downlink Selector.(Outputs)This signal is the parent switch data uplink. It will<br>become some Dx on the input to the parent of<br>this switch ( $0 \le x \le 3$ ).CupThis signal is the parent switch control uplink.DbrThis is the data downlink of the switch which<br>broadcasts a packet to 1-4 children switches or<br>devices (stations).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Csel               |                                                      |  |  |

| ancestor of both the source and destination<br>device, and low otherwise.CoutThis is the new control signal for a packet exiting the<br>switch.PidleGoes high when the parent downlink line is not<br>transmitting a packet.Ddn, CdnThese two signals carry packets from the Address<br>Recognizer to the Downlink Selector.(Outputs)Image: Comparison of the parent switch data uplink. It will<br>become some Dx on the input to the parent of<br>this switch (0 $\leq x \leq 3$ ).CupThis signal is the parent switch control uplink.DbrThis is the data downlink of the switch which<br>broadcasts a packet to 1-4 children switches or<br>devices (stations).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                    |                                                      |  |  |

| device, and low otherwise.CoutThis is the new control signal for a packet exiting the<br>switch.PidleGoes high when the parent downlink line is not<br>transmitting a packet.Ddn, CdnThese two signals carry packets from the Address<br>Recognizer to the Downlink Selector.(Outputs)Image: Comparison of the signal is the parent switch data uplink. It will<br>become some Dx on the input to the parent of<br>this switch ( $0 \le x \le 3$ ).CupThis signal is the parent switch control uplink.DbrThis is the data downlink of the switch which<br>broadcasts a packet to 1-4 children switches or<br>devices (stations).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 21                 |                                                      |  |  |

| CoutThis is the new control signal for a packet exiting the<br>switch.PidleGoes high when the parent downlink line is not<br>transmitting a packet.Ddn, CdnThese two signals carry packets from the Address<br>Recognizer to the Downlink Selector.(Outputs)This signal is the parent switch data uplink. It will<br>become some Dx on the input to the parent of<br>this switch $(0 \le x \le 3)$ .CupThis signal is the parent switch control uplink.DbrThis is the data downlink of the switch which<br>broadcasts a packet to 1-4 children switches or<br>devices (stations).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                    |                                                      |  |  |

| switch.PidleGoes high when the parent downlink line is not<br>transmitting a packet.Ddn, CdnThese two signals carry packets from the Address<br>Recognizer to the Downlink Selector.(Outputs)This signal is the parent switch data uplink. It will<br>become some Dx on the input to the parent of<br>this switch ( $0 \le x \le 3$ ).CupThis signal is the parent switch control uplink.DbrThis is the data downlink of the switch which<br>broadcasts a packet to 1-4 children switches or<br>devices (stations).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Cout               |                                                      |  |  |

| PidleGoes high when the parent downlink line is not<br>transmitting a packet.Ddn, CdnThese two signals carry packets from the Address<br>Recognizer to the Downlink Selector.(Outputs)This signal is the parent switch data uplink. It will<br>become some Dx on the input to the parent of<br>this switch ( $0 \le x \le 3$ ).CupThis signal is the parent switch control uplink.DbrThis is the data downlink of the switch which<br>broadcasts a packet to 1-4 children switches or<br>devices (stations).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                    |                                                      |  |  |

| transmitting a packet.Ddn, CdnThese two signals carry packets from the Address<br>Recognizer to the Downlink Selector.(Outputs)This signal is the parent switch data uplink. It will<br>become some Dx on the input to the parent of<br>this switch ( $0 \le x \le 3$ ).CupThis signal is the parent switch control uplink.DbrThis is the data downlink of the switch which<br>broadcasts a packet to 1-4 children switches or<br>devices (stations).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Pidle              |                                                      |  |  |

| Ddn, Cdn   These two signals carry packets from the Address<br>Recognizer to the Downlink Selector.     (Outputs)   This signal is the parent switch data uplink. It will<br>become some Dx on the input to the parent of<br>this switch (0 ≤ x ≤ 3).     Cup   This signal is the parent switch control uplink.     Dbr   This is the data downlink of the switch which<br>broadcasts a packet to 1-4 children switches or<br>devices (stations).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                    |                                                      |  |  |