# UNIVERSITY OF CALIFORNIA, IRVINE

Aging-induced Performance Degradation: Monitoring and Mitigation

#### DISSERTATION

submitted in partial satisfaction of the requirements for the degree of

#### DOCTOR OF PHILOSOPHY

in Computer Science

by

Zana Ghaderi

Dissertation Committee: Professor Nader Bagherzadeh, Chair Professor Isaac Scherson Professor Jean-Luc Gaudiot

$\bigodot$  2017 Zana Ghaderi

## DEDICATION

#### To my family; Zaher, Maryam, Dana, and Arina

"Listen," said Pugatschew, with a sort of wild enthusiasm, "I shall tell you a fable which I have heard in my infancy, from an old Kalmouk woman. Once upon a time the eagle asked the raven:-'tell me my good raven how is it that your race lives to the age of three hundred years, whilst we eagles only live to the age of thirty three?'-' The reason, my good sir, is, because you devour your prey alive whilst we live upon dead carcasses.' The eagle thought, well, I shall try that too. They thereupon went out together and found a dead horse. They alighted upon it. The raven began to feed and enjoyed it. The eagle tried several morsels, then shook his pinions, and said to the raven:'-Nay, brother raven, rather than live three hundred years upon dead horses, I once feast upon a live victim, and then let fate do its worst.

Alexander Pushkin, The Captain's Daughter. Ch. XI, P. 117. 1836.

## TABLE OF CONTENTS

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Page                                                                                                      |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|

| LIST OF FIGURES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | vi                                                                                                        |

| LIST OF TABLES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ix                                                                                                        |

| LIST OF ALGORITHMS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | x                                                                                                         |

| ACKNOWLEDGMENTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | xi                                                                                                        |

| CURRICULUM VITAE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | xii                                                                                                       |

| ABSTRACT OF THE DISSERTATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | xvi                                                                                                       |

| 1       Introduction         1.1       Aging background                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | $\begin{array}{cccc} \cdot & \cdot & \cdot & \cdot & 7 \\ \cdot & \cdot & \cdot & \cdot & 12 \end{array}$ |

| 2       SENSIBLE, a novel scalable low-overhead aging sensor design         2.1       State-of-the-art aging sensors for FPGAs         2.2       Our novel proposed aging sensor (SENSIBLE)         2.3       SENSIBLE vs. state-of-the-art works         2.4       Aging-aware representative critical paths selection         2.5       Experiment         2.5.1       Setup         2.5.2       Sensor insertion         2.5.3       Results and discussion         2.6       Utilized aging-induced delay degradation model         2.7       Chapter summary | 21          25          28          31          31                                                        |

| <ul> <li>3 Aging-aware representative critical path selection for FPGAs</li> <li>3.1 Related works on RCP selection for age monitoring</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                  | 44<br>45<br>45                                                                                            |

|          | 3.4  | Experiment                                                                       | 53  |

|----------|------|----------------------------------------------------------------------------------|-----|

|          |      | 3.4.1 Insertion flow and setup                                                   | 53  |

|          |      | 3.4.2 Results and discussion                                                     | 54  |

|          |      | 3.4.3 Evaluation of the proposed filtering algorithm                             | 57  |

|          | 3.5  | Chapter summary                                                                  | 57  |

| 4        | Agi  | ng-aware physical planning for FPGAs                                             | 60  |

|          | 4.1  | Related work                                                                     | 62  |

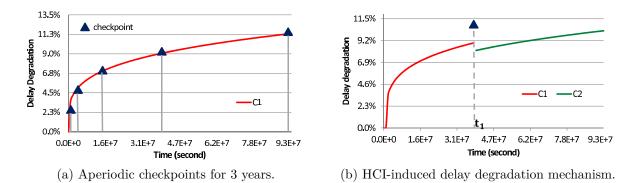

|          | 4.2  | Aging-induced delay degradation estimation in FPGAs                              | 63  |

|          |      | 4.2.1 BTI aging effect.                                                          | 63  |

|          |      | 4.2.2 HCI aging effect                                                           | 64  |

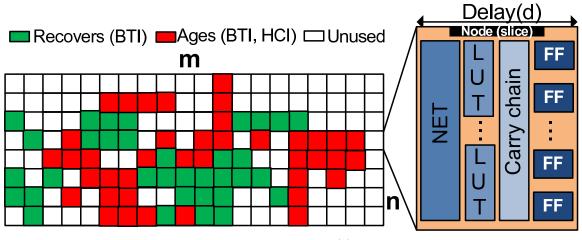

|          |      | 4.2.3 Aged-delay map                                                             | 64  |

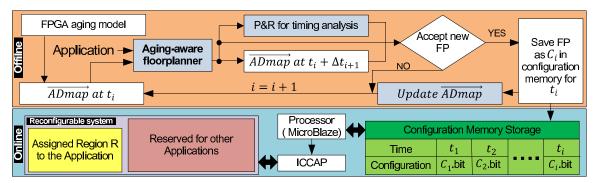

|          | 4.3  | Problem formulation                                                              | 67  |

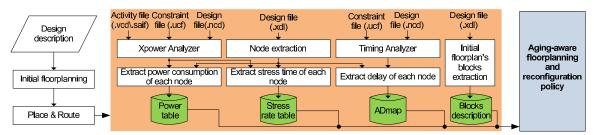

|          | 4.4  | The proposed aging-aware physical planning and reconfiguration policy            | 67  |

|          | 4.5  | Experiments                                                                      | 73  |

|          |      | 4.5.1 Setup                                                                      | 73  |

|          |      | 4.5.2 Results and discussion                                                     | 74  |

|          | 4.6  | Chapter summary                                                                  | 79  |

| <b>5</b> | Stre | ess-aware Boolean matching to protect SRAM cells in FPGAs                        | 80  |

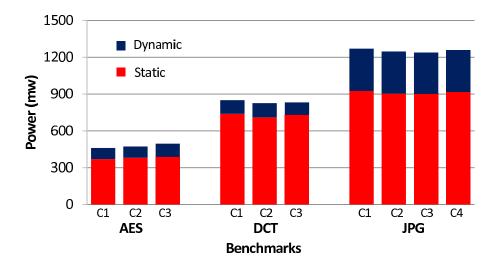

| 0        | 5.1  | BTI aging impact on SRAM                                                         | 83  |

|          | 0.1  | 5.1.1 BTI aging modeling                                                         | 83  |

|          |      | 5.1.2 BTI-induced SNM reduction in SRAM                                          | 85  |

|          | 5.2  | FPGA susceptibility to aging                                                     | 87  |

|          | 5.3  | Related works and motivation                                                     | 88  |

|          | 5.4  | SAT-based Boolean matching (BM) overview                                         | 90  |

|          | 5.5  | Problem formulation                                                              | 91  |

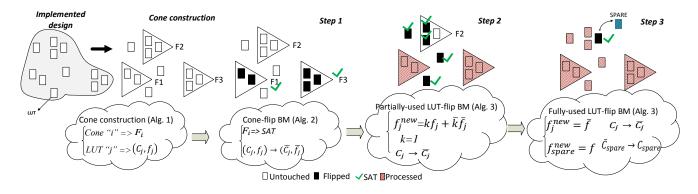

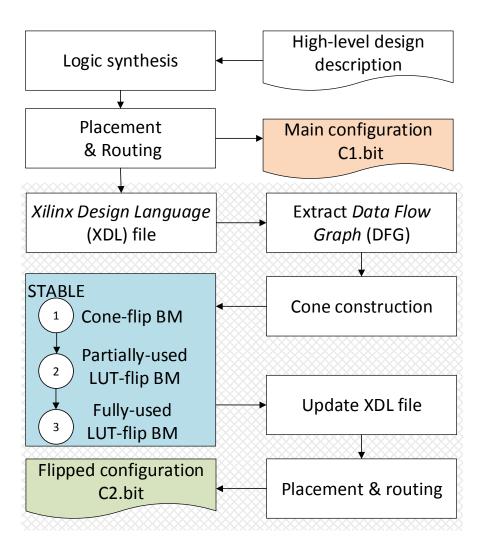

|          | 5.6  | STABLE, stress-aware Boolean matching                                            | 92  |

|          | 0.0  | 5.6.1 Cone construction                                                          | 93  |

|          |      | 5.6.2 Cone-flip Boolean matching (Step one)                                      | 96  |

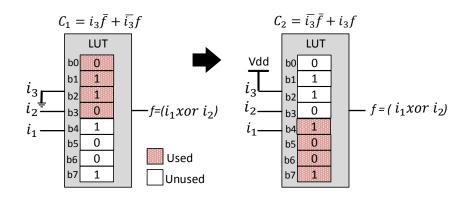

|          |      | 5.6.3 Partially-used LUT-flip Boolean matching (Step two)                        | 97  |

|          |      | 5.6.4 Fully-used LUT-flip Boolean matching (Step three)                          | 100 |

|          | 5.7  | Experimental evaluation                                                          | 101 |

|          | 0.1  | 5.7.1 Setup                                                                      | 102 |

|          |      | 5.7.2 Results                                                                    | 102 |

|          |      | 5.7.3 Analysis and discussion                                                    | 107 |

|          | 5.8  | Cone size impact on the run time of step 1                                       | 110 |

|          | 5.9  |                                                                                  | 112 |

| c        |      | ANANT aging among tool, manning in hotonogonoong multiprocessor                  |     |

| 6        | AD   | AMANT, aging-aware task mapping in heterogeneous multiprocessor<br>architectures | 113 |

|          | 6.1  | Related work and motivation                                                      | 115 |

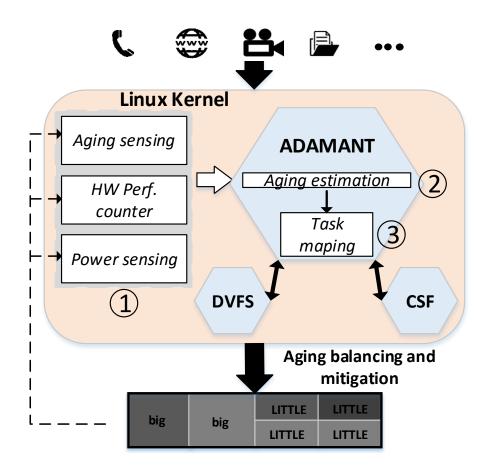

|          | 6.2  | ADAMANT framework overview                                                       | 118 |

|          | 6.3  | System model and metrics                                                         | 119 |

|          | 6.4  | *                                                                                | 121 |

|    | 6.5   | Aging-aware task mapping                                            | 5 |

|----|-------|---------------------------------------------------------------------|---|

|    |       | 6.5.1 Task mapping algorithm                                        | 6 |

|    |       | 6.5.2 Iterative performance/power prediction                        | 8 |

|    |       | 6.5.3 Complexity analysis                                           | 0 |

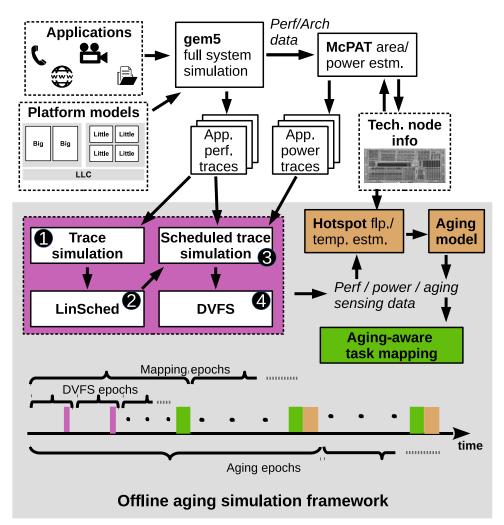

|    | 6.6   | Experimental evaluation                                             | 0 |

|    |       | 6.6.1 Setup                                                         | 0 |

|    |       | 6.6.2 Workloads                                                     | 2 |

|    |       | 6.6.3 Results and discussion                                        | 3 |

|    | 6.7   | Chapter summary                                                     | 7 |

| 7  | AR    | OMa, a novel aging-aware adaptive routing and online monitoring for |   |

| •  |       | 3D and 2D NoCs                                                      | 8 |

|    | 7.1   | 3D NoC background                                                   | 3 |

|    | 7.2   | Aging-induced delay degradation background                          | 5 |

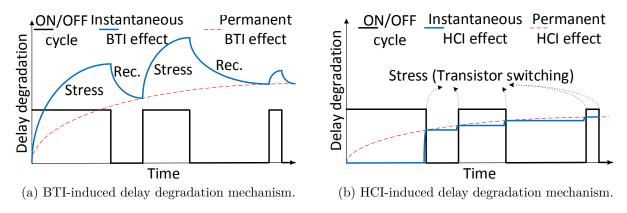

|    |       | 7.2.1 BTI aging impact                                              | 6 |

|    |       | 7.2.2 HCI aging impact                                              | 7 |

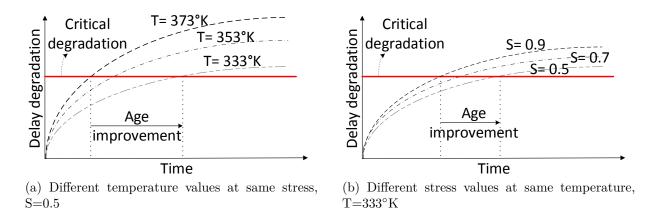

|    |       | 7.2.3 Joint impact of BTI and HCI                                   | 8 |

|    | 7.3   | Problem formulation                                                 | 1 |

|    | 7.4   | Online aging monitoring in 3D NoC                                   | 2 |

|    |       | 7.4.1 D-CAT construction algorithm                                  | 7 |

|    | 7.5   | Adaptive aging-aware routing 15                                     | 8 |

|    |       | 7.5.1 Adaptive aging-aware routing algorithm in AROMa               | 1 |

|    | 7.6   | Related work                                                        | 2 |

|    |       | 7.6.1 Congestion aware adaptive routings                            | 3 |

|    |       | 7.6.2 Fault tolerant adaptive routings                              | 4 |

|    |       | 7.6.3 Aging-aware adaptive routings and motivation                  | 5 |

|    | 7.7   | Experimental evaluation                                             | 6 |

|    |       | 7.7.1 Setup                                                         | 6 |

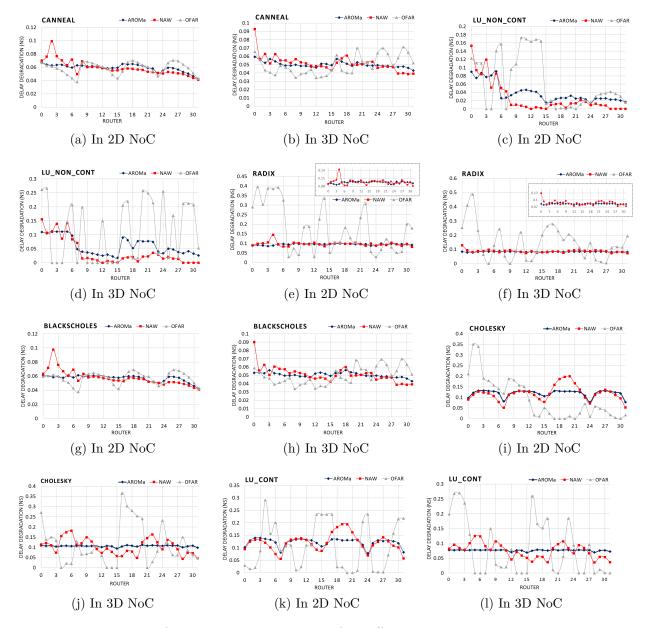

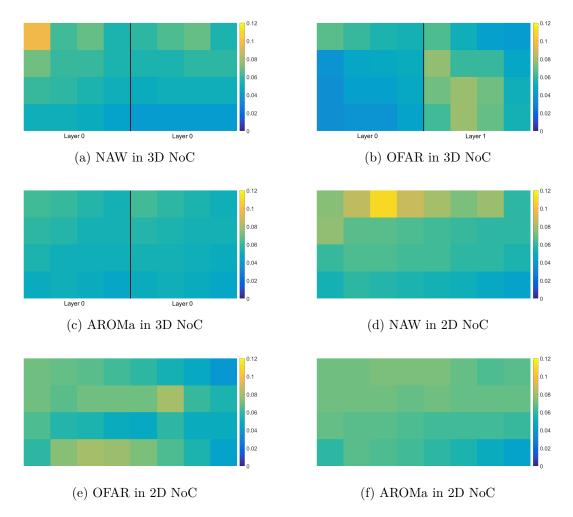

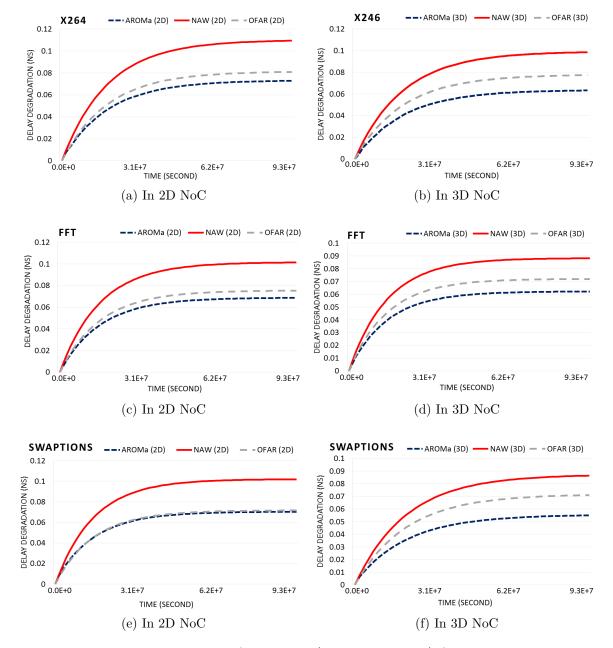

|    |       | 7.7.2 Results $\ldots$ $\ldots$ $\ldots$ $16$                       | 9 |

|    |       | 7.7.3 Analysis and discussions                                      | 4 |

|    |       | 7.7.4 Overhead                                                      |   |

|    | 7.8   | Chapter summary                                                     | 0 |

| 8  | Con   | nclusion 18                                                         | 2 |

|    |       | 8.0.1 Future work                                                   | 4 |

| Bi | bliog | graphy 18                                                           | 6 |

## LIST OF FIGURES

### Page

| $1.1 \\ 1.2 \\ 1.3 \\ 1.4 \\ 1.5 \\ 1.6$                                                                   | PMOS transistor cross section illustration during NBTI.       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       . | $     \begin{array}{r}       3 \\       3 \\       4 \\       5 \\       8 \\       10 \\     \end{array} $ |

|------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|

| $\begin{array}{c} 2.1 \\ 2.2 \\ 2.3 \\ 2.4 \\ 2.5 \\ 2.6 \\ 2.7 \\ 2.8 \\ 2.9 \\ 2.10 \\ 2.11 \end{array}$ | Multiple aging sensor architecture in FPGAs.Block diagram of SENSIBLE.MCLK and SCLK representation.The sensor operation in the presence of late transition happened due to aging.Sensor design.Sensor implementation on FPGA resources.Sensor insertion flow.On board sensor sensitivity-test flow.Aging sensitivity comparison.Aging sensor displacement (15 inserted sensors).Temperature map impact on critical path aging.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | $18 \\ 21 \\ 22 \\ 23 \\ 26 \\ 27 \\ 32 \\ 35 \\ 36 \\ 37 \\ 40$                                            |

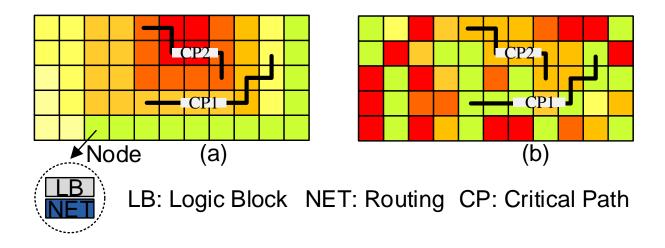

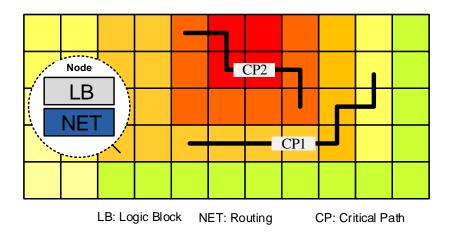

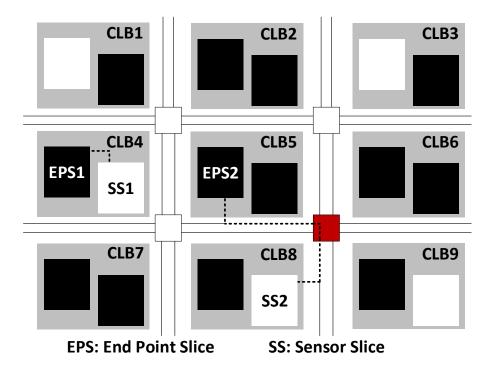

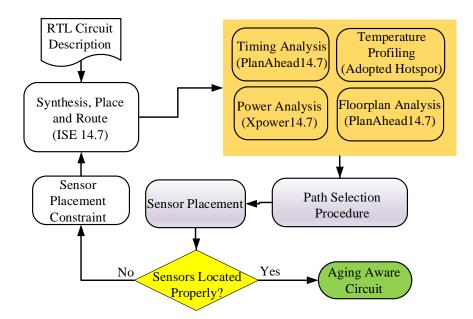

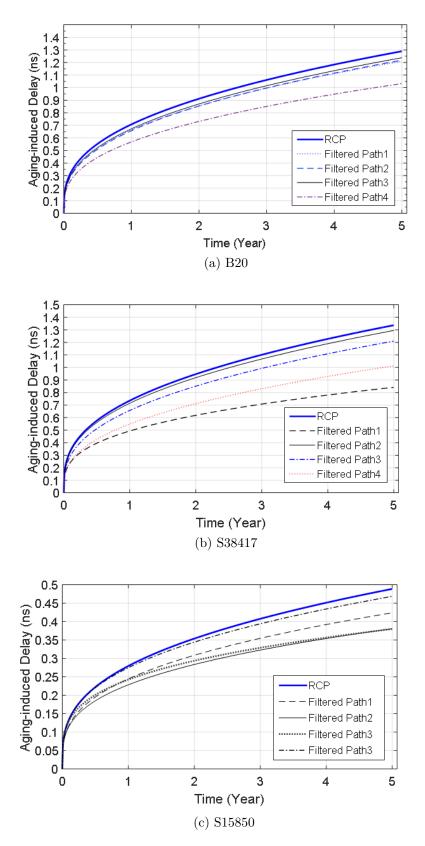

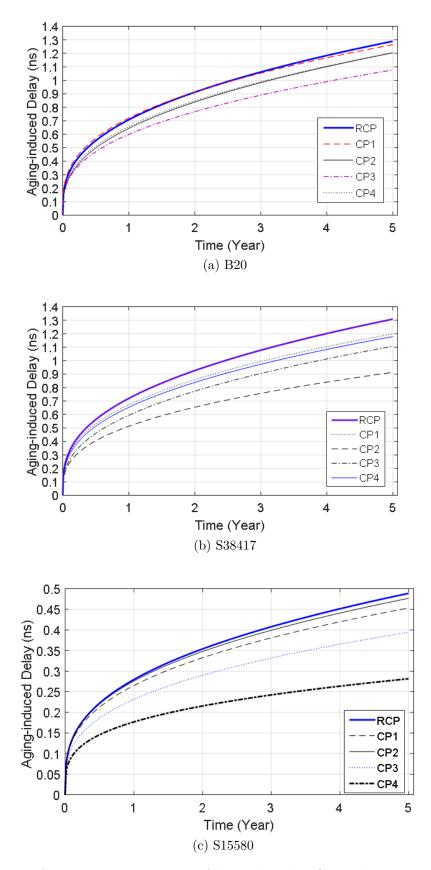

| 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7                                                              | Temperature map impact on critical path aging                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | $\begin{array}{c} 45 \\ 47 \\ 51 \\ 52 \\ 55 \\ 56 \\ 58 \end{array}$                                       |

| $\begin{array}{c} 4.1 \\ 4.2 \\ 4.3 \\ 4.4 \\ 4.5 \\ 4.6 \\ 4.7 \end{array}$                               | Aging-induced Average Delay Degradation, $\Delta d(t)$ , in FPGA (BTI and HCI).<br>Aged-Delay Map, ADmap(t), of region $R$ at time $t_i$ Aging-aware high-level physical planning and reconfiguration framework Generation of required data for aging-aware floorplanner Critical path delay with aperiodic checkpoints for reconfiguration Power consumption of different accepted configurations in each benchmark .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 63<br>65<br>67<br>73<br>76<br>76<br>78                                                                      |

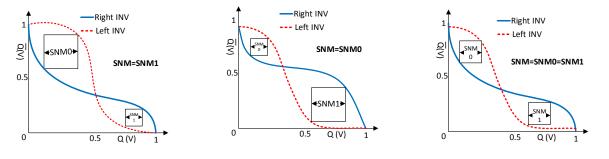

| 5.1  | Architecture of SRAM and its SNM.                                                         | 81        |

|------|-------------------------------------------------------------------------------------------|-----------|

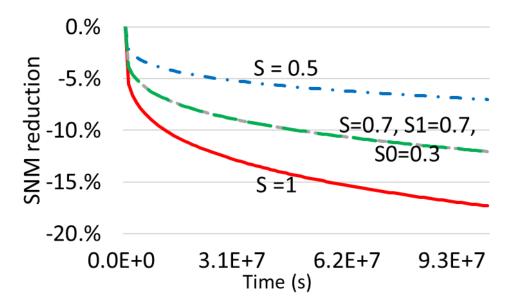

| 5.2  | SNM reduction in different scenarios                                                      | 82        |

| 5.3  | Impact of different stress (S) amount on SNM reduction at worst case $(T=375K)$           |           |

|      | after three years in 40nm technology. $SNM_{t_0} = 250$ mV                                | 85        |

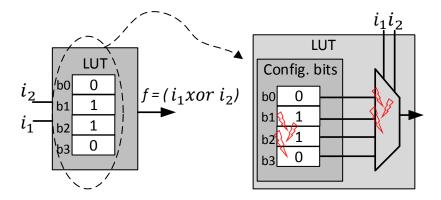

| 5.4  | LUT components and their sensitivity to aging.                                            | 88        |

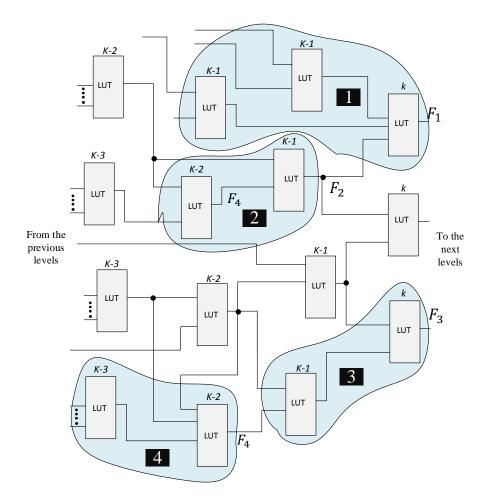

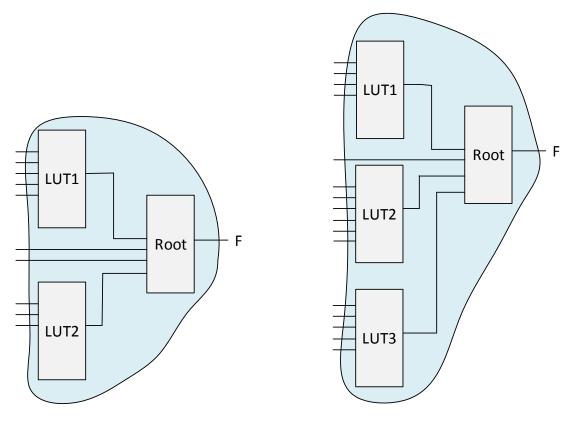

| 5.5  | Partitioning the Data Flow Graph (DFG) to cones.                                          | 93        |

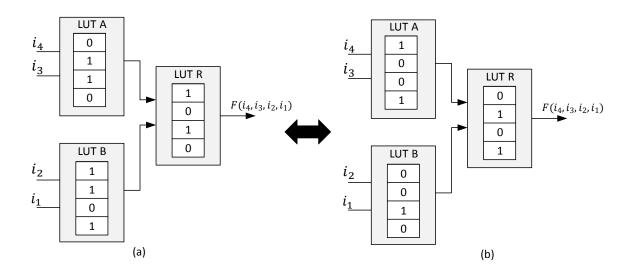

| 5.6  | Cone flip motivation; one cone with two complemented configuration bits, (a)              |           |

|      | and (b), and same function                                                                | 94        |

| 5.7  | The STABLE, stress-aware Boolean Matching                                                 | 94        |

| 5.8  | C1 and C2 represent the same function using different configuration bits inside           |           |

|      | on LUT                                                                                    | 98        |

| 5.9  | STABLE implementation flow                                                                | 101       |

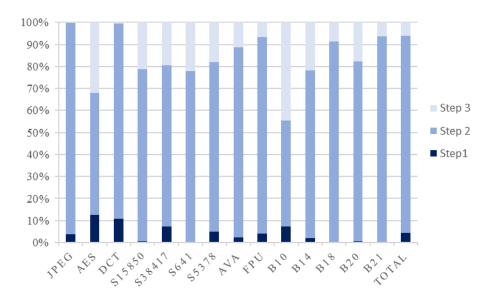

| 5.10 | LUT Coverage in each step of STABLE                                                       | 104       |

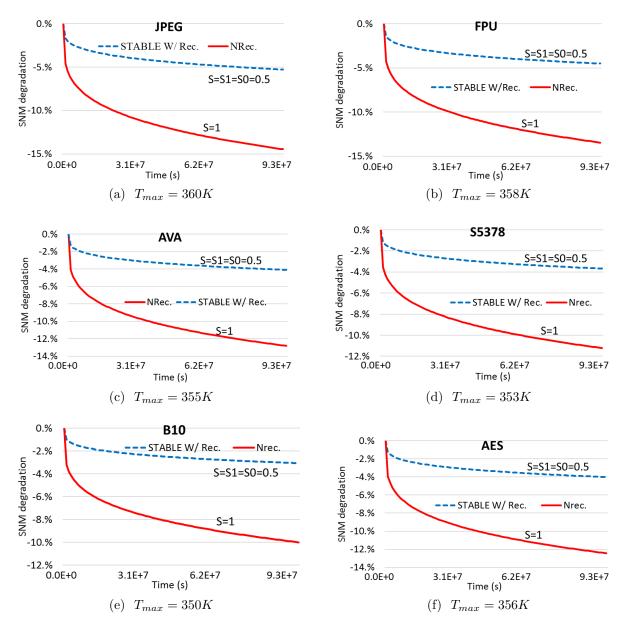

| 5.11 | SNM degradation comparison in 3 years (9.6E+7 seconds). $\ldots$ $\ldots$ $\ldots$        | 106       |

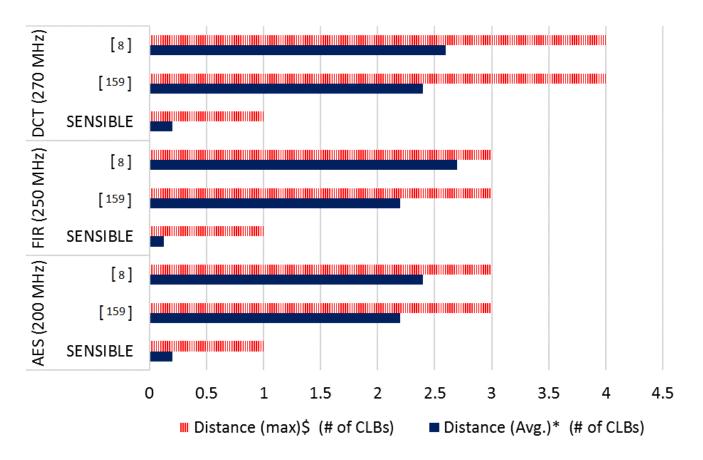

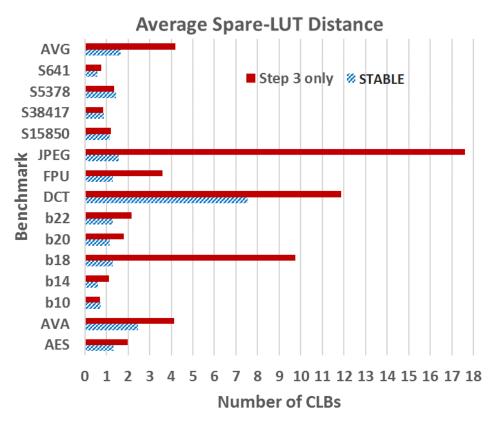

| 5.12 | Comparison of average distance of spare LUT from main LUT between Step                    |           |

|      | 3 and STABLE (Step 1, Step 2, and Step 3)                                                 | 108       |

| 5.13 | Cones with different size                                                                 | 111       |

| C 1  | (a) The ditional tools meaning (b) A sing energy tools meaning with DVEC                  |           |

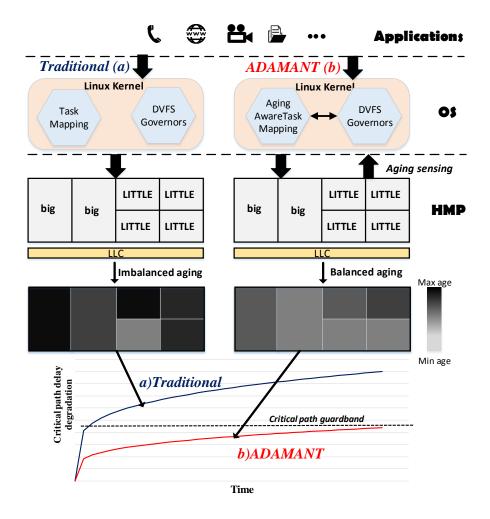

| 6.1  | (a) Traditional task mapping. (b) Aging-aware task mapping with DVFS.                     |           |

|      | Due to wearout caused by the aging imbalance in (a), the circuit critical path            | 11/       |

| 6.9  | delay may violate its operating frequency guardband                                       | 114       |

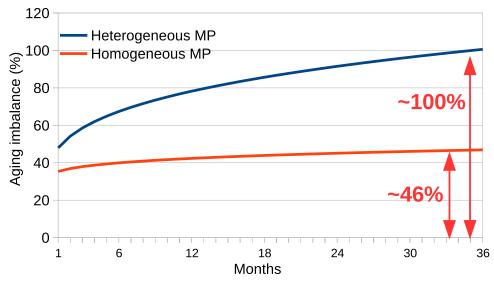

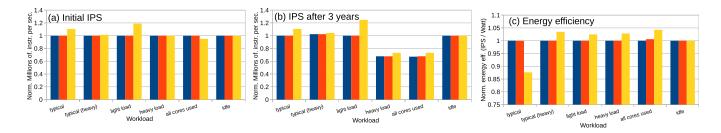

| 6.2  | Relative difference between the most and the least aged cores in homogeneous              |           |

|      | and heterogeneous architectures. <i>typical</i> workload (Table 6.2). GTS scheduling [14] | 116       |

| 6.3  | ing [14]                                                                                  | 110       |

| 6.4  | Relative difference between the most and the least aged cores in homogeneous              | 120       |

| 0.4  | and heterogeneous architectures. <i>typical</i> workload (Table 6.2). GTS schedul-        |           |

|      | ing $[14]$                                                                                | 131       |

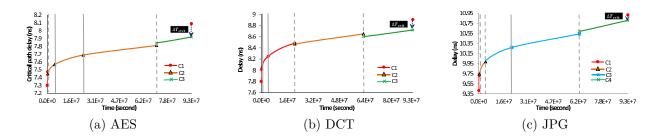

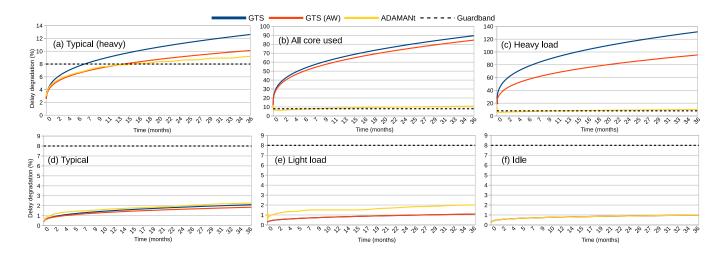

| 6.5  | Delay degradation. In the (f) <i>Idle</i> case, only background OS services are run-      | 101       |

| 0.0  | ning with no active tasks                                                                 | 133       |

| 6.6  | Performance degradation under DVFS frequency capping                                      | 133 $134$ |

| 0.0  | renormance degradation under DVFS frequency capping                                       | 104       |

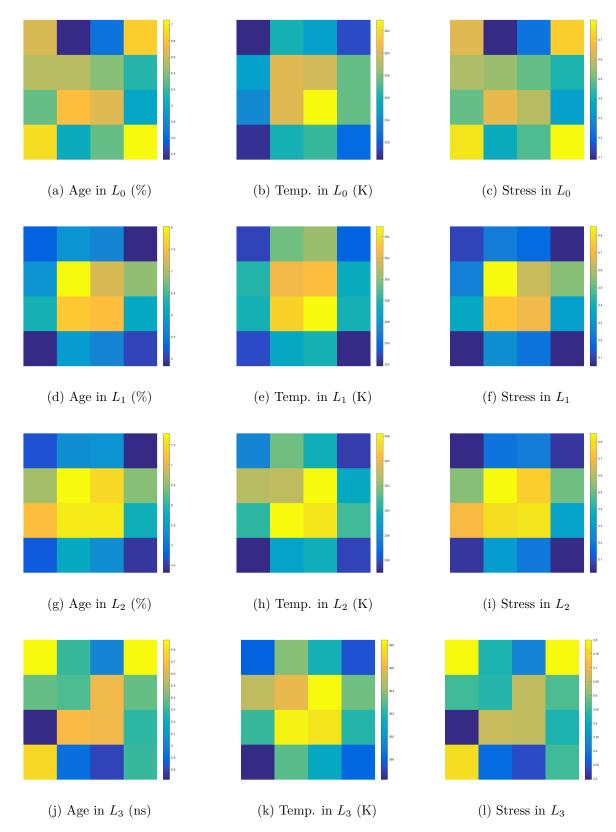

| 7.1  | Age, temperature (Temp.) and stress maps in each layer $L_i$ of 3D NoC (4 $\times$        |           |

|      | $4 \times 4$ ) for uniform random distribution                                            | 140       |

| 7.2  | Comparison of 2D and 3D NoC area overheads.                                               | 143       |

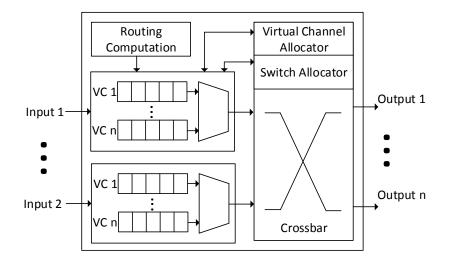

| 7.3  | Router components and architecture.                                                       | 144       |

| 7.4  | BTI and HCI aging mechanisms dependency on stress.                                        | 146       |

| 7.5  | Temperature and stress impacts on delay degradation.                                      | 148       |

| 7.6  | Different delay degradation due to temperature and stress in consecutive time             |           |

|      | periods.                                                                                  | 150       |

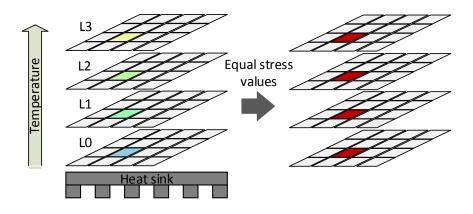

| 7.7  | Routers in different layers of 3D NoCs with equal amount of stresses have                 |           |

|      | different temperatures                                                                    | 153       |

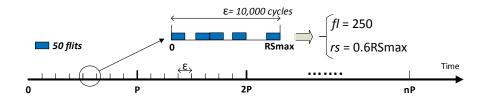

| 7.8  | Age monitoring at each period of $P$ at each layer $L_i$                                  | 154       |

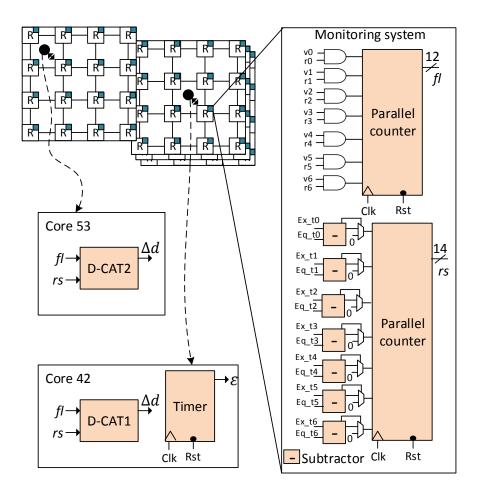

| 7.9  | AROMa online aging monitoring architecture. Other cores (black circles) and               |           |

|      | two D-CATs are not shown for clarity)                                                     | 156       |

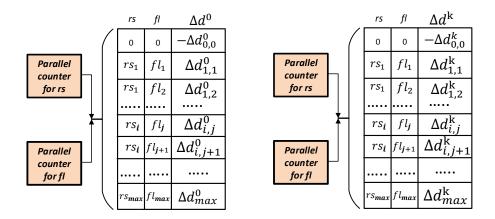

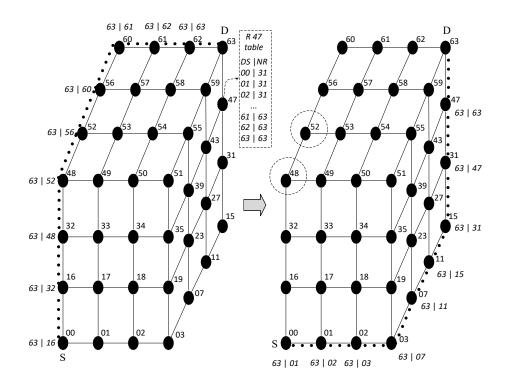

| 7.10 | D-CATs for layer $L_0$ and layer $L_k$                                          | 157 |

|------|---------------------------------------------------------------------------------|-----|

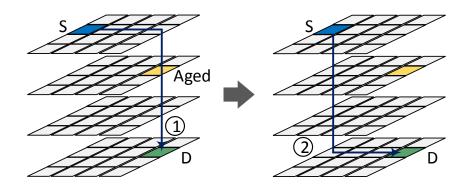

| 7.11 | Swapping between different shortest paths that have different routers' ages     | 159 |

| 7.12 | Updating routers' routing tables' entries for the new shortest path from S to D |     |

|      | considering high aging in routers number 48 and 52. Routing table is detailed   |     |

|      | for router number 47                                                            | 160 |

| 7.13 | Age imbalance in 3 years for different routers in the network                   | 172 |

| 7.14 | Age imbalance between different routers in X264.                                | 173 |

| 7.15 | Delay degradation for 3 years (9.3E+7 seconds) for maximum aged routers in      |     |

|      | the network                                                                     | 176 |

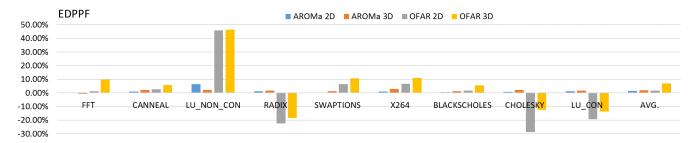

| 7.16 | EDPPF for 3-year (9.3E+7 seconds) execution time in each benchmark for          |     |

|      | different schemes                                                               | 178 |

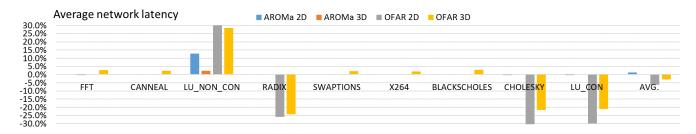

| 7.17 | Average network latency for 3-year (9.3E+7 seconds) execution time in each      |     |

|      | benchmark for different schemes.                                                | 178 |

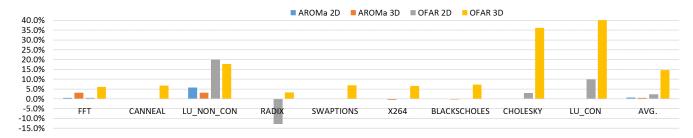

| 7.18 | Link utilization for 3-year (9.3E+7 seconds) execution time in each benchmark   |     |

|      | for different schemes                                                           | 179 |

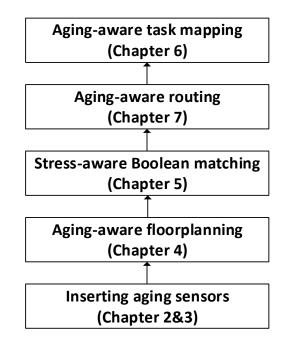

| 01   | The monored framework for aging mitigation and monitoring in many con-          |     |

| 8.1  | The proposed framework for aging mitigation and monitoring in many-core         | 104 |

|      | 3D heterogeneous architectures                                                  | 184 |

## LIST OF TABLES

### Page

| $2.1 \\ 2.2$                              | SENSIBLE overheads for different numbers of inserted sensors                                                                                       | $\frac{34}{35}$   |

|-------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| $3.1 \\ 3.2$                              | Number of sensors after applying filtering algorithm                                                                                               | 54<br>57          |

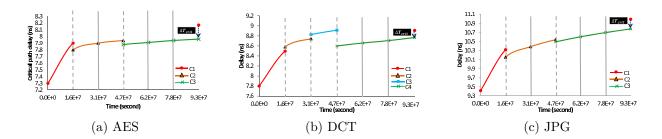

| 4.1<br>4.2                                | Selected benchmarks characteristics                                                                                                                | 74<br>77          |

| $5.1 \\ 5.2$                              | Cone construction result for each benchmark                                                                                                        | 103               |

| $5.3 \\ 5.4$                              | execution (At time zero, SNM= 250mV and SER=1000FIT/Mbit) The required time for STABLE steps in seconds                                            | 105<br>109<br>111 |

| $\begin{array}{c} 6.1 \\ 6.2 \end{array}$ | Heterogeneous Core Parameters                                                                                                                      | 132<br>133        |

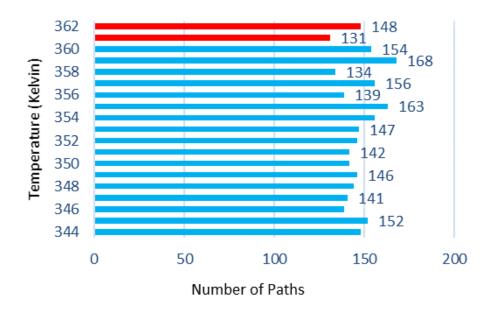

| $7.1 \\ 7.2$                              | Simulation platform configuration                                                                                                                  | 167               |

|                                           | imbalance ( $\Delta$ ) in 2D NoC for 3 years of execution (9.3E+7 seconds)                                                                         | 168               |

| 7.3                                       | Aging-induced delay degradation for maximum aged router and network age imbalance ( $\Delta$ ) in 3D NoC for 3 years of execution (9.3E+7 seconds) | 170               |

|                                           |                                                                                                                                                    |                   |

# List of Algorithms

|    |                                                     | Page  |

|----|-----------------------------------------------------|-------|

| 1  | RCP selection                                       | . 29  |

| 2  | The proposed RCP selection                          | . 50  |

| 3  | Aging-aware floorplanner and reconfiguration policy | . 69  |

| 4  | Cone Construction                                   | . 96  |

| 5  | Cone-flip Boolean Matching (Step 1)                 | . 97  |

| 6  | LUT-flip Boolean Matching (step two and step three) | . 99  |

| 7  | ADAMANT task mapping algorithm                      | . 127 |

| 8  | DVFS prediction algorithm                           | . 129 |

| 9  | D-CAT Construction                                  | . 158 |

| 10 | Aging aware routing algorithm                       | . 161 |

## ACKNOWLEDGMENTS

I would like to thank my advisor professor Nader Bagherzadeh, who gave me the opportunity to finish my thesis successfuly. I also would like to express my gratitude to my committee members professor Isaac D. Scherson and professor Jean-luc gaudiot for the comments on my thesis.

I owe everything to my family. I would like to express my everlasting gratitude to my parents, Zaher Ghaderi-Baneh and Maryam Jahangiri for their believe in me and their perpetual support. I dedicate very special thanks to my lovely brother and sister Dana Ghaderi and Arina Ghaderi, for their endless kindness and their special role in my life.

Many thanks to my friends and coauthors for their thoughts, helps, and companionship. I am thankful to my colleagues Tiago R. Muck, Ayed Alqahtani, Mohammad Ebrahimi and Ahmad Albaqsami.

I am very fortunate to have the supprts of great friends. I would specifically like to thank Marzieh Tousi, Kevin Mcquown, Mohmmad Kamandi, Mahsa Darvish, Ahmad Shirazi, Esmaeil Babakrpour, Ayed Alqahtani, Tiago Muck, Hamid Mirzaei, Saba Mohammadi, and Isaac Ramsey.

I would like to express my speciall thanks to my masters degree advisor at Sharif University of Technology, professor Seyed-Ghassem Miremadi who I lost him lately.

I wish to thank NSF for the financial support. Chapter 4 contains material taken from "Aging-aware high-level physical planning for reconfigurable systems" which appears in ACM/IEEE Asia and South Pacific Design Automation Conference (ASPDAC) 2016, which is partially supported by NSF.

## CURRICULUM VITAE

### Zana Ghaderi

#### EDUCATION

| Doctor of Philosophy in Computer Science                                     | Sep. 2013 - May 2017            |

|------------------------------------------------------------------------------|---------------------------------|

| University of California Irvine                                              | Irvine, California              |

| Master of Science in Computer Engineering<br>Sharif University of Technology | Sep. 2010 - Sep. 2012<br>Tehran |

| Bachelor of Science in Computer Engineering                                  | Sep. 2003 - Sep. 2008           |

| University of Science and Technology                                         | Tehran                          |

#### **RESEARCH EXPERIENCE**

| Graduate Research Assistant             | 2013 – 2017                |

|-----------------------------------------|----------------------------|

| University of California, Irvine        | Irvine, California         |

| Graduate Research Assistant             | <b>2011–2013</b>           |

| Sharif University of Technology         | <i>Tehran</i>              |

| <b>Undergraduate Research Assistant</b> | <b>Jan. 2008–Sep. 2008</b> |

| University of Science and Technology    | <i>Tehran</i>              |

#### TEACHING EXPERIENCE

**Teaching Assistant** University of California, Irvine

**Teaching Assistant** Sharif University of Technology

#### WORK EXPERIENCE

**R&D Engineering Intern** Abreezio LLC. (Acquired by Qualcomm) Sep. 2015–March 2017 Irvine, California Jan. 2012–Jun. 2012 Tehran

> Jun. 2015–Sep. 2015 San Diego, California

#### AWARDS

### Design and Automation Conference (DAC) Young Student Award 2015 San Francisco, California

### ICS Dean's Fellowship for 4 years of support

2013 – 2017

University of California, Irvine

Irvine, California

### **REFEREED JOURNAL PUBLICATIONS**

| AROMa: Aging-aware adaptive routing algorithm and<br>online monitoring in 3D NoCsUnderIEEE Transactions on Parallel and Distributed Systems                                  | r review-2017 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

|                                                                                                                                                                              | review-2017   |

| SENSIBLE: A highly scalable sensor design for path-<br>based age monitoring in FPGAs<br>IEEE Transactions on Computers                                                       | 2017          |

| Exploiting heterogeneity for aging-aware load balancing<br>in mobile platforms<br>IEEE Transactions on Multi-scale Computing Systems                                         | 2017          |

| HAFTA: Highly available fault-tolerant architecture to<br>protoect SRAM-based FPGAs agains multiple bit us-<br>pets<br>IEEE Transactions on Device and Materials Reliability | 2013          |

| REFEREED CONFERENCE PUBLICATIONS                                                                                                                                             |               |

| SLAPUF: Highly scalable low area delay-based physical<br>unclonable functionUnderIEEE Computer Society Annual Symposium on VLSI (ISVLSI)                                     | r review-2017 |

| Online monitoring and adaptive routing for aging miti-<br>gation in NoCs<br>IEEE/ACM Conference on Design, Automation & Test in Europe (DATE)                                | March 2017    |

| Path selection and sensor insertion flow for age moni-<br>toring in FPGAs<br>IEEE/ACM Conference on Design, Automation & Test in Europe (DATE)                               | March 2016    |

| Harvesting-aware adaptive energy management in solar-<br>powered embedded systems<br>IEEE International Symposium on Quality Electronic Design (ISQED)                       | March 2016    |

| Aging-aware high-level physical planning for reconfig-<br>urable systems                       | January 2016   |

|------------------------------------------------------------------------------------------------|----------------|

| IEEE/ACM Asia and South Pacific Design Automation Conference (AS                               | PDAC)          |

| A non-intrusive portable fault injection framework to assess reliability of FPGA-based designs | September 2013 |

IEEE International Conference on Field-Programmable Technology (FPT)

### ABSTRACT OF THE DISSERTATION

Aging-induced Performance Degradation: Monitoring and Mitigation

By

Zana Ghaderi

Doctor of Philosophy in Computer Science University of California, Irvine, 2017 Professor Nader Bagherzadeh, Chair

One of the fundamental challenges to the performance gain in advanced semiconductor technology is aging-induced delay degradation of transistors, which consequently increases the logic gates delays and eventually critical paths delays. Hence, designers have to add significant time margin as guardband to the main critical path, which imposes considerable performance degradation to the system. Temperature and stress (or usage) are the major sources of transistor's aging, which vary for different applications and are highly workload dependent. This thesis covers challenges and opportunities in monitoring aging, its effects and methods to combat the imposed performance and lifetime degradation in nanometer scales semiconductor platforms.

We devise methods to monitor and mitigate aging in computing platforms ranging from the conventional reconfigurable architectures to the contemporary 3D network-on-chips and many-core systems. To monitor aging-induced delay degradation on critical paths, we proposed SENSIBLE, a highly scalable aging sensor design that can help system-level designers to detect aging and react accordingly. Additionally, we proposed an application-dependant filtering methodology to select *Representative Critical Paths* (RCPs) among a large pool of critical paths for aging monitoring in reconfigurable architectures. Furthermore, two proactive methods are presented to mitigate aging impacts on application's critical paths and SRAM cells in reconfigurable architectures. The former is a high-level physical planning coupled with a reconfiguration policy and the latter is STABLE, a post-synthesis stress-aware Boolean matching technique. To mitigate and monitor aging on *Network on Chip* (NoC) components in both 2D and 3D IC designs we proposed AROMa, which is an aging-aware adaptive routing algorithm. To this end, we devised *Centralized Aging Table* (CAT) to convert transistor level aging phenomenon to the workloads' behavior in NoC-based many-core systems. Finally, an aging-aware task mapping, ADAMANT, is proposed to balance aging in many-core heterogeneous architectures' components.

## Chapter 1

## Introduction

Performance degradation due to runtime (temporal) variations is a fundamental challenge in the advanced semiconductor technology [2]. Extremely low feature size in CMOS technology leads to higher temperature, which as time passes, increases the threshold voltage  $(V_{th})$  of under stress transistors. Hence, these delay degradations at the transistor level increase critical paths' delays, manifesting itself as performance degradation at the system level. The aforementioned phenomenon is the so called transistor aging or briefly aging as a new reliability concern in advanced silicon technology. Accordingly, designers have to add aging guradband to the circuit's main critical path which imposes significant performance overhead [2, 51, 132, 149, 155]. Consequently, aging imperils the performance gain from the movement toward many-core systems and 3D IC design in nano-era technology.

## 1.1 Aging background

Reliability is a perpetual concern in nanoscale circuits. Among various reliability challenges aging can significantly impact the dependable operation of applications. Aging can cause timing failure in the running application and/or considerably diminish the operational lifetime of the circuit. Different aging mechanisms are classified as following [2]:

- Bias Temperature Instability (BTI)

- Hot Carrier Injection (HCI)

- Time Dependent Dielectric Breakdown (TDDB)

- *Electromigration* (EM)

#### $\mathbf{BTI}$

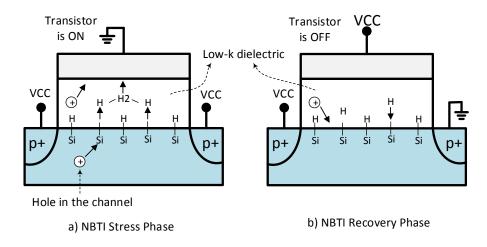

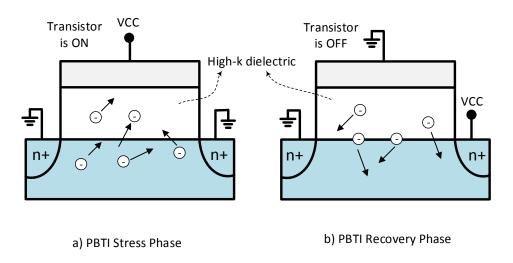

BTI is a two phases mechanism which includes *stress* phase and partial *recovery* phase. Negative BTI (NBTI) happens in PMOS transistors and Positive BTI (PBTI) happens in NMOS transistors. The transistors cross sections during NBTI and PBTI mechanisms are shown in Fig.1.1 and Fig.1.2, respectively [86, 91, 132, 143]. As shown in Fig.1.1.a, when the PMOS transistor is ON, the stress voltage brakes the covalent bound of Si-H at interface; this process is so called *reaction*. The separated hydrogen atoms combine to form H2, which diffuses toward the gate of the transistor. These broken Si-H bonds generate positively charged traps for holes and leads to increase in transistor's  $V_{th}$ . Interestingly, as illustrated in Fig.1.1.b, when the PMOS switches off and stress is removed the recovery phase starts where some of the traps are released and the broken Si-H bounds heal. PBTI in NMOS transistors was not a challenge in silicon dioxide dielectrics. However, as the high-k dielectric stacks started from the 32 nm technology node, its contribution to the aging also becomes considerable [164, 165]. Similarly, Fig.1.2 illustrates the NMOS transistor cross section during PBTI mechanism. In contrary to NBTI, as shown in Fig.1.2.a, PBTI is generally happens due to the electrons trapping within the gate dielectric or at the interface when the NMOS transistor is ON. During its recovery phase, these electrons are released and partially go back to the channel which leads to partial improve in transistor's  $V_{th}$ . Temperature accelerates BTI mechanism.

Figure 1.1: PMOS transistor cross section illustration during NBTI.

Figure 1.2: NMOS transistor cross section illustration during PBTI.

#### HCI

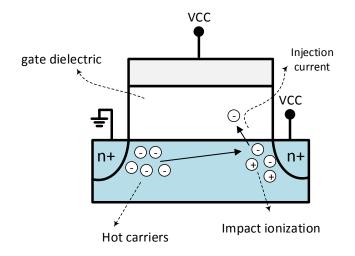

HCI mechanism is more prominent in NMOS transistors. The transistor cross section during HCI mechanism is shown in Fig.1.3. When the transistor switches to turn ON the high energy

carriers, that are called hot-carriers, collide with other atoms and carriers in the transistor's channel. If their energies are higher than impact-ionization threshold then electron-hole pairs are generated. Some of these carriers are injected to the gate oxide and as a result  $V_{th}$  increases [91, 119, 145].

Figure 1.3: NMOS transistor cross section illustration during HCI.

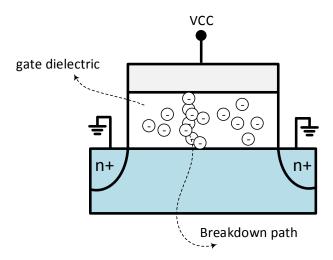

#### TDDB

TDDB mechanism occurs when the voltage across gate generates traps in the dielectric. Accumulation of these carriers increases the electron density in the transistor dielectric. As shown in Fig.1.4 when the electron density is high a breakdown path (i.e. conductive path) between the transistor's gate and channel is generated [46, 91, 94]. The generated breakdown path increases leakage power of the transistor, shifts its  $V_{th}$ , and eventually fails its correct functionality [94, 158].

Figure 1.4: NMOS transistor cross section illustration during TDDB.

$\mathbf{E}\mathbf{M}$

EM occurs along conductors in the direction of electron flows which cause to diffuse metal atoms. For example, the metal connection between transistors suffers from EM mechanism. The mass migration of metal atoms along with the electrons depletes a part of conductor and makes it thinner. Consequently, thinning of the metal increases the resistance of the connection and eventually leads to an open circuit in the wire [27, 36].

#### Aging sources and design time solution

The main source of aforementioned aging mechanisms in transistors or wires is usage, or the so called stress. For example, when the transistor is ON or is switching or a current flows inside a wire stress happens. Aging rate increases in high temperatures. BTI and HCI that increase  $V_{th}$  and switching delay of transistors are the dominant aging mechanisms [2, 45, 64, 65, 105]. In [18], it is shown that BTI and HCI impacts are 15% and 5%, respectively in 65nm technology. This shows that BTI is the dominant mechanism and its impact is

three times higher than HCI. These get worse for technologies beyond 65nm and the timing variation are expected to aggravate with technology scaling [2, 35]. Furthermore, In [115], BTI and HCI impacts are reported 9.4% and 8.5%, respectively. Additionally, [17] reports about 10% degradation for 32nm in 3 years due to BTI. Based on these reports, in this work, we assume BTI and HCI in worst case degrades critical paths by 12% and 4% in 3 years, respectively, given a fixed temperature of 380K. In this dissertation, we study and consider the impact of BTI and HCI aging mechanisms on delay of a circuit (i.e. performance).

The path with the highest delay in a circuit (i.e. an implemented application) is the main critical path, which determines the circuit's clock frequency or performance. Aging increases the critical paths' delays which demands for higher period of clock (or lower clock frequency). Sequential elements (e.g. Flip-flops) are connected at the end of each path to store the state of the circuit. Any variation on path delay because of aging causes timing violation and error which results in incorrect state of the circuit. This could lead to failure at the system level. Therefore, designers have to add pessimistic timing margins to the circuit's critical paths (i.e. clock frequency) as guardbands. In addition, dynamic variations at run time due to running workloads' variations lead to distinct stress as well as temperature between resources. For that, designers must consider the worst case scenario due to the unpredictability of running workloads' behaviors at runtime on the circuit. Besides, due to process variation, temperature, and voltage variation other guardbands are required to be added. These timing guardbands' lengths are increasing rapidly as technology advances, which account for almost 40% of the target performance [2]. For example, 20% guardband is required to avoid failure due to aging in 65nm technology within the first 10 years [51, 155]. Guardbanding constraints those advantages that are because of technology scaling [2].

The static variations (i.e. process variation) effects can be mitigated by pre-silicon and post-silicon tuning techniques. While aging as a temporal variation requires after fabrication solutions, during runtime and at system level to compensate for the performance degradation related to guardbands and help designers to avoid adding considerable guardbands to the system at fabrication time. In all, not only design time analysis and adding guardbands but also runtime techniques can help to cope with aging effects.

Since stress and temperature change broadly for different transistors in a circuit, aging rates of logic gates and the paths along them are not balanced [51, 66, 153]. Therefore, the aging-induced delay increments of different paths vary, which may cause generation of new critical paths by converting non-critical path to critical path. The imbalance aging rate becomes more severe in many-core systems and 3D ICs, where temperature is a fundamental challenge. Beside that, various components (e.g. cores, interconnection infrastructures, and etc.) inside devices experience different temperatures and stresses. Similarly, reconfigurable architectures components where not only the running application on them but also the implemented logics among them change. This also causes imbalance and unfair aging of components.

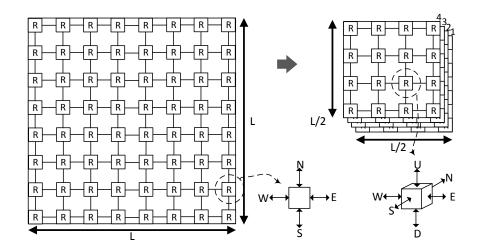

## **1.2** Selected platforms and motivation

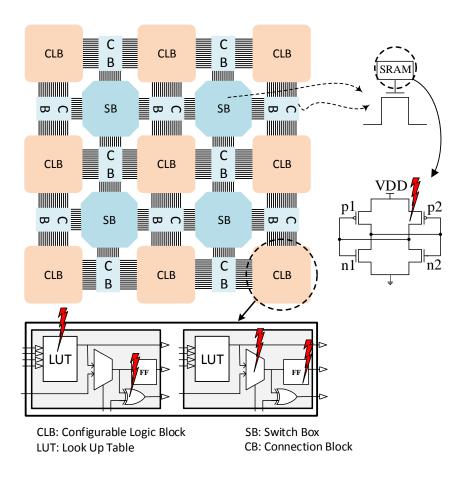

Runtime reconfigurable architectures enable dynamic adaptation of changing workloads, that allows to optimize area, performance and power [61, 67]. They comprise general purpose cores and a reconfigurable architecture which is implemented as SRAM-based Field Programmable Gate Array (FPGA) to allow swift runtime reconfigurations. Fig. 1.5 illustrates the contemporary island style SRAM-based reconfigurable architecture. The ever-increasing usage of FPGAs in mainstream applications such as acceleration in data-centers as well as safety critical application such as space, automotive, and medical made us to investigate aging in such a platform.

As shown in Fig. 1.5 the application's logics are implemented in tiles which are known as

Figure 1.5: Island style SRAM-based reconfigurable architecture.

Configurable Logic Blocks (CLBs) is composed of Look-up-Tables (LUTs), Flip-Flops (FFs), Carry chain, logic gates and etc. These components are connected to each other through Connection Blocks (CBs) and also connected to other CLBs through Switch Boxes (SB). SRAM cells inside these components are configured to implement the desired logics and their required routings. Fig. 1.5 shows that all the components in an FPGA suffer from aginginduced delay degradation (red thunders). For example, the delay of implemented critical paths along a reconfigurable architecture components can increase due to aging mechanisms such as BTI or HCI. Additionally, aging impact on SRAM cells in a reconfigurable architecture manifests itself as the SRAM's Static Noise Margin (SNM) reduction. SNM is the SRAM cell reliability measurement. Hence, SNM reduction in an SRAM cell decreases its stability and increases its Soft Error Rate (SER).

There have been noticeable numbers of studies in the literature about aging in reconfigurable architectures [6, 87, 88, 123, 138, 142, 167, 169]. These techniques tried to mitigate aging through changes in placement or routing of the implemented design on FPGAs. It is required to be noted that temperature map of the implemented circuit cannot change drastically by these local changes. Therefore, the local tuning not only cannot change the aging map of the implemented design but also induces performance overheads due to stringent constraints of placed and routed design. Furthermore, these methods only focused on the performance degradation of implemented design on an FPGAs and the impact of aging on SRAM cells of reconfigurable architectures is ignored.

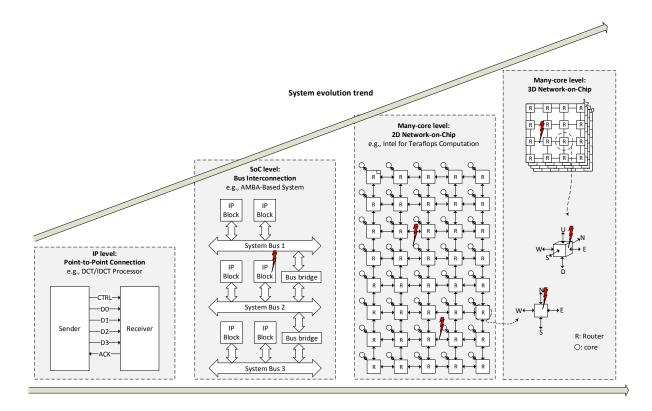

Additionally, the movement toward many-core systems and the demand for lower area, power, and scalability as well as higher performance leads computer architects to 3D IC and NoC designs [47]. Furthermore, the broad diversity of application requires many-core heterogeneous architectures, as well. Fig. 1.6 illustrates the system evolution toward many core systems and their on-chip interconnections. It can be seen that routers are the main components to connect cores in a platform with 80 cores [47] which can suffer from aging. Aging-induced performance degradation in routers endangers the reliability and scalability of such platforms. Furthermore, cores in heterogeneous architectures have different clock frequencies which increases the chance of higher imbalanced aging among cores.

All of these lead us to investigate aging in NoCs, as a promising solution for scalable and high performance many-core systems, and heterogeneous architectures. It is shown in Fig. 1.6 that all the components in a many core system such as cores, routers, and links are susceptible to aging-induced performance degradation. It can be concluded that in many-core systems different components experience various temperatures and stresses related to the running workload on them. This leads to aging imbalance among them which causes premature lifetime degradation of highly aged components (i.e. cores or routers).

Figure 1.6: The trend of many core systems and on-chip interconnection.

The related works in [11, 12, 19, 20] focused on aging degradation in NoC components. The focus of their works was to mitigate aging by changing the routing between source-destination pairs through profiling aging information at offline. These techniques are not able to catch the runtime behavior of workloads and their impact on temperature and aging. Also, non of these related works studied the impact of aging for 3D NoCs. Additionally, the impact of aging on processing units in many-core systems are studied in [121, 104, 69]. These techniques tried to mitigate aging through task mapping for homogeneous architectures. We observed that for heterogeneous architectures age imbalance between the highest aged core and the lowest aged core is almost 55% higher than homogeneous architectures.

In this dissertation we chose reconfigurable architectures and NoC in many-core system as our platforms for aging study. The usage of both platforms in embedded systems such as safety critical applications as well as main stream applications is inevitable. Performance and reliability demands for the new application of digital systems such as *Internet-of-Things* (IoT) requires careful investigation of aging to avoid loss in performance, energy, area, power, and scalability.

## 1.3 Dissertation contribution

This dissertation focuses on mitigating performance degradation for aging in both reconfigurable architectures and many-core system components (i.e. cores and NoC). We devise methods to monitor aging on critical paths, mitigate aging impact on performance in reconfigurable architectures as well as their SRAM cells' SNM. In addition, we investigate aging for both 2D and 3D NoCs and heterogeneous cores in many-core architectures. Our proposed methods objective is to balance aging among available resources and minimizes the delay degradation of highly aged components.

We classify our aging investigation methods for reconfigurable architectures as reactive and proactive methods. In the reactive category, we proposed:

- A highly scalable sensor design for late transition detection in FPGA-based platforms.

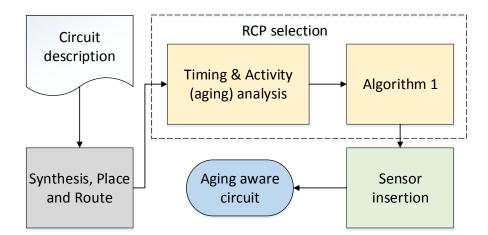

- A two-step aging-aware methodology for *Representative Critical Paths* (RCPs) selection from a large number of *Critical Paths* (CPs) in programmable logic devices.

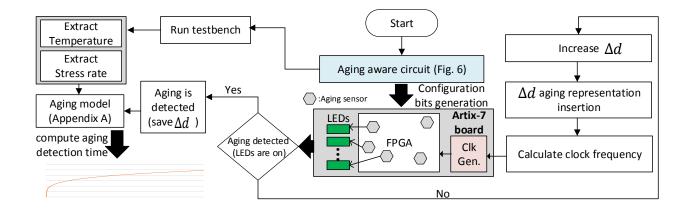

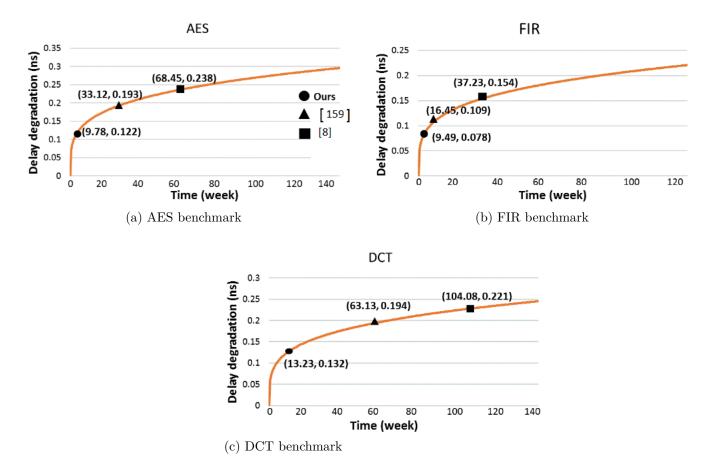

At first, we propose a sensor clock (SCLK) that is a function of minimum slack time of a set of paths selected for age monitoring. There will be one such clock for many sensors as are needed in an entire FPGA. Our proposed sensor architecture makes it possible for a single SCLK to be shared by all sensors. Additionally, the proposed sensor occupies one slice (basic FPGA logic block), which leads to low area, power, and performance overhead.

In addition, we proposed a two-step filtering methodology to select RCPs for aging monitoring in a reconfigurable architecture. In the first step, nomination of CPs is based on delay, temperature, and lexicographic function of duty cycle and switching activity filtering, which are the major causes in BTI and HCI aging mechanisms. Secondly, RCPs will be selected based on Fan-out (FO) and physical location of *Logic Blocks* (LBs) along a CP to decrease aging propagation and sensor distribution fairness, respectively. We then present a sensor insertion algorithm that will be used during design placement to avoid sensors' inaccuracy. Implementation steps of sensor insertion are performed automatically with a limited human interaction.

In the proactive category, we proposed:

- A high-level physical planning with reconfiguration strategy in order to mitigate the aging-induced delay degradation in FPGA resources.

- A three-step post-synthesis stress-aware technique, to reduce the impact of BTI-induced SNM reduction in FPGA LUTs using SAT-based Boolean Matching (BM) algorithm.

The first method is an offline framework composed of an aging-aware floorplanner coupled with a proactive aging-aware reconfiguration policy which generates checkpoints aperiodically for runtime reconfiguration. We consider BTI and HCI aging mechanisms and consider the BTI-based aging recovery during idle periods using aging history map.

Secondly, our proposed methodology partitions *Data-Flow-Graph* (DFG) of the implemented design into different cones. First, our SAT-based BM algorithm finds a new configuration for each cone in DFG while all SRAMs are flipped and its functionality is preserved. Secondly, cones that did not pass step one can benefit from unused SRAMs in their partially-used LUTs. Hence, we store the flipped configuration of such LUTs in their unused SRAMs. Finally, flipped configurations of fully-used LUTs are stored in unused LUTs. The main configuration of implemented design on FPGA will be swapped by the new flipped configuration, periodically.

To cope with the delay degradation in 2D and 3D NoCs we proposed an online monitoring method through a *Centralized Aging Table* (CAT) for routers in NoCs. To capture interlayer temperature variations in 3D NoC we exploit Distributed CAT (D-CAT). Router's capacity in flits, which are the main stimuli in routers, is predictable and limited for a given period of time. Consequently, stress rate and temperature, which are the major sources of aging mechanisms such BTI and HCI, will be in the predictable ranges, as well. Our methodology uses CAT which is populated by values that represent aging degradation for each different pairs of stress and temperature ranges during a given period of time. In 3D NoC, each layer has its own D-CAT to capture the difference between temperature of different layers even with same stress. Furthermore, utilizing D-CAT, we propose AROMa, an online adaptive aging-aware routing algorithm in order to avoid highly aged routers which eventually leads to age balancing between routers. Our proposed routing algorithm reduces maximum age of routers by changing the shortest paths between source-destination pairs adaptively, considering routers' ages across them in each given period of time.

The pervasiveness of heterogeneous multiprocessors (HMP) in the mobile domain enables more energy efficient systems. Current approaches to exploit the energy efficiency of HMPs results in unbalanced usage of resources, which leads to higher aging rates and delay degradation when compared to homogeneous architectures. Hence, we propose ADAMANT, an aging-aware task mapping algorithm for HMPs. ADAMANT exploits on-chip sensing of aging, performance, and power in order to enable online workload characterization to select task-to-core mappings that yield both increased system lifetime and energy efficiency.

## 1.4 Dissertation organization

The rest of this dissertation is organized as follows. First, Chapter 2 presents SENSIBLE a highly scalable sensor design for reconfigurable architectures. Chapter 3 elaborates on our two-step methodology to find RCPs among large pool of critical paths to insert aging sensors (e.g. SENSIBLE) on them. We propose our high-level physical planning method along with reconfiguration policy for aging mitigation in FPGAs in Chapter 4. Chapter 5 proposes STABLE, a three-step post-synthesis technique to mitigate SNM reduction due to BTI in SRAM cells in FPGAs using Boolean matching technique. In Chapter 6 we elaborate on AROMa, an adaptive aging-aware routing algorithm for 3D NoCs and 2D NoCs along with our novel online aging monitoring system. Next, in Chapter 7, we propose ADAMANT, an aging-aware task mapping technique for heterogeneous architectures.

## Chapter 2

# SENSIBLE, a novel scalable low-overhead aging sensor design

FPGAs are broadly deployed to accelerate computation in various applications ranging from embedded applications such as automotive, vision, and medical devices to data-center applications. Fabricated in latest advanced silicon technology and deployed for highly computationally intensive kernels, FPGAs face reliability challenges such as aging [18, 30, 161]. BTI and HCI aging mechanisms induce delay degradation to FPGA resources and increase leakage power consumption [142, 148, 7, 138, 50]. The delay degradation in logic and routing resources along *Critical Paths* (CPs) of a design on FPGA results in late transitions that can cause timing failures.

Delay degradation (aging rate) in BTI and HCI mechanisms is exponential function of temperature and nonlinear function of stress time. Each resource in FPGA can be possibly in a critical path of target applications with different temperature and *Stress Rate* (SR) maps. This means different CPs experience different temperatures and stresses, thus different aging rates. Therefore, delay of CPs with longer slack times may exceed smaller ones (including longest critical path) [50]. This chapter focuses on on-chip aging sensors for critical path delay monitoring in FPGAs.

On-chip aging sensors that are referred to as application dependent sensor [7, 118, 148], are deployed along the paths in a circuit to detect any increase in delay of the paths for system level aging mitigation techniques [118, 160]. A path has a slack time relative to the longest critical path or operating clock period (MCLK). Any transition in slack time is an indication of aging that needs to be detected by aging sensors. While critical paths with negligible slack times are more vulnerable to timing failure due to aging, it is shown that some of nearcritical paths with relatively small non-zero slack time often have higher aging rates [50]. Hence, by selecting and monitoring such *near-critical* paths as *Representative Critical Paths* (RCPs), we can potentially detect aging pro-actively to avoid functional failures caused by timing failures in the entire system [50]. Such RCPs even tend to exceed the longest CP's delay due to aging.

Inserting aging sensors on such RCPs' endpoint avoids performance loss due to the added delay of sensors to RCPs. To find these RCPs we deployed and improved version of our RCP selection algorithm in Chapter 3. This algorithm finds RCPs that have higher aging rates than CPs with smaller slack time. However, if aging rates of CPs with smaller slack times (including longest CP) are high enough that may result in timing failure before detection of aging on other selected RCPs, the algorithm selects them for monitoring. Hence, negligible performance loss is unavoidable.

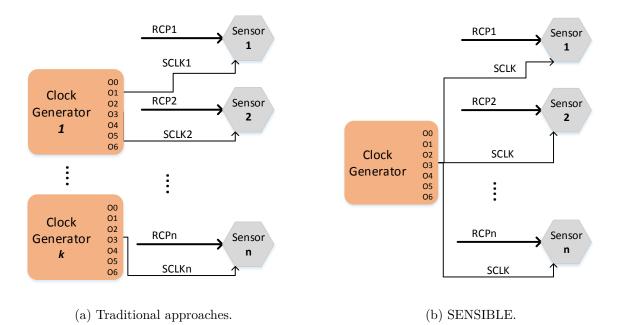

Slack-based aging sensor architecture and design for such RCPs is challenged by various factors. Because of a large number of RCPs in a design, the number of required sensors will be high [50]. Each aging sensor requires a sensor clock (SCLK) and state-of-the-art aging sensors cannot share a single clock source [7, 148]. Given that the number of clock generation modules is limited for an FPGA, existing aging sensor designs are not scalable to be deployed in a large scale for RCPs (Fig. 2.1a). This becomes more important in multiple

Figure 2.1: Multiple aging sensor architecture in FPGAs.

clock domain designs. Another challenge is sensor placement at the RCPs' endpoints. Sensors with higher resource utilization (logic and clock resources) incur more stringent placement constraints. If aging sensors utilize fewer logic resources and share a clock resource, they are more likely to be inserted near RCPs' endpoints. This leads to higher scalability and more accurate operation of sensors with less overhead. Higher accuracy (or sensitivity) leads to faster aging detection than previous works [148, 7]. This helps system level aging mitigation methods to react better by having more precise aging information in RCPs.

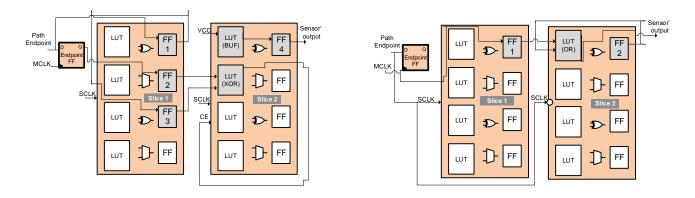

This chapter presents a highly scalable sensor architecture by utilizing the minimum slack time of selected RCPs to build a shared sensor clock (SCLK) called SENSIBLE. The proposed multi-sensor clock design has lower area and power overhead in comparison with state-ofthe-art aging sensors. As illustrated in Fig. 2.1b, using SENSIBLE we can utilize the same clock generator for a group of sensors. Additionally, the proposed sensor only occupies one basic FPGA logic block (e.g., a slice in Xilinx Artix FPGAs). Programmable routing resources between programmable logic blocks (CLBs) on FPGAs impose significant delay overhead in a sensor design, which may sometimes exceed the aginginduced delay degradation. By containing the sensor in one logic block and avoiding programmable routing resources, our proposed aging sensors are able to detect aging earlier (i.e. higher accuracy) than existing aging sensors, and yet, they have lower area and power overheads. Earlier (more accurate) aging detection before happening of timing failure helps the system level aging mitigation techniques to react sooner and properly. For example, by changing the placement (configuration bits) of more aged regions we are able to mitigate aging in reconfigurable architectures [65].

The experimental results on Artix7-based board show that the SENSIBLE is a scalable low-overhead aging sensor and it can be inserted in designs on FPGAs in large scale with negligible impact on design performance. Our experimental results support this claim that unlike previous works [148, 7], our proposed sensor design with lower logic resource utilization can fit as closely as possible to path endpoint CLB so as to avoid programmable routing resources. Due to higher accuracy, the aging along CPs are detected earlier than using aging sensors in [148, 7]. To the best of our knowledge this is the first attempt for scalable design of aging sensors on FPGAs which can be applied for ASIC design as well.

# 2.1 State-of-the-art aging sensors for FPGAs

Logic-based aging sensors for ASIC designs have been proposed in the literature. For instance, sensors presented in [118, 117] measure delay degradation in a circuit due to transistor aging. In [118], two approaches for detection and correction of late transition due to NBTI are proposed, which either impose performance or area overhead to the circuit. The sensor introduced in [117] is based on two ring oscillators, one as a reference, and the other one under stress conditions. The difference between their frequencies is a representation of their delay difference. In [170], a ring oscillator based multi-purpose sensor on FPGA is presented. Although their method is suitable to extract the FPGA delay, they cannot be used for monitoring aging on CPs (i.e., not application dependent).

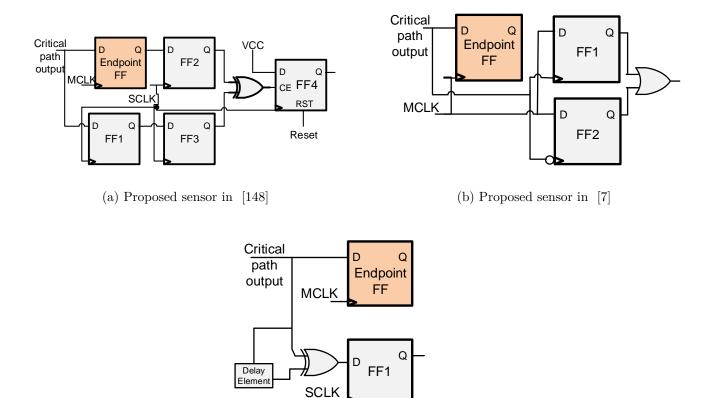

Application dependent aging sensors (i.e. by monitoring aging along CPs) for FPGA-based designs are proposed in [148, 7]. In order to detect transitions on path endpoints near the active clock edge, they monitor RCPs. In [7], an FPGA-based aging sensor is proposed which occupies more than one slice. A similar approach is used in [148], with a difference that their proposed sensor is able to adjust the observation interval dynamically. Since such aging sensors require different clocks, multiple clock sources are required (See more details in Section 2.4). This not only reduces their scalability due to limited numbers of clock generation modules, but also increases the area and power overheads. Additionally, the aging sensors occupy more than a basic logic block (e.g. slice) and they are forced to connect to the RCPs' endpoint through programmable routing resources (outside the slice), with a higher delay. In addition, due to higher resource utilization (clock resources and logic), it is less likely to be able to place the sensors close to the RCPsãAŹ endpoints. Detailed comparison in Section 2.4 is provided.

Some of the related works try to mitigate aging in re-configurable architecture at different levels of granularity by changing the placement of design inside an FPGA [138, 65, 32]. [138, 32] proposed offline aging mitigation techniques by profiling the aging rates of different blocks in an application to increase chip lifetime or avoid timing failure at runtime. However, the applications' behavior (temperature and stress) at runtime might be different and result to impaired solutions which leads to online aging mitigation techniques [32]. Aging sensors on RCPs will be one way of online monitoring. Therefore, sensors with lower overheads and higher sensitivity are needed. Lower overheads (area, power, performance, number of required clock generators, clock routing) leads to higher scalability and lower design complexity. In this work, we amended our proposed RCP selection method in [50] to find required

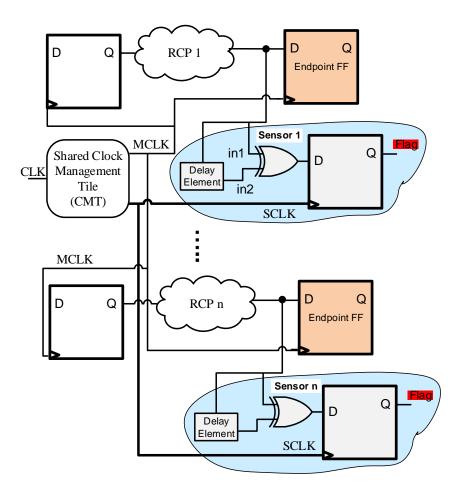

Figure 2.2: Block diagram of SENSIBLE.

RCPs for aging monitoring in FPGAs (Section 2.4).

# 2.2 Our novel proposed aging sensor (SENSIBLE)

Operation of SENSIBLE is based on the fact that several paths (selected RCPs) in a circuit have non-zero slack times that are relatively close to the slack time of the critical paths. A transition on such path's endpoints during the slack time is known as an erroneous behavior. Detection of any transition on a path's endpoint during the slack time caused by aging mechanism, is considered as an aging effect.

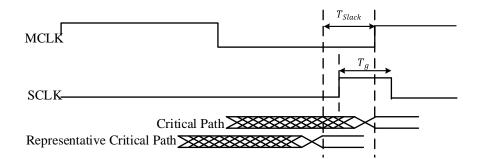

Figure 2.3: MCLK and SCLK representation.

The design of the proposed method is shown in Fig. 2.2. The aging sensor is potentially placed on a near-critical path's (RCP1) endpoint. The sensor consists of an FF, an XOR gate, and a *Delay Element* (DE). For clocking the sensors, a sensor clock (SCLK) is generated that is synchronized with the main system clock (MCLK) using *Clock Management Tiles* (CMTs). Fig. 2.3 shows the timing diagram of SCLK and MCLK. The SCLK frequency is the same as that of MCLK. SCLK makes a 0-to-1 (active edge) transition during the slack time before the active edge of MCLK.

Today's FPGAs have a feature for generating different clock signals using embedded standard resources called *Clock Management Tiles* (CMTs), which consist of *Mixed-Mode Clock Manager* (MMCM) and/or PLLs. For a given clock period  $T_{clk}$ , CMTs allow a configurable phase shift to take any discrete value;  $phase\_shift = N \times T_{clk}/256$ , where N is an integer in the range -255 < N < 255. In addition, CMTs allow generation of various duty cycles for a given clock period. Therefore, we can generate a shifted clock signal with a desired duty cycle for the sensor, as required by the proposed aging sensor in this work.

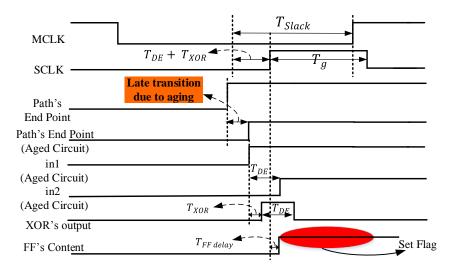

Fig. 2.3 shows the timing diagram of the sensor presented in Fig. 2.2 (for RCP1). As shown, a late transition generates a positive pulse with width of  $T_{DE}$  at the output of the XOR gate. The sensor's FF is initialized to '0'. The XOR gate receives data from the near CP (in1) (RCP1), and its time-shifted data (in2) by delay element. Because of the delay element,

Figure 2.4: The sensor operation in the presence of late transition happened due to aging.

any transition at the output of the RCP driving this sensor will cause a positive pulse on the XOR output. If this pulse happens outside of the slack time, it will safely pass without affecting the FF value. On the other hand, due to the induced delay by aging in the RCP, the aging sensor's FF will capture the pulse at XOR output during slack time window. This occurs on the positive edge of SCLK where FF setup and hold times are also considered.

This positive pulse causes a '1' at the FF output. When there is no aging effect, the path's endpoint does not have any transition that can be captured by SCLK during slack time and there will be no difference between the XOR inputs. XOR output remains at '0' and hence, the FF remains at '0' indicating no late transition.

In order to ensure correct operation of the sensor,  $T_{Slack}$  must be chosen based on slack times of selected paths sharing the same clock. Given a set of RCP *i* with slack time Si,  $T_{Slack}$  is the minimum of all slack times.

$$T_{Slack} = min(S_1, S_2, ..., S_n)$$

(2.1)

This condition guarantees that none of the selected paths has any transition in  $T_{Slack}$ . Valid changes at in1 input of XOR gate can occur up to the start of  $T_{Slack}$ . Since in2 is formed by delaying in1 by  $T_{DE}$ , we can expect in2 to change  $T_{DE}$  after the start of  $T_{Slack}$ . Considering  $T_{XOR}$  gate delay, the clocking of the FF must be after  $T_{DE} + T_{XOR}$  in order to capture slack time violations. It should be noted that as long as the aforementioned condition for SCLK start point is met, its duty cycle could exceed the duty cycle of MCLK. This leads to the easier design of SCLK for our proposed sensor.

To determine the delay of the delay element  $T_{DE}$ , the timing difference between the XOR gate inputs must be long enough such that the XOR gate can propagate this difference to its output (e.g., generating positive pulse at its output). Hence, the first condition to be satisfied by  $T_{DE}$  is:

$$T_{DE} \ge T_{XOR} \tag{2.2}$$

This pulse propagates to the output of XOR gate (input of FF). Also,  $T_{DE}$  must be long enough so that FF setup and hold times are not violated, i.e.,

$$T_{DE} \ge T_{FF\_setup\_hold\_time} \tag{2.3}$$

From (2.2) and (2.3), we can conclude:

$$T_{DE} \ge Max(T_{XOR}, T_{FF\_setup\_hold\_time})$$

$$(2.4)$$

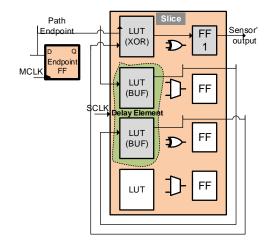

The implementation of the proposed sensor on FPGA resources is shown in Fig. 2.6c. In Xilinx Artix (or Virtex) FPGAs, our sensor occupies only one slice. Recall that slice is the basic logic block in Xilinx FPGA devices. Our proposed sensor only uses the intra-slice interconnect resources for connectivity and does not require programmable routing resources. The proposed sensor has higher accuracy in comparison to available aging sensors in the literature and the delay element (DE) is implemented using two LUTs connected serially.

When there is no unused slice inside the endpoint CLB, an unused slice in the nearby CLBs will be selected as the sensor slice. In this case, the programmable routing resources are used. To avoid such scenarios, the placement tools can reserve a slice in the endpoint CLB for sensor insertion. Unlike previous works that propose aging sensors with two slices [148, 7], our proposed sensor only occupies one slice and hence, the probability of finding an unused slice inside the endpoint CLB without changing original design placement is higher. We use a greedy local search to find the closest unused slices (more details in Section 2.5.2).

Since aging is a gradual mechanism and happens in a long term we can turn on sensors in steps of time to avoid aging in sensor's components (Delay element, FF, and XOR). This can be easily done by disconnecting the clock source (SCLK) from them (e.g. by setting a flag). Next, we present a comprehensive comparison between our proposed sensor and existing sensors presented in [148] and [7].

# 2.3 SENSIBLE vs. state-of-the-art works

As shown in Fig. 2.5a and Fig. 2.6a the proposed sensor in [148] utilizes the observation (guard-band) interval  $(T_g)$  of the clock period for detecting any unwanted late transition due to aging. SCLK is the negative-shifted MCLK by  $T_g$  to store the correct data before late transition. Then, the faulty data after late transition will be stored in endpoint flip-flop for comparison. By using a  $T_g$  shift of MCLK for generation of SCLK, it only detects aging on the targeted RCP accurately (with same  $T_g$ ).

For multi-sensor insertion on different RCPs multiple clock generators are required because they have different  $T_g$ . We can use shared SCLK for this sensor too but in cost of losing

(c) SENSIBLE

Figure 2.5: Sensor design.

sensitivity and accuracy significantly due to its described way of detecting timing violation. Furthermore, to avoid sensor sensitivity-loss FF1 and endpoint FF must be placed in the same CLB to avoid programmable inter-CLB routing resources with higher delay overhead. Clock enable (CE) input of FF4 is different from other FFs inside the sensor. There is a need for at least two slices (sometimes three) to implement this sensor since flip-flops inside a slice have the same CE inputs (only one CE).