## UC San Diego UC San Diego Electronic Theses and Dissertations

## Title

Low-Latency Techniques for Improving System Energy Efficiency /

## Permalink

https://escholarship.org/uc/item/0bm3d3t6

## Author

Strong, Richard D.

## Publication Date 2013

Peer reviewed|Thesis/dissertation

#### UNIVERSITY OF CALIFORNIA, SAN DIEGO

Low-Latency Techniques for Improving System Energy Efficiency

A dissertation submitted in partial satisfaction of the requirements for the degree of Doctor of Philosophy

in

#### Computer Science (Computer Engineering)

by

Richard D. Strong

Committee in charge:

Tajana S. Rosing, Chair Dean M. Tullsen, Co-Char Clark C. Guest Andrew B. Kahng George Porter Steven Swanson

2013

Copyright Richard D. Strong, 2013 All rights reserved. The Dissertation of Richard D. Strong is approved and is acceptable in quality and form for publication on microfilm and electronically:

Co-Chair

Chair

University of California, San Diego

2013

## DEDICATION

To all those that keep on trying.

EPIGRAPH

We are what we pretend to be, so we must be careful what we pretend to be.

Kurt Vonnegut

| Signatur                            | e Page                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | iii                                                                                    |

|-------------------------------------|---------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|

| Dedicati                            | on                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | iv                                                                                     |

| Epigrapl                            | 1                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | v                                                                                      |

| Table of                            | Conten                                                        | ts                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | vi                                                                                     |

| List of F                           | igures                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ix                                                                                     |

| List of T                           | ables .                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | xii                                                                                    |

| Acknow                              | ledgem                                                        | ents                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | xiv                                                                                    |

| Vita                                |                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | xvii                                                                                   |

| Abstract                            | of the                                                        | Dissertation                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | xix                                                                                    |

| Chapter<br>1.1<br>1.2<br>1.3<br>1.4 | Efficie<br>Power<br>Fast C                                    | roduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1<br>1<br>5<br>8<br>9                                                                  |

| Chapter 2.1 2.2 2.3                 | Relate<br>Power<br>2.2.1<br>2.2.2<br>2.2.3<br>2.2.4<br>System | emory Access Power Gatingd WorkGating and Power Distribution NetworkProgrammable Power Gating Switch (PPGS) DesignPDN Model for Power Estimation and Circuit AnalysisSafe Wake-Up Mode Analysis and EquationCore Wake-Up Staggern DesignCentralized Wake-Up Controller (WUC)Distributed, Staggered Wake UpMAPG-Counter: Counter-Based Controller DesignTAP: Token-Based Adaptive Power GatingFormal Analysis of In-Order Core Energy SavingsCore State Retention and Restoration | 14<br>17<br>20<br>20<br>23<br>26<br>28<br>30<br>30<br>30<br>32<br>34<br>36<br>40<br>42 |

| 2.4<br>2.5                          |                                                               | ation Methodology                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 44<br>47<br>48<br>53                                                                   |

#### TABLE OF CONTENTS

|         | 2.5.3   | Energy Savings as a Function of Wake-up Latency   | 55  |

|---------|---------|---------------------------------------------------|-----|

|         | 2.5.4   | Adapting to Memory Contention                     | 57  |

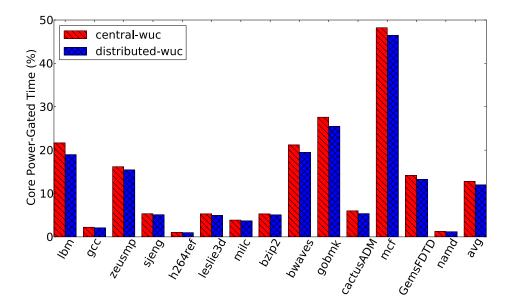

|         | 2.5.5   | Distributed, Staggered Wake Up                    | 59  |

| 2.6     | Summ    | nary                                              | 62  |

| 2.7     | Ackno   | owledgments                                       | 63  |

| Chapter | 3 Ve    | ry Fast Core Switching                            | 65  |

| 3.1     | Relate  | ed Work                                           | 69  |

|         | 3.1.1   | Thread Migration Techniques                       | 69  |

|         | 3.1.2   | Scheduling for Heterogeneous Multicores           | 70  |

| 3.2     | Softwa  | are Approaches to Core Switching                  | 72  |

|         | 3.2.1   | Modified System Calls                             | 73  |

|         | 3.2.2   | V1: Linux's Thread-Migration Mechanism            | 74  |

|         | 3.2.3   | V2: Modified Scheduler                            | 75  |

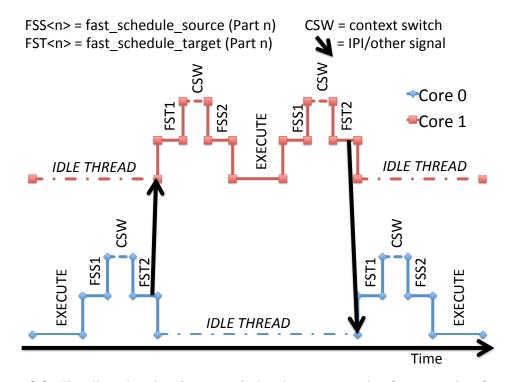

|         | 3.2.4   | V3: Scheduler Fast Paths                          | 76  |

|         | 3.2.5   | V4: Addressing IPI Costs                          | 77  |

|         | 3.2.6   | V5: Cross-Core Wake Up from Quiesce               | 79  |

| 3.3     | Simula  | ation Environment and Workloads                   | 80  |

|         | 3.3.1   | Modeling Core Power Up                            | 81  |

|         | 3.3.2   | Workloads                                         | 82  |

|         | 3.3.3   | Organization of Experiments                       | 84  |

| 3.4     | Micro   | benchmark Results                                 | 84  |

|         | 3.4.1   | Results on Real x86 Hardware                      | 85  |

|         | 3.4.2   | Results on Simulated Hardware                     | 85  |

| 3.5     | Effects | s of Architectural Parameters                     | 86  |

|         | 3.5.1   | L1 Cache Sizes                                    | 87  |

|         | 3.5.2   | Core Wake-Up Delay                                | 88  |

| 3.6     | Macro   | benchmark Results                                 | 89  |

|         | 3.6.1   | Web Benchmark                                     | 89  |

|         | 3.6.2   | Database Benchmark                                | 92  |

|         | 3.6.3   | Network Streaming Benchmarks                      | 95  |

|         | 3.6.4   | Energy Efficiency                                 | 97  |

| 3.7     | Summ    | ary                                               | 98  |

| Chapter | 4 Int   | egrating Microsecond Circuit                      |     |

|         | Sw      | vitching into the Data Center                     | 100 |

| 4.1     | Relate  | d Work                                            | 104 |

| 4.2     | Motiva  | ation: Reducing Network Cost via Faster Switching | 106 |

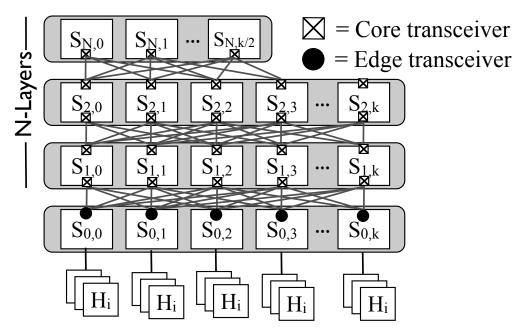

|         | 4.2.1   | Multi-layer Switching Networks                    | 106 |

|         | 4.2.2   | OCS Power Advantages                              | 108 |

|         | 4.2.3   | OCS Model                                         | 110 |

| 4.3     | OCS 7   | Fhroughput and Latency                            | 111 |

|         | 4.3.1   | Throughput                                        | 112 |

|                       | 4.3.2 Latency                               | 112 |  |

|-----------------------|---------------------------------------------|-----|--|

| 4.4                   | Implementation                              | 115 |  |

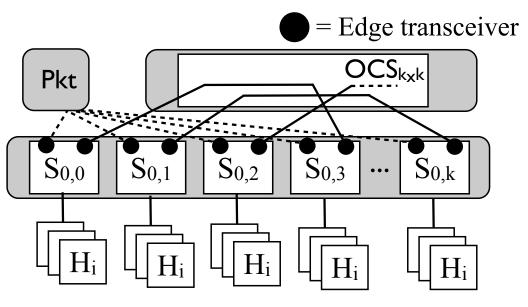

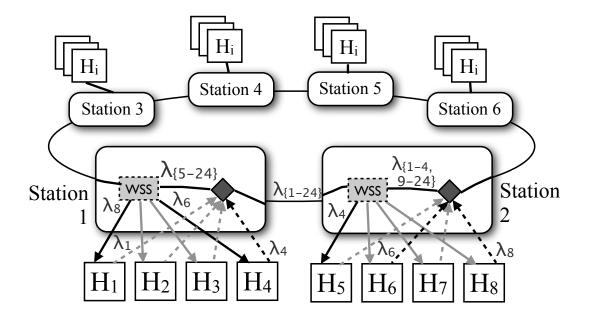

|                       | 4.4.1 Mordia Prototype                      | 116 |  |

|                       | 4.4.2 Emulating TORs with Commodity Servers | 121 |  |

|                       | 4.4.3 All-to-All Traffic Generator          | 138 |  |

| 4.5                   | Evaluation                                  | 140 |  |

|                       | 4.5.1 Emulated TOR Software                 | 140 |  |

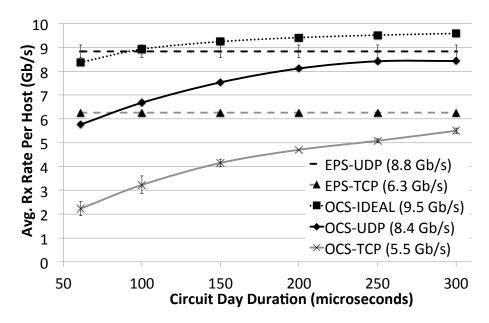

|                       | 4.5.2 Throughput                            | 142 |  |

| 4.6                   | Summary                                     | 146 |  |

| 4.7                   | Acknowledgments                             | 146 |  |

| Chapter 5 Summary 148 |                                             |     |  |

| Bibliography 15       |                                             |     |  |

#### LIST OF FIGURES

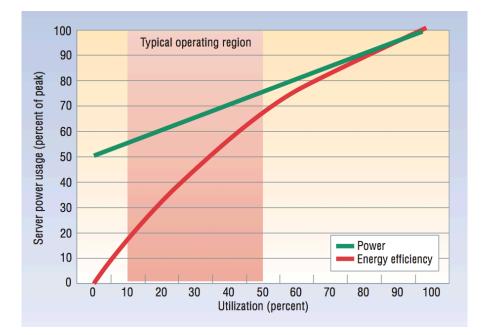

| Figure 1.1.  | Data center server average power and energy efficiency as a func-<br>tion of CPU utilization from [16]                      | 2  |

|--------------|-----------------------------------------------------------------------------------------------------------------------------|----|

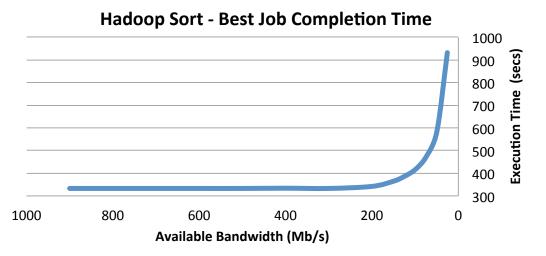

| Figure 1.2.  | Best job completion time for Hadoop sort as a function of greater network oversubscription [121]                            | 10 |

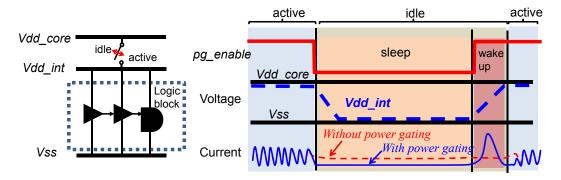

| Figure 2.1.  | Operation of the power-gating technique                                                                                     | 21 |

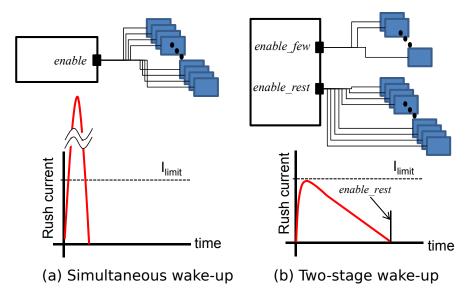

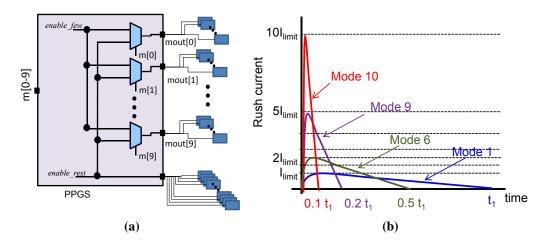

| Figure 2.2.  | Wake-up current profiles with different wake-up controls                                                                    | 21 |

| Figure 2.3.  | PPGS design and inrush current profiles vs. wake-up modes                                                                   | 23 |

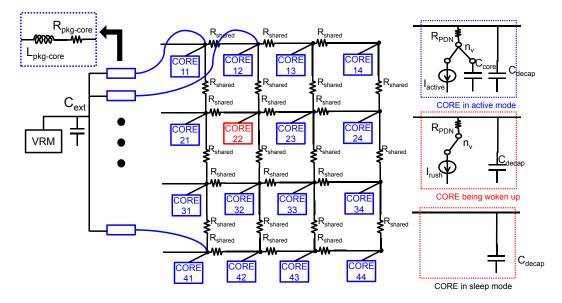

| Figure 2.4.  | 16-core system power delivery network with power gating                                                                     | 26 |

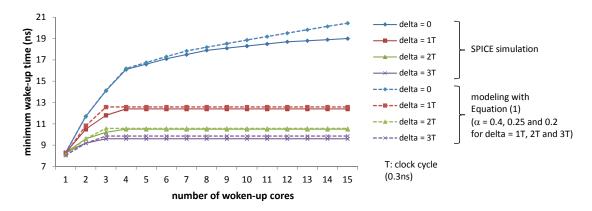

| Figure 2.5.  | SPICE-calculated minimum wake-up latency for an EV6 16-core CMP with various wake-up scenarios                              | 27 |

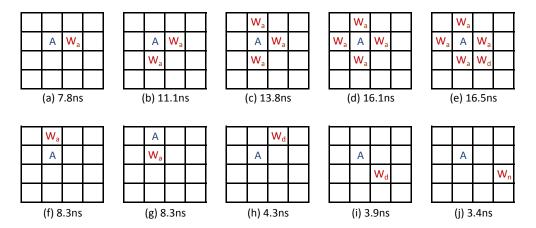

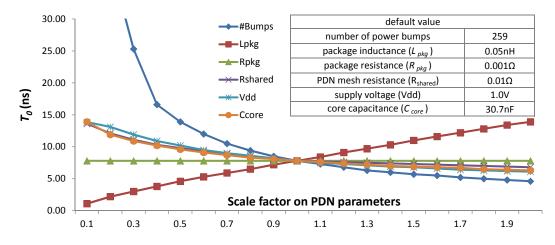

| Figure 2.6.  | Wake-up latency coefficient, $T_0$ , as a function of PDN parameters.                                                       | 29 |

| Figure 2.7.  | Minimum wake-up latency as a function of wake-up stagger                                                                    | 30 |

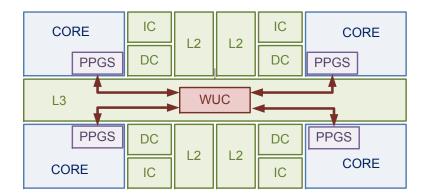

| Figure 2.8.  | WUC and PPGS integration into a 4-core CMP                                                                                  | 31 |

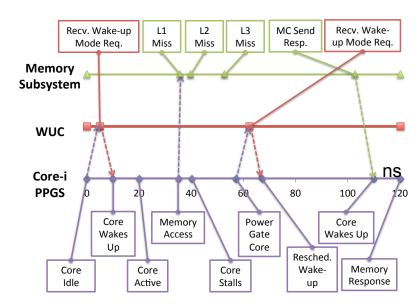

| Figure 2.9.  | WUC, Core-i PPGS, and Memory Subystem timing diagram                                                                        | 31 |

| Figure 2.10. | Wake-up slot assignments with different number of slots $(\eta)$                                                            | 33 |

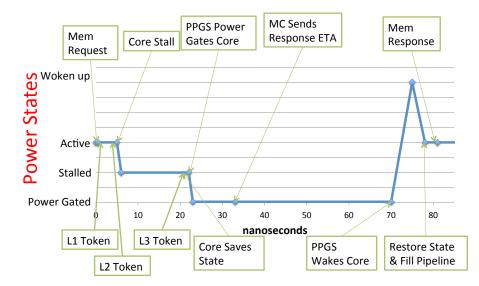

| Figure 2.11. | A diagram of TAP's power-gating behavior                                                                                    | 38 |

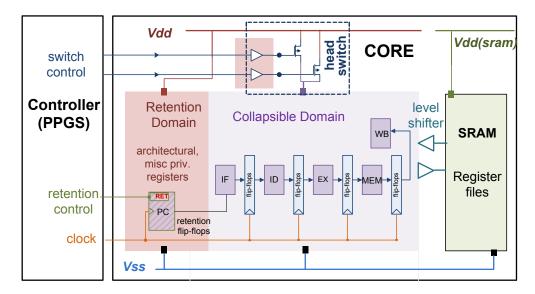

| Figure 2.12. | Interface for power gating and data retention                                                                               | 43 |

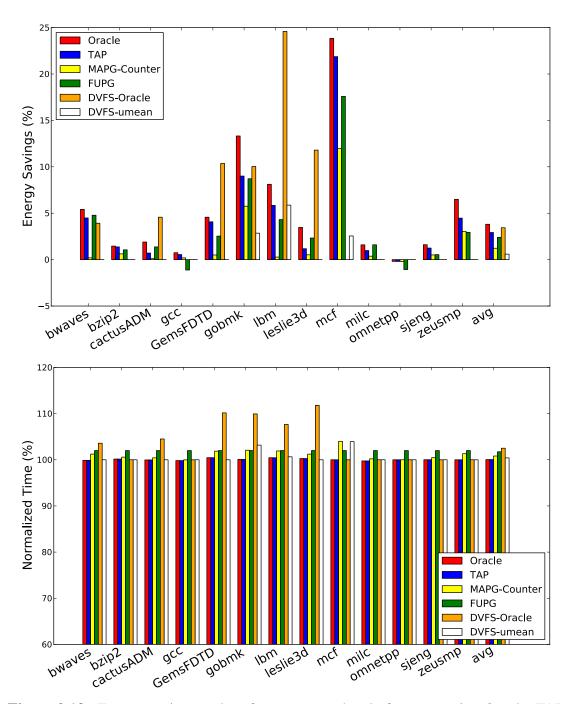

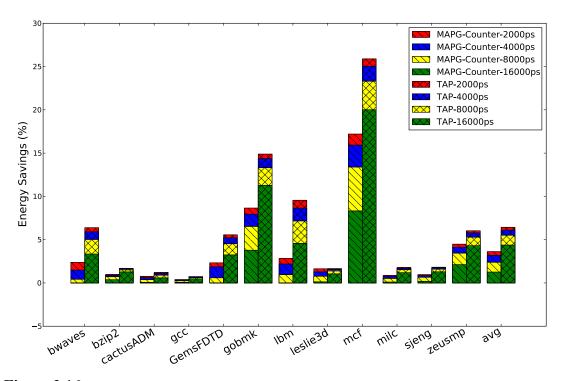

| Figure 2.13. | TAP and MAPG-Counter EV6 energy savings                                                                                     | 49 |

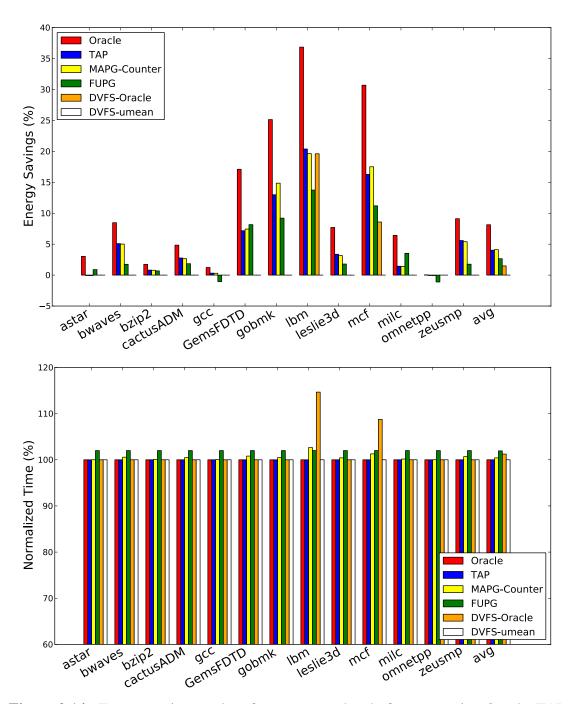

| Figure 2.14. | TAP and MAPG-Counter in-order energy savings                                                                                | 50 |

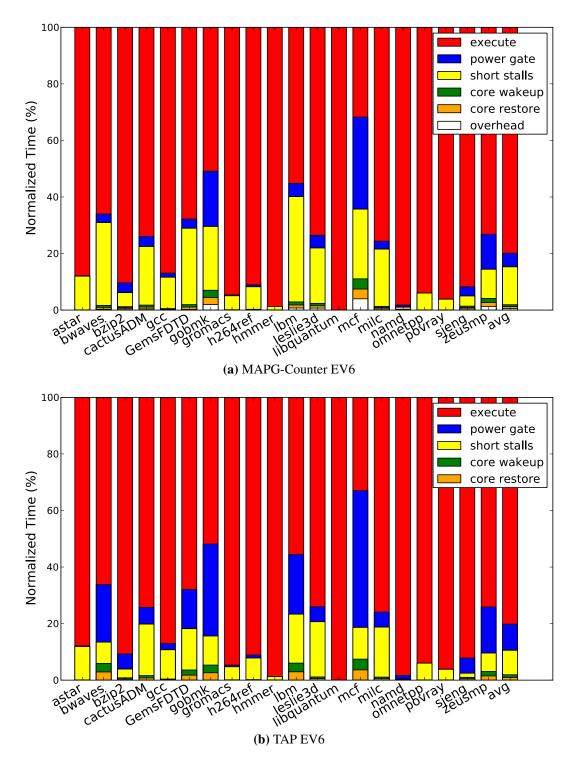

| Figure 2.15. | Breakdown of simulation time for each benchmark running on an EV6 core utilizing either MAPG-Counter or TAP to save energy. | 54 |

| Figure 2.16. | Energy savings for MAPG-Counter and TAP as core wake-up latency varies from 2 <i>ns</i> to 16 <i>ns</i>                     | 56 |

| Figure 2.17. | TAP and MAPG-Counter adapting to increasing memory contention                                                               | 58 |

| Figure 2.18. | Core wake-up latency improvement from stagger                                                                               | 61 |

| Figure 2.19. | Core energy savings improvement from stagger                                                                       | 61  |

|--------------|--------------------------------------------------------------------------------------------------------------------|-----|

| Figure 2.20. | Distributed WUC's impact on power-gated time                                                                       | 62  |

| Figure 3.1.  | Example of a system call modified to support core switching                                                        | 74  |

| Figure 3.2.  | Timeline showing 2 core switches between a pair of cores, using fast-path versions of <i>schedule</i>              | 77  |

| Figure 3.3.  | Abstract pseudo-code for modified versions of <i>schedule()</i>                                                    | 78  |

| Figure 4.1.  | A comparison of a scale-out FatTree network and a Hybrid electri-<br>cal/optical network                           | 102 |

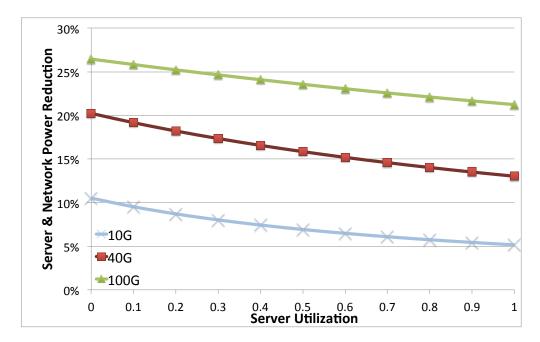

| Figure 4.2.  | Data center power reduction from the introduction of a core switch OCS                                             | 110 |

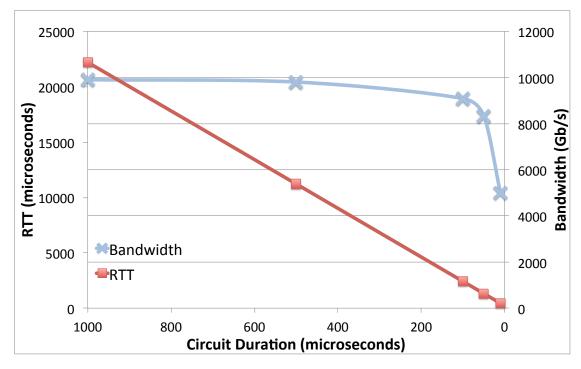

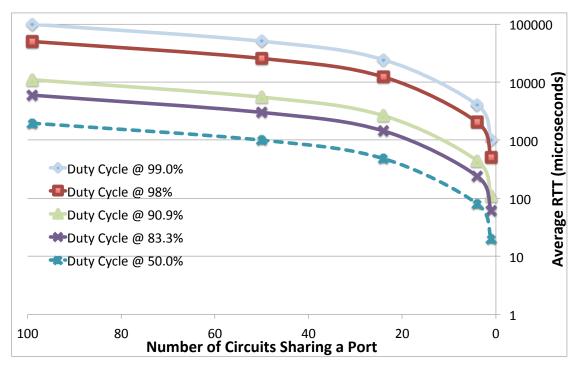

| Figure 4.3.  | The effect of changing duty cycle on OCS bandwidth and RTT                                                         | 113 |

| Figure 4.4.  | The effect of changing duty cycle and number of port sharers on OCS RTT                                            | 114 |

| Figure 4.5.  | Logical diagram of the Mordia OCS prototype                                                                        | 116 |

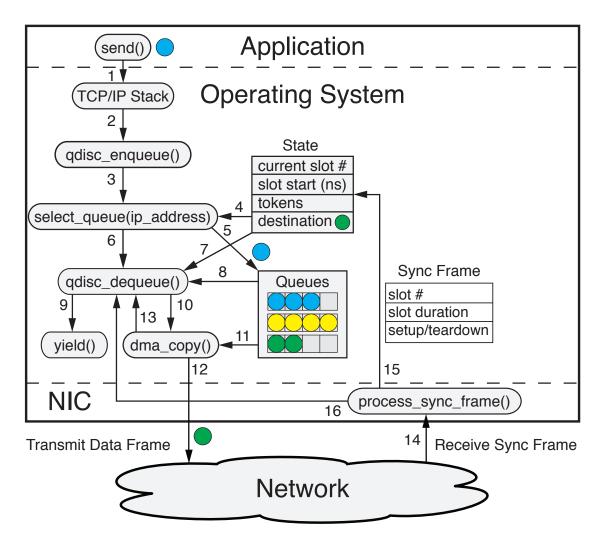

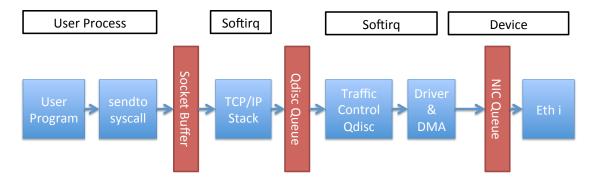

| Figure 4.6.  | The software implementation of a software TOR                                                                      | 123 |

| Figure 4.7.  | Steps for a user program to transmit a packet                                                                      | 124 |

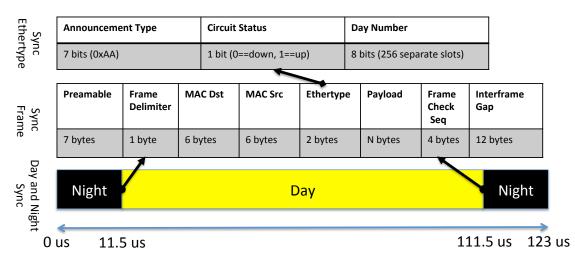

| Figure 4.8.  | Organization of day and night synchronization frames                                                               | 128 |

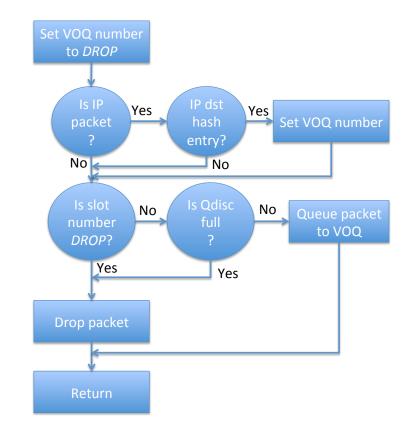

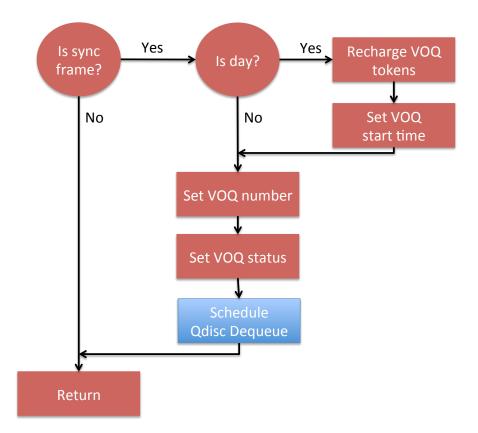

| Figure 4.9.  | A flow diagram depicting the MTOR Qdisc enqueue function                                                           | 130 |

| Figure 4.10. | Pseudo-code flow diagram for synchronization processing                                                            | 131 |

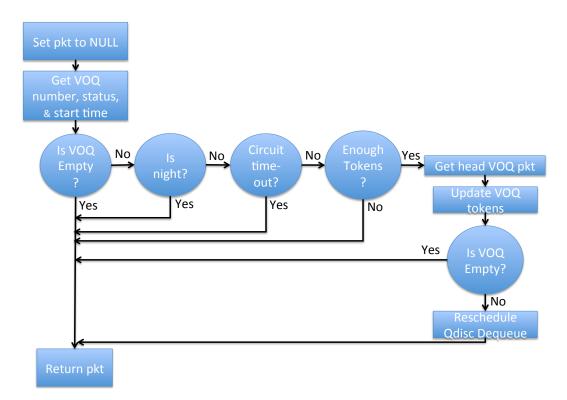

| Figure 4.11. | A flow diagram depicting the MTOR Qdisc dequeue function                                                           | 132 |

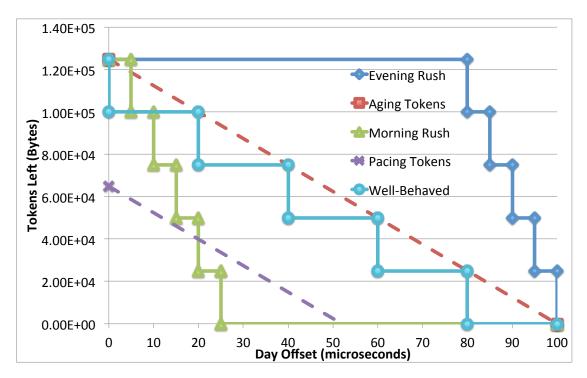

| Figure 4.12. | The case for enhanced token management                                                                             | 134 |

| Figure 4.13. | Actual OS code for how the <i>enough_tokens</i> function stage in Figure 4.11 determines the number of tokens left | 135 |

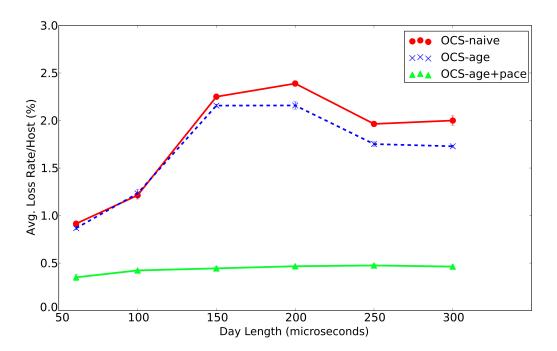

| Figure 4.14. | The impact of aging and pacing tokens on packet loss rate                                                          | 136 |

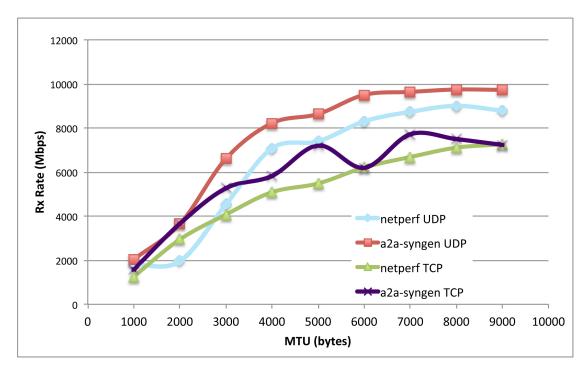

| Figure 4.15. | Throughput comparison between a2a-syngen and netperf for vary-<br>ing MTU between two hosts                        | 139 |

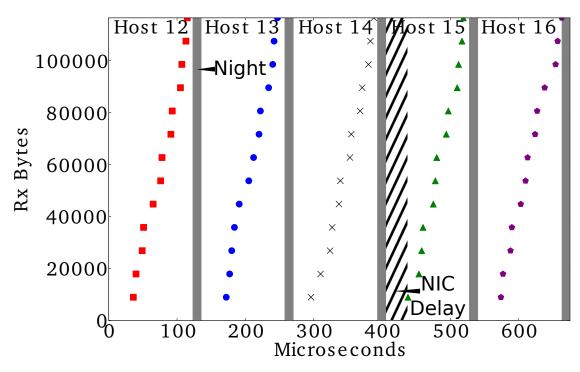

| Figure 4.16. | Host 1's Qdisc receiving UDP packets from Hosts 12–16 as it cycles through circuits connecting it to 22 other hosts. | 141 |

|--------------|----------------------------------------------------------------------------------------------------------------------|-----|

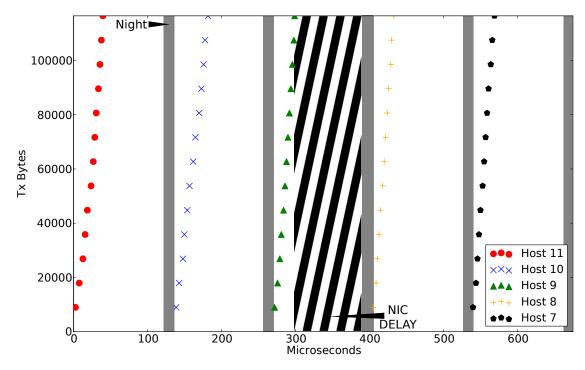

| Figure 4.17. | Host 1's Qdisc transmitting UDP packets to Hosts 7–11 as it cycles through circuits connecting it to 22 other hosts. | 142 |

| Figure 4.18. | Network throughput delivered over the OCS                                                                            | 143 |

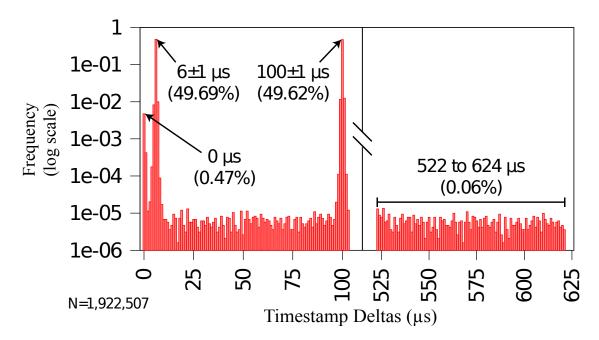

| Figure 4.19. | Synchronization jitter as seen by our software TOR's OS                                                              | 145 |

#### LIST OF TABLES

| Table 2.1.  | Estimated data for 32 <i>nm</i> HP, LOP and 22 <i>nm</i> HP, LOP in-order cores.                                                     | 24 |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------|----|

| Table 2.2.  | Average and maximum error on the modeled wake-up time for 4-, 6-, 8-, and 16-core cases (EV6, 32 <i>nm</i> HP).                      | 28 |

| Table 2.3.  | System configuration values                                                                                                          | 45 |

| Table 3.1.  | Summary of core-switching versions                                                                                                   | 72 |

| Table 3.2.  | A mapping from architectural configuration name to core types for<br>both the application and OS core                                | 80 |

| Table 3.3.  | Fraction of CPU time spent in various modes. Measurements are based on unmodified Linux on a <i>simulated</i> uniprocessor           | 83 |

| Table 3.4.  | Microbenchmark results for <i>gettid</i> per-call delay with 1,000,000 samples per trial                                             | 85 |

| Table 3.5.  | Microbenchmark results with cross-core wake up                                                                                       | 86 |

| Table 3.6.  | Effect of L1 cache size on microbenchmark results, using the V5 core-switching mechanism                                             | 87 |

| Table 3.7.  | Effect of power-up delay on performance                                                                                              | 88 |

| Table 3.8.  | Simulated Web results on dual-core CPUs for 1G and 10G NICs.<br>Values are KB transferred during 133 ms.                             | 90 |

| Table 3.9.  | Core-switch counts for 1 Web trial, dual-core X86                                                                                    | 91 |

| Table 3.10. | Simulated Web results on quad-core CPUs. Values are KB trans-<br>ferred during 133 ms                                                | 91 |

| Table 3.11. | Simulated throughput for <i>ex_tpcb</i> . Values are transactions/sec. rates (for 100 transactions). This trial used 16 KB L1 caches | 92 |

| Table 3.12. | Throughput for $ex\_tpcb$ on dual-core X86                                                                                           | 94 |

| Table 3.13. | Core-switch counts for 1 ex_tpcb trial, dual-core X86                                                                                | 94 |

| Table 3.14. | Simulated Netperf results for TCPstream. Values are KB transferred during 167 ms.                                                    | 94 |

| Table 3.15. | Simulated Netperf results: TCPmaerts. Values are KB transferred during 167 ms.       | 95  |

|-------------|--------------------------------------------------------------------------------------|-----|

| Table 3.16. | Core-switch counts for 1 netperf trial, dual-core X86                                | 96  |

| Table 3.17. | Energy efficiency comparison between the bound and V5 kernels (KTrans/s/W or MB/s/W) | 97  |

| Table 4.1.  | Power consumption of data center networking components                               | 109 |

#### ACKNOWLEDGEMENTS

I would like to take this chance to acknowledge the people, who have been instrumental in my getting a PhD. I thank my parents who instilled in me a sense of importance for continuing my education. I thank my wife, who not only withstood my nearly endless turmoils and would selflessly offer her help in my research, but who also managed to take this road to a PhD at the same time. I also would like to thank my advisors, my dissertation committee, my fellow researchers, my friends, and my family. I thank the people at the following institutions based on chronological order: J. L. Pettis VA Medical Center, UC Los Angeles, City of Hope, Uwink Inc., UC San Diego, MIPS Technologies, and HP Labs. I am grateful to Ericsson, Google, Qualcomm, Oracle, Cisco, Microsoft, CIAN, MuSyC, GSRC, and NSF grants CCF-0702349, EEC-0812072, CNS-0923523, SHF-0916127, SHF-1218666, SHF-1116667, and CCF-1162085 for supporting the research projects that contributed to my dissertation.

Chapter 2 contains material from "MAPG: Memory Access Power Gating", by Kwangok Jeong, Andrew B. Kahng, Seokhyeong Kang, Tajana S. Rosing, and Richard Strong, which appears in *Design, Automation & Test in Europe Conference & Exhibition*, 2012. The dissertation author was a principle contributor and author of this paper.

Chapter 2 also contains material from "TAP: Token-Based Adaptive Power Gating", by Andrew B. Kahng, Seokhyeong Kang, Tajana S. Rosing, and Richard Strong, which appears in the *ACM/IEEE International Symposium on Low Power Electronics and Design*, 2012. The dissertation author was a principle contributor and author of this paper. This material is copyright ©2012 by the Association for Computing Machinery, Inc. Permission to make digital or hard copies of part or all of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. Copyrights for components of this work owned by others than ACM must be honored. Abstracting with credit is permitted. To copy otherwise, to republish, to post on servers, or to redistribute to lists, requires prior specific permission and/or a fee. Request permissions from Publications Dept., ACM, Inc., fax +1 (212) 869-0481, or permissions@acm.org.

In addition, Chapter 2 contains material from "Many-Core Token-Based Adaptive Power Gating", by Andrew B. Kahng, Seokhyeong Kang, Tajana S. Rosing, and Richard Strong, which will appear in in the *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems*. The dissertation author was a principle contributor and author of this paper.

Chapter 3 contains material from "Fast Switching of Threads Between Cores", by Richard Strong, Jayaram Mudigonda, Jeffrey C. Mogul, Nathan Binkert, and Dean Tullsen, which appears in *SIGOPS Operating Systems Review*, Volume 43, Issue 2 on April 2009. The dissertation author was the primary investigator and author of this paper. This material is copyright ©2009 by the Association for Computing Machinery, Inc. Permission to make digital or hard copies of part or all of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. Copyrights for components of this work owned by others than ACM must be honored. Abstracting with credit is permitted. To copy otherwise, to republish, to post on servers, or to redistribute to lists, requires prior specific permission and/or a fee. Request permissions from Publications Dept., ACM, Inc., fax +1 (212) 869-0481, or permissions@acm.org.

Chapter 4 contains material from "Integrating Microsecond Circuit Switching into the Data Center", by George Porter, Richard Strong, Nathan Farrington, Alex Forencich, Pang-Chen Sun, Tajana S. Rosing, Yeshaiahu Fainman, George Papen, and Amin Vahdat, which will appear in the proceedings of *The Special Interest Group on*  *Data Communications*, 2013. The dissertation author was the secondary investigator and author of this paper.

#### VITA

| 2003      | Internship<br>J. L. Pettis VA Medical Center, Loma Linda, CA                            |

|-----------|-----------------------------------------------------------------------------------------|

| 2005      | Internship<br>City of Hope, Duarte, CA                                                  |

| 2006      | B.S. of Computer Science and Engineering<br>University of California, Los Angeles       |

| 2006      | Software Engineer<br>Uwink Inc.                                                         |

| 2007      | Internship<br>MIPS Technologies, Mountain View, CA                                      |

| 2008      | Internship<br>HP Labs, Palo Alto, CA                                                    |

| 2009      | Teaching Assistant<br>University of California, San Diego                               |

| 2009      | M.S. of Computer Science<br>University of California, San Diego                         |

| 2009      | Teaching Assistant<br>University of California, San Diego                               |

| 2009–2013 | Research Assistant<br>University of California, San Diego                               |

| 2013      | Ph.D. of Computer Science (Computer Engineering)<br>University of California, San Diego |

#### PUBLICATIONS

G. Porter, R. Strong, N. Farrington, A. Forencich, P. Sun, T. Rosing, Y. Fainman, G. Papen, and A. Vahdat. Integrating Microsecond Circuit Switching into the Data Center. To appear in *Proc. Special Interest Group on Data Communications*, 2013.

A. B. Kahng, S. Kang, T. S. Rosing, and R. Strong. Many-Core Token-Based Adaptive Power Gating. To appear in *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems*.

A. B. Kahng, S. Kang, T. S. Rosing, and R. Strong. TAP: Token-Based Adaptive Power Gating. In *Proc. International Symposium on Low Power Electronics and Design*, pages 203-208, 2012.

K. Jeong, A. B. Kahng, S. Kang, T. S. Rosing, and R. Strong. MAPG: Memory Access Power Gating. In *Proc. Design, Automation, & Test in Europe Conference & Exhibition*, pages 1054-1059, 2012.

R. Strong, J. Mudigonda, J. C. Mogul, N. Binkert, and D. Tullsen. Fast Switching of Threads Between Cores. *SIGOPS Operating Systems Review*, 43(2):35-45, 2009.

A. K. Coskun, R. Strong, D. M. Tullsen, and T. S. Rosing. Evaluating the Impact of Job Scheduling and Power Management on Processor Lifetime for Chip Multiprocessors. In *Proc. Conference on Measurement and Modeling of Computer Systems*, pages 169-180, 2009.

S. Li, J. Ahn, R. Strong, J. B. Brockman, D. M. Tullsen, and N. P. Jouppi. McPAT: An Integrated Power, Area, and Timing Modeling Framework for Multicore and Manycore Architectures. In *Proc. International Symposium on Microarchitecture*, pages 469-480, 2009.

#### ABSTRACT OF THE DISSERTATION

Low-Latency Techniques for Improving System Energy Efficiency

by

Richard D. Strong

#### Doctor of Philosophy in Computer Science (Computer Engineering)

University of California, San Diego, 2013

Tajana S. Rosing, Chair Dean M. Tullsen, Co-Char

U.S. data center energy consumption is expected to rise past 100 billion kWh in 2013. Approximately 50% of this energy usage can be attributed to servers, networks, and storage, and the other half goes to power and cooling infrastructures in their support. Servers are so non-energy efficient that they consume 65% of a fully utilized server's power when only 30% utilized. Even when 100% utilized, the server may not be running efficiently.

This dissertation improves the energy efficiency of data center systems in three ways. The first method improves server energy efficiency by turning off CPU cores during

long-latency memory accesses with no performance penalty to data center applications. This technique leverages peak rush current from on-chip power distribution networks to quickly charge core capacitance, and allows the core to resume execution in as little as 8.06 ns. Core state is saved through careful use of slave latches and source biasing.

A key means to increasing effective CPU utilization and energy efficiency of servers, is to leverage virtual machine and thread migration at minimal performance overhead. Our second technique speeds up software thread migration by up to  $2.5 \times$  compared to Linux, with latencies as small as 933 ns. We leverage this technique to quickly migrate operating system code between asymmetric cores to reduce application energy consumption.

The techniques introduced so far assume that I/O devices have sufficient bandwidth to keep the server processor busy. In contrast to this assumption, many data centers oversubscribe their networks to reduce cost and power consumption, sometimes at the expense of overall data center efficiency. Our last contribution is a software top-of-the-rack switch capable of offloading unmodified TCP/IP traffic onto a prototype, microsecond optical circuit switch within a microsecond. We demonstrate that servers can utilize up to 95.4% of optical circuit bandwidth even when switch reconfiguration latency is reduced by three orders of magnitude to 11.5  $\mu$ s, supporting the introduction of low-latency optics into the data center to radically reduce cost and power consumption of full bisection bandwidth networks.

## Chapter 1 Introduction

U.S. data center energy consumption has risen steadily since the year 2000, and is expected to reach more than 100 billion kWh in 2013, costing \$7.4 billion each year [5]. Further, individual data centers have increased their power demand to as much as 100 MW [34]. Data centers are expected to grow in size and number, due to demand for cloud services from mobile devices, tablets, and big data. The U.S. EPA found that 50% of data center energy usage can be attributed to servers, networks, and storage with each part accounting for 40%, 5%, and 5%, respectively [5]. Hence pressure exists to improve the energy efficiency of data centers, and such efforts must consider the contributions of servers, networks, and disks. Further, the remaining 50% of power consumption is attributed the power and cooling infrastructure that supports servers, networks and disks, and so their energy efficiency in inherently intertwined.

## **1.1 Efficiency with Minimal Performance Impact**

Servers are one of the largest contributors to data center power. However, two disturbing trends exist in today's data center servers. First, they spend a majority of their time at 30% utilization or less [16]. This happens because data center operators over provision their data center to meet peak demands due to strict quality of service (QoS) guarantees, and reliability requirements.

For an example of strict QoS guarantees, Google search found that users who were subjected to a random delay between 100 ms to 400 ms, reduce their total number of searches by up to 0.76% [24]. Google also found that longer exposures to delay, causes an increasing reduction in searches, implying a worrisome correlation between service delay and profitability. Inside the data center, the acceptance for delay is less. Services like *Memcached* [46] and *RAMCloud* [97] can be queried numerous times by other servers to satisfy a single request, leading to sensitivity on a microsecond time scale. In addition, some services are more sensitive to the tail latency of requests, meaning that overall speed does not matter so much as the worst case. As a result, data center operators over provision their systems to avoid costly regions of operation and disgruntled users.

**Figure 1.1.** Data center server average power and energy efficiency as a function of CPU utilization from [16]

Over provisioning data center servers comes at a price since servers are not energy proportional (see Figure 1.1). An ideal energy proportional server should use power in proportion to the amount of resources it uses. However, a 30% utilized server consumes 65% of the power of a fully utilized server [16]. Even worse, a data center that accomplishes no interesting work still consumes half as much server power as a fully utilized data center.

The lack of energy proportionality of servers is worse than the result reported in [16]. The study reports only CPU utilization, under the assumption that server utilization is proportional to CPU utilization. However, even when a server is fully utilized as measured by CPU utilization, the server many have many subcomponents, including the CPU, that are not fully utilized. For instance, the CPU may experience a long-latency memory access that misses in the cache hierarchy, causing it to stall. If the CPU executes operating system code with significant instructional dependencies, both the CPU and memory subsystem will be underutilized. Alternatively, if a network application uses the *poll* system call or non-blocking sockets to check for incoming data, but is bottlenecked by the network, then the CPU and memory will once again be underutilized. In all of these cases, the operating system would report CPU utilization at 100%. Ergo, the second disturbing trend is that a server at 100% CPU utilization may not necessarily be operating efficiently.

Moore's Law [92] may improve data center energy efficiency via smaller transistors that offer both performance improvements and power reduction. However, a transistor-based device in the data center consumes power in two forms: dynamic and leakage. Dynamic power represents the power of switching transistors while they perform useful work, while leakage power is consumed even when the device is idle. Distressingly, constraints that limit scaling of device threshold voltages, reduce device supply voltages, and improve transistor switching speed lead to leakage power becoming an increasingly dominate component of system power consumption. For example, leakage power contributes to 41% of overall server processor power to run the Spec2006 application suite on a processor built in the 22 nm technology node [78]. Transistor leakage is significant for not only the server processor, but for many other data center devices such as memory, NICs, controllers, switches, and others.

Given that technology scaling alone will likely not solve the problem, and the critical interactions between data center software and hardware, solutions should come in the forms of both hardware and software changes. In the domain of hardware-only changes, there have been several exciting proposals. These techniques range from automatically generating custom ASICs to efficiently execute common applications [113] and advanced dynamic voltage frequency scaling (DVFS) techniques [35, 38, 63], to introducing network switches that dynamically adapt links rates to improve network energy proportionality [10]. Such hardware changes can avoid software control, allowing very fine-grained decisions for a subsystem of the data center. For the case of hardware techniques, it is important to remember that the improvement of a subsystem can have important implications for the entire data center since data centers often reuse the same components throughout their infrastructure. For example, a technique that improves the energy efficiency for a single core may be applied across millions of cores in the data center. This dissertation contributes to this area of research by investigating the use of low-overhead power gating to improve the energy efficiency of server processors.

However, software is critically involved in the interaction of data center servers. Although software can be an order of magnitude slower than hardware-only solutions, it often allows coarser-grain decisions that affect the efficiency of several data center subsystems. For instance, some publications focus on the interaction of disks, memory, and software to improve the performance of processing big data [102, 119], while others may use binary translation to more efficiently use processor resources [120]. Software changes can also yield benefits at the data center scale, as data center operators like Amazon, Rackspace, Google, and Red Hat use a virtualized infrastructure that shares hypervisors, operating systems, and services across tens of thousands of servers. A technique that speeds up thread migration between cores, or allows virtual machines (VM) to migrate faster between servers can often be leveraged at data center scale. This dissertation develops a fast core-switching technique that can quickly migrate threads between cores on a multicore processor to enable energy efficiency opportunities that rely on constant thread migration.

The interaction of software and hardware is not limited to servers as the network is often involved in the efficiency of both. Software designs can use different software techniques, protocols (i.e. TCP and UDP), and operating system calls (e.g., *poll* and *select*), which can all change the behavior of data center network demand. Even for a fixed software configuration, the topology and offered link rates of the interconnecting switches can have dramatic impacts on the availability of bandwidth between two servers. Techniques that address these concerns range from software control of the network via OpenFlow [86] and Open vSwitch [99], to techniques that provide full bisection network bandwidth from commodity switches [12, 93]. This dissertation uses software control of the network to demonstrate the viability of integrating a prototype microsecond optical circuit switch into the data center. Optical switches offer the promise of providing full bisection bandwidth and a three orders of magnitude reduction in energy consumption. The next sections provide greater detail about the actual techniques that this dissertation proposes.

## **1.2** Power Gating

Up to this point, we introduce research that makes a case that servers are not energy proportional, and that transistor scaling alone will not solve the problem. Further, transistor scaling exasperates the problem due to an increased contribution of leakage power to total power. A useful example of this problem exists for server processors, which usually account for the largest contribution of server power [40]. During every cycle that a server processor core is on, even when stalled, leakage power is consumed via gate leakage, gate-induced drain leakage, junction leakage, and subthreshold leakage.

*Power gating* is a technique that drastically reduces leakage power by cutting off the current path from supply to ground through introduction of a transistor switch between them. Better yet, it does not suffer from the inability to scale device threshold voltages in the face of aggressive supply voltage scaling that plagues DVFS.<sup>1</sup> At one end of the spectrum, functional unit power gating reduces power consumption of unused core functional units [116] with wake-up latencies of several nanoseconds. At the other end, entire cores may be power gated and woken up, with latencies of several tens of microseconds to account for saving and restoring all core state from memory [103].

Power gating cuts all supply voltage to logical cells, causing them to lose state. The techniques to address this problem differ by cell type: complex, sequential, and SRAM. Complex cells implement gate logic, and after power gating, they merely require time to power up and for their input signals to be valid. Sequential cells maintain state, and after power gating, they must power up, be reset, and restore their logical state. The fact that sequential cells must restore their logical state, means that they must save it in a modified cell that is able to survive supply voltage collapse, or that their value may be restored through an interaction of other sequential cells and complex logic. Saving sequential cells comes at roughly a 20% overhead in leakage power and area per cell [67], so the minimal subset of sequential cells should be able to retain state when power gated. Last, if SRAM were power-gated, then it too would lose state, which could potentially cause large performance penalties. Alternatively, source biasing may be used in which supply voltage is reduced by half, so that SRAM leakage is reduced, but logical state is maintained. This technique requires a separate voltage domain to supply SRAM, which

<sup>&</sup>lt;sup>1</sup>DVFS is one of the most common techniques for reducing server processor power consumption in servers today

results is less leakage power savings, but also minimizes performance overhead.

Once we can power gate each cell, the next problem is when to power gate, and when to wake up from a power-gated state. Waking up from a power-gated state takes time and energy to supply all cells with the necessary charge from the supply voltage line. If the device does not remain in the power-gated state for long enough, it is quite possible that wake-up energy would exceed the energy savings from reductions in leakage power. Even if power gating can reduce leakage power consumption over power-gated intervals, if the delay to wake the device is too long, the contribution of other system components can easily increase energy consumption overall.

The goal is to power gate underutilized cores, avoid performance impact, and to improve overall server energy efficiency. Chapter 2 proposes a low-latency, power-gating technique to turn off cores stalled on a long-latency, memory access. When a core accesses a memory address that is not cached, the memory request must propagate through the cache hierarchy, chip interconnect, and get scheduled by the memory controller. If the core stalls due to the memory dependency, a controller saves the core's architectural state and then power gates the core. To avoid performance and energy overhead, the controller maintains a lower bound on each memory request's latency, and only power gates the core if sufficient time remains. This technique allows cores to make power-gating decisions at a 10 *ns* time scale without any measured performance impact. Simulations show up to 22.4% core energy savings on a memory bound benchmark. Further, avoiding performance impact allows this technique to be deployed in data center servers without impact on a service's QoS.

Power gating is best suited to address the energy efficiency of servers executing memory bound applications, but it does little to improve the efficiency of applications that experience short stalls or underutilized subcomponents in the processor. Further, the technique requires modifications to hardware which will not benefit existing servers.

## **1.3 Fast Core Switching**

Today's servers continue to receive the benefits of the multicore era, in which a single 1 U server can support up to 64 cores [8]. As a result, the communication costs between cores have been reduced by an order of magnitude. If we consider that data centers can have tens of thousands of servers, each server has tens of cores, and that these cores are mostly underutilized, then there are, currently, millions of underutilized cores in the data center. One way to exploit this vast resource is through low-latency thread migration.

Thread migration may be used to distribute single-threaded computation between many cores to see parallel-like speedups and energy reduction due to an increase in cache capacity from many cores [66]. Low-latency thread migration can also speedup loadbalancing operations to allow cores to more quickly balance the assignment of threads between symmetric cores in which maximizing simultaneous operations on a server and improving its energy efficiency [82]. For asymmetric core architectures, dynamic, fine-grained load-balancing of threads between cores can outperform static assignment between 20% and 40% on average [18]. When a server executes a system call and enters the operating system, it is possible to improve energy efficiency by switching to a simpler core due to many instructional dependencies and large working sets of operating system code [89]. Many existing servers support changing the voltage and frequency of different cores or sockets, which allows the transformation of the vast idle core resource into an asymmetric core resource.

In all of these cases, the latency of thread migration between cores is critical. Chapter 3 considers a dimension of this problem by developing a low-latency, softwarebased, core-switching technique that can be used to migrate applications between asymmetric cores. Asymmetric cores may be chosen to posses those resources most critical for efficient execution of each application, enabling energy savings even when the core does not stall long enough to power gate. Specifically, the technique migrates operating system (OS) code to a simpler, energy efficient core that still offers good performance. If the OS and hardware are co-designed, then further efficiency may be achieved. Simulation and server experiments indicate that the new technique can migrate Linux OS code between cores up to  $2.5 \times$  faster than previous software techniques with latencies as small as 933 ns. Use of core switching with asymmetric cores can improve server processor energy efficiency by up to  $6.16 \times$  for OS intensive codes. Data center servers may leverage this low-latency technique to improve the efficiency of load-balancing VMs<sup>2</sup>, thermal management, and computation spreading with minimal impact to QoS agreements that demand responses from critical servers within 10s of microseconds or less.

## **1.4** The Need for Efficient Network Bandwidth

Both power gating and fast core switching can offer improvements in server energy efficiency through hardware-only and software/hardware co-design. However, they both operate under the assumption that servers have access to the data they need to process locally, or that their I/O devices have sufficient bandwidth to keep the processor busy. In contrast to this assumption, sometimes a server or VM spends its time waiting for I/O, especially from the network due to oversubscription.

Data centers commonly oversubscribe their network at the higher levels of the switching fabric in order to manage cost, complexity, and power consumption of the network. As a result, should two or more servers need to communicate through the higher levels of the network, they may only receive a fraction of their requisite bandwidth demand called the *oversubscription ratio*. The Cisco design manual suggests that an oversubscription ratio between 2.5:1 and 8:1 is common in large cluster designs [1].

<sup>&</sup>lt;sup>2</sup>A VM is often a thread of some operating system

**Figure 1.2.** Best job completion time for Hadoop sort as a function of greater network oversubscription [121].

Other data center centers claim to suffer from an oversubscription ratio of 240:1 for 1 Gb/s servers [49]. Such oversubscribed networks may account for only 5% of data center power, but they can dramatically slow down virtualized services and nearly double server energy consumption to complete the same amount of work [121] (see Figure 1.2). At the extreme, some services like Hadoop [4] kill and retry parallel computations across hundreds of servers if a sufficient number of servers suffer from poor network behavior, resulting in high energy and performance overhead.

Many commodity servers often come integrated with 10 Gb/s network devices, and 40 Gb/s adapters compatible with PCI Express are available for \$260. Servers can offer these high-bandwidth network devices data from memory buffers at a data rate limited by either memory bandwidth<sup>3</sup> or PCI Express<sup>4</sup>. Today, some big data applications use server memory as a distributed parallel cache to save recently generated data for map reduce like jobs that require several iterations over that data, yielding order of magnitude improvements in performance over a disk only solution [119]. RAMCloud uses DRAM

<sup>&</sup>lt;sup>3</sup>79.55 GB/s for an 8-core, 2.9 GHz, Intel E5-2690 server running STREAM [84]

<sup>&</sup>lt;sup>4</sup>PCI Express v4.0 can offer 31.51 GB/s bandwidth across 16 lanes [25]

as a drop in replacement for disk to offer up to three orders of magnitude improvement in storage performance [97].

Even the underlying storage for the data center is poised to greatly increase in speed. Today, data centers use spinning disk technologies that have been around for decades, and operate near 7,200 RPM. Flash-based SSDs are commodity, scale linearly in performance in RAID arrays, and can offer sequential bandwidths of up to 569 MB/s. Phase change memory could potentially offer an order of magnitude improvement in sequential throughput at 2.932 GB/s [26]. Such an increase in raw storage bandwidth for a distributed file system may put significant pressure on the network. Taking these factors into account, network bandwidth demand will likely continue to rise in the foreseeble future.

To prevent the negative consequences of oversubscription and increasing network bandwidth demand, data centers can introduce a scaled-out network that offers full bisection bandwidth between any two hosts [12, 93]. However, such a network needs to be provisioned for the worst case communication pattern, leading to as many as nine layers in the largest networks. In general, an *N*-level scaled-out network built from *k*-radix switches can support  $k^N/2^{N-1}$  servers, with each layer of switching requiring  $k^{N-1}/2^{N-2}$  switches (though layer *N* itself requires half this amount). The implication is that higher level switches become less likely to be utilized and waste energy, as they also are not energy proportional [10]. Further, a full bisection network would consume as much power as the servers, if the servers became energy proportional and were 15% utilized on average [10].

In summary, today's data center networks contribute to only 5% of data center power, but offer bandwidth at an oversubscription ratio, which can adversely affect the energy efficiency of large distributed applications. Underlying storage technology, and software techniques that utilize memory for storage are poised to increase network bandwidth demand of commodity servers. Left unchecked, the network, especially near the core switch level, acts as a bottleneck against improving data center energy efficiency. Current techniques to provide networks with full bisection bandwidth can remove this bottleneck, but their complexity and power consumption may offset any gains seen from energy proportional servers. Thus, improvements in server energy proportionality should be followed by improvements in network energy consumption and offered bandwidth.

Electrical packet switch (EPS) networks have long been a cornerstone in data center networks, because of their improvements in offered bandwidth and ability to schedule each switch on a per packet basis. Today, 10 Gb/s Ethernet, high-radix switches with up to 96 ports are commodity. However, port switches with 40 Gb/s often have much lower port counts in the range of 16 to 24 ports, which adds complexity to the design of the data center network. Should the port counts of a 40 Gb/s and 100 Gb/s EPS continue to scale, then the limits of skin effect and Ethernet cable input power for practical data center distances will likely impede efforts to offer bandwidth in excess of 100 Gb/s [87].

In contrast, an optical fiber suffers loss of only  $2 * 10^{-4}$  dB/m [87], separating the concern of transmission rate from distance for today's data center sizes. Each fiber of an optical network can use wave division multiplexing to transmit between 44 - 177 channels (depending on channel spacing) at 20 Gb/s [71] per channel yielding between 880 - 3540 Gb/s. Optical circuit switches (OCS) based on 3D-MEMS Glimmerglass can offer switches that scale at 240 mW/port, agnostic to data rate compared to an electrical packet switch that consumes as much as 14.1 W/port at 10 Gb/s [43]. Such an OCS is also a space switch capable of each port delivering all frequencies to a specific output port.

There are at least two major challenges in integrating an OCS into the data center. First, an OCS port does not process each individual packet to determine a destination port. Instead, a circuit is setup between a source and destination port, which means that network control resides closer to the server. Second, in order to switch between circuits, a reconfiguration time is necessary. During this time, mirrors move into position, stop, vibrate, and no data may transit through the OCS port. A reconfiguration time imposes a duty cycle on the offered bandwidth of the switch, and also increases the average delay of packet through the switch if it shares a source or destination port with some other circuit.

Therefore, EPS networks face several challenges in terms of scaling up in bandwidth, while still offering full bisection bandwidth between hosts. Optics offers an opportunity to increase bandwidth per port by an order magnitude or more, while also allowing a two orders of magnitude reduction in power per port. However, an OCS offers its bandwidth in the form a circuit which could affect latency of packets through the network.

Chapter 4 explores the introduction of a microsecond optical switch (OCS) into the data center, with the focus on reducing the monetary cost and power consumption of providing full bisection network bandwidth between all servers. Specifically, this chapter designs a software top-of-the-rack switch (TOR) capable of delivering unmodified TCP/IP network traffic to a prototype OCS that can establish new circuits in as little as 11.5  $\mu$ s. The TOR is composed from a modified, network card device driver and OS that mutually schedule each other at a microsecond granularity. This technique enables OCS experiments with commodity servers and unmodified applications. Experiments with a small server cluster indicate that today's systems can utilize up to 95.4% of OCS bandwidth, giving rise to data center networks with full bisection bandwidth at a 24.7% reduction in data center power compared to an electrical technology. Consequently, data center servers that do not suffer network bottlenecks run more efficiently, and are more likely to meet their QoS requirements.

# Chapter 2 Memory Access Power Gating

Chapter 1 explains that servers contribute to 40% of the power consumption of data centers, the processor is often the largest contributor to this consumption, and that even a 100% utilized processor may not be executing efficiently. Indeed, during every cycle that a server processor core is on, even when stalled, leakage power is consumed via gate leakage, gate-induced drain leakage, junction leakage, and subthreshold leakage. A core may stall quite often if it is intensely accessing the memory subsystem, as every time a thread makes a memory request that misses in the L1 cache, the core is subjected to a variable access latency. This variable latency often translates into a core stall during which no forward thread progress occurs and energy is wasted. For a 32*nm* out-of-order EV6 core, stall energy can be up to 39.1% of total energy consumption for the Spec2006 benchmarks [78]. Further, many data center applications spend significant time in the OS, executing system calls and interrupts, which suffer from a large working set and memory bound behavior.<sup>1</sup>

Previous work has reduced core energy waste by lowering core frequency and voltage (DVFS) for memory-intensive threads when directed by L2-cache misses [37, 38, 63]. Some schemes can even direct core DVFS behavior based on signals from the L2-cache and estimates of instruction-level parallelism [77]. A slower core frequency results in

<sup>&</sup>lt;sup>1</sup>For more details, refer to Chapter 3, Table 3.3

fewer cycles waiting for the memory subsystem. Scaling down both frequency and voltage results in an estimated cubic dynamic power and quadratic leakage power savings [62]. However, the inability to scale device threshold voltages, coupled with aggressive scaling of supply voltages (subject to overdrive and performance requirements), means that cores have little room to reduce voltage during DVFS [105]. The net effect is decreased energy savings from DVFS, which motivates the development of new techniques to reduce core energy consumption while waiting for the memory subsystem.

*Power gating* is a technique that drastically reduces leakage power by cutting off the current path from supply to ground through introduction of a transistor switch between them. At fine granularity, functional unit power gating reduces power consumption of unused core functional units [116] with wake-up latencies of several nanoseconds. At coarse granularity, entire cores may be power gated and woken up, with latencies of several tens of microseconds to account for saving and restoring all core state from memory [103]. An intermediate mechanism that we design provides the ability to power gate an entire core, wake up a power-gated core in about 10 *ns*, and maintain the core's architectural and cache state. It uses a combination of a *programmable power gating switch* (PPGS), state retention cells, and source biasing to enable the core to efficiently enter and exit a power-gated state.

In this chapter, we compare two architectural techniques for directing the PPGS's behavior: *Memory Access Power Gating Counter* (MAPG-Counter) and *Token-Based Adaptive Power Gating* (TAP). MAPG-Counter directs core power gating by tracking the duration of core-stall periods with a counter for those stall periods that last longer than a last-level cache miss. It uses core-stall history to predict future stall periods. With these predictions, MAPG-Counter can predict the duration of stall periods, and direct the PPGS when to power gate a core with minimal performance hit. The benefit of this technique is in both its simplicity and its significant energy savings for in-order

cores. However, without detailed knowledge of all core memory requests, out-of-order execution and hard-to-predict stalls become a significant barrier to the use of this power gating mechanism.

TAP deterministically applies power gating during core stalls which are caused by the variable latency of requests to the memory subsystem. TAP achieves this by providing the capability to track every ongoing memory request and the expected response time for each memory access that misses in the L1 cache. An expected lower bound on latency is sent to each core's PPGS by modifying the cache controllers to send a token on any miss where the token includes an estimate of the access latency of a next-level memory hit. The result is that TAP can support power gating with no measured performance loss.<sup>2</sup>

To summarize, this chapter makes the following contributions:

- We compare two practical techniques, MAPG-Counter and TAP, to direct the PPGS controller on unmodified applications. We show that TAP can offer  $2.58 \times$  the average energy savings of MAPG-Counter for out-of-order cores.

- We show that MAPG-Counter can achieve slightly higher energy savings on average than TAP for an in-order core.<sup>3</sup>

- We show that TAP has no measurable impact on application performance or QoS.

- We formally analyze TAP's energy savings for in-order cores to achieve predictions of energy savings for an arbitrary memory hierarchy and application, with 0.82% and 9.75% average and maximum error.

- We compute the time at which a power-gating action breaks even with the wake-up energy to be 8.53 *ns* and 17.17 *ns* for in-order and out-of-order cores, respectively.

<sup>&</sup>lt;sup>2</sup>Our technique could cause a performance hit if a token got lost on the on-chip interconnect, or if a token got significantly delayed. However, our simulations do not observe this behavior.

<sup>&</sup>lt;sup>3</sup>The HP Moonshot System released in 2013 contains 45 hot pluggable servers, that are based on the Intel Atom S1260, a in-order core at 2 GHz.

- We decompose MAPG-Counter and TAP behavior into time spent power gating, waking up the core, restoring core state, and overhead to show that core wake-up and restore time averages 1.9% of execution time.

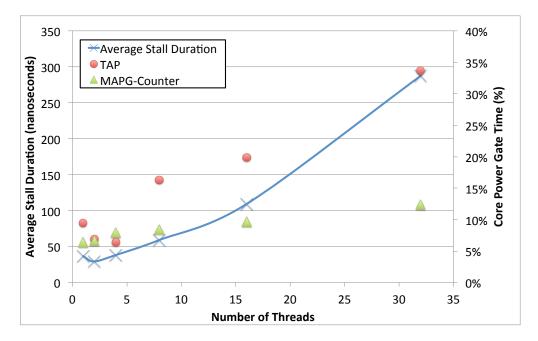

- We demonstrate that both MAPG-Counter and TAP can adapt to an increase in memory contention by increasing power-gated time by 2.02× and 3.69×, respectively, as the number of threads increases from 1 to 32.

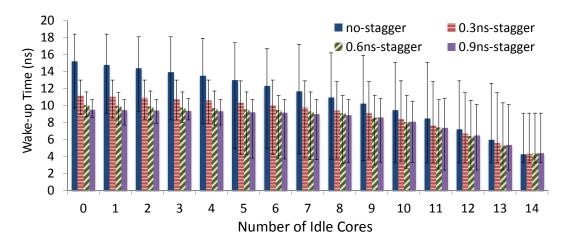

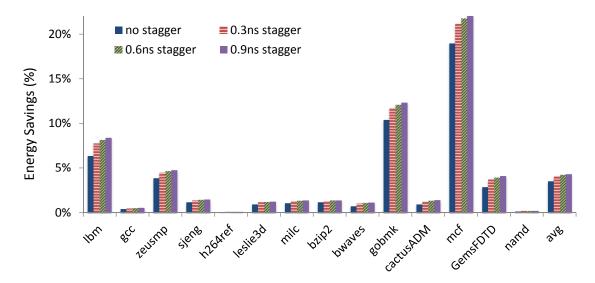

- We design and implement a staggered wake-up scheme capable of reducing wakeup latency up to 58.2%; this results in a 3.14% increase in energy savings for TAP.

# 2.1 Related Work

Power gating has been studied at both architectural and circuit levels. Microarchitectural works typically examine the questions related to use of different power-gating modes, what to power gate, predicting when to power gate, and control algorithms to avoid energy penalties from poor power-gating decisions. Circuit-level papers typically analyze different circuit techniques aimed at reducing wake-up latency, efficiently retaining logic states, minimizing ground bounce, and achieving resilience to process variation. The following briefly reviews representative works in these two areas.

Hu et al. [58] propose power gating as a technique to reduce functional unit leakage power when applications underutilize their functional units. Specifically, they power gate the floating-point and fixed-point units according to three different predictors which are respectively ideal, time-based, and branch-misprediction-guided. The best technique (branch-misprediction-guided) is able to put functional units to sleep for up to 40% of total cycles with only 2% performance loss. The authors of [58] also develop equations to estimate the break-even points for power gating an out-of-order superscalar processor. However, although they build a power consumption model with precise analysis of virtual supply voltage during power gating, they do not consider the wake-up energy required to restore circuit nodes.

Lungu et al. [83] show that in many cases, the predictor of [58] can lead to increased energy consumption. A monitor that controls the use of power gating is introduced to bound the performance and energy penalty for misbehaved applications. Madan et al. [14] extend the idea of Lungu et al. to the core level, and propose a "guard mechanism" that reduces harmful use of power gating.

Power-gating technology is also readily visible in leading commercial products. The recent Nehalem architecture employs power gating at the core level to reduce leakage power on idle cores, but 100 *ms* is required to wake up a core [73, 76]. AMD [103] has improved this power-gating technique by optimizing the wake-up sequence to skip built-in self tests (BIST) and restoration of cache state; this results in wake-up times as short as 75  $\mu$ s. In today's systems, the OS typically power gates the cores in the idle loop, missing out on power gating long memory accesses.

In the realm of circuit innovation, the pioneering work of Horiguchi et al. [56] has been followed by many works on fundamental circuit design issues related to power gating, including switch-cell sizing, data-retention methods, physical-implementation methodologies, and mode-transition noise analysis and reduction. The recent survey of Shin et al. [106] gives an excellent summary of the history and highlights of power-gating techniques.

We propose a *multi-mode power-gating* technique that allows multiple wake-up modes to minimize wake-up latency. Configurable power gating has been used in the past to mitigate process variation, reduce ground bounce noise, and minimize wake-up time. Agarwal et al. [11] and Singh et al. [107] examine multiple sleep modes that feature different wake-up overheads and leakage power savings. Use of multiple sleep

modes achieves an extra 17% reduction in leakage power compared to a single powergating mode. Also, one of the sleep modes can reduce leakage power by 19% while preserving circuit state. However, these energy savings are based on static traces of bus activity and do not address the runtime problem of predicting *when* to power gate. In addition, the reported results are likely optimistic since wake-up noise and the overhead of implementing low-voltage sleep control signal distribution are not considered.

To minimize ground bounce during mode transition, Kim et al. [69] control turn-on voltage ( $V_{GS}$ ), which makes sleep transistors turn on in a non-uniform stepwise manner. Kim et al. [70] propose a tri-mode power-gating structure in which a PMOS switch is combined in parallel with traditional NMOS power-gating switches. The additional PMOS transistor supports intermediate power-saving state-retaining modes at low-supply voltage, and reduces ground bounce noise during transitions between normal and power-gated modes. Chowdhury et al. [32] propose a similar tri-mode (i.e., RUN, HOLD, CUT-OFF) power-gating technique using PMOS switches in parallel with NMOS footer switches, combined with additional NMOS switches in parallel with PMOS header switches. Kim et al. [68] propose a programmable-width power-gating switch that adjusts the widths of power-gating switches to compensate for core-to-core process variation occurring in multicore systems. Finally, Zhang et al. [122] propose a multi-mode powergating technique using three NMOS switches with different sizes and threshold voltages. Using various combinations of the three switches, they can provide multiple power-gating modes with different leakage savings. They also note that their method is tolerant to process variation.

The most similar work to this chapter, Memory Access Aware Power Gating for MPSoCs [81], examines the potential to power gate an in-order core while monitoring a single memory bus and estimating memory latencies. A controller that sits at the memory bus sends explicit commands to each core to power gate and to wake up from

a power-gated state. The controller estimates memory latencies by tracking whether each memory request is a row buffer hit or miss. However, this work does not consider out-of-order execution, and is limited in scalability to a system with a single memory bus, which precludes understanding of its application to data-center servers. In addition, it does not consider the importance of core location and state information for determining safe wake-up modes, the possibility of using staggered wake-up to reduce the latency of core wake-up from a power-gated state, or the scalability of their designs. By contrast, this chapter addresses these issues, is applicable to out-of-order cores, formally analyzes the energy savings for in-order cores, considers the importance of core location and wake-up stagger, and considers the scalability of the design to many-core processors.

# 2.2 **Power Gating and Power Distribution Network**

This section provides a low-level analysis of our power-gating methodology and its impact on the power distribution network. Section 2.2.1 gives the details of the programmable power-gating switch, Section 2.2.2 describes our models for capacitance of a core and voltage noise in the power distribution network, Section 2.2.3 explains how we model core wake-up mode constraints and the benefit of a *staggered* wake-up.

#### 2.2.1 Programmable Power Gating Switch (PPGS) Design

As noted above, power gating cuts off leakage current paths between supply  $(Vdd\_core)$  and ground (Vss) by using switch transistors (often, high- $V_{th}$  or long-channel devices). A typical power-gating methodology with *header* switches is illustrated in Figure 2.1. When the *pg\_enable* signal goes low, the header switches turn off and leakage current is reduced. While in the power-gated state, all logic gates connected to the virtual supply  $(Vdd\_int)$  lose their logical states. Setting the *pg\_enable* signal to high resumes circuit operation after a delay that corresponds to charging circuit capacitive

Figure 2.1. Operation of the power-gating technique.

Figure 2.2. Wake-up current profiles with different wake-up controls.

loads, resetting memory elements, and restoring state from retention flip-flops connected to *Vdd\_core*.

The delay to charge circuit capacitive elements is a function of total design charge (Q) and peak charging current  $(I_{limit})$ . If all header switches turn on simultaneously, a large "inrush" current charges internal nodes in minimal time. To satisfy inrush current upper limits (too-large IR drop can affect functionality of neighboring active blocks), header switches are partially turned on in sequence, which increases charging time to at least  $T_{charge} = Q/I_{limit}$ . Minimal charging time is achieved with a rectangular current

profile, but such a profile requires very fine-grained control of header switches. To avoid this design complexity, we use a two-stage wake-up control [51] where the first stage (*enable\_few* signal) turns on header switches to allow  $I_{limit}$  charge current. The remaining header switches are turned on in the second stage (*enable\_rest* signal) once the circuit nodes are nearly charged, resulting in a triangular charging current profile (see Figure 2.2b). This increases the wake-up latency to at least twice the minimum square wake-up profile, but simplifies signal connections.

To maximize opportunities for power gating subject to wake-up inrush current and supply noise constraints, we seek to enable multiple *wake-up modes*, with a range of wake-up latencies, per core. Figure 2.3 shows our *programmable power-gating switch* (PPGS) for a core, along with the wake-up current profile for different wake-up modes. We configure the number of first-stage wake-up switches to control the inrush current as shown in Figure 2.3b. With the dynamic configuration of the PPGS, we can minimize the wake-up time according to the core configurations — e.g., the number or location of active cores relative to the waking-up cores. To power gate a core, all mode selection signals m[0-9] are set to one, which turns off all switches at the same time.<sup>4</sup>

Core wake-up time and inrush current are determined by the mode selection. For example, Mode 1, which has the longest wake-up time and smallest inrush current, is set by m[0] = 0 and m[1-9] = 1. Thus, m[0] is enabled by signal *enable\_few* and m[1-9] is enabled by signal *enable\_rest*. Mode 2 is set by m[0-1] = 0 and m[2-9] = 1; inrush current increases with the number of first-stage switches, while wake-up time decreases, as shown in Figure 2.3b. The other modes can be set similarly.

<sup>&</sup>lt;sup>4</sup>Due to the large resistance of off-state switches, inrush current from simultaneous turn off is negligibly small compared to wake-up inrush current.

Figure 2.3. PPGS design and inrush current profiles vs. wake-up modes

## 2.2.2 PDN Model for Power Estimation and Circuit Analysis

Table 2.1 shows estimated design parameters, power-gating results and PDNmodel parameters for 32 *nm* and 22 *nm* in-order cores with high performance (HP) and low-operating power (LOP) devices. To study wake-up latency and inrush current, we estimate the total charge for core logic and interconnect capacitance as  $Q_{core} = (C_{logic} + C_{int}) V dd_core$ , where  $Q_{core}$ ,  $C_{logic}$ , and  $C_{int}$  represent total charge, device capacitance, and interconnect capacitance for a single core without caches. We estimate a core's total transistor count using [78] to determine the core's area and average transistor density. Based on this transistor count and parameters from the 2009-2010 *International Technology Roadmap for Semiconductors* (ITRS) [6], we estimate  $C_{logic}$  and  $C_{int}$ . The inrush current limit ( $I_{limit}$ ) and on-current ( $I_{active}$ ) are estimated from McPAT data for peak power and average power, respectively.

From the calculated charge ( $Q_{core}$ ), the minimum wake-up latency with a rectangular form current profile is  $T_{min-charge} = Q_{core}/I_{limit}$ , and the minimum two-stage wake-up latency (Figure 2.2b) is  $2 \times T_{min-charge}$ .

We estimate leakage power consumption during power gating of the core logic

| Estimated Data           | 32 nm   | 32 nm   | 22 nm    | 22 nm    |  |  |  |  |  |

|--------------------------|---------|---------|----------|----------|--|--|--|--|--|

| Estimated Data           | HP      | LOP     | HP       | LOP      |  |  |  |  |  |

| Design Data              |         |         |          |          |  |  |  |  |  |

| Vdd_core (V)             | 1.00    | 0.77    | 1.00     | 0.77     |  |  |  |  |  |

| core area $(mm^2)$       | 4.593   | 4.608   | 2.701    | 3.657    |  |  |  |  |  |

| logic area $(mm^2)$      | 2.891   | 2.863   | 1.635    | 1.636    |  |  |  |  |  |

| $C_{core}(F)$            | 7.53E-9 | 7.48E-9 | 4.58E-9  | 4.58E-9  |  |  |  |  |  |

| total charge $(C)$       | 7.53E-9 | 5.76E-9 | 4.26E-9  | 3.30E-9  |  |  |  |  |  |

| core leakage (W)         | 0.355   | 0.042   | 0.147    | 0.019    |  |  |  |  |  |

| $I_{active}(A)$          | 0.725   | 0.374   | 0.371    | 0.233    |  |  |  |  |  |

| $I_{limit}(A)$           | 1.298   | 0.674   | 0.701    | 0.632    |  |  |  |  |  |

| Power Gating and Wake-up |         |         |          |          |  |  |  |  |  |

| $T_{min-charge}$ (ns)    | 5.08    | 7.36    | 6.40     | 6.55     |  |  |  |  |  |

| wake-up energy $(pJ)$    | 3.30E+3 | 1.91E+3 | 2.24E+3  | 1.60E+3  |  |  |  |  |  |

| # head switches          | 9,664   | 6,222   | 5,516    | 5,127    |  |  |  |  |  |

| leakage in PG state (W)  | 8.03E-3 | 7.14E-4 | 3.37E-3  | 3.59E-4  |  |  |  |  |  |