# UCLA UCLA Electronic Theses and Dissertations

## Title

Integration of Voltage-Controlled Spintronic Devices in CMOS Circuits

**Permalink** https://escholarship.org/uc/item/0cx596gk

Author Lee, Hochul

Publication Date 2017

Peer reviewed|Thesis/dissertation

### UNIVERSITY OF CALIFORNIA

Los Angeles

Integration of Voltage-Controlled Spintronic Devices in CMOS Circuits

A dissertation submitted in partial satisfaction of the

requirements for the degree Doctor of Philosophy

in Electrical Engineering

by

Hochul Lee

2017

## © Copyright by

Hochul Lee

2017

#### ABSTRACT OF THE DISSERTATION

#### Integration of Voltage-Controlled Spintronic Devices in CMOS Circuits

by

Hochul Lee

Doctor of Philosophy in Electrical Engineering University of California, Los Angeles, 2017 Professor Kang Lung Wang, Chair

Spintronics is an emerging field that studies the properties of electron spin and discovers the methods to detect and manipulate its associated magnetic moment in a solid-state device, in addition to its fundamental electronic charge. Utilization of spintronic devices has been considered as a possible alternative for beyond CMOS technology. One of the most promising spintronic devices is a magnetic tunnel junction (MTJ) that has attracted the attention of academia and industry owing to its remarkable characteristics such as non-volatility, virtually unlimited endurance, and CMOS compatibility. Also, due to the discovery of the spin-transfer torque (STT) and spin Hall effect (SHE) as new switching mechanisms, a nanosecond switching speed has been demonstrated in MTJ devices. However, these current-driven switching methods inherently cause a significant ohmic loss since they require relatively a large amount current to generate sufficient spin torque. Recently, a voltage-controlled effect has been utilized to mitigate the energy issue by drastically reducing ohmic dissipation during

switching in a noble memory architecture called magnetoelectric RAM (MeRAM). In addition to achieving high-energy efficiency, voltage-induced switching leads to further improvement in terms of density and switching speed, opening the door to new possibilities of next generation low-power and high-speed system architectures.

In this dissertation, we explore the characteristics of voltage-controlled magnetic anisotropy (VCMA) effect driven precessional switching based on an MTJ macrospin compact model including the VCMA effect in its built-in Landau-Lifshitz-Gilbert (LLG) equation. In particular, this compact model allows predicting required bias conditions for switching, monitoring the three-dimensional magnetization dynamics, and extracting the write error rate (WER). Furthermore, we demonstrate a wide variety of spintronics-CMOS circuits utilizing unique features of voltage-controlled MTJ for many applications. Overall, the performances of the proposed circuits are improved by an order of magnitude, especially, in terms of energy and area. Also, we develop several practical design techniques to improve the reliability of the read and write operations in MeRAM. Lastly, a synchronous 4Kbit MeRAM macro is designed based on IBM 130 nm technology. After discussing the MeRAM macro specification and constraints, each circuit component of the macro and its verification results are presented.

The dissertation of Hochul Lee is approved.

Yong Chen

Puneet Gupta

Dejan Markovic

Kang Lung Wang, Committee Chair

University of California, Los Angeles

2017

To my family

This dissertation is specially dedicated to my beloved wife Julie Yom

| CHAPTER 1: INTRODUCTION                          | 1  |

|--------------------------------------------------|----|

| 1.1 Overview of Spintronics                      | 4  |

| 1.2 Magnetic Tunnel Junction (MTJ)               | 7  |

| 1.2.1 MTJ Device Structure                       | 7  |

| 1.2.1.1 In-plane MTJ                             | 8  |

| 1.2.1.2 Perpendicular MTJ                        | 9  |

| 1.2.2 Tunneling Magnetoresistance (TMR) Ratio    | 11 |

| 1.3 Magnetoresistive Random-Access Memory (MRAM) | 15 |

| 1.3.1 Oersted-field-switched MRAM                | 15 |

| 1.3.2 Spin-Transfer Torque MRAM (STT-MRAM)       | 16 |

| 1.3.3 Magnetoelectric RAM (MeRAM)                | 19 |

| 1.3.4 Spin-Orbit Torque MRAM (SOT-MRAM)          | 20 |

| 1.3.5 Performance Comparison                     | 22 |

| 1.3.5.1 Device Level                             | 22 |

| 1.3.5.2 Array Level                              | 26 |

| CHAPTER 2: MACROSPIN COMPACT MODELING OF MTJ     | 33 |

| 2.1 Motivation                                   | 33 |

| 2.2 Physical and Dynamic Model of MTJ            | 34 |

### **TABLE OF CONTENTS**

| 2.2.1 Landau–Lifshitz–Gilbert (LLG) equation                              | 34 |

|---------------------------------------------------------------------------|----|

| 2.2.2 Effective Magnetic Field                                            | 34 |

| 2.2.2.1 Perpendicular Magnetic Anisotropy (PMA)                           | 35 |

| 2.2.2.2 Voltage-Controlled Magnetic Anisotropy (VCMA)                     | 35 |

| 2.2.2.3 Shape Anisotropy and Demagnetization                              | 36 |

| 2.2.2.4 External Field                                                    | 36 |

| 2.2.3 Thermal Noise                                                       | 37 |

| 2.2.4 Modeling of Spin-Transfer Torque                                    | 38 |

| 2.2.5 Modeling of Tunnel Magnetoresistance (TMR) Ratio                    | 39 |

| 2.3 Two Terminal MTJ Switching Mechanisms and Compact Model Simulations   | 40 |

| 2.3.1 Voltage Dependence of Effective Magnetic Field                      | 40 |

| 2.3.2 Timing of Voltage-Driven Precessional Switching                     | 41 |

| 2.3.3 Thermal Noise Effect                                                | 43 |

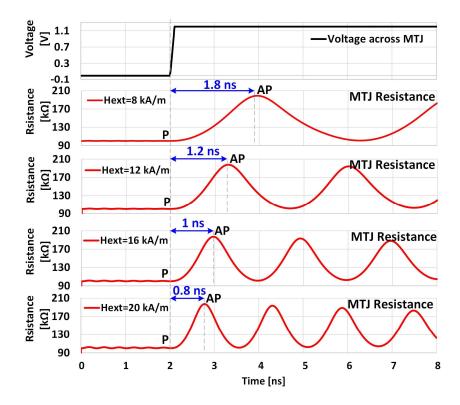

| 2.3.4 External Magnetic Field Dependence of Switching Speed               | 44 |

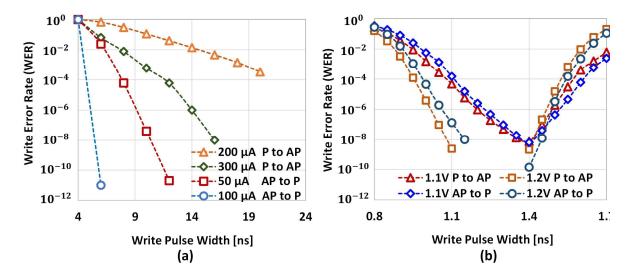

| 2.3.5 Write Error Rate (WER)                                              | 45 |

| 2.3.6 Thermal Stability and Retention Time                                | 48 |

| 2.4 Three Terminal MTJ Switching Mechanisms and Compact Model Simulations | 49 |

| 2.4.1 Modeling of Spin Hall Effect                                        | 49 |

| 2.4.2 SHE-driven Switching and VCMA Assisted SHE-driven Switching         | 52 |

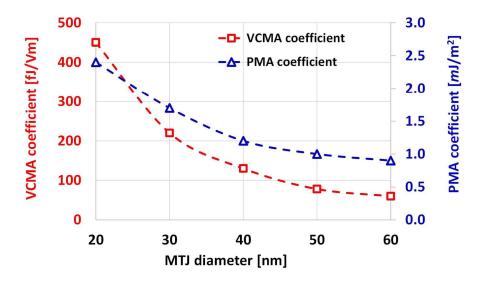

| 2.5 Scalability of Voltage-Controlled MTJ                                    | 54 |

|------------------------------------------------------------------------------|----|

| CHAPTER 3: VOLTAGE-CONTROLLED SPINTRONICS-CMOS CIRCUITS                      | 56 |

| 3.1 Introduction                                                             | 56 |

| 3.2 Voltage-controlled MTJ based Ternary Content-Addressable Memory          | 56 |

| 3.2.1 Overview of TCAM                                                       | 56 |

| 3.2.2 Design of MTJ based TCAM Cell                                          | 57 |

| 3.2.3 Configuration and Search Operations                                    | 59 |

| 3.2.4 Performance Evaluation and Comparison                                  | 61 |

| 3.3 A Spintronic Voltage-Controlled Stochastic Oscillator                    | 62 |

| 3.3.1 Uniform Sampling versus Non-uniform Sampling                           | 62 |

| 3.3.2 Advantages of using MTJ for the Non-uniform Clock Generator            | 64 |

| 3.3.3 Design and Performance Evaluation                                      | 66 |

| 3.4 Voltage-controlled MTJ based True Random Number Generator                | 70 |

| 3.4.1 Overview of Random Number Generator                                    | 70 |

| 3.4.2 Advantages of using MTJ for the True Random Number Generator           | 71 |

| 3.4.3 Design and Performance Evaluation                                      | 73 |

| 3.5 Spintronic Programmable Logic (SPL) using Voltage-gated Spin Hall Effect | 77 |

| 3.5.1 Overview of Programmable Logic                                         | 77 |

| 3.5.2 Advantages of using three terminal MTJ for the SPL                     | 78 |

| 3.5.3 Configuration and Logic Operations of the SPL                          | 78  |

|------------------------------------------------------------------------------|-----|

| 3.5.4 Performance Evaluation: Sensing Margin, Power Consumption, and Area    | 79  |

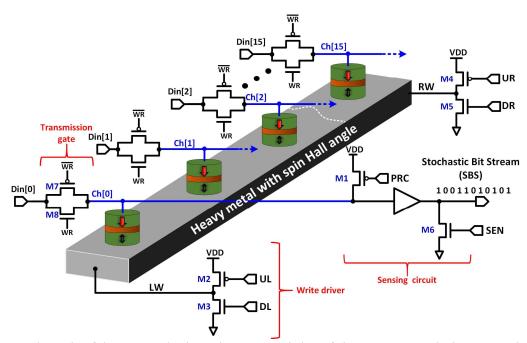

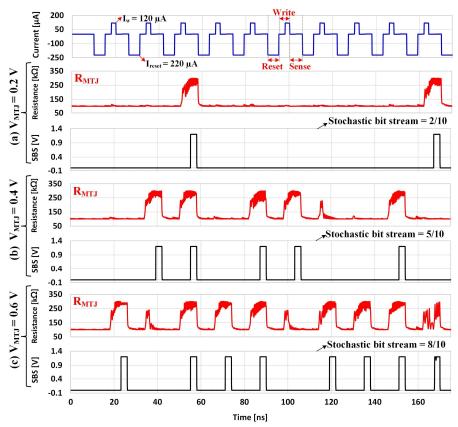

| 3.6 Analog to Stochastic Bit Stream Converter                                | 83  |

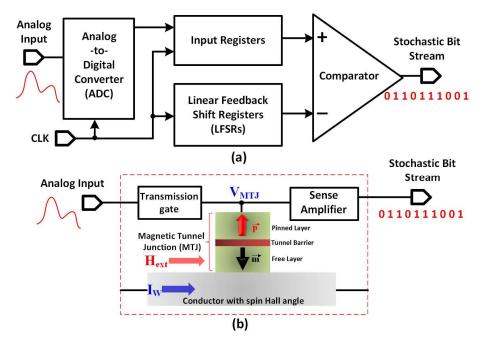

| 3.6.1 Overview of Analog to Stochastic Bit Stream Converter                  | 83  |

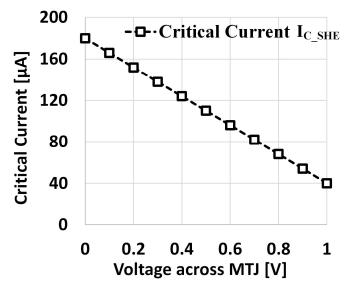

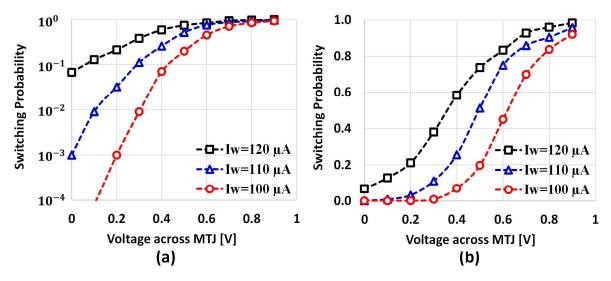

| 3.6.2 Switching Probability of Voltage-Assisted spin Hall effect             | 85  |

| 3.6.3 Design and Performance Evaluation                                      | 87  |

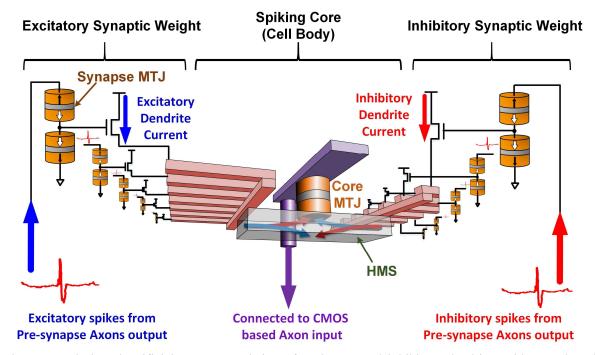

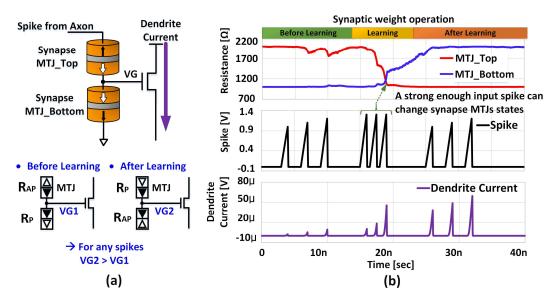

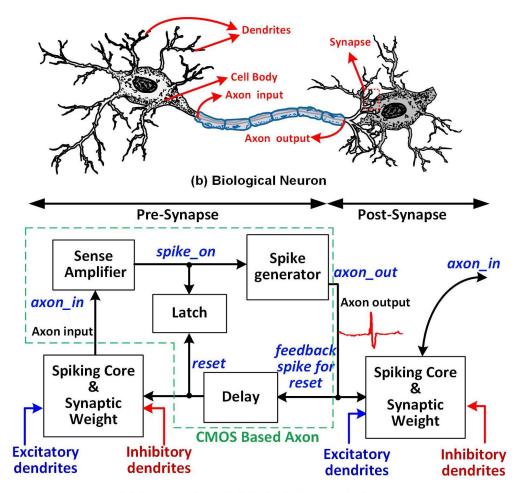

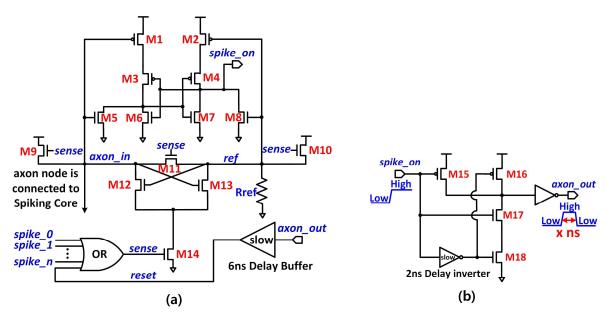

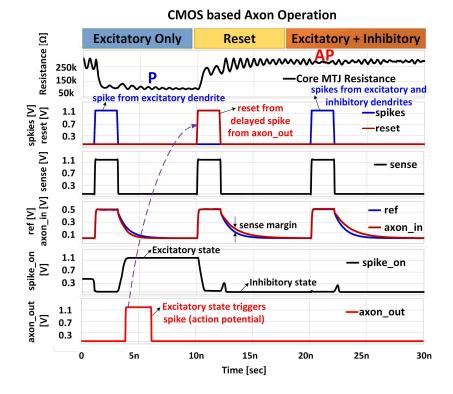

| 3.7 Spin and CMOS based Neural Network                                       | 90  |

| 3.7.1 Motivation                                                             | 90  |

| 3.7.2 Design and Performance Evaluation                                      | 91  |

| CHAPTER 4: DESIGN TECHNIQUES ENHANCING MERAM PERFORMANCE                     | 96  |

| 4.1 Motivation                                                               | 96  |

| 4.2 Source Line Sensing (SLS) Scheme to Improve Read Performance             | 96  |

| 4.2.1 Use of VCMA with reverse voltage                                       | 96  |

| 4.2.2 Circuit Architecture of the SLS                                        | 98  |

| 4.2.3 Evaluation                                                             | 102 |

| 4.3 Word Line Pulse (WLP) based Write Operation for Reduced Write Error Rate | 104 |

| 4.3.1 Pulse Shape Dependence of Magnetization Behavior                       | 104 |

| 4.3.2 Timing of the WLP                                                      | 105 |

| 4.3.3 Performance Evaluation: Write Error Rate and Cell Area Efficiency      | 109 |

| 4.4 Write Pulse Termination (WPT) Circuit Technique                             | 112 |

|---------------------------------------------------------------------------------|-----|

| 4.4.1 Motivation                                                                | 112 |

| 4.4.2 Schematic of the WPT                                                      | 113 |

| 4.4.3 Simulation and Analysis                                                   | 116 |

| 4.5 Circuit for Controlling Non-deterministic Switching                         | 119 |

| 4.5.1 Motivation                                                                | 119 |

| 4.5.2 Schematic and Simulation of the pre-read and write sense amplifier (PWSA) | 112 |

| 4.5.3 Performance Evaluation                                                    | 124 |

| CHAPTER 5: 4KBIT MeRAM MACRO DESIGN                                             | 127 |

| 5.1 Specification                                                               | 127 |

| 5.2 Cell and Array Design                                                       | 129 |

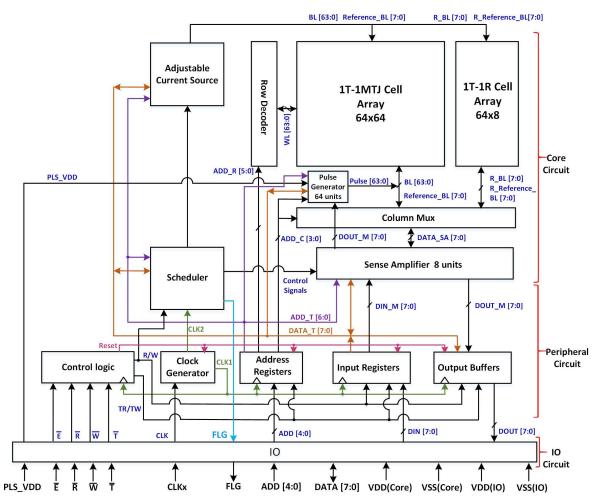

| 5.3 Core Circuit Design                                                         | 131 |

| 5.4 Peripheral Circuit Design                                                   | 135 |

| 5.5 Full-chip Analog and Digital Mixed Signal Verification                      | 140 |

| 5.6 Full-chip Layout                                                            | 144 |

| 5.7 Test and Evaluation                                                         | 145 |

| CHAPTER 6: CONCLUSION                                                           | 150 |

| REFERENCE                                                                       | 153 |

## LIST OF FIGURES

| Fig. 1.1 Trends of power consumption and dark silicon for SOC                                           | 2           |

|---------------------------------------------------------------------------------------------------------|-------------|

| Fig. 1.2 State of the art computing system architecture                                                 | 3           |

| Fig. 1.3 Emerging system architecture with the embedded non-volatile memory                             | 4           |

| Fig. 1.4 In-plane MTJ utilizing the shape anisotropy                                                    | 8           |

| Fig. 1.5 Perpendicular MTJ utilizing the interfacial perpendicular anisotropy                           | 10          |

| Fig. 1.6 Spin-split density of states (DOS) for non-magnetic and magnetic metals                        | 12          |

| Fig. 1.7 Two channel Jullière model for the tunneling between two ferromagnetic layers                  | 13          |

| Fig. 1.8 Majority and minority DOS for the Fe Fermi energy Block states                                 | 14          |

| Fig. 1.9 Oersted-field-switched MRAM cell structure                                                     | 16          |

| Fig. 1.10 1T-1MTJ cell architecture in STT-MRAM                                                         | 17          |

| Fig. 1.11 Amplitude of write current as a function of write pulse width for STT-driven switching        | 18          |

| Fig. 1.12 1T-1MTJ cell architecture in MeRAM                                                            | 19          |

| Fig. 1.13 1T-1MTJ cell architecture in SOT-MRAM                                                         | 21          |

| Fig. 1.14 Memory Hierarchy in a conventional computer architecture                                      | 23          |

| Fig. 1.15 Performance comparison of different memory technologies                                       | 25          |

| Fig. 1.16 Memory bank architecture and Schematic of a single column connection of MeRAM                 | 27          |

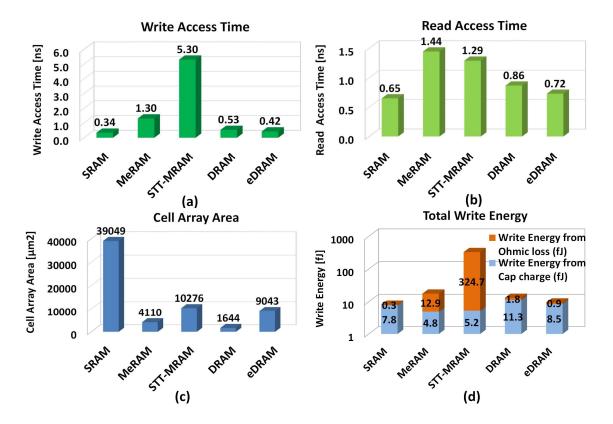

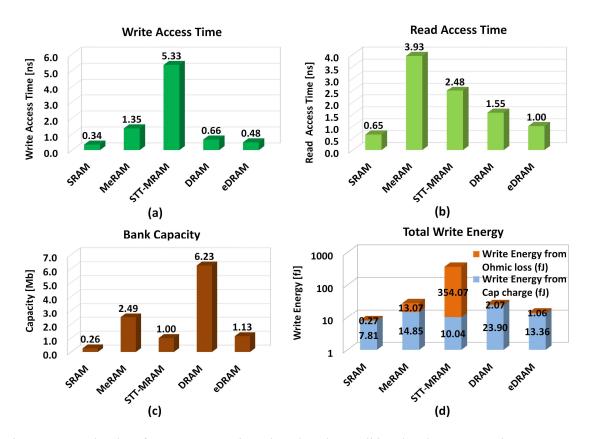

| Fig. 1.17 Array level performance comparisons based on the same capacity 256 Kbit                       | 30          |

| Fig. 1.18 Array level performance comparisons based on the same array area 200 $\mu m~\times 200~\mu m$ | 1 <b>31</b> |

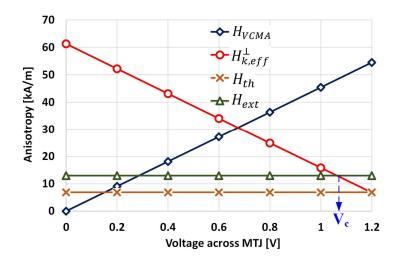

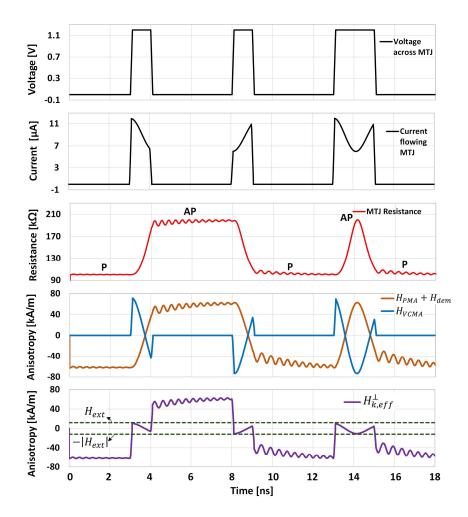

| Fig. 2.1 Voltage dependence of the components of the effective magnetic field                           | 41          |

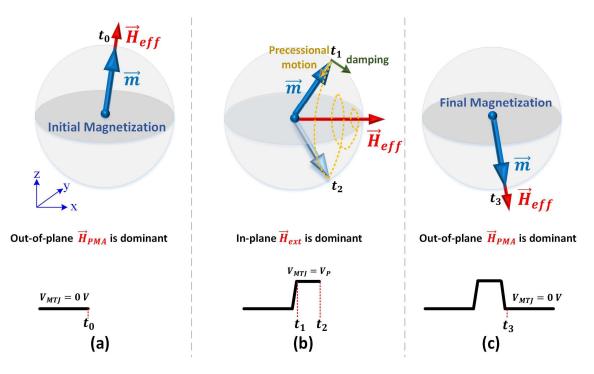

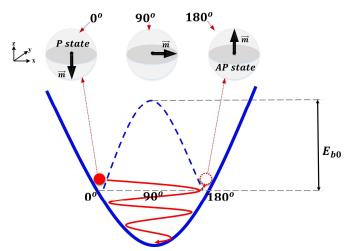

| Fig. 2.2 Illustration of the voltage-induced precessional switching mechanism                           | 42          |

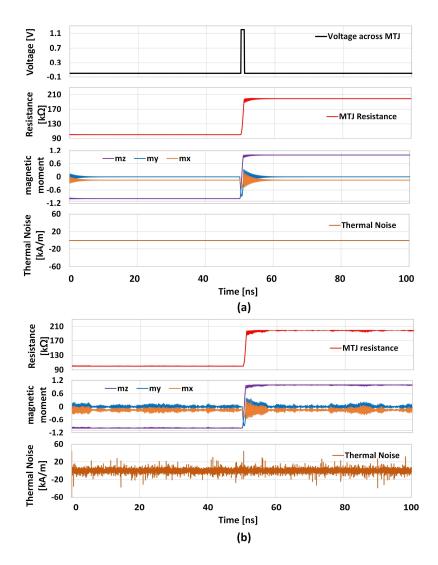

| Fig. 2.3 Transient simulation of the non-deterministic voltage-driven precessional switching            | 43          |

| Fig. 2.4 Transient simulation in the absence/presence of the thermal noise                              | 44          |

| Fig. 2.5 Transient simulations for the in-plane $H_{ext}$ dependence of the switching speed    | 45 |

|------------------------------------------------------------------------------------------------|----|

| Fig. 2.6 WER of STT-induced switching and voltage-controlled precessional switching            | 46 |

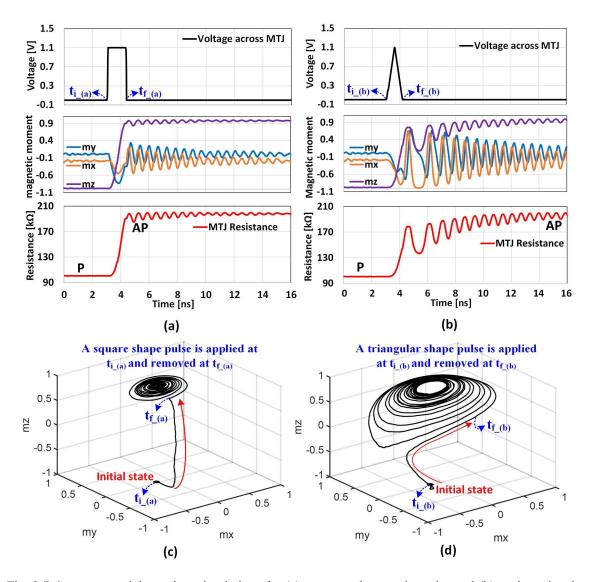

| Fig. 2.7 Compact model transient simulations for a square/triangular shape write pulse         | 47 |

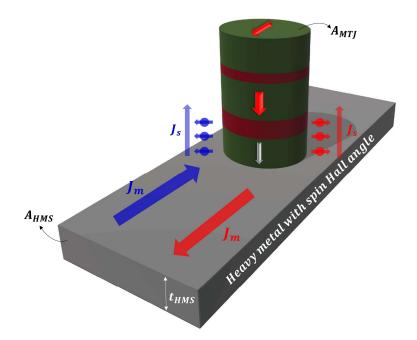

| Fig. 2.8 WER simulation as a function of slew rate and amplitude for precessional switching    | 48 |

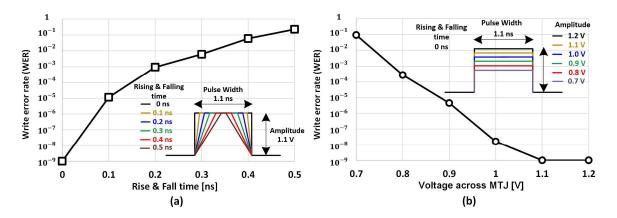

| Fig. 2.9 Voltage dependence of energy barrier and thermal stability via the VCMA effect        | 49 |

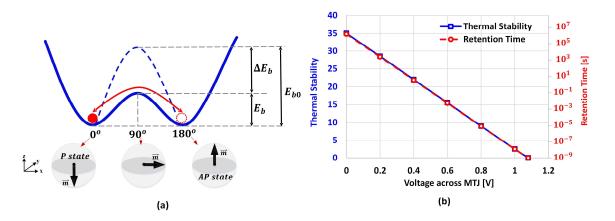

| Fig. 2.10 Schematic of the 3-terminal MTJ on the heavy metal layer with spin-orbit interaction | 50 |

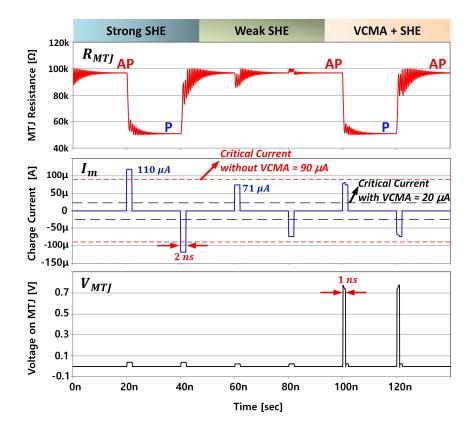

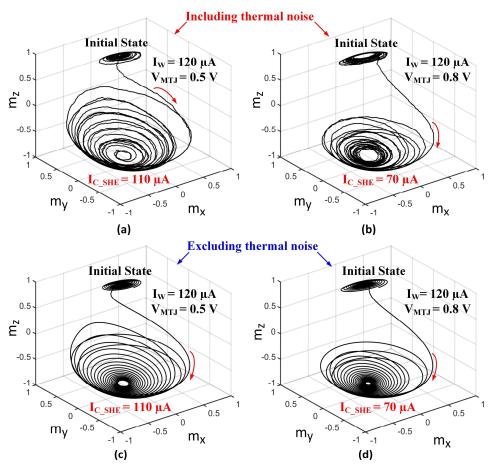

| Fig. 2.11 Simulation of pure SHE switching and gate-voltage-modulated SHE switching            | 52 |

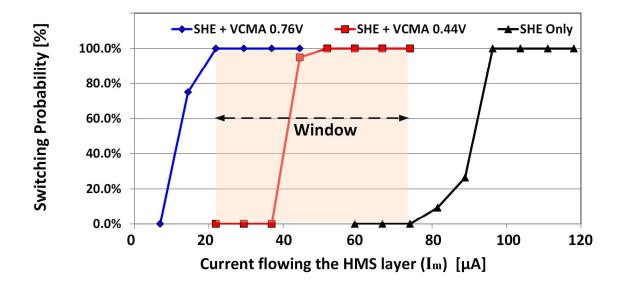

| Fig. 2.12 Switching probability as a function of current amplitude and applied voltage         | 53 |

| Fig. 2.13 Required VCMA coefficient and interfacial anisotropy for device scaling              | 54 |

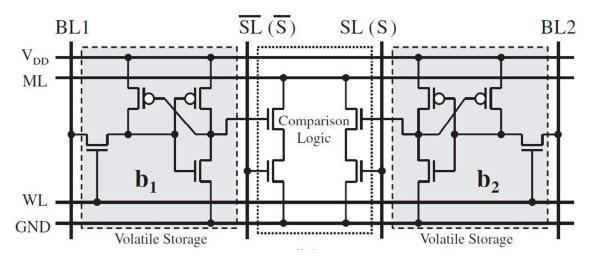

| Fig. 3.1 Conventional SRAM based TCAM cell architecture                                        | 57 |

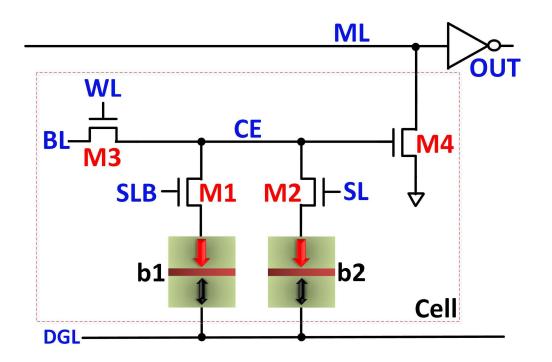

| Fig. 3.2 Voltage-controlled MTJ based MeTCAM cell architecture                                 | 58 |

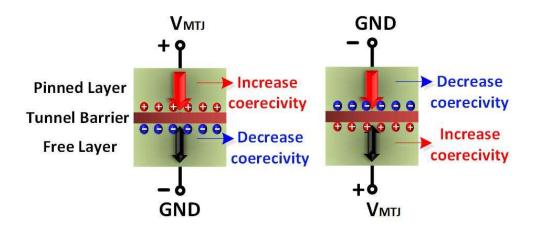

| Fig. 3.3 Voltage dependence of the coercivity                                                  | 59 |

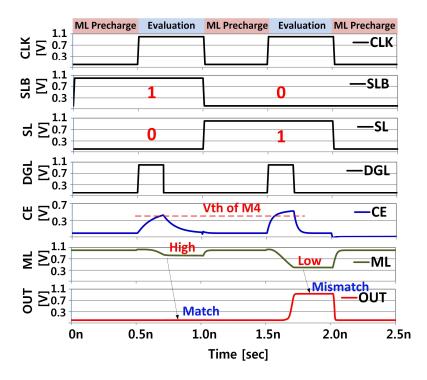

| Fig. 3.4 Search operations of the MeTCAM                                                       | 60 |

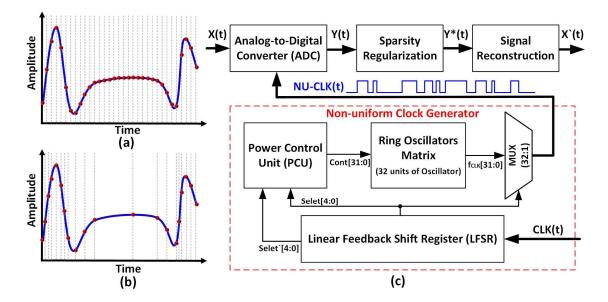

| Fig. 3.5 Uniform/Non-uniform sampling and Non-uniform clock based system                       | 63 |

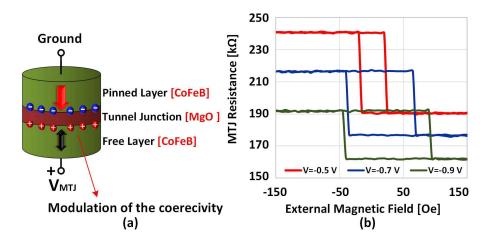

| Fig. 3.6 Measured coercivity as a function of the voltage across the device                    | 65 |

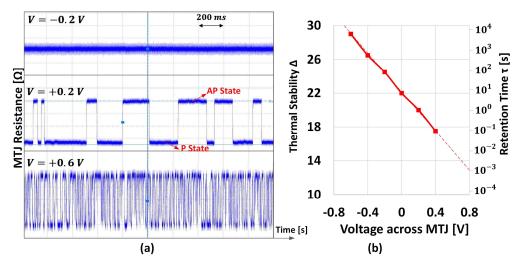

| Fig. 3.7 Measured MTJ's resistance fluctuation and thermal stability                           | 66 |

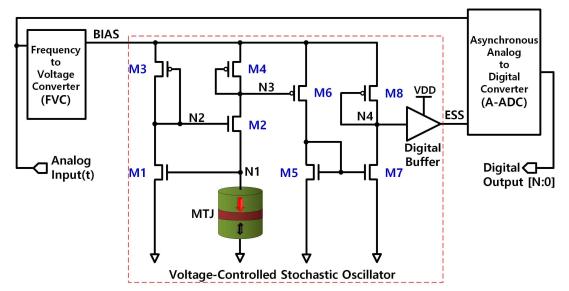

| Fig. 3.8 MTJ based voltage-controlled stochastic oscillator (VCSO)                             | 67 |

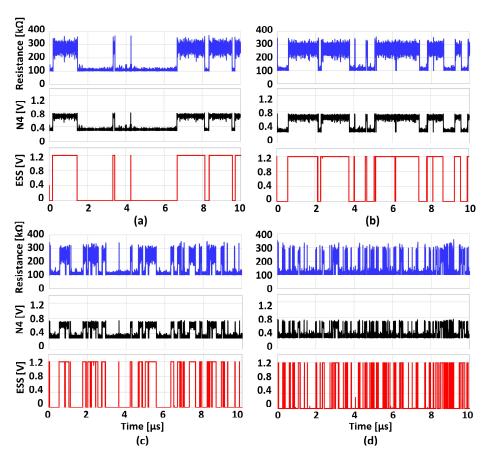

| Fig. 3.9 Transient circuit simulation of the VCSO with the MTJ compact model                   | 68 |

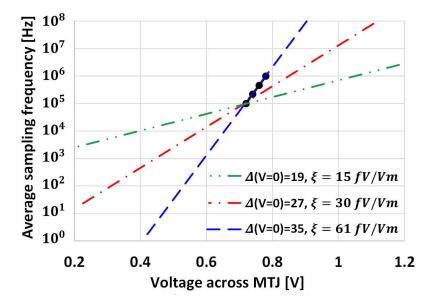

| Fig. 3.10 Average sampling frequency of the VCSO with different thermal stabilities            | 69 |

| Fig. 3.11 Description of VCMA-induced switching mechanisms in a perpendicular MTJ              | 71 |

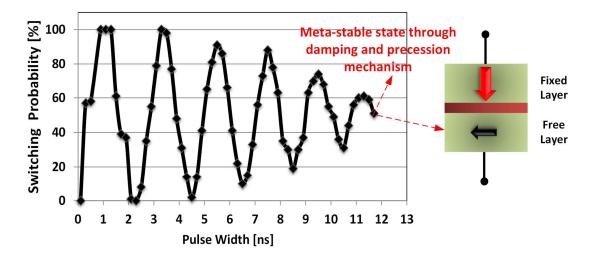

| Fig. 3.12 Simulated VCMA-induced switching probability as a function of write pulse width      | 72 |

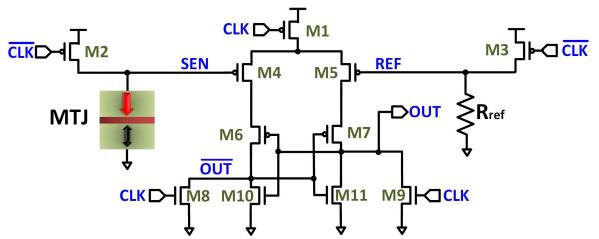

| Fig. 3.13 Schematic of the proposed MTJ based true random number generator (MRNG)              | 73 |

| Fig. 3.14 Simulation result of the MRNG for a random bit operation                             | 74 |

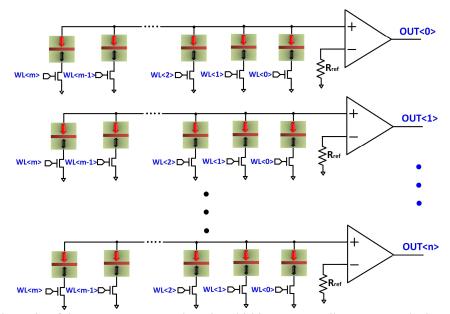

| Fig. 3.15 Schematic of the m×n MTJs array based multi-bit MRNG                                     | 75  |

|----------------------------------------------------------------------------------------------------|-----|

|                                                                                                    |     |

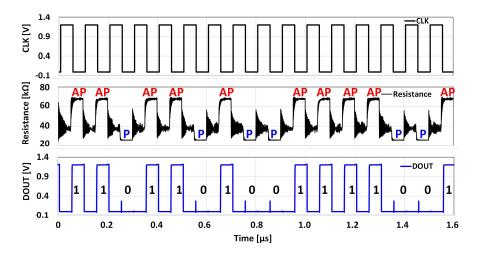

| Fig. 3.16 Simulation results of consecutive random bit generations by using the MRNG               | 75  |

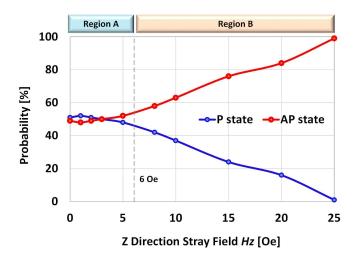

| Fig. 3.17 Switching probability of MTJ in the presence of z-direction external field               | 76  |

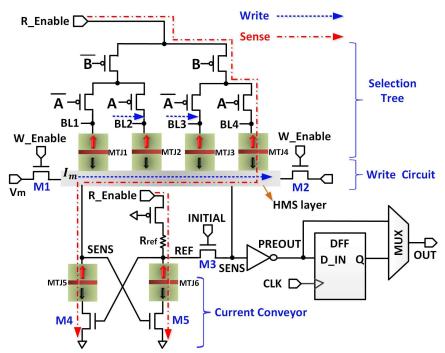

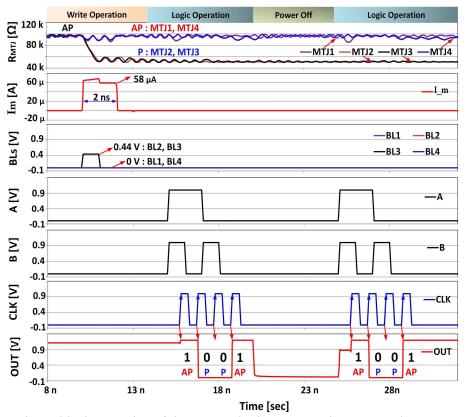

| Fig. 3.18 Schematic of the proposed 2-input spintronic programmable logic (SPL)                    | 79  |

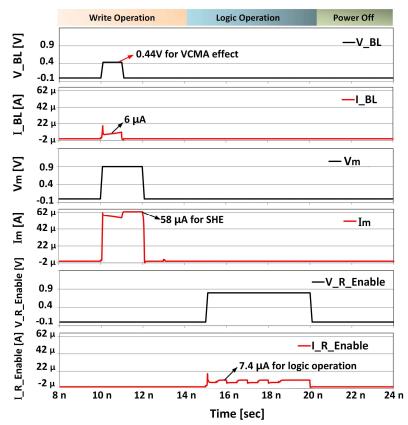

| Fig. 3.19 Write and logic operation of the proposed 2-input SPL                                    | 80  |

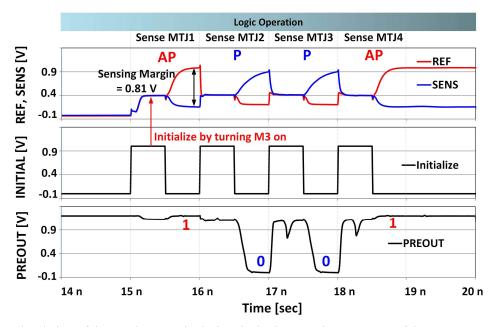

| Fig. 3.20 Simulation of the sensing margin during the logic operation                              | 81  |

| Fig. 3.21 Power consumption of the SPL at write, logic, and stand-by modes                         | 82  |

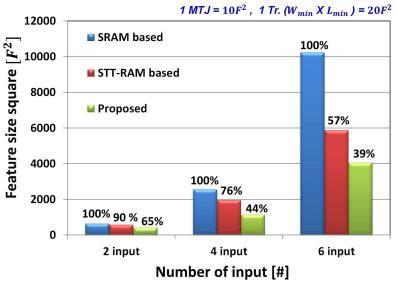

| Fig. 3.22 Area comparison of different types of LUT                                                | 82  |

| Fig. 3.23 CMOS based and MTJ based analog to stochastic bit stream converter (ASC)                 | 84  |

| Fig. 3.24 Critical current $I_{C_{SHE}}$ of the SHE effect as a function of voltage across the MTJ | 85  |

| Fig. 3.25 Switching probability as a function of voltage across the MTJ                            | 86  |

| Fig. 3.26 Trajectory of the free layer's magnetization during the voltage assisted SHE switching   | 87  |

| Fig. 3.27 Schematic of the proposed spintronic ASC                                                 | 88  |

| Fig. 3.28 Transient circuit simulation of the spintronic ASC                                       | 89  |

| Fig. 3.29 Spin-based artificial neuron                                                             | 91  |

| Fig. 3.30 Schematic of CMOS and MTJ based artificial dendrite and synapse                          | 92  |

| Fig. 3.31 Structure of the spin-based neural network                                               | 93  |

| Fig. 3.32 Circuit components of a CMOS based Axon                                                  | 94  |

| Fig. 3.33 Simulation result of CMOS based Axon operation                                           | 95  |

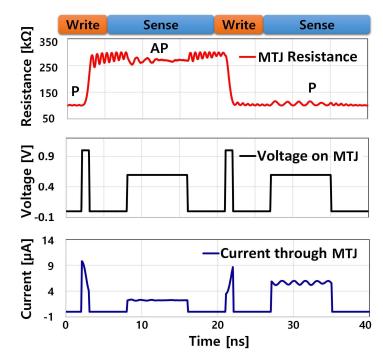

| Fig. 4.1 One transistor and one MTJ of MeRAM cell structure                                        | 97  |

| Fig. 4.2 Conventional write and read operations of MeRAM                                           | 98  |

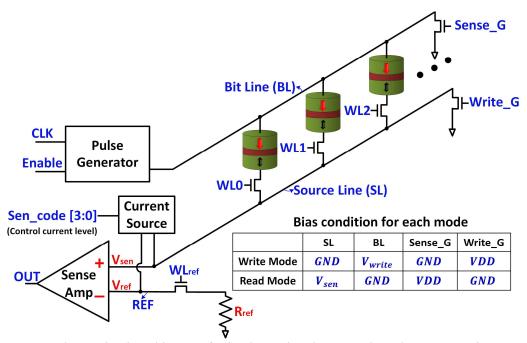

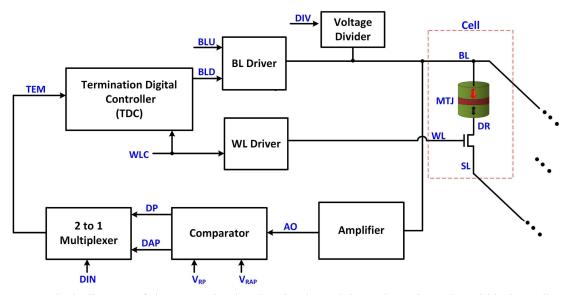

| Fig. 4.3 Proposed core circuit architecture for implementing the SLS                               | 100 |

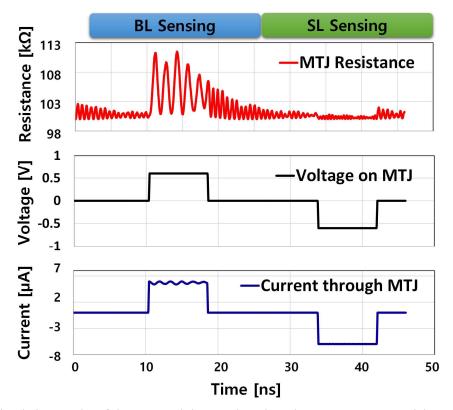

| Fig. 4.4 Simulation results of the BLS and the SLS based on the MTJ compact model                  | 101 |

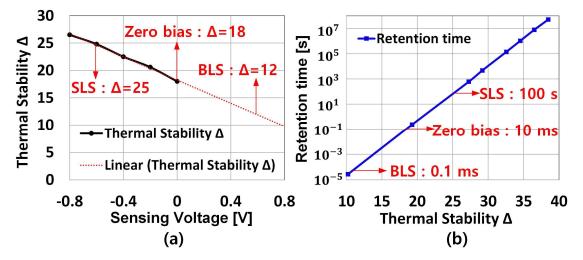

| Fig. 4.5 Measured thermal stability and retention time of an MTJ as a function of applied voltage | 102 |

|---------------------------------------------------------------------------------------------------|-----|

| Fig. 4.6 Read disturbance, sensing margin, and TMR as a function of sensing voltage               | 103 |

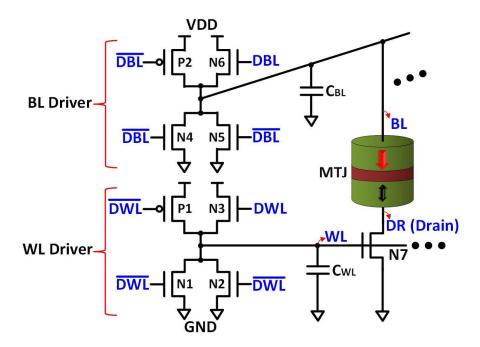

| Fig. 4.7 Schematic of cell array architecture, including the BL driver and WL driver              | 106 |

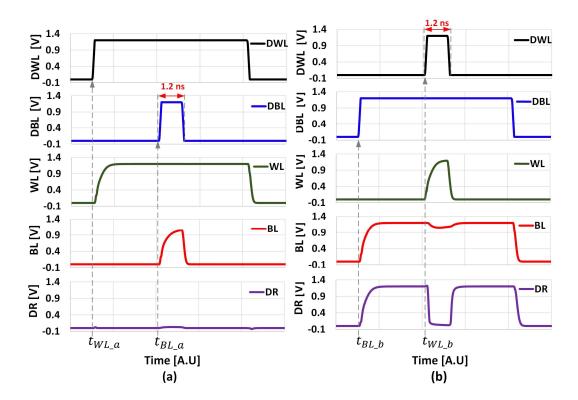

| Fig. 4.8 Timing of conventional BLP scheme and proposed WLP scheme                                | 107 |

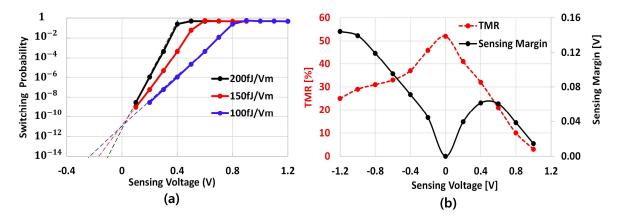

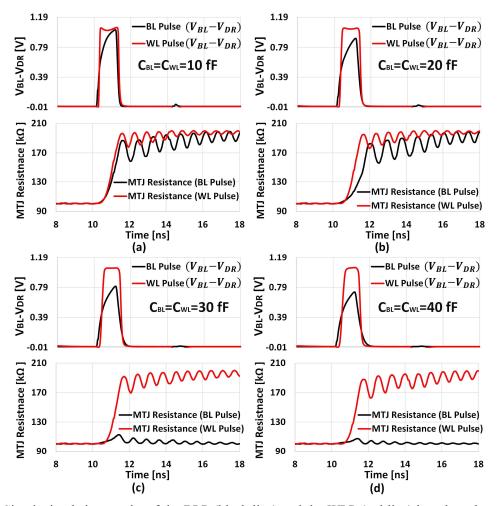

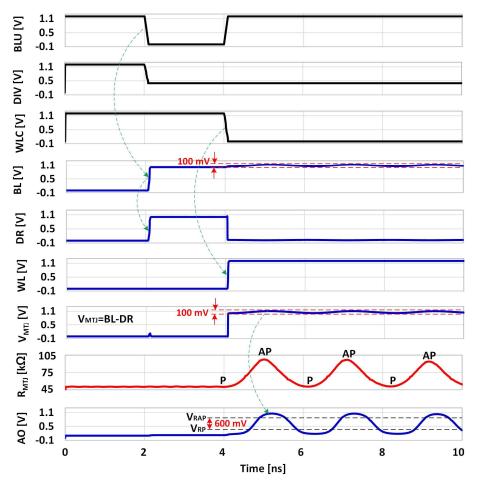

| Fig. 4.9 Circuit simulation results of the BLP and the WLP                                        | 109 |

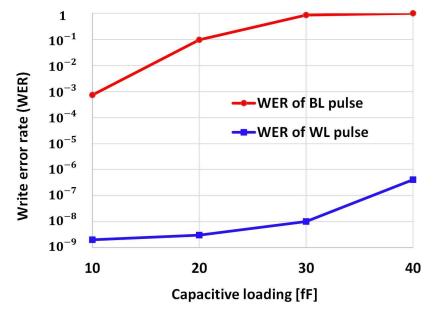

| Fig. 4.10 Write error rates of the BLP and the WLP with respect to the capacitive loading         | 110 |

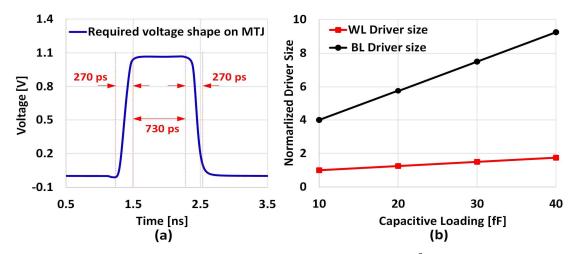

| Fig. 4.11 Required pulse shape that achieves an acceptable BER and normalized driver size         | 112 |

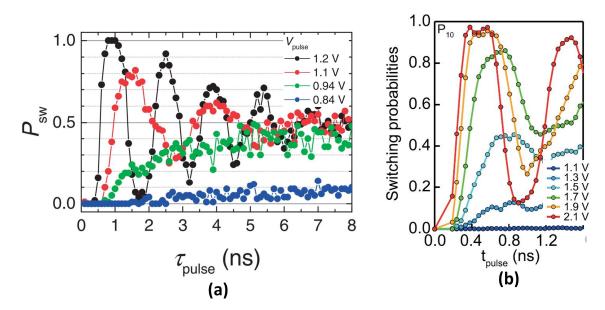

| Fig. 4.12 Experimentally observed an oscillatory behavior of the switching probability            | 113 |

| Fig. 4.13 Block diagram of the write pulse termination (WPT) circuit                              | 114 |

| Fig. 4.14 Simulation result of voltage divider                                                    | 115 |

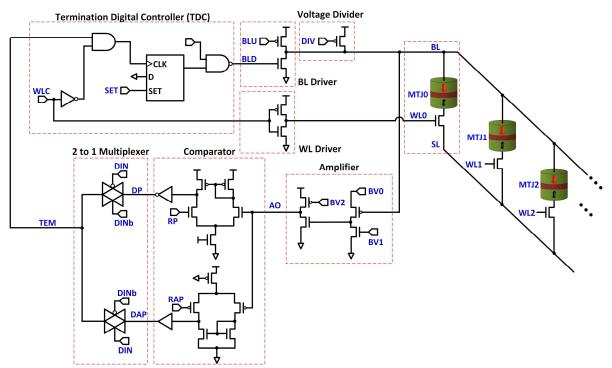

| Fig. 4.15 Transistor-level schematic of the WPT circuit                                           | 117 |

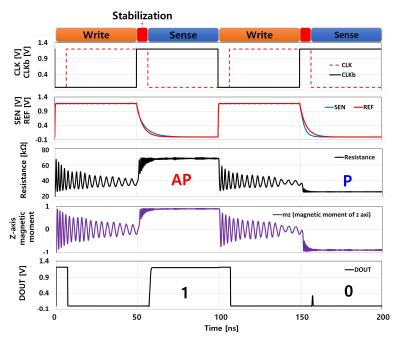

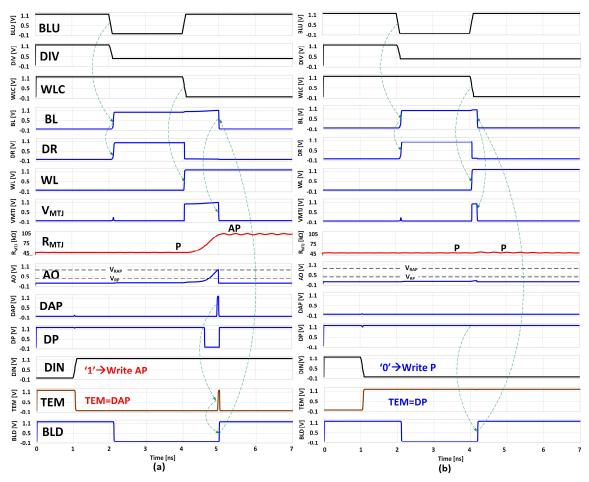

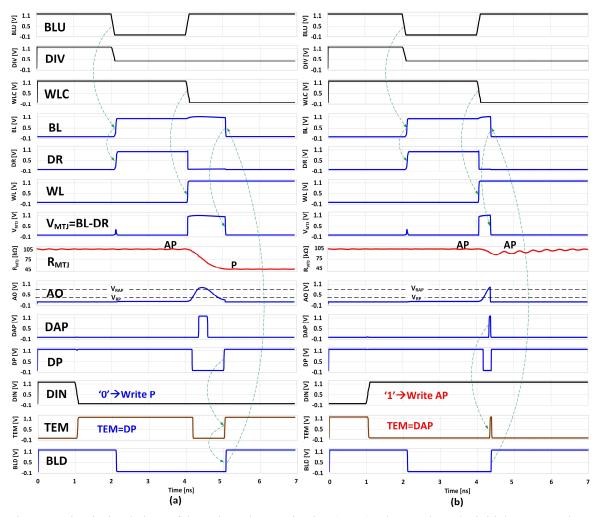

| Fig. 4.16 Circuit simulations of the WPT scheme (P state)                                         | 118 |

| Fig. 4.17 Circuit simulations of the WPT scheme (AP state)                                        | 119 |

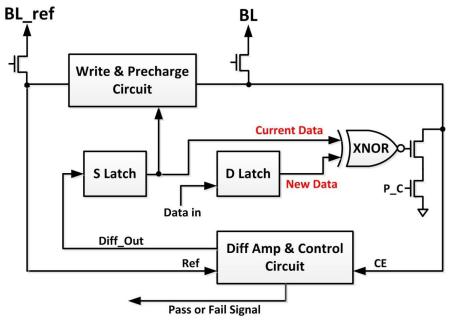

| Fig. 4.18 Concept diagram of the proposed pre-read and write sense amplifier (PWSA)               | 112 |

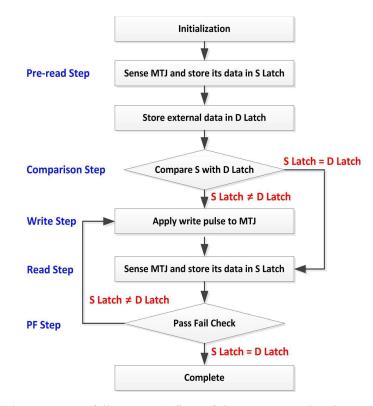

| Fig. 4.19 Proposed data program flow of the PWSA                                                  | 121 |

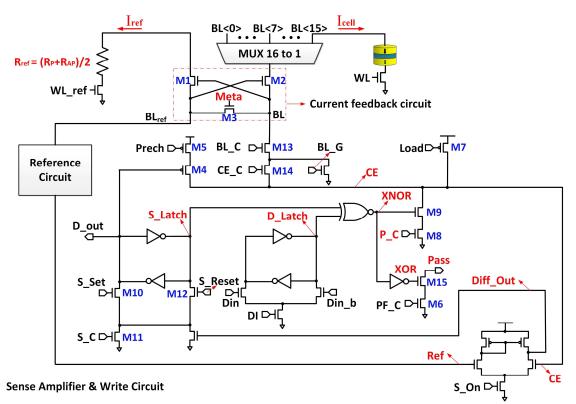

| Fig. 4.20 Transistor-level schematic of the PWSA                                                  | 122 |

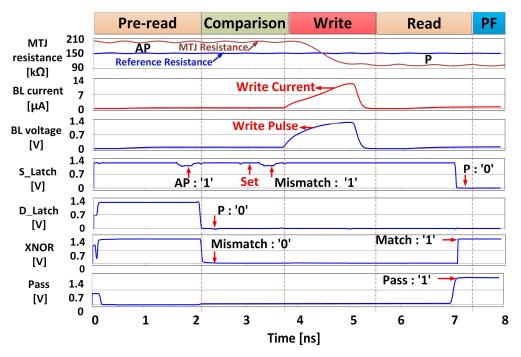

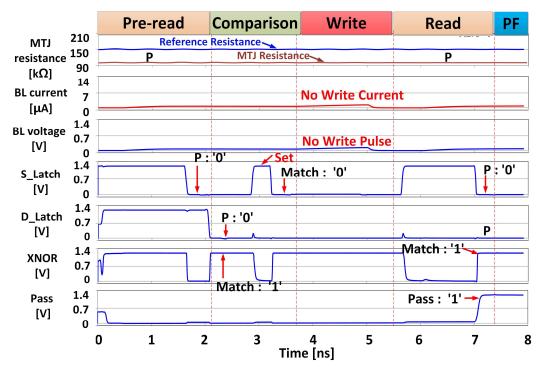

| Fig. 4.21 Simulation of the PWSA operation (AP to P)                                              | 123 |

| Fig. 4.22 Simulation of the PWSA operation (P to P)                                               | 124 |

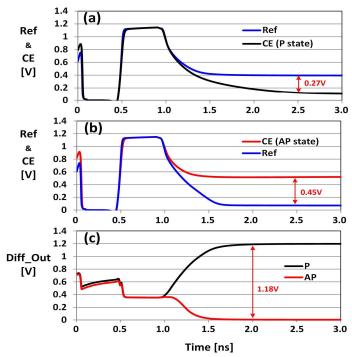

| Fig. 4.23 Simulations for the sensing margin                                                      | 126 |

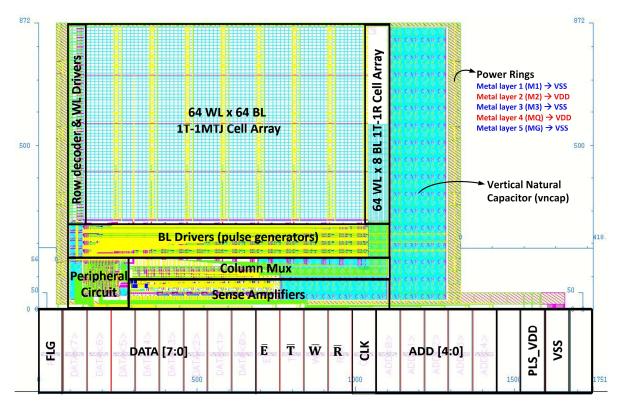

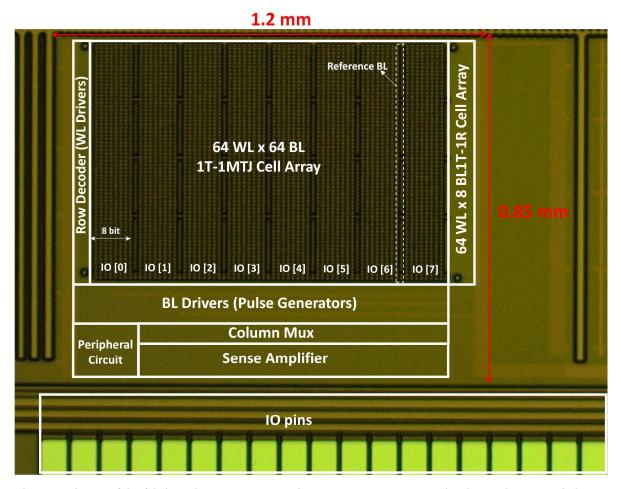

| Fig. 5.1 MeRAM macro architecture                                                                 | 127 |

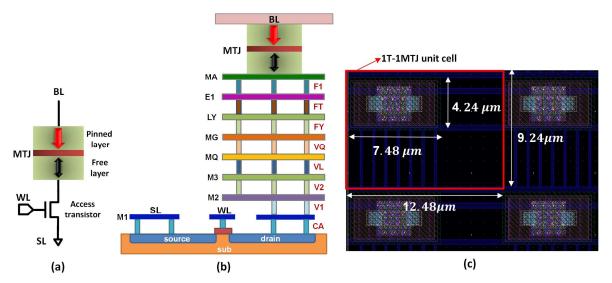

| Fig. 5.2 1T-1MTJ structure based unit cell design for MeRAM                                       | 130 |

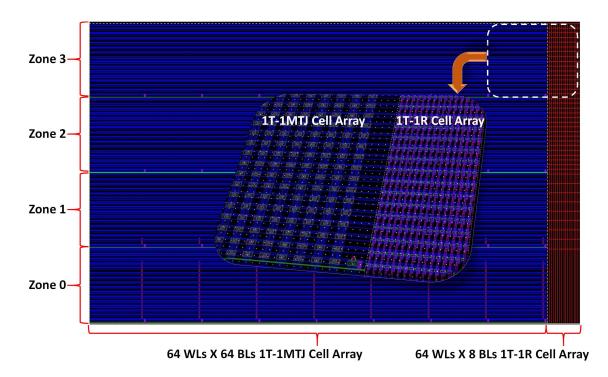

| Fig. 5.3 Layout design of the main and test cell array                                            | 131 |

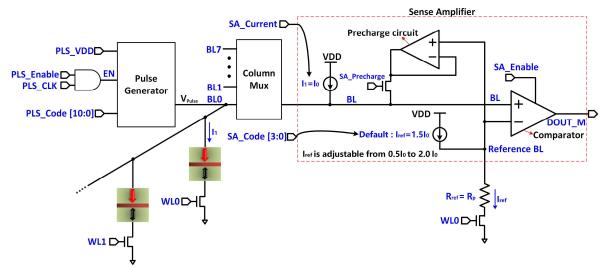

| Fig. 5.4 Schematic of the core circuit                                                            | 132 |

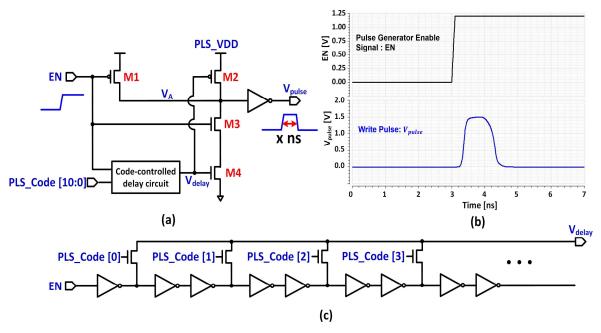

| Fig. 5.5 Schematic and simulation of the pulse generator                                        | 133 |

|-------------------------------------------------------------------------------------------------|-----|

| Fig. 5.6 Simulation of the sense amplifier for the sensing                                      | 134 |

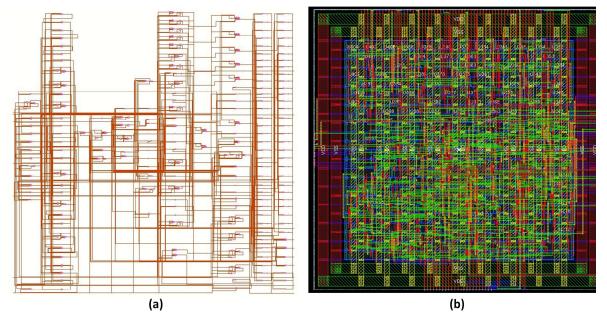

| Fig. 5.7 Schematic and layout design of the peripheral circuit                                  | 135 |

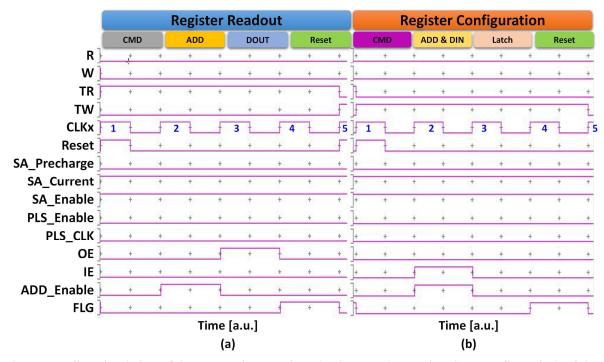

| Fig. 5.8 Verilog simulation of the test read and test write operations                          | 137 |

| Fig. 5.9 Verilog simulation of the peripheral circuit read operation                            | 138 |

| Fig. 5.10 Verilog simulation of the peripheral circuit program operation                        | 139 |

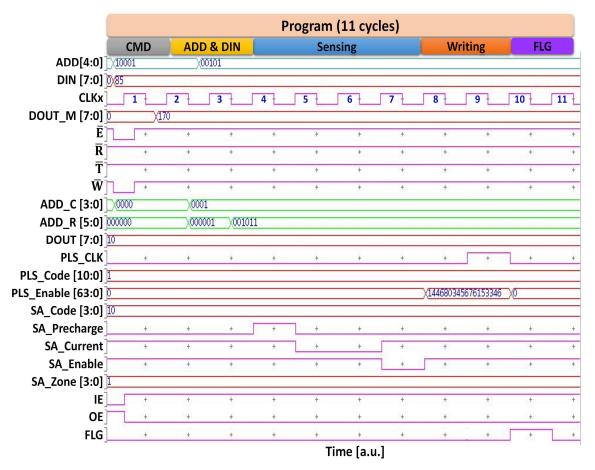

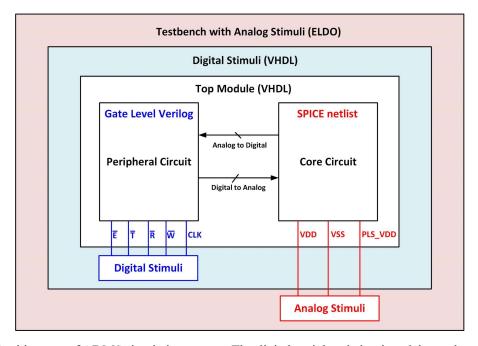

| Fig. 5.11 Architecture of ADMS simulation system                                                | 140 |

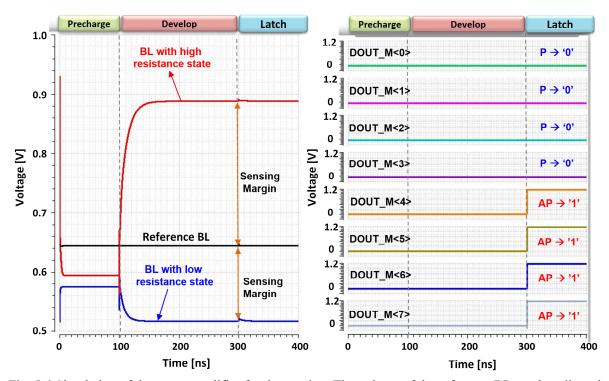

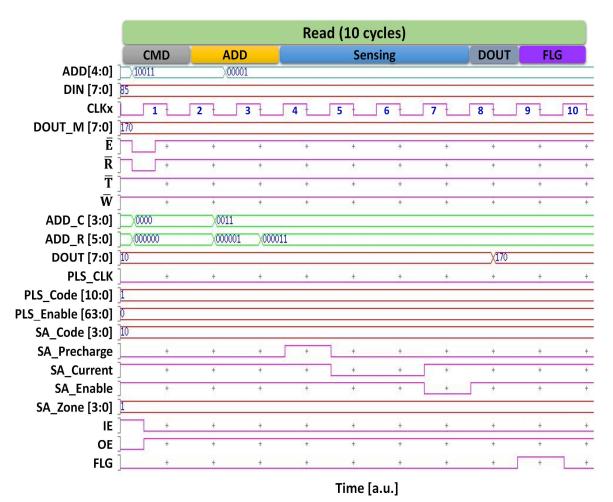

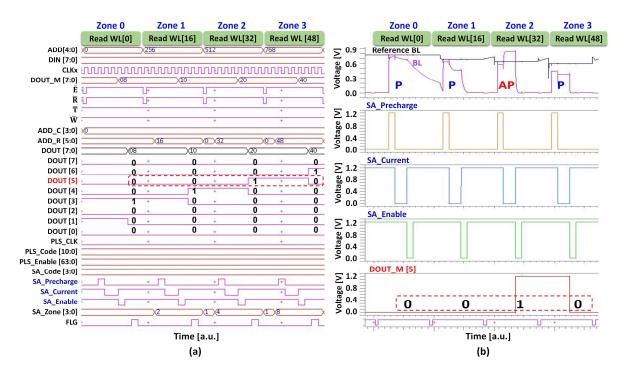

| Fig. 5.12 ADMS simulation for the read operation                                                | 141 |

| Fig. 5.13 Pulse generator enable signals corresponding to the comparison result of Table 5.6    | 142 |

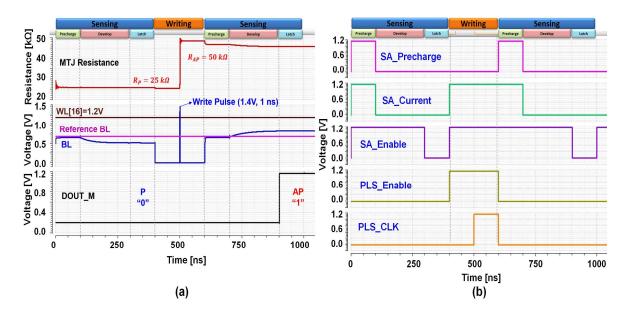

| Fig. 5.14 MTJ resistance change and core circuit control signals during the sensing and writing | 143 |

| Fig. 5.15 Layout of the MeRAM macro                                                             | 144 |

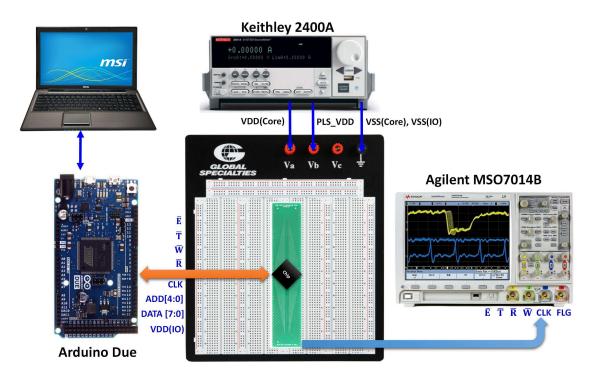

| Fig. 5.16 Picture of the fabricated MeRAM macro via 130 nm IBM RF-DM technology                 | 146 |

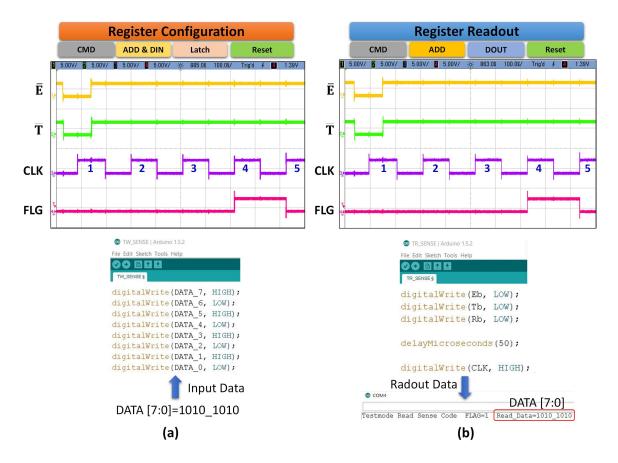

| Fig. 5.17 Test set up for the MeRAM macro                                                       | 147 |

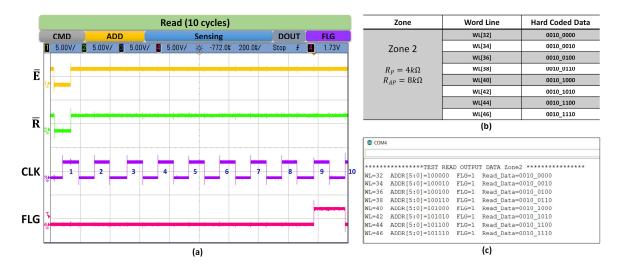

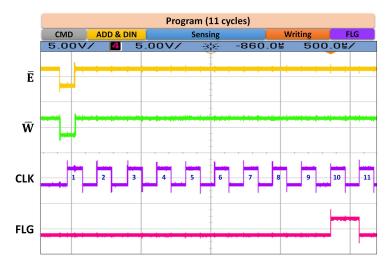

| Fig. 5.18 Measured macro signals for the test write/read operations                             | 148 |

| Fig. 5.19 Measured macro signals for the read operation                                         | 149 |

| Fig. 5.20 Measured macro signals for the program operation                                      | 149 |

## LIST OF TABLES

| Table 1.1 Performance comparison of emerging memory technologies in 1T-1R cell structure | 24  |

|------------------------------------------------------------------------------------------|-----|

| Table 1.2 28 nm node technology parameters and device characteristics                    | 28  |

| Table 1.3 Memory technologies unit cell area based on 28 nm node                         | 28  |

| Table 1.4 Formulas for array level parameters                                            | 29  |

| Table 2.1 Parameters of the macrospin compact model                                      | 40  |

| Table 3.1 Truth table of TCAM cell including Don't care condition                        | 57  |

| Table 3.2 Bias conditions for the MeTCAM configuration mode                              | 59  |

| Table 3.3 Performance comparison of TCAMs associated with different types of memories    | 62  |

| Table 3.4 Performance comparison with previous works                                     | 69  |

| Table 3.5 Area and performance of 64×64 MTJs Array based multi-bit-MRNG (45 nm node)     | 76  |

| Table 3.6 Performance comparison with previous works                                     | 89  |

| Table 3.7 Area and performance of the proposed spin and CMOS based hybrid neuron         | 95  |

| Table 4.1 Resistive and capacitive loads on the BL and the WL (28 nm node)               | 108 |

| Table 5.1 Specification of 4Kbit MeRAM Macro                                             | 128 |

| Table 5.2 Pin list and descriptions of the MeRAM macro                                   | 129 |

| Table 5.3 Port list and descriptions of the core circuit                                 | 132 |

| Table 5.4 Input port list and descriptions of the peripheral circuit                     | 136 |

| Table 5.5 Output port list and fan-out of the peripheral circuit                         | 136 |

| Table 5.6 New data and sensed data from the predefined cell patterns                     | 142 |

#### ACKNOWLEDGEMENT

I have always believed that passion, persistence, practice, and self-motivation are key words that lead to success. Throughout my life, I have been driven by my passion and continued to practice until I was satisfied regardless of failure. As a result, I have progressively achieved many goals and accomplishments that I had dreamed of. However, as I reflect on my life, I come to realize that my accomplishments were not the result of myself alone but have been possible because of the people who surround me. These are my family, advisors, colleagues, and friends who have played a pivotal role in shaping my life. I feel sincerely grateful and fortunate to have such exceptional figures who have helped me achieve my goals throughout my educational and professional development. It is an honor to have an opportunity to thank them individually through the acknowledgment section of this dissertation.

First and foremost, I would like to thank my beautiful wife Julie Yom, who has provided me unconditional love and support. Because of her dedication throughout my Ph.D. program, I was able to better focus on my research and be productive. Although her profession is in a different discipline, she has shown a great interest in my research. She puts in time to read my journals and publications to understand my research and engages in constructive conversation with me on a daily basis. I would also like to thank my parents who taught me to have a positive outlook in life and encouraged me to pursue academic achievement. Additionally, I would like to express my gratitude to every member of my family.

It has been an honor to work with my advisor, Prof. Kang L. Wang, who is a remarkable educator and researcher. I am incredibly grateful for the opportunity to conduct my research in his group, the Device Research Laboratory (DRL), and learn from him not only about scientific knowledge and skills but also research ethics. His tenacious efforts to open doors to new ideas have inspired many young researchers and provided invaluable guidance. Owing to his support, I was able to develop unique engineering skills from the device level to the circuit design level for realizing emerging spintronic based systems. In addition, I thank the committee members, Prof. Yong Chen, Prof. Puneet Gupta, and Dejan Markovic, for providing me with their valuable advice, time, and patience.

I would also like to thank my co-advisor, Prof. Pedram Khalili, who has led the Spintronics team of DRL since 2009. I feel fortunate to have learned about fundamental physics of voltage-controlled magnetism as well as communication and writing skills. Moreover, he has provided specific research directions and taught me how to manage my schedule for projects.

I have two colleagues to thank specifically. Albert Lee is a smart, passionate, and collaborative young researcher. Ever since joining the group, Albert and I have worked together and successfully completed numerous projects. I have been inspired by his problem-solving skills, excellent circuit design skills, and sincerity. Farbod Ebrahimi is a brilliant colleague who has supported me to setup experiment and simulation environments. I have enjoyed having countless productive discussions with both Albert and Farbod from brainstorming new ideas to realizing them. As a result of our synergetic efforts, our work has been published in several prestigious journals.

Furthermore, I am grateful for the opportunity to collaborate with Shaodi Wang in Prof. Gupta's group, Richard Dorrance and Sina Basir-Kazeruni in Prof. Marcovic's group, and Yilei Li in Prof. Chang's group. Last but not the least, many thanks to the members of the Spintronics team, Ayran Navabi, Xiang Li, Armin Razavi, Yuxiang Liu, Kin Wong, Guoqiang Yu, and all the members and alumni of the DRL. I wish each and every one of them successful careers, prosperity, and happiness.

#### VITA

#### Education

| 2005-2007 | M.S. in Electrical Engineering<br>Seoul National University<br>Seoul, South Korea |

|-----------|-----------------------------------------------------------------------------------|

| 2001-2005 | B.S. in Electrical Engineering<br>Korea University<br>Seoul, South Korea          |

#### **Employment history**

| 2012-2017 | Graduate Student Researcher<br>Department of Electrical Engineering<br>University of California, Los Angeles<br>Los Angeles, California |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------|

| 2015-2017 | Circuit Design Engineer (Part-time)<br>Inston Inc.<br>Los Angeles, California                                                           |

| 2007-2012 | Circuit Design Engineer<br>Samsung Electronics Co., LTD.<br>Flash Memory Circuit Design Team<br>Hwaseong, South Korea                   |

#### Publication

**<u>H. Lee</u>**, A. Lee, S. Wang, F. Ebrahimi, P. Khalili, and K. L. Wang, "Anaylysis and compact modeling of magnetic tunnel junctions utilizing voltage-controlled magnetic aninsotropy," under review, IEEE Trans. Magn., pp. 1–1, 2015.

A. Lee, <u>H. Lee</u>, F. Ebrahimi, B. Lam, W. Chen, M. Chang, P. Khalili, and K. L. Wang, "A Dual Data Line Read Scheme for High-Speed Low-Energy Resistive Nonvolatile Memories," under review (minor revision), IEEE Trans. Very Large Scale Integr. Syst. 2017.

**<u>H. Lee</u>**, A. Lee, F. Ebrahimi, P. Khalili, and K. L. Wang, "Analog to Stochastic Bit Stream Converter Utilizing Voltage-Assisted Spin Hall Effect," IEEE Electron Device Lett., pp.1-1, 2017.

<u>**H. Lee**</u>, S. Wang, A. Lee, F. Ebrahimi, P. Gupta, P. Khalili, and K. L. Wang, "A Word Line Pulse Circuit Technique for Reliable Magnetoelectric Random-Access Memory," IEEE Trans. Very Large Scale Integr. Syst., pp. 1–8, 2017.

A. Lee, C.-P. Lo, C.-C. Lin, W.-H. Chen, K.-H. Hsu, Z. Wang, F. Su, Z. Yuan, Q. Wei, Y.-C. King, C.-J. Lin, <u>H. Lee</u>, P. Khalili Amiri, K.-L. Wang, Y. Wang, H. Yang, Y. Liu, and M.-F. Chang, "A ReRAM-Based Nonvolatile Flip-Flop With Self-Write-Termination Scheme for Frequent-OFF Fast-Wake-Up Nonvolatile Processors," IEEE J. Solid-State Circuits, pp. 1–14, 2017.

**<u>H. Lee</u>**, A. Lee, F. Ebrahimi, P. Khalili, and K. L. Wang, "Array-Level Analysis of Magnetoelectric Random Access Memory (MeRAM) for High-Performance Embedded Applications," IEEE Magn. Lett., pp. 1–1, 2017.

**<u>H. Lee</u>**, F. Ebrahimi, P. Khalili, and K. L. Wang, "Design of High-Throughput and Low-Power True Random Number Generator Utilizing Perpendicularly Magnetized Voltage-Controlled Magnetic Tunnel Junction," Cit. AIP Adv., vol. 7, no. 55934, 2017.

**<u>H. Lee</u>**, C. Grezes, A. Lee, F. Ebrahimi, P. Khalili Amiri, and K. L. Wang, "A Spintronic Voltage-Controlled Stochastic Oscillator for Event-Driven Random Sampling," IEEE Electron Device Lett., vol. 38, no. 2, pp. 281–284, Feb. 2017.

C. Grezes, <u>H. Lee</u>, A. Lee, S. Wang, F. Ebrahimi, X. Li, K. Wong, J. A. Katine, B. Ocker, J. Langer, P. Gupta, P. Khalili, and K. L. Wang, "Write Error Rate and Read Disturbance in Electric-Field-Controlled MRAM," IEEE Magn. Lett., pp. 1–1, 2016.

H. Lee, C. Grezes, S. Wang, F. Ebrahimi, P. Gupta, P. K. Amiri, and K. L. Wang, "Source Line Sensing in Magneto-Electric Random-Access Memory to Reduce Read Disturbance and Improve Sensing Margin," IEEE Magn. Lett., vol. 7, pp. 1–5, 2016.

**H. Lee**, F. Ebrahimi, P. K. Amiri, and K. L. Wang, "Low-Power and High-Density Spintronic Programmable Logic (SPL) Using Voltage-Gated Spin Hall Effect in Magnetic Tunnel Junctions," IEEE Magn. Lett., vol. PP, no. 99, pp. 1–1, 2016.

S. Wang, <u>H. Lee</u>, F. Ebrahimi, P. K. Amiri, K. L. Wang, and P. Gupta, "Comparative Evaluation of Spin-Transfer-Torque and Magnetoelectric Random Access Memory," IEEE J. Emerg. Sel. Top. Circuits Syst., vol. 6, no. 2, pp. 134–145, Jun. 2016.

P. Khalili Amiri, J. Alzate, X. Cai, F. Ebrahimi, Q. Hu, K. Wong, C. Grezes, <u>H. Lee</u>, G. Yu, X. Li, M. Akyol, Q. Shao, J. Katine, J. Langer, and B. Ocker, "Electric-Field-Controlled Magnetoelectric Random Access Memory: Progress, Challenges, and Scaling," IEEE Trans. Magn., pp. 1–1, 2015.

K. L. Wang, <u>H. Lee</u>, and P. Khalili Amiri, "Magnetoelectric Random Access Memory-Based Circuit Design by Using Voltage-Controlled Magnetic Anisotropy in Magnetic Tunnel Junctions," IEEE Trans. Nanotechnol., vol. 14, no. 6, pp. 992–997, Nov. 2015.

H. Lee, J. Alzate, R. Dorrance, X. Cai, D. Markovic, P. Khalili Amiri, and K. Wang, "Design of a Fast and Low-Power Sense Amplifier and Writing Circuit for High-Speed MRAM," IEEE Trans. Magn., vol. PP, no. 99, pp. 1–1, 2014.

## CHAPTER 1 INTRODUCTION

We stand on a transition point between the third and the fourth industrial revolution where emerging technologies will dramatically change the way we live. One of the key characteristics of the fourth is that independently developed technologies start to be integrated into a single mobile device, and billions of these devices are connected to each other, creating new functionalities that humankind have never experienced. Also, the advent of artificial intelligence (AI), automation (autonomous), virtual reality, and 3-D printing makes the functionalities more sophisticated and comprehensive. However, all these advanced technologies create a large amount of data via their distributed sensors, and such big data should be transferred, processed and stored in a fast and efficient way, allowing systems to function properly. Hence, new electronic computing systems are required to have unprecedented performances in terms of throughput, power, capacity, and area. Furthermore, these demands are growing at an exponential rather than a linear pace.

For the past few decades, the performances of computing systems have been enhanced by independently improving the performance of processors and separated memory layers within Von Neumann architectures via scaling of CMOS technologies. During the third industrial revolution or the digital revolution, the scaling strategies have successfully fulfilled the growing demand for computation performances under the Moore's Law: the number of transistors in a dense integrated circuit doubles approximately every two years [1], [2]. As shrink the size of transistors, the response time of transistors and the energy consumption for computing are reduced while the cost of fabrications effectively decreases by producing more chips on a wafer. However, improvement through scaling has saturated due to several reasons. First, the channel length of transistor approach a physical limit where a transistor cannot perform as an electrical switch due to its exponentially growing leakage current [3], as shown in Fig. 1.1(a). Second, such leakage current causes a significant static power consumption,

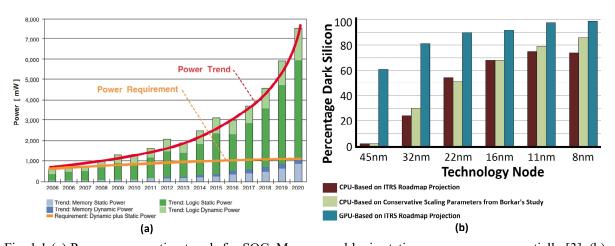

Fig. 1.1 (a) Power consumption trends for SOC. Memory and logic static power grow exponentially [3]. (b) Trend of dark silicon for different technology nodes. A significant portion of the total number of transistors in a chip needs to be turned off due to a thermal design power constraint, especially, in advanced nodes [4]. limiting low-power applications. More importantly, it becomes difficult to increase the clock frequency (throughput) due to dark silicon problem. In such a highly integrated chip, only part of the chip can be turned on at any given time, referred to dark silicon, due to a thermal design power (TDP) constraint. The percentage of dark silicon continues to increase as technology nodes are advanced [4], as shown in Fig. 1.1(b) Moreover, at the architecture level, the bandwidth of the system bus between the working memory (e.g., DRAM) and the processor cannot meet the demands of recent applications

[5], which is known as Von Neumann bottleneck.

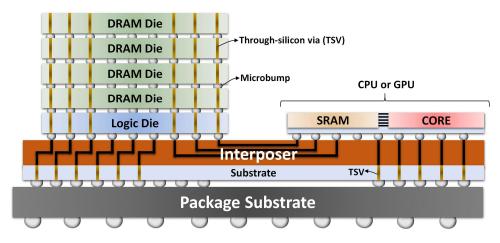

As a result, the semiconductor industry has begun to incorporate new system architectures for further performance improvements. For example, high bandwidth memory (HBM) and hybrid memory cube (HMC) techniques shorten the physical distance between working memories and processors and increase the number of channels by putting them together into a single package, as shown in Fig. 1.2. Although this approach has achieved hundreds of GB/s bandwidth in stacked 8GB DRAMs [6], the latency of signal transmissions via the interposer, ranging from 50 to 200 cycles depending on the network topology [7], is still longer than that of on-chip data transfer (4~60 cycles).

Another way of improving the throughput of a system is increasing the capacity of the processor's on-chip cache memory to reduce the cache miss rate. When the processor does not find needed data in

the cache, it allocates a memory space and fetches the required data from the main memory. This process typically takes hundreds of system clock cycles, thus acting as a bottleneck in terms of throughput. State-of-the-art processors have a few tens of MB L3 cache. However, the large area overhead of SRAM prohibits further increasing the cache capacity.

Regarding the power consumption issues, researchers have developed many standby power reduction schemes such as multiple power domains, reduced frequency, and body biasing. Other than a conventional electric power supply, additional energy sources have been implemented into a chip; for example, energy harvesting via vibration, temperature differentials, and light, to alleviate power related issues [8]. While these approaches are effective to some extent, they cannot completely eliminate leakage and often incur additional overheads.

All these approaches have pros and cons, motivating the need for a game-changing alternative that improves the performance of systems further without a trade-off. The proposed solutions are as follows. At the architecture level, integrating a high-density non-volatile memory device into a processor (nonvolatile embedded system memory) has the potential to significantly improve throughput and energy efficiency, while reducing chip area and cost [9]. The improvement comes as a result of the following: (i) On-chip data transfers are faster by one order of magnitude and more energy-efficient by a factor

Fig. 1.2 State of the art computing system architecture where the main memory and the processor are connected via the interposer in a packaged chip.

Fig. 1.3 Emerging system architecture with the embedded non-volatile memory, which has the potential to improve the bandwidth and reduce the data transfer energy further.

of 100, compared to off-chip data transfers with large capacitive loads of IO pads and off-chip wire connections. (ii) It is physically more feasible to expand the number of channels between different memory layers by using on-chip metal lines in the embedded memory compared to off-chip wires. (iii) Higher embedded memory capacity decreases the cache miss rate, effectively increasing the throughput of the system. (iv) Non-volatility can reduce the total system power consumption via zero standby power.

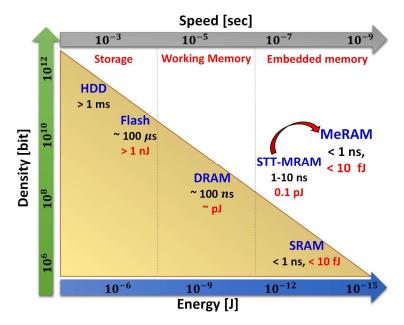

At the device level, the entire semiconductor community is looking for an emerging non-volatile device that can help CMOS continue to enhance system performances. Considering requirements of the embedded system memory in terms of speed, energy, area, and endurance, spintronic devices have been considered the strongest candidates among other emerging device technologies such as resistive RAM (ReRAM), phase-change RAM (PCRAM), and ferroelectric RAM (FeRAM). In the next section, the basic concept and history of spintronics are briefly discussed.

#### **1.1 Overview of Spintronics**

Spintronics (spin electronics) is an emerging interdisciplinary field that explores the methods to control the electrons' spin degrees of freedom and detect its associated magnetic moment in a solid-state device. The existence of a magnetic moment originating from electrons was discovered in the early 1920s, and later on, people found that it is related to the quantized electron spin. Specifically,

Wolfgang Pauli introduced Pauli matrices to explain the spin state and formalize the theory of spin based on quantum mechanics. In the 1970s, the conservation of the spin in electron tunneling was observed in ferromagnetic/insulator/superconducting aluminum junctions [10]. Although the spin of the electron has been theoretically and experimentally studied and contributed to areas of condensed matter physics, it had rarely used for practical applications due to its small magnetoresistance, a change in the electrical resistance of the device induced by an applied electrical or magnetic field, unlike the conventional electron charge-based electronics.

However, the discovery of the giant magnetoresistance (GMR) in ferromagnetic (FM) thin film multilayers separated by a non-magnetic metal layer attracted intense attention and became one of the significant milestones in spintronics in 1988 [11]. This is because the electrical resistance depending on the magnetization of adjacent ferromagnetic layers showed the potential that it can be used in many applications including memory devices, biosensors, and microelectromechanical systems (MEMS). Since the discovery of GMR, there have been two major directions in the field of spintronics, especially for memory applications. One has focused on further increasing the magnetoresistance (MR) to be utilized in practical memory applications, and another one has focused on developing new switching mechanisms to achieve energetically efficient and fast switching.

In 2001, it was theoretically proved that MR ratios of MgO-based tunnel barrier device could reach over 1000% based on first principle calculation [12]. A few years later, MR ratios of 200% were experimentally obtained in magnetic tunnel junctions (MTJs) with a crystalline MgO (001) barrier at room temperature in 2004 [13]. MR ratios of MTJ is called tunneling magnetoresistance (TMR), which is also defined the resistance difference between the high resistive state and low resistive state of the MTJ. The TMR has been continuously improved, achieving up to 604% at room temperature [14] via tremendous progress of MTJ fabrication, in particular, thin film deposition. From the memory circuit design perspective, high TMR not only causes reliable read operations by reducing sensing errors but also increases read speed by enhancing the sensing margin. Therefore, ever since demonstrating such

high TMR, the semiconductor industry have actively developed MTJs based magnetoresistive randomaccess memory (MRAM).

Regarding switching mechanism for MTJ devices, at the early development stage, a magnetic field was used to switch the state of spintronic devices (e.g. MTJ) by applying current to the adjacent metal line. However, in principle, directly applying a current or voltage to the MTJ for controlling its magnetization dynamic is more favorable in terms of energy and speed, compared to generating magnetic fields. This is because an enormous amount of energy is required to create a sufficient magnetic field to switch devices via a metal line, which in turn causes speed and scaling bottlenecks. Therefore, the magnetic field-driven switching method may be difficult to be used in practical applications.

The concept of the spin-transfer torque (STT) effect, controlling magnetization dynamics by using spin-polarized charge current directly flowing through the device, was proposed independently by Berger and Slonczewski in 1996. The STT effect has allowed achieving a fairly energetically efficient and fast switching of MTJ devices [15]–[18]. Also, the spin Hall effect (SHE), spin accumulation of the surface of a heavy metal (e.g. Ta, Pt) induced by flowing charge current, was predicted in 1971 [19] and experimentally observed in materials with a high spin-orbit coupling (SOC) in 2004 [20]–[23]. The SHE has the potential to reduce the switching energy further by one order of magnitude compared to a switching induced by the STT effect.

Although both current-driven switching mechanisms of MTJs have the promising advantages compared to that of conventional storage memory devices (e.g. flash memory) in terms of speed and energy, they need to be further improved to be comparable with embedded system memories (DRAM, SRAM). However, there are fundamental limits for the current-driven switching mechanisms to improve both speed and energy simultaneously since there exists a trade-off between them. Recently, a possible alternative has been proposed to achieve an ultra-low-energy and high-speed switching of the magnetization by using voltage-driven effect [24]–[26]. Specifically, the voltage-controlled

magnetic anisotropy (VCMA) effect, modulating the magnetic properties via interfacial effects, ideally does not involve any ohmic dissipation during the switching, resulting in extremely low switching energy (down to ~1fJ). Also, VCMA-driven switching of an MTJ offers the advantage of high switching speed (down to ~100 ps) due to the nature of the precessional magnetic dynamics. This dissertation focuses on the study of voltage-driven switching in an MTJ device including its modeling, circuit design, and memory applications.

#### **1.2 Magnetic Tunnel Junction (MTJ)**

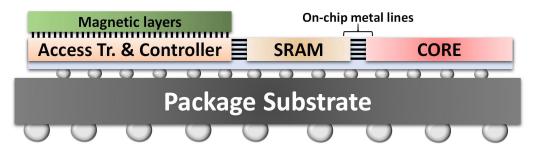

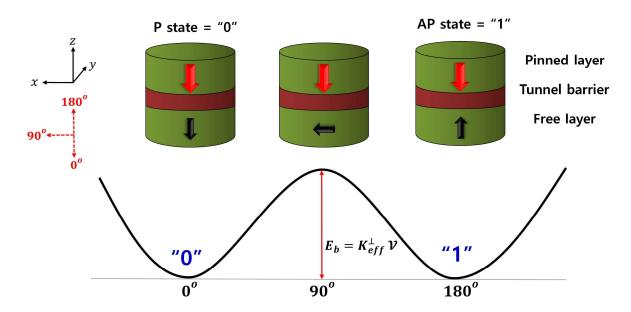

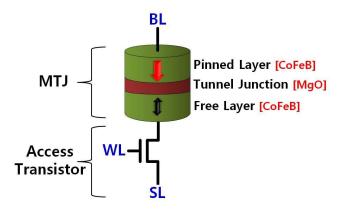

Magnetic tunnel junction (MTJs) have been considered the most practical spintronic device due to their compatibility with CMOS fabrication, sufficient on/off ratio (i.e. TMR), and scalability. These characteristics allow MTJs interacting with the-state-of-the-art charge-based electronics on the same chip as a non-volatile storage block, leading to more compact, faster, and efficient electronics systems. An MTJ consists of two ferromagnetic layers (e.g. CoFeB) separated by a tunneling barrier (e.g. MgO). The magnetization of the pinned (or fixed) layer should not be changed under any bias conditions to achieve normal memory operations. Typically, two stable magnetic equilibrium exist along an easy magnetic axis in the free layer. The parallel state (P) occurs when the magnetic moments of the both layers are aligned in the same direction giving rise to a low resistance ( $R_P$ ); on the other hand, the antiparallel state (AP) occurs when the magnetic moment of the free layer is magnetized in the opposite direction to that of the pinned layer giving rise to a high resistance ( $R_{AP}$ ). Note that the MTJ can also have an intermediate resistance value between  $R_P$  and  $R_{AP}$  if the magnetization of the free layer has transient positions.

#### **1.2.1 MTJ Device Structure**

The energy of the free layer is minimized if its magnetization is aligned with a certain axis called an easy axis resulting from the sum of different types of anisotropy in ferromagnetic systems. The opposite directions along an easy axis are equivalent. Also, it is possible to have two or more thermally stable equilibrium states in an MTJ by engineering anisotropies. However, due to limited TMR, it is preferred to have two equilibrium states to fully exploit the resistance difference in the device for practical memory applications. Based on the direction of easy axis, MTJs can be categorized into two types: in-plane and out-of-plane (perpendicular) devices. In this dissertation, we mainly focus on the out-of-plane MTJ with the international system of units (SI) rather than the centimetre-gram-second system of units (CGS).

#### 1.2.1.1 In-plane MTJ

An in-plane configuration has been used in early stage MTJ devices by engineering shape anisotropy. The demagnetization field is not equal for all directions in an elliptic cylinder shape device, creating easy axis. As shown in Fig. 1.4, the  $\hat{x}$  direction is the easy axis, and a rotation of the magnetization occurs via the  $\hat{y}$  direction (hard axis) where the smallest energy barrier is observed. Since the demagnetization field of the  $\hat{z}$  direction is very large ( $H_d \sim M_s$ ), it is difficult to switching the magnetization through the  $\hat{z}$  direction. The magnitude of in-plane MTJ energy barrier is given by

Fig. 1.4 In-plane MTJ utilizing the shape anisotropy for creating two equilibrium states. The ellipsoidal shape generates unequal demagnetizing fields for  $\hat{x}$ ,  $\hat{y}$ , and  $\hat{z}$  directions, creating the energy barrier.

$$E_b = K_{eff} \mathcal{V} \tag{1.1}$$

where  $K_{eff}$  is the effective anisotropy energy [in units of energy per unit volume] and v is the volume of the free layer. The effective anisotropy energy is equal to the shape anisotropy energy difference between the hard axis and easy axis, which is given by

$$K_{eff} = \mu_0 M_s H_{k,eff} / 2 = \mu_0 M_s^2 (N_y - N_x) / 2$$

(1.2)

where  $\mu_0$  is the permeability [H/m],  $M_s$  is the saturation magnetization [A/m],  $N_x$  and  $N_y$  are the demagnetization factors in  $\hat{x}$  and  $\hat{y}$  direction, respectively, and  $H_{k,eff}$  is the effective anisotropy field  $H_{k,eff} = (N_y - N_x)M_s$  [A/m] where its magnitude is determined by the aspect ratio (AR) of the ellipse.

As the device size shrinks, the effective anisotropy energy  $K_{eff}$  needs to be enhanced to maintain the same magnitude of the energy barrier. Therefore, as the device scales down, either the AR should be increased, or the thickness of the free layer needs to be increased if the materials of the MTJ are identical. However, the former approach is feasible up to certain values of AR due to the limitation of patterning high aspect ratio memory bit. As for the latter approach, the free layer thickness is quadratically increased to compensate the volume reduction due to the scaled MTJ diameter. Hence, the required free layer's thickness would be comparable or larger than the lateral dimension of the device, causing the other direction ( $\hat{z}$ ) to have the minimum energy barrier which is different to an inplane rotation of the magnetization. Although in-plane MTJ devices typically have lower damping factor and larger TMR ratio [27]–[29], the semiconductor industry has moved toward developing perpendicular MTJ devices due to the scalability issue of the in-plane device.

#### 1.2.1.2 Perpendicular MTJ

Another type of MTJ has the perpendicularly magnetized pinned and free layers as shown in Fig. 1.5. To make a perpendicularly magnetized MTJ, the both layers overcome the large demagnetization field  $H_{dem}$ , especially, in the  $\hat{z}$  direction by introducing a relatively stronger uniaxial anisotropy energy in the perpendicular axis. In case of the perpendicular MTJ, the demagnetization energy is calculated by subtracting the in-plane demagnetization energy from the perpendicular demagnetization energy, which is given by

$$K_d = \mu_0 M_s H_{dem} / 2 = \mu_0 M_s^2 (N_z - N_{x,y}) / 2 \approx \mu_0 M_s^2 / 2$$

(1.3)

where  $N_z$  is the demagnetization factor in the  $\hat{z}$  direction. We can approximate  $N_z \approx 1$ ,  $N_{x,y} = N_x = N_y \approx 0$ , and  $H_{dem} \approx M_s$  in a cylinder (circular) shape MTJ where the diameter of the device is much larger than the free layer thickness. Therefore, the magnitude of the uniaxial anisotropy energy  $K_u$  should meet the requirement  $K_u > \mu_0 M_s^2/2$  to realize a perpendicular MTJ.

The uniaxial anisotropy energy  $K_u$  for a perpendicular MTJ can be created by an interface effect between the tunneling barrier and the ferromagnetic layer or a magnetocrystalline effect [30]. Also, the uniaxial anisotropy can be expressed in terms of the uniaxial perpendicular anisotropy  $H_{k\perp}$ .

$$K_u = \mu_0 M_s H_{k\perp} / 2 \tag{1.4}$$

Fig. 1.5 Perpendicular MTJ utilizing the interfacial perpendicular anisotropy for creating two equilibrium states by overcoming the demagnetization field in the  $\hat{z}$  directions. Since the shape anisotropy is not necessary for forming the energy barrier, the geometry of the device can be circular, leading to a better scalability.

Therefore, the effective anisotropy energy  $K_{eff}^{\perp}$  is obtained by subtracting the demagnetization energy from the uniaxial anisotropy energy based on the single-domain approximation, which is given by

$$K_{eff}^{\perp} = K_u - K_d = \mu_0 M_s H_{eff}^{\perp} / 2 = \mu_0 M_s (H_{k\perp} - H_{dem}) / 2 = \mu_0 M_s (H_{k\perp} - M_s) / 2$$

(1.5)

where the perpendicular effective anisotropy field  $H_{eff}^{\perp}$  is defined as  $H_{eff}^{\perp} = H_{k\perp} - M_s$ , but it will be revised by adding other mechanisms in the following chapter. The energy barrier between the two equilibrium states is simply given by  $E_b = K_{eff}^{\perp} v$  in a perpendicular MTJ.

In the perpendicular MTJ, the magnetization rotation between the  $\hat{z}$  and  $-\hat{z}$  directions occurs via traveling the in-plane (hard axis) by overcoming the energy barrier as shown in Fig. 1.5. One of the most promising advantages of the perpendicular MTJ is that its energy barrier is not dominated by the geometry of the device but by the uniaxial perpendicular anisotropy. Since the uniaxial perpendicular anisotropy can be readily enhanced by engineering the interface effect, the perpendicular MTJ has a better scalability compared to that of the in-plane device governed by the AR. Recently, the large interfacial perpendicular anisotropy with a TMR ratio larger than 100% has been demonstrated in a Fe-rich CoFeB based MTJ [31], opening the door to practical applications. More importantly, it has been experimentally observed that such perpendicular anisotropy can be modulated by applying electric fields across the MTJ device, resulting in a low-energy and high-speed voltage-controlled switching scheme. This voltage-controlled switching mechanism in perpendicular MTJ will be discussed throughout this dissertation.

#### 1.2.2 Tunneling Magnetoresistance (TMR) Ratio

Magnetic tunnel junctions (MTJs) have become the most promising spintronic devices as their tunneling magnetoresistance (TMR) ratio has been increased, resulting in a large readout sensing margin in memory applications. The TMR ratio is defined as the ratio between the high resistance  $(R_{AP})$  and the low resistance  $(R_P)$ , which is given by

$$TMR = \frac{R_{AP} - R_P}{R_P}$$

(1.6)

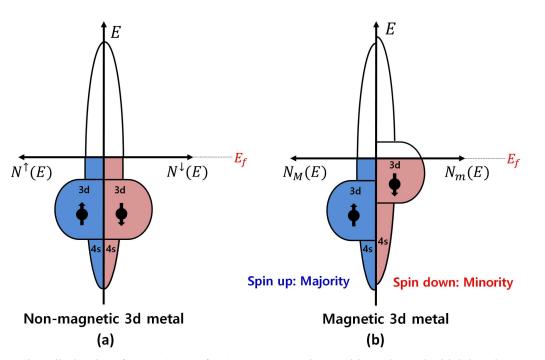

Although Jullière theoretically proposed the TMR effect and observed it only at low temperature in 1975 [32], it took 20 years to realize the effect in amorphous  $Al_2O_3$  based MTJ devices at room temperature [33], [34]. For a better understanding of the Jullière model, it is necessary to introduce the spin-split density of states (DOS). Figure 1.6 shows the simplified DOS of non-magnetic and magnetic transition 3d metals. Especially, in magnetic metals, the DOS for spin-up and spin-down are unequal, causing the net magnetization and spin-polarization of the current.

It is important to distinguish two concepts between magnetization and spin-polarized current in the context of the DOS. The magnetization (M) originates from the difference between the total number of occupied electrons in the majority DOS and the minority DOS, which is given by

$$M \propto \int_{E=0}^{E=\infty} N_M(E) - \int_{E=0}^{E=\infty} N_m(E)$$

(1.7)

Fig. 1.6 Spin-split density of states (DOS) for (a) non-magnetic transition 3d metal which has the symmetry of the DOS for spin-up and spin-down (b) magnetic transition 3d metal that has the asymmetry of the DOS for spin-up (majority) and spin-down (minority).

However, electrical transport is caused by charge carriers close to the Fermi edge  $E_F$ . Then, we can define the spin polarization with the majority  $(N_M)$  and minority  $(N_m)$  DOSs at the Fermi edge  $E_F$ .

$$P = \frac{N_M - N_m}{N_M + N_m} \tag{1.8}$$

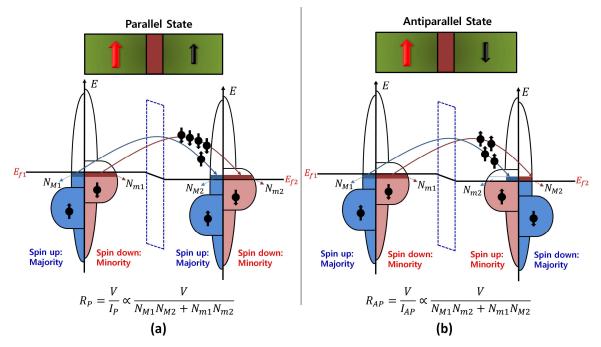

Jullière model assumes that not only the tunneling rate is proportional to the product of the DOS at the Fermi edge  $E_F$  for the two magnetic layers, but also there is no decay of the DOS within the tunnel barrier. Therefore, the tunneling currents of parallel and anti-parallel configuration in the MTJ would be expressed by

$$I_P \propto N_{M1} N_{M2} + N_{m1} N_{m2} \tag{1.9}$$

$$I_{AP} \propto N_{M1} N_{m2} + N_{m1} N_{M2} \tag{1.10}$$

Fig. 1.7 Two channel Jullière model for the tunneling between two ferromagnetic layers with (a) parallel (b) anti-parallel magnetization. The model shows that the parallel state is dominated by the minority channel. However, in reality, the majority channel always dominates the tunneling process due to the severe decay of the minority DOS within the tunnel barrier despite the fact that the minority DOS is relatively larger than that of majority in the ferromagnetic layers.

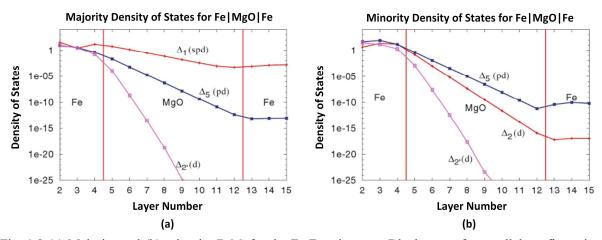

Fig. 1.8 (a) Majority and (b) minority DOS for the Fe Fermi energy Block states for parallel configuration [35]. Overall, the decay rate of the majority DOS is slower than that of the minority, allowing majority electron dominating the conductance.

where  $N_{M1}$  and  $N_{M2}$  are the majority Fermi energy DOS for the left and right ferrormagnets, respectively, and  $N_{m1}$  and  $N_{m2}$  are the minority Fermi energy DOS for the left and right ferrormagnets, respectively. We can define the polarization of the Fermi energy DOS for the two ferrormagnets as,

$$P_1 = \frac{N_{M1} - N_{m1}}{N_{M1} + N_{m1}} \tag{1.11}$$

$$P_2 = \frac{N_{M2} - N_{m2}}{N_{M2} + N_{m2}}$$

(1.12)

Based on the equation from (1.9) to (1.12), we can rewrite the TMR ratio as,

$$TMR = \frac{R_{AP} - R_P}{R_P} = \frac{I_P - I_{AP}}{I_{AP}} = \frac{2P_1 P_2}{1 - P_1 P_2}$$

(1.13)

$$[P_1P_2 > 0: normal and P_2 < 0: inverse TMR effect]$$

Typically, the minority Fermi energy DOS in 3d transient metals such as cobalt and nickel is often several times larger than that of the majority, allowing the minority channel conductance to dominate the tunneling between two magnetic layers. However, this interpretation cannot be supported by experimental observations of tunneling in ferromagnets where the majority channel conductance always dominates the tunneling regardless of the Fermi energy DOSs for both majority and minority. This is because the DOS decays within the tunnel barrier (MgO). The amount of the decay with the barrier can be calculated by including the incident Bloch states and all reflected Bloch states on the left and all possibly transmitted Bloch states on the right [35]. As shown in Fig. 1.8, the minority DOS has a faster decay compared to the majority DOS, making the majority DOS a dominant channel conductance in the actual tunneling process.

## **1.3 Magnetoresistive Random-Access Memory (MRAM)**

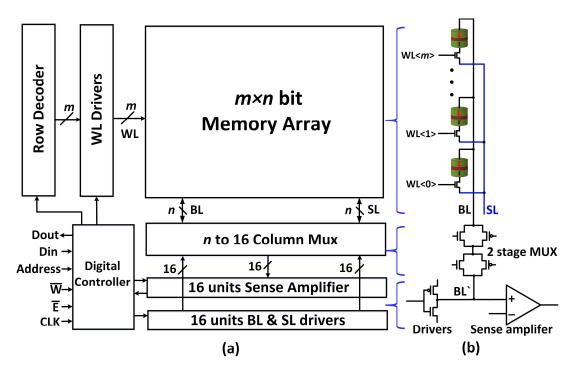

Magnetoresistive random-access memory (MRAM), utilizing MTJ devices as memory elements, is categorized into several families based on the switching mechanisms: Oersted-field-switched (toggle) MRAM, STT-MRAM, MeRAM, and spin-orbit torque MRAM (SOT-MRAM). In this section, we will qualitatively describe the switching mechanisms and their bias condition for writing in one transistor and one MTJ (1T-1MTJ) cell structure. Also, advantages and disadvantages of each memory type will be discussed. Since a read (sensing) operation is quite common among the families of MRAM, detecting the current or voltage difference on the bit line (BL) or the source line (SL) depending on the state of an MTJ, we skip the detail description of the read operation in this section.

## 1.3.1 Oersted-field-switched MRAM

The Oersted-field-switched MRAM is considered as the first generations of MRAM and initially proposed in 1960 [36]. In order to switch the magnetization of the free layer, this type of MRAM generates the Oersted fields by applying a relatively large amount current via adjacent metal lines. The current flowing through the BL ( $I_{w1}$ ) plays role in reducing the energy barrier between two states by generating the Oersted field in the direction of the hard axis as shown in Fig. 1.9. The other current flowing in the adjacent metal ( $I_{w2}$ ) at the bottom side of the MTJ determines the final state depending on the sign of  $I_{w2}$  by changing the direction of the Oersted field which is parallel to the easy axis.

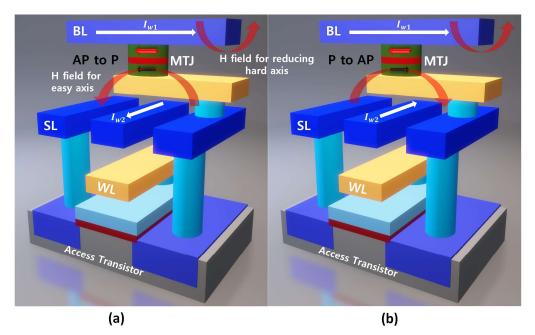

Fig. 1.9 Oersted-field-switched MRAM cell structure consisting of an access transistor and an in-plane MTJ. Two currents are applied to the adjacent metal lines to generate magnetic fields in the hard and easy axis of the MTJ. Bias conditions for switching from (a) AP to P and (b) P to AP.

Although the Oersted field based switching has been successfully demonstrated, this family of MRAM has not been widely used in practical electronic systems due to several critical issues. First of all, the magnitude of the write current for switching is substantial. For example, if an MTJ has 100 Oe (7957 A/m) coercivity, and the distance from the adjacent metal and the MTJ is 100 nm, the required current would be approximately 5 mA per bit. If the chip writes multiple MTJ devices simultaneously, it gives rise to large power consumption and heating problem. As the device size shrinks, these problems become severe because the switching current is inversely proportional the volume of the MTJ [37]. Also, as the distance between cells reduces, the stray fields from the selected cells more strongly affect the state of the adjacent cells, which may occur bit errors.

#### **1.3.2 Spin-Transfer Torque MRAM (STT-MRAM)**

Along with a giant TMR effect, the discovery of the spin-transfer torque (STT) manipulating the magnetization by spin-polarized currents in nanomagnets is considered as another milestone in the

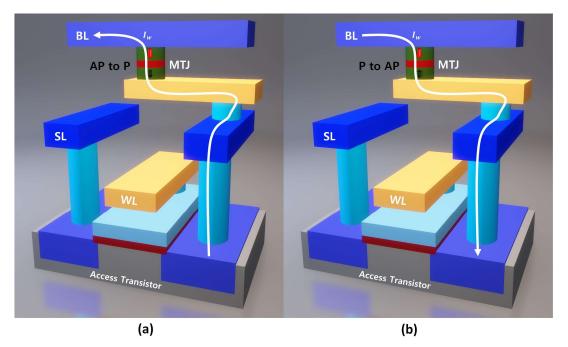

Fig. 1.10 1T-1MTJ cell architecture in STT-MRAM. Any magnetic fields are not involved in a write operation, allowing a relatively low energy switching compared to that of Oersted-field-switched MRAM. Switching can be achieved by passing a current through the MTJ, delivering the spin-transfer torque to the free layer. The final state of the MTJ is determined by the write current direction. (a) AP to P and (b) P to AP switching.

field of spintronics, accelerating the development of MRAM. STT-MRAM addresses the problems of Oersted-field-switched MRAM including scalability and switching energy issues while it maintains the general advantages of MRAM such as high endurance, high speed, and non-volatility. It has been demonstrated that the switching energy via STT effect (~100 fJ/bit) is two orders of magnitude smaller than that of Oersted-field-induced switching (~10 pJ/bit).

In a 1T-1MTJ cell structure of STT-MRAM as shown in Fig. 1.10, the writing operation is executed by applying a charge current via the MTJ device, and its final state is determined by the direction of the current. Specifically, for achieving AP to P switching, the current flows from the SL to the BL (from the free layer to the pinned layer), which allows electrons to be aligned with the magnetization of the pinned layer when they penetrate the pinned layer. This spin-polarized current transfers some of its momentum to the free layer, leading to switching of the MTJ from AP to P. On the other hand, to obtain switching from P to AP, the current flows from the BL to the SL (from the pinned layer to the

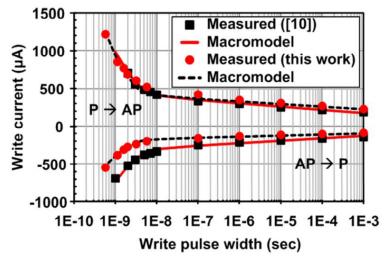

Fig. 1.11 Amplitude of write current as a function of write pulse width for switching. To achieve a high-speed switching, the required write current becomes very large, limiting the density of the array due to the large size of the access transistor [38].

free layer). In this case, electrons are transferred from the free layer to the pinned layer. However, some of the electrons, which are spin-polarized in the opposite direction of the magnetization of the pinned layer, bounce back to the free layer and transfer their momentums to the free layer, resulting in switching of the MTJ from P to AP. This current-driven STT switching is deterministic, which means that the current direction decides the final state of the MTJ. This deterministic switching allows having a simplified write circuitry, which is beneficial in terms of the circuit design effort.

Albeit STT-MRAM has many advantages, several problems need to be addressed. It is possible to change the magnetization of the free layer with relatively low current (~100  $\mu$ A) as long as the write operation time is long enough (> 10 ns). However, to achieve a few nanosecond switching speed, the write current drastically increases as shown in Fig. 1.11 [38]. Also, the size of the access transistor should be sufficiently large to drive a required switching current, which limits the density of the cell array. Therefore, the high-performance STT-MRAM can be obtained at the expense of cell density and energy efficiency. Furthermore, the switching current from P to AP is typically larger than that of from AP to P due to different spin momentum transfer efficiencies as shown in Fig. 1.11. The asymmetry of the switching currents may lead to a uniformity issue in terms of write error rate (WER). This

problem can be more severe because of the effect of the source degeneration from the access transistor depending on the cell configuration (connection) of the access transistor and the MTJ.

## 1.3.3 Magnetoelectric RAM (MeRAM)

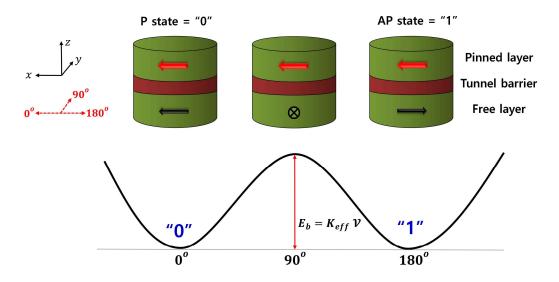

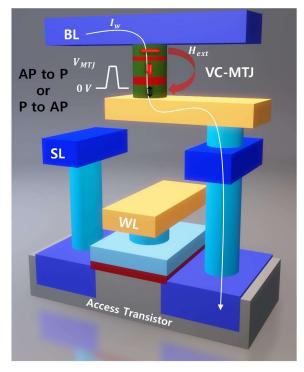

The tradeoff between speed and power of the STT-driven switching makes difficult for STT-MRAM to be used in high-performance and low-power applications. As an alternative, the VCMA effect can replace the STT and achieve both low-energy and high-speed switching by avoiding the flow of large current and exploiting the fast precessional magnetization dynamic during the switching process while maintaining other remarkable features of STT-MRAM such as high endurance, compatibility with CMOS process, and non-volatility. This type of MRAM is called magnetoelectric RAM (MeRAM), which is one of the main parts of this dissertation. We will scrutinize physics behind of the VCMA effect and its precessional switching mechanism in the next chapter. In this section, we

Fig. 1.12 1T-1MTJ cell architecture in MeRAM. Switching can be achieved by applying an electric pulse to the MTJ, which induces a magnetic precessional motion in the free layer. Since this type of switching mechanism is non-deterministic, a unipolar pulse can switch either from AP to P or from P to AP.

will discuss general features of MeRAM and its write bias conditions within the 1T-1MTJ cell structure.

There is no huge difference between MeRAM and STT-MRAM in terms of cell structure as shown in Fig. 1.12. However, the size of the access transistor in MeRAM can be reduced further in that the VCMA-driven switching ideally does not require the flow of current. Thus the bit cell array of MeRAM can achieve higher density compared to other families of MRAM. Also, the thickness of the tunnel barrier is relatively thicker than that of MTJ in STT-MRAM, practically reducing ohmic dissipation during the write operation.

For switching the MTJ device based on the VCMA effect, an electric pulse is applied to the device in the presence of an in-plane stray field which can be generated by the other ferromagnetic layer. The applied electric pulse modulates the magnetic property of the MTJ, resulting in precessional motion of the magnetization of the free layer. It is noted that the duration, slew rate, and amplitude of the pulse should be well defined depending on the MTJ characteristics to achieve high switching probability. Also, since the VCMA effect is unipolar, switching from AP to P or from P to AP is achieve by pulses with the same polarity. Thus, this type of switching is non-deterministic, which requires new considerations in terms of circuit design.

#### 1.3.4 Spin-Orbit Torque MRAM (SOT-MRAM)

The spin Hall effect (SHE), which is one type of spin-orbit torques (SOTs), have been considered as an another alternative for switching MTJs. Although the SHE was initially detected in thin films of the semiconductors GaAs and InGaAs by using Kerr rotation measurement [20], this mechanism has attracted a significant attention after demonstrating the SHE induced magnetic switching in a perpendicularly magnetized Ta/CoFeB/MgO/Ta film at room temperature [22]. This family of MRAM that utilizes spin-orbit torque is referred to SOT-MRAM.

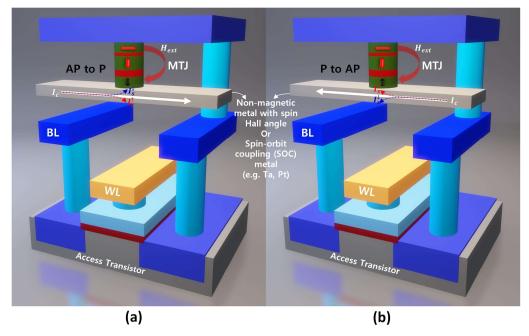

Figure 1.13 shows a unit cell of SOT-MRAM where the access transistor is connected to the top electrode of the MTJ, which is fabricated on top of the non-magnetic metal with spin Hall angle, also

called the spin-orbit coupling (SOC) metal. For the write operation, the current flowing in the nonmagnetic metal generates a spin current that delivers spin-orbit coupling (SOC) to the MTJ device for switching. The conversion efficiency between the charge current  $I_s$  and the spin current  $I_s$  is called spin Hall angle  $\theta_{SH} \propto I_s/I_s$ . The polarization of the spin current is the in-plane, which is the direction of the cross product of the charge current and the spin current. The desired MTJ state can be determined by the direction of the charge current.

The advantages of SOT-MRAM is as follows. First, it is possible to reduce the switching current by one order of magnitude by engineering the thickness of the metal layer with spin Hall angle compared to that of STT-MRAM. Second, the separation of the electrical paths between the write and the read operations in the three-terminal device decreases read disturbances, improving the reliability. In addition, the write circuit would be simple since the SHE-driven switching current from P to AP

Fig. 1.13 1T-1MTJ cell architecture in SOT-MRAM. The three-terminal device utilizes the spin Hall effect of the SOC metal. For switching an MTJ, the charge current flowing in the SOC metal creates the spin-current via the SHE effect, which causes spin-orbit coupling in the free layer. A stray field is required to break the symmetry to switch perpendicular MTJ devices. The final state of the MTJ is determined by the write current direction. (a) AP to P and (b) P to AP switching.

and from AP to P is symmetric. Finally, a relatively low resistive metal layer (e.g. Ta, Pt) decreases ohmic loss further, resulting in the significant reduction of switching energy (~10 fJ/bit).

However, SOT-MRAM also faces challenges and issues that need to be solved. First, since the unit cell is based on the three-terminal magnetic device, it may require additional transistors at the edges of the metal with spin Hall angle for the write operation other than the access transistor, leading to penalties in terms of cell array density. Second, the spin current polarized into in-plane, in principle, cannot switch a perpendicularly magnetized MTJ device. Hence, additional methods are necessary to break the symmetry by using applying an external stray field, structural manipulation, and interfacial electromagnetic coupling [39], which increases the fabrication complexity.

#### **1.3.5 Performance Comparison**

#### 1.3.5.1 Device Level

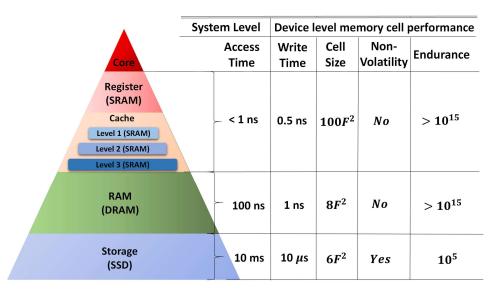

Conventional memory technologies for Von-Neumann structures have their physical limitations. Although SRAM has fast access time (<1 ns) and unlimited endurance, this memory technology are power-hungry at the advanced CMOS technology nodes due to high leakage current [40]. Also, DRAM plays an important role in the main memory of the Von-Neumann architecture. However, it is volatile, requires refresh, and is not as fast as SRAM [41]. Although solid-state devices such as Flash memory are typically used in embedded systems as a secondary storage because of their high density, they suffer from low endurance (<  $10^5$ ), slow write time (> 10 µs) and high write and erase energy [42]. The performance of existing memory technologies is summarized in Fig. 1.14.

Since each conventional memory has its pros and cons, sophisticated hierarchical memory structures consisting of several specialized layers have been used in current computing systems to achieve a high-performance with low cost. Even though potential performance breakthroughs are possible in specific layers based on emerging technologies, it remains difficult to improve the

Fig. 1.14 Memory Hierarchy in a conventional computer architecture with system level and device level memory performance.

performance of an overall system because interactions between the layers often act in unexpected ways [43].

To solve these challenges, many researchers have worked on next generation memory technologies, with the ultimate goal often described as "Universal Memory" (UM), i.e. a solution satisfying all the key requirements for a combined embedded and storage memory device: cell size  $< 4F^2$ , read/write time < 1 ns, write energy < 1 fJ, endurance  $> 10^{15}$ , non-volatility with retention of more than 10 years, and low cost for fabrication [44]. Although currently none of the emerging memories in development meet all the requirements of the UM, some of the emerging memories, i.e. Resistive RAM (ReRAM), Phase-Change RAM (PCRAM), and Magnetoresistive (MRAM), may be able to merge more than one layer of the present memory hierarchy, hence bring the UM concept closer to realization.

The 1T-1R (i.e. one access transistor associated with one resistive element) structure is widely used in memory cells since a high on/off ratio of the metal–oxide–semiconductor field-effect transistor (MOSFET) allows to select an individual memory element effectively, preventing sneak paths. In addition, the access transistor can be used in not only unipolar operations but also bipolar operations, expanding its application to different cell characteristics. However, considering the layout design limits of the MOSFET device, the feasible minimum size of an access transistor is  $\sim 20F^2$  with standard logic processes, which limits the density of the memory cell array. Although the effective cell size can reach further down to  $\sim 10F^2$  by sharing the source regions of the adjacent two cells with special via contacts [29], the access transistor is still the key factor limiting the density. Here, we briefly introduce several types of emerging memory technologies and compare their performance with that of MeRAM in the form 1T-1R structure.

First of all, PCRAM takes advantage of the resistance difference between the crystalline (low R) and amorphous (high R) states in phase change materials such as  $Ge_2Sb_2Te_5$  and  $Sb_2Te$ . The on/off ratio is ~10<sup>3</sup>-10<sup>4</sup>, allowing it to be used in multi-level cell (MLC) operations. In terms of retention, PCRAM can exceed 10 years at 85°C [45], [46]. However, PCRAM is a power hungry device because the reset current for converting to the amorphous state is relatively large. For example, a PCRAM device with the 300  $nm^2$  aperture requires 300 µA (10<sup>8</sup> A/cm<sup>2</sup>) reset current [47]. Therefore, the access transistor in a cell must be carefully chosen so that it can deliver a sufficient current. In order to provide such a high reset current, PCRAM based 1T-1R cell structures typically occupy ~30 $F^2$ - 50 $F^2$  due to the large size of the access transistor, limiting its density.

|                                | PCRAM                   | Re-RAM           | STT-RAM              | MeRAM                 |

|--------------------------------|-------------------------|------------------|----------------------|-----------------------|

| Non-volataility                | Yes                     | Yes              | Yes                  | Yes                   |

| Device size [nm <sup>2</sup> ] | 7.5 	imes 22            | $10 \times 10$   | $11 \times 11$       | $30 \times 30$        |

| Cell size with Tr. $[F^2]$     | $30-50F^2$              | $20-40 F^2$      | $20-50 F^2$          | $20 F^2$              |

| Cell size crossbar $[F^2]$     | $4 F^2$ (with diode)    | $4 F^2$          | Cannot be applicable | $4 F^2$ (with diode)  |