# $\begin{array}{c} {\rm UNIVERSITY\ OF\ CALIFORNIA,} \\ {\rm IRVINE} \end{array}$

Performance-robust, Non-blocking, Data-driven Barrier Synchronization for Multicore, Multithreaded Parallel Algorithms

#### DISSERTATION

submitted in partial satisfaction of the requirements for the degree of

#### DOCTOR OF PHILOSOPHY

in Computer Science

by

Arturo Garza Rodriguez

Dissertation Committee: Professor Isaac D. Scherson, Chair Professor Magda S. El Zarki Professor Tony D. Givargis

# **DEDICATION**

To mom and dad

# TABLE OF CONTENTS

|              | F                                                                                                                                                                                                                                                                                                                                                                                                    | Page                                               |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| LI           | ST OF FIGURES                                                                                                                                                                                                                                                                                                                                                                                        | $\mathbf{v}$                                       |

| LI           | ST OF TABLES                                                                                                                                                                                                                                                                                                                                                                                         | vii                                                |

| LI           | ST OF ALGORITHMS                                                                                                                                                                                                                                                                                                                                                                                     | viii                                               |

| A            | CKNOWLEDGMENTS                                                                                                                                                                                                                                                                                                                                                                                       | ix                                                 |

| $\mathbf{V}$ | $\mathbf{TA}$                                                                                                                                                                                                                                                                                                                                                                                        | x                                                  |

| $\mathbf{A}$ | BSTRACT OF THE DISSERTATION                                                                                                                                                                                                                                                                                                                                                                          | xii                                                |

| 1            | Introduction                                                                                                                                                                                                                                                                                                                                                                                         | 1                                                  |

| 2            | Preliminaries  2.1 Multicore Parallel Computing                                                                                                                                                                                                                                                                                                                                                      | 4<br>5<br>6<br>7<br>9<br>13                        |

| 3            | Problem Statement  3.1 Thread-level Parallelism in Multicore CPUs  3.2 CPU Hardware Capabilities  3.2.1 Cache Coherence  3.2.2 Atomic Memory Operations  3.2.3 Memory Fences  3.3 Barrier Synchronization in Multicore CPUs  3.4 Challenges in Barrier-synchronized Multithreaded Parallel Algorithms  3.4.1 Scalability of Atomic Memory Operations  3.4.2 Blocking Due to Unexpected System Delays | 16<br>17<br>18<br>19<br>19<br>20<br>21<br>23<br>23 |

| 4            | Related Work 4.1 Scaling Barrier Synchronization                                                                                                                                                                                                                                                                                                                                                     | 28<br>29<br>29                                     |

|    |        | 4.1.2 Tree-based Barriers                                                    |     |

|----|--------|------------------------------------------------------------------------------|-----|

|    |        | 4.1.3 Dissemination Barriers                                                 | 32  |

|    | 4.0    | 4.1.4 Tournament Barriers                                                    | 33  |

|    | 4.2    | Unblocking Barrier Synchronization                                           | 34  |

|    |        | 4.2.1 Multiple Disjoint Barriers                                             | 34  |

|    |        | 4.2.2 Fuzzy Barriers                                                         | 35  |

|    |        | 4.2.3 Task-stealing Barriers                                                 | 36  |

|    |        | 4.2.4 Speculative Barriers                                                   | 38  |

|    | 4.3    | Related Work Summary                                                         | 39  |

| 5  | AN     | Non-blocking Data-driven Barrier Synchronization Model (NBD <sup>2</sup> BS) | 40  |

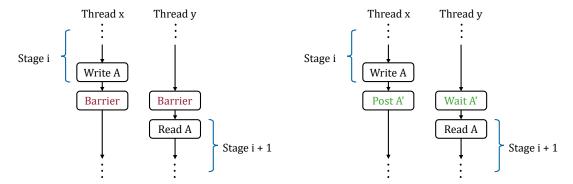

|    | 5.1    | Post-wait Synchronization Semantics                                          | 42  |

|    | 5.2    | Non-blocking Data-driven Barrier Synchronization                             | 44  |

|    | 5.3    | Summary of Conditions for the Applicability and Properties of $NBD^2BS$      | 46  |

| 6  | Exp    | perimental Verification                                                      | 48  |

|    | 6.1    | Parallel Sorting                                                             | 50  |

|    |        | 6.1.1 High Performance Sorting: Bitonicsort                                  | 50  |

|    |        | 6.1.1.1 Barrier-synchronized Parallel Bitonicsort                            | 54  |

|    |        | 6.1.1.2 Non-blocking Parallel Bitonicsort                                    | 56  |

|    |        | 6.1.1.3 Performance Analysis                                                 | 57  |

|    |        | 6.1.1.4 Bitonicsort and Multiway Mergesort Comparative Analysis .            | 62  |

|    |        | 6.1.2 A Pedagogical Example: Odd Even Transposition Sort                     | 65  |

|    |        | 6.1.2.1 Barrier-synchronized Parallel Odd Even Transposition Sort .          | 66  |

|    |        | 6.1.2.2 Non-blocking Parallel Odd Even Transposition Sort                    | 67  |

|    |        | 6.1.2.3 Performance Analysis                                                 | 69  |

|    | 6.2    | Parallel Signal Processing                                                   | 73  |

|    |        | 6.2.1 The Core Operation: Fast Fourier Transform                             | 74  |

|    |        | 6.2.1.1 Barrier-synchronized Parallel Fast Fourier Transform                 | 75  |

|    |        | 6.2.1.2 Non-blocking Parallel Fast Fourier Transform                         | 77  |

|    |        | 6.2.1.3 Performance Analysis                                                 | 78  |

| 7  | Roa    | nd to Wait-free Barrier Synchronization                                      | 82  |

|    | 7.1    | A Task-stealing Multithreading Model                                         | 83  |

|    | 7.2    | Case Study: Can Bitonicsort Achieve Wait-freedom?                            | 85  |

|    |        | 7.2.1 Stealing-barrier Parallel Bitonicsort                                  | 85  |

|    |        | 7.2.2 Wait-free Parallel Bitonicsort                                         | 87  |

|    |        | 7.2.3 Performance Analysis                                                   | 89  |

|    |        | 7.2.4 Wait-free Bitonicsort and Multiway Mergesort Comparative Analysis .    | 93  |

| 8  | Con    | acluding Remarks                                                             | 95  |

| D: | ihlioo | rranhy                                                                       | 0.8 |

|    |        |                                                                              |     |

# LIST OF FIGURES

|            |                                                                                  | Page |

|------------|----------------------------------------------------------------------------------|------|

| 2.1<br>2.2 | Hierarchy of thread progression guarantees                                       |      |

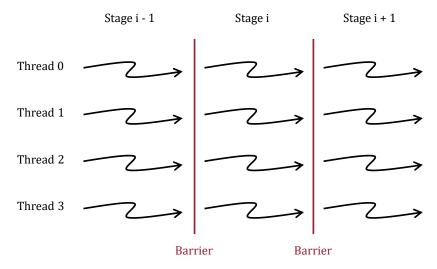

| 2.2        | Barrier synchronization                                                          |      |

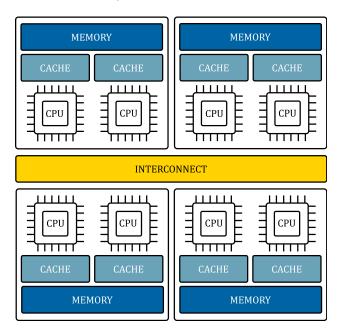

| 3.1        | Multicore system architecture                                                    |      |

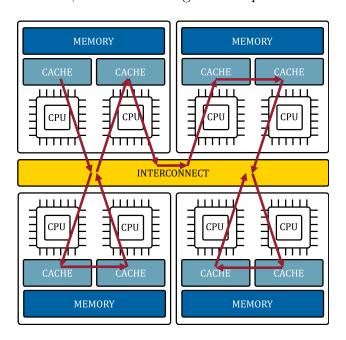

| 3.2        | Cache line bouncing                                                              |      |

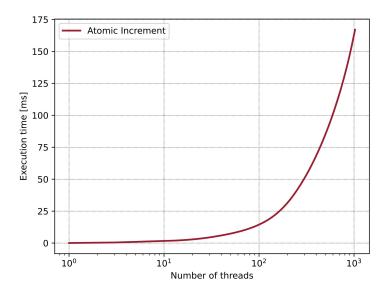

| 3.3        | Atomic increment scalabilty in x86                                               |      |

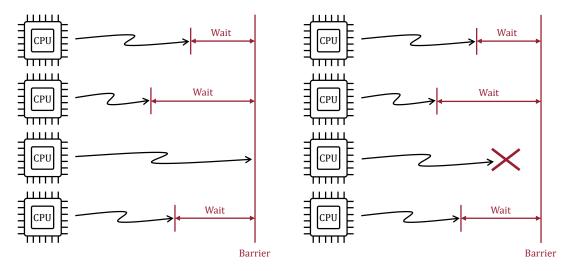

| 3.4        | Waiting for slowest thread                                                       |      |

| 3.5        | Blocking the overall task                                                        |      |

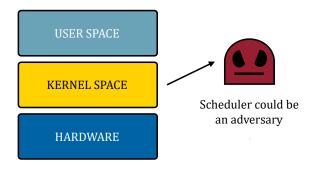

| 3.6        | Kernel scheduler could be an adversary                                           |      |

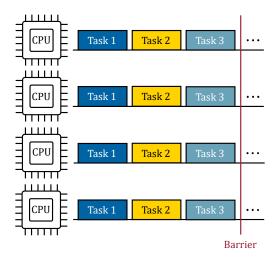

| 3.7        | Ideal barrier-synchronized parallel computational model                          |      |

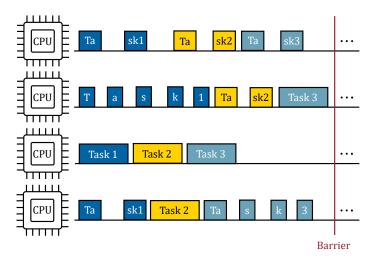

| 3.8        | Real barrier-synchronized parallel computational model                           | . 27 |

| 4.1        | Central counter barrier                                                          | . 29 |

| 4.2        | Distributed counter barrier                                                      |      |

| 4.3        | Wait at the static-tree barrier                                                  | . 31 |

| 4.4        | Leave the static-tree barrier                                                    | . 31 |

| 4.5        | Dissemination barrier                                                            | . 32 |

| 4.6        | Tournament barrier                                                               | . 33 |

| 4.7        | Progress with multiple disjoint barriers                                         | . 34 |

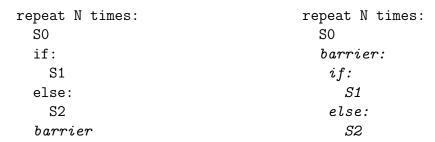

| 4.8        | Branches outside barrier                                                         | . 35 |

| 4.9        | Branches inside barrier                                                          | . 35 |

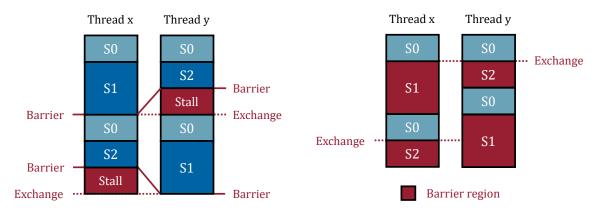

|            | Progress with normal barrier                                                     |      |

|            | Progress with fuzzy barrier                                                      |      |

|            | Task-stealing barrier                                                            |      |

|            | Task-stealing barrier steals task                                                |      |

| 4.14       | Speculative thread is rolled back                                                | . 38 |

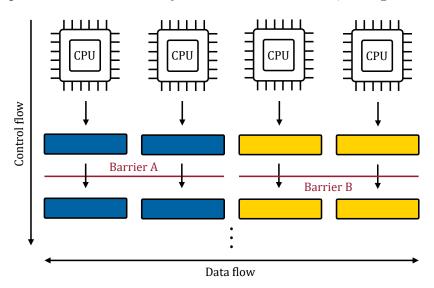

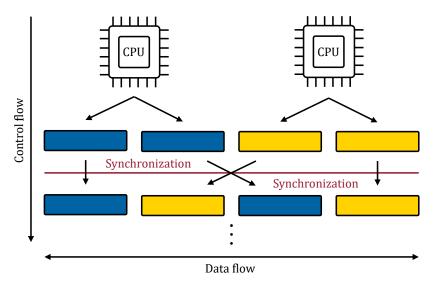

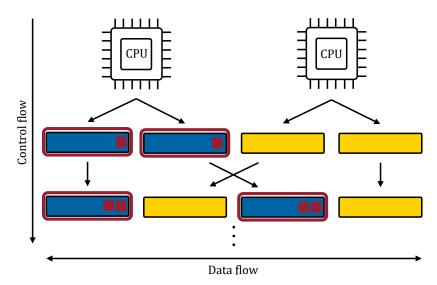

| 5.1        | Control flow vs data flow in parallel applications with barrier synchronization  | . 41 |

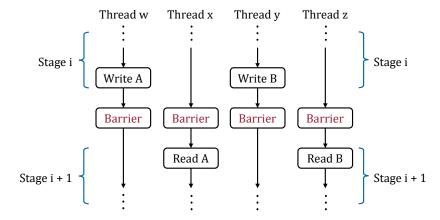

| 5.2        | Barrier semantics                                                                |      |

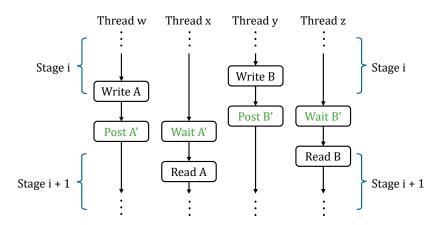

| 5.3        | Post-wait semantics                                                              |      |

| 5.4        | Progress using barrier synchronization semantics.                                |      |

| 5.5        | Progress using post-wait synchronization semantics                               |      |

| 5.6        | Control flow vs data flow in parallel applications with post-wait synchronizatio |      |

| 5.7        | Control flow barrier                                                             |      |

| 5.8  | Data flow barrier.                                                                 | 44 |

|------|------------------------------------------------------------------------------------|----|

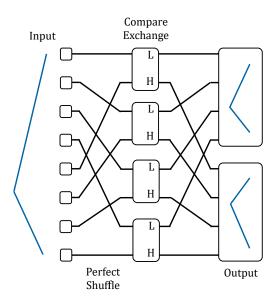

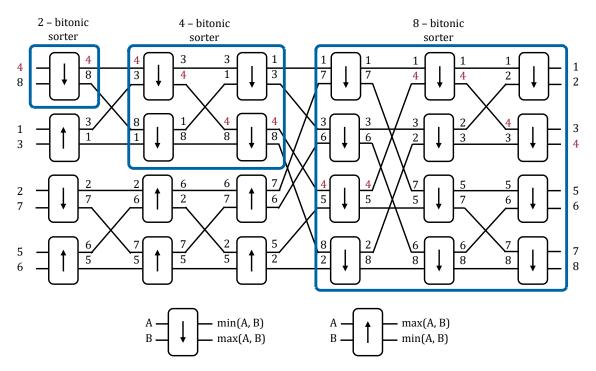

| 6.1  | Bitonic theorem for a bitonic sequence of size 8                                   | 51 |

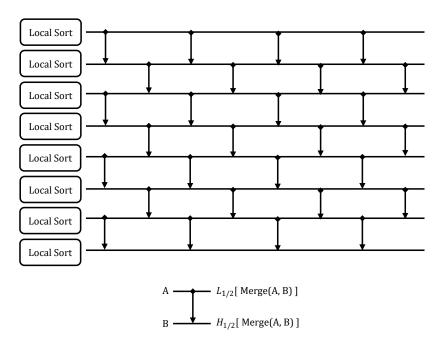

| 6.2  | Bitonicsort network for an arbitrary sequence of size 8                            | 52 |

| 6.3  | Bitonicsort algorithm pattern for an arbitrary sequence of size 8                  | 53 |

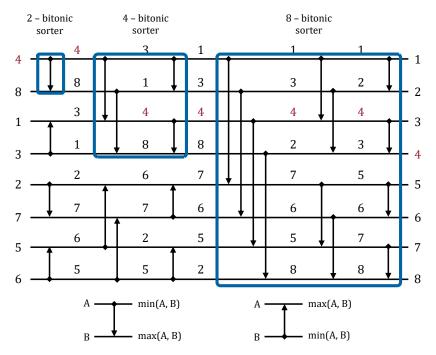

| 6.4  | Bitonicsort algorithm pattern for an arbitrary sequence divided into segments.     | 54 |

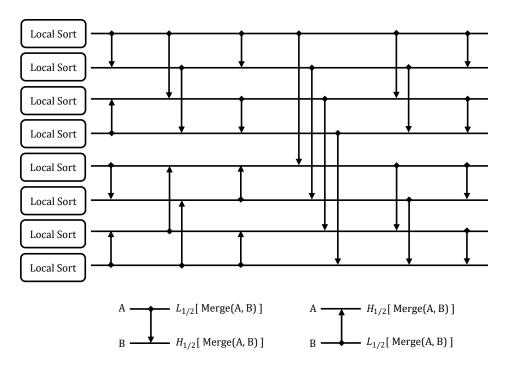

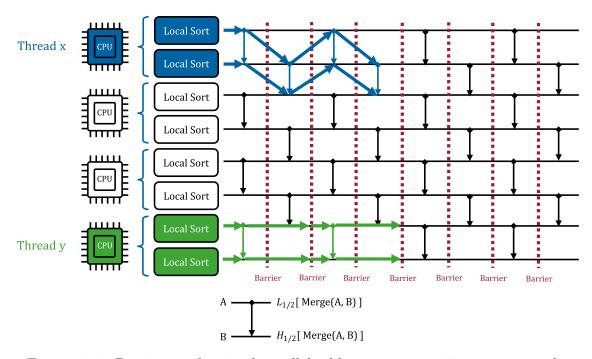

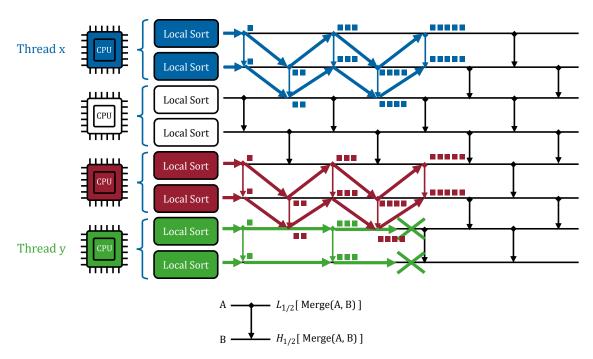

| 6.5  | Barrier-synchronized parallel bitonicsort example                                  | 55 |

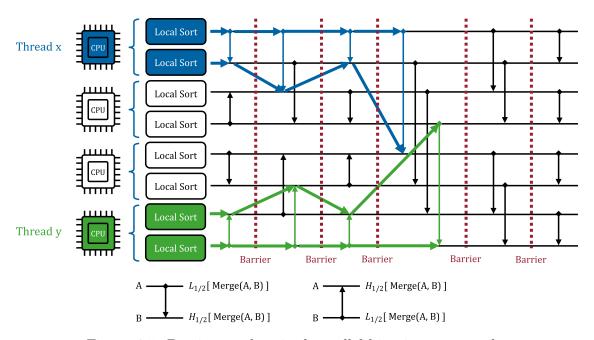

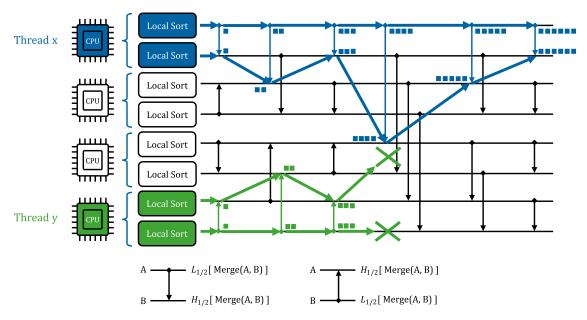

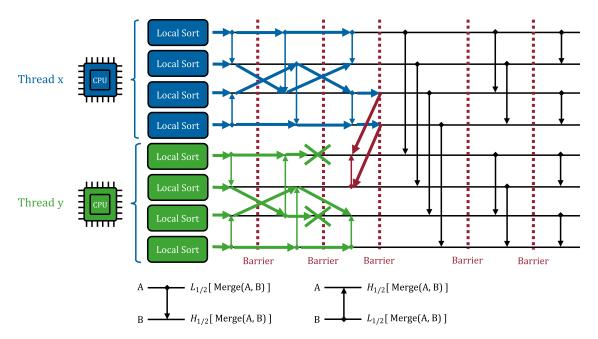

| 6.6  | Non-blocking parallel bitonicsort example                                          | 56 |

| 6.7  | Bitonicsort performance behavior in terms of input size                            | 58 |

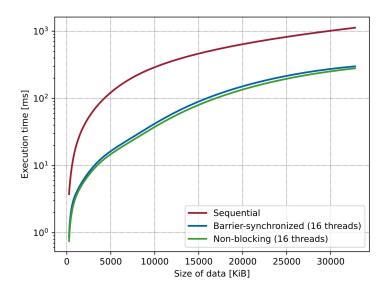

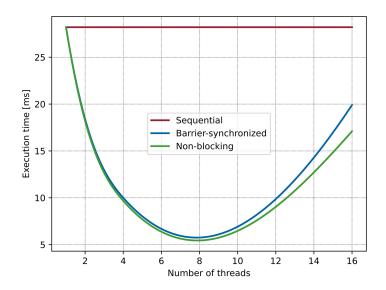

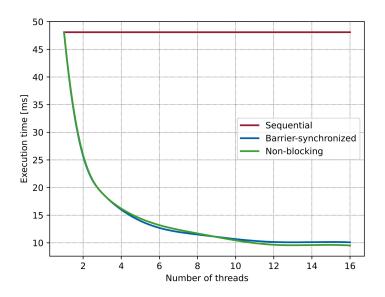

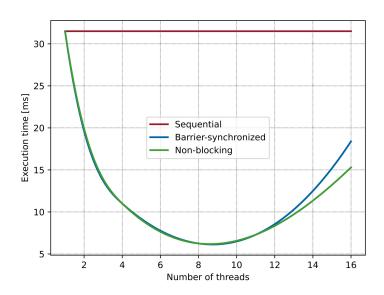

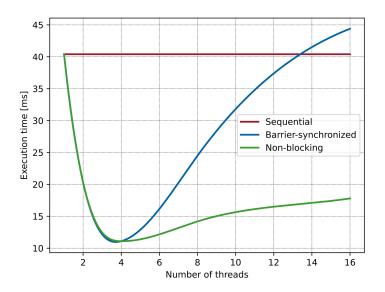

| 6.8  | Bitonicsort performance behavior in terms of number of threads                     | 59 |

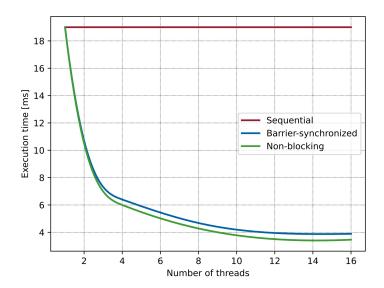

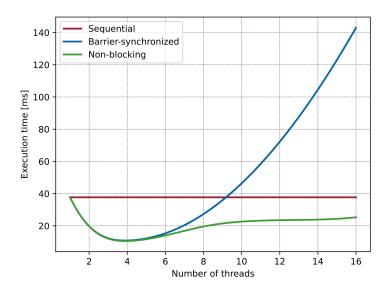

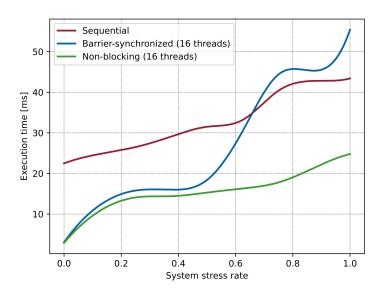

| 6.9  | Bitonicsort performance behavior in terms of system stress rate                    | 60 |

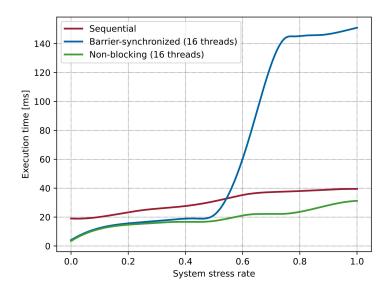

| 6.10 | Bitonicsort performance robustness at 50% system stress rate                       | 61 |

| 6.11 | Bitonicsort performance robustness at 75% system stress rate                       | 61 |

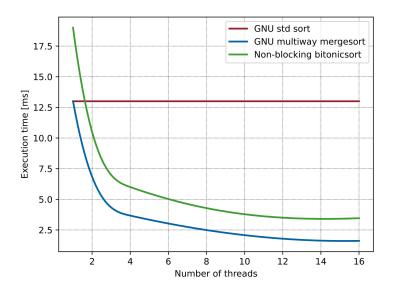

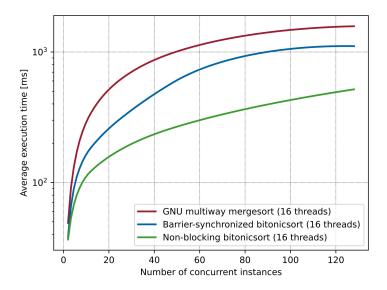

| 6.12 | Bitonicsort and Multiway Mergesort varying the number of threads                   | 63 |

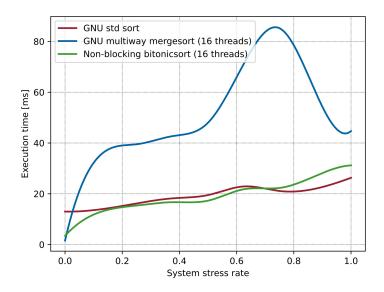

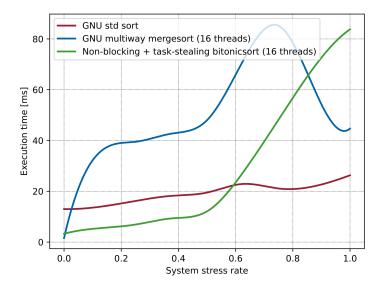

|      | Bitonicsort and Multiway Mergesort varying the system stress rate                  | 64 |

|      | Bitonicsort and Multiway Mergesort varying the number of concurrent instances.     | 64 |

| 6.15 | Odd-even transpose pattern for an arbitrary sequence divided into segments         | 65 |

|      | Barrier-synchronized parallel odd-even transposition sort example                  | 66 |

|      | Non-blocking parallel odd-even transposition sort example                          | 68 |

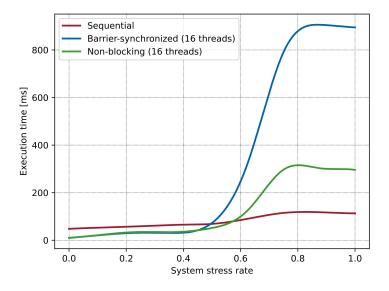

|      | Odd-even sort performance behavior in terms of number of threads                   | 71 |

|      | Odd-even sort performance behavior in terms of system stress rate                  | 71 |

|      | Odd-even sort performance robustness at 50% system stress rate                     | 72 |

|      | Odd-even sort performance robustness at 75% system stress rate                     | 72 |

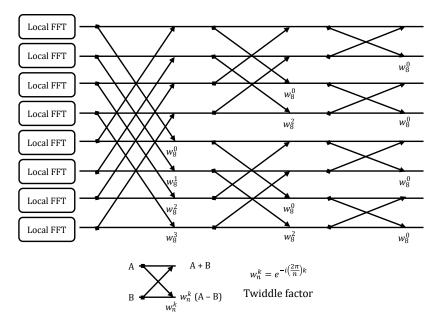

|      | FFT algorithm pattern for an arbitrary sequence divided into segments              | 74 |

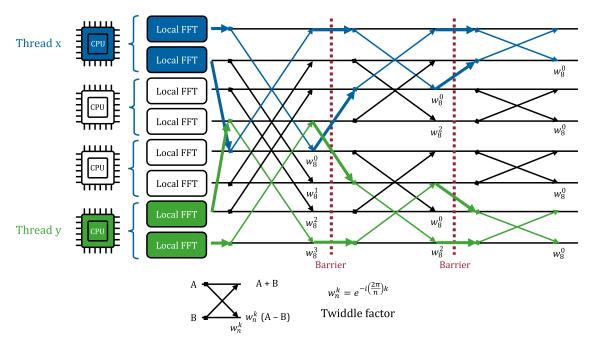

|      | Barrier-synchronized parallel FFT example                                          | 76 |

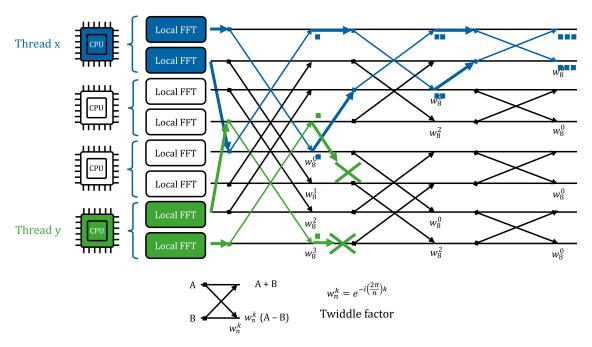

|      | Non-blocking parallel FFT example                                                  | 77 |

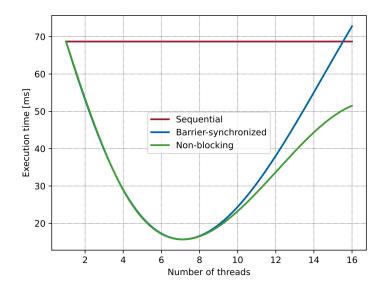

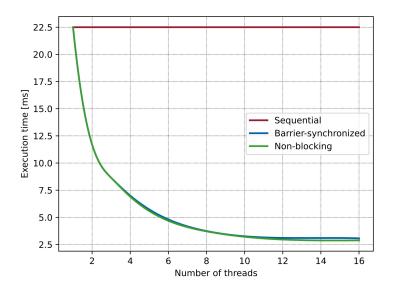

|      | FFT performance behavior in terms of number of threads                             | 79 |

|      | FFT performance behavior in terms of system stress rate                            | 79 |

|      | FFT performance robustness at 50% system stress rate                               | 80 |

| 6.28 | FFT performance robustness at $75\%$ system stress rate                            | 81 |

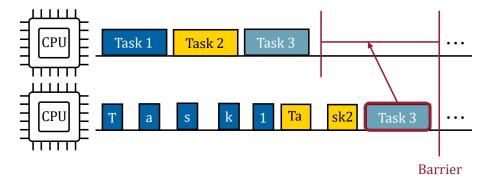

| 7.1  | Task-stealing model                                                                | 83 |

| 7.2  | Stealing-barrier parallel bitonicsort example                                      | 85 |

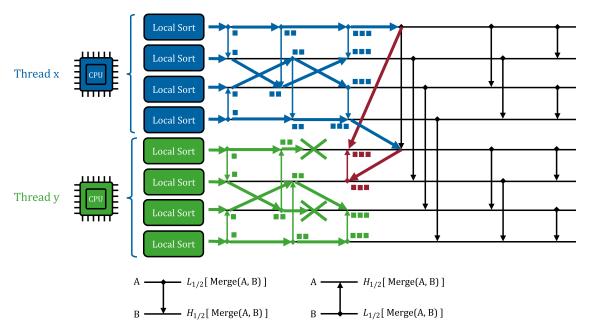

| 7.3  | Wait-free parallel bitonicsort example                                             | 87 |

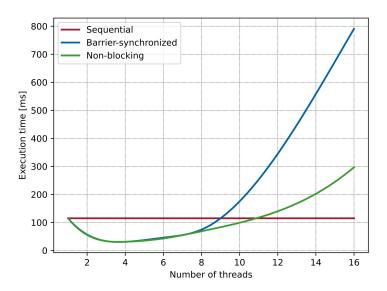

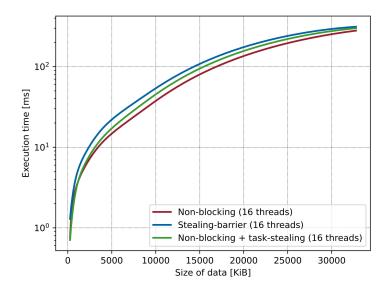

| 7.4  | Task-stealing bitonicsort performance behavior in terms of input size              | 89 |

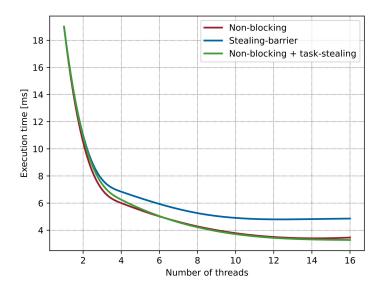

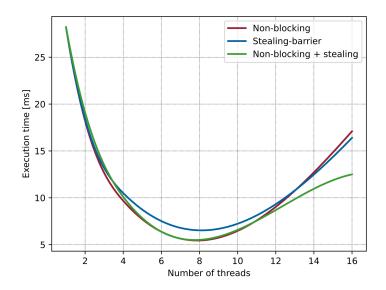

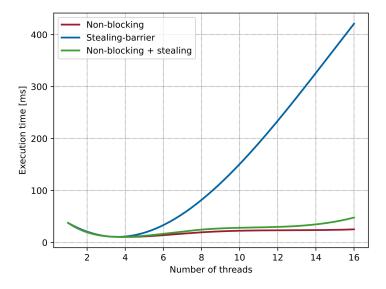

| 7.5  | Task-stealing bitonicsort performance behavior in terms of number of threads.      | 90 |

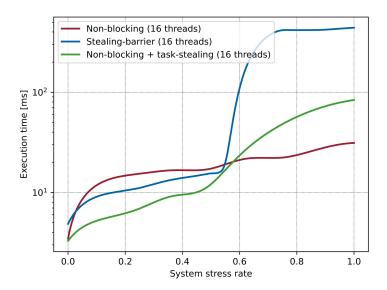

| 7.6  | Task-stealing bitonicsort performance behavior in terms of system stress rate.     | 91 |

| 7.7  | Task-stealing bitonics<br>ort performance robustness at $50\%$ system stress rate. | 92 |

| 7.8  | Task-stealing bitonics<br>ort performance robustness at $75\%$ system stress rate. | 92 |

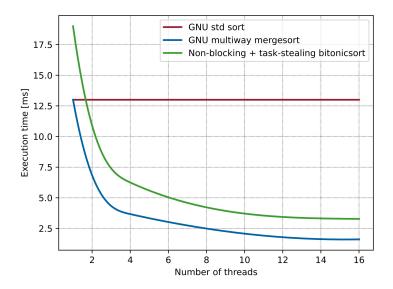

| 7.9  | Wait-free Bitonicsort and Multiway Mergesort varying the number of threads.        | 94 |

| 7.10 | Wait-free Bitonicsort and Multiway Mergesort varying the system stress rate.       | 94 |

## LIST OF TABLES

|     |                                                                             | Pag | e |

|-----|-----------------------------------------------------------------------------|-----|---|

| 2.1 | Taxonomy of thread progression guarantees                                   | 1   | 0 |

| 4.1 | Summary of related work in barrier synchronization                          | 39  | 9 |

| 5.1 | Differences between barrier-based and NBD $^2$ BS-based parallel algorithms | 4   | 7 |

| 8.1 | New summary of related work in barrier synchronization                      | 9   | 6 |

# LIST OF ALGORITHMS

|   |                                                             | Page |

|---|-------------------------------------------------------------|------|

| 1 | Central counter barrier implementation                      | . 21 |

| 2 | Blocking barrier bitonicsort implementation                 | . 55 |

| 3 | Non-blocking bitonicsort implementation                     | . 57 |

| 4 | Blocking barrier odd-even transposition sort implementation | . 67 |

| 5 | Non-blocking odd-even transposition sort implementation     | . 69 |

| 6 | Blocking barrier FFT implementation                         | . 76 |

| 7 | Non-blocking FFT implementation                             | . 78 |

| 8 | Stealing-barrier bitonicsort implementation                 | . 86 |

| 9 | Wait-free bitonicsort implementation                        | . 88 |

## **ACKNOWLEDGMENTS**

I would like to thank a lot of people, this work would not have been possible without you.

First and foremost, I thank my advisor Isaac D. Scherson. Thank you for your friendship. Thank you for taking me on as your student and for believing in me throughout this process. This dissertation is the result of your constant guidance and I will forever be grateful.

Thank you Prof. El Zarki and Prof. Givargis, for serving as members of my dissertation committee and helping improve this work. Thank you Prof. Shindler, for taking me as your Teaching Assistant. I enjoyed and learned a lot working with you.

Thanks to my family and friends. To my parents, Tirzo and Rosalinda, I cannot overstate how important your support has been to me. You have always been a lifeline during challenging times and there are no words to thank you enough. To my brothers, Alejandro and Alberto. You have always been a pillar and have enriched my life in countless ways. To Melina, thank you for motivating me to keep pushing in this journey. Your help and support has been unparalleled. To all my friends, thank you for the good times. I will always cherish every moment.

Also, I would like to acknowledge the sources of funding that made this dissertation possible. To the department of Computer Science for their support in the form of Teaching Assistantships and thanks to the Consejo Nacional De Ciencia y Tecnología (CONACYT) for their additional financial support during my first four years of doctoral studies.

Finally, the formatting of this dissertation is based on Lars Otten's LaTeX template [74], thanks to everyone that has contributed to it over the years.

#### VITA

## Arturo Garza Rodriguez

#### **EDUCATION**

Doctor of Philosophy in Computer Science2023University of California, IrvineIrvine, CaliforniaMaster of Science in Computer Science2020University of California, IrvineIrvine, CaliforniaBachelor of Science in Telematics Engineering2015Instituto Politécnico NacionalMexico City, Mexico

#### RESEARCH EXPERIENCE

Graduate Research Assistant

University of California, Irvine

2018 – 2023

Irvine, California

#### TEACHING EXPERIENCE

Teaching Assistant

University of California, Irvine

2018 – 2023

Irvine, California

#### ENGINEERING EXPERIENCE

Software Engineering Intern Summer 2022 Google Irvine, California Software Engineering Intern **Summer 2021** Google Irvine, California Software Engineering Intern Summer 2020 Google Irvine, California Student Software Developer **Summer 2019 CERN** Irvine, California **Programmer Analyst** 2015 - 2018Oracle Guadalajara, Mexico

#### REFEREED PUBLICATIONS

Non-blocking Technique for Parallel Algorithms with December 2021 Global Barrier Synchronization

International Conference on Computational Science and Computational Intelligence

Recursive MaxSquare: Cache-friendly, Parallel, Scalable in situ Rectangular Matrix Transposition

International Conference on Computational Science and Computational Intelligence

SIMD-node Transformations for Non-blocking Data September 2020 Structures

International Conference on Parallel Processing and Applied Mathematics

## ABSTRACT OF THE DISSERTATION

Performance-robust, Non-blocking, Data-driven Barrier Synchronization for Multicore, Multithreaded Parallel Algorithms

By

Arturo Garza Rodriguez

Doctor of Philosophy in Computer Science

University of California, Irvine, 2023

Professor Isaac D. Scherson, Chair

In a general-purpose multicore multithreaded parallel environment, multiple threads work simultaneously to finish a task faster. Usually, threads need to communicate with each other due to the need to share data or synchronize access to shared data. Communications commonly occur when threads need to wait for the computational results of other threads before continuing their own computations; all necessary data dependencies need to be met before subsequent computations take place.

A barrier is a synchronization construct that enforces a collective pause and data sharing at a given execution point between all participating threads of a parallel computation. No thread proceeds beyond a barrier until all other threads have reached it. However, in a general-purpose system where many processes compete for the available computational cores, a scheduler decides which thread gets a core to execute its next line of code. The barrier can easily become a performance bottleneck due to its global blocking nature: one preempted thread blocks the progress of all other threads that are waiting at a barrier.

This dissertation introduces a novel technique that changes the global nature of the barrier into a distributed data-driven synchronization model with non-blocking thread progression guarantees. The idea is to exploit the algorithm-based memory access patterns to extract

peer-to-peer interthread communication and remove the explicit use of a barrier synchronization construct. Our proposed technique is experimentally validated. The results are promising and show considerable robustness in performance as opposed to their barrier-based algorithm counterparts.

# Chapter 1

## Introduction

Prophets have voiced the contention that the organization of a single computer has reached its limits and that truly significant advances can be made only by interconnection of a multiplicity of computers.

Gene Amdahl

Multicore CPU architectures are a pillar in modern computing platforms. However, it is not straightforward to efficiently exploit the underlying parallelism that the hardware provides. This has brought considerable attention to this research field.

One of the most common forms of parallelism for these modern computer architectures is the Single Program Multiple Data (SPMD) model. The SPMD model splits a task into multiple identical execution threads that will run simultaneously on multiple CPU cores and, usually, work on disjoint subsets of data. Generally, these programs are written in sequential languages extended with communication and synchronization primitives, with barrier synchronization being one of the most common constructs for synchronizing parallel programs. Also, these parallel algorithms exhibit data dependencies at different points in time within their implementations; and threads may need to wait for the results produced by other threads. A barrier is a synchronization construct that forces an execution thread to wait until all participating threads reach the same barrier. The necessity for barrier synchronization arises from the algorithmic data dependencies requirements.

Communicating and synchronizing multiple execution threads present significant challenges. Modern CPUs are powerful out of order execution engines, there are features like branch prediction, instruction prefetching, store buffering, and others that accelerate the computations of sequential programs. However, these features may represent major drawbacks when multiple threads try to work collectively.

Additionally, these systems are not designed to execute just specific types of workloads, they are also formidable general purpose engines that execute large volumes of diverse tasks. The oversubscribed nature of multicore computing platforms impose additional difficulties since a CPU core is now a resource that needs to be shared between multiple threads that are just waiting to be executed. The overall performance of a parallel application may suffer significantly when multiple threads are waiting for the result of the computations of another thread that is yet to be assigned for execution on a CPU core.

This work presents a model that addresses the previously mentioned deficiency and provides performance robustness to parallel tasks with data dependencies that require barrier synchronization. By exploiting the memory access patterns, our data-driven model confers better thread progression guarantees against the oversubscribed blocking nature of modern multicore computing platforms. The rest of the thesis is organized as follows.

Chapter 2 presents the preliminary information, concepts, definitions, and terms that are necessary in order to introduce the rest of the material. It explores the notion of parallel computing and its taxonomy, a classification of the different types of thread progression guarantees that have been proposed, and a deeper insight into barrier synchronization.

Chapter 3 illustrates the challenges to overcome and the embodiment for the rest of this work. It presents the target architecture, its capabilities, its limitations, how barrier synchronization can be achieved, and the main complications faced by parallel multithreaded applications.

Chapter 4 gathers and summarizes a thorough study in all the related work that has been performed so far to address the challenges stated in chapter 3. The summary is organized in two major categories. One to address the overhead introduced by barrier synchronization constructs and how to mitigate it. The second one shows how to design parallel algorithms that are more tolerant to unexpected system delays.

Chapter 5 presents the main contribution of this dissertation: the non-blocking data-driven barrier synchronization (NBD<sup>2</sup>BS) model. The general idea is to exploit the fixed memory access patterns that are exhibited in some parallel algorithms. This, in order to generate peer-to-peer communication and synchronization schemes, instead of using blocking barrier synchronization constructs.

Chapter 6 is the experimental verification of the proposed model. We devised novel non-blocking implementations of important algorithms that are core computational tasks in the fields of parallel sorting and signal processing that can be attractive to other research areas.

Chapter 7 motivates future work towards wait-free barrier synchronization. A multithreaded task-stealing model is proposed and the experimental results are promising to keep exploring more efficient methods.

Finally, chapter 8 presents the concluding remarks, emphasizing the impact of our contributions and motivating the future opportunities in this research field.

# Chapter 2

# **Preliminaries**

If I have seen further, it is by standing on the shoulders of giants.

Isaac Newton

The advent of multicore parallel computing has become a revolution, enabling new technology advances and delivering high performance to the most demanding applications. Over the years, this research field has been widely studied: from the design and implementation of novel parallel computer architectures, all the way to unprecedented approaches to solve massively large problems.

However, only one thing is certain, the field of parallel computing is in constant evolution with different goals in mind; including, but not limited to: improving performance, reducing costs, using multiple computational resources effectively, and ease of programming. This chapter presents the necessary concepts to introduce the rest of the dissertation and serves as a guideline of the main areas in which this thesis contributes to the field of computer science.

## 2.1 Multicore Parallel Computing

Parallel computing is the art of solving a problem by decomposing it into smaller subproblems and solving them simultaneously using multiple computational resources. It is a necessity in problems and tasks that would otherwise take a long time to complete. With claims in the past few years of the deceleration of Moore's law [50], the need for and popularity of multicore parallel computers has been steadily increasing.

Arguably, one of the most important turning points in parallel computing is the Gustafson's correction [36] to Amdhal's law [7], where the benefits of using multiple computational resources to solve large problems was shown. Michael Flynn introduced a taxonomy of computing systems [30] that has been highly adopted ever since, which includes Single Instruction Multiple Data (SIMD), Multiple Instructions Single Data (MISD), and Multiple Instructions Multiple Data (MIMD) to help classify parallel computing systems.

SIMD-type systems refer to the so-called data-parallelism or vector-parallelism, where the granularity of the computation is at the instruction level. The same instruction is executed simultaneously across multiple pieces of data. Whereas, MISD-type systems refer to multiple different instructions working on a single data stream. A simple example of a MISD computational model is an instruction pipeline where each stage of the pipeline executes, simultaneously, a different instruction over the same data pool. MIMD-type systems extend the MISD model, multiple instructions are being independently executed over different pieces of data and most modern general-purpose processors follow this model.

Throughout the years, MIMD-type computers have been in the vanguard of research efforts. Multiple interconnected processing units (cores) executing independent instruction streams and working cooperatively to solve a given problem. Consequently, recent advances focus on increasing the available parallelism and exploiting such parallelism is at the forefront of modern computing challenges [40, 58].

One fundamental characteristic of multicore systems is the utilization of a shared memory address space. Applications running on such systems exploit their parallelism by using more than one core at the same time. By sharing a common memory address space, multicore processors facilitate data sharing across all cores. It provides low latency and high bandwidth for communication, making them ideal for high performance computing.

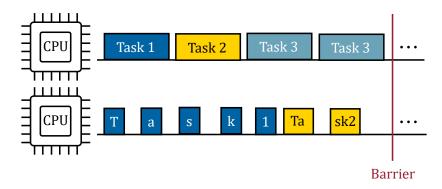

Programming parallel algorithms in multicore systems is relatively straightforward. It is similar to writing sequential programs, but multiple identical copies of the same program run simultaneously on different cores and they usually work on disjoint sets of data. This parallel computational model was introduced as Single Program Multiple Data (SPMD).

## 2.2 Single Program Multiple Data (SPMD)

The Single Program Multiple Data (SPMD) parallel computational model was originally devised by Frederica Darema [20, 21, 22]. This model was first developed as an effort to pursue low-overhead, ease of programming, and high-cooperative parallelism. The premise to maximize cooperativeness is based on that all processing units execute the same stream of instructions; the same computer program. It is often referred to as an execution thread. Without loss of generality, a thread can be defined as a lightweight process and as the smallest unit of execution of the SPMD model.

SPMD-type parallelism is sometimes considered a generalized version of the SIMD-type or vector-type parallelism, since SPMD becomes SIMD at its minimum possible program size: one instruction. Another way to think about it is that if all SPMD programs are executed in lockstep, then it becomes SIMD. This is one of the most important characteristics of the SPMD model, there is no restriction about which instruction is executed at any point in

time. Multiple threads can be executing different instructions of the same program at the same time and not necessarily moving at the same step.

The described behavior has been also widely studied and it is a research field in its own right. *Concurrency*, then, can be defined as a composition of multiple independent threads. This is, any thread can execute any given instruction at any given point in time.

Furthermore, the SPMD model is also considered more general than the SIMD model in the data spectrum, since each thread is not limited to act on different and disjoint pieces of data; creating contention and consistency problems when some pieces of data are shared across multiple execution threads. Hence, heavily impacting and degrading the performance and scalability of parallel applications.

The SPMD model has been widely adopted and several state-of-the-art parallel programming environments are based on SPMD: OpenMP [91], MPI [90], and multithreading techniques are just a few. SPMD proved that it is straightforward to map parallel applications into parallel machines, but imposes significant challenges as well; including, but not limited to: communication and synchronization among multiple execution threads.

## 2.3 Concurrent Computations and Synchronization

Synchronization refers to the use of mechanisms or techniques to impose or constraint some order in the operations performed by multiple concurrent threads. In other words, it is a consensus problem, where all involved participant threads need to agree in the order of their actions. In a system with multiple threads, getting all of them to observe the same order of events is a very difficult task [55].

There is an unpredictable nature about when an operation or event can occur or be observed among multiple independent execution threads. It is not hard to imagine a scenario where one action takes place in a particular thread, but it does not communicate it properly to the rest of them. It is possible, that from another thread's point of view, this action never takes place or it just happens after another series of events.

**Definition 2.1.** A "happened before" time ordering relation between two events, "a" and "b", of a system is the smallest relation satisfying the following three conditions:

- 1. If "a" and "b" are events in the same thread, and "a" comes before "b", then "a" happens before "b".

- 2. If "a" is the sending of a message by one thread and "b" is the receipt of the same message by another thread, then "a" happens before "b".

- 3. If "a" happens before "b" and "b" happens before "c", then "a" happens before "c".

Two distinct events "a" and "b" are said to be concurrent if no "happened before" relationship can be established between them.

Leslie Lamport formalized this notion of time in multithreaded systems [55]. The idea that a certain event can happen before another must be specified in terms of events that are observable within the system and not just in terms of physical theories about an event happening at an earlier time than other event. Lamport also devised one of the concepts that refer to the correctness properties of parallel and concurrent algorithms [56]. The sequentially consistent concept states that the result of any concurrent execution is the same as if the operations of all threads were executed in some sequential order and the operations of each thread appear in this sequence in the order specified by its program. Sequential consistency has been widely adopted and it is arguably one of the most common ways to corroborate the correctness of multithreaded algorithms.

**Definition 2.2.** Sequential consistency states that the result of an execution is the same as a single interleaving of sequential, program-order memory accesses from different threads.

In the context of shared memory multicore systems, one thread sending a message to another thread is implicit and transparent via memory access instructions (read and write). The sending of a message by one thread is performed via writing into memory and the receipt of the same message by another thread is done by reading from memory.

**Definition 2.3.** Concurrent shared memory computing consists of multiple threads, each of which is a sequential program on its own right. These threads communicate by calling methods of objects that reside in a shared memory. Threads are asynchronous, meaning that they run at different speeds, and any thread can halt for an unpredictable duration at any time.

Multicore systems are naturally concurrent, the operations performed by the many threads running in the different cores can interleave arbitrarily and halt unpredictably. Multiple synchronization mechanisms with different goals in mind have been proposed [44]. The next section presents a model to classify different synchronization mechanisms on how the behavior of one thread can have an effect on the execution of other threads.

## 2.4 A Thread Progression Model

Maurice Herlihy and Nir Shavit [39, 41, 43, 44] proposed and formalized a widely adopted taxonomy of multithreaded systems based on the progression guarantees that each of the threads exhibit. These thread progression guarantees are classified based on the ability of each thread to take steps towards its completion regardless of the progress of the rest of the threads, see table 2.1.

The concepts illustrated in table 2.1 will be explained by means of example. Without loss of generality, assume we are required to devise a mechanism to solve one of the oldest problems in synchronization: *mutual exclusion*. In order to protect a shared computational resource, often referred as *critical section* (CS), from multiple threads accessing it at the same time.

|                             | Blocking           | Non-blocking |

|-----------------------------|--------------------|--------------|

| Some threads make progress  | Deadlock-freedom   | Lock-freedom |

| Every thread makes progress | Starvation-freedom | Wait-freedom |

Table 2.1: Taxonomy of thread progression guarantees.

**Definition 2.4.** Mutual exclusion is when critical sections of different threads do not overlap. For threads A and B, and integers j and k, either  $CS_A^k$  happened before  $CS_B^j$  or  $CS_B^j$  happened before  $CS_A^k$ ; where  $CS_A^k$  is the interval during which A executes the critical section for the k-th time.

One way to solve the mutual exclusion problem is to let threads compete for a *lock*, which is a construct that a thread can acquire in one indivisible step (*atomic read-modify-write memory operation*). Then, the first thread to acquire the lock is the one who wins access to the shared resource. Otherwise, if a thread fails to acquire the lock, it keeps trying until success. This technique is considered to be *deadlock-free* because at least one thread makes progress towards the shared resource and eventually another thread might gain access to the shared resource when the lock becomes available again.

**Definition 2.5.** Deadlock-freedom guarantees that if some thread attempts to acquire the lock, then some thread will succeed in acquiring the lock. If a thread calls acquire\_lock() but never acquires the lock, then other threads must be completing an infinite number of critical sections.

However, there is no guarantee that all involved threads will actually gain access to the shared resource; with just a little bit of bad luck, a thread might never win a contention match to acquire the lock. Hence, it is not considered *starvation-free*.

**Definition 2.6.** Starvation-freedom guarantees that every thread that attempts to acquire the lock eventually succeeds. Every call to acquire\_lock() eventually returns. This property is sometimes called lockout-freedom.

A different way to approach mutual exclusion, with starvation-freedom progression guarantees, is to enqueue each thread in order to gain access to the shared resource. This fairness mechanism guarantees that all threads eventually will make progress towards the shared resource. Nevertheless, it is important to point out that a stronger progression guarantee does not necessarily imply better performance. The introduction of the queue might slowdown the overall performance, but it ensures that all threads will eventually acquire the lock.

An important aspect of deadlock-freedom and starvation-freedom is that both continue to block the computational progress of the rest of the threads while they wait for the lock to become available, this is known as blocking synchronization.

**Definition 2.7.** Blocking synchronization comprises techniques used to prevent multiple threads from simultaneously accessing shared computational resources by allowing only a single thread to make progress.

Synchronizing multiple threads using locks is relatively straightforward to reason about. However, threads get blocked under these circumstances and new ways to maximize the available parallelism among multiple threads have become a necessity. Herlihy and Shavit pioneered what is known as *non-blocking synchronization* [39, 41, 43, 44].

**Definition 2.8.** Non-blocking synchronization comprises techniques used to prevent multiple threads from simultaneously accessing shared computational resources without having to block other threads progress.

In non-blocking synchronization there are three different progression guarantees that generally apply to the SPMD parallel model. Each one with better progression guarantees than the previous one. It is said that an operation is *obstruction-free* if a thread makes progress when the rest of the threads do not take any steps in their execution. Then, a *lock-free* mechanism guarantees that at least one thread makes progress. Finally, an operation is *wait-free* if it guarantees that all threads make progress.

**Definition 2.9.** A method is obstruction-free if, from any point after which it executes in isolation, it finishes in a finite number of steps.

**Definition 2.10.** A method is lock-free if it guarantees that infinitely often some method call finishes in a finite number of steps.

**Definition 2.11.** A method is wait-free if it guarantees that every call finishes its execution in a finite number of steps.

These definitions are similar to their blocking counterparts, deadlock-freedom and starvation-freedom. However, non-blocking synchronization algorithms are designed to not block the progress of other threads while executing their own operations. Figure 2.1 presents the complete hierarchy of the different thread progression guarantees.

# Deadlock-freedom Starvation-freedom Obstruction-freedom Lock-freedom Wait-freedom Stronger Guarantees

Figure 2.1: Hierarchy of thread progression guarantees.

To illustrate non-blocking synchronization, the mutual exclusion mechanism will be modified and it will allow multiple read-only threads in the shared resource. This is known as a reader-writer lock. If a thread only wants to read from the shared resource, it may proceed without waiting. On the other hand, if a thread wants to write into the shared resource, it waits until all read-only threads finish. This technique provides wait-free progression guarantees

to all read-only threads. However, a writer thread must compete against all readers in order to access the shared resource and potentially impacting its performance. Ideally, the goal is to maximize progress among multiple threads without side effects; but in practice, this is not easy to accomplish.

This dissertation leverages the same model proposed by Herlihy and Shavit to characterize the different progression guarantees that our proposed technique exhibits. Our target synchronization construct is the so-called *barrier synchronization* and we show how it achieves non-blocking thread progression guarantees.

## 2.5 Barrier Synchronization

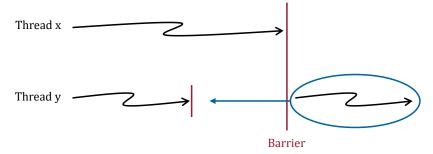

Arguably, the most common construct to coordinate multiple execution threads in the SPMD parallel model is the so-called *barrier synchronization*, ensuring that no thread continues execution beyond a barrier until all other threads reach the same barrier. See figure 2.2.

Figure 2.2: Barrier synchronization.

Barrier synchronization is used to protect the concurrent reads and writes that can happen across multiple iterations or stages of a parallel algorithm. This ensures the correctness of the algorithm by safeguarding the possible data dependencies that the algorithm exhibits. Figure 2.3 shows a general pseudocode snippet of the execution flow of a parallel algorithm where each participating thread needs to complete a series of iterations. The explicit barrier construct ensures that all threads complete their current task before proceeding into the next iteration. An important aspect to point out is that the finer the granularity of the computational task, the more barriers may be necessary.

```

// sequential code

// parallel section

for each thread:

for i in 1 to N:

Task(i)

barrier

// sequential code

```

Figure 2.3: Barrier synchronization pseudocode usage example.

The barrier is the synchronization point where data realignment, repartitioning, and all communication between all participating execution threads takes place. Barrier synchronization points can easily become hot-spots and significantly degrade the performance of parallel applications. The overall performance is limited by the slowest of the threads involved in the computations and a single delayed thread blocks the progress of the rest of the threads.

#### 2.6 Common Terms

- Parallel computing: Art of solving a problem by decomposing it into smaller subproblems and solving them simultaneously using multiple computational resources.

- Single Program Multiple Data (SPMD): Computational model where the same sequences of instructions are executed simultaneously over disjoint sets of data.

- Thread: Smallest unit of execution of the SPMD parallel model.

- Atomic memory operation: Instruction that allows a thread to read, modify, or write memory in one indivisible step.

- Concurrency: Multiple threads can execute multiple operations at any time.

- Synchronization: Art of enforcing some order in the operations of concurrent threads.

- Blocking synchronization: One thread may prevent others from making progress.

- Non-blocking synchronization: One thread may make progress regardless of others.

- Deadlock-freedom: At least one thread makes progress in a finite number of steps, but may prevent others from making progress.

- Starvation-freedom: Each thread makes progress in a finite number of steps, but may prevent others from making progress.

- Obstruction-freedom: Each thread makes progress in a finite number of steps when they are executed in isolation (the rest of threads do not take any steps).

- Lock-freedom: At least one thread makes progress in a finite number of steps.

- Wait-freedom: Each thread makes progress in a finite number of steps.

- Barrier synchronization: One thread waits for all others before resuming execution.

# Chapter 3

# **Problem Statement**

If you were plowing a field, which would you rather use: two strong oxen or 1024 chickens?

Seymour Cray

Barrier synchronization is an algorithmic need in parallel algorithms that are composed of several computational stages. The barrier implementation is critical to deliver high performance. It should be fast, avoid unnecessary overhead, and minimize the time between the last thread reaching the barrier and the last thread leaving the barrier.

In this chapter, the limitations to overcome are presented within the context of the target computer architecture: the Central Processing Unit (CPU) and multicore CPU systems with a shared memory address space. Primarily, there are two major performance troublemakers: the own hardware abilities to guarantee correctness and consistency across all CPUs and the oversubscribed nature of these general-purpose systems where multiple threads compete with each other to execute their next line of code in a CPU core.

## 3.1 Thread-level Parallelism in Multicore CPUs

SPMD parallel algorithms are relatively straightforward to implement in modern multicore CPU architectures: one thread runs in one CPU core. There are several multithreaded programming techniques and libraries that allow programmers to execute the same program (thread) simultaneously across the different CPU cores. However, efficiently exploiting the full parallel capabilities of multicore systems is a hard task.

Figure 3.1: Multicore system architecture.

Multicore systems have many CPUs per physical chip, also known as cores, see figure 3.1. CPUs are powerful out of order execution engines: branch prediction, instruction prefetching, store buffering, speculation, compiler instruction scheduling, and other compiler optimizations are features to make the CPU as fast as possible and most of the time the program is executed in a different order than it was originally written. These features increase the performance of sequential programs, but they do more harm than good to parallel multithreaded SPMD applications where threads need to communicate: remember Lamport's work on correctness of multithreaded systems [55, 56]. The hardware needs to provide additional conditions to guarantee that a computer correctly executes multithreaded programs.

## 3.2 CPU Hardware Capabilities

When threads communicate with each other, they do it via *messages*. Intuitively, due to the out of order execution nature of multicore CPU systems, it is not difficult to imagine a scenario where receiving or sending a message from or to another thread actually happens in a different order than expected and, for that reason, compromising the correctness of the algorithm.

The multiple CPU cores communicate through a complex system of interconnected memories, namely, *caches*. In consequence, receiving and sending messages translates into reading and writing memory, respectively. Instructions that interact with memory are usually more expensive than others that perform simple calculations, even for a single thread.

Memory operations become more expensive when shared among multiple cores, since somehow it is necessary to enforce the correct order when reading and writing memory. All CPU cores maintain their own copy of the piece of shared data and it is stored in what is known as a cache line and it can store multiple elements depending on their size. Then, memory consistency refers to the property where each core must have an up-to-date copy of the shared data. A phenomena known as race condition happens when at least two threads perform memory operations to the same location, one of them is a write, and there is no notion that either of them happened before the other.

**Definition 3.1.** A memory consistency model defines the ordering of externally observable events, i.e. reads and writes to memory. A read operation returns the value of the most recent write operation.

**Definition 3.2.** A race condition occurs when two or more threads access the same memory location, at least one is a write, and no happened before relation can be established between said operations.

In order to overcome all these major drawbacks, the hardware provides different mechanisms to help maintain memory consistency for multithreaded parallel SPMD applications. The most important ones are *cache coherence* protocols, *atomic memory operations*, and *memory fences*. Each of these specifically designed to address a particular problem and each has its own associated performance costs.

#### 3.2.1 Cache Coherence

The cache coherence problem arises because all CPU cores maintain their own copy of shared data in their local cache and at least one core modifies its copy. This action *invalidates* the rest of the copies and creates an incoherent situation. To avoid this, a cache coherence protocol defines a set of rules to maintain consistency across all local copies of shared data.

Each cache line is marked with a given status, most coherence protocols in modern multicore CPUs are based in the MESI protocol, which stands for Modified, Exclusive, Shared, and Invalid. One cache line can transition from one state to another depending on a given action. For example, in *bus interconnected* caches, if one core broadcasts on the bus a request of a cache line in exclusive mode, the other cores, which are constantly *snooping* the bus, will invalidate any copies of that particular cache line.

## 3.2.2 Atomic Memory Operations

An atomic memory operation allows a thread to read, modify, or write memory in one indivisible step. In order to ensure this behavior, the core writing to a piece of shared data must have exclusive access to the specific cache line. This consists in identifying and *locking* the cache lines that contain the shared data. Once the exclusive access is guaranteed, the core can then proceed with its atomic memory operation and relinquish the lock afterwards.

Another important aspect of working with atomic memory operations in shared data is that an update to an individual element of a cache line, *invalidates* the entire cache line. This is particularly harmful when another core wants to read a different piece of data that happens to be stored in the same cache line and needs to wait for the cache line to be valid again, referred to as a *cache miss*. This phenomena is known as *false sharing* and if the cache line gets invalidated frequently, for example in a loop, the performance cost increases.

#### 3.2.3 Memory Fences

Memory fences are used to avoid reordering of memory operations. For example, a store buffer is a First-In-First-Out (FIFO) hardware construct that is used to accelerate the write to memory operations of a single thread. This buffer is smaller than the cache and faster to access. So, whenever a write instruction is issued, the piece of data is written in the store buffer and not directly in the cache. Eventually, the store buffer is flushed and the modified piece of data reaches the cache.

However, in contrast to the cache, the store buffer is also local to the CPU but does not have a coherence protocol with respect to the other store buffers. As a consequence, a write operation that is still in the store buffer has not yet occurred from the perspective of the rest of the threads. A thread that reads the same piece of data will observe a different order of operations than the one that is actually happening in the system. This is known as bypassing the store to load operations and it is common in Total Store Order (TSO) memory consistency models such as x86. To address this problem, a memory fence instruction needs to be issued to force the contents of the store buffer to be flushed into memory.

## 3.3 Barrier Synchronization in Multicore CPUs

Synchronization can be achieved via *busy-wait* techniques. One thread is constantly checking a piece of shared data to see if certain criteria is met. Only then, the thread may proceed with its computations.

To implement a barrier synchronization construct, it is necessary to consider how to properly signal all the threads that are involved in the parallel execution. First, a thread should announce when it reaches the barrier and, second, a thread should know when to leave the barrier. Algorithm 1 presents a pseudocode implementation of a *central counter* barrier.

#### **Algorithm 1** Central counter barrier implementation.

```

1: procedure Wait(atomic &thread_count, atomic &global_flag)

2:

this\_thread\_flag = load(\&global\_flag)

this_thread_position = fetch_and_sub(&thread_count, 1)

3:

4:

▶ Last thread reaches the barrier

if (this\_thread\_position == 1)

5:

store(&thread_count, total_number_of_threads)

6:

store(&global_flag, ~this_thread_flag)

7:

8:

else

while (load(&global_flag) == this_thread_flag)

▶ Wait for last thread

9:

vield_cpu()

10:

```

The central counter barrier has two pieces of data that are shared between all participating threads. These two variables are marked as atomic: the thread count is used to signal that a thread has reached the barrier and the global flag is employed to notify threads to leave the barrier.

Whenever a thread reaches the barrier, it atomically decreases the thread count and, if it is not the last thread that reaches the barrier, it waits for the last thread to flip the global flag by constantly and atomically reading the flag value. Otherwise, if the thread that reaches the barrier is the last one, it then atomically resets the thread count and flips the global flag so the other threads can leave the barrier.

It is important to mention that when a thread waits for synchronization, it can basically engage in only one of two different behaviors (line 10 of algorithm 1): *active* waiting (consuming CPU cycles) and *passive* waiting (yielding the CPU core to another thread).

**Definition 3.3.** A thread is actively waiting for synchronization if it is constantly consuming CPU cycles without doing any meaningful computation towards completion.

**Definition 3.4.** A thread is passively waiting for synchronization if it yields the CPU and then it is scheduled back at a later time. This, however, requires support from the kernel scheduler and it has no difference from active waiting if there are no threads waiting to be executed.

Nevertheless, none of the two waiting mechanism help to unblock a thread faster while waiting since this totally depends on other threads delays. Yet, algorithms with passive waiting might outperform those with active waiting in scenarios where CPU cores are heavily contended by multiple threads, since there will be threads that have not yet reached the barrier, but they are waiting to be assigned to a CPU core by the kernel *scheduler*. This problem will be discussed in more detail in section 3.4.2.

Algorithm 1, even though it is easy to reason about, may present some inconveniences. One, already mentioned, there is another agent (the scheduler) that may impact parallel multithreaded applications and, second, the inherent overhead of the barrier itself. For example, the complexity of decreasing the thread count grows exponentially with the number of threads trying to access it because the threads need to compete against each other in order to gain exclusive access to the cache line where the variable is stored. This problem will be discussed in more detail in section 3.4.1.

# 3.4 Challenges in Barrier-synchronized Multithreaded Parallel Algorithms

Barriers are widely used and, in parallel algorithms that require multiple of them, it is of utmost importance to minimize their inherent overhead in order to maximize the application performance. The challenges to overcome are the *scalability* of the atomic operations within the barrier implementation and the *unnecessary waiting* that a thread has to endure due to their asynchronous nature, i.e. the execution threads will not reach the barrier at the same time. Being the latter the main problem addressed in this dissertation.

## 3.4.1 Scalability of Atomic Memory Operations

Atomic operations are expensive because the may involve flushing the store buffer, obtaining exclusive access to a cache line, and invalidating other copies of a shared piece of data.

Figure 3.2: Cache line bouncing.

Imagine a scenario where we want to implement a concurrent counter. This counter is shared among multiple execution threads and each thread increments the count by one. This is not trivial to do so. In order for a thread to correctly increase the count, it needs to consider all the hardware limitations to make sure that each increment is *consistent*.

Each thread running in a CPU core will update its local copy of the counter and will invalidate the rest of the copies. The most up-to-date copy of the counter will be moving from cache to cache so that each thread correctly increments its own copy of the value, figure 3.2. This phenomena is known as *cache line bouncing* and results in poor performance, figure 3.3.

Figure 3.3: Atomic increment scalabilty in x86.

When a CPU reads an invalid cache line, it waits for the most up-to-date value from another CPU cache and only then proceed with its computations. This is known as a *cache miss* and they are one of the major obstacles in CPU performance.

## 3.4.2 Blocking Due to Unexpected System Delays

Unexpected delays are common due to the asynchronous nature of multicore systems, hence breaking the ideal computational model where all threads reach the barrier at the same time, figure 3.4. In modern multicore systems, some of the common culprits are, but not limited to: cache misses, page faults, clock rates, network, I/O, and interruptions.

However, a CPU is also a shared resource. An execution thread is assigned to a CPU core by the operating system kernel *scheduler*, but this thread can also be *preempted* and give up the CPU to another thread. This phenomena is known as *context-switching* and it can severely degrade the performance of barrier-synchronized multithreaded parallel SPMD programs. It is not hard to imagine a scenario where a preempted thread will block the progress of all the threads that are already waiting at the barrier, see figure 3.5. Hence, heavily impacting the overall execution time of a parallel application.

Figure 3.4: Waiting for slowest thread.

Figure 3.5: Blocking the overall task.

This is the main problem that this dissertation addresses. Thread preemption is very likely to happen due to the oversubscribed nature of modern multicore systems. The number of threads from different programs that are being executed is much greater than the number of physical CPU cores.

When developing parallel solutions, it is natural to try to use all available physical CPU cores in order to take full advantage of the parallelism offered by the hardware. These programs run in what is called *user space* and all hardware resources are managed by the operating system *kernel*, see figure 3.6. These resources include, but are not limited to: scheduling threads to CPU cores, memory management, I/O, interruption handling, etc. It is noteworthy to clarify that the software stack levels are independent of each other and one user space program can only interact with whatever kernel space provides. For example, it is not possible to avoid thread preemption from user space.

Figure 3.6: Kernel scheduler could be an adversary.

As a consequence, the kernel scheduler could be consider as a non-deterministic adversary that can block the execution of all threads of a parallel application and, overall, degrade its performance. Figures 3.7 and 3.8 respectively show what an ideal computational model looks like and what actually occurs in reality where a thread is preempted and tasks partitioned at any time, so the CPU can be shared with other programs.

The only assumption we make about the underlying scheduler is that eventually all threads will be scheduled for execution. This dissertation contributes with a novel *scheduler-oblivious* and *preempt-robust* technique to provide performance-robustness and non-blocking thread progression guarantees to barrier-synchronized multithreaded parallel SPMD applications.

Figure 3.7: Ideal barrier-synchronized parallel computational model.

Figure 3.8: Real barrier-synchronized parallel computational model.

# Chapter 4

# Related Work

I know of no way of judging the future but by the past.

Patrick Henry

Past literature has given great attention to barrier synchronization primitives and their implementations. It has been shown how barriers can easily become a hot-spot in parallel applications due to the challenges presented in section 3.4. Research in barrier synchronization has targeted different ways to avoid the performance degradation caused by atomic operations and unexpected system delays.

This chapter includes a summary of the related work in the field. In section 4.1, a variety of different barrier synchronization implementations are presented: counter barriers, tree-based barriers, dissemination barriers, and tournament barriers. In section 4.2, a variety of different mechanisms to avoid the unnecessary waiting problem are presented: use of multiple disjoint barriers, fuzzy barriers, task-stealing barriers, and speculative barrier synchronization. Other proposals are based on these techniques or they solve the barrier synchronization problem by leveraging additional, but sometimes unpractical, hardware support [1, 2, 25, 31, 45, 78].

# 4.1 Scaling Barrier Synchronization

Barriers are commonly used across stages of data parallel algorithms in order to protect data dependencies between those stages. One research goal is to reduce the associated cost of the atomic memory operations that take place to ensure algorithmic correctness and to notify other threads when they reach the barrier.

The barrier implementations that rely on busy-waiting (spinning) in a global flag produce high amounts of memory and interconnection network contention that significantly impact the performance of parallel applications. Thus, research on the field aims to improve the locality of reference of atomic operations in pursuance of decreasing the inherent overhead of the barrier synchronization construct.

### 4.1.1 Counter Barriers

Counter-based barriers have been widely studied [38, 44, 61, 66, 67, 73, 76, 87, 99]. They are conceptually simple and straightforward to think about. However, they can suffer from high contention problems in central shared counters.

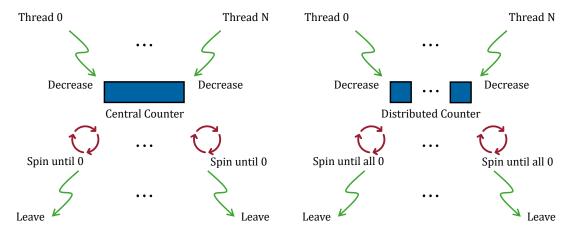

Figure 4.1: Central counter barrier.

Figure 4.2: Distributed counter barrier.

In a central counter barrier, figure 4.1, the value of the counter is initialized to the number of execution threads that are participating in the parallel computations. When a thread reaches the barrier, it decreases the value of this counter and then waits (spins) until it becomes zero. This means that the last thread from the execution group has reached the barrier.

On the other hand, distributing the shared counter across local counters in each participating thread, figure 4.2, helps to avoid contention in a central counter. The downside of this implementation is that threads waiting at the barrier need to verify that all local counters of all participating threads have reached zero so they can proceed.

### 4.1.2 Tree-based Barriers

Tree-based barriers have been widely studied [8, 38, 44, 47, 66, 67, 69, 87, 98, 99]. The general idea behind a tree-based barrier is to distribute the signaling between threads in a tree-like fashion, where threads are assigned to nodes in a tree with notifications going up and down whenever a thread reaches the barrier. This, in order to alleviate the contention that is commonly presented in their central barrier counterparts. Some important contributions are the static-tree barrier [44], the combining-tree barrier [98], and the MCS (Mellor-Crummey and Scott) barrier [66].

In the combining-tree barrier, the execution threads are organized in groups of k and each group is assigned to a leaf of a k-ary tree. When a thread reaches the barrier, it performs an increment operation in a local counter of its own group. The last thread of the group continues up the tree by updating the count of the node's parent. This eventually propagates the updates to the root of the tree when the last thread of all groups reaches the barrier. Finally, a series of notifications are propagated down the tree so the waiting threads wake up and continue execution.

In the MCS barrier, to synchronize k threads, the barrier employs a pair of k-node trees, an arrival, and a wake-up tree. The general idea is that when a thread reaches the barrier, it sets a flag in its parent node in the arrival tree and gets notified by its parent in the wake-up tree when all threads have reached the barrier. This way, any given thread (at a node) does not modify nor test any other nodes rather than its parent or its children, leveraging the importance of locality of reference.

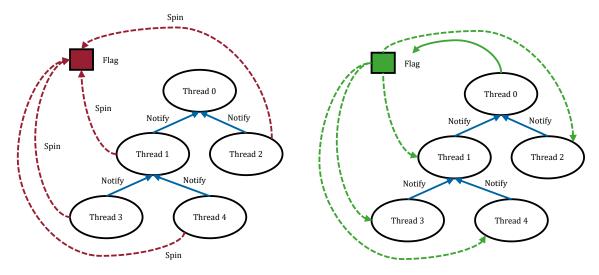

Figure 4.3: Wait at the static-tree barrier. Figure 4.4: Leave the static-tree barrier.

Finally, the static-tree barrier is a great pedagogical example, and it will be used to show the importance of tree-like barriers in a more detailed way. Figures 4.3 and 4.4 help exemplify. Same as the MCS barrier, each thread is statically assigned to a node in the tree. This is, k nodes to synchronize k execution threads and each node has an associated count to it, which is the number of children that have not yet reached the barrier. When a thread reaches the barrier: if its local counter is 0, it means that all its children have reached the barrier, so it notifies its parent node by decreasing the local counter of the parent and it waits by spinning on a global flag (figure 4.3). Otherwise, the thread waits locally until its local counter becomes 0. Eventually, the root counter will become 0 and this thread is in charge to flip the global flag so the rest of the threads may proceed (figure 4.4).

### 4.1.3 Dissemination Barriers

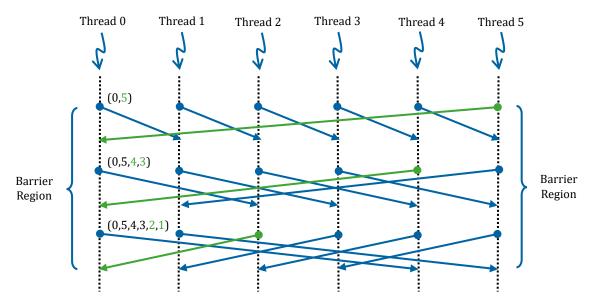

Dissemination barriers are possibly the most widely used barriers in the field thanks to their performance and scalability [13, 31, 38, 66, 67, 70, 78]. First devised by Brooks [13] with a butterfly barrier proposal and then Hensgen et al. introduced the dissemination barrier [38], which enhances the original algorithm with a more efficient synchronization signaling pattern. An example can be found in figure 4.5.

Figure 4.5: Dissemination barrier.

The main idea is that one thread will signal only another thread in a specific pattern. In the illustrated example, in round j, thread i signals thread  $((i+2^j) \mod k)$  and waits for thread  $((i-2^j) \mod k)$  in order to synchronize k threads. As a result of this, a given thread only needs to wait for another specific thread to move forward within the barrier region requiring only  $\lceil \log_2 k \rceil$  synchronization rounds. Figure 4.5 shows how thread  $\theta$  is signaled by a specific thread in each round.

The dissemination barriers present characteristics that make them good candidates for shared memory computer architectures where network interconnect accesses can be performed in parallel, due to the nature of its series of symmetric and pairwise synchronization operations.

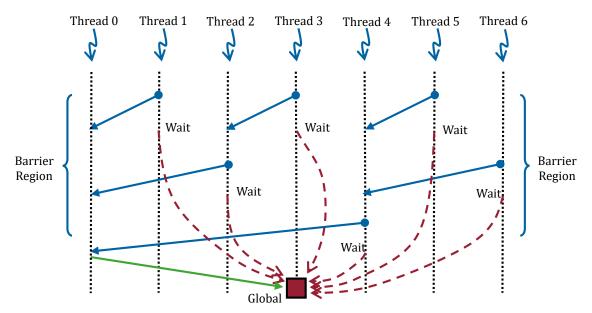

### 4.1.4 Tournament Barriers

Tournament barriers are a form of dissemination barriers where *winner* threads continue to the next round and *loser* threads wait at a global flag. The idea behind these barriers is that only winner threads wait for the signaling of other winner threads.

These type of barriers might be more suitable for different scenarios than their dissemination barrier counterparts, for example, in architectures with a central memory bus where contention in the interconnection network can happen [67]. Figure 4.6 shows an example of a tournament barrier.

Figure 4.6: Tournament barrier.

Lubachevsky [61] and Hensgen et al. [38] first devised the tournament barriers. At each round within the barrier region, a winner thread is statically determined and continues to the next round. Whereas the loser threads spins at the global flag, waiting for thread  $\theta$  to flip it at the end of the synchronization rounds. A tournament barrier, as in the dissemination barriers, requires a total of  $\lceil \log_2 k \rceil$  rounds to synchronize k threads.

# 4.2 Unblocking Barrier Synchronization

Barrier-synchronized parallel algorithms suffer from the global blocking nature of the barrier itself. Section 4.1 shows different ways to implement different barrier synchronization constructs, aiming to reduce their intrinsic overhead.

However, research in non-blocking barrier synchronization and this dissertation have a different goal: allow the necessary system-wide progress of all execution threads without compromising the algorithmic correctness that is enforced by data dependencies.

# 4.2.1 Multiple Disjoint Barriers

If different execution threads do not exhibit data dependencies that will force them to synchronize every time a barrier is used. Disjoint threads can synchronize only among themselves by placing independent barriers for only those threads involved, see figure 4.7.

Figure 4.7: Progress with multiple disjoint barriers.

There are numerous ways to achieve this. The key idea is that each thread must anticipate which other threads are involved at each barrier synchronization.

Logically, separate barriers are assigned to distinct subsets of the input data. As a consequence, a thread needs to know which barrier to reach at each synchronization point. This requires overcomplicated control flows.

Furthermore, it has been shown that a system with N threads, with at most N input data streams, may need at most N-1 barriers [35]. Hence, although the problem is solved and unnecessary barrier synchronization constructs are eliminated, the added complexity in the program's control flow makes this technique exceptionally difficult to maintain and scale to a general model.

### 4.2.2 Fuzzy Barriers

The Fuzzy Barrier was originally devised by Rajiv Gupta in 1989 [35]. The main idea is to extend the barrier concept to include a sequence of statements that a thread can execute while waiting for the others to reach the barrier and necessary data communication, alignment, or partitioning can happen at any time inside the *barrier region*. Ideally, the larger the barrier region, the more likely it is that none of the threads will have to stall.

Figure 4.8: Branches outside barrier. Figure 4.9: Branches inside barrier.

For example, figures 4.8 and 4.10 show a simple case where a thread executes multiple statements with branches and waits for the rest of the threads at the end of each iteration. Without loss of generality, assume that statement S1 takes longer to execute than statement S2. Then, all threads taking the S2 branch will reach the barrier first and stall.

Figure 4.10: Progress with normal barrier. Figure 4.11: Progress with fuzzy barrier.

If the branches are included as part of the barrier region, even if multiple threads take different execution paths, they may not have to stall; see figures 4.9 and 4.11. It is important to point out that both S1 and S2 can be independent of each other, which means that a thread can start its next iteration without waiting for other threads. Note that the data exchange/communication is triggered when the last thread reaches the beginning of its barrier region and all other threads are inside their respective barrier region.

This example shows how the fuzzy barrier provides better protection against the performance degradation that is caused by the unexpected delays of other threads. Data communication can take place at any point in a wider range rather than forcing all threads to do so at a specific point.

The concept of the fuzzy barrier pioneered the idea of exploiting the communication and computation overlap that some parallel algorithms exhibit. Motivating the pursuit of more efficient implementations of parallel algorithms [48, 79, 83].

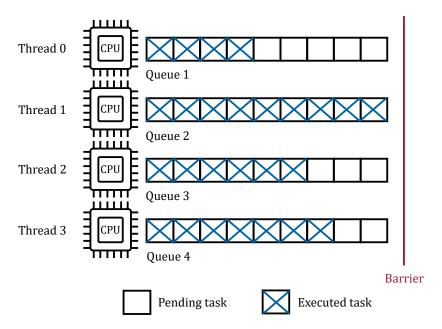

# 4.2.3 Task-stealing Barriers

Task-stealing barriers form part of a broader spectrum of techniques known as *load balancing* [24, 29, 44, 51, 54, 57, 65, 97]. As seen so far, barrier synchronization is used when the

computations of a program are divided into several stages and a given thread waits for the necessary data dependencies in order to proceed to its next stage.