## **UC Irvine**

## **ICS Technical Reports**

#### **Title**

Exploiting iteration-level parallelism in declarative programs

#### **Permalink**

https://escholarship.org/uc/item/0j11x8nt

#### **Author**

Roy, John M.A.

## **Publication Date**

1991

Peer reviewed

#### Department of Information and Computer Science

#### University of California at Irvine

Irvine, CA 92717

Z 699 C3 no.9/-24

# Exploiting Iteration-Level Parallelism in Declarative Programs

John M.A. Roy

March 1991

Notice: This Material may be protected by Copyright Law (Title 17 U.S.C.)

Technical Report #91-24

#### Abstract

In order to achieve viable parallel processing three basic criteria must be met: (1) the system must provide a programming environment which hides the details of parallel processing from the programmer; (2) the system must execute efficiently on the given hardware; and (3) the system must be economically attractive.

The first criterion can be met by providing the programmer with an *implicit* rather than *explicit* programming paradigm. In this way all of the synchronization and distribution are handled automatically. To meet the second criterion, the system must perform synchronization and distribution in such a way that the available computing resources are used to their utmost. And to meet the third criterion, the system must *not* require esoteric or expensive hardware to achieve efficient utilization.

This dissertation reports on the Process-Oriented Dataflow System (PODS), which meets all of the above criteria. PODS uses a hybrid von Neumann-Dataflow model of computation supported by an automatic partitioning and distribution scheme. The new partitioning and distribution algorithm is presented along with the underlying principles. Four new mechanisms for distribution are presented: (1) a distributed array allocation operator for data distribution; (2) a distributed L operator for code distribution; (3) a range filter for restriction index ranges for different PEs; and (4) a specialized apply operator for functional parallelism.

Simulations show that PODS balances communication overhead with distributed processing to achieve efficient parallel execution on distributed memory multiprocessors. This is partially due to a new software array caching scheme, called *remote caching*, which greatly reduces the amount of remote memory reads. PODS is designed to use off-the-shelf components, with no specialized hardware. In this way a real PODS machine can be built quickly and cost effectively. The system is currently being retargeted to the Intel iPSC/2 so that it can be run on commercially available equipment.

Keywords: single assignment, dataflow, multiprocessor, declarative programming, matrix multiply, SIMPLE

#### UNIVERSITY OF CALIFORNIA

#### **IRVINE**

# Exploiting Iteration-Level Parallelism

in Declarative Programs

#### DISSERTATION

submitted in partial satisfaction of the requirements for the degree of

#### DOCTOR OF PHILOSOPHY

in Information and Computer Science

by

John Marc Andre Roy

Dissertation Committee:

Professor Lubomir Bic, Chair

Professor Nikil Dutt

Professor Alexandru Nicolau

© by John Marc Andre Roy

All rights reserved.

The dissertation of John Marc Andre Roy is approved,

and is acceptable in quality and form

for publication on microfilm:

University of California, Irvine

Committee Chair

1991

## DEDICATION

To

my wonderful wife for all of her love, support, and understanding.

I love you Charlene.

## TABLE OF CONTENTS

| LIST OF FIGURES                            | viii |

|--------------------------------------------|------|

| LIST OF TABLES                             | xi   |

| ACKNOWLEDGEMENTS                           | xii  |

| CURRICULUM VITAE                           | xiii |

| PUBLICATIONS                               | xiii |

| ABSTRACT OF THE DISSERTATION               | xiv  |

| Background                                 | 1    |

| 1.1. Basic Issues in Parallel Processing   | 5    |

| 1.1.1. Parallel Programming                | 5    |

| 1.1.2. Distributed Memory MIMD             | 6    |

| 1.2. Previous Research                     | 6    |

| 1.2.1. Single Assignment Principle         | 6    |

| 1.2.2. ID Nouveau Dataflow Language        | 8    |

| Single Assignment Approach                 | 9    |

| Iteration                                  | 10   |

| I-Structures                               |      |

| Discussion                                 |      |

| 1.2.3. Hybrid Dataflow                     | 13   |

| 1.3. Overview of PODS Execution Model      | 14   |

| 1.3.1. Subcompact Processes (SP)           | 15   |

| 1.3.2. State Transitions                   | 17   |

| 1.3.3. Distributed Memory Approach         | 19   |

| 1.3.4. Discussion                          | 20   |

| 1.4. Contributions of this Research        | 21   |

| 1.4.1. Execution Model Extensions          | 21   |

| 1.4.2. Partitioning and Distribution Model | 21   |

| 1.4.3. Remote Array Caching                | 22   |

| 1.4.4. Logical Architecture                |      |

| 1.4.5. Simulations                         | 22   |

|                                            |      |

| PODS Partitioning and Distribution Model   | 24   |

| 2.1. Overview                              | 25   |

| 2.2. Underlying Principles                 | 27   |

| 2.2.1. Basic Principles                    | 28   |

| 2.2.2. PODS Specific Principles            | 30   |

| Grouping Principle                         | 30   |

| Virtual Sources Principle                  | 31   |

| Collector Writes Principle                 | 32   |

| 2.3. PODS Instructions and Processes       | 33   |

| 2.3.1. Activity Names                      | 34   |

| 2 3 2 PODS Instruction Format              | 36   |

| 2.3.3. PODS Dataflow Operator Implementation | . 38           |

|----------------------------------------------|----------------|

| Arithmetic and Logical Operators             | 40             |

| switch and forkjump                          |                |

| d and d_inverse                              | 13             |

| l and l_inverse                              | 45             |

|                                              |                |

| a and a_inverse                              | 4/             |

| 2.4. Array Partitioning and Distribution     | 48             |

| 2.5. Distributing Processes                  | . 56           |

| 2.5.1. Data-Distributed Execution Principle  | . 57           |

| 2.5.2. Range Filters                         | 61             |

| Objective and Usage                          | 61             |

| Boundary Table                               | 64             |

| Master Array                                 | . 65           |

| Master Array                                 | . 65           |

| Algorithm                                    | . 63           |

| 2.5.3. LCD Effects                           |                |

| 2.5.4. Remote Array Accesses                 |                |

| Remote Reads                                 | . 71           |

| Remote Writes                                |                |

| 2.5.5. For-Loop Distribution Algorithm       |                |

| 2.5.6. Examples                              |                |

|                                              |                |

| LCD Examples                                 |                |

| Matrix Multiply                              |                |

| 2.6. Functional Distribution                 |                |

| 2.7. Deadlock Handling                       | . 90           |

| C                                            |                |

| PODS Logical Implementation                  | 95             |

| 3.1. System Overview                         | 95             |

| 3.2. Logical PE Architecture.                | 07             |

|                                              |                |

| 3.2.1. Execution Unit                        | 99             |

| 3.2.2. Routing Unit                          | 100            |

| • 3.2.3. Array Manager                       | 102            |

| 3.2.4. Memory Manager                        | 104            |

| 3.2.5. Matching Unit                         | 104            |

| 3.3. Remote Array Caching                    | 104            |

|                                              |                |

| 3.4. Software Support                        | 100            |

| 3.4.1. ID World and GITA Compiler            | אַט            |

| 3.4.2. Translator                            |                |

| 3.4.3. Partitioner                           |                |

| 3.4.4. Simulator                             | 113            |

|                                              |                |

| PODS Simulations                             | 14             |

| 4.1. Overview                                |                |

|                                              |                |

| 4.1.1. Simulator Approach                    | .14            |

| 4.1.2. Timing Assumptions                    | .16            |

| Execution Unit1                              |                |

| Array Manager1                               | .17            |

| Routing Unit1                                | 10             |

|                                              | 18             |

| Memory Manager 1                             | 18             |

| Memory Manager1                              | 19             |

| Memory Manager1  Matching Store1             | 19<br>19       |

| Memory Manager1                              | 19<br>19<br>19 |

| 4.3. Example Programs                                  | 121 |

|--------------------------------------------------------|-----|

| 4.3.1. Matrix Multiply                                 | 121 |

| Discussion                                             |     |

| Results                                                |     |

| 4.3.2. SIMPLE                                          | 128 |

| Discussion                                             |     |

| Results                                                |     |

| 4.4. Summary                                           |     |

| ·                                                      |     |

| Conclusions                                            | 145 |

| 5.1. Related Work                                      |     |

| 5.1.1. Iannucci's Hybrid Architecture                  | 145 |

| 5.1.2. Gao's Hybrid Machine                            | 146 |

| 5.1.3. Alfalfa                                         | 147 |

| 5.1.4. Decoupled Multilevel Dataflow Model             | 147 |

| 5.1.5. Dynamic Structured Dataflow                     | 148 |

| 5.1.6. Pingali and Rogers' Compiler                    | 148 |

| 5.2. Advantages and Disadvantages of Single Assignment | 149 |

| 5.3. Summary                                           |     |

| 5.4. Future Research                                   | 153 |

| 5.4.1. HyperPODS                                       | 153 |

| 5.4.2. PODS Compiler                                   | 154 |

| <b>1</b>                                               |     |

| References                                             | 156 |

|                                                        |     |

| Appendix A: Range Filter Algorithms                    | 165 |

## LIST OF FIGURES

| Figure 1.1.  | Lines of Research                             | 2  |

|--------------|-----------------------------------------------|----|

| Figure 1.2.  | ID Nouveau Quicksort Code                     | 9  |

| Figure 1.3.  | ID Nouveau Iteration Example.                 | 11 |

| Figure 1.4.  | ID Nouveau I-Structure Example                | 11 |

| Figure 1.5.  | Subcompact Process Example Code.              | 15 |

| Figure 1.6.  | PODS Subcompact Processes Example             | 17 |

| Figure 1.7.  | Process State Transition Diagram              | 18 |

| Figure 1.8.  | PODS Memory Accessing Scheme                  | 20 |

| Figure 2.1.  | Simple Array Assignment.                      | 28 |

| Figure 2.2.  | Equal Distribution Principle.                 | 29 |

| Figure 2.3.  | Grouping Principle                            | 30 |

| Figure 2.4.  | Virtual Sources Principle.                    | 31 |

| Figure 2.5.  | Collector Writes Principle.                   | 32 |

| Figure 2.6.  | Basic Dataflow Operator                       | 34 |

| Figure 2.7.  | Activity Name Components.                     | 35 |

| Figure 2.8.  | SP Components                                 | 38 |

| Figure 2.9.  | ID vs PODS Statement "Addressing"             | 40 |

| Figure 2.10. | PODS SWITCH and FORKJUMP Instruction Examples | 42 |

| Figure 2.11. | PODS Branch.                                  | 43 |

| Figure 2.12. | PODS Code Fragment for a Loop.                | 45 |

| Figure 2.13. | Example L Operators                           | 46 |

| Figure 2.14. | Example Apply and Inv_Apply Operators         | 48 |

| Figure 2.15. | Matrix Multiply ID Nouveau Source Code        | 50 |

| Figure 2.16. | PODS Partitioning of A 2-D Array.             | 52 |

| Figure 2.17  | 2-D Array Read Pseudo-Code.                   | 55 |

| Figure 2.18  | 8. Example 2-D Array Remote Read                                              | 55  |

|--------------|-------------------------------------------------------------------------------|-----|

| Figure 2.19  | Example 2-D Array Local Read                                                  | 56  |

| Figure 2.20  | Partitioning a 2D Iteration Space                                             | 58  |

| Figure 2.21  | . Partitioning a 3D Iteration Space                                           | 59  |

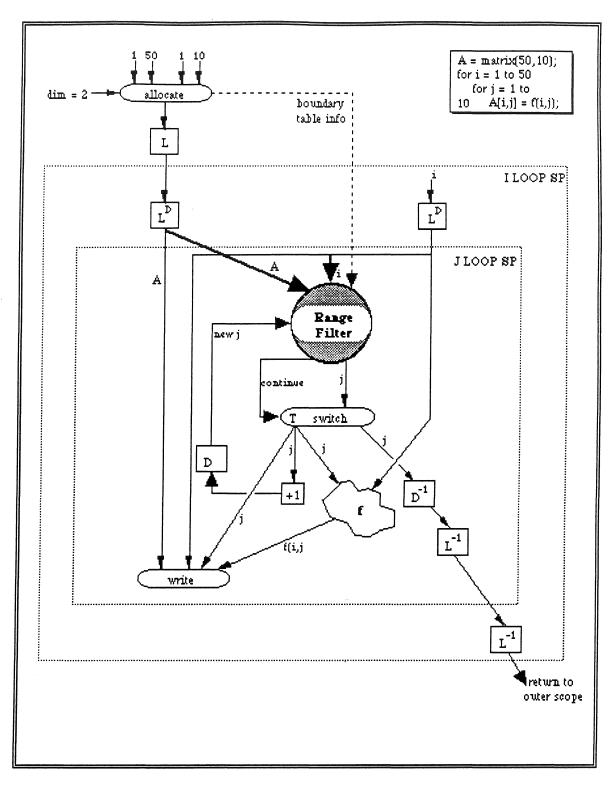

| Figure 2.22  | . Simple 2-D Array Fill.                                                      | 62  |

| Figure 2.23  | . 2-D Array Fill with Range Filter                                            | 63  |

| Figure 2.24  | . Algorithm for Second Level, Descending Range Filter for A[ci*i+ki,cj*j+kj]. | 66  |

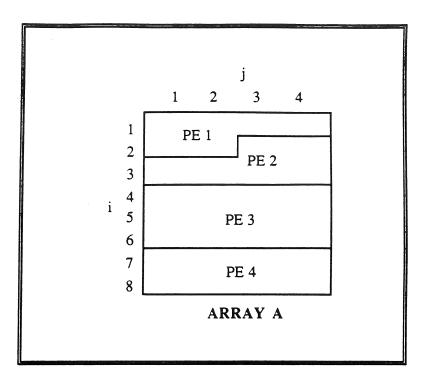

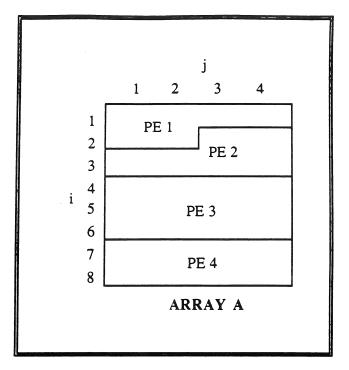

| Figure 2.25  | . Non-rectangular Array Partitioning Example                                  | 67  |

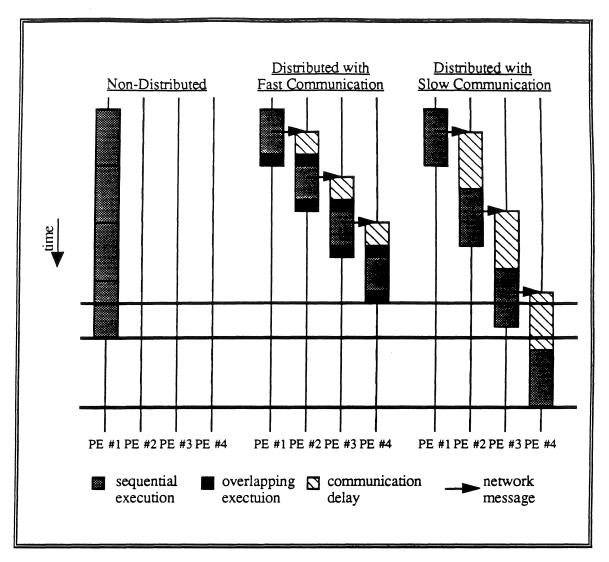

| Figure 2.26  | . Effects of Communication Speed on Overlapping Iterations                    | 69  |

| Figure 2.27  | . Remote Read Code Example                                                    | 72  |

| Figure 2.28  | . Remote Write Code Example                                                   | 73  |

| Figure 2.29. | Impossible Collector Writes                                                   | 74  |

| Figure 2.30. | Simple Array Filling Example Code                                             | 76  |

| Figure 2.31. | Simple Row-Major Array Partitioning.                                          | 77  |

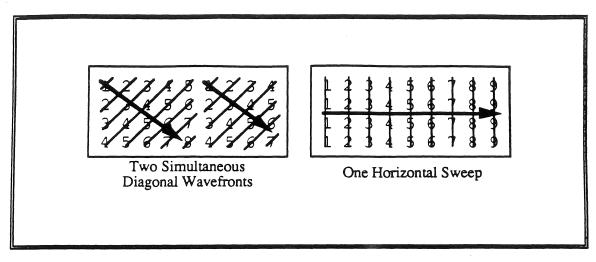

| Figure 2.32. | LCD Execution Wavefronts.                                                     | 84  |

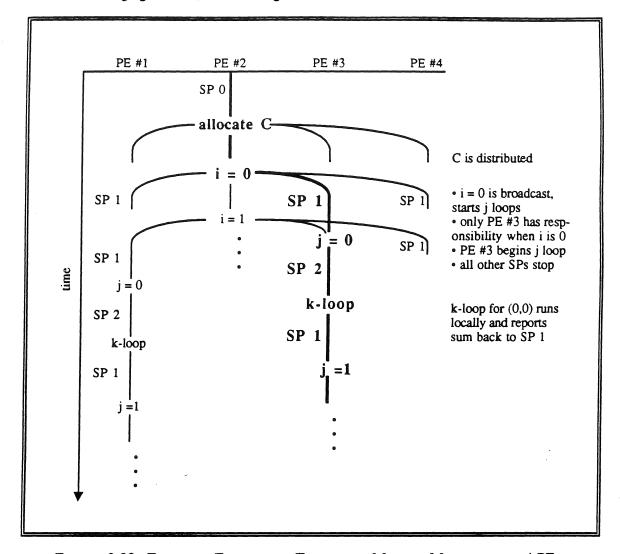

| Figure 2.33. | Example Execution Trace for Matrix Multiply on 4 PEs                          | 88  |

| Figure 2.34. | ID Nouveau Deadlock Code Example                                              | 92  |

| Figure 3.1.  | Logical Units of a PODS PE.                                                   | 98  |

| Figure 3.2.  | Routing Table.                                                                | 100 |

| Figure 3.3.  | Routing Unit Block Diagram.                                                   | 101 |

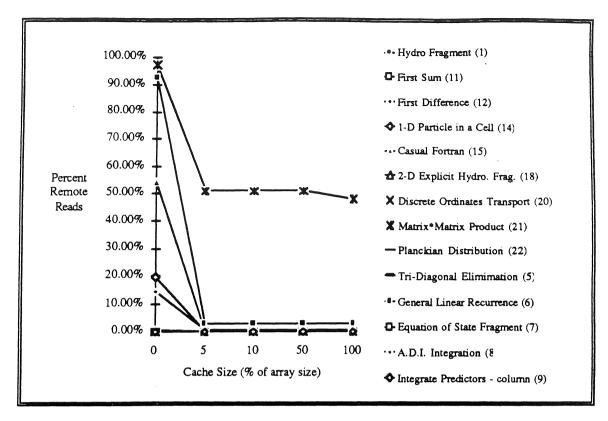

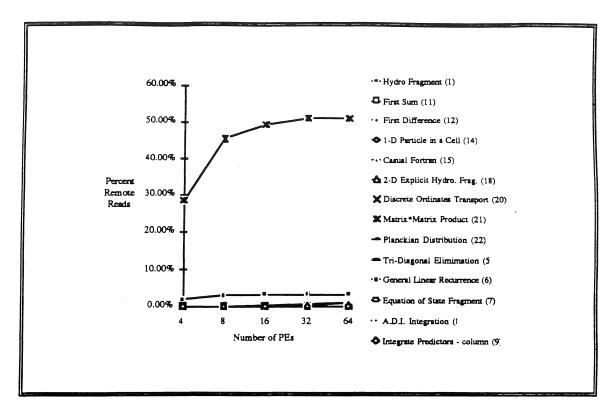

| Figure 3.4.  | Effects of Cache Size on Percentage of Remote Reads                           | 107 |

| Figure 3.5.  | Remote Reads for the Livermore Loops using Remote Caching                     | 108 |

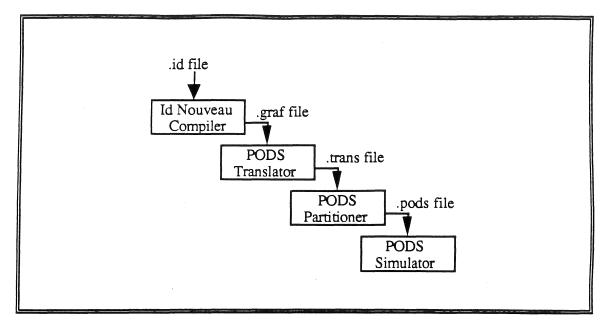

| Figure 3.6.  | PODS Programming System.                                                      | 109 |

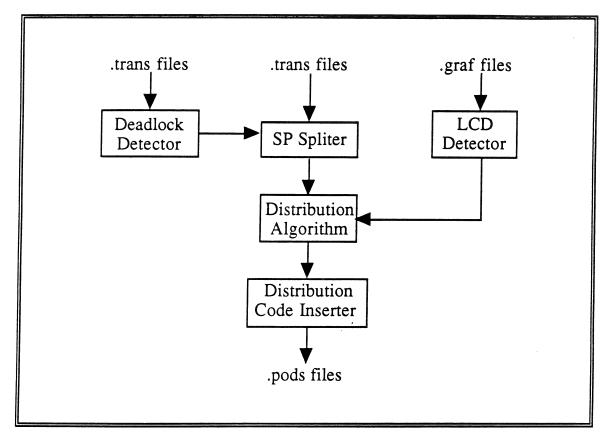

| Figure 3.7.  | PODS Partitioner Block Diagram.                                               | 111 |

| Figure 4.1.  | 2-D Array Read Pseudo-Code.                                                   | 117 |

| Figure 4.2.  | Matrix Multiply ID Nouveau Source Code                                        | 122 |

|              |                                                                               |     |

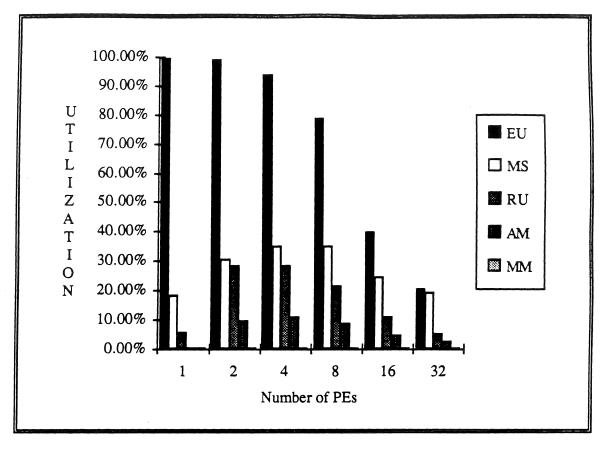

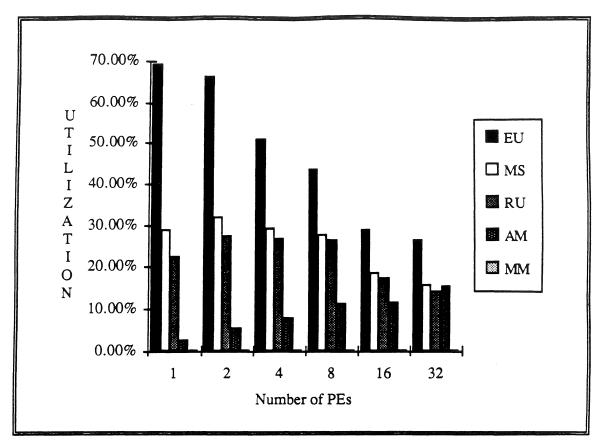

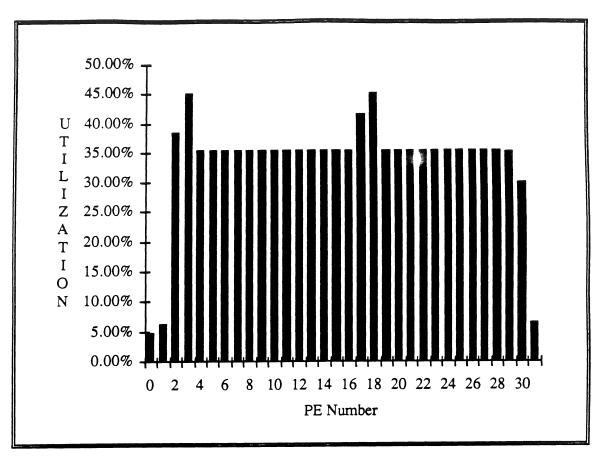

| Figure 4.3.  | Utilization for Each Functional Unit (16 x 16 MM)                   | . 123 |

|--------------|---------------------------------------------------------------------|-------|

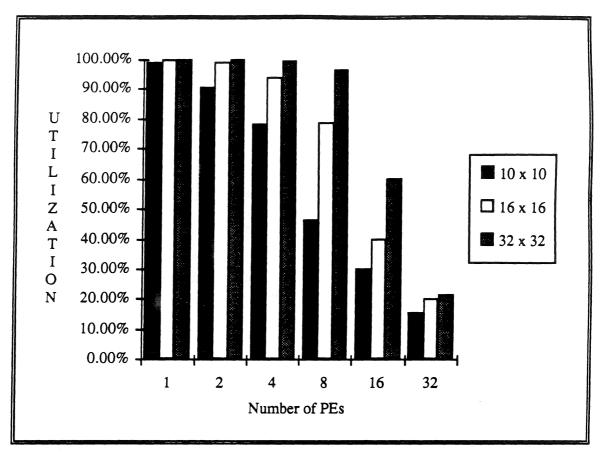

| Figure 4.4.  | Average Execution Unit Utilization for Matrix Multiply              | . 124 |

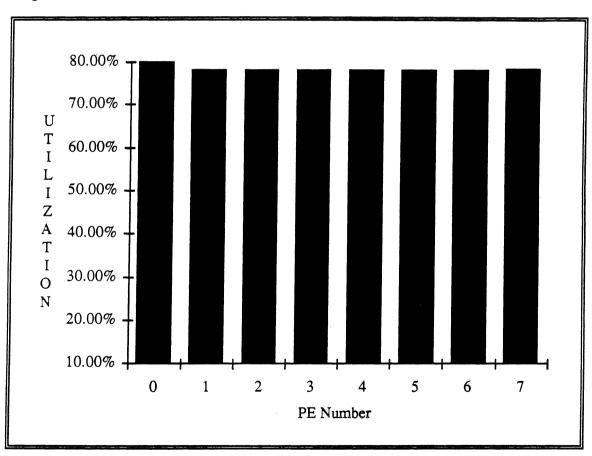

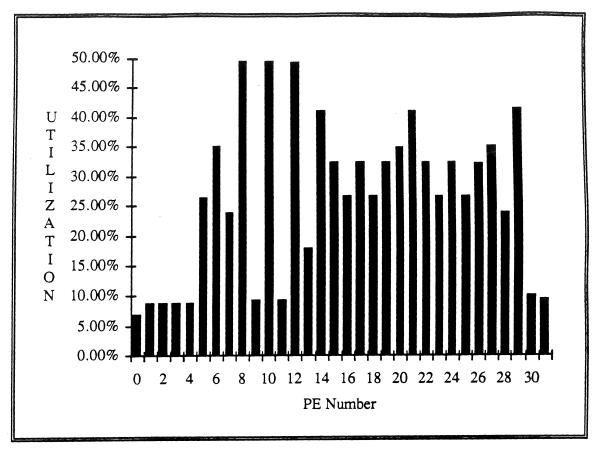

| Figure 4.5.  | Utilization for each Execution Unit (16 x 16 MM on 8 PEs)           | 125   |

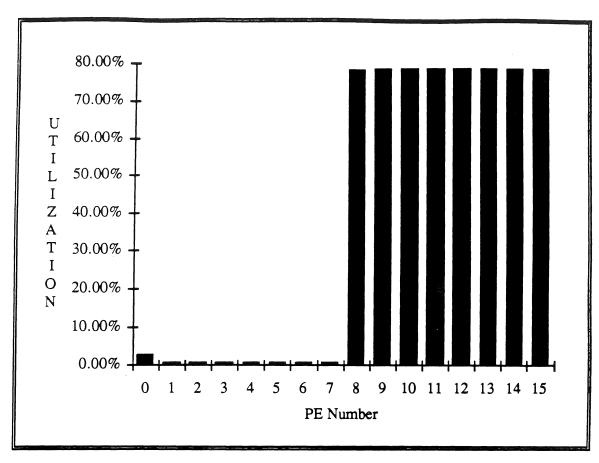

| Figure 4.6.  | Utilization for each Execution Unit (16 x 16 MM on 16 PEs)          | 126   |

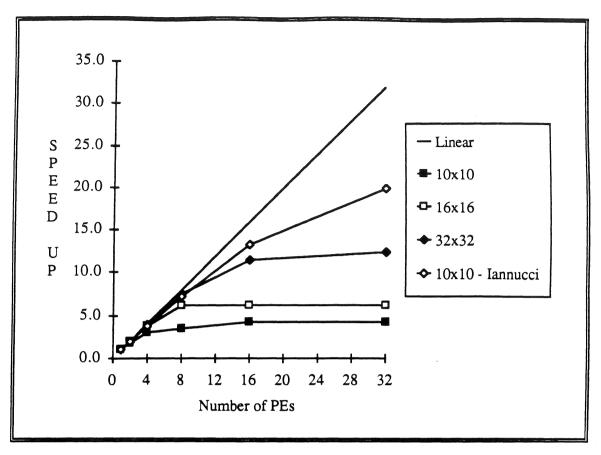

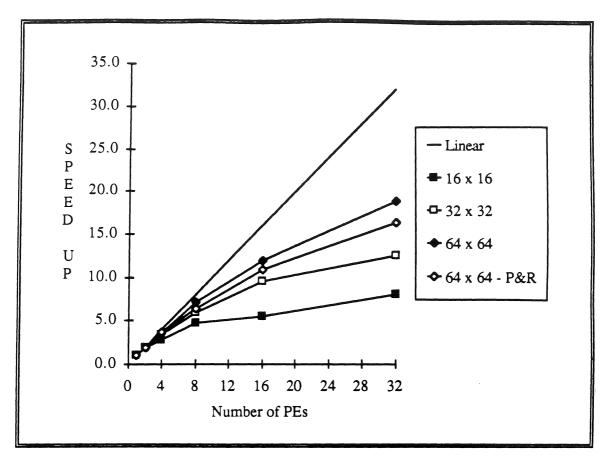

| Figure 4.7.  | Speed-Up of Matrix Multiply.                                        | . 128 |

| Figure 4.8.  | Sweep For-Loops in Conduction Code.                                 | . 130 |

| Figure 4.9.  | Original Conduction Code with Multiple LCDs                         | . 131 |

| Figure 4.10. | Scalar Expanded Conduction Code Fragment                            | . 132 |

| Figure 4.11. | Utilization for Each Functional Unit (16 x 16 SIMPLE)               | . 135 |

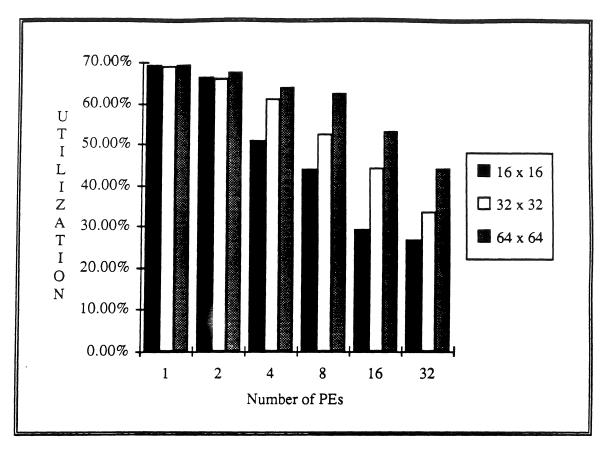

| Figure 4.12. | Execution Unit Utilization for SIMPLE.                              | . 136 |

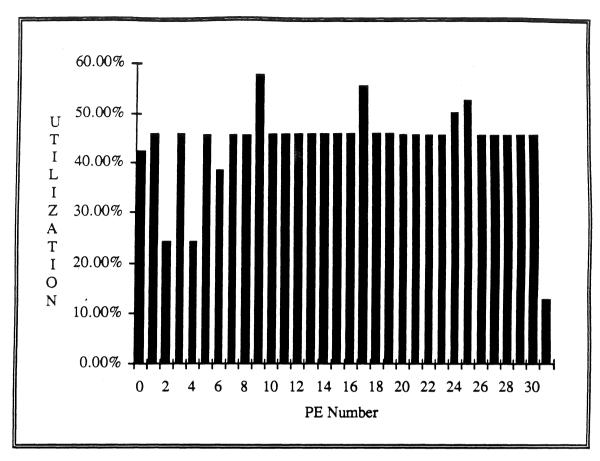

| Figure 4.13. | Execution Unit Utilization (16 x 16 SIMPLE on 32 PEs)               | . 137 |

| Figure 4.14. | Execution Unit Utilization (32 x 32 SIMPLE on 32 PEs)               | 138   |

| Figure 4.15. | Execution Unit Utilization (64 x 64 SIMPLE on 32 PEs)               | 139   |

| Figure 4.16. | Speed-Up of SIMPLE.                                                 | 141   |

| Figure A.1.  | Base Range Filter Algorithm for Outermost Level Distribution        | 165   |

| Figure A.2.  | Base Range Filter Algorithm for Second Outermost Level Distribution | 166   |

| Figure A.3.  | Base Range Filter Algorithm for Third Outermost Level Distribution  | 167   |

| Figure A.4.  | Range Filter Algorithm for Stepsize -1                              | 168   |

| Figure A.5.  | Second Level Distribution Range Filter for A[ci*i+ki,cj*j+kj]       | 169   |

| Figure A.6.  | Range Filter for Third Level Distribution with Stepsize C           | 170   |

## LIST OF TABLES

| Table 2.1. | PODS Array Header Information.                    | 53  |

|------------|---------------------------------------------------|-----|

| Table 2.2. | 2-D Array Example Header                          | 54  |

| Table 2.3. | Example Boundary Table for a Given PE.            | 64  |

| Table 2.4. | Effects of Outer Loop Distribution with No LCDs   | 78  |

| Table 2.5. | Effects of Inner Loop Distribution with No LCDs.  | 79  |

| Table 2.6. | Effects of Inner Loop Distribution with LCDs      | 81  |

| Table 2.7. | Effects of No Distribution due to LCDs.           | 83  |

| Table 4.1. | Measured Times of Operations on iPSC/2            | 116 |

| Table 4.2. | Percent Overhead Instructions for Matrix Multiply | 126 |

| Table 4.3. | SP Statistics for Conduction.                     | 134 |

| Table 4.4. | Percent Overhead Instructions for SIMPLE          | 139 |

#### ACKNOWLEDGEMENTS

I would like to express my thanks to my committee chair, Professor Lubomir Bic, for his continuing insights through out the years, and for this diligence in helping me prepare this dissertation.

I would like to particularly thank my research associate, Mark Nagel, for his ideas and programming expertise. Without Mark this work would still be in the programming stages. Good luck Mark.

Special thanks to my parents for their support and encouragement through out my entire life.

Financial support has been provided by a number of sources through out the years: Hughes Aircraft Company, Fail-Safe Technology, JMAR Research Group, and from my wonderful wife, Charlene. I would also like to thank the National Science Foundation for their support of the PODS research through NSF grant #CCR-8709817.

#### **CURRICULUM VITAE**

#### John M.A. Roy

| 1982         | B.S. in Electrical Engineering, University of California, San Diego.                                                                                                                       |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1982-1987    | Systems Engineer, Hughes Aircraft Company, Fullerton, California.                                                                                                                          |

| 1984         | M.S. in Electrical Engineering, University of Southern California.                                                                                                                         |

| 1987-1988    | Senior Member of Technical Staff, Fail-Safe Technology, Los Angeles, California.                                                                                                           |

| 1988-1989    | Systems Consultant, JMAR Research Group, Irvine, California.                                                                                                                               |

| 1989         | M.S. in Information and Computer Science, University of California, Irvine.                                                                                                                |

| 1989-1990    | Vice-President, Engineering and Operations, Trintech USA, Irvine, California.                                                                                                              |

| 1991-Present | Vice-President, Engineering, National Paging, Santa Ana, California.                                                                                                                       |

| 1991         | Ph.D. in Information and Computer Science, University of California, Irvine. Dissertation: "Exploiting Iteration-Level Parallelism in Declarative Programs." Professor Lubomir Bic, Chair. |

#### **PUBLICATIONS**

- L. Bic, M. D. Nagel, J. M. A. Roy. Automatic Data/Program Partitioning Using the Single Assignment Principle. Supercomputing '89 (1989), pp. 551-556.

- L. Bic, M. D. Nagel, J. M. A. Roy. Executing Matrix Multiply on a Process Oriented Dataflow Machine. *Technical Report 90-08* (April 1990), Department of ICS, University of California, Irvine.

- L. Bic, M. D. Nagel, J. M. A. Roy. On Array Partitioning in PODS. In *Advanced Topics in Data-Flow Computing*. J. L. Gaudiot, L. Bic, Eds. (Prentice Hall, Englewood Cliffs, New Jersey, 1990), pp. 305-325.

- J. M. A. Roy, M. D. Nagel, L. Bic. Partitioning Declarative Programs into Communicating Processes. *Supercomputing '90* (1990), pp. 846-855.

#### ABSTRACT OF THE DISSERTATION

Exploiting Iteration-Level Parallelism

in Declarative Programs

by

John Marc Andre Roy

Doctor of Philosophy in Information and Computer Science

University of California, Irvine, 1991

Professor Lubomir Bic, Chair

In order to achieve viable parallel processing three basic criteria must be met: (1) the system must provide a programming environment which hides the details of parallel processing from the programmer; (2) the system must execute efficiently on the given hardware; and (3) the system must be economically attractive.

The first criterion can be met by providing the programmer with an *implicit* rather than *explicit* programming paradigm. In this way all of the synchronization and distribution are handled automatically. To meet the second criterion, the system must perform synchronization and distribution in such a way that the available computing resources are used to their utmost. And to meet the third criterion, the system must *not* require esoteric or expensive hardware to achieve efficient utilization.

This dissertation reports on the Process-Oriented Dataflow System (PODS), which meets all of the above criteria. PODS uses a hybrid von Neumann-Dataflow model of computation supported by an automatic partitioning and distribution scheme. The new partitioning and distribution algorithm is presented along with the underlying principles. Four new mechanisms for distribution are presented: (1) a distributed array allocation operator for data distribution; (2) a distributed L operator for code distribution; (3) a range filter for restriction index ranges for different PEs; and (4) a specialized apply operator for functional parallelism.

Simulations show that PODS balances communication overhead with distributed processing to achieve efficient parallel execution on distributed memory multiprocessors. This is partially due to a new software array caching scheme, called *remote caching*, which greatly reduces the amount of remote memory reads. PODS is designed to use off-the-shelf components, with no specialized hardware. In this way a real PODS machine can be built quickly and cost effectively. The system is currently being retargeted to the Intel iPSC/2 so that it can be run on commercially available equipment.

#### CHAPTER 1

### Background

Scientific programmers are the primary users of parallel systems today. The current parallel programming systems do not meet the needs of this important group. Recent user surveys show that only one user program in twenty executed on the Cornell supercomputer is parallel, [P&B90]. These surveys also indicate that many more scientists would program for parallel systems if they were not so difficult to program. Hand-coded parallelism is too difficult and time consuming, while parallelizing compilers do not achieve significant speed-up.

What is needed is a system which provides scientific programmers with a means to express their problem clearly and to have it execute efficiently in parallel automatically. Add to this the desire to run on standard MIMD architectures (e.g., iPSC/2) and the problem becomes very difficult. MIMD architectures require that programs be decomposed into independent processes, running asynchronously on the different processor nodes and communicating with one another through message passing or through shared memory. The current state of the art in programming such machines efficiently is to let the programmer explicitly partition the program into processes and insert the necessary synchronization and communication primitives. This is very time-consuming and error-prone. Automatic generation of parallel programs from conventional languages has not, as yet, achieved sufficient speed-up to warrant wide-spread usage.

To achieve these goals many declarative programming languages [A&E88] have been designed. Declarative programming languages are much better suited for program decomposition than procedural languages such as C or FORTRAN. Declarative languages allow the programmer to describe the problem using high-level constructs, yet their

semantics eliminate uncontrolled side-effects though functional expressions and single assignment restrictions.

Declarative languages have been developed primarily in the context of approach of radically different computer architectures, in particular, dataflow architectures, where parallelism is to be exploited at the *instruction level*. For conventional loosely-coupled MIMD systems, this level of parallelism is too low; the communications costs are too high. By moving to *iteration level* parallelism this problem can be overcome [Burns, 88]. Iteration level parallelism is achieved when different iterations (or groups of iterations) from the same loop are run on different PEs.

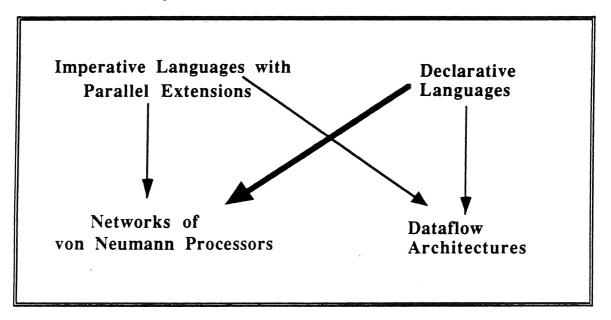

Process-Oriented Dataflow Systems (PODS) make use of iteration level parallelism and declarative programing on distributed memory MIMD machines. The PODS line of research is show in Figure 1.1 as the bold arrow.

FIGURE 1.1. LINES OF RESEARCH.

Figure 1.1 shows the different lines of research in parallel processing. The first line involves running imperative languages with parallel extensions (e.g., FORTRAN\*

[K&B88]) on Networks of von Neumann Processors (e.g., iPSC/2 [Intel, 89]). This approach is the least revolutionary and has had some commercial success. The second line of research is to take imperative languages and execute them on dataflow architectures (e.g., Monsoon [Pap88]). This direction has not seen much research, only the ASTOR [U&Z89, Z&U87] project in Germany has looked into this. The next line of research is to take a declarative language (e.g., ID [ANP87b], SISAL[A&O85, MSS85]) and run them on von Neumann networks. This is where PODS is, and there are a number of others, notably Pingali and Rogers at Cornell [P&R90]. The final approach is the most revolutionary, running declarative languages on dataflow architectures involves both new hardware and software. P-RISC [N&A89] and the Monsoon project are both taking this approach.

In [Bic87], the basic principles of PODS were presented. The algorithms for subdividing dataflow graphs into communicating processes, however, were too simplistic, concentrating on only functional parallelism. In scientific code, most parallelism comes from loops iterating over large data structures (i.e., data parallelism). This issue has been addressed in subsequent studies [BNR89a, Bic90, BNR90a, BNR90b] which show that, for languages based on the single assignment principles (declarative languages), a simple automatic partitioning of arrays exposes significant parallelism that can be exploited at runtime.

In PODS, the programming language ID Nouveau [Nik88] is used because it is one of the most developed and supported dataflow languages to date and has single-assignment. Single-assignment is central to PODS. Given an ID Nouveau program, a compiler would produce a dataflow graph, where nodes represent individual instructions and arcs show all data dependencies. This graph is then used to generate light-weight processes, referred to as "subcompact processes" (SPs). This is accomplished by partitioning the dataflow graph

into subgraphs, each of which is executed as a sequential process on a given processing element (PE).

This dissertation describes the partitioning method used to form the SPs, the SP distribution criteria, the logical implementation of PODS, the remote caching scheme used, and the results of experiments with an event-driven, instruction-level, simulator. The dissertation is organized as follows:

- Chapter 1 Background an overview of the pertinent basic concepts. This includes discussions on parallel programming, distributed memory MIMD architectures, the ID dataflow language, and the previous work on PODS. Knowledgeable readers may skip any or all of this chapter.

- Chapter 2 PODS Partitioning and Distribution Model a detailed discussion of the inner workings of the partitioning of programs into SPs and their distribution.

- Chapter 3 PODS Logical Implementation a discussion of the tasks necessary to make the PODS system work. The array caching scheme is presented along with a discussion of the special PODS instructions. This is followed up with a description of the PE architecture and the necessary support software.

- Chapter 4 Simulations a presentation of the experiments using Matrix Multiply and SIMPLE. The simulation approach is discussed and the results are examined.

- Chapter 5 Conclusions a discussion of the findings about PODS. Future research and related work are also discussed.

#### 1.1. Basic Issues in Parallel Processing

#### 1.1.1. Parallel Programming

Parallel processing has been touted as the wave of the future for a number of years, yet its use is not yet common. This is because parallel processing requires parallel programming. For the average, highly-intelligent, but inexperienced, scientific programmer, the task of programming a parallel system can be daunting.

In [K&B88], Karp and Babb discuss the complications which arise when trying to program in any one of twelve parallel FORTRAN dialects. They state that even trivial examples frequently become a challenge. Programming parallel systems present complications not found in sequential programming. Often parallel programing environments force the programmer to explicitly partition function and data according to the constraints of the architecture. Thus requiring the scientific programmer to become knowledgeable about the particular computer architecture being used.

In debugging parallel programs, synchronization and timing are often the problem [K&T88]. By requiring the programmer to explicitly state the communication and synchronization points in a program, the system is opening itself to subtle timing errors. The difficult thing about timing errors is their unpredictability. Often a timing error may disappear based upon some seemingly unrelated fact (e.g. the load on the I/O network to the host), and reappear at a later date.

In their 1989 report on supercomputers, the IEEE Scientific Supercomputer Subcommittee sited the lack of software as *the* major problem [IEEE89] in supercomputing today.

All of the above problems are addressed in PODS, the parallelization is implicit not explicit, the synchronization is handled automatically, and, due to the dataflow nature of PODS, the special timing problems of parallel programs are non-existent.

#### 1.1.2. Distributed Memory MIMD

Distributed-memory MIMD computers can be made massively parallel by adding PE's in a modular fashion. This modularity allows dramatic increases the theoretical maximum speed. As an example, the latest supercomputer from Intel, called the Delta System, will incorporate 528 i860 microprocessors and have a theoretical peak processing rate of 32 billion floating-point operations per second [Ins91]. The problem is exploiting all of this parallelism.

#### 1.2. Previous Research

#### 1.2.1. Single Assignment Principle

The Single Assignment Principle simply states that no variable will be assigned a value more than once. This would seem like a very limiting restriction, i.e. one may not even write x = x + 1. However, researchers have found that a number of benefits can be derived from using single assignment in combination with a functional language. A functional language is one which is based on function application and is therefore free of side effects. Some of the programming benefits of single assignment functional languages [Veg88] are:

- Programs can be written at a higher level. Time can be spent concentrating on the algorithm rather than the program details.

- More algorithmic work can be expressed per line of code. This

is important because evidence suggests that the number of lines

- of *correct* code per day is roughly a constant for a given programmer, independent of the language used.

- Functional languages are free of side effects. This greatly

reduces unexpected modification of variables in other routines.

- Programs are easier to verify because proofs can be based upon the concept of a function rather than some complex von

Neumann model.

- Functional programs can contain a great deal of implicit rather than explicit parallelism. This is crucial to the PODS concept.

As is described in the next section, ID Nouveau is the single assignment functional language which PODS uses. Some of the basic ID Nouveau principles are discussed in the next section.

PODS specifically uses the following abilities of single assignment functional languages:

- Implicit Parallelism the ability of a programmer to code a

parallel program without explicitly specifying the parallelism.

- Parallel Program Synchronization single assignment automatically synchronizes the data reads and writes of a program, thus preventing innocuous timing bugs.

- Automatic Cache Coherency single assignment allows remote caching to avoid the cache coherency problem. Thus an efficient implementation can be designed, see Section 3.3, Remote Array Caching.

#### 1.2.2. ID Nouveau Dataflow Language

ID (Irvine Dataflow) was born at the University of California, Irvine in a 1978 technical report [AGP78]. This report laid the foundations for all further versions of ID. ID has gone through many changes but still retains the basic dataflow ideas, the single assignment concept, and the compiler approach outlined by Arvind. The latest version is being worked at MIT and is called ID Nouveau. The ID Nouveau language environment, called ID-World, is a complete parallel language simulator. There are over twenty sites using ID-World and many more will be appearing as ID-World expands outside of the LISP machine world and onto UNIX workstations.

The syntax of ID Nouveau and its functional nature lead to clean algorithms, which in turn is easier to read and understand. Consider the quicksort code in Figure 1.2 below. Notice that ID Nouveau allows standard list operations which are easy to understand.

```

def Quicksort A =

Split L =

{ startvalue = hd L;

for v in L;

if (v < startvalue) then cons Llist v;

if (v == startvalue) then center = v;

if (v > startvalue) then cons Rlist v;

end for

in

Llist, center, Rlist

} ; % Split

in

% Quicksort routine body

if (length A < 2)

then

Α

else

L, Middle, R = Split(Data)

cons Quicksort(L) Middle Quicksort(R);

% Quicksort

```

FIGURE 1.2. ID NOUVEAU QUICKSORT CODE.

The split function is repeatedly called until each sublist has only one element it it. Then the sublists are concatenated in order. This is a very clean and clear program for quicksort.

#### Single Assignment Approach

The central issue for PODS in ID is its single assignment nature. All dataflow languages begin with single assignment, yet many diverge as further developments are made. ID has tried to stay true to its original single assignment concept:

...a dataflow operation is purely functional and produces <u>no</u> sideeffects as a result of its execution. This is the essence of single assignment; however, the issue of array handling is in conflict. To provide arrays this constraint has to be relaxed. ID Nouveau arrays (called *I-structures*) produce a side-effect, but are not allowed to be updated to ensure determinacy. Yet, with no update how useful is an array? The answer to this question is still being researched. Arvind, Nikhil, and Pingali feel that they are very useful and that this is the best approach [ANP87a]. They believe that an update operator is inadequate and *over-specifies* algorithms is such a way that unnecessary copying of intermediate data structures and substantial unnecessary sequentialization occur. They also feel that automatic detection is not tractable in general, contrary to other researchers beliefs [A&K87, A&N87, P&W86].

#### <u>Iteration</u>

Iteration is a major source of parallelism. How a language handles iteration is going to affect the ability of the programmer and compiler to exploit the parallelism in the loops. In ID Nouveau the evaluation of loops and conditionals is not eager. This is the same as VAL/SISAL for expressions [A&O85]. This forces the predicate to be fired before either of the two branches of a conditional are fired.

As an example of iteration, consider the program below, taken from [Tra86]. It fills each element of its argument array with a value and returns the sum of all the elements. The loop body contains ordinary bindings (like the variable val), I-structure stores (for A[i]), and some *newified* variable bindings. These newified variable bindings describe how to compute the values the newified variables take on the next iteration of the loop, e.g. the variable i is incremented each time through the loop. These newified variables must have an initial binding outside the loop, otherwise it would have no value for the first iteration. Newified variables do not make sense outside of loops and are not allowed there.

```

{ def fill_it A =

let

i = lower_bound A;

sum = 0;

in

while i \le upper_bound A;

val = (upper_bound A - lower_bound A) ^ 2 - i*i;

A[i] = val;

new sum = sum + val;

new i = i + 1;

return sum

}

```

FIGURE 1.3. ID NOUVEAU ITERATION EXAMPLE.

#### I-Structures

The basic array structure mechanism in ID Nouveau is the I-structure [ANP87a]. An I-structure is an *incremental structure* which obeys the single assignment rule. An I-structure is available as soon as it is allocated and the array elements are individually accessible. Consider the wavefront example below:

```

{ A = matrix ((1, m) , (1, n)) ;

{for i from 1 to m do

A[i,1] = 1}

{for j from 2 to n do

A[1,j] = 1}

{for i from 2 to m do

{for j from 2 to n do

A[i, j] = A[i-1, j] + A[i-1, j-1] + A[i, j-1] }}

in

A}

```

FIGURE 1.4. ID NOUVEAU I-STRUCTURE EXAMPLE.

Here a matrix has its upper and left borders filled with 1's, while its interior is filled with the sum of the upper, left, and diagonal elements. The matrix A will be returned as the value of the entire expression as soon as it is allocated. Meanwhile, all the loop bodies are initiated in parallel, but some will be delayed until the loop bodies to the left and top

(cartesian coordinate wise) complete. Thus a "wavefront" of processes fills the matrix in parallel.

To achieve this flexibility I-structures use a *presence bit*. Each cell of an I-structure has a logical bit attached to it to determine if the cell's value is present. If a read occurs before the cell is written, the read is enqueued by the I-structure. When a write occurs, all pending reads are dequeued and processed. If a write occurs to a cell which has already been written, then a run-time error occurs. This is an efficient way to enforce single assignment.

I-structures do have a referential transparency problem. Referential transparency demands that the values returned by two calls to the same constructor function with the same arguments must never be distinguishable. Thus, in a functional language, one can never alter a data structure once it has been created, and consequently one must specify the contents of all elements of the structure at creation time (as in VAL/SISAL [A&O85] and LUCID [W&A85]). Since ID Nouveau includes I-structures, and I-structures do not specify the contents of all elements at creation, ID Nouveau is not a completely functional language. Yet it is still single assignment and declarative.

Referential transparency can be given up but determinacy cannot. If a language possess the Church-Rosser property [Lan65], also called the confluence property, then overall program determinacy is guaranteed even if the machine exhibits non-determinacy in instruction scheduling. The Church-Rosser property requires that the answer computed by an expression be unaffected by the choice of which subexpressions are evaluated first. Since I-structures enqueue all early reads until the cell is written to, and each cell is single assignment, I-structures have the Church-Rosser property. No matter how one interleaves the execution of reads and writes, every fetch to a given I-structures element always returns the same value.

#### Discussion

ID Nouveau is highly developed language system with many sites using its development environment (ID-World). The ID Nouveau language reference manual [Nik87a] describes a complete environment with a compiler, a context sensitive editor, and simulators with parallelism detectors.

In [A&E88] a convincing argument is made for single assignment programming of scientific programming. In this technical report the SIMPLE hydrodynamics and heat conduction problem is detailed, and an efficient ID Nouveau program is designed. This design is then contrasted with a parallel version of the program in annotated FORTRAN where each program does the same number of arithmetic, load, and store operations.

#### 1.2.3. Hybrid Dataflow

Since Dennis first described the first dataflow execution model [Den75], many architecture designers have attempted to apply the model to real systems. Dataflow is attractive because all parallelism in a program is exposed for potential concurrent execution. In spite of the elegance of the model, dataflow is not widely used after more than twenty years of research. The focus has instead turned to the evolution of modern systems by extending them with dataflow techniques. The results of research in this area include hybrid systems using large-grain or macro dataflow [Bab84, B&E87, DFL89, Ian88, Kap86, L&G86, S&H87].

Iannucci [Ian88] has reported on a hybrid dataflow / von Neumann architecture. This approach is similar to PODS in its use of ID Nouveau as the input language and split-phased structure access. However the Iannucci approach uses a finer grain scheduling approach, called *scheduling quanta* (SQ). An SQ of two to three instructions is desirable for Iannucci's approach, and each iteration of a loop is a new SQ. In PODS, however, the

natural decomposition of the program is used and SPs are allowed to run-in-place, thus reducing overhead. Another difference is in data structure distribution. There is no mechanism for spreading iterations of a single loop across processors in Iannucci's approach. Combining data structure distribution with loop distribution is a central goal in PODS. Finally Iannucci's model requires a special purpose architecture capable of fast context switching among very small SQs. PODS tries to generate SPs large enough to produce good computation-communication ratios on available distributed memory multiprocessors. Certainly PODS would benefit from a tailored architecture, but the model itself is not restricted to such.

In [G&H89], Goldberg and Hudak presented Alfalfa, a system similar at a high level to PODS. They have implemented the ALFL functional programming language and run-time system on an Intel iPSC hypercube using what they call *serial combinators*. Serial combinators are similar to PODS SPs in that they are sequential threads that execute on a von Neumann processor. The run-time system handles thread creation and distribution. The main focus of their work is the study of the effects of dynamic scheduling (diffusion scheduling) of parallel threads of execution. They show that diffusion scheduling works well in many cases, however, they have not addressed the problem of distributing large data structures such as arrays. This is illustrated through the relatively poor performance achieved with the Matrix Multiply algorithm.

#### 1.3. Overview of PODS Execution Model

The primary objective of PODS is to achieve an efficient execution model for dataflow programs by reducing the overhead associated with scheduling each instruction individually [Bic90]. The greatest deficiency of the pure dataflow model is the excessive communication and token matching overhead associated with passing data from one

operation to another. These operations may lie on the same or different processors, thus potentially forcing token traffic over the processor interconnection network.

Originally it was thought the normal communication overhead could be reduced by grouping the instructions into threads. This was based on the observation that many threads of instructions in the dataflow graph must be executed sequentially due to inherent data dependencies. Grouping instructions in this manner is similar to Babb's Large Grain Data Flow (LGDF) [Bab84]. However, it was found this produced SPs which were too small for the communication to computation ratio of typical distributed-memory machines.

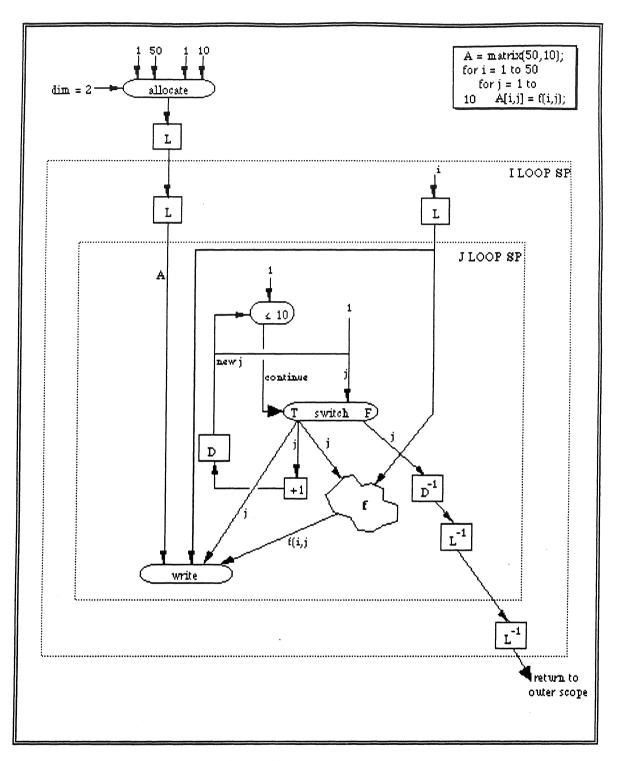

#### 1.3.1. Subcompact Processes (SP)

In order to overcome the small SP problem, a different approach was tried and found to be sufficient. This approach uses the code-blocks inherent in the program. Each code-block is a different SP, which will then be distributed by the Partitioner as necessary. This is how PODS exploits the iteration level parallelism in a program.

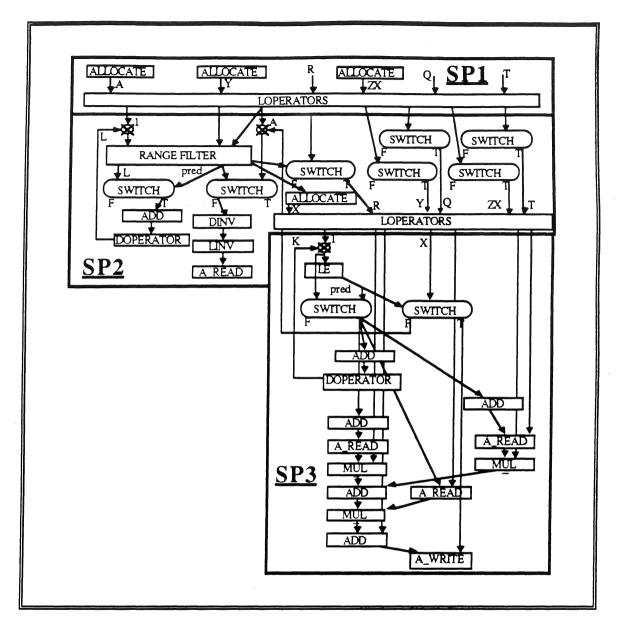

The code fragment below in Figure 1.5 shows a simple nested loop. For this loop there are three different program scopes which turn into SPs. The first takes care of initial actions, mainly array allocation. The second handles the L level of the loop, and the third handles the K level and the actual computations.

```

(initial A := < >; Y := < >; ZX := < >

for L from 1 to LOOP do

new A := (initial X := < >

for K from 1 to 1000 do

new X[K] := Q + Y[K]*(R* ZX[K+10]+T*ZX[K+11])

return X)

return A[1])

```

FIGURE 1.5. SUBCOMPACT PROCESS EXAMPLE CODE.

Figure 1.6 shows the code fragment as a dataflow diagram. The SPs are outlined in bold lines. Notice that the SPs are grouped so that each one will be as independent from the others as possible. This is were the parallelism is. SP1 allocates the arrays and then passes that information on to SP2. There may be multiple versions of SP2 running (if it is distributed), each executing only part of the *L*-loop. Each SP2 will then spawn SP3, which will run in-place (SP3 would never be distributed if SP2 were). In Chapter 2 the algorithm for distributing SPs is discussed in detail.

FIGURE 1.6. PODS SUBCOMPACT PROCESSES EXAMPLE.

#### 1.3.2. State Transitions

Once the static SPs are formed they will need to be scheduled for execution. Instead of scheduling individual operators of a dataflow graph for execution, the level of granularity is changed to that of an SP. An SP is *passive* as long as its *first* operator is disabled (i.e., it is still missing some operands). A passive SP resides in program memory. When all

operands for the first operator have arrived, the SP becomes *active*. This is accomplished by loading the SP into execution memory and creating a simple process control block (PCB) for it. The PCB contains the following information:

- the starting address of the SP in execution memory

- a program counter pointing to the current instruction

- a status field indicating whether the process is running, ready, or blocked.

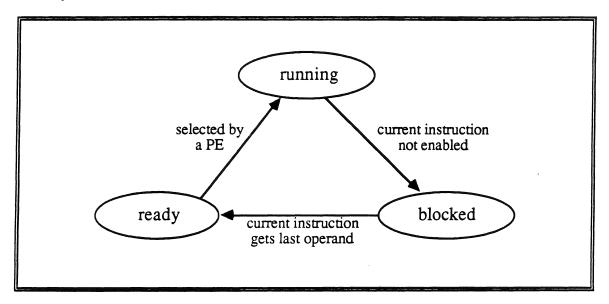

The three states are defined as follows. An SP is said to be *running* when a PE is currently fetching and executing instructions from that sequence. An SP is *ready* when its current instruction is enabled (has all its operands), but the PE is not available to execute that SP. Finally, an SP is *blocked* when its current instruction is not enabled.

FIGURE 1.7. PROCESS STATE TRANSITION DIAGRAM.

The possible state transitions are illustrated in Figure 1.7. Initially, an SP is loaded into execution memory in the ready state. Whenever the PE becomes free, it begins executing one of the ready SPs in its execution memory; at that time, the status of the selected SP changes from ready to running. The PE continues executing the SP until it reaches the end

of the SP (at which time it is destroyed) or until it encounters an operator that does not yet have all its operands present. In the latter case, the SP is blocked and the PE switches to another ready SP. The blocked SP changes its status to ready as soon as the last operand for the current instruction arrives.

This process-oriented viewpoint permits us to execute a dataflow program as a collection of communicating SPs. A given dataflow program is transformed into one or more SPs, which are mapped onto the available PEs. Each SP continues executing as long as it has all the operands necessary to perform its current operation. When an operation produces a result token destined for a subsequent operation within the same SP, it is passed directly to the destination operand slot using a simple memory operation. Only when the token is destined for a different SP must it travel through the dataflow routing network (within the same PE or to another PE) and pass through the matching store. It is important to note that the amount of resources need for a particular SP is known at load time. With this information the amount of parallelism can be reduced if necessary.

#### 1.3.3. Distributed Memory Approach

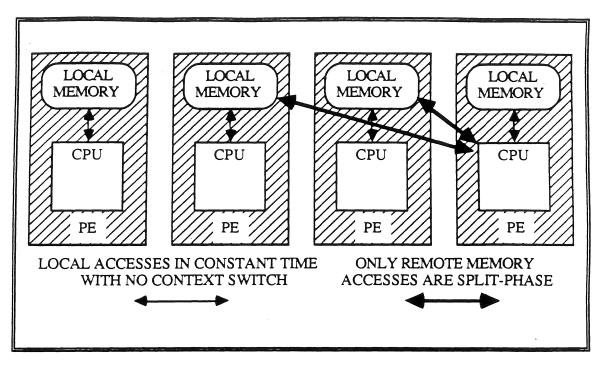

In PODS, the memory is distributed as shown in Figure 1.8 below. The physical separation between the PEs is recognized and exploited. Remote memory requests are performed in a *split-phase* manner. This allows the CPU to continue processing during the long remote memory latency. Local memory requests are handled instantly and do not cause the CPU to context switch. This is one reason PODS is able to exploit the power of massively parallel distributed-memory machines.

FIGURE 1.8. PODS MEMORY ACCESSING SCHEME.

#### 1.3.4. Discussion

This model of execution has a number of advantages. Since it uses a program counter, loops can be run in place efficiently. If necessary, due to dependencies, PODS can drop into completely sequential execution. When a process block occurs, the execution unit performs a simple context switch (no register storage is necessary) and takes the next ready SP off the ready list. And array accesses are split-phased to allow the long memory latency to be tolerated.

In summary, PODS uses a combination of dataflow and von Neumann models of computation. It uses single assignment to reduce side-effects which aides parallelism. The declarative nature of ID, and its implicit programming of parallelism, allows the programmer to ignore the architecture, which increases programmer productivity. For a more detailed description of the execution model, the reader is referred to [Bic87, Bic90].

#### 1.4. Contributions of this Research

This research has made contributions on many levels. It extends the existing models (the PODS Execution Model and ID Instruction Set). It presents new principles and algorithms (for partitioning and distribution). It exploits the abilities of old concepts in new ways (Remote Array Caching). It explains how all of these can work together in a logical manner (Logical Architecture). And it shows that this approach is efficient and scalable (the simulations).

#### 1.4.1. Execution Model Extensions

The PODS Execution Model was extended to allow iteration level parallelism. The previous model, based on the concept of sequential threads, produced SPs which were too small. The extension to iteration level parallelism allows larger SPs which are more easily distributed.

#### 1.4.2. Partitioning and Distribution Model

The new PODS Partitioning and Distribution Model is based upon two existing and three new principles of parallel execution. The existing principles (the Equal Distribution Principle and the Centralization Principle) are well known and are continually pushing in opposite directions. The new principles (the Grouping Principle, the Virtual Sources Principle, and the Collector Writes Principle) explain ways in which the two existing principles can be managed.

From these five principles, two partitioning and distribution algorithms were derived. The first shows how data should be partitioned and distributed to balance work load and speed up accesses. The second describes how code should be partitioned and distributed to balance parallel execution with communication costs.

Three primary and two secondary mechanisms were devised to make these algorithms work. The first primary mechanism is a distributed array allocate operator which distributes data. The second is a distributed L operator; it spawns processes across the PEs to distribute code. The third is an index range filter for restricting the indices for different PEs. These form the basis for PODS distributed processing. The secondary mechanisms are: an APPLY operator for functional distribution; and remote array caching for efficient array accesses. Together these provide an efficient means of applying the new partitioning and distribution algorithms.

# 1.4.3. Remote Array Caching

Remote Array Caching is a new approach similar to the concept of virtual memory and based upon the Virtual Sources Principle. This allows arrays to be accessed as if there were local to every PE. The locality-of-reference of computer programs is heavily exploited in Remote Array Caching.

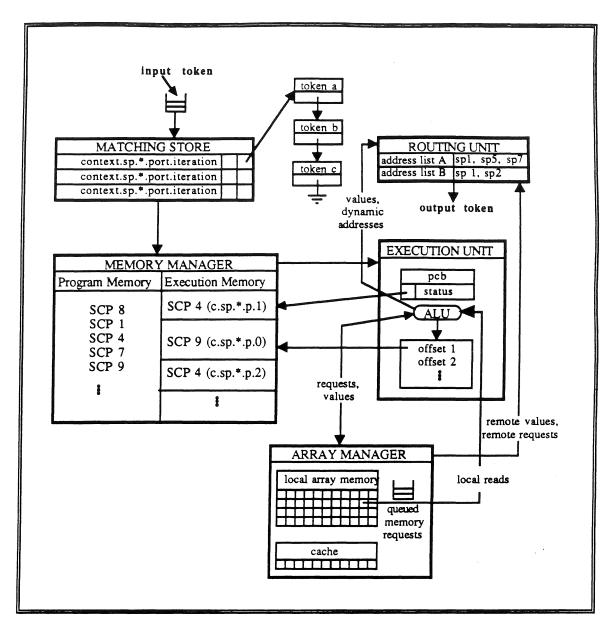

# 1.4.4. Logical Architecture

A description of how all of these new concepts and approaches are implemented are contained in the Logical Architecture. The functional units in a PODS PE are: the Execution Unit, the Matching Store, the Routing Unit, the Array Manager, and the Memory Manager. Each of these is designed to run in parallel with the others.

Extensions to the ID instruction set were necessary to allow PODS to execute on a von Neumann CPU. Some of these extensions involve the addition of a program counter to each instruction's semantics. Others involve extensive modifications of existing instructions (e.g. the L operator), and finally others involved totally new instructions to support the PODS Range Filters (e.g. INTERVAL\_COUNT).

# 1.4.5. Simulations

The PODS Translator, Partitioner, and Simulator were designed and written to test PODS concepts. The simulations were necessary to test the logical architecture for correctness and efficiency. These simulations have shown PODS to be an efficient and viable approach.

#### CHAPTER 2

# PODS Partitioning and Distribution Model

The performance of PODS comes from its ability to map the inherent granularity of a program onto a given architecture. The inherent granularity of a program comes from its block structure. The larger (smaller) the loops and procedures, the larger (smaller) the granularity. This granularity controls the size of the PODS SPs. The partitioning and distribution model allows the hybrid nature of PODS to be exploited: sequential code is run on an efficient von Neumann processor, and parallel code is distributed such that communication costs are not prohibitively high. This is not to say that *all* programs will run well on PODS, bad code can be written for any computer system. The aim of this model is to handle the large majority of code which will be executed on distributed memory MIMD machines and to flag code which is poorly written.

The key elements of PODS partitioning and distribution are:

- array partitioning, which uses a simple page grouping scheme to allow equal load across the PEs;

- 2. array distribution, which follows the partitioning such that each PE produces only those elements for which it is responsible;

- loop distribution, which considers data dependencies when distributing;

- 4. functional distribution, which attempts to off-load functions if the calling PE is overloaded.

Chapter 2 is organized as follows: (1) a quick overview of the model; (2) presentation and discussion of the underlying principles; (3) a detailed discussion of PODS instructions and processes; (4) a discussion of array partition and distribution; (5) an in-depth examination of process distribution; (6) a discussion of functional distribution; and finally (7) a discussion of deadlock handling.

#### 2.1. Overview

In order to exploit a program's parallelism, the program must be partitioned, an activity that has been the subject of much research. Because optimal partitioning is NP-complete, these partitioning techniques strive for near-optimality, usually through the use of heuristics or programmer supplied directives. PODS performs partitioning automatically using the decomposition implied by the program structure. Programs are broken into code-blocks by the ID Nouveau compiler and replicated on each PE, making all processors homogeneous with respect to code. The key problem with partitioning and distribution in PODS is that of determining where to send tokens that activate SPs. Since the PEs are homogeneous, an instance of a specific SP can be executed anywhere simply by routing the initial activating tokens to a specific PE. Because each PE is aware only of its own state, this routing decision is binary: should an SP execute locally or remotely? PODS decides which SPs will be distributed and which will run locally at compile time. At run-time PODS decides where the distributed SPs will be executed. The exact methods for this distribution are explained in this chapter.

Simply put, the PODS partitioning and distribution uses data distribution to control execution distribution. There are two basic conceptual steps to achieve this.

1. Using a simple global algorithm, partition the data and allocate each partition to a PE.

2. Execute the program such that the owner of a particular array element will write that element.

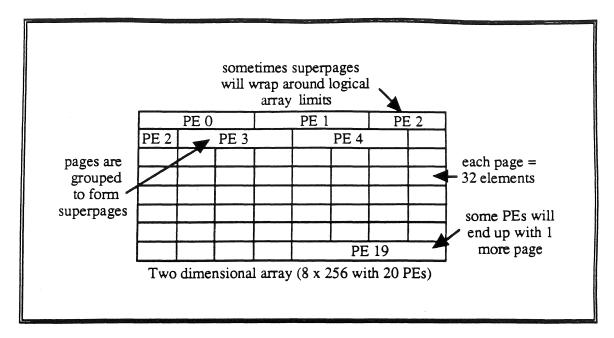

By using a simple global algorithm for array partitioning, each PE can easily calculate where a particular array element is located during execution. This additional checking costs 29% more cycles for each array read or write, but allows arrays to be accessed in parallel with little or no communication and without context switching.

In order to realize the above, the following tasks are performed:

- Arrays are cut-up into pages of fixed size X, where X is determined by the hardware architecture.

- 2. Arrays are grouped into superpages which are assigned to PEs sequentially.

- Execution follows the array partitioning and distribution if it is executing loop code which has no Loop-Carried Dependencies (LCDs).

- 4. For code with LCDs, the execution will stay on the current PE unless a function call is made.

- When a function call is made the execution may move to another

PE depending upon the length to the current PE's task list.

There are three primary mechanisms for achieving data parallelism. These mechanisms are:

The ALLOCATE Operator: used to distribute data (data parallelism).

- 2. The DIST-L Operator: used to spawn processes on all PEs.

- 3. The RANGE-FILTER Operator: used to restrict loop indices ranges for different PEs.

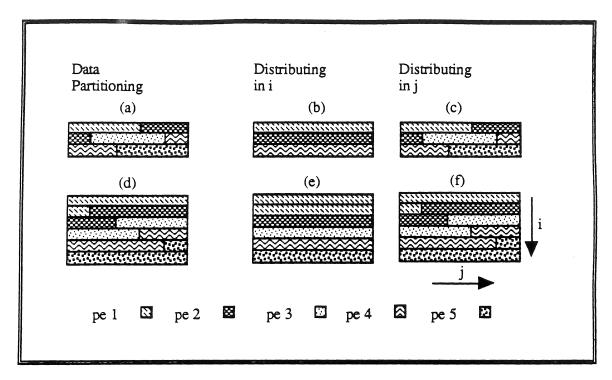

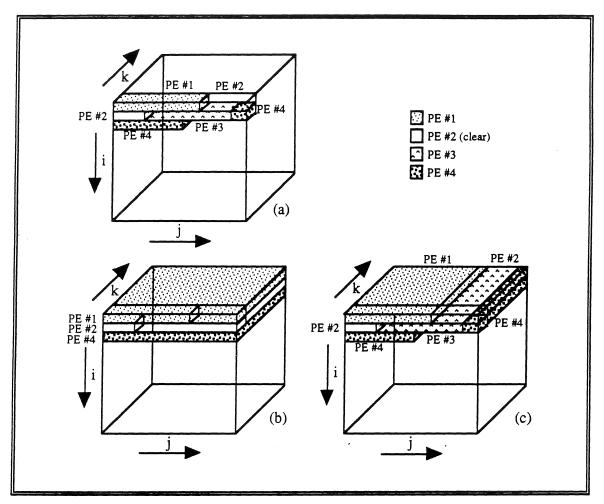

The basic approach to distribute code for data parallelism is to:

- 1. distribute the arrays

- 2. decide which level of the nested loop to distribute

- this level gets the RANGE\_FILTER while its parent gets the DIST-L operators.

The mechanism for functional parallelism:

1. The APPLY Operator: used to spawn function calls on a single remote PE (functional parallelism).

In this way the work load is partitioned at compile time and distributed using an efficient run-time algorithm without the programmer's explicit instructions.

#### 2.2. Underlying Principles

There are two basic principles which apply to any parallel system. They are:

- 1. The Equal Distribution Principle

- 2. The Centralization Principle

These two are supplemented by three PODS specific principles. These principles show ways in which the two basic principles can be reconciled somewhat. The PODS specific principles are:

- 1. The Grouping Principle

- 2. The Virtual Sources Principle

- 3. The Collector Writes Principle

By using each of these principles, PODS is able to provide efficient execution of scientific programs on MIMD machines. Each principle is explained below.

# 2.2.1. Basic Principles

For any assignment to be accomplished, the RHS calculations must be performed and the writing of the element must occur. Consider the simple assignment below:

```

A[i] = sqrt(B[i+1] + C[i]) * exp(D[m+i])

```

FIGURE 2.1. SIMPLE ARRAY ASSIGNMENT.

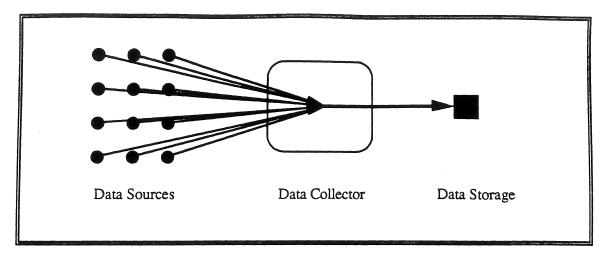

In this statement B[i+1], C[i], and D[m+i] are data sources which need to be collected together so that the calculations can be performed. Once they are performed the assignment can occur. The diagram below illustrates these how these three agents interact. Note that each data source, the data collector, and the data storage could be on different PEs.

FIGURE 2.2. EQUAL DISTRIBUTION PRINCIPLE.

In order for the data sources to respond to multiple data collectors simultaneously they should be spread over all the available PEs. Since the access patterns are not know a priori, each PE should get an equal number of data sources. This is the Equal Distribution Principle. More concisely,

#### Definition: Equal Distribution Principle

In order to allow maximum parallel access, data sources, data collectors, and data storage should be distributed equally among the available PEs.

This principle is implemented in PODS by partitioning each array and distributing the pieces equally among the PEs.

The Centralization Principle concerns the cost of communication and the overloading of the interconnect network. Once the agents are widely distributed a problem occurs. The communication costs become extremely high. In order to reduce the effects of communication delays, all of the items (data sources, data collectors, and data storage) should be kept together (i.e. centralized). This is the Centralization Principle which states:

# Definition: Centralization Principle

In order to reduce communication costs and network overloading, data sources, data collectors, and data storage should be centralized on one PE.

These two principles are obviously in conflict. The PODS specific principles below show how the balance can be tilted in favor of distribution.

# 2.2.2. PODS Specific Principles

# Grouping Principle

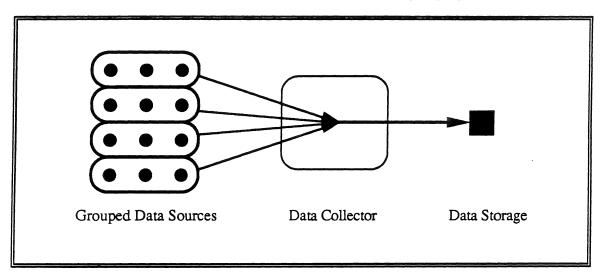

In order to reduce the effects of communication delays without completely centralizing, the data sources should be grouped together until some size, x, is reached. The diagram below shows how the number of communication lines is reduced by grouping.

FIGURE 2.3. GROUPING PRINCIPLE.

This is the Grouping Principle which states the following.

# Definition: Grouping Principle

In order to reduce communication over the network, data sources should be grouped together until some reasonable size is reached.

This principle fights against the Equal Distribution Principle, a balance between them must be maintained. In PODS this is achieved by grouping the arrays into pages of a fixed size which is only dependent on the hardware architecture.

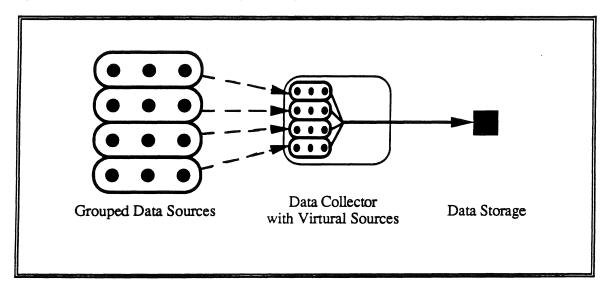

#### Virtual Sources Principle

One aspect of single assignment is that data sources never need to be updated. This can be exploited by moving copies of the data sources into the collector for easy access. Locality of reference implies that the grouped data sources should be moved in toto when one of the data sources is needed. The diagram below shows how the amount of communication can be reduced by caching the data source in the collector without any cache coherency problems; the dashed lines are truly one way.

FIGURE 2.4. VIRTUAL SOURCES PRINCIPLE.

This is the Virtual Sources Principle which states the following.

# Definition: Virtual Sources Principle

Since each data source will never need to be updated, a copy should be moved into the data collector when any one of the grouped data sources is needed. The Virtual Sources Principle states that a single assignment system should cache data sources in its local memory to form a virtual source to reduce communication.

This principle allows remote reads to be reduced in PODS, and is implemented by remote access caching.

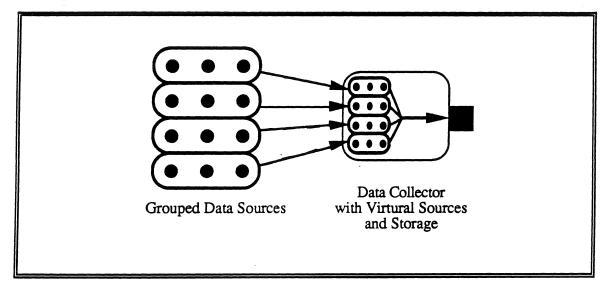

# Collector Writes Principle

In a single assignment system there will be only one write to a particular array element. The thick black arrow in the diagrams above represents this write. Since there is only one collector and one write, these two should be on the same PE. The diagram below shows this.

FIGURE 2.5. COLLECTOR WRITES PRINCIPLE.

The producer of an array element is the PE which collects the RHS calculations needed for the formation of a LHS value. This PE, the collector, becomes the writer by executing the WRITE\_ARRAY instruction which assigns that array element a value. Since the single-assignment principle is in force; there will be one writer. This is the Collector Writes Principle which states the following.

# Definition: Collector Writes Principle

The Collector Writes Principle states that the system should map an array element such that the PE which holds that array element in its local memory (the owner) shall be the collector of the RHS data sources, and shall also be the writer of that array element.

This principle, in collaboration with the other principles, forces the execution to follow the data distribution. In PODS this is called Data Distributed Execution.

#### 2.3. PODS Instructions and Processes

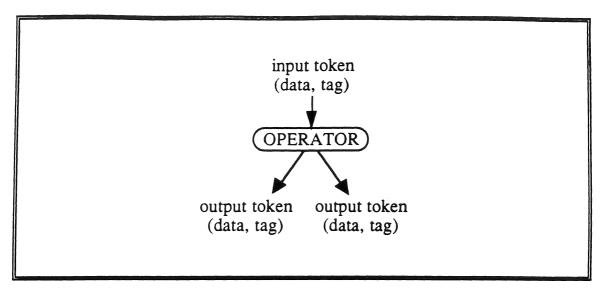

The basic concept of a dataflow operator has *not* changed, only the *implementation* of that concept. In PODS dataflow operators are implemented using PODS instructions. The basic dataflow concept (shown below) allows the dataflow graph to execute cleanly; without leaving tokens unconsumed.

FIGURE 2.6. BASIC DATAFLOW OPERATOR.

The standard dataflow implementation of this concept performs the following steps when a token arrives:

- 1. consume input tokens

- 2. compute new data value

- 3. compute new tag

- 4. form new output tokens

- 5. send output tokens to destination operators

For PODS this implementation needs to be modified to contain the concept of an SP's state. An SP's state is basically a PODS activity name, which is discussed next in Section 2.3.1.

# 2.3.1. Activity Names

An activity name is the colored tag which identifies a token's complete context. What is presented below is a logical implementation, a physical implementation would use unique

frame IDs. Logically, activity names consist of two parts: (1) the static part which is known at compile time; and (2) the dynamic part which is built as the token moves from context to context. Figure 2.7 below shows the make-up of an activity name.

|         | Activity Name |    |             |      |

|---------|---------------|----|-------------|------|

| Dynar   | Dynamic Part  |    | Static Part |      |

| context | iteration     | sp | instruction | port |

FIGURE 2.7. ACTIVITY NAME COMPONENTS.

The static part is know by the compiler from the dataflow graph once the SPs are built. The dynamic part is based upon the incoming token's activity name and is only affected by the context manipulating functions: D and D\_INVERSE, L and L\_INVERSE, A and A\_INVERSE. The activity name is also known as the *tag*. The individual subparts are listed below, along with their function.

- context: holds the pointer to past activity names, affected by L

and L\_INVERSE, A and A\_INVERSE. The context holds a token's

tag in a linked list. This list represents all of the execution

scopes through which a given token has passed. This

information is necessary for PODS to know how to move a

token from one execution scope (i.e. SP) to another.

- iteration: holds the current iteration number, affected by D and D\_INVERSE.

- sp: holds the SP number, based on partitioned dataflow graph.

- instruction: holds the instruction number within this SP.

• port: holds the port number within this instruction, usually 0 or 1.

#### 2.3.2. PODS Instruction Format

There are three types of PODS instructions. These types indicate how the instruction was derived from the output of the ID Nouveau compiler. The first type is formed from a simple mapping from TTDA instructions and PODS instructions. These are the basic instructions such as ADD, and ARRAY\_READ. The second type actually disappears when the output is translated. These are the IDENT instructions which are used for synchronization. These are not needed because the sequential nature of SPs synchronizes instructions automatically. The third type is composed of new instructions which are added or modified to accomplish the distribution. These are the SWITCH, FORKJUMP, D and D\_INVERSE, L and L\_INVERSE (in both dist and local forms), A and A\_INVERSE, and ALLOCATE. Each of these will be explained as they are encountered in this chapter.

PODS instructions have the following fields (see Figure 2.10 for an example):

- 1. Op Code operation to be performed.

- 2. Number Arguments the number of arguments this operation needs before it is ready to fire.

- 3. Operand List slots for values of operands. Initially some of the operands are constants which are set at compile time. Each constant is represented by the pair (value, port). Other operand ports are flagged with a special "sticky bit" (STKY) which means that once a token is received on that port, it is then held there and does not need to be replenished for the instruction to fire.

- Local Destination List output value destinations which are within this SP. Each destination is represented by the pair [instruction number, port].

- 5. Route ID ID of route to be used when output tokens are to be sent to other SPs. This is not a list because the routing information is stored in the Routing Unit and not in the Execution Unit. A route ID is simply a short-hand for: [SP ID, instruction number, port] ..., see Chapter 3 for complete details.

- 6. Comments variable names from the source code, shown in brackets, "{}".

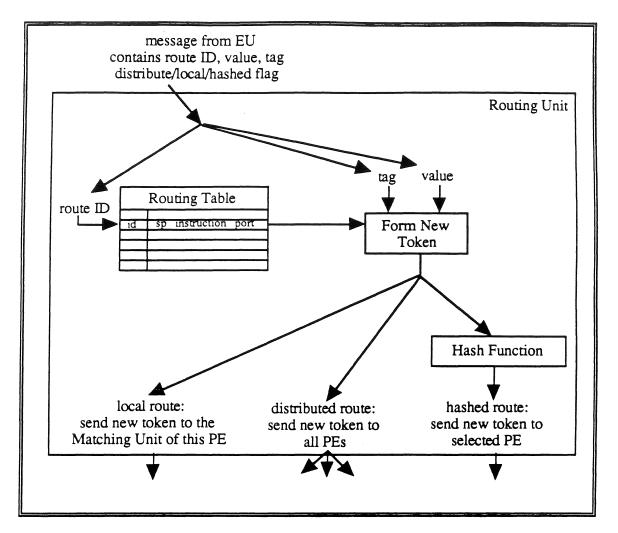

Values can be sent using any of the following paths:

- Using the local destination list. This is the way almost all of the operators communicate. Only L and A operators can send tokens to other SPs.

- 2. Using the route list. This is performed in one of three ways depending on the type of L or A operator. Only L or A operators have routes.

- (1) the DIST-L operator sends tokens to SPs on every PE.

- (2) the LOCAL-L operator sends the token to a different SP on the same PE.

(3) the A operator sends the token to a different SP on some PE. Which PE is decided by a hash function.

#### 2.3.3. PODS Dataflow Operator Implementation

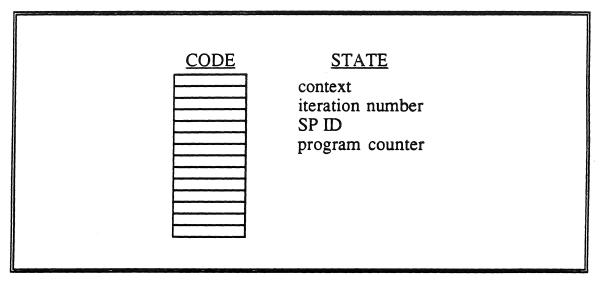

In PODS, an SP contains code and a state. The code represents the operations to be performed and the state holds the status of these operations.

FIGURE 2.8. SP COMPONENTS.

When a token arrives at a PODS operator the state of the SP is used to decide the steps to execute this operator. All of the original ID operators which are not special operators are called basic PODS operators. All of the special operators are discussed individually after a discussion of the basic PODS operator implementation.

The basic PODS operator implementation performs the following steps when a token arrives:

- 1. Consume input tokens.

- 2. Compute new data value.

- 3. Compute new tag.

- 4. If the context and SP ID are the same, then no tokens are formed, only data is stored into destination instruction and port.

If either of these has changed, then form new output tokens and route them using the routes specified for this operator.

- 5. Increment the program counter.

This implementation is the same as the basic dataflow version in Steps 1 - 3. Step 4 however now checks the SP state to see how to deal with the output data, whether to store it locally within this SP or to form a token and route it to another SP. Notice that Step 4 does not check the iteration number of the tag. This is because the iteration number can only be changed by a D operator, and D operators do not change SP. Step 5 has been added to increment the program counter. There are a couple of operators (the D and FORKJUMP operators) which set the program counter to a value rather than just incrementing it. All other operators follow these steps exactly. What follows is a description of the new PODS instructions, and why these implement the same semantics as the original ID operators.

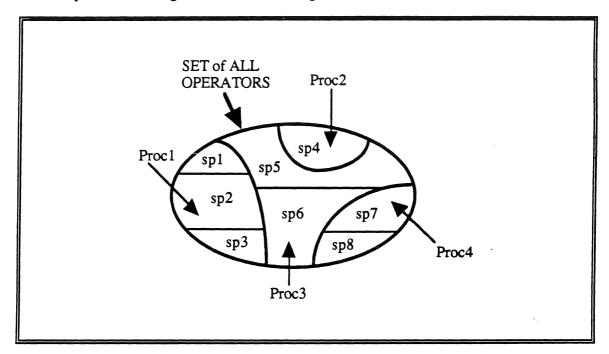

In order to show that the semantics of the original ID operators have not changed each operation type will be addressed. It is quite simple to understand the way in which PODS implements the semantics of ID. The original ID had the following fields in its tag: context c, procedure p, statement number s, and iteration i. As explained above in the section on activity names, PODS uses a context c, a SP ID sp, an instruction number si, and an iteration i. PODS uses the context and iteration exactly the same, it is only the procedure and statement number which differ.

Basically the procedure cuts the dataflow program into subsets, and the statement number identifies the operator within the subset. PODS uses the same approach but just cuts the collection into smaller subsets. In Figure 2.9 below, the set of all operators is cut into procedures Proc1 - Proc4 (in bold lines), while the SPs are just subsets sp1 - sp8. In this way the combination of the two field holds exactly the same information, i.e. the "address" of a particular operator. Also note that since each procedure cut is also an SP cut, then when a procedure change is made an SP change is also make.

FIGURE 2.9. ID VS PODS STATEMENT "ADDRESSING".

#### Arithmetic and Logical Operators

The vast majority of ID operators fit into this the class of arithmetic and logical operators. In the original ID these operators only changed the statement number and the value of the token. This can be expressed by:

ID Arithmetic & Logical

$c, p, s, i, v \rightarrow c, p, s', i, v'$

In PODS exactly the same value calculation is performed, and the instruction number is changed. Expressing this in a similar format to the above:

Notice that the "address" (sp, si) for the output token specifics the receiving operator just as is done in ID with (p, s).

The switch operator falls into this class and is discussed along with a new instruction (forkjump) below.

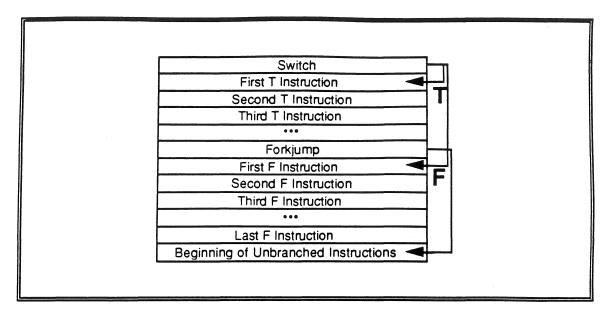

# SWITCH and FORKJUMP