Circuits and Control for High-Performance Grid-tied Ac-Dc Conversion Systems

by

Zitao Liao

A dissertation submitted in partial satisfaction of the

requirements for the degree of

Doctor of Philosophy

in

Engineering — Electrical Engineering and Computer Sciences

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Associate Professor Robert C.N. Pilawa-Podgurski, Chair Professor Seth R. Sanders Associate Professor Duncan Callaway Assistant Professor Minjie Chen

Spring 2021

Circuits and Control for High-Performance Grid-tied Ac-Dc Conversion Systems

Copyright © 2021 by Zitao Liao

### Abstract

## Circuits and Control for High-Performance Grid-tied Ac-Dc Conversion Systems

by

Zitao Liao

Doctor of Philosophy in Engineering — Electrical Engineering and Computer Sciences

University of California, Berkeley

Associate Professor Robert C.N. Pilawa-Podgurski, Chair

Ac-dc (and dc-ac) power converters are the interfaces between the electrical grid and the systems for emerging applications such as electric vehicle (EV) charging, renewable energy source integration, data center power delivery, consumer electronics and numerous other applications. In this dissertation, new circuit topologies and control techniques to improve the performance for both single-phase and three-phase grid-tied converters are explored for three major conversion scenarios: high power bidirectional single-phase ac-dc converters for EV charging and data center applications, low power single-phase ac-dc converters for consumer electronics, and high power three-phase ac-dc converters. For single-phase conversion, the challenge of twice-line frequency energy buffering is addressed with active buffering techniques that can significantly reduce the required capacitor size compared to conventional solutions. Through the development of active buffers with systematic multi-objective optimization methods and associated advanced digital control, the energy utilization ratios of the passive components are much improved, and the system losses are optimized. For threephase conversion, control and modulation techniques to reduce computational complexity and inductor current ripple are proposed and validated. The proposed circuit topologies and control techniques for both single-phase and three-phase are all validated with high performance hardware demonstrations. Some of the highlighted ones in this dissertation are: a 6 kW, 400 V<sub>dc</sub> single-phase liquid-cooled EV charger with optimized series-stacked buffer, achieving record power density; a 6 kW 400  $V_{dc}$  three-phase multilevel rectifier with advanced digital control techniques; an active single-phase buffer with the smallest reported capacitor size for 2 kW, 400 V<sub>dc</sub> inverters; a compact active buffer for 65 W USB-C charger.

"Learning without thinking is labor lost, thinking without learning is perilous"

- Confucius

# Contents

| С  | ntents                                                                                                                                                                                                                                                     | ii                                |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|

| Li | at of Figures                                                                                                                                                                                                                                              | v                                 |

| Li | t of Tables                                                                                                                                                                                                                                                | xiii                              |

| 1  | Introduction1.1Grid-tied Ac-dc and Dc-ac Conversion1.2Research Scope and Goals1.3Organization of Thesis                                                                                                                                                    | <b>1</b><br>1<br>3<br>4           |

| 2  | Single-Phase Energy Buffer Background         2.1       Ideal Energy Buffering in Single-phase Converters         2.2       Passive Solutions         2.3       Active Solutions         2.4       Energy Storage, Passive Components and Converter Sizing | <b>5</b><br>7<br>12<br>16         |

| 3  | Operation Principle and Constraints of the Series-Stacked Buffer3.1 Introduction to the Series-Stacked Buffer Topology3.2 Operation Principle3.3 Operation Constraints for Major Passive Components3.4 Comparison to Previous Work on Component Sizing     | <b>19</b><br>19<br>19<br>21<br>23 |

| 4  | Control and Modeling of the Series-Stacked Buffer         4.1 Equivalent Impedance Modeling for the SSB         4.2 Voltage Control of the SSB Based on the RLC Model         4.3 Control Limitations with Small $R_s$                                     | <b>27</b><br>27<br>29<br>33       |

| 5  | Multi-Objective Design Optimization of the Series-Stacked Buffer5.1Motivation for Multi-Objective Design Approach5.2Series-Stacked Buffer Operation Constraints5.3Loss and Volume Objective Functions5.4Optimization Formulation                           | <b>35</b><br>35<br>36<br>40<br>43 |

|    | $5.5 \\ 5.6 \\ 5.7 \\ 5.8$                                                 | Optimization Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | $45 \\ 50 \\ 54 \\ 56$                                                                                                                                 |

|----|----------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6  | Hig<br>6.1<br>6.2<br>6.3                                                   | h Power Density Full Ac-dc System Implementations with the SSB<br>Proposed Coupled Control for the SSB in PFC and Inverter Applications<br>Design and Implementation of a 1.5 kW Universal Input PFC<br>Design and Implementation of a 6 kW on-board EV Charger                                                                                                                                                                                                                                                                                       | <b>57</b><br>57<br>61<br>66                                                                                                                            |

| 7  | Hali<br>7.1<br>7.2<br>7.3<br>7.4<br>7.5<br>7.6                             | f-Bridge Series-Stacked Buffers for Low-power Flyback Rectifiers Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | <b>79</b><br>79<br>80<br>81<br>85<br>86<br>88                                                                                                          |

| 8  | Bip<br>8.1<br>8.2<br>8.3<br>8.4<br>8.5<br>8.6<br>8.7<br>8.8<br>8.9<br>8.10 | olar Multilevel Full Ripple Port Buffer         Introduction         Review of the Full Ripple Port Buffer         Buffer Control with Film Capacitors as the Main Buffer Capacitor         Challenges of Using Nonlinear Ceramic Capacitors as the Main Buffer Capacitor         Buffer Control with MLCCs as the Main Buffer Capacitor         Modulation Scheme for the two FCML Legs         Design and Implementation of the Full-Bridge FCML Converter         Experimental Verifications         Loss-Volume Tradeoff Study         Conclusion | <ul> <li>89</li> <li>89</li> <li>92</li> <li>94</li> <li>s 96</li> <li>100</li> <li>105</li> <li>109</li> <li>112</li> <li>118</li> <li>120</li> </ul> |

| 9  |                                                                            | and Modulation of Three-phase Flying Capacitor Multilevel         nverters         Introduction          Proposed Modulation Strategy          Digital Implementation of the Proposed Modulation Strategy          Hardware prototype and Experimental Validations          Conclusion                                                                                                                                                                                                                                                                | <b>121</b><br>121<br>123<br>135<br>136<br>139                                                                                                          |

| 10 | Con                                                                        | nclusions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 140                                                                                                                                                    |

| 11 | 11.1                                                                       | ure work<br>Series-Stacked Buffers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | <b>142</b><br>142<br>147                                                                                                                               |

| Bi | bliography                                                                   | 148 |

|----|------------------------------------------------------------------------------|-----|

| A  | Control Software/firmware Implementation in TI C2000 DSP for 6 kW EV Charger | 156 |

| в  | Source code repositories for other projects in the dissertation              | 158 |

iv

# List of Figures

| 1.1  | Typical single-phase conversion system block diagram for EV charging, data cen-<br>ter power delivery and solar inverter applications. | 2        |

|------|----------------------------------------------------------------------------------------------------------------------------------------|----------|

| 1.2  | Typical single-phase conversion system block diagram for low power USB-C adapter applications                                          | 2<br>2   |

| 1.3  | Typical three-phase conversion system block diagram for EV charging, data center<br>and solar inverter applications                    | 2        |

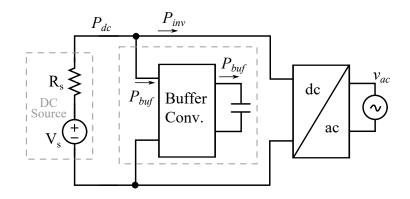

| 2.1  | Typical single-phase conversion system block diagram for EV charging, data cen-<br>ter power delivery and solar inverter applications. | 5        |

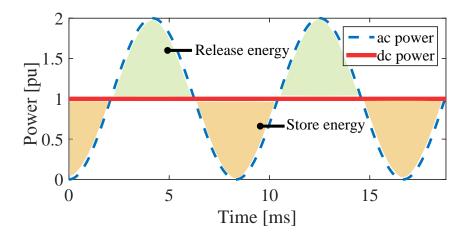

| 2.2  | Typical dc-ac power waveform and energy flow of the energy buffering device.                                                           | 6        |

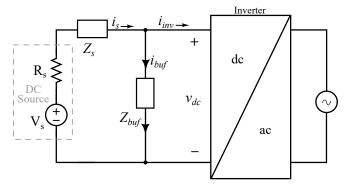

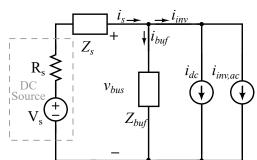

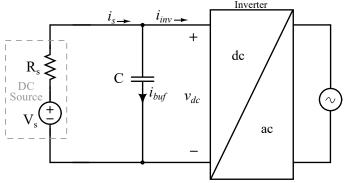

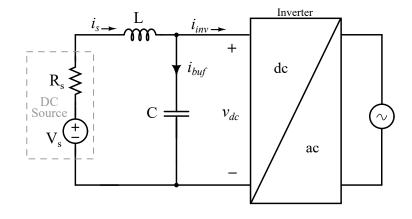

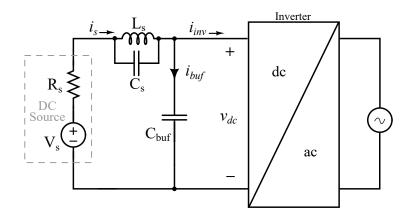

| 2.3  | General schematic of passive filter solutions for single-phase inverters                                                               | 7        |

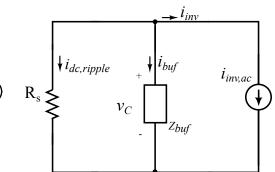

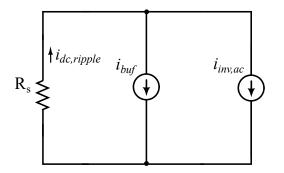

| 2.4  | Equivalent circuit of single-phase energy buffering with inverter load modeled as                                                      |          |

|      | current loads.                                                                                                                         | 7        |

| 2.5  | Dc-link capacitor bank solution.                                                                                                       | 8        |

| 2.6  | Ac equivalent circuit of the capacitor bank solution at twice-line frequency                                                           | 8        |

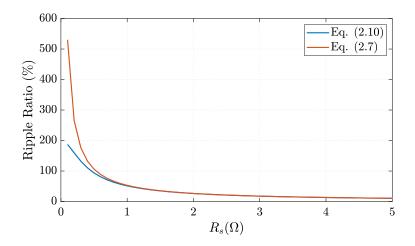

| 2.7  | Ripple ratio comparison using (2.7) and (2.10), with $C = 5000 \mu F$ , $I_{dc} = 5 A$ ,                                               |          |

|      | $\omega_{2L} = 2\pi \times 120 \text{ rad/s.}$                                                                                         | 10       |

| 2.8  | LC low-pass filter solution.                                                                                                           | 11       |

| 2.9  | Parallel LC notch filter solution.                                                                                                     | 11       |

| 2.10 | Series LC notch filter solution.                                                                                                       | 11       |

| 2.11 | Dc-side series compensator solution.                                                                                                   | 14       |

|      | Ac equivalent circuit of the dc-side series compensator.                                                                               | 14       |

|      | Buffer branch compensator solution.                                                                                                    | 14       |

|      | Ac equivalent circuit of the buffer branch series-stacked compensator solution.                                                        | 14<br>15 |

|      | Power port buffer architecture                                                                                                         | 15 $15$  |

| 2.10 | Equivalent ac circuit of the power port buller architecture                                                                            | 10       |

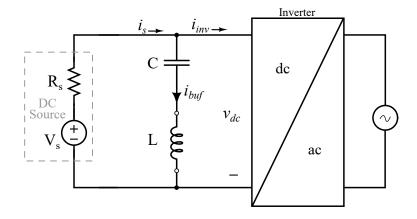

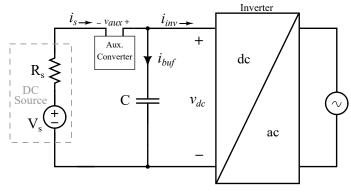

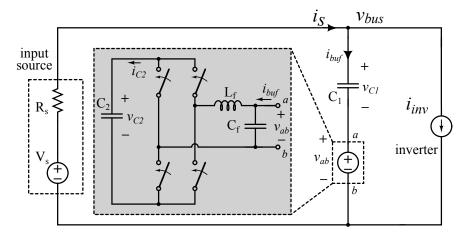

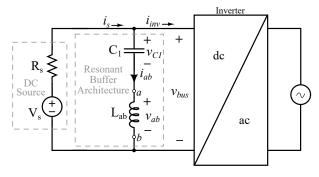

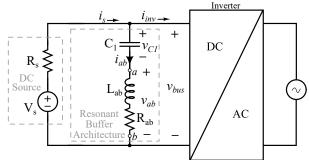

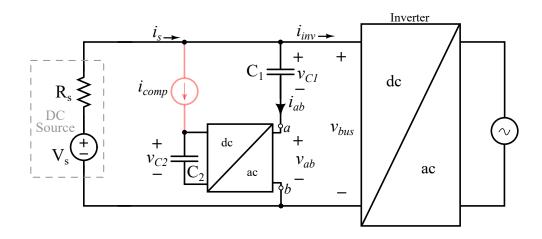

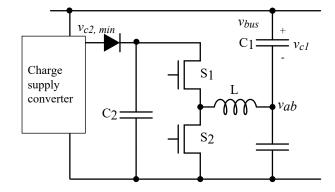

| 3.1  | The series-stacked buffer architecture with a dc source and an inverter (repre-<br>sented as a current load).                          | 20       |

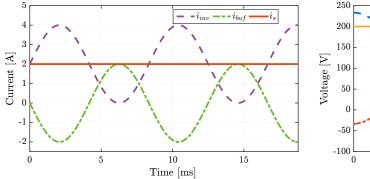

| 3.2  | The ideal current waveforms for the SSB. $C_1 = 80 \ \mu\text{F}$ , $V_{\text{bus}} = 200 \text{ V}$ , 400 W load power.               | 20       |

| 3.3  | The ideal voltage waveforms for the SSB. $C_1 = 80 \ \mu\text{F}$ , $V_{\text{bus}} = 200 \text{ V}$ , 400 W load power.               | 20       |

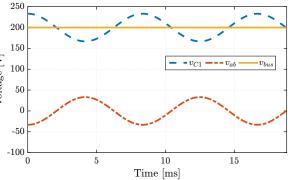

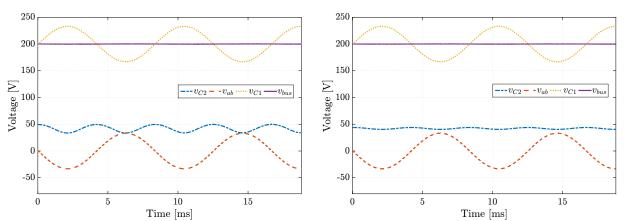

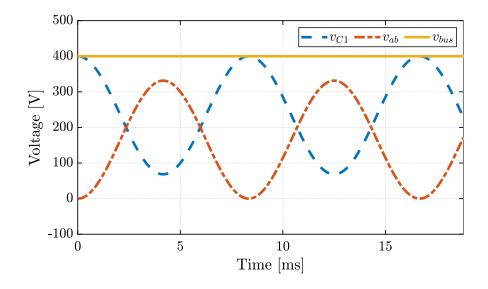

| 3.4 | Simulated voltage waveforms of the SSB in PLECS for the test case: $C_1 = 80$<br>$\mu$ F, $C_2 = 68 \mu$ F, $V_{C2, dc} = 42$ V, $I_{dc} = 2$ A                                                                                                                                 | 24              |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| 3.5 | Simulated voltage waveforms of the SSB in PLECS for the test case: $C_1 = 80$<br>$\mu F, C_2 = 307 \ \mu F, V_{C2, dc} = 42 \text{ V}, I_{dc} = 2 \text{ A}. \dots \dots$ | 24              |

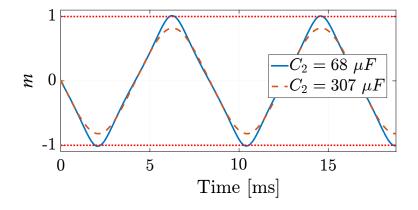

| 3.6 | Corresponding conversion ratios for $C_2 = 68 \ \mu\text{F}$ and $C_2 = 307 \ \mu\text{F}$ for the test case: $C_1 = 80 \ \mu\text{F}$ , $V_{C2, dc} = 42 \text{ V}$ , $I_{dc} = 2 \text{ A}$ .                                                                                 | 24<br>24        |

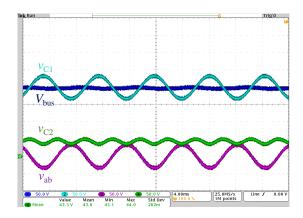

| 3.7 | Experimental voltage waveforms of the SSB for the test case: $C_1 = 80 \ \mu\text{F}, C_2 = 68 \ \mu\text{F}, V_{\text{C2. dc}} = 42 \text{ V}, I_{\text{dc}} = 2 \text{ A}.$                                                                                                   | 25              |

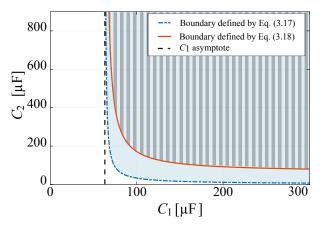

| 3.8 | Design space for $C_1$ and $C_2$ under the constraints: $V_{C2, dc} = 42$ V, $I_{dc} = 2$ A (solid-filled shaded area is confined by (3.17), and striped area is confined by (3.18)).                                                                                           | 25              |

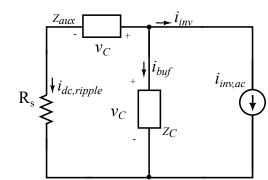

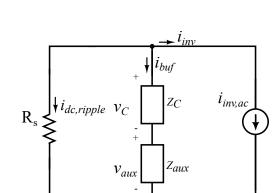

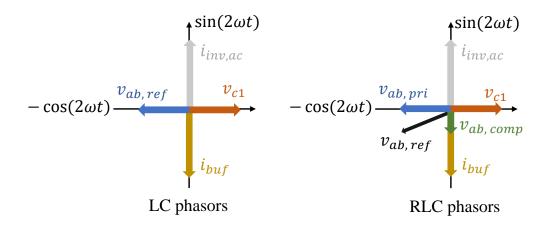

| 4.1 | Equivalent LC circuit of the SSB (figure created in collaboration with Nathan Breaks)                                                                                                                                                                                           | 28              |

| 4.2 | Brooks)                                                                                                                                                                                                                                                                         | 20<br>28        |

| 4.3 | Phasor diagrams at 120 Hz for both LC and RLC models of the SSB.                                                                                                                                                                                                                | $\frac{20}{28}$ |

| 4.4 | Voltage control method for the SSB [16]                                                                                                                                                                                                                                         | 29              |

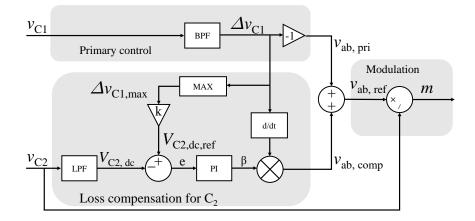

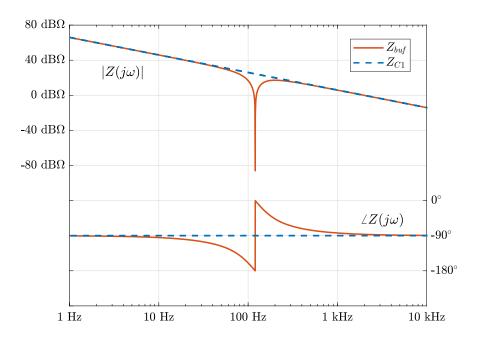

| 4.5 | Bode plot of the SSB impedance with the band-pass filter (figure created in collaboration with Nathan Brooks).                                                                                                                                                                  | 31              |

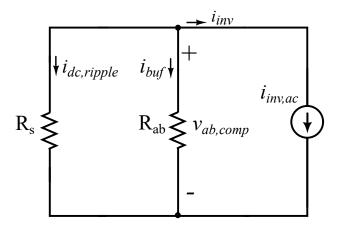

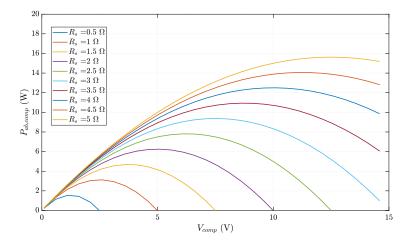

| 4.6 | Equivalent ac impedance of the SSB. The LC resonant tank is omitted because                                                                                                                                                                                                     | 01              |

|     | of their zero ohm impedance at resonance                                                                                                                                                                                                                                        | 31              |

| 4.7 | Real power at $ab$ terminal v.s. $V_{\text{comp}}$ with different $R_s$ .                                                                                                                                                                                                       | 32              |

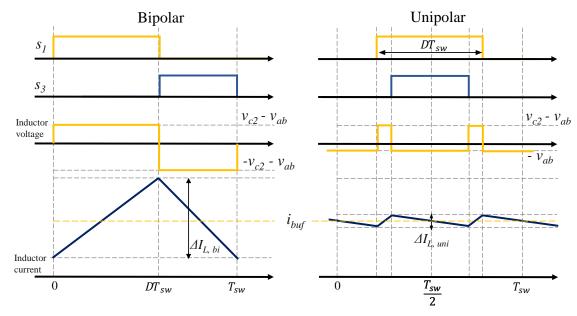

| 5.1 | Gate signals for $S_1$ and $S_3$ , inductor voltage and current waveforms of bipolar (left) and unipolar modulation (right) in a full-bridge with identical duty ratio and average inductor current.                                                                            | 38              |

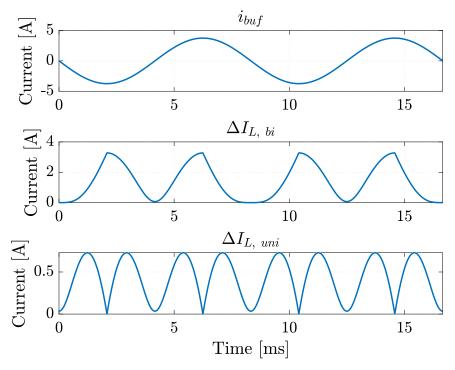

| 5.2 | Waveforms of $i_{\text{buf}}$ , $\Delta I_{\text{L, bi}}$ , and $\Delta I_{\text{L, uni}}$ under the condition: $C_1 = 80 \ \mu\text{F}$ , $C_2 =$                                                                                                                              | 39              |

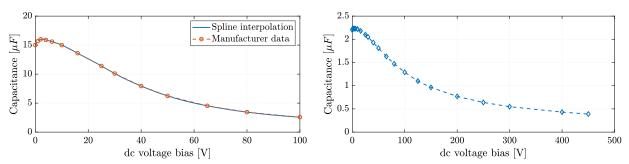

| 5.3 | 68 $\mu$ F, $V_{\text{bus}} = 400$ V, $L_f = 94 \mu$ H, 1.5 kW load power                                                                                                                                                                                                       |                 |

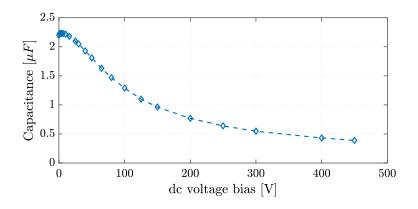

| F 4 | characteristic for TDK CGA9.                                                                                                                                                                                                                                                    | 42              |

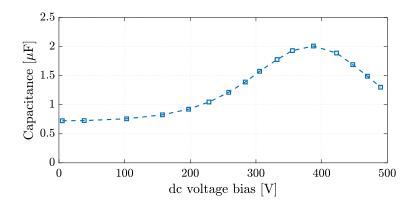

| 5.4 | Manufacturer's data for dc voltage bias v.s. Capacitance characteristic for TDK C5750                                                                                                                                                                                           | 42              |

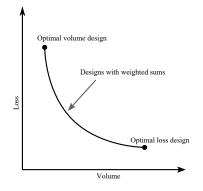

| 5.5 | Pareto front example. The curve illustrates the trade-off between the loss and                                                                                                                                                                                                  |                 |

|     | the volume within achievable design space                                                                                                                                                                                                                                       | 46              |

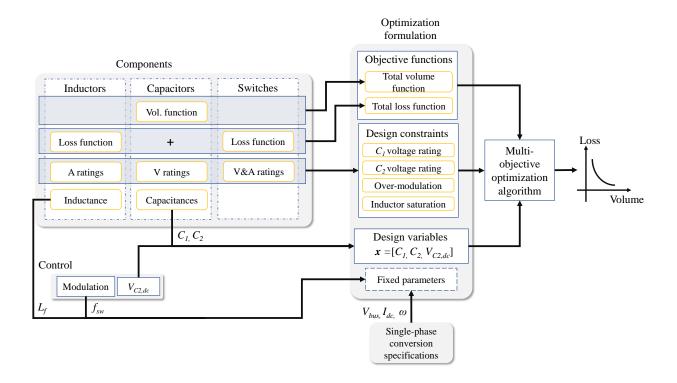

| 5.6 | Design flow chart for the proposed optimization methodology                                                                                                                                                                                                                     | 46              |

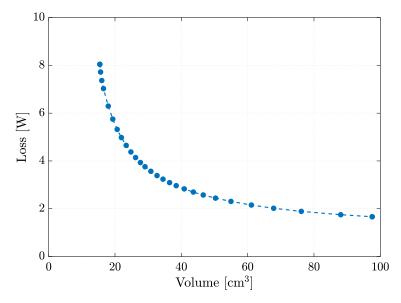

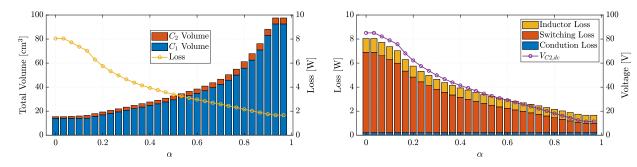

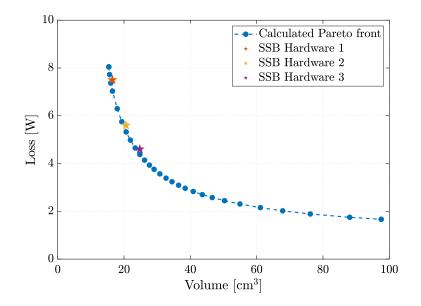

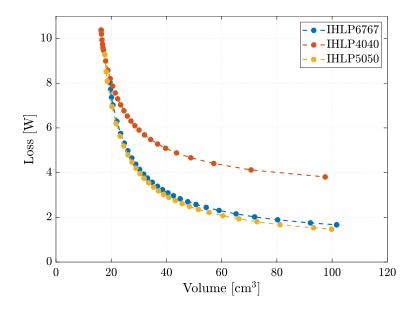

| 5.7 | Generated Loss-Volume Pareto front curve.                                                                                                                                                                                                                                       | 48              |

| 5.8 | Generated optimized volume of $C_1$ and $C_2$ for all design choices on the Pareto                                                                                                                                                                                              |                 |

|     | front, plotted with corresponding total loss for each $\alpha$ increments                                                                                                                                                                                                       | 48              |

| 5.9 | Generated loss breakdown for all design choices on the Pareto front, plotted with                                                                                                                                                                                               | 40              |

|     | corresponding $V_{C2, dc}$ for each $\alpha$ increments.                                                                                                                                                                                                                        | 48              |

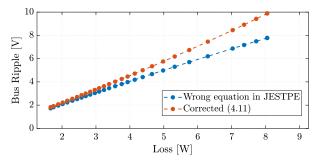

| 5.10                                      | Calculated compensation ripple $\Delta v_{\text{bus, pk-pk}}$ vs. loss in the SSB $P_{\text{loss}}$ , for all design<br>choices on the Pareto-front. Source resistance $R_s = 10 \ \Omega$ . Note that the wrong<br>result in [17] is compared with the correct equation (4.11). | 49 |

|-------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

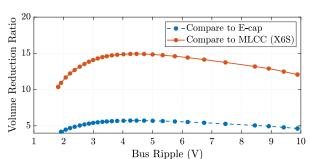

| 5.11                                      | Volume reduction ratio of the SSB compared to passive capacitor bank solutions                                                                                                                                                                                                   | 49 |

|                                           | vs. bus ripple                                                                                                                                                                                                                                                                   | 49 |

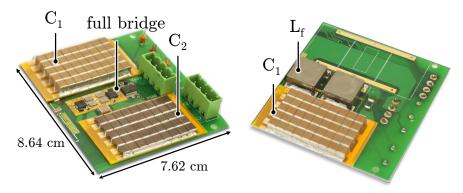

| 5.12                                      | Photos (top and bottom) of the 1.5 kW SSB hardware test bed. The capacitors are soldered on the yellow daughter boards for the ease of adjustment during testing.                                                                                                                | 50 |

| 5.13                                      | Measured loss and component volume of three hardware configurations, plotted<br>with the calculated Loss-Volume Pareto-front curve                                                                                                                                               | 51 |

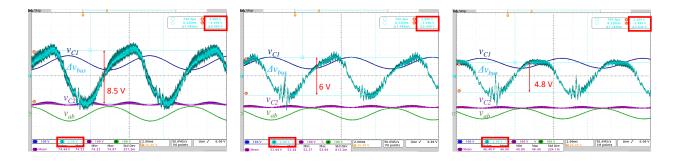

| 5.14                                      | 1.5 kW, 400 V dc-bus operation waveform of the SSB hardware prototype 1. Bus voltage is ac-coupled to show the ripple component.                                                                                                                                                 | 51 |

| 5.15                                      | 1.5 kW, 400 V dc-bus operation waveform of the SSB hardware prototype 2. Bus voltage is ac-coupled to show the ripple component.                                                                                                                                                 | 51 |

| 5.16                                      | 1.5 kW, 400 V dc-bus operation waveform of the SSB hardware prototype 3. Bus voltage is ac-coupled to show the ripple component.                                                                                                                                                 | 51 |

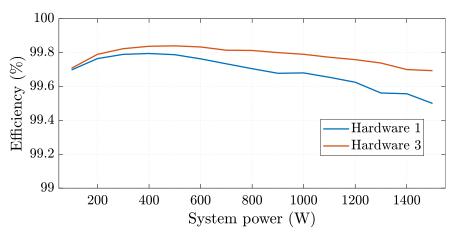

| 5.17                                      | Efficiencies of hardware 1 and 3 across the full load range.                                                                                                                                                                                                                     | 54 |

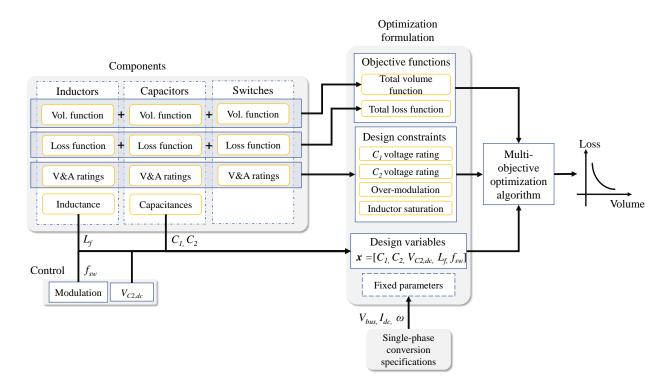

|                                           | Design flow chart with generalized optimization methodology.                                                                                                                                                                                                                     | 55 |

| 5.19                                      |                                                                                                                                                                                                                                                                                  | 55 |

| 6.1                                       | Block diagram of the PFC and SSB system.                                                                                                                                                                                                                                         | 58 |

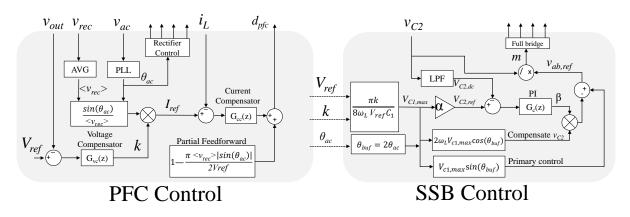

| $\begin{array}{c} 6.2 \\ 6.3 \end{array}$ | Control diagram for the PFC and SSB                                                                                                                                                                                                                                              | 58 |

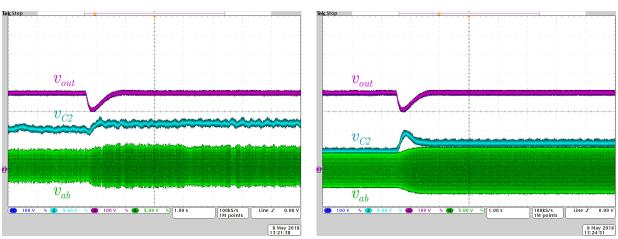

| 6.4                                       | band-pass fitler based SSB control methods                                                                                                                                                                                                                                       | 62 |

| ~ ~                                       | coupled SSB control methods.                                                                                                                                                                                                                                                     | 62 |

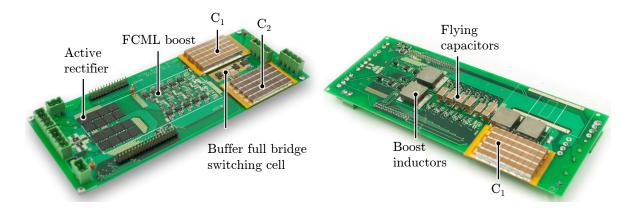

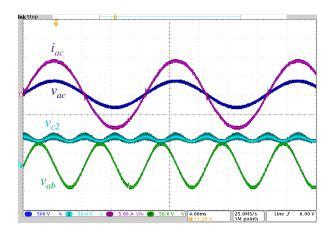

| $\begin{array}{c} 6.5 \\ 6.6 \end{array}$ | Converter photos with key components annotated. $\ldots \ldots \ldots \ldots \ldots \ldots \ldots$<br>Experimental waveforms of input voltage $v_{ac}$ , input current $i_{ac}$ , $C_2$ voltage $v_{c2}$                                                                         | 62 |

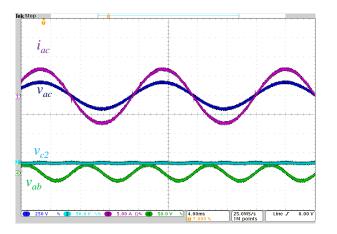

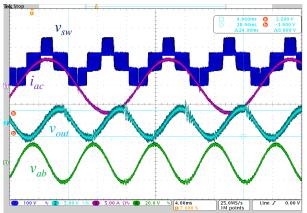

| 6.7                                       | and buffer converter output voltage $v_{ab}$ . 240 V <sub>ac</sub> to 400 V <sub>dc</sub> , 1.5 kW load<br>Experimental waveforms of output dc voltage $v_{out}$ , input current $i_{ac}$ , switching                                                                            | 63 |

| 0.1                                       | node voltage $v_{\rm sw}$ , buffer converter output voltage $v_{\rm ab}$ . The output dc bus voltage                                                                                                                                                                             |    |

|                                           | is ac-coupled to show the ripple component. 240 $\rm V_{ac}$ to 400 $\rm V_{dc},1.5\;kW$ load                                                                                                                                                                                    | 63 |

| 6.8                                       | Experimental waveforms of input voltage $v_{ac}$ , input current $i_{ac}$ , $C_2$ voltage $v_{c2}$<br>and buffer converter output voltage $v_{ab}$ . 120 V <sub>ac</sub> to 400 V <sub>dc</sub> , 600 W load                                                                     | 64 |

| 6.9                                       | Experimental waveforms of output dc voltage $v_{out}$ , input current $i_{ac}$ , switching node voltage $v_{sw}$ , buffer converter output voltage $v_{ab}$ . The output dc bus voltage                                                                                          |    |

| 6 10                                      | is ac-coupled to show the ripple component. 120 $V_{\rm ac}$ to 400 $V_{\rm dc},600$ W load. $~$ .                                                                                                                                                                               | 64 |

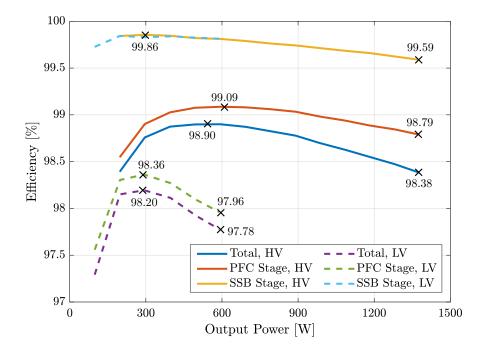

| 0.10                                      | Efficiency measurement with 240 $V_{ac}$ (HV) and 120 $V_{ac}$ (LV) inputs. Total system efficiency, PFC efficiency and SSB efficiency are plotted.                                                                                                                              | 64 |

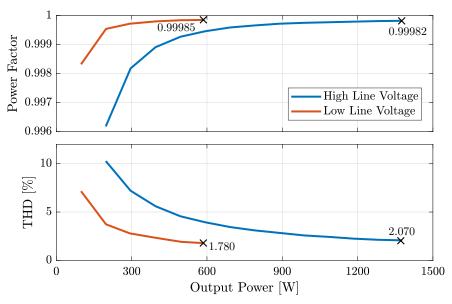

| 6.11                                      | Power factor and THD measurement for 240 Vac and 120 Vac input.                                                                                                                                                                                                                  | 65 |

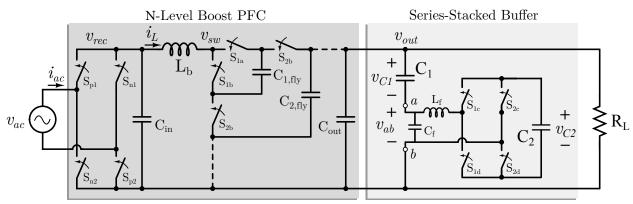

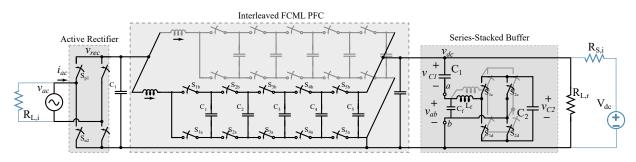

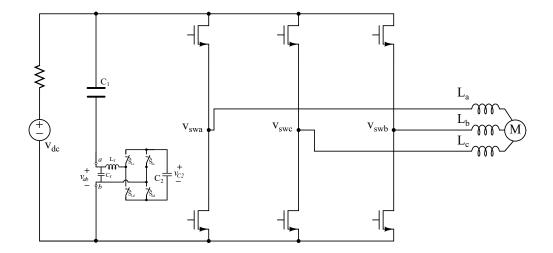

| 6.12 | Schematic of the overall system with active rectifier (unfolder), interleaved FCML, and series-stacked buffer. The dc source and load are shown in blue                                                 | 67 |

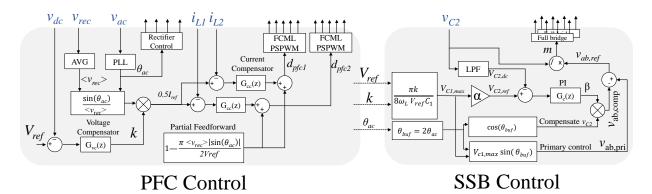

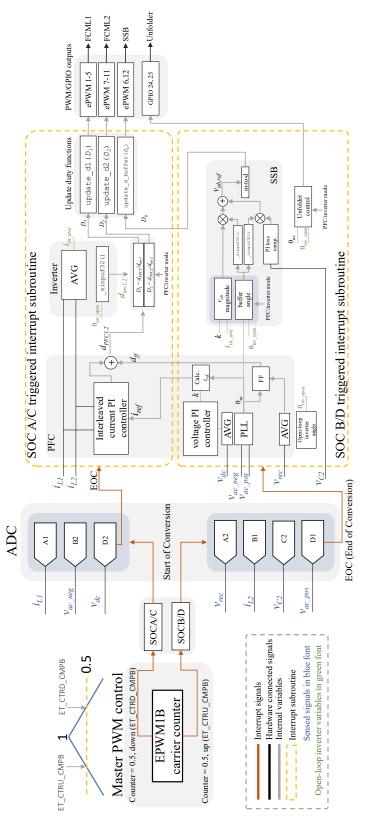

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 6.13 | Overall control system of the interleaved PFC and SSB in rectifier mode. The sensed parameters are in blue font.                                                                                        | 67 |

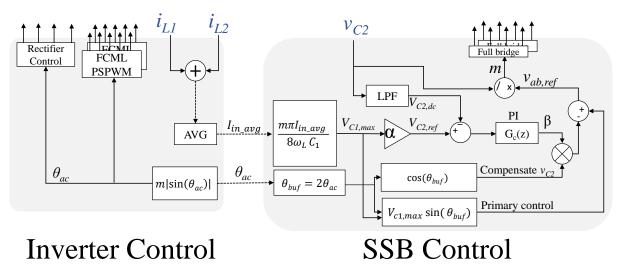

| 6.14 | Overall control system in open-loop inverter mode.                                                                                                                                                      | 68 |

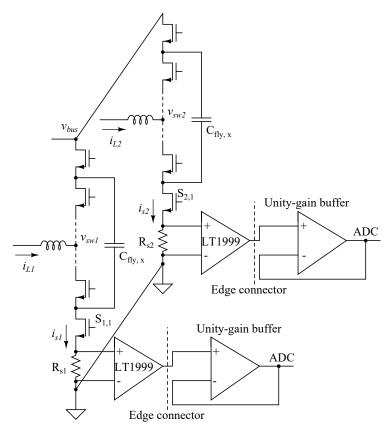

|      | Current sensing circuitry for two interleaved FCML phases                                                                                                                                               | 69 |

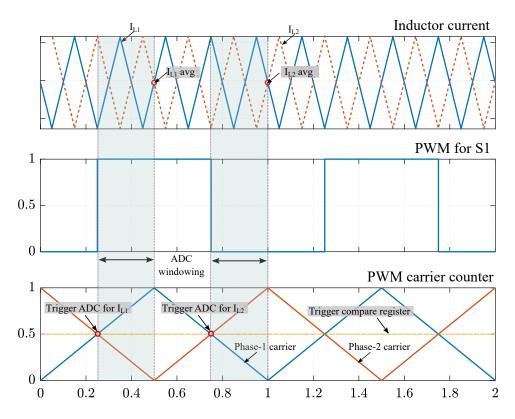

|      | Generalized key waveforms demonstrating the timing of ADC triggering to sample<br>the average inductor current of the two phases. Duty ratio is 0.5 for PSPWM.                                          |    |

|      | Peak value of the carrier counter and the switching period are normalized                                                                                                                               | 70 |

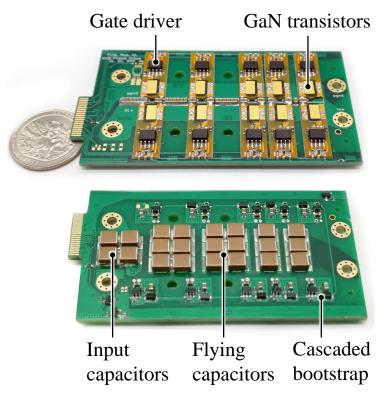

| 6.17 | First version of the 6-level FCML module with switching cell daughter boards, with a US quarter for size reference.                                                                                     | 71 |

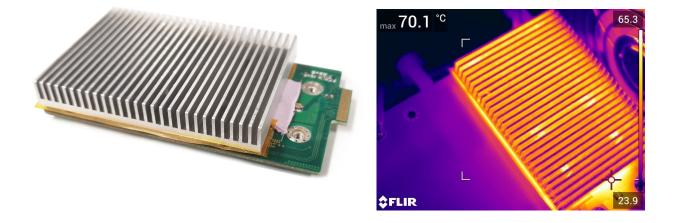

| 6 18 | FCML module with custom designed low-profile heatsink.                                                                                                                                                  | 72 |

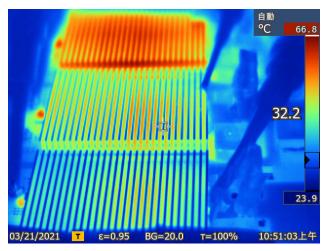

|      | Thermal image of the FCML module testing at 4.3 kW, 400 V to 250 V dc-dc.                                                                                                                               | 72 |

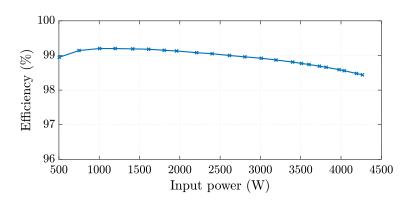

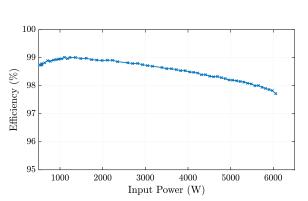

|      | Efficiency of the FCML module high power dc-dc thermal testing up to 4.3 kW, 400 Vdc to 250 Vdc with air-cooled heatsink solution.                                                                      | 72 |

| 6 91 |                                                                                                                                                                                                         | 12 |

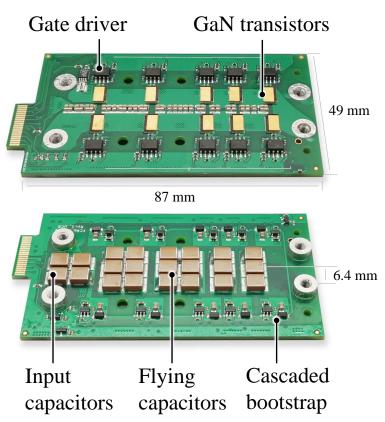

| 0.21 | 6-level FCML module without switching cell PCBs with dimensions. This module                                                                                                                            | 70 |

| c    | was contract-manufactured.                                                                                                                                                                              | 73 |

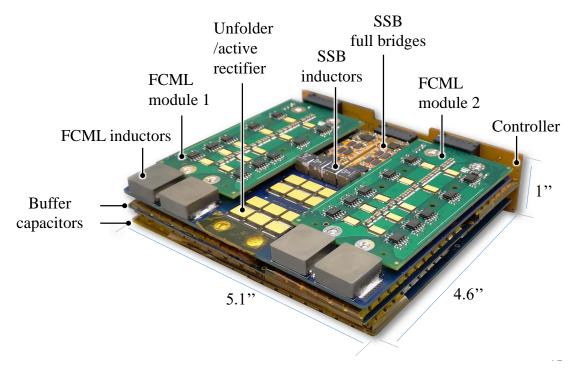

|      | The hardware assembly of the EV charger                                                                                                                                                                 | 74 |

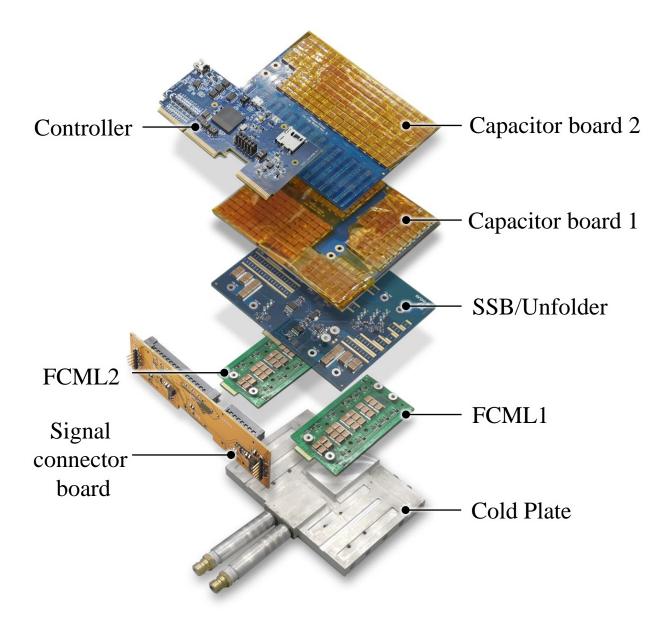

|      | Exploded view render of the hardware assembly                                                                                                                                                           | 75 |

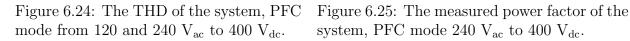

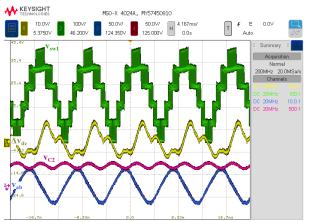

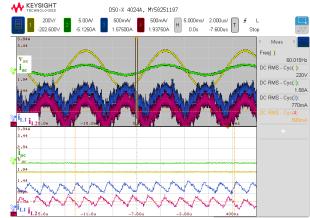

|      | The THD of the system, PFC mode from 120 and 240 $V_{ac}$ to 400 $V_{dc}$                                                                                                                               | 76 |

|      | The measured power factor of the system, PFC mode 240 $V_{ac}$ to 400 $V_{dc}$                                                                                                                          | 76 |

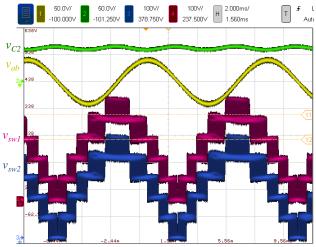

| 6.26 | Typical SSB voltage waveforms for $v_{C2}$ and $v_{ab}$ , dc bus voltage ripple (ac coupled),<br>and FCML switch-node of the system, PFC mode from 240 V <sub>ac</sub> to 400 V <sub>dc</sub> , 1.5 kW. | 77 |

| 6.27 | Typical current waveforms of the interleaved FCML, PFC mode from 240 $\rm V_{ac}$ to                                                                                                                    |    |

|      | 400 $V_{dc}$ , 375 W                                                                                                                                                                                    | 77 |

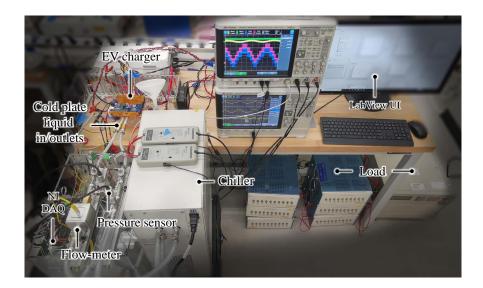

| 6.28 | Full experimental setup with the liquid cooling loop and temperature data acqui-<br>sition.                                                                                                             | 77 |

| 6.29 | The efficiency of the 6.1 kW inverter test, 400 $V_{dc}$ to 240 $V_{ac}$ .                                                                                                                              | 78 |

| 6.30 | Typical SSB voltage waveforms for $v_{c2}$ and $v_{ab}$ , and FCML switching node voltages from 400 V <sub>dc</sub> to 240 V <sub>ac</sub> , 6.1 kW.                                                    | 78 |

|      |                                                                                                                                                                                                         |    |

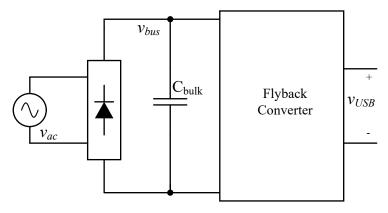

| 7.1  | Conventional charger solution with diode bridge, input bulk capacitor, and a flyback converter.                                                                                                         | 80 |

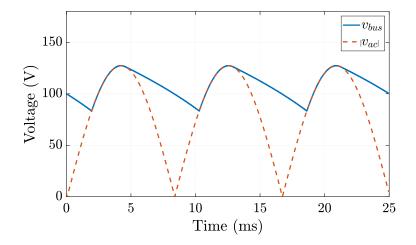

| 7.2  | Input voltage waveforms with a 80 $\mu$ F input bulk capacitor, at 90 V <sub>ac</sub> , 60 Hz,                                                                                                          |    |

| •    | and $65 \text{ W}$ .                                                                                                                                                                                    | 80 |

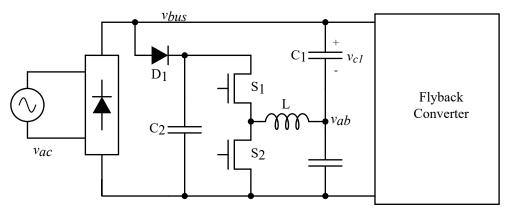

| 7.3  | Proposed buffer solution and flyback.                                                                                                                                                                   | 81 |

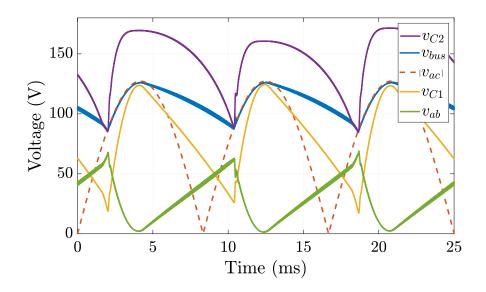

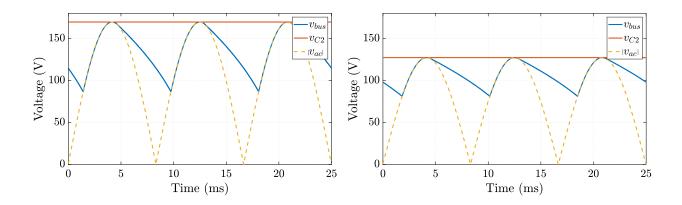

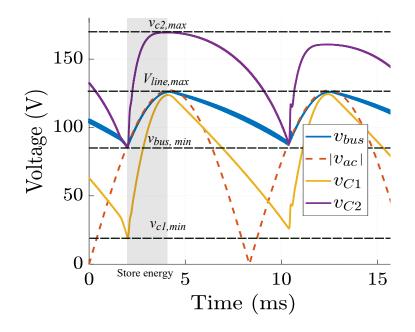

| 7.4  | Simulated waveforms of the proposed active buffer in PLECS for 90 Vac, 65 W.                                                                                                                            | 82 |

| 7.5  | Simulated waveforms of the proposed active buffer in PLECS for 120 Vac, 65 W,                                                                                                                           |    |

| 7.6  | with $S_2$ shorted to ground                                                                                                                                                                            | 82 |

|      | with $S_2$ shorted to ground                                                                                                                                                                            | 82 |

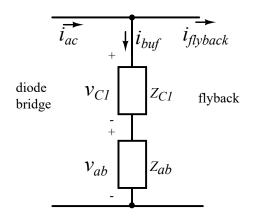

| 7.7  | Equivalent impedance of the proposed buffer structure                                                                                                                                                   | 83 |

|      |                                                                                                                                                                                                         |    |

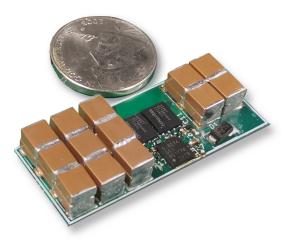

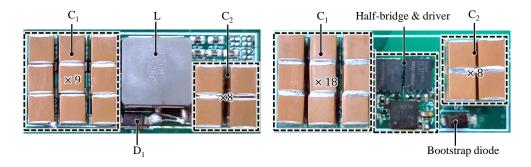

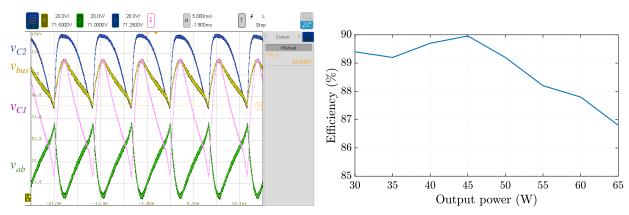

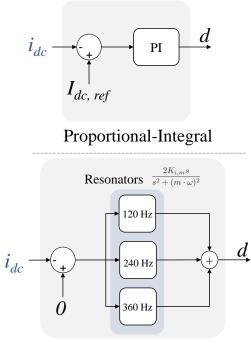

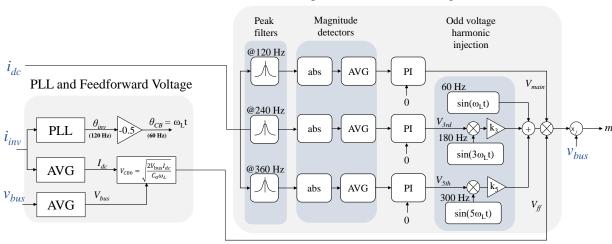

| $7.8 \\ 7.9 \\ 7.10 \\ 7.11 \\ 7.12 \\ 7.13$ | Overall control diagram                                                                                             | 84<br>84<br>85<br>85<br>87<br>87 |

|----------------------------------------------|---------------------------------------------------------------------------------------------------------------------|----------------------------------|

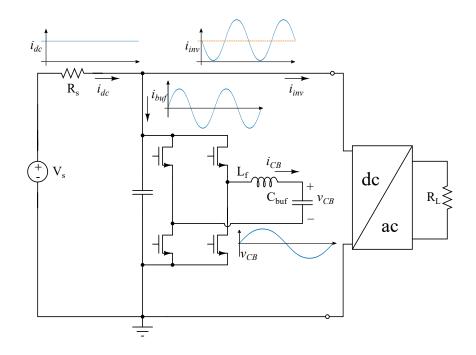

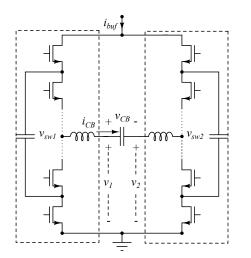

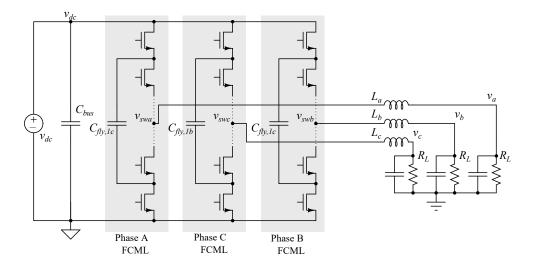

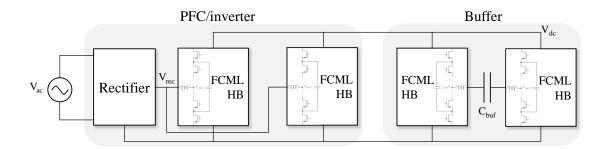

| 8.1                                          | Schematic drawing and key waveforms of the bipolar ripple-port active buffer in single-phase inverter applications. | 90                               |

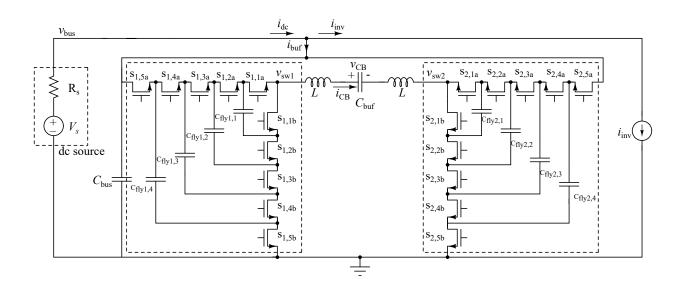

| 8.2                                          | Schematic drawing of the bipolar active buffer implemented with two 6-level                                         |                                  |

| 8.3                                          | FCML converters                                                                                                     | 91                               |

| 8.4                                          | $C_{\text{buf}} = 80 \ \mu F.$                                                                                      | 93                               |

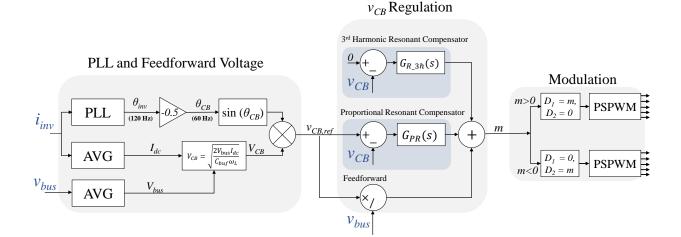

|                                              | sensed parameters are in blue font.                                                                                 | 95                               |

| 8.5                                          | Capacitance v.s. voltage bias curve of TDK C5750X6S                                                                 | 97                               |

| 8.6                                          | Capacitance v.s. voltage bias curve of Ceralink capacitor.                                                          | 97                               |

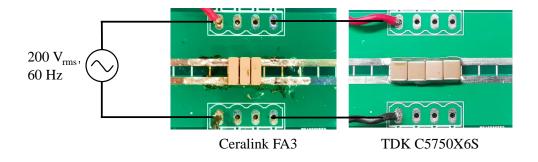

| 8.7                                          | Applying ac voltage to test nonlinear behavior of both Ceralink and X6S capacitors.                                 | 97                               |

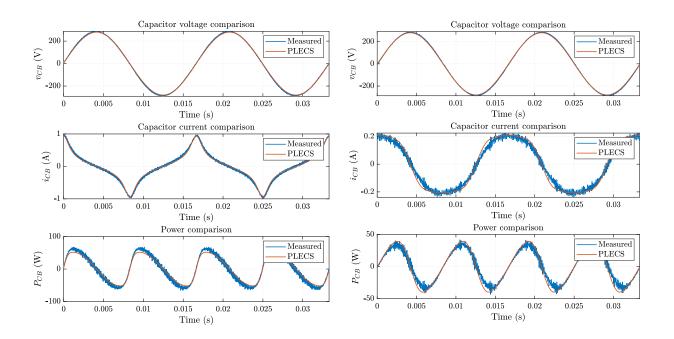

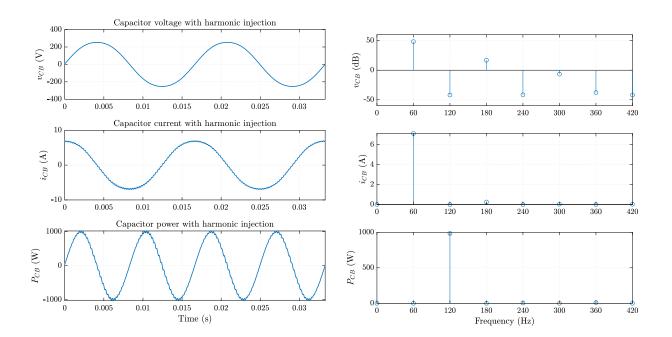

| 8.8                                          | Experimental and simulated wavef orms of four TDK C5750X6S under $v_{\rm CB} =$                                     |                                  |

|                                              | $280\sin(\omega_L t) \mathrm{V} .............$                                                                      | 98                               |

| 8.9                                          | Experimental and simulated waveforms of three <b>Ceralink</b> capacitors (FA3) under                                |                                  |

|                                              | $v_{\rm CB} = 280\sin(\omega_L t)  \mathrm{V}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $     | 98                               |

|                                              | 1                                                                                                                   | 99                               |

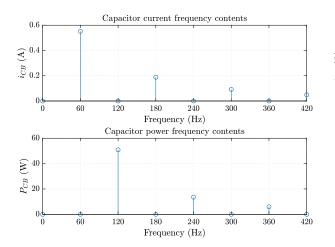

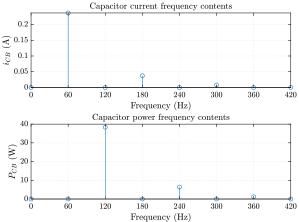

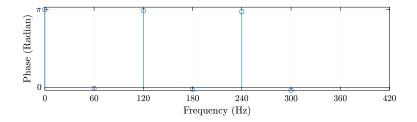

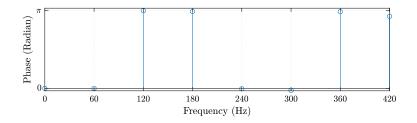

|                                              | Harmonic contents of the <b>Ceralink</b> capacitor current and power                                                | 99                               |

|                                              | 1 1                                                                                                                 | 100                              |

|                                              | 1                                                                                                                   | 100                              |

|                                              |                                                                                                                     | 101                              |

|                                              |                                                                                                                     | 102                              |

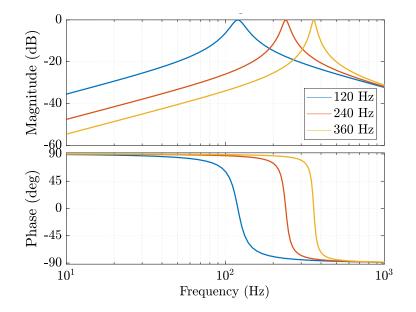

| 8.16                                         | Bode plots of three peak filters with center frequencies at 120 Hz, 240 Hz and                                      |                                  |

|                                              |                                                                                                                     | 104                              |

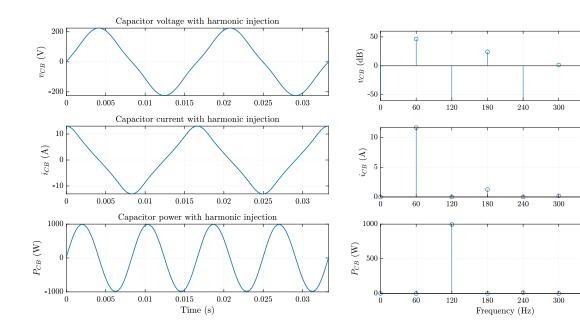

| 8.17                                         | Simulated waveform for single-phase buffering scenario with 1 kW system power                                       |                                  |

|                                              | and 400 V dc-bus using TDK C5750 X6S capacitors as the buffer capacitor. $\ .$ .                                    | 105                              |

| 8.18                                         | Harmonic contents of the capacitor voltage, current and power with the proposed                                     |                                  |

|                                              | control using TDK C5750 X6S capacitors.                                                                             | 105                              |

| 8.19                                         | Simulated waveform for single-phase buffering scenario with 1 kW system power                                       |                                  |

|                                              | and 400 V dc-bus using Ceralink capacitors as the buffer capacitor.                                                 | 106                              |

| 8.20                                         | Harmonic contents of the capacitor voltage, current and power with the proposed                                     |                                  |

|                                              | control using Ceralink capacitors.                                                                                  | 106                              |

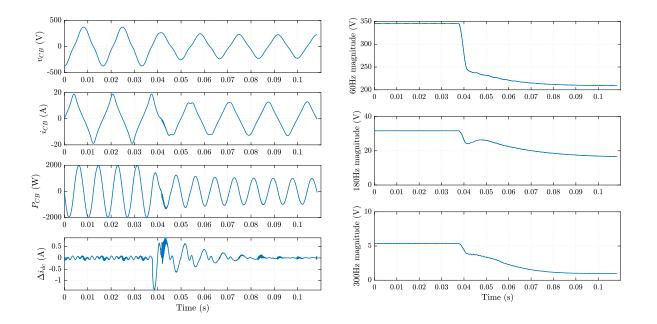

| 8.21                                         | MLCC buffer capacitor voltage, current, power and corresponding dc-side current                                     |                                  |

|                                              |                                                                                                                     | 107                              |

| 8.22                                         | Capacitor voltage magnitudes of each frequency contents during a load step from                                     |                                  |

|                                              |                                                                                                                     | 107                              |

|                                              | -                                                                                                                   |                                  |

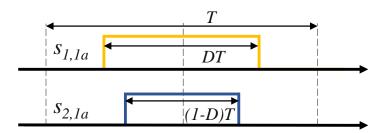

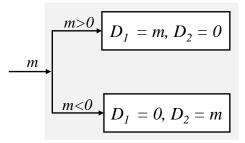

| 8.23         | Exemplar unipolar PWM signals for $s_{1,1a}$ and $s_{2,a}$ , with switching period T. $s_{1,1a}$ |       |

|--------------|--------------------------------------------------------------------------------------------------|-------|

|              | operates with duty ratio $D$ , and $s_{2,1a}$ operates with complimentary duty $1 - D$ .         | 100   |

|              | The center of the two signals are aligned                                                        | 108   |

|              | Leg-alternating modulation scheme                                                                | 108   |

| 8.25         | Terminal voltage $v_1$ and $v_2$ are defined to calculate the power processed by each            |       |

|              | FCML leg.                                                                                        | 110   |

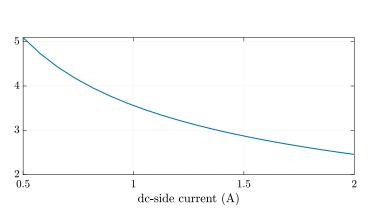

| 8.26         | Calculated ratio of $\frac{P_{\text{FCML, uni}}}{P_{\text{FCML, la}}}$ vs. dc-side current.      | 110   |

| 8.27         | Calculated inductor current ripple and flying capacitor voltage ripple in two line               |       |

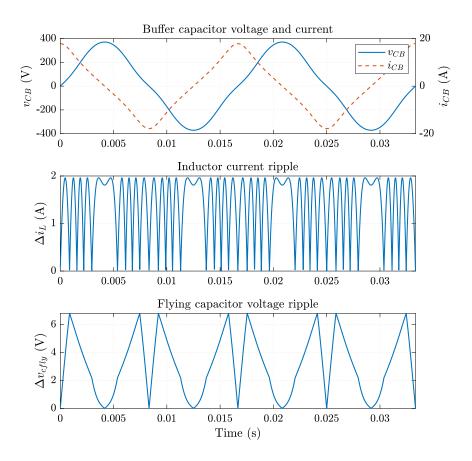

|              | cycles with MLCC buffer capacitor for 2 kW, 400 V dc-bus.                                        | 111   |

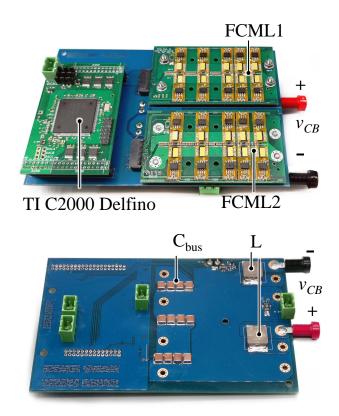

| 8.28         | Tested buffer hardware. The dc-ac converter is implemented with a full-bridge                    |       |

|              | converter with two FCML legs.                                                                    | 112   |

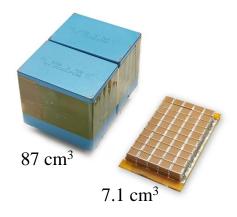

| 8.29         | Buffer capacitor size comparison between the tested film capacitors (TDK B32776G                 |       |

| 0.20         | and MLCCs (TDK C5750X6S)                                                                         | 113   |

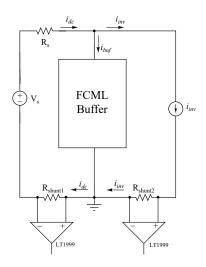

| 8.30         | Current sensing circuitry with two shunt resistors and current amplifiers                        | 113   |

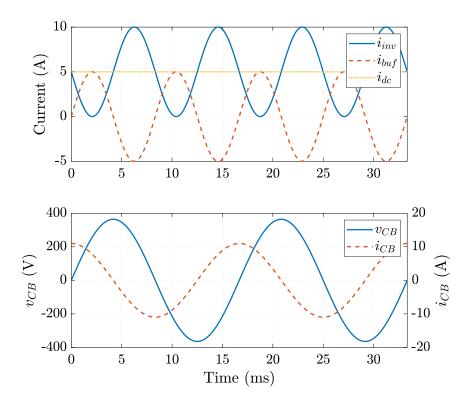

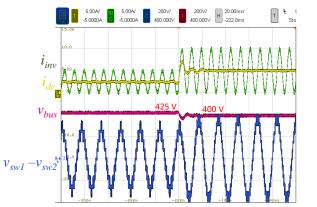

|              | Experimental waveforms of the proposed buffer with <b>film capacitors</b> controlled             | 110   |

| 0.01         | with only feedforward and PR compensator. The dc source current $i_{dc}$ is ac-                  |       |

|              | coupled to showcase the ripple component. Without 3rd harmonic compensation,                     |       |

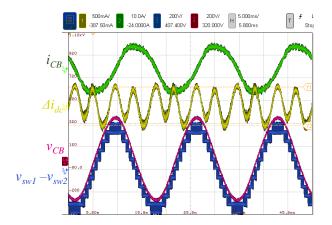

|              | the dc current ripple is 850 mA. Test condition: 400 V dc bus, 2 kW dc power.                    | 114   |

| 8 32         | Experimental waveforms of the proposed buffer with <b>film capacitors</b> controlled             | 114   |

| 0.02         | with additional 3rd harmonic compensation, along with feedforward and PR com-                    |       |

|              | pensator. The dc source current $i_{dc}$ is ac-coupled to showcase the ripple compo-             |       |

|              | nent. As shown, the dc-side current has much lower ripple component of only                      |       |

|              |                                                                                                  |       |

|              | 200 mA with 3rd harmonic compensation. Test condition: 400 V dc bus, 2 kW                        | 11/   |

| 0 99         | dc power.                                                                                        | 114   |

| 8.33         | Experimental waveforms of the proposed buffer during load step up. The dc side                   | 115   |

| 0.04         | current steps from 2.5 A to 5 A                                                                  | 115   |

| 8.34         | Experimental waveforms of the proposed buffer during load step down. The dc                      |       |

| 0.0 <b>r</b> | side current steps from 5 A to 2.5 A.                                                            | 115   |

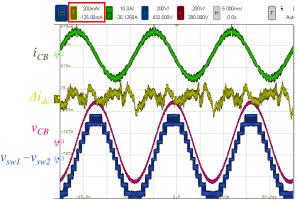

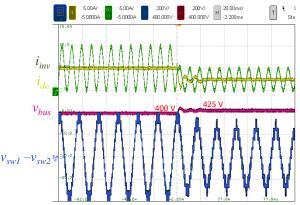

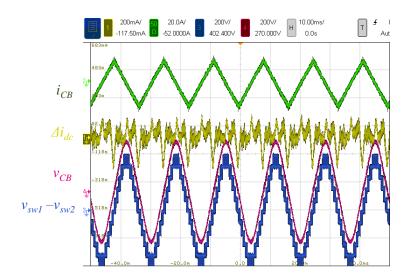

| 8.35         | Experimental waveforms of the buffer with MLCCs controlled with the proposed                     |       |

|              | power harmonic elimination scheme. The dc source current $i_{dc}$ is ac-coupled to               |       |

|              | showcase the ripple component. As shown, the dc-side current has low ripple                      |       |

|              | component of only 300 mA, resulting from the low-harmonic buffer power. Test                     |       |

|              | condition: 400 V dc bus, 2 kW dc power                                                           | 116   |

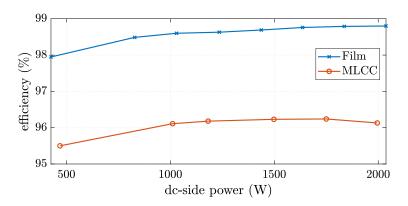

| 8.36         | Measured buffer efficiencies of using both film capacitor and MLCC as buffer                     |       |

|              | capacitors                                                                                       | 116   |

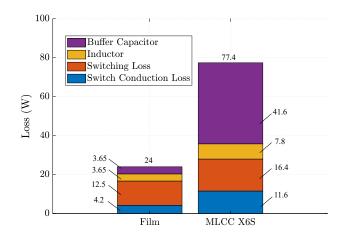

| 8.37         | Estimated loss composition of the buffer converters with film capacitor and MLCC                 | 2.117 |

| 8.38         | Calculated total loss of the buffer converter with simulated voltage and current                 |       |

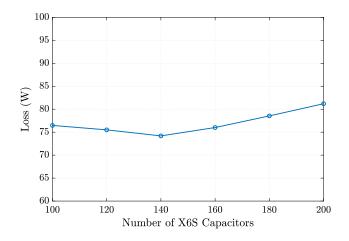

|              | waveforms for each number of X6S capacitors.                                                     | 119   |

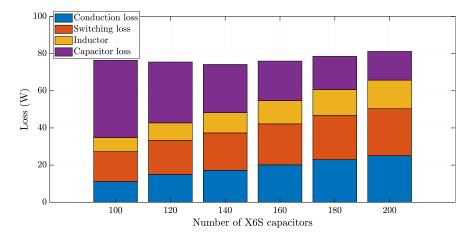

| 8.39         | Loss breakdown of the buffer converter with simulated voltage and current wave-                  |       |

|              | forms for each number of X6S capacitors                                                          | 119   |

| <b>a</b> .:  |                                                                                                  | 105   |

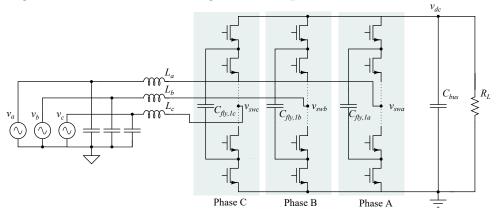

| 9.1          | Schematic drawing of a three-phase N-level FCML inverter                                         | 122   |

| 9.2  | Schematic drawing of a three-phase N-level FCML PFC.                                                        | 122 |

|------|-------------------------------------------------------------------------------------------------------------|-----|

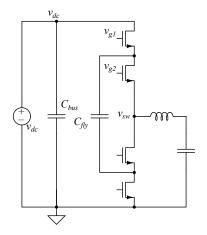

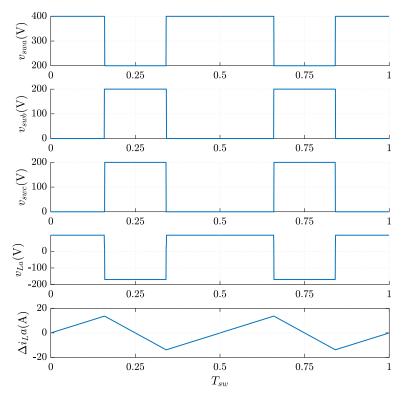

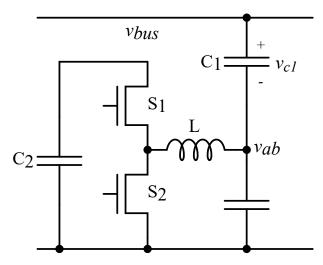

| 9.3  | Schematic drawing of a single three-level FCML converter.                                                   | 123 |

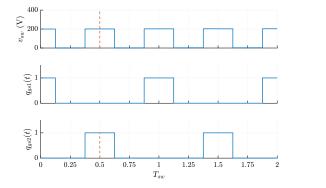

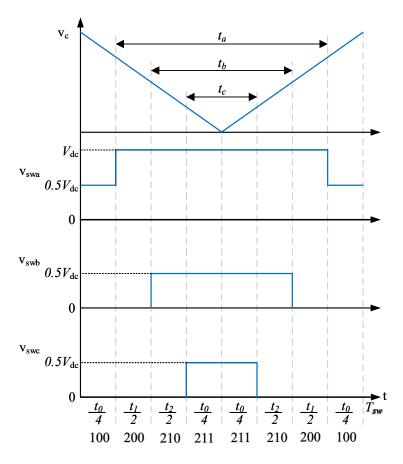

| 9.4  | Three-level FCML switching waveforms with 0.25 duty ratio. Top: $v_{sw}$ , middle                           |     |

|      | and bottom: two PSPWM signals. The center of the switching node voltage is                                  |     |

|      | aligned with the PSPWM.                                                                                     | 124 |

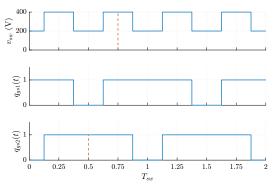

| 9.5  | Three-level FCML switching waveforms with 0.75 duty ratio. The center of the                                |     |

|      | switching node voltage is not aligned with the high level of PSPWM. Instead, the                            |     |

|      |                                                                                                             | 124 |

| 9.6  | Ideal waveforms of the three-phase three-level FCML with PSPWM without any                                  |     |

|      |                                                                                                             | 125 |

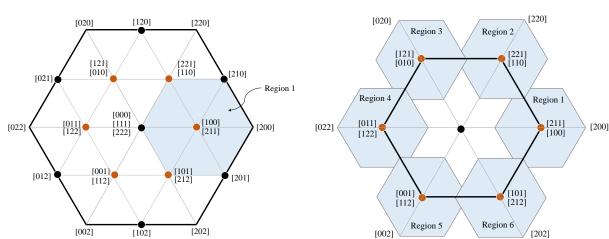

| 9.7  | The vector distribution of three level SVPWM. The shaded small hexagonal area                               |     |

|      | is the re-centered region that is equivalent to two-level SVPWM                                             | 126 |

| 9.8  | All re-centered small hexagonal regions that are equivalent to two-level SVPWMs.                            | 126 |

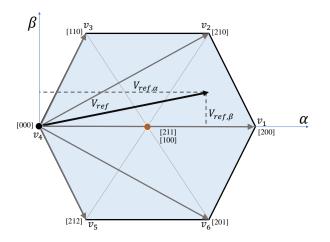

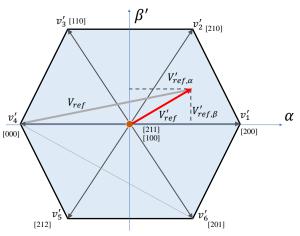

| 9.9  | Region one of three-level SVPWM with a reference vector.                                                    | 127 |

| 9.10 | Region one of three level SVPWM with the modified reference vector re-centered                              |     |

|      | at [211] ([110])                                                                                            | 127 |

| 9.11 | The timing diagram of switching node voltages of three-level SVPWM in region                                |     |

|      | one. The vector sequence in a half cycle is $[100] - [200] - [210] - [211]$ .                               | 128 |

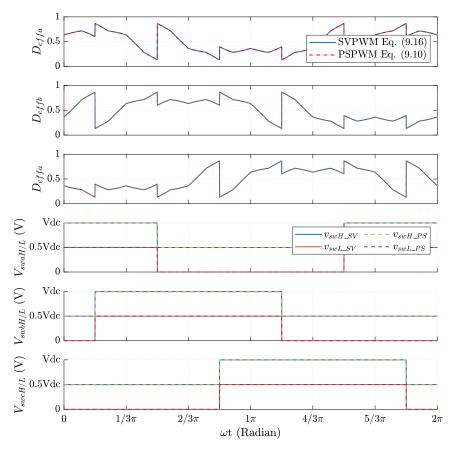

| 9.12 | The effective duty ratio and the modulating voltage level of PSPWM with ZSI                                 |     |

|      | and SVPWM when $v_{\rm an}$ , $v_{\rm bn}$ and $v_{\rm cn}$ are 120 $v_{\rm rms}$ and $V_{\rm dc}$ is 400 V | 129 |

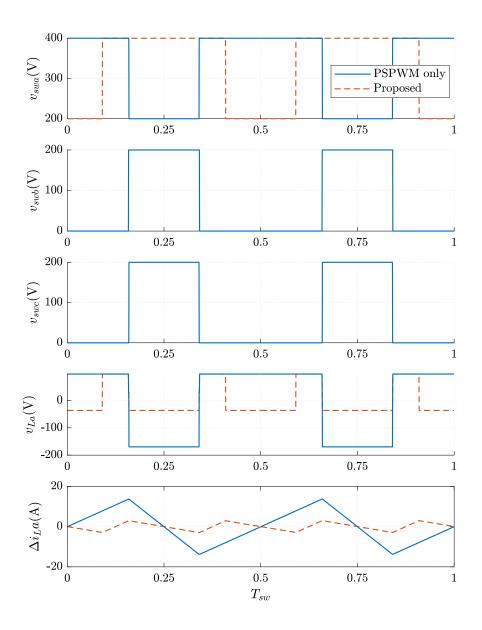

| 9.13 | Ideal waveforms of the three-phase three-level FCML with PSPWM only and                                     |     |

|      | with proposed modulation with ZSI. $D_a = 0.82$ , $D_b = 0.18$ , $D_c = 0.18$ . As can                      |     |

|      | be seen, the proposed control aligns the center of $v_{swa}$ with the other two phases,                     |     |

|      | resulting in reduced voltage and current ripple on the inductor. With ZSI, the                              |     |

|      | effective frequency on the inductor is $2(N-1)f_{sw}$                                                       | 130 |

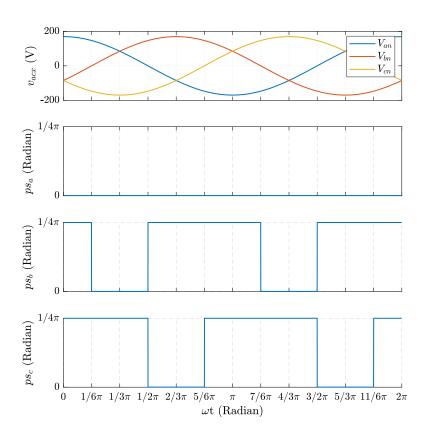

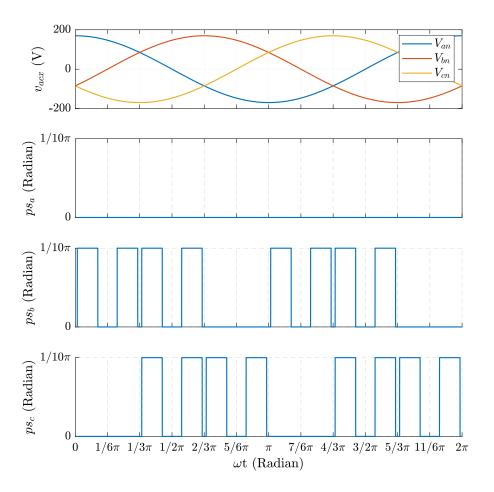

| 9.14 | The phase shift commands of each phase leg in a three-level FCML inverter with                              |     |

|      | the proposed control in a full line cycle where $V_{acx}$ is 120 $V_{rms}$ , $V_{dc}$ is 400 $V_{dc}$ .     | 131 |

| 9.15 | Flow chart of the derivation process of the duties and phases for modulation each                           |     |

|      | FCML legs.                                                                                                  | 132 |

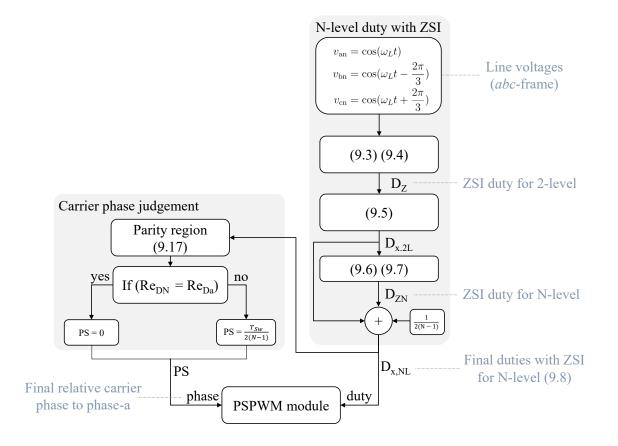

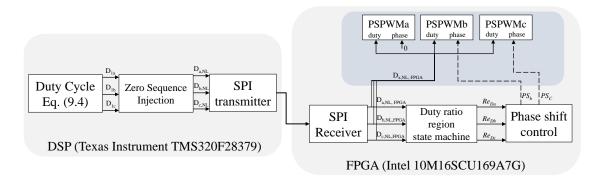

| 9.16 | Digital implementation of the proposed control for six-level three-phase FCML                               |     |

|      | inverters                                                                                                   | 132 |

| 9.17 | The phase shift commands of each phase leg in a six-level FCML inverter with                                |     |

|      | the proposed control in a full line cycle where $V_{acx}$ is 120 $V_{rms}$ , $V_{dc}$ is 400 $V_{dc}$ .     | 133 |

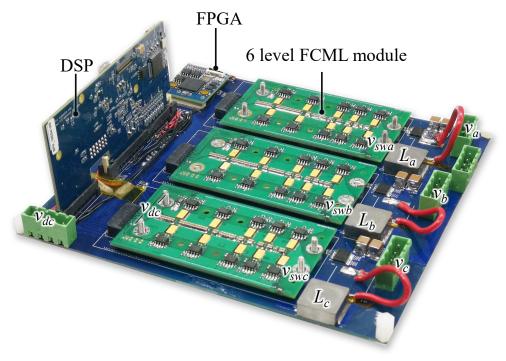

| 9.18 | The experimental hardware prototype of six-level three-phase FCML inverter.                                 |     |

|      | The three six-level FCML modules are mounted onto the main control board                                    |     |

|      | with DSP and FPGA.                                                                                          | 134 |

| 9.19 | Experimental waveforms of the three-phase six-level FCML inverter with PSPWM                                |     |

|      | and ZSI, without any phase shift control. $V_{\rm dc} = 400$ V, $V_{\rm ac} = 120$ V <sub>rms</sub> , 360 W |     |

|      | system power                                                                                                | 136 |

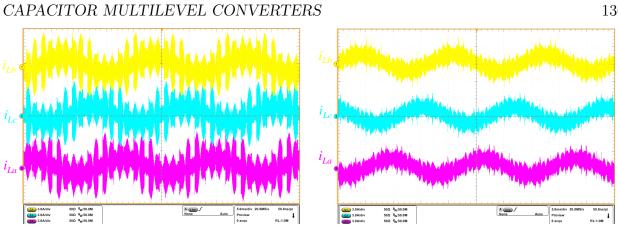

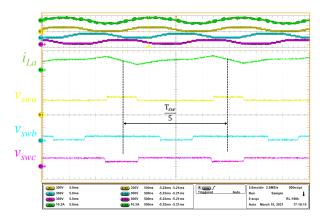

| proposed modulation. The inductor current ripple with the proposed control strategy is smaller than PSPWM with ZSI without any phase shift control in   |                                                                                      |

|---------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|

| •                                                                                                                                                       | 136                                                                                  |

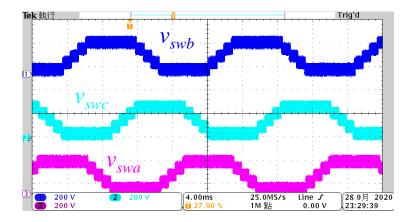

| The switching node voltages of the three phases at 400 $V_{dc}$ , 360 W, inverter mode, demonstrating good flying capacitor voltage balancing.          | 136                                                                                  |

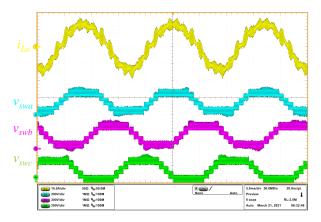

| Three-phase FCML PFC inductor current and switching node voltages with PSPWM only, with no carrier phase shift control. Test condition: $208 V_{ac,LL}$ |                                                                                      |

| to 400 $V_{dc}$ , 3 kW                                                                                                                                  | 137                                                                                  |

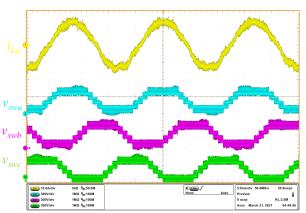

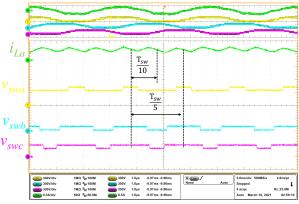

| I 0 0                                                                                                                                                   |                                                                                      |

|                                                                                                                                                         | 137                                                                                  |

|                                                                                                                                                         |                                                                                      |

| using PSPWM only without carrier phase shift control. As can been seen, the                                                                             |                                                                                      |

|                                                                                                                                                         | 138                                                                                  |

|                                                                                                                                                         |                                                                                      |

|                                                                                                                                                         |                                                                                      |

|                                                                                                                                                         |                                                                                      |

|                                                                                                                                                         | 138                                                                                  |

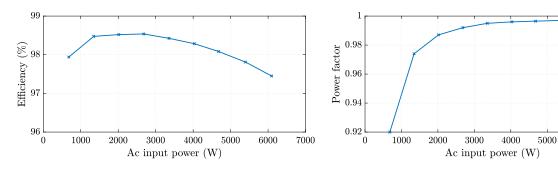

| · · · · · ·                                                                                                                                             | 138                                                                                  |

| *                                                                                                                                                       | 138                                                                                  |

|                                                                                                                                                         |                                                                                      |

| bottom to the top.                                                                                                                                      | 139                                                                                  |

| Potential charge injection solution to control $v_{C2}$                                                                                                 | 143                                                                                  |

| <u> </u>                                                                                                                                                | 144                                                                                  |

|                                                                                                                                                         | 145                                                                                  |

|                                                                                                                                                         | 145                                                                                  |

|                                                                                                                                                         | 146                                                                                  |

|                                                                                                                                                         | 147                                                                                  |

| Block diagram of the firmware setup and major computational tasks for of charger controller implemented in TI C2000 Delfino DSP.                        | 157                                                                                  |

|                                                                                                                                                         | strategy is smaller than PSPWM with ZSI without any phase shift control in Fig. 9.17 |

# List of Tables

| 5.1 | Ceramic Capacitors for implementing $C_1$ and $C_2$                             | 43  |

|-----|---------------------------------------------------------------------------------|-----|

| 5.2 | Constants in the optimization                                                   | 43  |

| 5.3 | Specifications of the inductor used in the design                               | 43  |

| 5.4 | Upper limits of design vectors in the optimization                              | 44  |

| 5.5 | Design parameters for three tested hardwares in this work                       | 52  |

| 5.6 | Calculated and measured ripple comparison                                       | 52  |

| 5.7 | Design parameters of previous hardware demonstration                            | 52  |

| 5.8 | Inductors for comparison                                                        | 54  |

| 6.1 | Component Listing of the Hardware Prototype                                     | 63  |

| 6.2 | Component listing                                                               | 76  |

| 6.3 | Key performance specifications for the 6.1 kW inverter test                     | 78  |

| 7.1 | Key component list.                                                             | 84  |

| 8.1 | Parameters of tested capacitors                                                 | 98  |

| 8.2 | Key component list of the buffer converter                                      | 114 |

| 8.3 | Volumes of passive components                                                   | 115 |

| 8.4 | Comparison to other active buffers                                              | 117 |

| 8.5 | Buffer control parameters for different numbers of X6S                          | 118 |

| 9.1 | High and Low Voltage Level of Switching Node in Each Phase at Different Regions |     |

|     | of Three-Level SVPWM                                                            | 127 |

| 9.2 | Key performance metrics.                                                        | 139 |

## Acknowledgments

This dissertation not only concludes my six-year graduate school journey, but also marks the tenth year since I came to the United States for studying. Ten years ago, I only knew that it would be cool to work on electric vehicle related fields in the future. Never could I have imagined that I would have the opportunities to work alongside and learn from some of the best minds in the field of power electronics and EVs, and work on projects that have truly pushed the boundary of existing technologies in fundamental ways.

I would like to direct my first thank you to my advisor Professor Robert Pilawa-Podgurski. Robert is a visionary researcher, a resourceful and supporting mentor, and a caring friend. I am extremely grateful to Robert for always inspiring me to solve challenging and meaningful problems, providing me the freedom and support to explore, and encouraging and comforting me after many failures in the lab. Moreover, his enthusiasm, humor and care always give me a sense of belonging to a large family in the research group, filling the everyday life of graduate school with laughter and joy. I would also like to thank my committee members, Professor Seth Sanders, Professor Duncan Callaway and Professor Minjie Chen for valuable suggestions throughout the course of this work.

Thank you to all the members of the big "Pilawa Group" family, past and present: Yutian Lei, Shibin Qin, Christopher Barth, Enver Candan, Andrew Stillwell, Ben Macy, Joseph Liu, Pourya Assem, Derek Heeger, Zichao Ye, Derek Chou, Thomas Foulkes, Tomas Modeer, Yizhe Zhang, Nathan Pallo, Nathan Brooks, Pei Han Ng, Samantha Coday, Maggie Blackwell, Rose Abramson, Kelly Fernandez, Joseph Schaadt, Mads Graungaard Taul, Logan Horowitz, Yicheng Zhu, Rahul Iyer, Yong-Long Syu, Ting Ge, Nathan Ellis, Raya Mahony, and many more. This is such an amazing group of people that I've learned from you as much as all the fun we've had together. A special thank you to Yutian, my first research mentor, the officiant of my wedding and my future colleague. Without the patient and substantial guidance from Yutian in the beginning of my graduate school, I could never have won a Best Paper award on my first paper. He showed me what it takes to become a world-class scientific researcher. Thank you to Shibin, for his ground-breaking prior work on the Series-Stacked Buffer and FCML PFC. I am glad that many of the future-work research items in his thesis got checked off in this work. I would like to thank Zichao, my academic brother, for sharing all the ups and downs in research and in life with me. His world-dominating research in the field of Hybrid Dc-Dc has always pushed me to excel in my own research. I would like to thank the EV-charger team, Derek, Kelly and Raya. Without the strong team efforts, we could not have built the most power-densed single-phase EV charger. Especially, it has been a privilage to work with Derek, whose strong hardware development and mechanical design skills are the very reasons that we were able to manage a very mechanically complicated yet compact design. I want to thank Nathan Brooks, for always being the friend that I can have open-minded conversations with. Without Nathan, some of the ideas on the Series-Stacked Buffer and PFC would not be as polished and rigorous. Thanks to system design expert Danny Lohan for developing a complicated multi-objective optimization script for the Series-Stacked Buffer after just a brief discussion with me. Thanks to Joseph Schaadt, for allowing me into the clean room one last time before I graduate, and inviting me to your home for a lovely thanksgiving dinner. I want to thank Yong-Long (Max), for providing the strong expertise in embedded system, which is crucial for the three-phase FCML work. I would never forget the dedication, efficiency and resourcefulness he demonstrated within just a few months in the group, and the seamless collaboration across continents since he went back to Taiwan.

In my journey of pursuing the passion for EV engineering, I had the pleasure and honor to work with some brilliant people that shared the same vision as I do. I would like to thank my peers in the Formula SAE Electric team during my early days in undergraduate, Evan Klepitsch, Andy Putch, Meyyappan Ramu, Matt Feddersen and many more for teaching me how to lead and collaborate in a large-scale project and dynamic environment. I would also like to thank my mentors from my first internship at Tesla Motors in 2014, Chenny Wang, Shino Xu, and Na Di. Thank you for giving me the opportunity to work on the cutting edge of EV technologies and shaping me into a more professional and well-rounded engineer, and driving me home or to groceries even after a long day of work.

I would like to thank my parents Liao Shengzhi and He Aizhen, for all the love and support over the years. They are not only the best parents who always respect and support my decisions, but also my best friends and mentors. Besides striving to provide me with the best education, their own established careers have always inspired me to pursue excellence in life. I thank them for teaching me the important lessons such as time management and critical thinking since very young age, which are both valuable qualities for success in research and beyond.

Last but definitely not the least, I want to thank my wife, Yun Hao. I am the luckiest person to have met my soul mate during graduate school. I want to thank her for the encouragement and support after long hours in the lab, for moving together with me to California, and for sharing ups and downs in graduate school with me as a fellow Ph.D. student. I am grateful to her for preparing the most beautiful wedding, which was the absolute highlight of the whole graduate school and my happiest moment. Finishing Ph.D. together with my life partner is something that I could never dreamed of when I started, and I have never been more certain that an exciting future is awaiting us.

## Chapter 1

## Introduction

## 1.1 Grid-tied Ac-dc and Dc-ac Conversion

Power electronics based ac-dc and dc-ac power conversion systems are critical links in the power delivery chains of today's electrical grid: With the recent increasing market penetration of electric vehicles, high-efficiency ac-dc converters become vital to deliver power from the ac grid to the high voltage dc battery in the vehicle; As human beings are generating more data than ever before, the energy consumption from the data centers, in which the servers are dc-powered, are becoming more and more significant; Delivering power to today's massive amount of consumer electronics products with more computing power and larger batteries also requires more efficient ac-dc converters; To integrate more renewable sources to cope with the increasing energy demand, photovoltaic (PV) systems and battery energy storage systems are often coupled together to provide a stable energy generation, which also requires bidirectional ac-dc power flow between the ac grid and the dc PV panels and batteries.

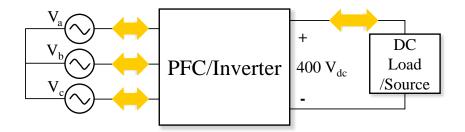

In the aforementioned applications and among many others, the ac grid voltage can be single-phase, three-phase or multi-phase with different regional voltage levels and frequencies, and the dc voltage can range from a few kilo-volts for solar inverters, to a few hundreds volts for EV battery charging, and a few volts for consumer electronics. While power electronics systems for these different specifications vary in the actual hardware designs, there are many desirable features and fundamental challenges in common. In all these systems, there are energy-storage components that are processing line-frequency power flows, and there are power converters that are operated at much higher frequencies, which contain both active switching devices and passive energy storage components. How to best utilize the energy in these components with the right circuit topology and architecture, and control the power converters accordingly become key to improve the power density and efficiency of the overall systems, which are desirable to reduce wasted energy and be more compliant with space and weight constraints.

Conventional solutions such as two-level based power converters and passive filtering

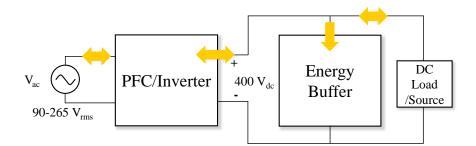

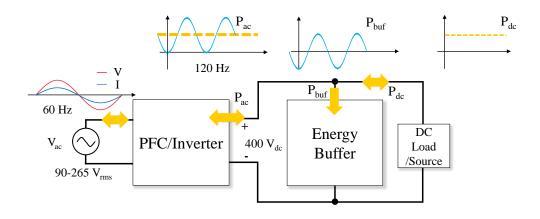

Figure 1.1: Typical single-phase conversion system block diagram for EV charging, data center power delivery and solar inverter applications.

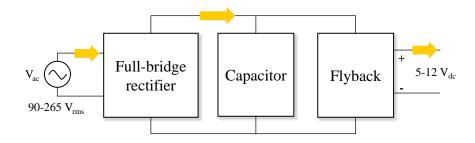

Figure 1.2: Typical single-phase conversion system block diagram for low power USB-C adapter applications

Figure 1.3: Typical three-phase conversion system block diagram for EV charging, data center and solar inverter applications

solutions at the line frequency have many limitations that prevent them from achieving higher power density and efficiency. As such, a more fundamental design philosophy that considers the energy utilization and the energy density of both low and high-frequency components, and the associate power electronics circuits and controls is needed to overcome the limitations of conventional designs.

## **1.2** Research Scope and Goals

In this dissertation, techniques to improve the power density and efficiency of both singlephase (ac-dc or dc-ac) and three-phase converters are explored.

For single-phase conversion, one of the most common conversion scenarios is between the universal single-phase ac (90-265  $\mathrm{V}_{\mathrm{rms}})$  and a dc load or source with voltage around 400  $V_{dc}$  (depending on the direction of the power flow), as depicted in Fig. 1.1. It can be used for emerging applications such as on-board EV charging, data center power delivery, and solar inverters. In such conversion scenarios, since the ac side has to deliver power at kilowatt level, the power factor is usually controlled to be close to unity with a Power Factor Correction (PFC) converter or current-controlled inverter. As such, there will be instantaneous power mismatch between the dc-side and ac-side, and an energy buffering device is needed to compensate for such mismatch. In conventional solutions, this energy buffering device is usually implemented with a large capacitor bank across the dc-bus, which dominates the volume of the overall system. In this thesis, we investigate the design and control of active buffer solutions that can significantly reduce the size of the energy buffer in level-II EV charging and data center power delivery applications. Moreover, by applying similar buffer topologies to other applications such as USB-C flyback adapter chargers in Fig. 1.2 for consumer electronics, the line-frequency energy storage capacitor size can also be much reduced.