### **Lawrence Berkeley National Laboratory**

**Recent Work**

#### **Title**

AN INTEGRAL DESIGN TECHNIQUE FOR WIDEBAND MULTISTAGE TRANSISTOR AMPLIFIERS

#### **Permalink**

https://escholarship.org/uc/item/0gk0v8x1

#### **Author**

Scott, Larry.

#### **Publication Date**

1962-04-27

# University of California

# Ernest O. Lawrence Radiation Laboratory

#### TWO-WEEK LOAN COPY

This is a Library Circulating Copy which may be borrowed for two weeks. For a personal retention copy, call Tech. Info. Division, Ext. 5545

Berkeley, California

#### **DISCLAIMER**

This document was prepared as an account of work sponsored by the United States Government. While this document is believed to contain correct information, neither the United States Government nor any agency thereof, nor the Regents of the University of California, nor any of their employees, makes any warranty, express or implied, or assumes any legal responsibility for the accuracy, completeness, or usefulness of any information, apparatus, product, or process disclosed, or represents that its use would not infringe privately owned rights. Reference herein to any specific commercial product, process, or service by its trade name, trademark, manufacturer, or otherwise, does not necessarily constitute or imply its endorsement, recommendation, or favoring by the United States Government or any agency thereof, or the Regents of the University of California. The views and opinions of authors expressed herein do not necessarily state or reflect those of the United States Government or any agency thereof or the Regents of the University of California.

UCRL-10009 Rev.

#### UNIVERSITY OF CALIFORNIA

Lawrence Radiation Laboratory Berkeley, California

Contract No. W-7405-eng-48

# AN INTEGRAL DESIGN TECHNIQUE FOR WIDEBAND MULTISTAGE TRANSISTOR AMPLIFIERS

Larry Scott

April 27, 1962

## AN INTEGRAL DESIGN TECHNIQUE FOR WIDEBAND MULTISTAGE TRANSISTOR AMPLIFIERS

Larry Scott

Lawrence Radiation Laboratory

University of California

Berkeley, California

April 27, 1962

#### ABSTRACT

Presented herein is a philosophy for designing wideband multistage transistor amplifiers. The amplifier is visualized as an integral unit, the interstage networks constituting the elements of the amplifier unit. By designing the amplifier as a unit and adjusting the overall response (gain and bandwidth) with the interstage time constants, an increase in gain-bandwidth product is realized over the iteratively designed amplifiers. The resulting increase in gain-bandwidth product results from absence of the bandwidth shrinkage factor for multistage amplifiers.

Formulas are derived for both a two- and three-transistor integrally designed wideband amplifier, in which shunt peaking networks are used for coupling. Experimental amplifiers were constructed following these formulas, and the observed performance agreed quite well with the calculations.

## AN INTEGRAL DESIGN TECHNIQUE FOR WIDEBAND MULTISTAGE TRANSISTOR AMPLIFIERS

Larry Scott

Lawrence Radiation Laboratory University of California Berkeley, California

April 27, 1962

#### I. INTRODUCTION

A greater overall gain-bandwidth product for multistage amplifiers is realizable through a design procedure that characterizes the total amplifier rather than characterizing each stage separately. The design entails picturing the several stages of the amplifier as an integral unit and adjusting the individual time constants to obtain the desired overall response. The principle of stagger tuning has been applied to transistor amplifiers by Victor H. Grinich and others, and can be considered as an application of the integral-unit philosophy of circuit design. However, the use of this design philosophy as shown in this paper is not yet reported elsewhere in print.

The increase in gain-bandwidth product will be shown to result from the absence of the bandwidth shrinkage factor in the calculation. Here the bandwidth shrinkage factor is the ratio of overall amplifier bandwidth to the interstage bandwidth of an iteratively designed amplifier. If the iteratively designed amplifier has a single-time-constant (one-pole) response, the shrinkage factor is given by  $(2^{1/N}-1)^{1/2}$ , where N is the number of cascaded stages. Absence of the shrinkage factor is the result of an integral-unit design philosophy, rather than an iterative (i. e., identical-stages-cascaded) design. The convenience of designing one stage and then cascading costs the designer a fraction of the attainable gain-bandwidth product of the multistage amplifier. The integral-unit philosophy is applied here

Work done under the auspices of the U. S. Atomic Energy Commission.

to the design of both two- and three- transistor amplifiers utilizing shunt-peaked interstage networks. Shunt-peaking interstage networks are selected because of their relative simplicity and conservation of gain-bandwidth product when broadbanded. The gain-bandwidth product of a shunt-peaked interstage is approximately equal to 4 of the transistor.

As shown in Appendix A, the current gain of a typical shunt-peaked interstage is of the form

$$A_i = H \frac{p+z}{p^2 + ap + b}$$

where p = ju, and H is a constant.

It can easily be shown that the shunt-peaked interstage can be designed to yield a single-time-constant (one-pole) form of response. This occurs by factoring the denominator polynomial into two real roots, one of which is set equal to the numerator term (the zero), and the resulting function is of the form (see Appendix A)

$$A_1 = \frac{H}{p+c} = \frac{p+z^2}{p+z} = \frac{H}{p+c}.$$

For two chunt-peaked interstages connected in series the current gain is of the form

$$A_1 = H_1H_2 \frac{p+3_1}{p^2+a_1p+b_1} \times \frac{p+3_2}{p^2+a_2p+b_2}$$

Let one stage (1) be designed for a single-pole response,

$$A_1 = H_1 H_2 \frac{p+3_1}{(p+c_1)(p+3_1)} \times \frac{p+3_2}{p^2+a_2 p+b_2};$$

then for c<sub>1</sub> = 3<sub>2</sub>,

$$A_1 = \frac{H_1 H_2}{p^2 + a_2 p + b_2}$$

.

This current-gain expression shows that the bandwidth is determined only by the second interstage, and the gain by both interstage networks. The two roots of the denominator polynomial may be varied to obtain the shape of response desired, maximally flat magnitude, linear phase, and other results.

For three stages, the final form of the gain is

$$A_1 = \frac{H_1 H_2 H_3}{(p^2 + a_2 p + b_2)(p + c_3)}$$

To generalize on this wheme, assume a product of n shunt-peaked interstage terms

$$A_{1} = \prod_{i=1}^{n} \frac{H_{i}(p + z_{i})}{p^{2} + a_{i} p + b_{i}}$$

#### List of symbols

C = depletion-layer capacitance of the collector-base junction

r,' = extrinsic base resistance of transistor

$r_0 = \frac{kT}{q_0^2} = \frac{0.026 \text{ volt}}{l_0}$ , intrinsic emitter resistance (where  $l_0$  is the dc emitter current)

$R_1 = (B_0 + 1) (r_e + R_e)$

R<sub>a</sub> = external emitter resistance, unbypassed

R<sub>1</sub> = interstage resistance

L = interstage inductance

$\beta_0 = \frac{a_0}{(1-a_0)}$ , or low-frequency current gain of a common emitter stage when the load is a short circuit

$\omega_{\beta}$  = frequency at which the common emitter current gain has dropped 3 db from  $\beta_0$ , with a short-circuit load

$\omega_{\rm g} = \omega_{\rm g} (\beta_0 + 1)$

ω<sub>3db</sub> = frequency at which the amplifier response is down 3 db from its low-frequency value

$= 1 + \omega_t (C_c + C_{cb})(R_L + r_c + R_e), \text{ a factor that indicates the degradation of bandwidth because of feedback through <math>C_c$  and  $C_{cb}$  (where  $C_{cb}$  is the extrinsic collector-to-base capacitance.)

By proper cancellation of the numerator and denominator factors the overall A<sub>I</sub> function can take the form

$$A_{1} = {n \choose 1} H_{1} / (p^{n} + a_{n}p^{n-1} + b_{n}p^{n-2} + \cdots + y_{n}p + z_{n}),$$

which means that the response function for n stages contains an nth-order polynomial in the denominator.

To determine the relative merit of this design, the resulting bandwidth, as determined by the nth-order denominator polynomial, is multiplied by the low-frequency gain, and this gain-bandwidth product is then compared with that obtained by cascading the same number of transistors in an iterative design. In the iterative design, all stages have the same bandwidth and a single-time-constant form of response.

#### II. ANALYSIS OF INTEGRAL DESIGN

The band-edge frequency of an nth-order gain function is determined by the shape of the response; for our examples, a maximally flat magnitude response is specified.

#### A. Two-Stage Amplifier

For the two-stage amplifier, we have

$$A_1 = H_1 H_2 / (p^2 + a_2 p + b_2)$$

(1)

For maximally flat magnitude we require

$$a_2^2 = 2b_2 . \tag{2}$$

and the 3-db frequency is

$$\omega_{3 \text{ db}} = \sqrt{b_2} . \tag{3}$$

The low-frequency gain to expressed by

$$A_1(0) = \frac{H_1 H_2}{b_2} , \qquad (4)$$

and the gain-bandwidth product in

$$A_1 (0) \omega_{3 db} = H_1 H_2 (b_2)^{1/2}$$

(5)

In terms of the circuit parameters, we have

$$H_1 = \omega_{q_1} / D_1$$

and

$$\omega_{3db}^{n} (b_{2})^{1/2} = \left[ \frac{\omega_{\beta(2)}}{D_{2}} \left( \frac{R_{I(2)}^{+} R_{1}^{+} r_{b}^{'}}{L_{2}} \right) \right]^{1/2}$$

, (6)

or

$$A_{i}(0) = \left(\frac{\omega_{t(1)}}{D_{1}} \times \frac{1}{\omega_{3db}}\right) \left(\frac{\omega_{t(2)}}{D_{2}} \times \frac{1}{\omega_{3db}}\right), \tag{7}$$

and

$$A_i(0) \omega_{3db} = \left(\frac{\omega_{t(1)}}{D_1} \times \frac{\omega_{t(2)}}{D_2}\right) \frac{1}{\omega_{3db}}.$$

(8)

It will be seen that the gain-bandwidth product for the integrally designed amplifier, Eq. (8), is greater than that of the iteratively designed amplifier with the same bandwidth by the reciprocal of the square of the shrinkage factor, for two stages, approximately a factor of 2.4.

#### B. Three-Stage Amplifier

In the case of the three-stage amplifier we have

$$A_1 = H_1 H_2 H_3 / (p^2 + a_2 p + b_2) (p + c_3),$$

(9)

and

$$p + s_2 = p + c_1 \text{ or } s_2 = c_1.$$

(10)

and we have

$$(p+s_1)(p+c_1)=p^2+a_1p+b_1$$

and

$$(P + z_3)(P + C_3) = P^2 + a_3P + b_3$$

or

$$\mathbf{z_1} + \mathbf{c_1} = \mathbf{a_1} \,. \tag{11}$$

$$\mathbf{z}_1 \in \mathbf{b}_1 . \tag{12}$$

and

$$\mathbf{z_3} + \mathbf{c_3} = \mathbf{a_3}, \tag{13}$$

$$\mathbf{z_3} \in_{\mathbf{3}} = \mathbf{b_3}. \tag{14}$$

For a maximally flat magnitude, we require

$$\mathbf{a_2} = \sqrt{\mathbf{b_2}}, \tag{15}$$

$$C_3 = C_2$$

(16)

and

$$\omega_{3 \text{ db}} = (b_2 \in_3)^{1/3}$$

(17)

The low-frequency gain for three stages is then expressed

$$A_{i}(0) = \frac{H_{1}H_{2}H_{3}}{b_{2}c_{3}}, \qquad (18)$$

and

$$A_{i}(0) \omega_{3} db = \frac{H_{1}H_{2}H_{3}}{(b_{2}c_{3})^{2/3}}$$

(19)

In terms of transistor parameters, we have

$$H_1 = \frac{\omega_{t(1)}}{D_1}.$$

$$H_2 = \frac{\omega_{t(2)}}{D_2}.$$

and

$$H_3 = \frac{\omega_{t(3)}}{D_3}.$$

Also,

$$b_2 = \frac{\omega_{\beta(2)}}{D_2} \left( \frac{R_{I(2)} + R_1 + r_b'}{L_2} \right)$$

$$\mathcal{E}_3 = \frac{\omega_{\beta(3)}}{D_3} \left( \frac{\mathbb{P}_{I(3)} \mathbb{P}_1 + \mathbf{r}_b'}{\mathbb{P}_{I(3)}} \right)$$

and

$$\omega_{3 \text{ db}} = (b_2 \circ_3)^{1/3}$$

;

oľ

$$A_{1}(0) = \left(\frac{\omega_{t}(1)}{D_{1}} \times \frac{1}{\omega_{3} db}\right) \left(\frac{\omega_{t}(2)}{\omega_{3} db} \times \frac{1}{\omega_{3} db}\right) \left(\frac{\omega_{t}(3)}{D_{3}} \times \frac{1}{\omega_{3} db}\right), \quad (20)$$

and

$$A_{i}(0) \omega_{3 db} = \left(\frac{\omega_{t(1)}}{D_{1}}\right) \left(\frac{\omega_{t(2)}}{D_{2}}\right) \left(\frac{\omega_{t(3)}}{D_{3}}\right) \left(\frac{1}{\omega^{2}_{3 db}}\right). \tag{21}$$

Generalizing, for n stages we apply the formula

$$A_{i}(0) = \left(\frac{\omega_{t(i)}}{D_{i}} \frac{1}{\omega_{3 db}}\right)^{n}. \tag{22}$$

#### III. ANALYSIS OF ITERATIVE DESIGN

The gain and bandwidth of an iteratively designed amplifier may be derived as follows.

Where the typical interstage gain in

$$a_1 = \frac{K}{(p} + p_0). \tag{23}$$

and

$$a_i(0) \omega_{3 db} = K$$

, and  $K = \frac{\omega_t}{D}$ . (24)

For n stages cascaded we have

$$a_{I} = [K/(p + p_{0})]^{n}$$

(25)

and

$$\omega_{3 \text{ db}} = P_0 \cdot S. \tag{26}$$

Where we have the chrinkago factor  $S = (2^{1/n} - 1)^{1/2}$ , (27) we have

$$a_{\mathbf{I}}(0) = \frac{K}{\mathbf{p_0}} = \left(\frac{\omega_{\mathbf{t}}}{\mathbf{D}} - \frac{1}{\omega_{\mathbf{3}d\mathbf{b}}}\right)^{\mathbf{n}} \mathbf{S}^{\mathbf{n}}$$

, (28)

and

$$\Delta_{1}(0) \omega_{3 db} (\omega_{t}/(D \omega_{3 db})^{n} \omega_{3 db} S^{n}$$

(29)

#### IV. COMPARATIVE THEORETICAL PERFORMANCE

By comparing integral equation (22) and iterative equation (28), we see that the gain of an n-transistor amplifier designed by the integral unit method is S<sup>-11</sup> times the gain of the iteratively designed one, where both amplifiers have the same overall bandwidth, and where S is the shrinkage factor calculated for n cascaded stages. Table I shows the gain-increase factor S<sup>-11</sup> for two-, three-, and four-stage integral designed amplifiers, in which

for equal bandwidths.

The resulting improvement in gain-bandwidth product indicates that for equal bandwidths the integrally designed amplifier will have a gain that is 2.4 times that of an iteratively designed amplifier using two interstages. For three transistor interstages the gain advantage is a factor of 8.48, and for a four-stage amplifier an impressive factor of 30.5.

If the compared amplifier designs are simplified to a typical or equivalent interstage of each overall design, the difference between them is the exclusion of the shrinkage factor from the integrally designed amplifier interstage. This indicates

an improvement in interstage broadbanding efficiency by the same amount as the gain-bandwidth product of that stage is increased; namely, the shrinkage factor.

#### V. EXPERIMENTAL VERIFICATION

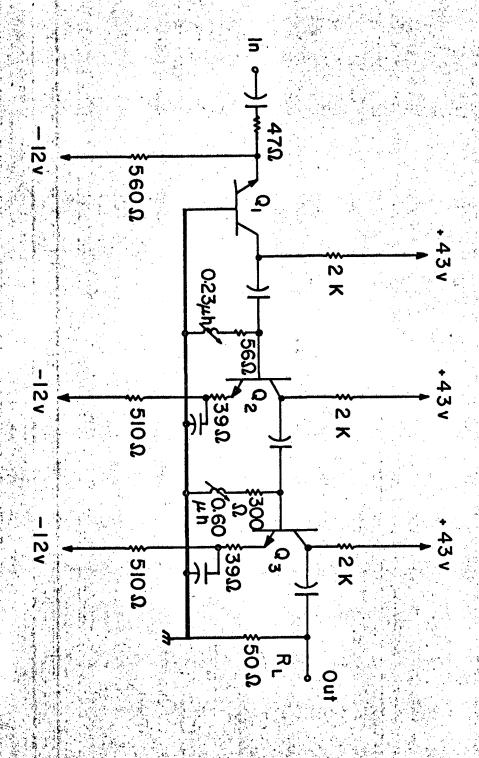

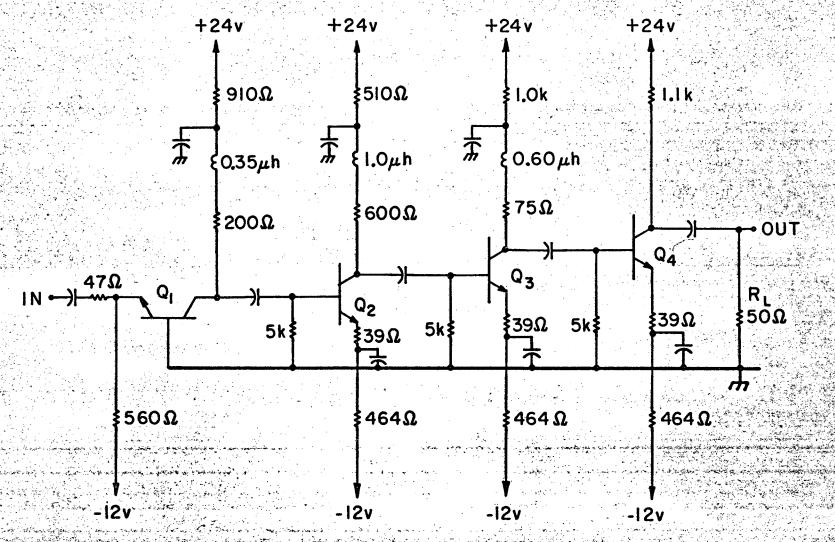

The procedures for integral designs, developed in detail in Appendices A and B, were used to design the two- and three-stage amplifiers shown in Figs. 1 and 2. Theoretical and experimental performance of the amplifiers are compared in Table II. The agreement between predicted gain and bandwidth, as shown, is as close as experimental accuracy allowed, about ±10%.

Although the design equations yield an exact cancellation between the numerator and demoninator terms, the realization of such exactness is not possible because of nonideal elements. The observed behavior of the two amplifiers, Figs. 1 and 2, indicates that considerable error in the cancellation may be tolerated before degradation of the performance results. Inasmuch as the final value of the numerator and denominator terms is determined by adjusting the value of the interstage inductance with a tuning slug while observing either the pulse or frequency response on an oscilloscope, the desired accuracy of cancellation is limited by the method of observation.

The amplifier of Fig. 1 was constructed with a silicon mesa-type transistor, 2N834. To reduce losses in the biasing circuitry a relatively large value of collector supply voltage was selected. However, in designing the second amplifier the selection of voltages was restricted to conform with LRL standards. The use of a lower supply potential necessitated placing the shunt-peaking circuit in the collector supply path rather than in the base. This in turn required the use of appropriate (5.0-kilohm) biasing resistors in the base circuit of the transistors.

The addition of a 39-ohm unbypassed resistance in the emitter lead of the shunt-peak stage desensitizes the circuit performance to transistor parameter changes (series feedback). The use of an unbypassed emitter resistance in no way degrades

the attainable performance of the shunt-peaked interstage, and it makes it possible to use arbitrarily selected transistors of the same type without redesign of the amplifier.

The design is most sensitive to changes in  $r_b$  of the transistors, as the value of the canceling term is approximately  $r_b$ /L, and the range of adjustment in L must be sufficient to account for variation in  $r_b$  from one transistor to another. The use of an unbypassed emitter resistance also reduces this sensitivity because the canceling term becomes  $(r_b' + R_e)$ /L. The available range of output voltage developed into a 50-ohm load for the examples is approximately  $\pm 0.75v$  with about 1% linearity.

#### VI. CONCLUSION

The philosophy of integral design is a useful technique for circumventing the limitation of gain-bandwidth product for multistage amplifiers. A greater gain-bandwidth product results for the integral design of multistage amplifiers because the bandwidth shrinkage factor is eliminated. This factor is defined as the loss in attainable gain-bandwidth product that results from cascading identically (iteratively) designed stages. By eliminating this loss, an appreciable increase in gain can be realized (see Table I), which could result in the use of fewer transistors to realize the same gain-bandwidth product as an iteratively designed amplifier.

Some practical difficulty is encountered with the design because the parameters of the transistors are not accurately known nor uniform from unit to unit. This difficulty can be somewhat reduced by such devices as the external emitter resistance used in amplifier design. The improvement in gain-bandwidth product realized by this design technique more than offsets these difficulties.

#### **ACKNOWLEDGMENTS**

I would like to thank D. O. Pederson of the University of California at Berkeley for his help and encouragement in developing this design technique, and the Lawrence Radiation Laboratory Nuclear Instrumentation Development Group, especially Horace G. Jackson, for frequent discussions.

The state of the s

#### APPENDICES

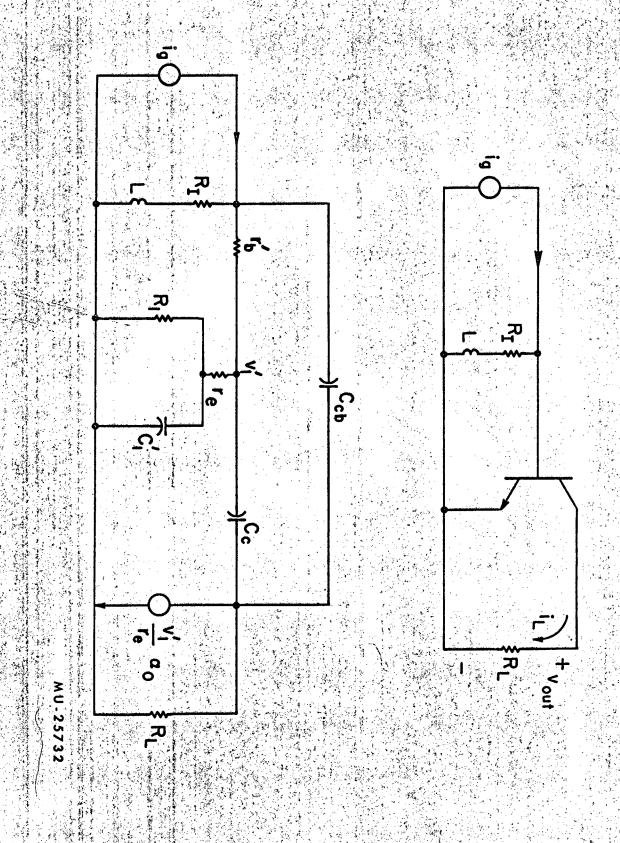

# A. The Integral Design of a Two-Transistor Shunt-Peaked Amplifier The gain of a typical shunt-peaked interstage may be derived as follows (see Fig. 3):

$A_{\underline{i}} = \frac{i_{\underline{L}}}{i_{\underline{g}}} = -\frac{\omega_{\underline{i}}}{D} \times \frac{P + R_{\underline{I}}/L}{P^{2} + \left(\frac{R_{\underline{I}} + r_{\underline{b}}'}{L} + \frac{\omega_{\underline{\beta}}}{D}\right) P + \frac{\omega_{\underline{\beta}}}{D} \left(\frac{R_{\underline{I}} + R_{\underline{I}} + r_{\underline{b}}'}{L}\right)}$ (A-1)

where

$$R_1 = (\beta_0 + 1)r_e$$

$$D = 1 + \omega_t(C_c + C_{cb}) (R_L + r_c)$$

,

and

$$\omega_t = \omega_{\beta}(\beta_0 + 1)$$

, as stated in Table I.

The condition for cancellation may be determined by dividing the denominator by the numerator to find

$$\begin{array}{c} \mathbf{p} + \frac{\mathbf{r}_{b}^{\prime}}{L} + \frac{\omega_{\beta}}{D} \\ \mathbf{p} + \frac{\mathbf{r}_{1}}{L^{\prime}} / \mathbf{p}^{2} + \left(\frac{\mathbf{R}_{1} + \mathbf{r}_{b}^{\prime}}{L^{\prime}} + \frac{\omega_{\beta}}{D}\right) \mathbf{p} + \frac{\omega_{\beta}}{D^{\prime}} \left(\frac{\mathbf{R}_{1} + \mathbf{R}_{1} + \mathbf{r}_{b}^{\prime}}{L^{\prime}}\right) \end{array}$$

$$\frac{p_{2}^{2}}{\left(\frac{r_{b}}{L} + \frac{\omega_{\beta}}{B}\right) p + \frac{\omega_{\beta}}{B} \left(\frac{R_{1}^{+} R_{1}^{+} r_{b}^{+}}{L}\right)}$$

$$\frac{\omega_{\beta}}{D} \left(\frac{R_{1}^{+}}{L} + \frac{R_{1}^{+} r_{b}^{+}}{L}\right)$$

$$\frac{\omega_{\beta}}{D} \left(\frac{R_{1}^{+} r_{b}^{+}}{L}\right) - \frac{R_{1}^{+} r_{b}^{+}}{L^{2}} = 0.$$

However, the denominator factors into

$$\left(p + \frac{R_I}{L}\right) \left(p + \frac{r_b}{L} + \frac{\omega_B}{D}\right), \tag{A-2}$$

provided that

$$\frac{\omega_{\beta}}{D} \left[ \frac{R_{1} + r_{b}'}{L} \right] - \frac{R_{1}r_{b}'}{L^{2}} = 0,$$

or if

$$\frac{R_{1}}{L} = \frac{\omega_{\beta}}{D} \left[ \frac{R_{1} + z_{b}'}{z_{b}'} \right]. \tag{A-3}$$

Now consider the case of two integral stages, for which we can derive the gain as follows:

$$A_{1} = \frac{\omega_{t(1)}}{D_{1}} \times \frac{\omega_{t(2)}}{D_{2}} \times \frac{\frac{p + R_{I(1)}/L_{1}}{D_{2}}}{\frac{p^{2} + \left(\frac{R_{I(1)} + R_{b}'}{L_{1}} + \frac{\omega_{\beta(1)}}{D_{1}}\right)p + \frac{\omega_{\beta(1)}}{D_{1}}\left(\frac{R_{I(1)} + R_{1} + R_{b}'}{L_{1}}\right)}$$

$$\times \frac{P^{+R_{1}(2)/L_{2}}}{P^{2}+\left(\frac{R_{1}(2)^{+R_{1}}}{L_{2}}+\frac{\omega_{\beta(2)}}{D_{2}}\right)P^{+\frac{\omega_{\beta(2)}}{D_{2}}}\left[\frac{R_{1}(2)^{+R_{1}+r_{0}}}{L_{2}}\right]. \quad (A-4)}$$

For cancellation we have

$$\frac{R_{I(1)}}{L_1} = \frac{\omega_{\beta(1)}}{D_1} \begin{bmatrix} R_1 + r_b' \\ -r_b' \end{bmatrix} , \tag{A-5}$$

and

$$\frac{R_{I(2)}}{L_2} = \frac{F_b'}{L_1} + \frac{\omega_{\beta(1)}}{D_1}.$$

(A-6)

The condition for maximally flat magnitude is

$$\frac{R_{1(2)} + r_{b}'}{L_{2}} + \frac{\omega_{\beta(2)}}{D_{2}} = \left[\frac{2\omega_{\beta(2)}}{D_{2}} \left(\frac{R_{1(2)} + R_{1} + r_{b}'}{L_{2}}\right)\right]^{1/2}$$

(A-7)

But we have

$$\omega_{3 \text{ db}} = \left[\frac{\omega_{\beta(2)}}{D_{2}} \left(\frac{R_{I(2)} + R_{1} + r_{b}}{L_{2}}\right)\right]^{1/2};$$

(A-8)

Then

$$A_{1} = \frac{\omega_{t}(1)}{D_{1}} \times \frac{\omega_{t}(2)}{D_{2}} \times \frac{1}{p^{2} + \left(\frac{R_{I(2)} + r_{b}}{L_{2}} + \frac{\omega_{\beta}(2)}{D_{2}}\right) p + \frac{\omega_{\beta}(2)}{D_{2}} \left[\frac{R_{I(2)} + r_{b}' + R_{I}}{L_{2}}\right]'}$$

and

$$A_1(0) = \frac{\omega_{\xi(1)}}{D_1} \times \frac{\omega_{\xi(2)}}{D_2} \times \frac{1}{\omega_{3 \text{ db}}}$$

(A-9)

A systematic design technique now appears in which we successively (a) pick a bandwidth ( $\omega_{3 \text{ db}}$ ) for the amplifier, or pick a gain, and then from Eq. (A-9) find the bandwidth;

(b) use the shape-constraint equation (A-7),

$$\frac{R_{I(2)} + r_b'}{L_2} + \frac{\omega_{\beta(2)}}{D_2} = \sqrt{2} \omega_{3 db}.$$

and Eq. (A-8), the bandwidth equation, to determine R<sub>I(2)</sub> and L<sub>2</sub>;

(c) use these data in turn to solve Eqs. (A-5) and (A-6) for  $R_{I(1)}$  and  $L_1$ .

There is an additional degree of freedom in the design that allows some flexibility in selecting components. This freedom results from varying  $\beta_0 r_e$ , since  $r_e = kT/qI_e$ , by changing  $I_e$ . These equations assume that the transistors,  $\omega_t$ ,  $\omega_b$ ,  $r_b$ ,  $C_c$ , and the optimum biasing conditions,  $I_e$ ,  $V_{ce}$ , have been specified.

If we include an unbypassed emitter resistance R<sub>e</sub>, to stabilize the design (see Appendix B), the design equations then become

(a) from (A-9),

$$A_1(0) = \frac{\omega_{t1}}{D_1} \times \frac{\omega_{t2}}{D_2} \times \frac{1}{\omega_{3db}};$$

(b) from (A-7) and (A-8),

$$\frac{R_{1_2} + r_{b_2}^{1'} + R_{e}^{1'}}{L_2} + \frac{\omega_{\beta_2}}{D_2} = \sqrt{2} \omega_{3 db},$$

$$\frac{\omega_{\beta_2}}{D_2} \left[ \frac{R_{I_2} + r_{b_2}^* + (\beta_{0_2} + 1) R^*}{L_2} \right] = \omega_{3db}^2$$

and (C) from (A-5) and (A-8),

$$\frac{R_{1}}{L_{1}} = \frac{\omega_{\beta_{1}}}{D_{1}} \left[ \frac{r_{b_{1}}^{\prime} + (\beta_{0_{1}} + 1) R_{E}^{\prime}}{r_{b_{1}}^{\prime} + R_{E}^{\prime}} \right]$$

and

$$\frac{R_{I_2}}{L_2} = \frac{r_{b_1}' + R'_E}{L_1} + \frac{\omega_{\beta_1}}{D_1}.$$

Let us assume an amplifier to be constructed from two 2N834 transistors to have a bandwidth of 75 Mc. The transistor parameters are as follows.

$$\frac{\beta_0}{(\text{Mc})} \frac{f_{\text{c}}}{(\Omega)} \frac{r_{\text{c}}^{1}}{(\text{pf})} \frac{C_{\text{c}} + C_{\text{c}}}{(\text{ma})} \frac{1}{(\text{volfs})}$$

$$\Omega_3 \qquad 54 \quad 500 \quad 90 \quad 4.0 \quad 20 \quad 5.0$$

$$\Omega_2 \qquad 46 \quad 460 \quad 55 \quad 4.0 \quad 20 \quad 5.0$$

To obtain a D factor assume  $R_L$  of  $\Omega_2$  is  $r_b^i$  of  $\Omega_3$ ,  $R_L$  of  $\Omega_3$  is 50  $\Omega$ .

Then

$$D_3 = 1 + \omega_t (C_c + C_{cb}) (R_L + R_E + r_e)$$

=  $1 + 2\pi (500 \times 10^6) (4.0 \times 10^{-12}) (50 + 40)$

=  $1 + 1.1 = 2.1$ ,

$D_2 = 1 + 2\pi (460 \times 10^6) (4.0 \times 10^{-12}) (90 + 40)$

=  $1 + 1.5 = 2.5$ .

then substitute into the design equations

(a)

$$A_i(0) = \left(\frac{460}{(2.5)(75)}\right) \left(\frac{500}{(2.1)(75)}\right) = 7.8$$

for  $\omega_{3 \text{ db}} = 2\pi \times 75 \times 10^6 = 4.7 \times 10^8$ ;

(b)

$$\frac{R_{1_2} + r_{b_2}^1 + R_E^1}{L_2} = \sqrt{2} \omega_{3db} - \frac{\omega_{\beta_2}}{D_2}$$

= (1.414)(4.7×10<sup>8</sup>) - 0.25×10<sup>8</sup> = 6.41×10<sup>8</sup>

and

$$\frac{R_{1_2} + r_{b_2}^{1} + (\beta_{0_2} + 1) R_{E}^{1}}{L_2} = \frac{\omega_{3 \text{ db}}^2}{\frac{\omega_{\beta_2}}{D_2}} = 88. \times 10^8,$$

or

$$\frac{\beta_0 R E}{L_2} = 88 \times 10^8 - \frac{R_{I_2} + R_{b_2} + R E}{L_2} = 81.4$$

$$L_2 = 0.23 \,\mu h$$

$$R_{I_2} = (6.62)(23.) - (55+40) = 56. \Omega;$$

(c) for cancellation,

$$\frac{R_{I_2}}{L_2} = \frac{r_{b_3}^{'} + R_{E}^{'}}{L_3} + \frac{\omega_{\beta_3}}{D_3},$$

$$L_3 = \frac{r_{b_3}^{'} + R_{E}^{'}}{\frac{R_{I_2}}{L_2} - \frac{\omega_{\beta_3}}{D_3}}$$

$$= \frac{90 + 40}{\frac{56}{0.23} - 27.7} \times 10^{-6} = 0.60 \mu h,$$

$$\frac{R_{I_3}}{L_3} = 27.7 \times 10^6 \left[ \frac{90 + (56 + 1)(40)}{90 + 40} \right].$$

$$R_7 = 300 \Omega.$$

The measured response showed a gain of 6.3 and a bandwidth of 85 Mc. A schematic of this amplifier, including a common base stage  $(O_1)$  at the input for matching the source impedance, is shown in Fig. 1. The loss in low-frequency gain due to the biasing resistances can be calculated as  $(\frac{2.0\times10^3}{2.3\times10^3}\times\frac{2.0\times10^3}{2.06\times10}3=)0.845$ , or a calculated gain of [(.845)(7.8)=] 6.6.

#### B. The Integral Design of a Three-Transistor Shunt-Peaked Amplifier

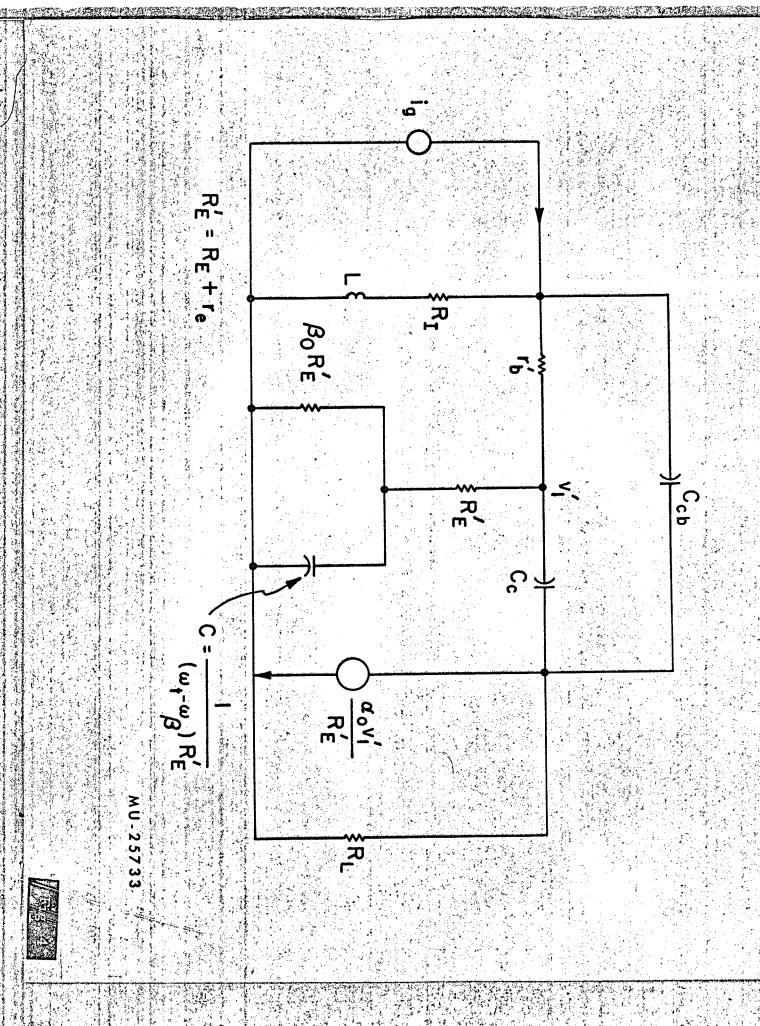

In order to operate the transistors at optimum emitter bias current while still maintaining the freedom to vary  $\beta_0 r_e$ , the input resistance of the transistor, a small unbypassed resistance ( $R_E$ ) is included in the emitter lead. The equivalent circuit is represented schematically in Fig. 4.

The gain can be derived as follows:

$$A_{i} = \frac{\omega_{t}}{D} \frac{p + R_{I}/L}{p^{2} + \left[\frac{R_{I} + R_{E}' + r_{b}' + \omega_{\beta}}{L}\right] p + \frac{\omega_{\beta}}{D}} \left[\frac{R_{I} + r_{b}' + \frac{(1)}{1 - \alpha_{0}}}{L}\right]$$

in which

$$D = 1 + \omega_t (C_c + C_{cb}) (R_L + R_E).$$

We now consider the case of three stages, for which we derive the gain as follows:

$$A_{1} = \frac{\omega_{t(1)}}{D_{1}} \times \frac{\omega_{t(2)}}{D_{2}} \times \frac{\omega_{t(3)}}{D_{3}}$$

$$\times \frac{p + R_{I(1)} / L_{1}}{p^{2} \left(\frac{R_{I(1)} + R_{E}^{i} + r_{b}^{i}}{L_{1}} + \frac{\omega_{\beta(1)}}{D_{1}}\right) p + \frac{\omega_{\beta(1)}}{D_{1}} \left(\frac{R_{I(1)} + r_{b}^{i} + \left(\frac{1}{1 - \alpha_{0}}\right) R_{E}^{i}}{L_{1}}\right)}{L_{1}}$$

$$\times \frac{\frac{p + R_{1(2)} / L_{2}}{P^{2} + \left(\frac{R_{1(2)} + R_{E}^{i} + r_{b}^{i}}{L_{2}} + \frac{\omega_{\beta(2)}}{D_{2}}\right) p + \frac{\omega_{\beta(2)}}{D_{2}} \left(\frac{R_{1(2)} + r_{b}^{i} + \left(\frac{1}{1 - \alpha_{0}}\right) R_{E}^{i}}{L_{2}}\right)}{L_{2}}$$

$$\times \frac{\frac{p + R_{I(3)} / L_{3}}{\sum_{p^{2} + \binom{R_{I(3)} + R_{E}^{i} + r_{b}^{i}}{L_{3}} + \frac{\omega_{\beta(3)}}{D_{3}} p + \frac{\omega_{\beta(3)}}{D_{3}} \binom{R_{I(3)} + r_{b}^{i} + \binom{1}{1 - \alpha_{0}} R_{E}^{i}}{L_{3}}}{\sum_{p^{2} + \binom{R_{I(3)} + R_{E}^{i} + r_{b}^{i}}{L_{3}}} \frac{(R_{I(3)} + r_{b}^{i} + \binom{1}{1 - \alpha_{0}}) R_{E}^{i}}{L_{3}}$$

For cancellation we have

$$\frac{R_{I(1)}}{L_1} = \frac{\omega_{\beta(1)}}{D_1} \left[ \frac{\beta_0 R_E^i + r_b^i}{R_E^i + r_b^i} \right]. \tag{B-3}$$

$$\frac{R_{I(2)}}{L_2} = \frac{\omega_{\beta(2)}}{D_2} \left[ \frac{\beta_0 R_E' + r_b'}{R_E' + r_b'} \right]. \tag{B-4}$$

and

$$\frac{R_{I(3)}}{L_3} = \frac{r_b' + R_E'}{L_2} + \frac{\omega_{\beta(2)}}{D_2}.$$

(B-5)

Then we can derive

$$A_{1} = \frac{\begin{pmatrix} \omega_{t(1)}/D_{1} \end{pmatrix} \begin{pmatrix} \omega_{t(2)}/D_{2} \end{pmatrix} \begin{pmatrix} \omega_{t(3)}/D_{3} \end{pmatrix}}{\begin{pmatrix} P_{1(3)}+P_{1}+P_{1}+P_{2}+P_{1}+P_{2}+P_{2}+P_{3}+P_{2}+P_{3}+P_{2}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{3}+P_{$$

For a maximally flat magnitude we have

$$\frac{R_{I(3)}^{+} r_{b}^{+} + R_{E}^{+}}{L_{3}} + \frac{\omega_{\beta(3)}}{D_{3}} = \left[ \frac{\omega_{\beta(3)}}{D_{3}} \left( \frac{R_{I(3)}^{+} r_{b}^{+} + R_{E}^{+}}{L_{3}} \right) \right]^{1/2} \\

= \frac{r_{b}^{+} + R_{E}^{+}}{L_{1}} + \frac{\omega_{\beta(1)}}{D_{1}}, \qquad (B-8)$$

and

$$\omega_{3db} = \left[ \left\{ \frac{\omega_{\beta(3)}}{D_3} \left( \frac{R_{I(3)} + r_b^{i} + R_E^{i}}{L_3} \right) \right\} \left\{ \frac{r_b^{i} + R_E^{i}}{L_1} + \frac{\omega_{\beta(1)}}{D_1} \right\} \right]^{1/3}$$

(B-9)

There are six unknowns (R<sub>1</sub> and L for each stage) and six equations (B-3, B-4, B-5, B-7, B-8, and B-9); therefore a solution is only a question of algebra. As in the two-transistor example, the initial step in the design is to specify the bandwidth, or to calculate the bandwidth from the specified gain and the gain-bandwidth product, which is

$$A_{\mathbf{I}}^{(0)} = \left(\frac{\omega_{\mathbf{t}(1)}}{D_{1}}\right) \left(\frac{\omega_{\mathbf{t}(2)}}{D_{2}}\right) \left(\frac{\omega_{\mathbf{t}(3)}}{D_{3}}\right).$$

$$A_{\mathbf{I}}^{(0)} = \omega_{\mathbf{3}db} = \left(\frac{\omega_{\mathbf{t}}}{D}\right)^{3} \left(\frac{1}{\omega_{\mathbf{3}db}}\right)^{2}.$$

(B-10)

An amplifier was constructed following the above design equations (see Fig. 2), with a specified bandwidth of 50 Mc. The gain calculated from Eq. (B-10) is 76 and the measured gain was 66, the difference resulting from losses in the bias circuitry (i.e., the 5 k base resistor). When the resulting 0.85 loss factor is included, the gains compare quite well.

The bandwidth was determined from a pulse-rise-time method to be

$$f_{3db} = 0.35/t_{r} = 0.35/(7.2 \times 10^{-9}) = 48 \text{ Mc.}$$

The amplifier comprised three 2N334 transistors, and the system was specified to have a bandwidth of 50 Mc. The properties of the transistors were as shown in the table.

|                | β <sub>0</sub> | f <sub>t</sub> (Mc) | r, | C <sub>C</sub> | <b>D</b> | Gain correction from biasing resistors |  |  |

|----------------|----------------|---------------------|----|----------------|----------|----------------------------------------|--|--|

| Ω <sub>2</sub> | 50             | 420                 | 60 | 4 pf           | 2.13     | 0.96                                   |  |  |

| 03             | 60             | 480                 | 60 | 4 pf           | 2.13     | 0.90                                   |  |  |

| 04             | 50             | 450                 | 60 | 4 pf           | 2,13     | 0.985                                  |  |  |

These properties yield a calculated gain

$$A_i = \begin{pmatrix} 450 \\ 2.13 \times 50 \end{pmatrix} \begin{pmatrix} 450 \\ 2.13 \times 50 \end{pmatrix} \begin{pmatrix} 420 \\ 2.13 \times 50 \end{pmatrix} = 76,$$

which, when the loss from the biasing resistors is included, gives us, for amplifier gain,

$$76 \times (0.96)(0.90)(0.985) = 66.$$

#### BIBLIOGRAPHY

- 1. / J. M. Pettit and M. M. McWhorter, Electronic Amplifier Circuits, McGraw-Hill Book Company, Inc., New York, 1961.

- 2. Victor H. Grinich, "Stagger-tuned transistor video amplifiers," in Proceedings of Western Electronic Show and Conference (WESCON), Los Angeles, California, 1956, Session of August 21, sponsored by the Group on Broadcast and TV Receivers.

- 3. D. O. Pederson and R. S. Pepper, "Evaluations of transistor low-pass broadbanding techniques," in Proceedings of the 1959 Western Electronic Show and Conference (WESCON), vol. 3, Part 2.

- 4. M. S. Ghausi, "Analysis and design of the shunt-series feedback pair,"

Series No. 60, Issue No. 307, Electronics Research Laboratory, University

of California, Berkeley, August 16, 1960.

Georg Brunn, "Common emitter-transistor video amplifiers," IRE Trans. on Instrumentation, vol. 44, No. 11, November 1956, pp. 1561-1572.

Table I. Gain increase factors for two-, three-, and four-stage amplifiers

| iadie i. Caiu |            |   | (wo-, c.,, co-,      |                     |  |

|---------------|------------|---|----------------------|---------------------|--|

|               | Stages (n) |   | S                    | s <sup>-n</sup>     |  |

|               | 3          | C | .64<br>).49<br>).425 | 2.4<br>8.48<br>30.5 |  |

Table II. Comparison of calculated and measured performances of the amplifiers (Figs. 1 and 2).

| n n       | Gair       | n        | Bandwidth (Mc) |            |          |     |

|-----------|------------|----------|----------------|------------|----------|-----|

|           | Calculated | Measured |                | Calculated | Measured |     |

| . <b></b> | 6.6        | 6.3      |                | 75         | 85       | y., |

|           | 66         | 66       |                | 50         | 48       |     |

#### FIGURE LEGENDS

- Fig. 1. Schematic diagram of a two-stage integrally designed amplifier.

- Fig. 2. Schematic diagram of a three-stage integrally designed amplifier.

- Fig. 3. Typical shunt-peaked interstage network.

- Fig. 4. Equivalent circuit with unbypassed resistance RE.

MU-25731

This report was prepared as an account of Government sponsored work. Neither the United States, nor the Commission, nor any person acting on behalf of the Commission:

- A. Makes any warranty or representation, expressed or implied, with respect to the accuracy, completeness, or usefulness of the information contained in this report, or that the use of any information, apparatus, method, or process disclosed in this report may not infringe privately owned rights; or

- B. Assumes any liabilities with respect to the use of, or for damages resulting from the use of any information, apparatus, method, or process disclosed in this report.

As used in the above, "person acting on behalf of the Commission" includes any employee or contractor of the Commission, or employee of such contractor, to the extent that such employee or contractor of the Commission, or employee of such contractor prepares, disseminates, or provides access to, any information pursuant to his employment or contract with the Commission, or his employment with such contractor.