### UC Berkeley UC Berkeley Electronic Theses and Dissertations

### Title

NEM Relay Scaling for Ultra-low Power Digital Logic

### Permalink

https://escholarship.org/uc/item/0s2216x1

### **Author** Yaung, Jack

# Publication Date 2014

Peer reviewed|Thesis/dissertation

NEM Relay Scaling for Ultra-low Power Digital Logic

by

Jack Yaung

A dissertation submitted in partial satisfaction of the

requirements for the degree of

Doctor of Philosophy

in

Engineering – Electrical Engineering and Computer Sciences

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Professor Tsu-Jae King Liu, Chair Professor Elad Alon Professor Junqiao Wu

Spring 2014

### NEM Relay Scaling for Ultra-low Power Digital Logic

Copyright © 2014

By

Jack Yaung

#### Abstract

#### NEM Relay Scaling for Ultra-low Power Digital Logic

By

Jack Yaung

Doctor of Philosophy in Engineering – Electrical Engineering and Computer Sciences

#### University of California, Berkeley

Professor Tsu-Jae King Liu, Chair

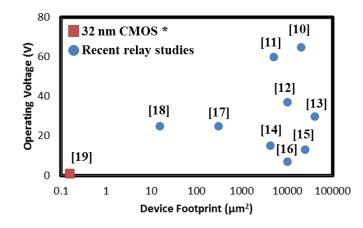

CMOS has been the building block for modern digital logic for decades and the performance and energy efficiency of CMOS continues to improve as technology develops, mainly through scaling. However due to the 60 mV/dec limit on MOS transistors, continue to reduce the power supply voltage would result in an increase in off-stage leakage current that would eventually dominate and increase the energy per operation of a transistor. In order to overcome this barrier, mechanical switches are proposed. Mechanical relays has the benefit of no leakage current through the air gap in the off state, which potentially enables further scaling of power supply voltage that can surpass MOS transistors. Several groups have been able to demonstrate mechanical switches with no leakage and abrupt on-off switching characteristics, however both the sizes of switches (~10<sup>4</sup>  $\mu$ m<sup>2</sup>) and the operation voltages (> 10 V) are huge, causing the switching energy to be significantly larger than MOS transistors. Scaling efforts are needed to minimize the switching energy of a mechanical switch.

In this thesis, prototype relay devices demonstrated by previous studies are discussed and the key factors that need to be addressed in order to minimize the switching energy are pointed out. The minimum switching energy is found to be limited by the contact adhesive force between contacts; studies on prototype devices with different contact areas shows that van der Waals force between contacts are the main source of adhesion in the prototype mechanical relays. Experiments show that by adding surface coating materials with low Hamaker constant can lower the contact adhesive force. In order to lower the structural stiffness, process development of poly-SiGe is optimized through multiple post-deposition processing techniques for reduced stress gradient of 100 nm thin films, a 10X reduction from the prototype devices. The combined learning from adhesive force work and thin film processing leads to the experiments of fabricating scaled devices of 500X smaller footprint. The results show that scaled relays can potentially operate at low voltages (~2V), but more process optimization needs to be done to demonstrate a fully operational device.

To my family

## **Table of Contents:**

| Acknowledgements                                            |    |  |

|-------------------------------------------------------------|----|--|

| Chapter 1: Introduction                                     | 1  |  |

| 1.1 The CMOS Power Crisis                                   | 1  |  |

| 1.2 The Subthreshold Swing Limitation of CMOS               | 2  |  |

| 1.3 MEM Relays for Energy-Efficient Computing               |    |  |

| 1.4 Thesis Overview                                         | 6  |  |

| 1.5 References                                              | 7  |  |

| Chapter 2: MEM Relay Theory and Operation                   | 9  |  |

| 2.1 Introduction                                            | 9  |  |

| 2.2 Prototype MEM Relay                                     |    |  |

| 2.2.1 Device Structure and Operation                        |    |  |

| 2.2.2 Fabrication Process                                   | 11 |  |

| 2.2.3 Measured Device Characteristics                       | 11 |  |

| 2.3 MEM Relays Switching Energy                             |    |  |

| 2.4 Key Challenges for Reducing Relay Switching Energy      | 20 |  |

| 2.5 Switching Energy Projection of Ultimately Scaled Relays |    |  |

| 2.6 Noise Considerations for Ultimately Scaled NEM Relays   |    |  |

| 2.6.1 Direct Tunneling Through the Contact Gap              | 23 |  |

| 2.6.2 Gravitational and Acceleration Forces                            | 24 |

|------------------------------------------------------------------------|----|

| 2.6.3 Thermal Vibrations                                               | 24 |

| 2.7 Summary                                                            | 25 |

| 2.8 References                                                         | 26 |

| Chapter 3: Study of Contact Adhesive Force                             | 28 |

| 3.1 Introduction                                                       | 28 |

| 3.2 Common Source of Adhesion                                          |    |

| 3.2.1 Capillary Force                                                  | 29 |

| 3.2.2 van der Waals Force                                              | 30 |

| 3.2.3 Hydrogen Bonding                                                 | 31 |

| 3.3 Characterization of Relay Contact Adhesion                         | 31 |

| 3.3.1 Experiment                                                       | 31 |

| 3.3.2 Adhesive Force Extraction from Electrical Measurements           | 31 |

| 3.3.3 Observations of Fabricated Relays                                | 32 |

| 3.3.4 Electrical Measurement Results                                   | 34 |

| 3.4 Modeling of Relay Contact Adhesion                                 | 36 |

| 3.5 Relay Switching Energy Projections Accounting for Contact Adhesion |    |

| 3.6 Impact of Ultra-thin Surface Coating                               |    |

| 3.7 Summary                                                            | 43 |

| 3.8 References                                                         | 44 |

| Chapter 4: Thin Film Process Development for NEM Relay Structure46                       |  |  |  |  |  |

|------------------------------------------------------------------------------------------|--|--|--|--|--|

| 4.1 Introduction                                                                         |  |  |  |  |  |

| 4.2 Stress Gradient Induced Out-of-Plane Deflection47                                    |  |  |  |  |  |

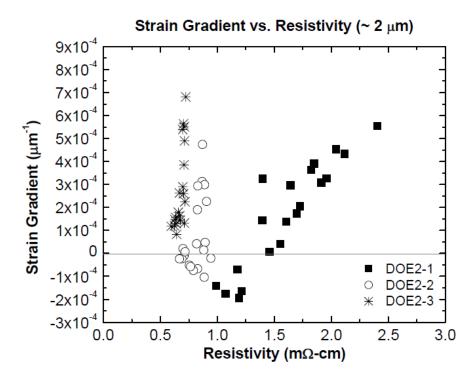

| 4.3 Reduction of Stress Gradient in LPCVD Poly-Si <sub>0.6</sub> Ge <sub>0.4</sub> Films |  |  |  |  |  |

| 4.3.1 Structural Properties of Poly-Si <sub>0.6</sub> Ge <sub>0.4</sub>                  |  |  |  |  |  |

| 4.3.2 Minimization of Amorphous Region Thickness                                         |  |  |  |  |  |

| 4.3.3 Post Deposition Processing to Reduce Stress Gradient                               |  |  |  |  |  |

| 4.3.4 Additional Scaling Challenges                                                      |  |  |  |  |  |

| 4.4 Summary                                                                              |  |  |  |  |  |

| 4.5 References                                                                           |  |  |  |  |  |

| Chapter 5: NEM Relay Fabrication using Electron-Beam Lithography61                       |  |  |  |  |  |

| 5.1 Introduction61                                                                       |  |  |  |  |  |

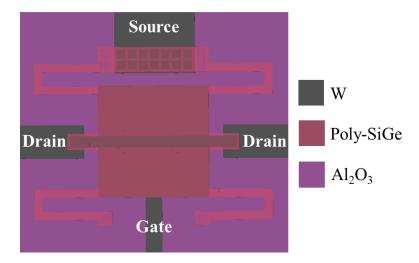

| 5.2 Relay Design and Fabrication Process                                                 |  |  |  |  |  |

| 5.3 NEM Relay Experimental results                                                       |  |  |  |  |  |

| 5.4 Summary71                                                                            |  |  |  |  |  |

| 5.5 References                                                                           |  |  |  |  |  |

| Cha | apter 6: Summary                           | 73 |  |

|-----|--------------------------------------------|----|--|

|     | 6.1 Contributions of This Work             | 73 |  |

|     | 6.2 Suggestions for Future Work            | 74 |  |

|     | 6.2.1 Process and Materials for NEM Relays | 74 |  |

|     | 6.2.2 Reliability of Scaled NEM Relays     | 74 |  |

|     | 6.2.3 Improved Relay Layouts               | 75 |  |

|     | 6.3 References                             |    |  |

## Acknowledgements

First I would like to acknowledge my advisor, Professor Tsu-Jae King Liu on advising my PhD thesis research, who is very patient and supportive along the years of my graduate life. Her extensive knowledge, discipline and passion on research have been important in guiding me through my thesis studies. Her involvement in multiple research centers also allows me to see a bigger picture and approach research, innovation and problem solving from a broader point of view, which are invaluable lessons that would benefit my career later in life.

I would like to thank Professor Junqiao Wu, Professor Ming Wu and Professor Elad Alon for serving on my PhD qualification committee, as their respective expertise and kind suggestions helped me to look at my research from different angles to have a more complete view of what needs to be understood.

I would like to also acknowledge Dr. Pratik Patel, Dr. Anupama Bowonder, Dr. Cheuk-Chi Lo, Dr. Hei Kam, Dr. Jaeseok Jeon, Dr. Vincent Pott and Dr. Rhesa Nathanael. As senior students and Postdocs at the time, they were very kind and helped me get up to speed with research and graduate student life. Without them I would have had a much more difficult time adjusting to graduate school life as a foreign student.

Students in the Berkeley's Device group are the absolute best people to work with, who are not only smart, knowledgeable but also passionate and cares for everyone in the group. I would like to thank Dr. Louis Hutin, Dr. Byron Ho, Dr. Chun Wing Yeung, Dr. Nuo Xu, Dr. Sung Hwan Kim, Dr. Eung Seok Park, Dr. Wookhyun Kwon, Dr. Min Hee Cho, Dr. Changhwan Shin, Dr. Peter Matheu, Dr. Xin Sun, Dr. Zachery Jacobson, Nattapol Damrongplasit, I-Ru Chen, Yenhao Chen, Chuang Qian and Peng Zheng. Their companionship during late nights in the clean room and many useful discussions in the office gave me many ideas to work on.

Since most of the experiments are done in the Marvell Nanofabrication Lab. I would like to thank all the Nanofabrication Lab staff, especially Jimmy Chang, Sia Parsa, Kim Chan, Jeff Clarkson and Richelieu Hemphill on helping me understanding the tools and adjust recipes; they were readily available for suggestions and were supportive of our often special requests. I would like to also thank Joe Donnelly, David Lo, Jay Morford, Ryan Rivers and Evan Stateler for keeping the tools up and running, which can be very difficult in a university clean room lab. Other lab members were also extremely nice to work with, their patience, lab etiquette and willingness to negotiate have helped me and many other members get the job done in a timely manner. I would like to thank Dr. Ting-Ta Yen, Dr. Chih-Ming Lin, Dr. Byung-Wook Yoo, Dr. Yuping Zheng, Dr. Chien-Yi Kuo, Ching Yi Hsu, Zeying Ren, Wei-Chang Li, Yang Lin for their help.

I want to thank the National Science Foundation for sponsoring my work, especially the Center of Integrated Nanomechanical Systems (COINS) and Center for Energy Efficient Electronics Science (E3S). I was very fortunate to work for research centers that have many different focuses and have a broad scope of interest in many different areas, which exposed me to different opportunities and a lot of people with various backgrounds. It gave me a better understanding of the problem at hand and discovered new approaches from people of different disciplines.

Finally I would like to thank my parents and my girlfriend Janie Lin. There are many difficult times during graduate school that makes me doubt my abilities and decisions, but because of their endless support and encouragement I was able to keep my head up and fight through. Without them I would have not survived and they are a part of everything I was able to accomplish.

### **Chapter 1**

### Introduction

### **1.1 The CMOS Power Crisis**

The evolution of technology not only depends on great minds, but also the capability to store and compute large amounts of information. As technology advances the amount of information processed is reaching incredible levels and yet more computational capacity is needed than ever. Complementary Metal-Oxide-Semiconductor (CMOS) transistors are the building blocks used predominantly in very large scale integrated circuits ("chips") since the 1980s. The number of transistors on a chip has roughly doubled every two years with each new generation of CMOS technology, so that the transistor count in the most advanced microprocessors grew from 42 million to 3 billion over the past decade [1]. Along the way, the performance and energy efficiency of CMOS transistors has improved, mainly due to miniaturization. By scaling down the device dimensions, capacitance and resistance are reduced, resulting in improved switching speed and decreased switching energy.

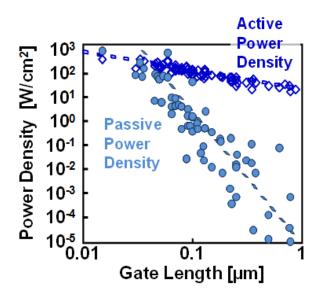

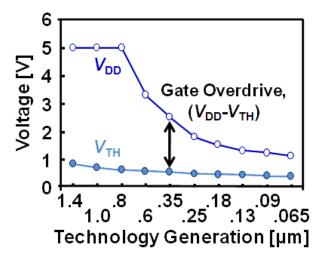

A fundamental challenge for continued CMOS technology scaling is that the chip operating voltage ( $V_{DD}$ ) cannot be reduced without degrading the transistor on/off current ratio. For this reason the leakage power density has been allowed to increase in recent CMOS technology nodes, so that it is now comparable to active power density [2] as shown in Fig. 1.1, in order to ensure sufficient circuit operating speed. Due to exponentially increasing off-state leakage current with threshold voltage ( $V_{TH}$ ) reduction, however,  $V_{TH}$  and  $V_{DD}$  scaling has slowed since the 90 nm technology node [3] as shown in Fig. 1.2.

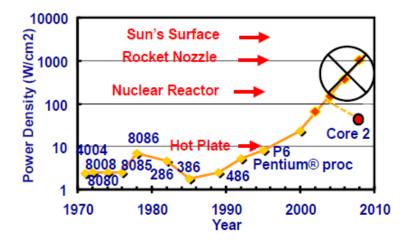

If  $V_{DD}$  is not reduced proportionately with transistor dimensions, then the active (switching) power density of a chip increases. For this reason parallelism (i.e. multi-core processors) was adopted beginning in 2005 to achieve improvements in system-level performance while averting a chip power density crisis (Fig. 1.3) [4].

Fig. 1.1 Chip power density vs. MOSFET gate length. Passive power density has been allowed to increase to become comparable to active power density (adapted from [2]), with CMOS scaling.

Fig. 1.2 Historical supply voltage and MOSFET threshold voltage scaling (adapted from [3]).

### **1.2 The Subthreshold Swing Limitation of CMOS**

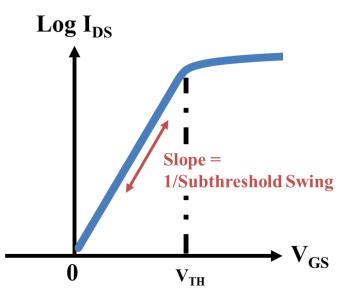

The reason for the CMOS power crisis is the nonscalability of  $V_{TH}$ . Fig. 1.4 illustrates the transfer characteristics of a CMOS transistor. In the sub-threshold region of operation, the output (drain) current increases exponentially as the input (gate) voltage increases. The steepness of this switching behavior is the Subthreshold Swing (SS), which is defined as the voltage swing required to effect a change in current by one order of magnitude (*i.e.* the inverse slope of the transfer characteristic in the sub-threshold region). A low value of SS is desirable, since it would mean that a smaller voltage swing is needed to switch the transistor on/off (*i.e.* V<sub>DD</sub> can be reduced). SS for a conventional planar bulk silicon MOS transistor is given by the following equation [5]:

**Fig. 1.3** Power density of commercial microprocessors. In recent years the power density of a microprocessor operates around the power density of a nuclear reactor, e.g. 65 W and 130W for Intel® CoreTM2 Duo E6320 (die size of 143 mm<sup>2</sup>) and Intel® CoreTM i7-990X (die size of 239 mm<sup>2</sup>), respectively [4].

$$SS = \left(1 + \frac{c_{DEP}}{c_{OX}}\right) \left(\frac{kT}{q} \ln 10\right)$$

(1.1)

where  $C_{OX}$  is the gate capacitance,  $C_{DEP}$  is the depletion capacitance, k is the Boltzmann constant, T is the absolute temperature and q is the electronic charge. The first factor on the right-hand side accounts for the capacitive voltage divider effect, and represents the ability of the gate voltage to control the semiconductor surface potential; it is always larger than 1. The second term relates to the thermal distribution of mobile charge carriers. Since kT/q = 25.6 mV, SS cannot be smaller than 60 mV/dec at room temperature.

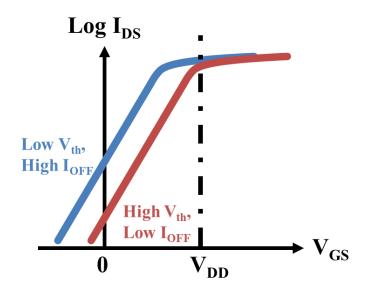

For a given (maximum) off-state leakage current specification ( $I_{OFF}$ ), SS sets the minimum value of  $V_{TH}$ . Lower  $I_{OFF}$  dictates a higher  $V_{TH}$  and hence lower on-state drive current ( $I_{ON}$ ) for a fixed value of  $V_{DD}$  [6]. This trade-off between  $I_{OFF}$  and  $I_{ON}$  is illustrated in Fig. 1.5.

An electronic switch that has SS lower than 60 mV/dec would allow for lower operating voltage with the same off-state leakage, making the device more energy efficient. The lower the SS, the more energy efficient a device can be.

### **1.3 MEM Relays for Energy-Efficient Computing**

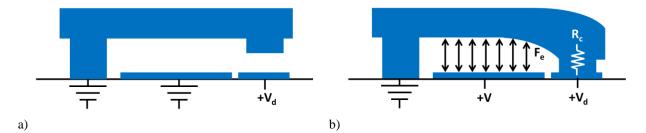

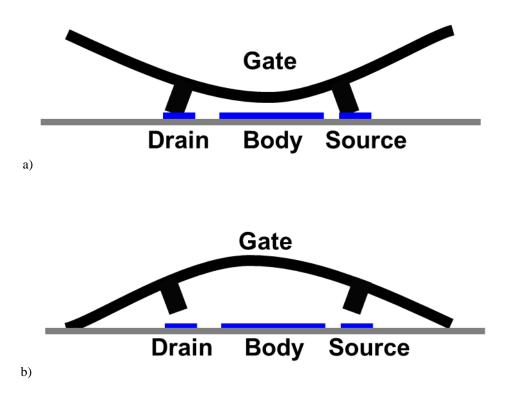

Current flow in a mechanical switch (relay) – which functions by making and breaking physical contact between conductive electrodes – transitions abruptly between off and on states, so that SS is nearly zero. Also, a mechanical switch has zero  $I_{OFF}$ , since an air-gap exists between the conductive electrodes in the off state, so that it can in principle provide for zero static power dissipation as well as very low active power dissipation. A simple three-terminal micro-electromechanical (MEM) relay structure comprising a cantilever beam is illustrated in Fig. 1.6. In the

**Fig. 1.4** Transfer characteristic of an n-channel MOSFET (semi-log plot). Current increases exponentially with gate voltage ( $V_{GS}$ ) in the subthreshold region, then linearly for  $V_{GS} > V_{TH}$ . The subthreshold swing (SS) is defined as the inverse of the subthreshold slope. Note that there is non-zero current in the off state ( $V_{GS} = 0$  V), which results in static power dissipation.

**Fig. 1.5** Transfer characteristics for MOSFETs with different values of  $V_{TH}$ . Low  $V_{TH}$  provides not only for higher drive current (at  $V_{GS} = V_{DD}$ ) and hence faster circuit operation, but also much higher off-state leakage current ( $I_{OFF}$ ) and hence greater static power dissipation.

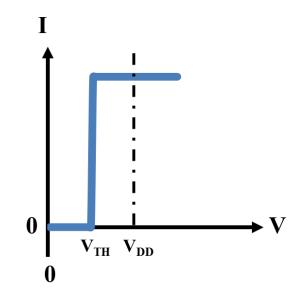

off state, an air gap exists between the cantilever tip and the underlying drain electrode so that no current can flow. If the voltage applied between the gate electrode and the cantilever beam exceeds a certain threshold, the electrostatic attractive force is sufficient to pull the tip of the cantilever beam into contact with the drain electrode so that current can flow. A conceptual current-*vs*.-voltage (I-V) characteristic is plotted in Fig. 1.7.

Fig. 1.6 Schematic cross-sectional illustration of a MEM relay. a) In the off state, there is zero leakage current since an air gap prevents current flow between the cantilever beam tip and underlying drain electrode. b) In the on state, electrostatic force between the gate electrode and the beam brings the tip into contact with the drain electrode. The on-state resistance is dominated by the contact resistance ( $R_c$ ).

Fig. 1.7 Conceptual transfer characteristics of a MEM relay. There is no leakage in the off state and the transition between off- and on-states is abrupt.  $V_{TH}$  can be reduced without any leakage power penalty.

Since they are generally larger and slower than transistors, MEM relays have been considered for applications such as RF switching or CMOS power gating [7][8]. In recent years, interest in scaled relay technology for digital computing has grown due to the CMOS power crisis. This is because a scaled, low-voltage relay technology potentially can provide for improved energy efficiency beyond the limits of CMOS technology. Much progress has been made in recent years to realize MEM switches with operating voltage approaching 1 V with high manufacturing yield and to demonstrate relay-based integrated circuits. Recently reported MEM switches are still behind state-of-the-art CMOS devices, as can be seen in Fig. 1.8 [10-18]. Relays must be scaled to nanoscale dimensions in order to be competitive [9].

Fig. 1.8 Benchmarking of device footprint and operating voltage of recently reported mechanical switches for digital logic. It is desired to have low operating voltage with small device footprint. There is generally a tradeoff between device footprint and operating voltage. \*Shown for reference is the footprint of a 6-transistor SRAM cell (0.157  $\mu$ m<sup>2</sup>) operated with V<sub>DD</sub> = 1 V [19].

### **1.4 Thesis Overview**

This thesis investigates NEM relays as potentially more energy-efficient alternatives to CMOS transistors for digital computation. Fundamental limitations for relay technology are identified, since off-state leakage and SS are not the limiters. Process technology challenges for NEM relay fabrication are also addressed.

Chapter 2 presents a MEM relay design that achieves zero off-state leakage and abrupt switching characteristics, and identifies the key issues that must be addressed in order to realize an energy efficient NEM relay. Performance characteristics of ultimately scaled NEM relays are projected.

Chapter 3 investigates contact adhesion, which can limit the energy efficiency of a mechanical switch. Adhesive force is extracted from electrical measurements and careful characterization of relay dimensions and contact topography. The cause of adhesion is identified by comparing experimental results with theoretical modeling. Surface coating is demonstrated to mitigate contact adhesion.

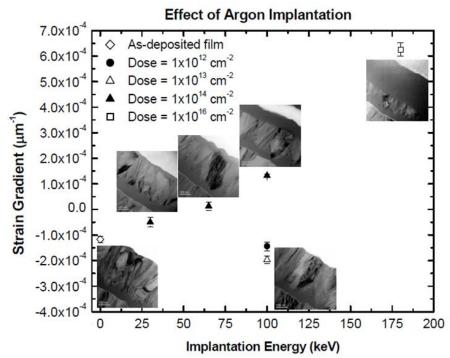

Chapter 4 investigates approaches to reduce the stress gradient within a thin polycrystalline  $Si_{1-x}Ge_x$  (poly-SiGe) structural film, which is used for nanoscale relay fabrication.

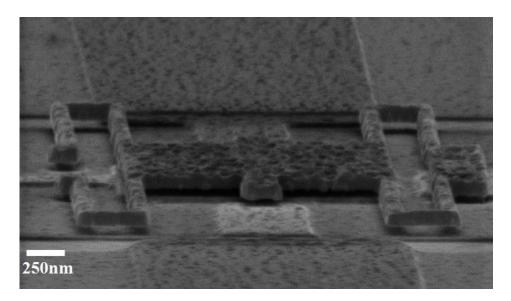

Chapter 5 describes the fabrication of scaled relays using e-beam lithography and optimized thin poly-SiGe films, which have  $500 \times$  smaller footprint as compared to the prototype devices in Chapter 2. Remaining challenges for realizing a fully functional scaled NEM relay are discussed.

Chapter 6 summarizes the key results and contributions of this work, and offers suggestions for future research directions.

### **1.5 References**

[1] Intel Processors. [Online] Available: http://ark.intel.com

[2] B. Meyerson, Semico Impact Conference, Taiwan, 2004.

[3] P. Packan, "Device and Circuit Interactions," IEEE International Electron Device Meeting (IEDM '07) Short Course: Performance Boosters for Advanced CMOS Devices, 2007.

[4] S. Y. Borkar, Intel Corp.

[5] R. S. Muller, T. I. Kamins, Device Electronics for Integrated Circuits, Wiley, 2003

[6] C. C. Hu, Modern Semiconductor Device for Integrated Circuits, Prentice Hall, 2010

[7] G. M. Rebeiz, J. B. Muldavin, "RF MEMS Switches and Switch Circuits," IEEE Microwave Magazine, Vol. 2, pp. 59-71, 2001.

[8] A. Raychowdhury, J. I. Kim, D. Peroulis, K. Roy, "Integrated MEMS Switches for Leakage Control of Battery-Operated Systems," CICC, 2006.

[9] K. Akarvardar, H. S. P. Wong, "Nanoelectromechanical Logic and Memory Devices," ECS Transactions, Vol. 19, No. 1, pp. 49-59, 2009.

[10] I. Schiele, J. Huber, C. Evers, B. Hillerich, F. Kozolowski, "Micromechanical Relay with Electrostatic Actuation," Proc. Transducer '97, 1997.

[11] K. E. Petersen, "Micromechanical Membrane Switches on Silicon, "IBM Journal of Research and Development, 1979.

[12] M. A. Gretillat, Y. J. Yang, E. S. Hung, V. Rabinovich, G. K. Ananthasuresh, N. F. de Rooij, S. D. Senturia, "Nonlinear Electromechanical Behavior of an Electrostatic Microrelay," Proc. Transducers '97, 1997.

[13] J. J. Yao, M. F. Chang, "A Surface Micromachined Miniature Switch for Telecommunications Applications with Signal Frequencies from DC up to 4GHz," Proc. Transducers '95, 1995.

[14] A. Hirata, K. Machida, H. Kyuragi, M. Maeda, "Electrostatic Micromechanical Switch for Logic Operation in Multichip Modules on Si," Sensors and Actuators A, vol. 80, pp. 119–125, 2000

[15] N. Sinha, T. S. Jones, Z. Guo, G. Piazza, "Demonstration of Low Voltage and Functionality Complete Logic Operations Using Body-Biased Complementary and Ultra-Thin AlN Piezoelectric Mechanical Switches," Proc. MEMS, 2010

[16] R. Nathanael, V. Pott, H. Kam, J. Jeon, T.-J. King Liu, "4-Terminal Relay Technology for Complementary Logic," IEEE International Electron Device Meeting (IEDM '09), 2009

[17] W. W. Jang, O. D. Kwon, J. O. Lee, J. B. Yoon, "Microelectromechanical (MEM) Switch and Inverter for Digital IC Applications," Sold-State Circuit Conference, 2007

[18] S. Chong, K. Akarvardar, R. Parsa, J. B. Yoon, R. T. Howe, S. Mitra, H. S. P. Wong, "Nanoelectromechanical (NEM) Relays Integrated with CMOS SRAM for Improved Stability and Low Leakage," Proc. ICCAD, 2009, pp. 478-484.

[19] X. Chen, S. Samavedam, V. Narayanan, K. Stein, C. Hobbs, C. Baiocco, W. Li, D. Jaeger, M. Zaleski1, H. S. Yang, N. Kim, Y. Lee, D. Zhang, L. Kang, J. Chen, H. Zhuang, A. Sheikh, J. Wallner, M. Aquilino, J. Han, Z. Jin, J. Li, G. Massey, S. Kalpat, R. Jha, N. Moumen, R. Mo, S. Kirshnan, X. Wang, M. Chudzik, M. Chowdhury, D. Nair, C. Reddy, Y. W. Teh, C. Kothandaraman, D. Coolbaugh, S. Pandey, D. Tekleab, A. Thean, M. Sherony, C. Lage1, J. Sudijono, R. Lindsay, J. H. Ku, M. Khare, A. Steegen, "A Cost Effective 32nm High-K/ Metal Gate CMOS Technology for Low Power Applications with Single-Metal/Gate-First Process," VLSI Symposium Technical Digest, pp. 88-89, 2008

### **Chapter 2**

## **MEM Relay Theory and Operation**

### **2.1 Introduction**

A scaled relay is a promising candidate to replace the transistor for ultra-low-power digital computing applications, because it offers the ideal characteristics of zero off-state leakage and abrupt switching behavior so that it in principle can provide for zero standby power and overcome fundamental  $V_{DD}$  scaling limitations for CMOS technology [1].

In this chapter, a prototype micro-electro-mechanical (MEM) relay design for digital logic applications is presented. In Section 2.2, the structure and operation of the 6-terminal relay are described. With the aid of the relay switching energy expression developed in Section 2.3, Section 2.4 identifies contact adhesion reduction and spring constant scaling by thinning the structural film as the key challenges to improve relay energy efficiency. In Section 2.5, switching energy projections of nanometer-scale (NEM) relays are made using Finite Element Method (FEM) simulations. Finally, Section 2.6 discusses some of the common concerns for NEM relays.

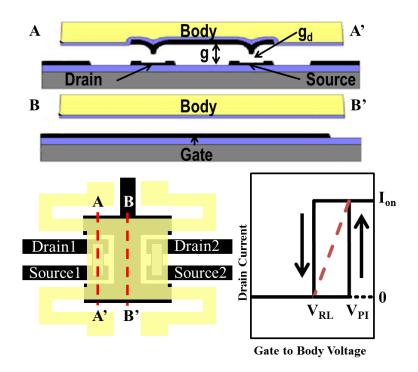

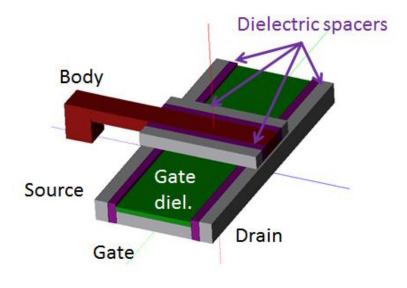

**Fig. 2.1** Top: Schematic cross sections through the channel (A-A') and center (B-B') of a MEM logic relay. Bottom left: Plan-view illustration of the MEM logic relay. Bottom right: conceptual  $I_{DS}$ - $V_{GB}$  characteristic of a MEM logic relay. The dashed line indicates an effective sub-threshold slope due to the difference between the turn-on voltage ( $V_{PI}$ ) and turn-off voltage ( $V_{RL}$ ).

### 2.2 Prototype MEM Relay

### 2.2.1 Device Structure and Operation

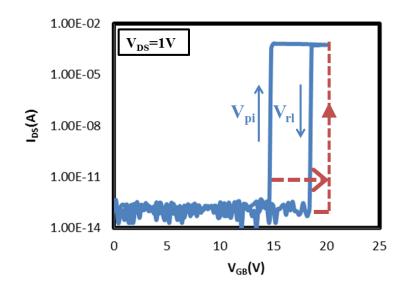

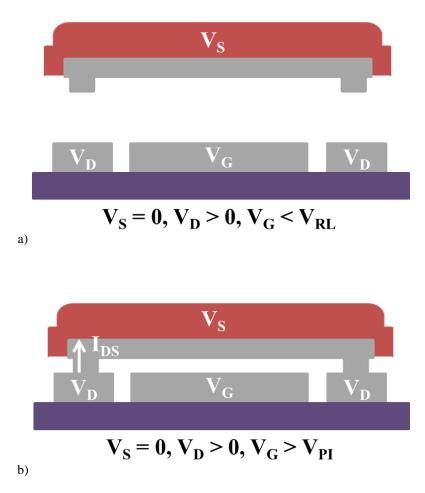

Fig. 2.1 illustrates the structure of an electrostatically actuated relay designed for digital logic applications [2]. The movable body electrode is suspended by folded-flexure beams above the source, drain and gate electrodes. No current flows in the off state because the channels (conductive strips attached underneath the body via an intermediary dielectric layer of Al<sub>2</sub>O<sub>3</sub>) are separated from the source/drain electrodes by the contact dimple gap. If a voltage is applied between the gate and body electrodes, the resultant electrostatic attractive force ( $F_e$ ) will actuate the body downward. When the applied gate-to-body voltage ( $V_{GB}$ ) is greater than or equal to the pull-in voltage ( $V_{PI}$ ), the channels will come into contact with the underlying source/drain electrodes, so that current can flow and hence the device is in the on state. Note that the current increases abruptly as  $V_{GB}$  is increased above  $V_{PI}$  to turn on the device. To turn off the device,  $V_{GB}$  must be reduced below the release voltage ( $V_{RL}$ ) such that the spring restoring force ( $F_k$ ) is larger than the contact adhesive force ( $F_A$ ) plus the electrostatic force ( $F_e$ ) and the channels will come out of contact with the source/drain electrodes. Note that the current decreases abruptly as  $V_{GB}$  is decreased below  $V_{RL} < V_{PI}$ .

### **2.2.2 Fabrication Process**

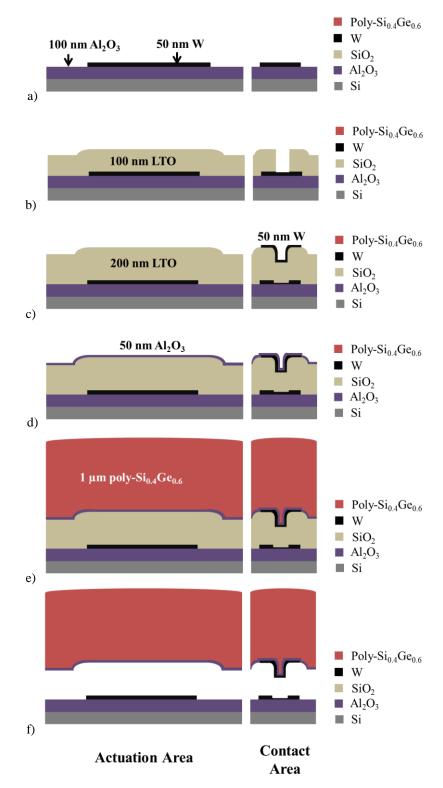

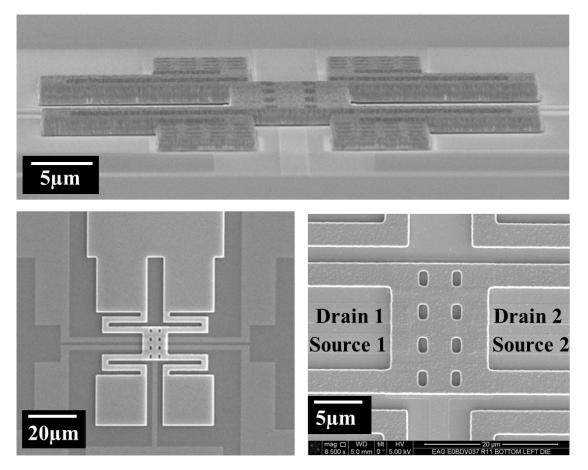

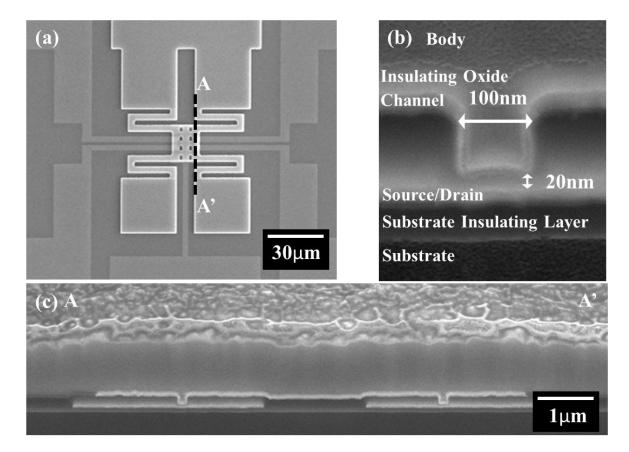

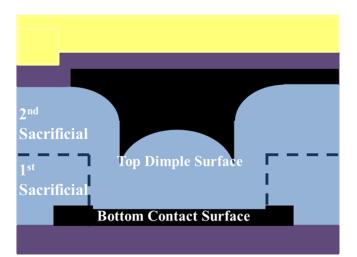

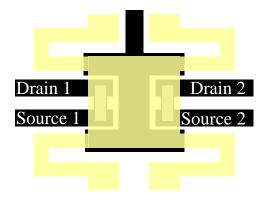

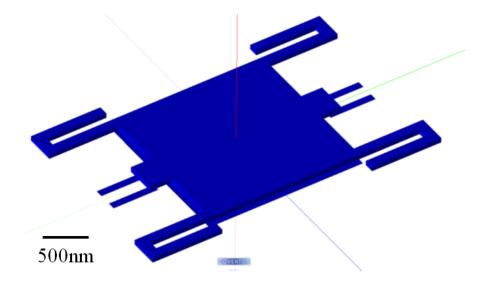

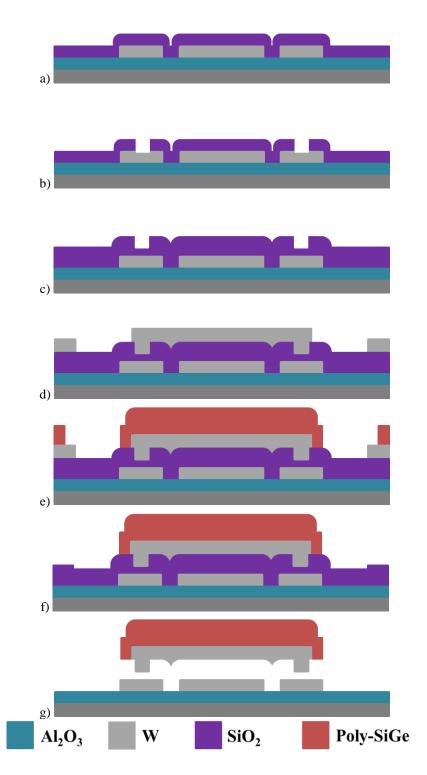

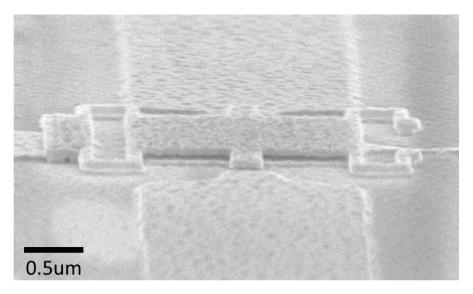

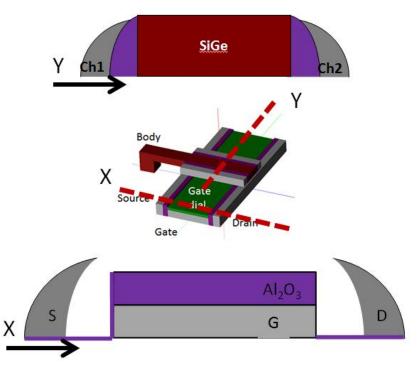

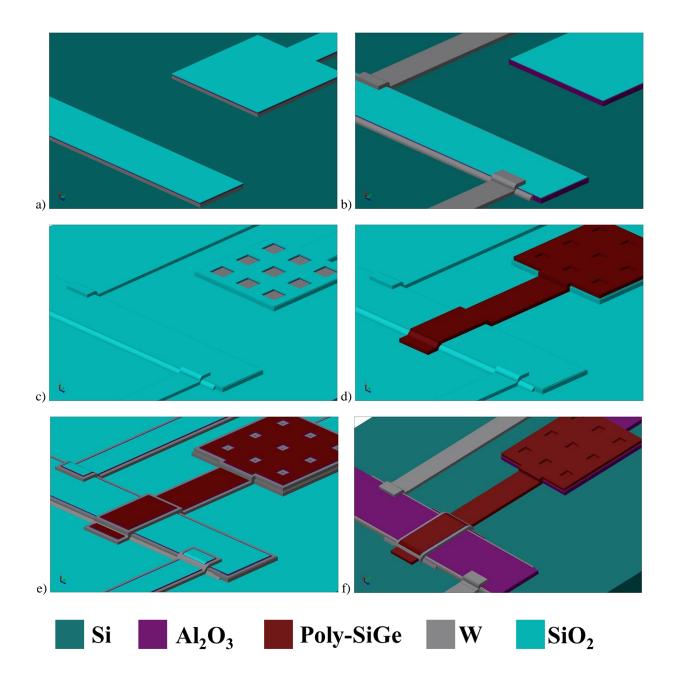

Prototype 6-terminal MEM logic relays were fabricated as follows. First, 100 nm Al<sub>2</sub>O<sub>3</sub> was deposited via Atomic Layer Deposition (ALD) to insulate the surface of the Si wafer substrate. Then, 50 nm Tungsten (W) was deposited by sputtering and patterned to form the source, drain and gate electrodes. Next, 100 nm SiO<sub>2</sub> (low temperature oxide, or LTO) was deposited via Low-Pressure Chemical Vapor Deposition (LPCVD) to form the first sacrificial layer, and patterned to define the contact dimple regions. Afterwards, a second layer of sacrificial LTO was deposited to provide for the contact dimple gap. Then, 50 nm W was sputtered and patterned to form the channels, and 50 nm Al<sub>2</sub>O<sub>3</sub> was deposited by ALD to insulate the channels from the body. Prior to deposition of 1  $\mu$ m p-type polycrystalline-Si<sub>0.4</sub>Ge<sub>0.6</sub> structural/body material by LPCVD, via holes were etched through the sacrificial layers to form anchor and interconnect regions. Lastly the structures were released by selectively removing the sacrificial LTO layers in HF vapor. Lithography is done using an ASML300 stepper with minimum feature size of 250 nm. ALD Al<sub>2</sub>O<sub>3</sub> is chosen as the insulating material due to its high resistance to HF vapor etching [3] [4]. An illustration of the process flow is shown in Fig. 2.2. Fig. 2.3 shows plan-view and cross-sectional scanning electron microscopy (SEM) images of a fabricated relay.

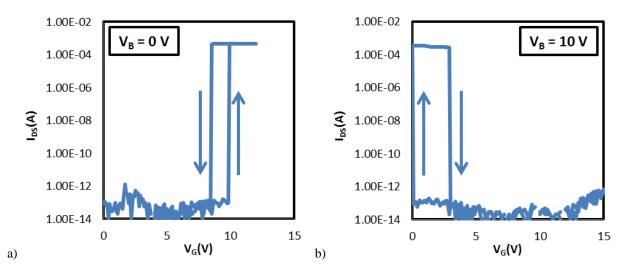

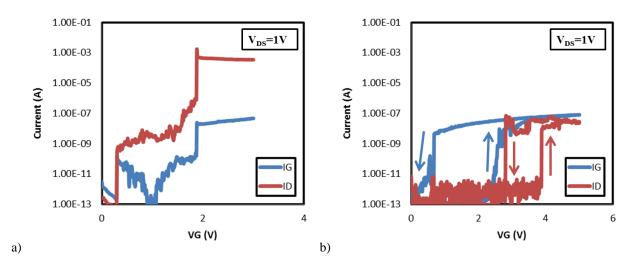

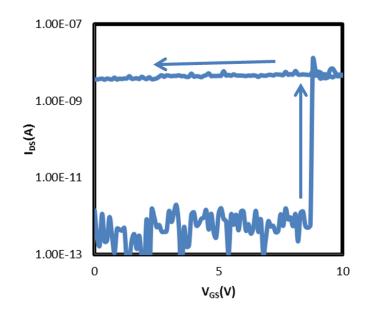

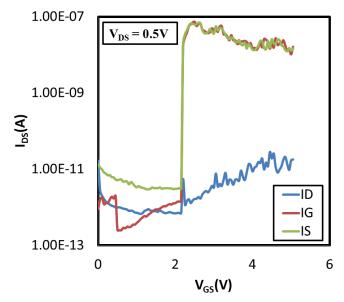

### 2.2.3 Measured Device Characteristics

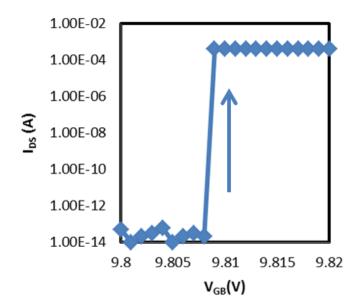

Measured  $I_{DS}$ -V<sub>GB</sub> characteristics are shown in Fig. 2.4. In the off state, the relay shows immeasurably low leakage current (<1 pA) [5]. The relay turns on abruptly when V<sub>GB</sub> increases above 10 V, transitioning from the OFF state to the ON state within a 1 mV step, as shown in Fig. 2.5. (1 mV is the minimum step size of the semiconductor parameter analyzer, so the actual subthreshold slope can be even steeper.) A 6-terminal relay has two sets of source/drain electrodes, *i.e.* it comprises two electrical switches. Since the structure is symmetrical, the two switches exhibit the same on-state current and switching voltages.

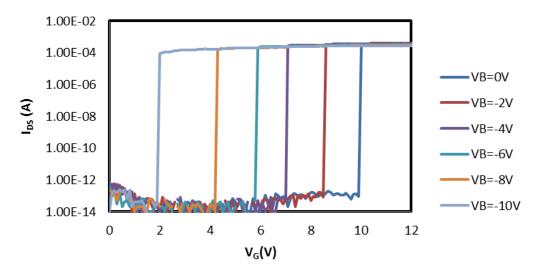

The switching gate voltages can be adjusted by applying a non-zero bias to the body electrode  $(V_B \neq 0)$  [6], since the electrostatic actuation force depends on  $V_{GB}$ . A negative body voltage  $(V_B < 0)$  can lower the gate voltage needed to turn the device on, as shown in Fig. 2.6.

The relay can be operated similarly as an n-channel (NMOS) transistor, to serve as a "pulldown" device, by applying zero or negative body bias ( $V_B \le 0$ ). Since electrostatic force is ambipolar, the relay also can be turned on by applying  $V_{GB} < -10$  V (*e.g.* by setting  $V_G = 0$  V and applying  $V_B > 10$  V). Thus, a relay can be operated similarly as a p-channel (PMOS) transistor, to serve as a "pull-up" device, by applying a positive body bias ( $V_B \ge 0$ ). This enables complementary logic circuits to be implemented without any extra process steps [7] [8].

**Fig. 2.2** Schematic cross-sections illustrating the relay fabrication process. ((a) Bottom electrodes are formed on  $Al_2O_3$ -coated substrate. (b)  $1^{st}$  sacrificial layer deposition and contact definition. (c)  $2^{nd}$  sacrificial layer deposition followed by metal channel deposition and patterning. (d)  $Al_2O_3$  gate oxide deposition. (e) Via patterning (not shown) and poly-Si<sub>0.4</sub>Ge<sub>0.6</sub> structure formation. (f) vapor-HF release etch.

**Fig. 2.3** Scanning electron micrographs of a MEM logic relay. Top: Side view. Bottom left: plan view. Bottom right: Zoomed-in plan view with two sets of source/drain electrodes labelled.

As shown in Fig. 2.4, the voltage at which a relay turns off  $(V_{RL})$  is smaller than the voltage at which the relay turns on  $(V_{PI})$ , *i.e.* there is hysteresis in the switching characteristic. The hysteresis voltage  $(|V_{PI} - V_{RL}|)$  sets the lower limit for the relay operating voltage, since the gate voltage swing must be sufficiently large to switch the relay between OFF and ON states. (A body bias voltage can be applied to reduce the gate switching voltages, but the turn-off voltage must be greater than or equal to zero in order for the relay to be OFF at 0 V.)

This prototype device demonstrates that a MEM relay can achieve zero standby power and has abrupt switching behavior so that it can potentially operate with very low voltage. Further work is needed, however, to demonstrate that a relay can be further miniaturized (to have comparable minimum dimension as a transistor) with a hysteresis voltage that is much lower than 1 V (corresponding to  $V_{DD}$  for modern CMOS technology). This is necessary in order to achieve superior energy efficiency [9].

**Fig. 2.4** Measured  $I_{DS}$ -V<sub>G</sub> characteristics of a 6-terminal relay. The off-state current is measured to average around 100 fA, which is limited by the semiconductor parameter analyzer noise level. Relay turn-on and turn-off is observed to be extremely abrupt. (a) MEM relay with  $V_B = 0$  V exhibits "NMOS like" characteristics. (b) MEM relay with  $V_B = 10$  V shows "PMOS like" characteristics (*i.e.* turning on with decreasing  $V_G$  and turning off with increasing  $V_G$ ).

**Fig. 2.5** Measured  $I_{DS}$ - $V_{GB}$  (for the same device as in Fig. 2.4) showing turn-on abruptness. The relay turns on between 9.808V and 9.809V with 10 orders of magnitude on/off ratio. SS is extracted to be less than 0.1 mV/dec.

**Fig. 2.6** Measured  $I_{DS}$ - $V_G$  curves for different body biases.  $|V_{GB}|$  at pull-in slightly increases as  $V_B$  becomes more negative, most likely due to parasitic capacitance between the gate and the source/drain electrodes.

### 2.3 MEM Relay Switching Energy

Modeling the switching energy of a relay requires the knowledge of all forces acting on the relay; mainly  $F_e$  and  $F_k$ . Fortunately, with the folded flexure structure design, the modeling can be relatively simple. A number of assumptions are made in order to simplify the model:

- 1) The moveable plate is rigid, so the stiffness of the relay only depends on the stiffness of the flexures.

- 2) F<sub>e</sub> only exists between gate and body electrodes, since the gate/body area is significantly larger than the drain/source area.

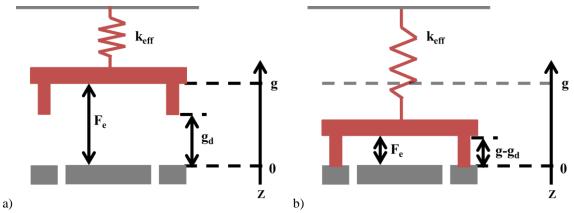

Under these assumptions, the relay structure can be modelled as a spring attached to a parallel plate shown in Fig. 2.7. The vertical positions are labeled on the right. Without any voltage applied, the moveable plate is suspended by the flexures and would be at z = g. When the relay is pulled down, the dimples will make contact with the bottom electrode and the moveable plate will be at position  $z = g - g_d$ .

Based on assumptions 1) and 2),  $F_e$  of the relay can be modeled as the electrostatic force between conductive parallel plates, which is given by the following equation [10]:

$$F_e = \frac{\varepsilon_o A_{OV} V^2}{2z^2} \tag{2.1}$$

where z is the distance between the parallel plates,  $\varepsilon_0$  is the permittivity of air,  $A_{OV}$  is the parallel plate area and V is the voltage between the plates.  $F_k$  can be modeled by Hooke's Law:

**Fig. 2.7** Simplified model of a relay structure. (a) In the off state, the vertical position is at z = g. (b) In the on state, the structure travels a distance of  $g_d$  and stops when the dimples make contact; the vertical position of the structure is  $z = g - g_d$ .

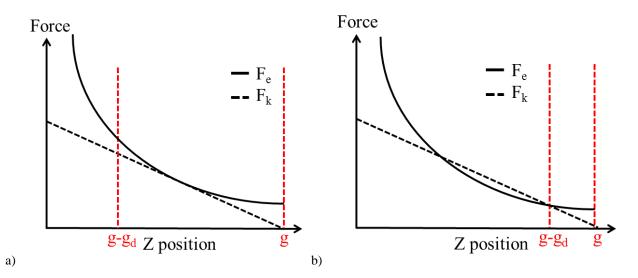

Fig. 2.8 Forces vs. vertical position of a relay in the off state. With  $V < V_{PI}$ ,  $F_k$  is always larger than  $F_e$  so the air gap cannot be closed.

$$F_k = k_{eff}(g - z) \tag{2.2}$$

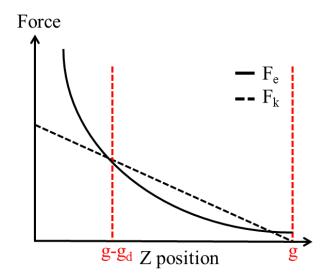

where  $k_{eff}$  is effective spring constant, dominated by the folded flexures, g - z is the deflection of the springs. To switch the relay from off to on, the electrostatic force needs to be larger than the spring restoring force. Fig. 2.8 shows the forces *vs.* vertical position of a relay. According to the force equations above,  $F_e$  has a superlinear relationship ( $z^{-2}$ ) to distance and  $F_k$  has a linear relationship to deflection. If  $F_e$  is larger than  $F_k$  at a given position, there is a net pull-down force on the relay. However if  $F_k$  is larger than  $F_e$ , then the relay will experience a net pull-up force.

With V < V<sub>PI</sub> (Fig. 2.8), the electrostatic force is only sufficient to pull the structure part-way down. But with V = V<sub>PI</sub> (Fig. 2.9),  $F_e$  will be larger than  $F_k$  at any given position, so the relay

**Fig. 2.9** Electrostatic force at  $V = V_{PI}$  vs. vertical position in the on state of (a) a relay designed for pull-in-mode operation, *i.e.* large  $g_d/g$  ratio, and (b) a relay designed for non-pull-in mode operation, *i.e.* small  $g_d/g$  ratio.

will experience a net pull-down force until the dimples come into contact with the source/drain electrodes to turn on the device.

According to Fig. 2.9a, the pull-in voltage is the voltage for which  $F_e$  will always be larger than  $F_k$ . In this situation, the  $F_e$  curve has only one point of intersection with the  $F_k$  curve, at z = 1/3 g. The above condition results in the following expression [11]:

$$\frac{\varepsilon_o A_{OV} V_{PI}^2}{2(g-z)^2} > k_{eff} z \tag{2.3}$$

$$\frac{\varepsilon_0 A_{OV} V_{PI}^2}{2k_{eff} g^3} = \frac{z}{g} \left(1 - \frac{z}{g}\right)^2 > \frac{4}{27}$$

(2.4)

At  $V = V_{PI}$ , the left hand side of Equation 2.3 is larger than the right hand side regardless of z. Since the right hand size has a maximum when z = (1/3)g, the pull-in voltage can be solved as:

$$V_{PI} = \sqrt{\frac{8k_{eff}g^3}{27\varepsilon_0 A_{OV}}} \tag{2.5}$$

The device turns off once  $F_k$  is sufficient to pull the structure away from the bottom electrodes; this condition gives the release voltage as shown below:

$$k_{eff}g_d > \frac{\varepsilon_o A_{OV} V_{RL}^2}{2(g - g_d)^2} + F_A$$

(2.6)

$$V_{RL} = \sqrt{\frac{2(k_{eff}g_d - F_A)(g - g_d)^2}{\varepsilon_o A_{OV}}}$$

(2.7)

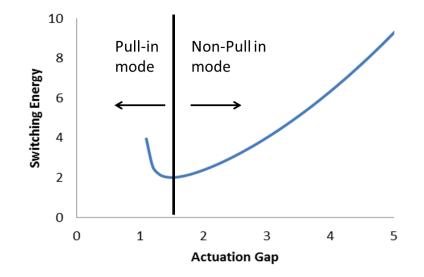

**Fig. 2.10** Normalized switching energy vs. normalized (to  $g_d$ ) actuation gap, assuming a fixed minimum dimple gap limited by the process technology.  $g_d$ ,  $A_{OV}$ ,  $k_{eff}$  each are set to 1. A minimum at  $g/g_d = 3/2$  is observed.

where  $F_A$  is the contact adhesive force. It is obvious that the pull-in and release voltages are not the same, resulting in hysteresis. From Equations 2.6 and 2.7, there are two main causes of hysteresis; one is the contact adhesive force, which works against  $F_k$ . The other can be seen from Fig. 2.9a: for this relay design,  $F_e$  exceeds  $F_k$  when the device is on, so the voltage must be lowered further (even without  $F_A$ ) in order to turn off the device. The hysteresis voltage is a fraction of  $V_{PI}$  and can be minimized by reducing  $g_d$  to be no greater than g/3. Fig. 2.9b shows the force curve for such a relay design: in the on state,  $F_e$  will be equal to  $F_k$ , and without  $F_A$  this device will have no hysteresis. A relay corresponding to Fig. 2.9a is of the "pull-in mode" design, whereas a relay corresponding to Fig. 2.9b is of the "non-pull-in-mode" design. The voltage at which a non-pull in mode relay turns on is

$$V_{NPI} = \sqrt{\frac{2k_{eff}g_d(g-g_d)^2}{\varepsilon_o A_{OV}}}$$

(2.8)

Regardless of the operating mode, the switching energy of a relay based on the earlier assumptions presented is the energy required to charge the structure-to-bottom-electrode parallel plate capacitor, which is the on-state capacitance times the operating voltage squared:

$$E_{PI} = C_{ON} V_{PI}^{2} = \frac{\varepsilon_{o} A_{OV}}{(g - g_{d})} \left( \sqrt{\frac{8k_{eff} g^{3}}{27\varepsilon_{o} A_{OV}}} \right)^{2} = \frac{8k_{eff} g^{3}}{27(g - g_{d})}$$

(2.9)

$$E_{NPI} = C_{ON} V_{NPI}^{2} = \frac{\varepsilon_{o} A_{OV}}{(g - g_{d})} \left( \sqrt{\frac{2k_{eff} g_{d} (g - g_{d})^{2}}{\varepsilon_{o} A_{OV}}} \right)^{2} = 2k_{eff} g_{d} (g - g_{d})$$

(2.10)

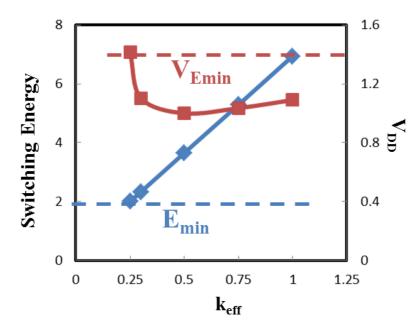

**Fig. 2.11** Switching energy (blue diamonds) and minimum operating voltage (red squares) *vs.*  $k_{eff}$  for an applied body bias of  $-V_{RL}$ .  $E_{min}$  is the minimum switching energy allowed by  $F_A$ .  $V_{Emin}$  is defined to be  $V_{DD}$  for  $E = E_{min}$ .

From the equation above it can be seen that in order to minimize the switching energy, one should lower the spring constant and minimize the actuation gap: lowering the spring constant would decrease  $F_e$  needed to turn the device on; reducing the actuation gap would decrease the voltage needed to create the same  $F_e$ . Relay switching energy scaling is ultimately limited by the contact adhesive force which sets the minimum  $F_k$  required to turn the device off, which in turn sets the minimum  $F_e$  needed to turn the device on. Given this  $F_A$  constraint, the minimum switching energy is derived below [12]:

$$k_{eff}g_d > F_A \tag{2.11}$$

$$E_{PI,MIN} = \frac{8k_{eff}g^3}{27(g-g_d)} = \frac{8F_Ag^3}{27g_d(g-g_d)}$$

(2.12)

$$E_{NPI,MIN} = 2F_A(g - g_d) \tag{2.13}$$

The optimal operation mode for a relay can be identified from Fig. 2.10;  $F_A$  and  $g_d$  values are assumed to be limited by the process technology and physics. The curve shows that there is a minimum energy for a relay operating in the pull-in mode at  $g_d = (2/3)g$ , which corresponds to pull-in-mode operation. This is mainly because there is a trade-off between on-state capacitance and voltage: as the actuation gap increases the on-state capacitance decreases but the actuation voltage increases, and *vice versa* [13].

It was mentioned above that a body bias voltage can be used to adjust the gate switching voltages, which can also reduce  $V_{DD}$  for a MEM relay. With body bias applied,  $V_{DD}$  can be reduced to the hysteresis voltage of the relay. The switching energy can be calculated by

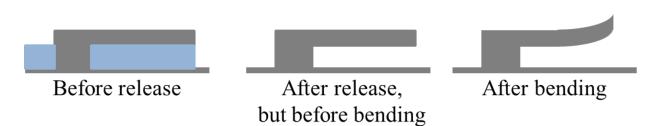

**Fig. 2.12** Cantilever with a stress gradient before and after release. After release but before bending is a hypothetical intermediate state to illustrate how residual stress is released to cause out-of-plane deflection. (Adapted from [10]).

subtracting the energy stored in the capacitor in the OFF state from the energy stored in the ON state, assuming  $V_B = -V_{RL}$ :

$$C_{ON}V_{PI}^{2} - C_{OFF}V_{RL}^{2} = \frac{8k_{eff}g^{3}}{27(g-g_{d})} - \frac{\varepsilon_{o}A_{OV}}{(g-g_{off})}V_{RL}^{2}$$

(2.14)

Note that

$$\frac{\varepsilon_o A_{OV} V_{RL}^2}{2(g - g_{off})^2} = k_{eff} g_{off}$$

(2.15)

where  $g_{off}$  is the amount of deflection in the off state. The switching energy and minimum operating voltage  $V_{DD} = V_{PI} - V_{RL}$  for a pull-in-mode relay with an applied body bias  $V_B = -V_{RL}$  are plotted as a function of  $k_{eff}$  in Fig. 2.11. Although  $V_{DD}$  is not minimized at minimum  $k_{eff}$ , the switching energy is still minimized at minimum  $k_{eff}$ . This indicates that, although body biasing can provide for lower  $V_{DD}$ , it is more important to lower  $k_{eff}$ , *i.e.* make the relay structure as compliant as allowed by  $F_A$ , to achieve the minimum switching energy.

### 2.4 Key Challenges for Reducing Relay Switching Energy

From the switching energy expression derived in the previous section, a number of technological challenges can be identified:

- 1)  $F_A$  scaling: In order for the relay to turn off,  $F_k$  must be larger than  $F_A$ . For the device to turn on  $F_k$  has to be overcome by  $F_e$ , which determines  $V_{PI}$  and switching energy. As a result, the minimum switching energy of a normally-off relay ultimately is limited by  $F_A$ . To study the origin and scalability of  $F_A$  is extremely important.

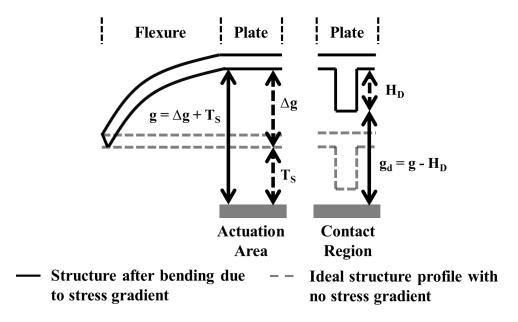

- 2) It is desirable to create relays with low structural stiffness ( $k_{eff}$ ), to lower the energy needed to turn the device on. For example the main reason the prototype relay has high operating voltage (ref. Fig. 2.4) is because the structure is too stiff. One can easily make a relay softer by making the suspension beams longer, but this increases the device footprint which is not desirable from a chip cost standpoint. It is preferable to scale down the structural layer thickness. Out-of-plane bending due to non-zero stress gradient (Fig.

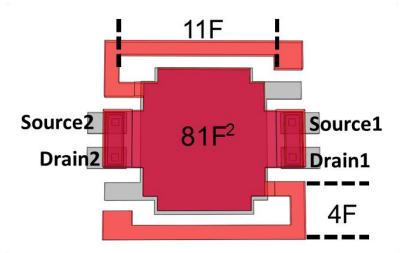

Fig. 2.13 Plan-view schematic of a 6-terminal relay design comprising two folded suspension beams. F is the minimum feature size, which is also the contact dimple width.

|                       | NEM Relay |     |     | CMOS |

|-----------------------|-----------|-----|-----|------|

| Technology Node (nm)  | 15        | 11  | 8   | 8.4  |

| Actuation Gap (nm)    | 5.5       | 4   | 3   | N/A  |

| Pull-in Voltage (mV)  | 113       | 100 | 86  | 610  |

| Switching Energy (aJ) | 1.1       | 0.6 | 0.3 | 1.28 |

Table 2.1 Relay technology scaling projections compared against 8 nm CMOS technology [18].

2.12) in polycrystalline films worsens with decreasing thickness, however. Thin-film process refinements are needed to mitigate this issue.

3) The actuation and contact dimple gaps should be as small as possible, and generally are limited by the sacrificial material deposition and selective etch (for structural release) process capabilities. It is desirable to have a conformal deposition process that can uniformly deposit films of thickness below 5 nm, and a release process than can have etchants undercut the structure and create nanometer-scale air gaps. Previous work on nanogap formation shows that, a gap of 3 nm can be successfully released using vapor-HF; however, a deposition process more uniform than LPCVD SiO<sub>2</sub> is desired.

Fig. 2.14 Energy band diagram of a metal-insulator-metal tunnelling junction with an applied bias of V. The insulator is an air gap and the barrier height is the work function  $(\chi_W)$  of the contact metal.

### 2.5 Switching Energy Projection of Ultimately Scaled Relays

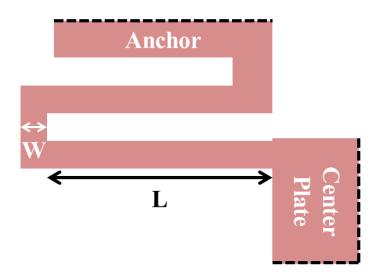

Using the model developed in Section 2.3, projections of switching energy can be made for ultimately scaled relay technology for comparison against CMOS technology. Fig. 2.13 shows the layout of the NEM relay structure studied herein, which comprises two folded-flexure suspension beams to reduce the spring stiffness. The technology node is defined by the smallest lithographically defined dimension, *i.e.* the dimple contact width. The switching energy is estimated by using FEM simulation tool Coventorware<sup>TM</sup> [14] to determine V<sub>PI</sub> and to calculate the on-state capacitance.

Table 2.1 shows the projection for ultimately scaled relays at various technology nodes, compared with the switching energy of a comparably scaled CMOS technology according to the latest ITRS predictions [15]. It shows that the active switching energy of a relay can be competitive, if the contact adhesive force is negligible. In order to discover the energy efficiency limit of an ultimately scaled NEM relay, surface adhesion in nano-scale contacts must be investigated.

### 2.6 Noise Considerations for Ultimately Scaled NEM Relays

Due to the nature of mechanical devices having air gaps and moving structures, there are concerns that a relay would be affected by noise, either due to tunneling current, gravitational force or thermal vibration, especially for relays with nanometer-scale gaps. These concerns are addressed in this section.

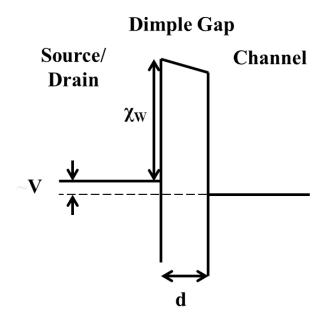

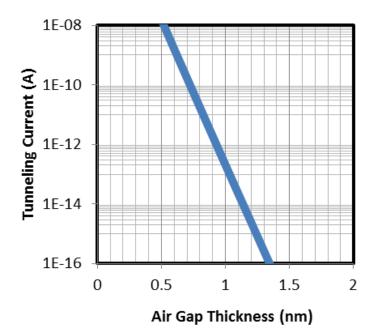

**Fig. 2.15** Direct tunnelling current vs. air gap thickness for an 8nm x 8nm contact dimple with a contact voltage of 100 mV. For off-state leakage current to be less than 10 fA,  $g_d$  should be larger than 1.1 nm.

#### 2.6.1 Direct Tunneling Through the Contact Gap

The greatest advantage of a MEM relay is that there is negligible current flow through the air gap in the OFF state. However this may no longer be true for extremely scaled relays, since significant direct tunneling can occur across a nanometer-scale gap with sufficient applied voltage across the gap.

Tunneling current of a metal-insulator-metal junction is well studied and estimated based on the model illustrated in Fig. 2.14. The two flat contact metal surfaces are separated by air, mimicking a mechanical contact. The direct tunneling current density is given by [16] [17]:

$$J = J_o \{\varphi \exp\left(-A\varphi^{\frac{1}{2}}\right) - (\varphi + eV)\exp\left(-A(\varphi + eV)^{\frac{1}{2}}\right)$$

(2.16)

$$J_o = \frac{e}{2\pi h(\beta d)^2} \tag{2.17}$$

$$A = \frac{4\pi\beta d}{h(2m)^{\frac{1}{2}}}$$

(2.18)

where m is the electron mass, h is the Plank's constant,  $\varphi$  is the mean barrier height, V is the voltage applied and  $\beta$  is a correction factor (~1). The calculated direct tunneling current is

shown in Fig. 2.15 for an 8 nm wide contact, assuming 100 mV is applied across the tunnel junction according to the ultimately scaled relay predictions ( $V_{PI} = 86 \text{ mV}$ ) and barrier height according to the Tungsten work function [18]. It can be seen that, to limit the off-state leakage below 10 fA for an ultimately scaled NEM relay, the contact gap has to be larger than 1.1 nm.

#### 2.6.2 Gravitational and Acceleration Forces

It is a common concern that a NEM relay would accidentally turn on if the device is dropped to the ground or it is experiencing acceleration. However due to the extremely low structural mass, the amount of deflection caused by gravitational force is extremely small. The calculated result of an ultimately scaled 8 nm relay is shown below [19]:

$$z_{gravity} = \frac{mg}{k_{eff}} = \frac{1.03 \times 10^{-18} N}{0.0435 \frac{N}{m}} \approx 23 \times 10^{-18} m$$

(2.19)

Using a similar calculation, it can be shown that the acceleration required to turn the relay on is extremely large:

$$a = \frac{k_{eff}g_d}{m_{eff}} = \frac{8.7 \times 10^{-11}N}{10^{-19}kg} = 8.7 \times 10^8 \frac{m}{s^2} \approx 8.8 \times 10^7 G$$

(2.20)

As a result, NEM relays should not be effected by gravitational and acceleration forces.

#### 2.6.3 Thermal Vibrations

Even at room temperature, there is concern that there can be enough thermal energy to create thermal vibrations and would turn a scaled relay on, especially with an ultimately scaled contact gap. Assuming a scaled 8nm NEM relay at room temperature, the amount of deflection can be approximated as the following calculation:

$$z_{thermal} = \sqrt{\frac{kT}{k_{eff}}} \approx 3.4 \times 10^{-10} m \tag{2.21}$$

which is much smaller than the minimum contact gap. Therefore, thermal vibrations should not be an issue in the operating temperature range of interest.

### 2.7 Summary

A scaled relay technology shows promise for ultra-low power digital logic applications. Proofof-concept prototype devices exhibit ideal switching properties such as zero off-state leakage current and nearly infinite local subthreshold slope, which potentially can provide for extremely low operating voltage. However, due to a relatively large device footprint and pull-in voltage ( $V_{PI}$ ), the active switching energy is significantly larger than for a CMOS transistor. Moreover, hysteresis is observed due to contact adhesive force ( $F_A$ ), resulting in finite effective subthreshold slope and limiting the minimum operating voltage. Scaling is needed to minimize the switching energy as well as the operating voltage.

The switching energy of a relay is dominated by the energy required to charge and discharge the parallel plate (or gate to body) capacitor. The simple model derived herein shows that the key to minimizing the switching energy is to reduce g and  $k_{eff}$ , where the minimum g possible is limited by fabrication process capabilities and the minimum  $k_{eff}$  possible is limited by F<sub>A</sub>. It is shown by FEM simulations that ultimately scaled NEM relays potentially can have switching energy less than 1 aJ, assuming that F<sub>A</sub> is negligible. The following chapters will focus on understanding the source of F<sub>A</sub>, and process technology development to enable  $k_{eff}$  reductions, in order to realize the sub-aJ switching energy projected by FEM simulations.

## **2.8 References**

[1] R. H. Dennard, J. Cai, and A. Kumar, "A Perspective on Today's Scaling Challenges and Possible Future Directions," Elsevier Solid-State Electronics, Vol. 51, No. 4, pp. 518-525, 2007.

[2] I. Chen, L. Hutin, C. Park, R. Lee, R. Nathanael, J. Yaung, J. Jeon and T.-J. K. Liu, "Scaled micro-relay structure with low strain gradient for reduced operating voltage," The 221th Electrochemical Society Meeting, May 2012.

[3] M. K. Tripp, C. Stampfer, D. C. Miller, T. Helbling, C. F. Herrmann, C. Hierold, K. Gall, S. M. George, and V. M. Bright, "The Mechanical Properties of Atomic Layer Deposited Alumina for Use in Micro- and Nano-Electro-Mechancal Systems," Elsevier Sensors and Actuators A: Physical, vol. 130-131, pp. 419-429, August 2006.

[4] T. Bakke, J. Schmidt, M. Friedrichs, and B. Völker, "Etch Stop Materials for Release by Vapor HF Etching," in Proceedings of the 16th Workshop on Workshop on Micromachining, Micromechanics, and Microsystems (MME '05), pp. 103-106, September 2005

[5] HP 4155B Semiconductor Parameter Analyzer Literature [Online] Available: http:// http://cp.literature.agilent.com/litweb/pdf/5968-6681E.pdf, Hewlett Packard Inc.

[6] R. Nathanael, V. Pott, H. Kam, J. Jeon, E. Alon, and T.-J. K. Liu, "Four Terminal Relay Body-biasing Schemes for Complementary Logic Circuits," IEEE Electron Device Letters, Vol. 31, No. 8, pp. 890–892, 2010.

[7] F. Chen, M. Spencer, R. Nathanael, C. Wang, H. Fariborzi, A. Gupta, H. Kam, V. Pott, J. Jeon, T.-J. K. Liu, D. Markovic, V. Stojanovic, and E. Alon, "Demonstration of Integrated Micro-electro-mechanical Switch Circuits for VLSI applications," in Proceedings of the IEEE International Solid-State Circuits Conference Technical Digest, pp. 150–151, 2010.

[8] M. Spencer, F. Chen, C. Wang, R. Nathanael, H. Fariborzi, A. Gupta, H. Kam, V. Pott, J. Jeon, T.-J. King Liu, D. Markovic, E. Alon, and V. Stojanovic, "Demonstration of integrated micro-electro-mechanical relay circuits for VLSI applications," IEEE Journal of Solid-State Circuits, Vol. 46, No. 1, pp. 308-320, 2011.

[9] H. Kam, T.-J. K. Liu, V. Stojanovic, D. Markovic, and E. Alon, "Design, Optimization, and Scaling of MEM Relays for Ultra-low-power Digital Logic," IEEE Transactions of Electron Devices, Vol. 58, No. 1, pp. 236–250, 2011.

[10] S. D. Senturia, "Microsystems Design," Kluwer, 2001

[11] H. Kam, "MOSFET Replacement Devices for Energy-Efficient Digital Integrated Circuits," Ph.D. Thesis, University of California, Berkeley, 2009

[12] H. Kam, V. Pott, R. Nathanael, J. Jeon, E. Alon, and T.-J. K. Liu, "Design and Reliability of a Micro-relay Technology for Zero-standby-power Digital Logic Applications," IEEE International Electron Devices Meeting Technical Digest, pp. 809-811, 2009.

[13] H. Kam, T.-J. K. Liu, V. Stojanovic, D. Markovic, and E. Alon, "Design, Optimization and Scaling of MEM Relays for Ultra-low-power Digital Logic," IEEE Transactions on Electron Devices, Vol. 58, No. 1, pp. 236-250, 2011.

[14] MEMS+ 2.1 User Guide and Reference, Coventor Inc. Cary, NC, 2011

[15] International Technology Roadmap for Semiconductors, 2012 Edition, [Online] Available: http://www.itrs.net/reports.html

[16] J. G. Simmons, "Generalized Formula for Electric Tunnel Effect between Similar Electrodes Separated by a Thin Insulating Film," Journal of Applied Physics, 34, pp. 1793-1803, 1963.

[17] Y. Isono, H. Nakano, "Measurement of Tunneling Current through Al/polyimide Langmuir-Blodgett film/Al Structure," Journal of Applied Physics, 75, pp. 4557, 1994

[18] R. W. Strayer, W. Mackie, L. W. Swanson, "Work Function Measurements by the Field Emission Retarding Potential Method," Surface Science, Vol. 34, No. 2, pp. 225-248, 1973.

[19] J. P. Dismukes, L. Ekstrom, and R. J. Paff, "Lattice Parameter and Density in Germanium-Silicon Alloys," The Journal of Physical Chemistry 68, No. 10, pp. 3021-3027, 1964.

## **Chapter 3**

## **Study of Contact Adhesive Force**

## **3.1 Introduction**

The adhesive force between contacting surfaces in the on state determines the minimum spring restoring force required for the relay to turn off in the absence of an applied electrostatic force. In turn, the spring restoring force determines the minimum electrostatic force and hence the minimum applied voltage required to turn on the relay. As a result, the minimum energy required to operate a relay is set by the contact adhesive force, which can depend on various factors such as the contact material, area and surface properties (which can depend on the device operating conditions) [1].

In this chapter, contact adhesive force in prototype MEM relays is investigated. Firstly, common causes of adhesion are discussed in Section 3.2. Then, experimental results for prototype relays with different contact dimple areas are presented in Section 3.3. Theoretical predictions of contact adhesive force are presented in Section 3.4, followed by projections of relay switching energy accounting for contact adhesive force in Section 3.5. Experimental investigations of surface coatings to mitigate adhesion are presented in Section 3.6.

#### **3.2 Common Sources of Adhesion**

It is important to identify the primary source(s) of contact adhesion so that appropriate measures can be taken to mitigate it. The most common sources of adhesion in micro-electro-mechanical devices include capillary force, van der Waals force, and bonding [2]. The mechanism which is dominant will depend on the contacting surface properties and device operating conditions.

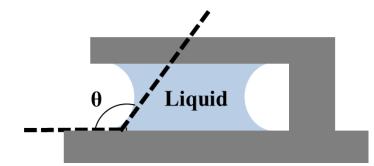

Fig. 3.1 Schematic illustration of capillary force due to liquid condensation during a wet release process. The contact angle between the liquid and the contact surface is  $\theta$ , and the surface is assumed to be hydrophilic in this diagram.

#### **3.2.1 Capillary Force**

To form the actuation and contact air gaps in a relay, a sacrificial material such as  $SiO_2$  is selectively removed from the regions between the actuation electrode and the structure, and between the contacting electrodes [3].  $SiO_2$  is commonly removed using a liquid hydrofluoric acid (HF) etchant. The exposed surfaces can be hydrophilic, such that a strong capillary force develops when the structure is pulled out from the liquid (either the etchant or a subsequent water rinse bath). The capillary pressure between surfaces created in this situation is given by the following equation [4] [5]:

$$P_L = \frac{2\gamma_l \cos\theta}{d} \tag{3.1}$$

where  $\gamma_1$  is the surface tension, d is the separation between two surfaces and  $\theta$  is the contact angle between the liquid and the solid surface. If the surface is hydrophilic, *i.e.*  $\theta < 90^\circ$ , there will be a strong attractive capillary force between the two surfaces. An illustration is shown in Fig. 3.1.

There are alternative techniques to release micro-mechanical structures without using a wet HF etch. For example, vapor-phase HF can be used. Although it has a slower etch rate, it allows devices to be released without immersion in liquid, to mitigate stiction.

Even with a dry release etch process there can still be capillary forces, *e.g.* during device operation. Water vapor can condense into small cracks and pores creating capillary force, a phenomenon called capillary condensation. The capillary condensation force is given by the following equation [1]:

$$F = \frac{2\gamma_l d_0 \cos\theta}{d^2} \tag{3.2}$$

Fig. 3.2 Illustration of van der Waals force between surfaces.

$$d_0 = \frac{2\gamma_l v cos\theta}{RT \log(\frac{P}{PSat})}$$

(3.3)

where R is the Bozeman constant, T is absolute temperature;  $P/P^{sat}$  is the relative humidity. Capillary condensation can be minimized or eliminated by hermetically sealed packaging.

#### 3.2.2 van der Waals Force

Van der Waals force is an attractive force originating from interactions between instantaneous dipole moments of atoms. Assuming two parallel flat surfaces, the van der Waals force can be modeled by the following equation [5]:

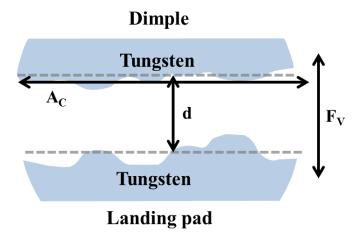

$$F_V = \frac{HA_c}{6\pi d^3} \tag{3.4}$$

where H is the Hamaker constant, d is the distance between the two surfaces and  $A_C$  is the contact area. d cannot be infinitesimally small, due to repulsion between surfaces in extremely close contact; the minimal distance is typically in the range from 0.2 nm to 0.7 nm [6]. An illustration of van der Waals force between surfaces is shown in Fig. 3.2.

Equation 3.4 assumes that the separation between surfaces is smaller than the characteristic length ( $z_0$ ) of approximately 20 nm. If the separation is larger than this, the van der Waals force is retarded and can be more accurately modeled by the following equation [7]:

$$F_V = \frac{HA_c}{6\pi d^3} \frac{z_0}{(d+z_0)}$$

(3.5)

Ideally the contact gap of a micro/nanometer-scale relay should be less than 20 nm; hence Equation 3.4 is relevant. If the van der Waals force dominates the force of adhesion ( $F_A$ ), then it should scale down with the contact area.

## **3.2.3 Hydrogen Bonding**

Surface hydroxyl groups can form strong hydrogen bonds when the separation between surfaces is very small [8], *i.e.* when the surfaces are in contact. The strength of the hydrogen bond is between 10 and 40 mJ/mol.

Due to surface roughness, the actual area of physical contact can be significantly smaller than the area of the dimpled contact region. If the contact dimple area is much larger than an asperity, then physical contact is made only at a few asperities and  $F_A$  should be relatively independent of the dimple area. If the dimple area is smaller than an asperity, then  $F_A$  should scale with the dimple area.

## 3.3 Characterization of Relay Contact Adhesion

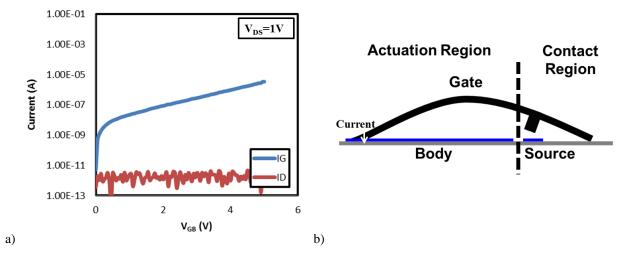

Contact area and surface properties are major factors for adhesive force [9]; relays with contact dimple width ranging from 100 nm to 1.3  $\mu$ m are characterized herein to investigate the dependence of F<sub>A</sub> on dimple area, to identify the primary source of adhesion and to allow for more accurate prediction of scaled relay switching energy accounting for contact adhesion.

## 3.3.1 Experiment

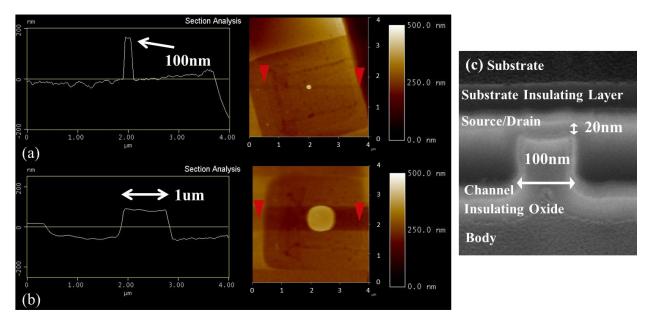

Relays of various contact sizes were fabricated to investigate contact adhesive force, using the same process flow as described in Section 2.2.2, but with drawn contact dimple width in the range from 100 nm to 1  $\mu$ m. During the contact dimple lithography process, larger features were overexposed in order to ensure that the minimum-sized feature sizes were printed. As a result, the fabricated devices have contact dimple widths in the range from 100 nm to 1.3  $\mu$ m, as measured by atomic force microscopy (AFM). Scanning electron microscopy (SEM) images of a fabricated relay with 100 nm contact dimple width, in plan view and in cross section, are shown in Fig. 3.3.

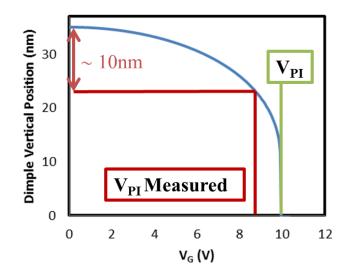

## 3.3.2 Adhesive Force Extraction from Electrical Measurements

The pull-in voltage ( $V_{PI}$ ) is the voltage at which the electrostatic force overcomes the spring restoring force, so the spring restoring force can be determined from the measured value of  $V_{PI}$ . The release voltage ( $V_{RL}$ ) is the voltage at which the electrostatic force is equal to the spring restoring force minus the contact adhesive force ( $F_A$ ). Therefore,  $F_A$  can be derived from the values of  $V_{PI}$  and  $V_{RL}$  as follows [10]:

**Fig. 3.3** SEM images of a MEM logic relay with ultra-small contact dimples: (a) plan view, (b) cross-sectional view of contact dimple region, (c) cross sectional view through the channel region.

$$V_{PI} = \sqrt{\frac{8k_{eff}g^3}{27\varepsilon_0 A_{OV}}} \tag{3.6}$$

$$V_{RL} = \sqrt{\frac{2(k_{eff}g_d - F_A)(g - g_d)^2}{\varepsilon_0 A_{OV}}}$$

(3.7)

$$F_A = \frac{27\varepsilon_o A_{OV}g_d}{8g^3} V_{PI}^2 - \frac{\varepsilon_o A_{OV}}{2(g-g_d)^2} V_{RL}^2$$

(3.8)

#### **3.3.3 Observations of Fabricated Relays**

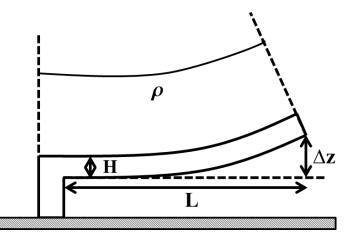

From Equation 3.8 it can be seen that in order to determine  $F_A$ , the values of the as-fabricated actuation gap (g), contact gap (g<sub>d</sub>) and actuation area (A<sub>OV</sub>) are needed. A<sub>OV</sub> is found to be approximately the same as designed. Ideally, g<sub>d</sub> and g should be determined by the thicknesses of the sacrificial layers formed during the device fabrication process. However, this is not the case due to the effects of 1) non-conformal thin-film deposition within the contact dimple region, causing g<sub>d</sub> to be smaller than designed; and 2) non-zero strain gradient within the structural

Fig. 3.4 Schematic cross-sections showing how g and  $g_d$  change due to a negative strain gradient within the structural layer causing the released structure to bend out of plane (primarily in the more compliant folded-flexure suspension beam regions) and increase g and  $g_d$  by the amount  $\Delta g$ .

material that results in out-of-plane deflection which increases both g and  $g_d$  [11] as illustrated in Fig. 3.4.

In order to accurately determine the values of g and  $g_d$ , the relay structures were carefully lifted off the substrate using conductive carbon tape, and an AFM was used to measure the actual dimple height (H<sub>D</sub>), which is the difference between g and  $g_d$ . Fig. 3.5 shows the AFM scan of a 1 µm-wide dimple and a 100 nm-wide dimple, where the dimple height is measured. It can been seen from these measurements that the dimple height increases as the dimple width decreases, due to poor conformality of the LPCVD process used to deposit the sacrificial SiO<sub>2</sub> layers.

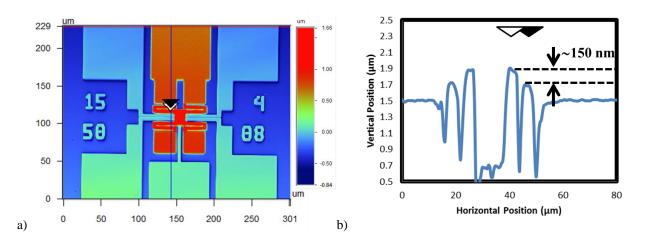

The amount of out-of-plane deflection ( $\Delta g$ ) of the relay structure can be determined from a surface map taken using an optical interferometry tool. An example is shown in Fig. 3.6. It is observed that the structure has a concave downward shape due to a negative strain gradient, with most of the out-of-plane deflection occurring along the folded-flexure suspension beams. The vertical deflection increases both g and g<sub>d</sub>, and is measured by comparing the vertical positions at the two ends of a folded-flexure beam. It is found that the deflection ranges from 100 nm to 200 nm, depending on the flexure beam length. Given these extracted values, the actual g and g<sub>d</sub> can be estimated as follows:

$$g = T_S + \Delta g \tag{3.9}$$

$$g_d = g - H_D = T_S + \Delta g - H_D \tag{3.10}$$

**Fig. 3.5** (a) AFM scan of a 100 nm-wide contact dimple (upside down). (b) AFM scan of a 1  $\mu$ m-wide dimple (upside down). (c) SEM cross section of a contact dimple for reference (shown upside-down as compared to Fig. 3.3b). Due to poor conformality of the LPCVD process, the 2<sup>nd</sup> sacrificial LTO layer is thinner in the contact region, so that the as-fabricated dimple gap (g<sub>d</sub>) is smaller.

where  $T_s$  is the total thickness of the sacrificial SiO<sub>2</sub> layers. Since the actual values of g and  $g_d$  depend on the lengths of the folded flexures and the contact dimples, g and  $g_d$  was measured for each relay design.

#### **3.3.4 Electrical Measurement Results**

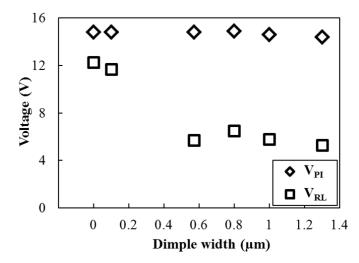

Fig 3.7 shows measured values of  $V_{PI}$  and  $V_{RL}$  for relays of various contact dimple areas [12]. The data shown is for a set of relay devices that have the same structure and gap dimensions with contact dimple width as the only design variation.  $V_{PI}$  is approximately the same for all of the devices, confirming that they have the same structure.

The difference between  $V_{PI}$  and  $V_{RL}$  is the hysteresis voltage. It is observed that the hysteresis is roughly the same for relays with large contact dimples, and that the hysteresis is dramatically lower for the relays with the smallest contact dimples suggesting a significant reduction in  $F_A$ .

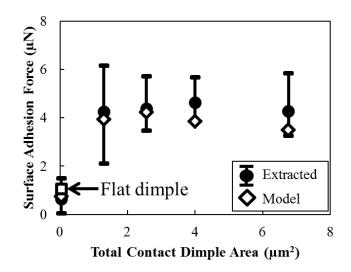

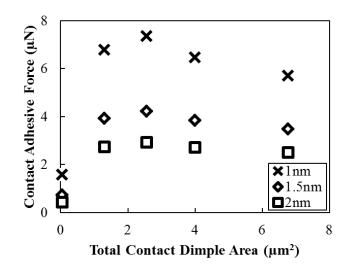

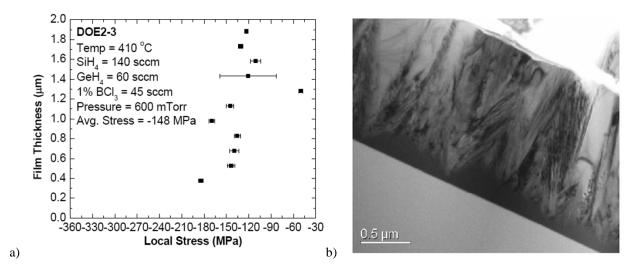

The adhesive force extracted using the method described in Section 3.3.3 is shown in Fig. 3.8. For each value of contact dimple area, roughly 15 devices were measured. The larger contact dimples have contact adhesive force of roughly 4  $\mu$ N, almost independent of dimple size. The smallest contact dimple has significantly lower contact adhesive force, ~ 0.7  $\mu$ N. To explain these experiment results, theoretical modeling is necessary.

**Fig. 3.6** a) Surface topology of a MEM relay, obtained by optical interferometry. The out-of-plane deflection is extracted from the height difference between the flexure ends near the anchor and near the center plate. b) 1-D cutline profile showing an extracted out-of-plane deflection of 150 nm.

**Fig. 3.7** Measured pull-in and release voltages of MEM logic relays of various contact dimple sizes. Theoretical values for the case of zero adhesive force are shown for "0" dimple width, for reference. (Note that the hysteresis voltage in this case is due purely to pull-in mode operation.)

**Fig. 3.8** Extracted  $F_A$  vs. total contact dimple area. Modeling results assuming 1.5 nm dimple surface roughness are indicated with diamond symbols. Also shown is the modeling result for the case of a flat (non-curved) contact dimple surface.

#### **3.4 Modeling of Relay Contact Adhesion**

As mentioned in Section 3.2, the three most commonly observed sources of adhesion are capillary force, van der Waals force, and bonding. For a rough surface, contact is only made at a few asperities; the number of asperities that are in contact should be almost independent of the contact dimple area [13]. Given that bonds can only be made at the contacting asperities,  $F_A$  should be the same for all contact sizes if bonding were the dominant source of adhesion. Also, the relays in this work are operated in a nitrogen-purged environment, and hence should not suffer from stiction [14].

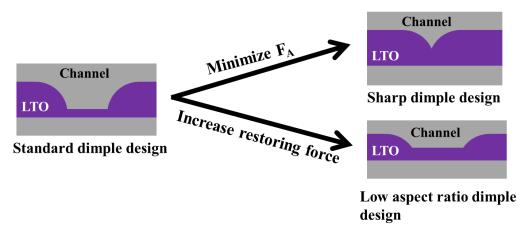

To estimate  $F_A$  due to capillary condensation, the surface profile must be investigated. From Fig. 3.5 it is observed that the contact dimple surface is curved instead of flat, due to nonconformality of the LPCVD SiO<sub>2</sub> process, illustrated in Fig. 3.9. Hence, only the perimeter of the dimple is in contact with the bottom electrode. From Equations 3.2 and 3.3, it can be estimated that capillary condensation is only significant when the distance between surfaces is less than 2 nm. Moreover, if capillary condensation were the dominant source of adhesion,  $F_A$ should be proportional to the contact dimple perimeter length, and hence show a linear dependence on contact dimple size, which is not seen in Fig. 3.8. The calculated value of capillary condensation force is not significant (< 0.1 µN) compared to the observed  $F_A$ . With neither bonding nor capillary force likely to be dominant, van der Waals force is the most likely dominant source of adhesion.

Equation 3.4 can be used to estimate the adhesive force between tungsten surfaces. However, one must be careful to consider the non-planar topography and roughness of the contact dimple surface.

**Fig. 3.9** Schematic cross section of a contact dimple. Due to poor conformality of deposition, the  $2^{nd}$  sacrificial LTO results in a curved dimple surface.

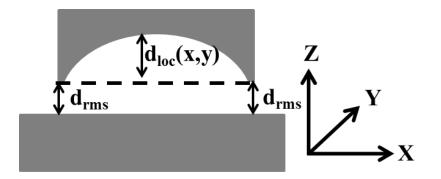

As shown in Fig. 3.9, the dimple surface is concave due to a non-conformal sacrificial-LTO deposition process. In contrast, the surface of the bottom electrode (which is contacted by the dimple when the relay is in the on state) is roughly planar. The van der Waals force at any location along the contact dimple surface is dependent on its separation from the bottom electrode surface, which depends on the curvature of the contact dimple surface as well as the surface roughness:

$$F_V = \int_{A_C} \frac{H dA}{6\pi (d_{loc}(x,y) + d_{rms})^3}$$

(3.11)

where  $d_{rms}$  is an equivalent root mean square (rms) roughness of the two contacting surfaces [15] and  $d_{loc}$  is the local distance between the two contacting surfaces due to the curved shape. The Hamaker constant used for tungsten is  $40 \times 10^{-20}$  J [16]. The roughness of the bottom electrode is measured by AFM. Since it is very difficult to measure the roughness of the contact dimple, estimations are made based on typical measured rms surface roughness of the 2<sup>nd</sup> sacrificial layer (SiO<sub>2</sub>). The modeled contact geometry is shown in Fig. 3.10.

The modeled van der Waals force is shown in Fig. 3.11 [17], for various values of rms surface roughness. It can be seen to be roughly independent of contact dimple size for total contact dimple areas larger than 1  $\mu$ m<sup>2</sup>, and to decrease significantly for the smallest total contact area (0.04  $\mu$ m<sup>2</sup>). This behavior can be explained qualitatively by the fact that, while the perimeter of the contact dimple decreases the average separation between contacting surfaces also decreases with decreasing contact size. However, for very small contact sizes the effect of the surface curvature becomes negligible, so that F<sub>A</sub> scales with contact size. The effect of decreasing average separation is more pronounced for lower surface roughness.

The modeled van der Waals force for 1.5 nm rms surface roughness well explains the experimental findings, as shown in Fig. 3.8. The large variation in  $F_A$  observed for the larger

**Fig. 3.10** Illustration of the modeled contact geometry. Surface roughness results in an average separation distance  $d_{rms}$ . The local separation distance between contacts is  $d_{total} = d_{rms} + d_{loc}$ . The radius of curvature for the top surface is 10.5µm, based on AFM measurements.

contacts is most likely due to variations in contact dimple surface curvature, which is confirmed by AFM measurements of several contact dimples. For reference, the van der Waals force assuming flat contacting surfaces is also shown in Fig. 3.8 for the smallest contact dimple area. Since the effect of surface curvature on  $F_A$  is relatively minor at that point, it can be used to estimate the van der Waals force per unit area: 0.02 nN/nm<sup>2</sup>.

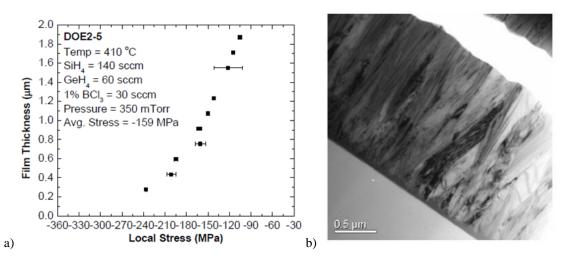

## 3.5 Relay Switching Energy Projections Accounting for Contact Adhesion

Table 3.1 shows the minimum switching energy values for a 100 nm (minimum feature size) relay and an 8 nm relay calculated using Equation 2.12, assuming a contact adhesive force of  $0.02 \text{ nN/nm}^2$ . The minimum switching energy of an 8 nm relay is 18 aJ instead of 0.3 aJ as projected in Chapter 2. Clearly, methods for reducing the contact adhesive force are desirable to reduce the switching energy of ultimately scaled relays to sub-aJ levels.

#### 3.6 Impact of Ultra-thin Surface Coating

In order to reduce the van der Waals force between contacts, one can increase the average distance between surfaces in the on state, or use contact materials with a lower Hamaker constant.

For a large contact dimple, the average contact distance can be increased by increasing the surface roughness [9]. However, this approach will not be effective for an ultimately scaled relay, since the contact dimple will comprise only one asperity.

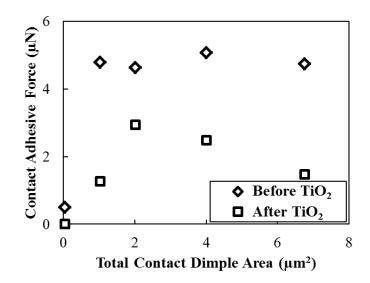

Table 3.2 compares the Hamaker constants for different materials [16] [18] [19]. It can be seen that oxides generally have much lower Hamaker constants than metals. However, oxides are poorer electrical conductors. Hence the use of an ultra-thin oxide coating is a more practical approach. To demonstrate this, relays were fabricated and electrically characterized before

Fig. 3.11 Modeled van der Waals force vs. total contact dimple area, for various values of rms roughness of the contact dimple surface. As surface roughness decreases, the average separation distance decreases and  $F_A$  increases.

|                        | NEM Relay           |      |                        | CMOS |

|------------------------|---------------------|------|------------------------|------|

| Technology Node (nm)   | 100                 | 8    | 8 (+TiO <sub>2</sub> ) | 8.4  |

| $F_a(nN)$              | 700                 | 4.5  | 1.7                    | N/A  |

| Actuation Gap (nm)     | 30                  | 3    | 3                      | N/A  |

| k <sub>eff</sub> (N/m) | 35                  | 2.25 | 0.85                   | N/A  |

| Pull-in Voltage (mV)   | 310                 | 100  | 61                     | 610  |

| Switching Energy (aJ)  | 2.8x10 <sup>4</sup> | 18   | 6.8                    | 1.28 |

Table 3.1 Scaled relay switching energy compared to 8 nm CMOS transistors [18].

further processing to apply an ultra-thin  $TiO_2$  coating (~0.5 nm) by atomic layer deposition [20]. The F<sub>A</sub> measurement results are shown in Fig. 3.12. It can be seen that the  $TiO_2$  coating provided for a significant reduction in F<sub>A</sub>.

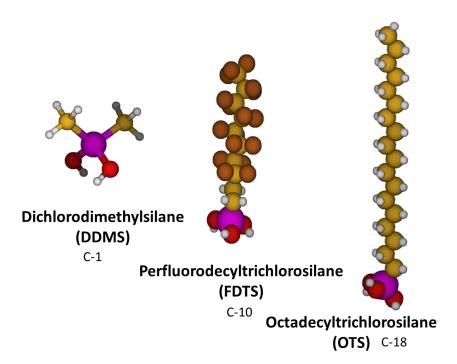

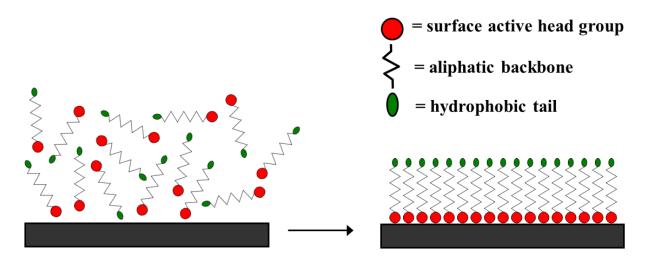

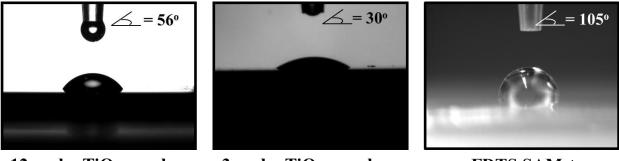

Organic coating materials also have been considered for MEM devices, since they tend to be hydrophobic and hence can reduce capillary force even in non-dry conditions [21] [22]. Some also have very low Hamaker constants. Self-assembled-monolayer (SAM) coating methods have been used to coat surfaces with organic films as thin as 1 nm depending on the size of the molecules [23]. In this work, Perfluorodecyltrichlorosilane (or FDTS) molecules were self-assembled onto relays after structural release. Some common molecules used for SAM coatings

| Material         | Hamaker Constant (10 <sup>-20</sup> J) |

|------------------|----------------------------------------|